5

www.vinafix.com

4

3

2

1

01

Dessert

D D

DDR4 2133MHz SODIMM1

8GB Max.

DDR4 2133MHz SODIMM2

8GB Max. DDR CHB

C C

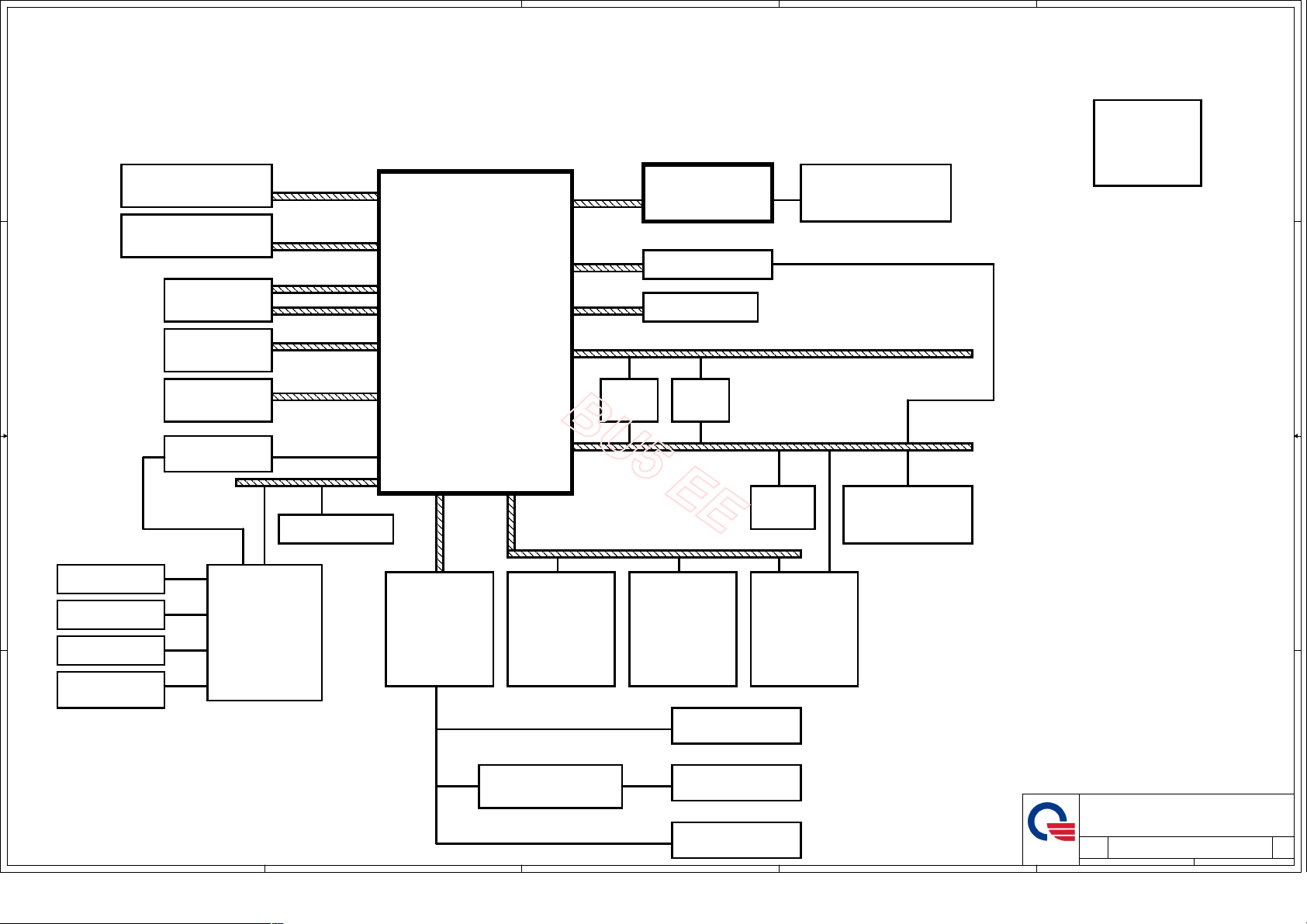

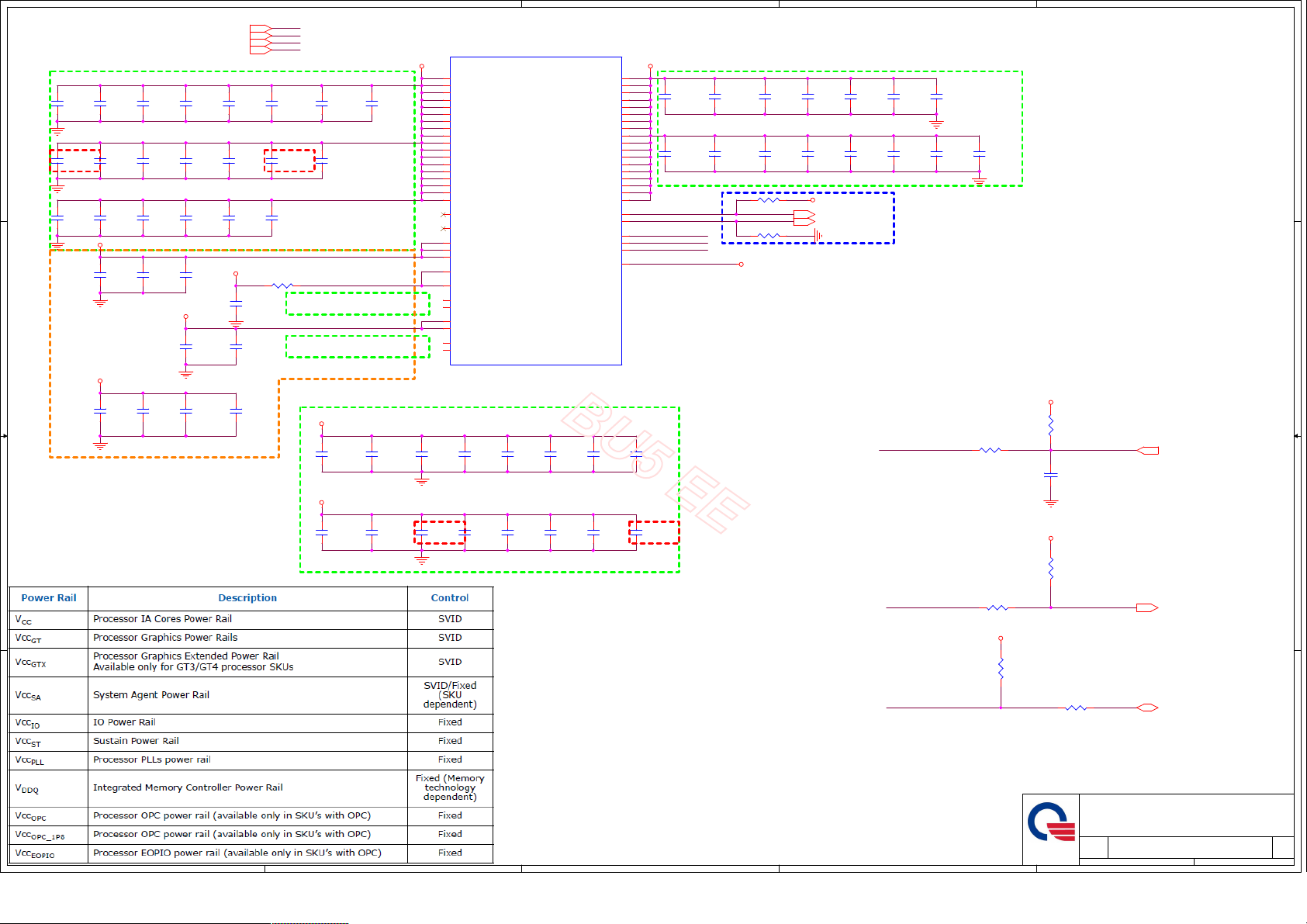

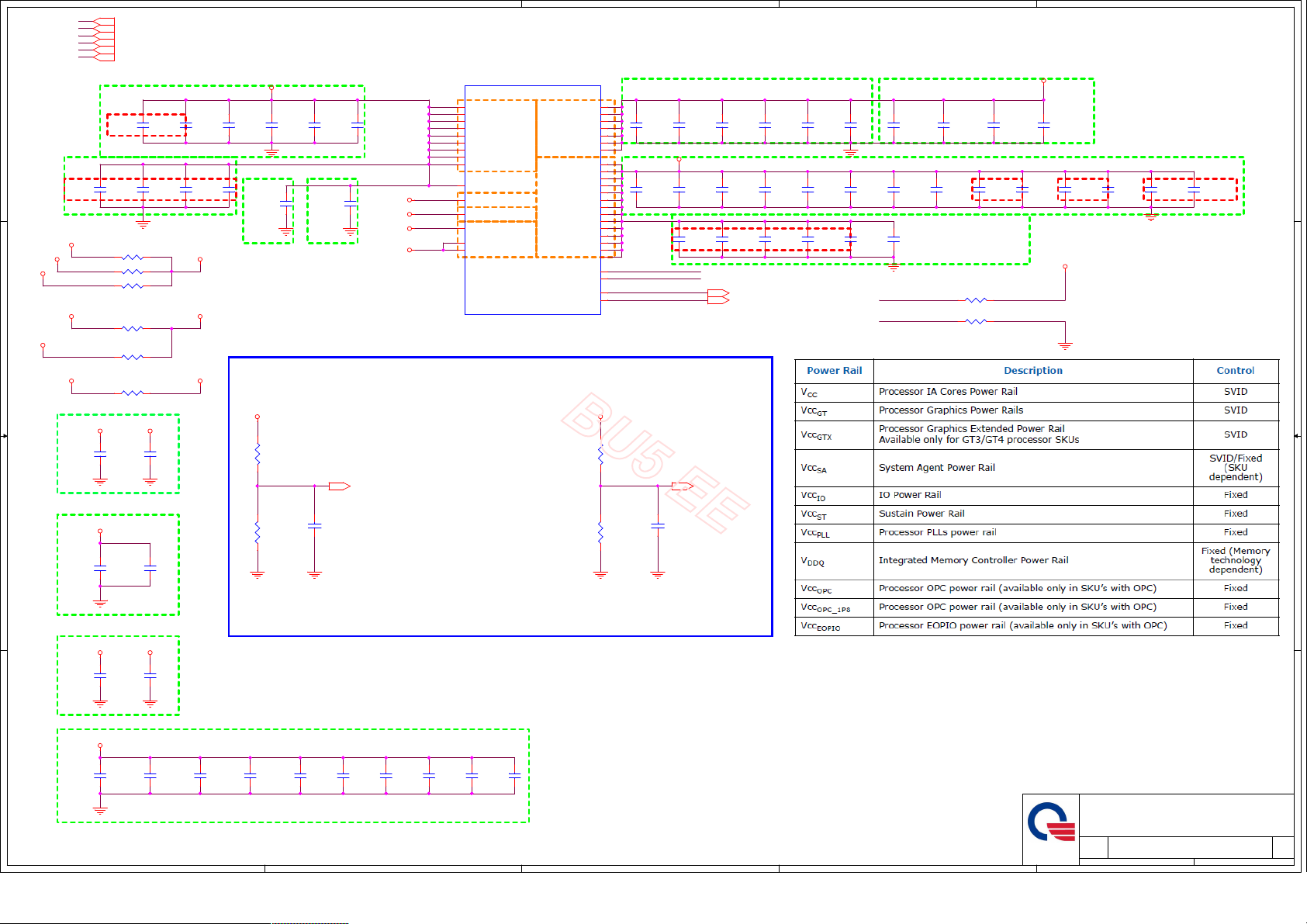

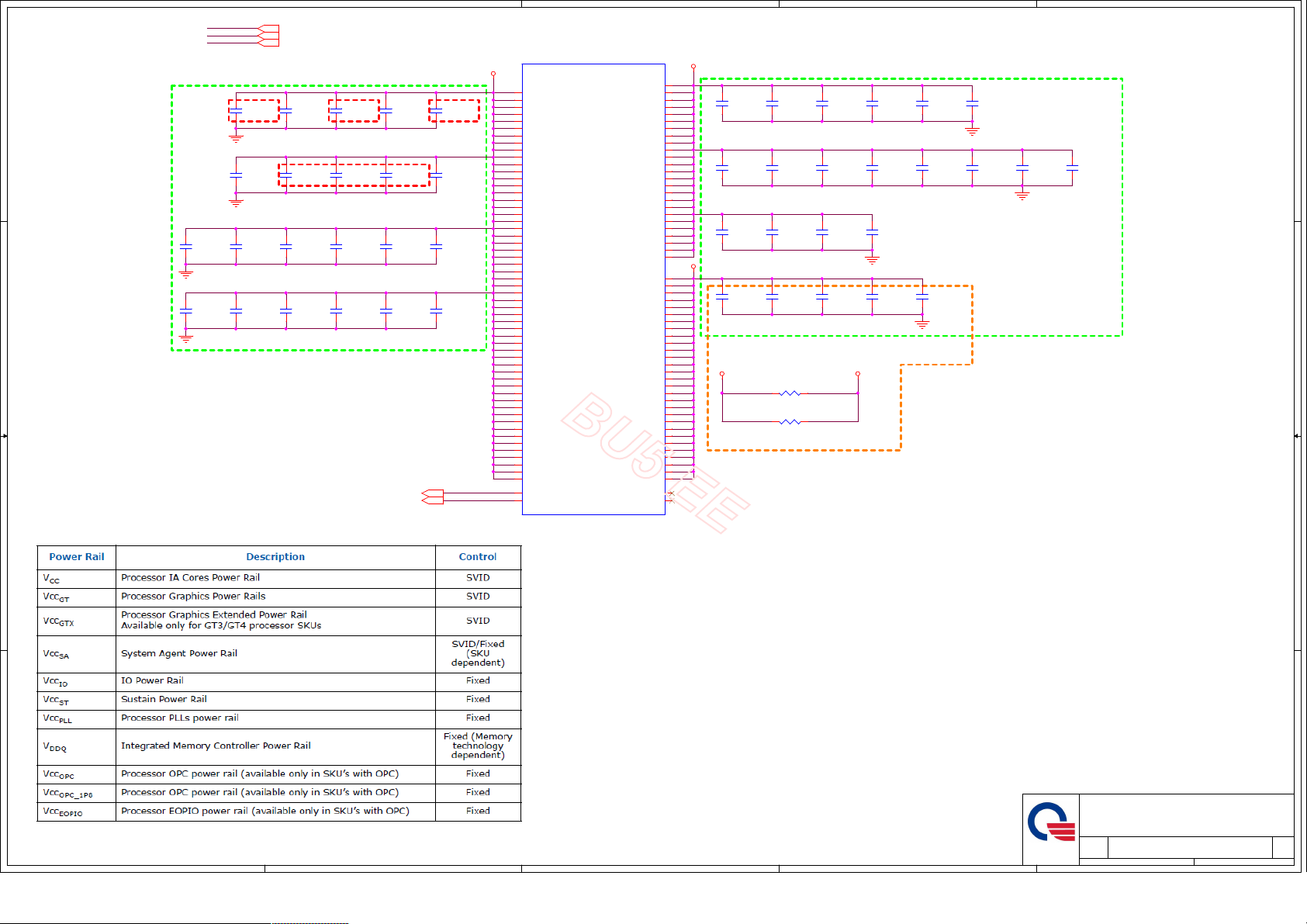

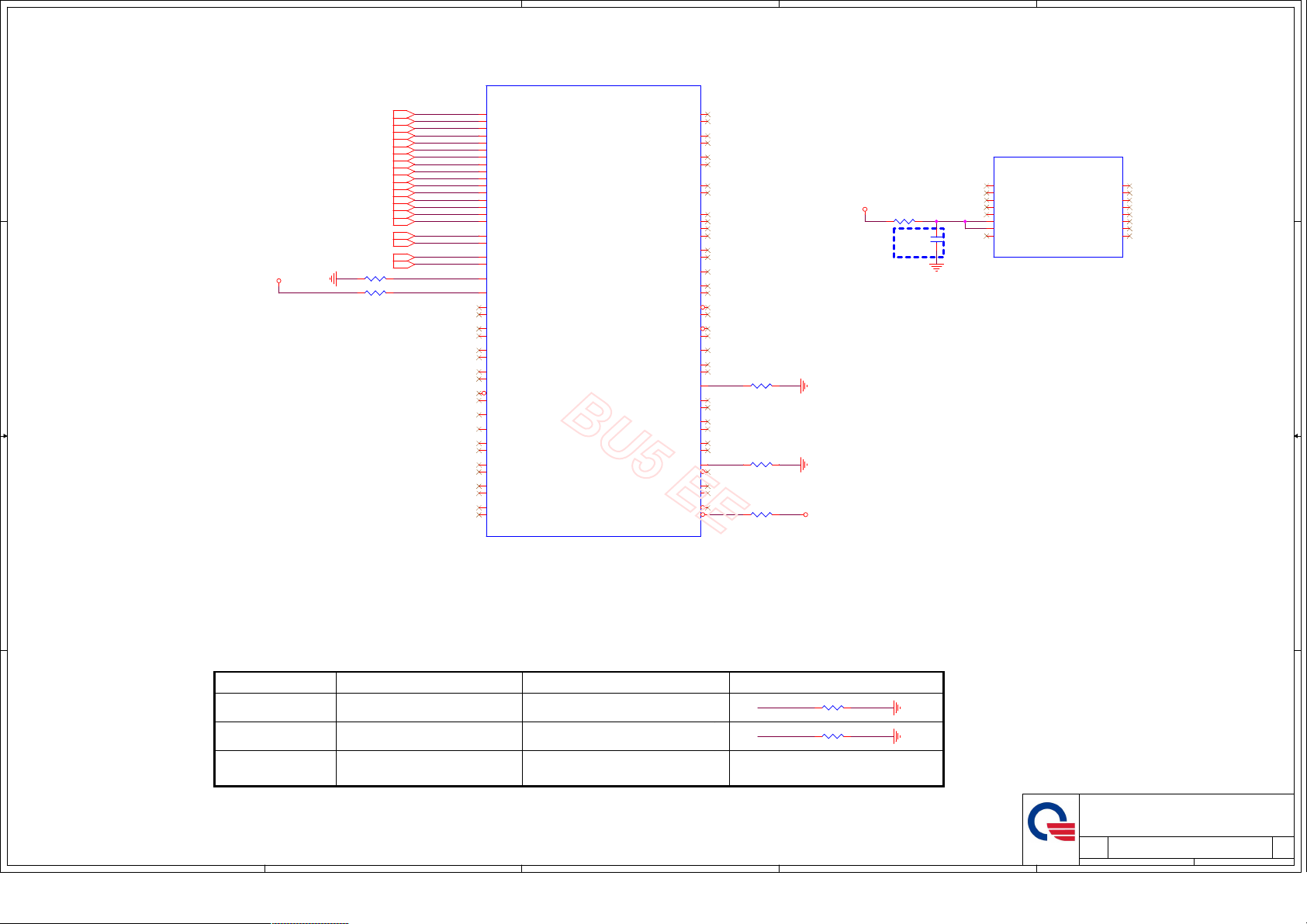

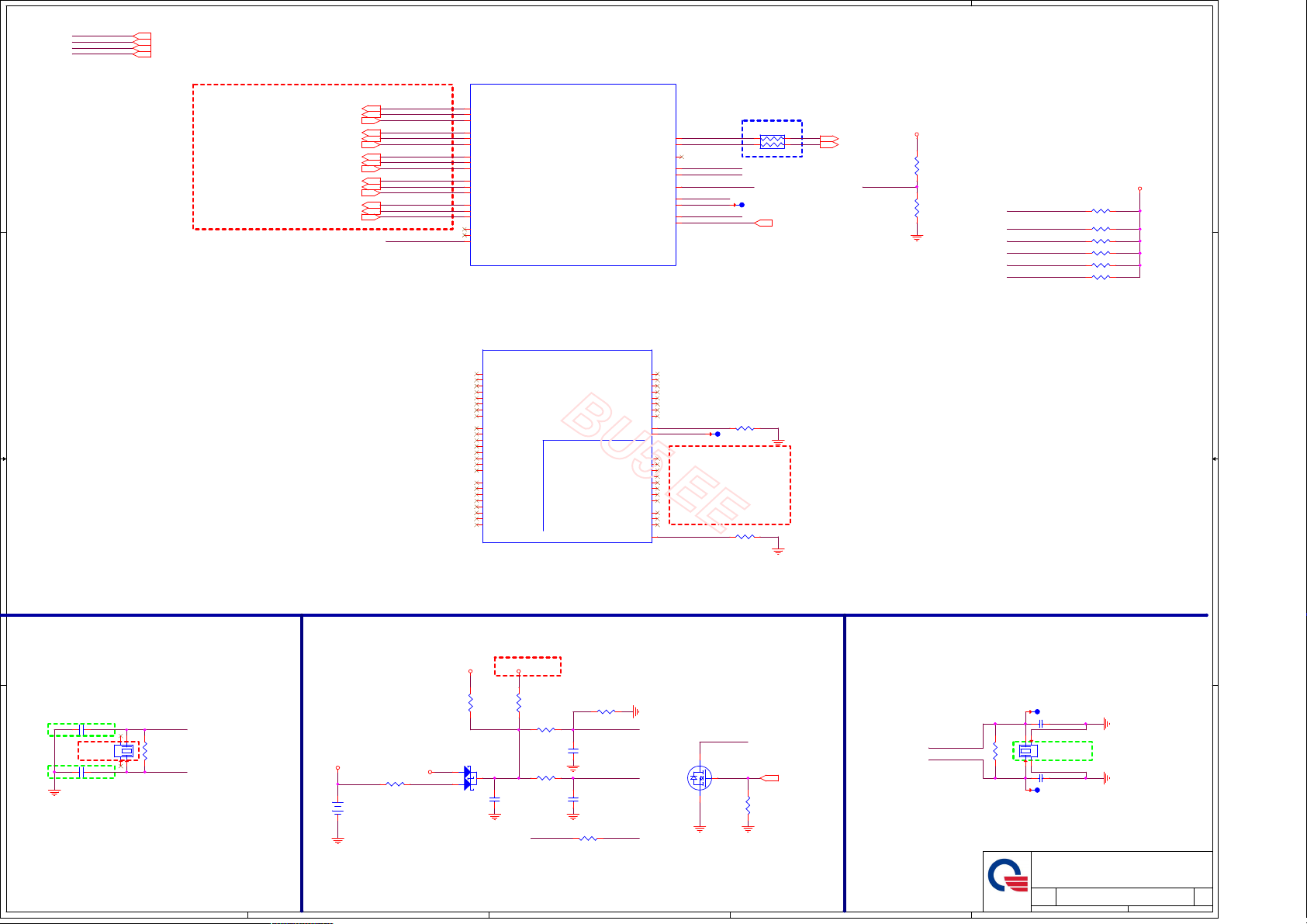

Intel SKL/KBL ULT Platform Block Diagram

PAGE 17

PAGE 18

M.2 2280-S3 SSD

SATA HDD

2.5" 7.2/9.5mm

Power :

9.0mm ODD 1.5GB/s

2.5" 7.2/9.5mm

Power : PAGE 34

PAGE 34

DDR4 2133MHz

DDR4 2133MHz

6GB/s

PCIEx2

6GB/s

DIS (15")

DDR CHA

SATA

PCIE

SATA

SKL/KBL U

Processor

Processor : Daul Core

Power : 15 (Watt)

Package : BGA1356

Size : 40 X 24 (mm)

USB3.0

PCIE

eDP

DDI

PCI-E

X4 Lane

eDP x4

USB3.0

USB2.0

CONN

PAGE 32

N16S-GTR-S

25W, 23x23mm

LCD Connector

HDMI V1.4

USB3.0

USB2.0

CONN

PAGE 33

PAGE 19~22

PAGE 27/27

PAGE 28

VRAM DDR3L

x4pcs

256Mx16 2.5GHz

512Mx16 2.5GHz

TOP

PCB 6L STACK UP

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1(High)

LAYER 4 : IN2(Low)

LAYER 5 : SVCC

LAYER 6 : BOT

PAGE 23~24

System BIOS

SPI ROM

B B

G-Sensor

HP3DC2TR PAGE32

Keyboard

Touch Pad

FAN

A A

PAGE 31

PAGE 31

PAGE 31

5

PAGE 10

PAGE 32TPM

SLB9665TT2.0 FW 5

Embedded Controller

iTE 8987

Power :

Package : LQPF128

Size : 14 x 14 (mm)

PAGE 35

SPI

LPC

HDA

Audio Codec

ALC3258-CG

Power :

Package : MQFN

Size : 6 x 6 (mm)

4

Azalia

PAGE 26

USB2.0

PAGE 2~16

PCIE

PCIE Gen 1 x 1 Lane

Card Reader

RTS5237S-GR

Power :

Package : LQPF48

Size : 7 x 7 (mm)

HP AMP

HPA022642RTJR

DB

LAN Controller

RTL8111HSH(Giga)

RTL8107EH(10/100)

Power :

Package : OFN32

DB

Speaker

Combo Jack

Digital MIC

3

Camera

Port 3

PAGE 28

M.2 Card

WLAN / BT Combo

Port 7

B

PAGE 29

PAGE 29

PAGE 28

PAGE 34

Touch Screen

Port 8

Elan EKTH3915 for 14",15"

Elan EKTH3918 for 17"

PAGE 32

2

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Block Diagram

Block Diagram

BU5

BU5

BU5

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

147Tuesday, January 05, 2016

147Tuesday, January 05, 2016

147Tuesday, January 05, 2016

1A

5

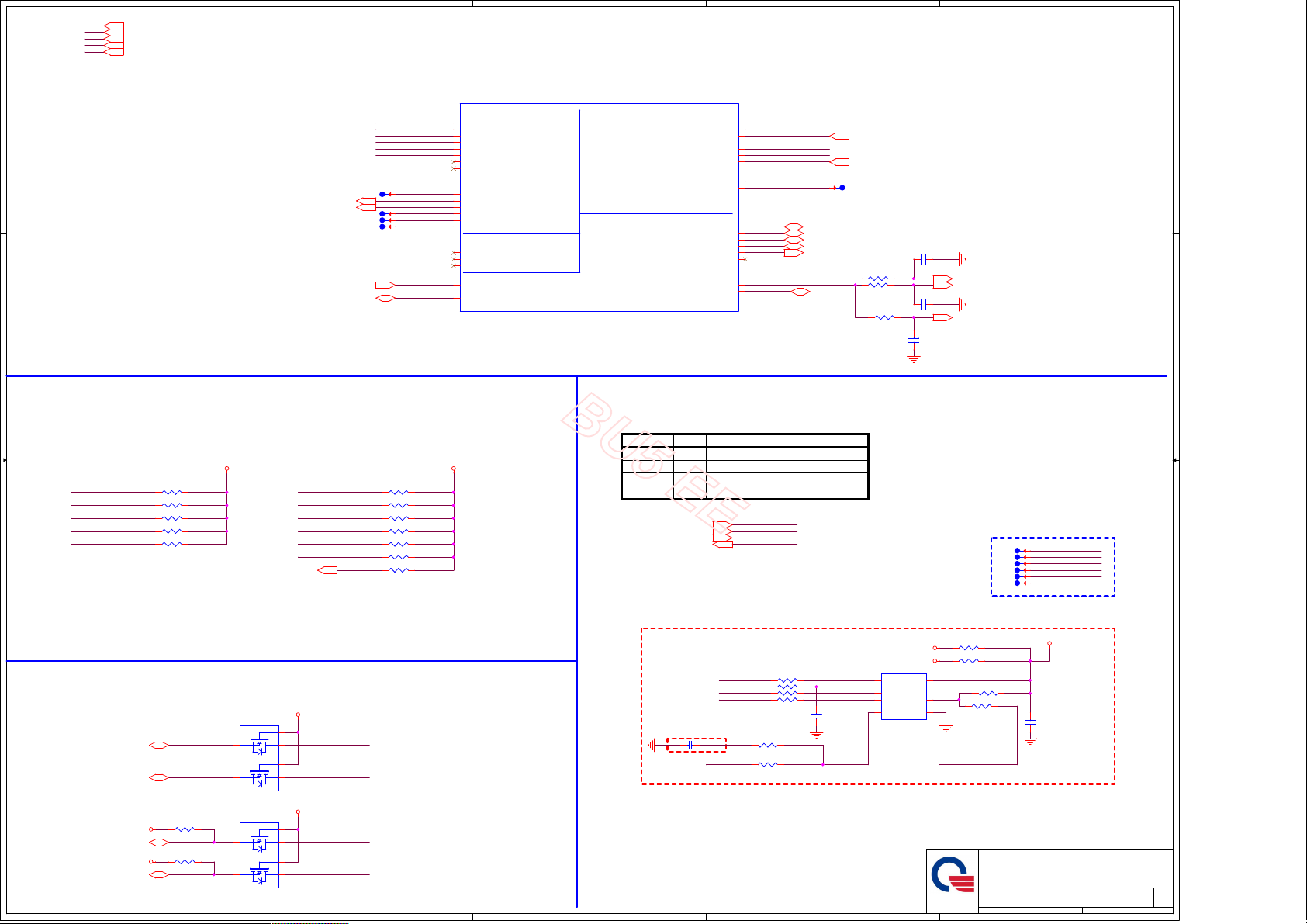

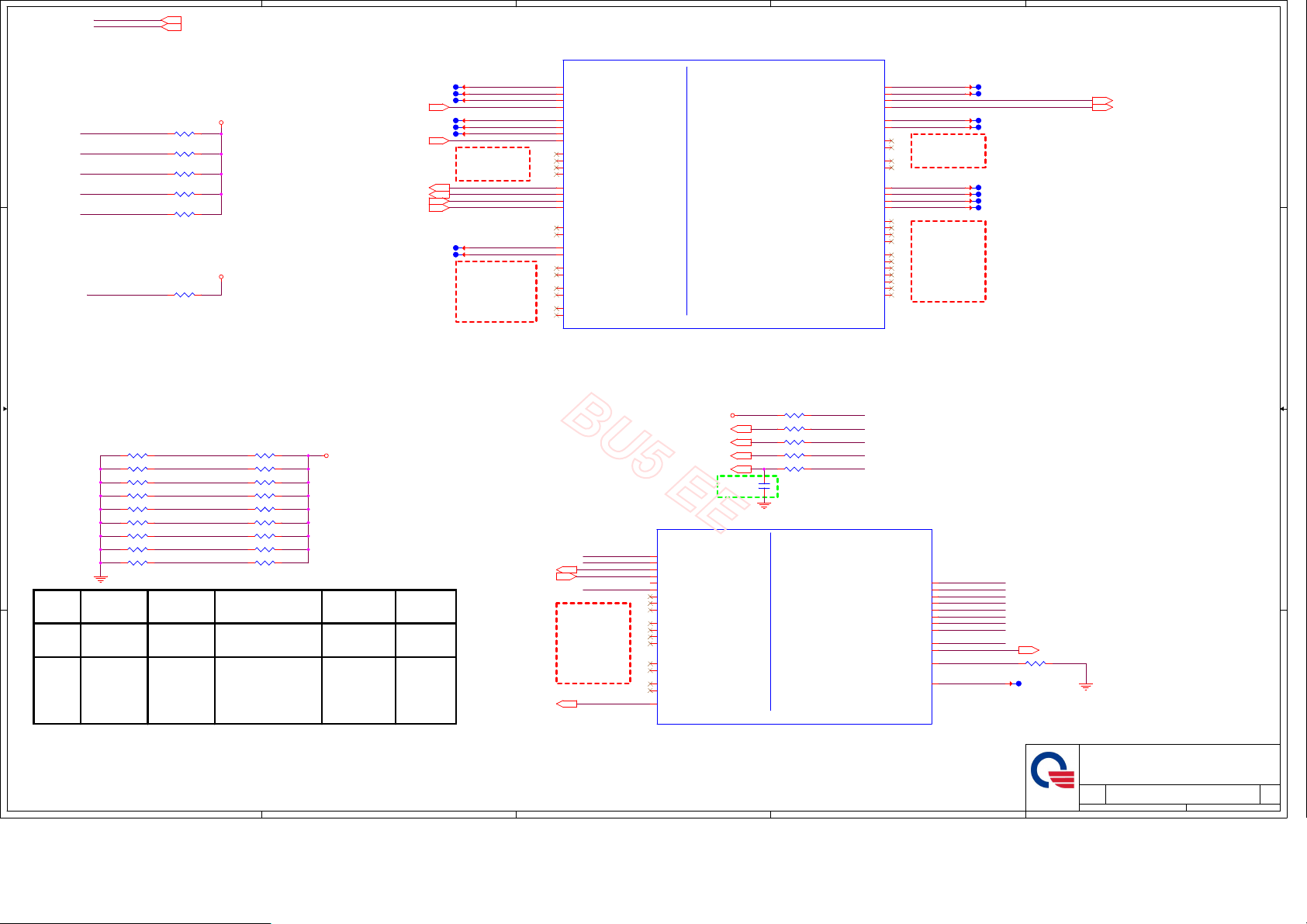

+3V [4,10,11,12,13,14,15,16,17,18,19,20,21,25,26,27,28,29,30,31,32,33,39,43,44,47]

+1.0V [4,6,16,33,38]

+VCCSTPLL [4,5,6,9,38,39]

D D

C C

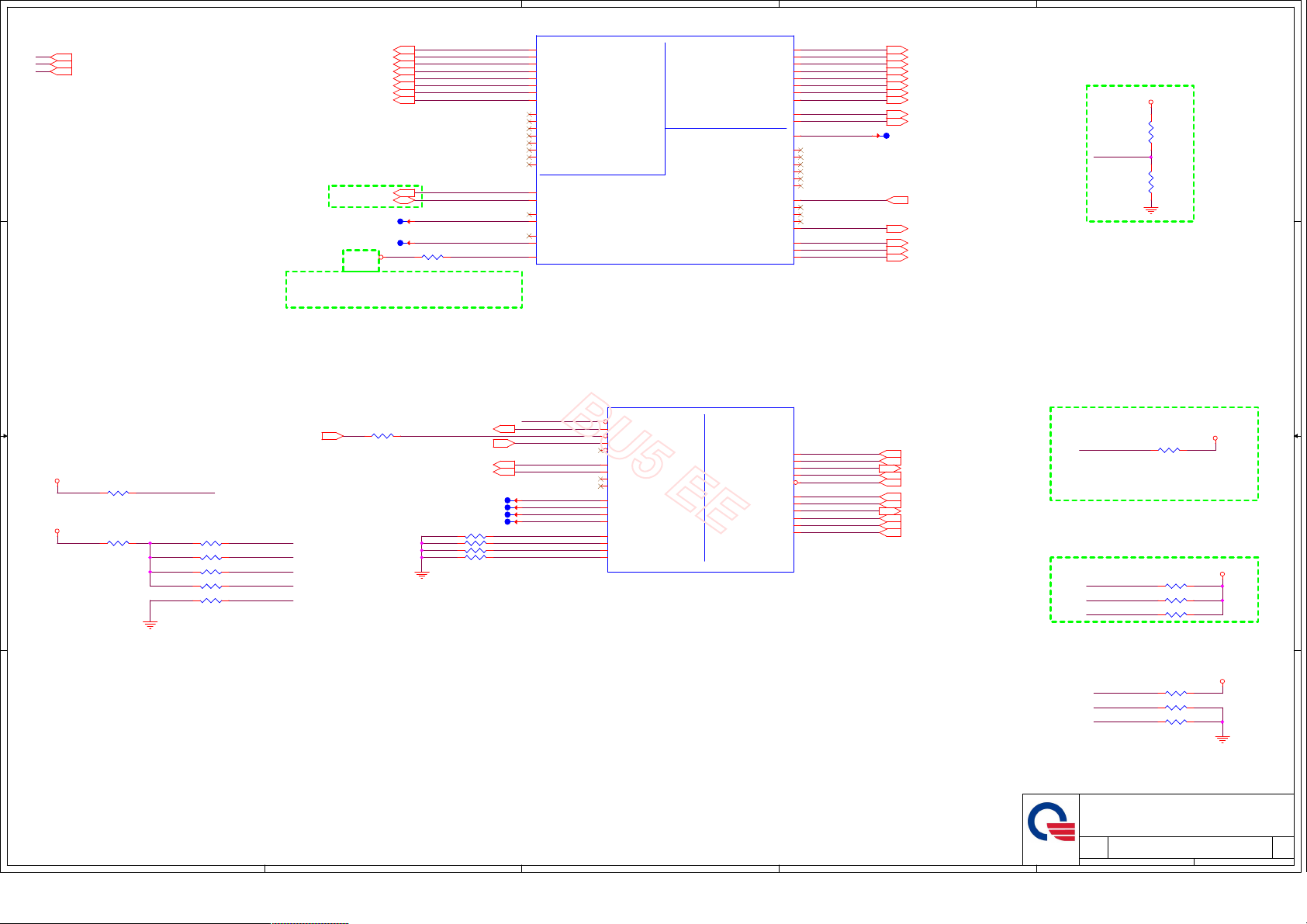

HDMI

eDP_COMPIO and ICOMPO signals should be shorted near

balls and routed with typical impedance <25 mohms

SDVO_CLK[27]

SDVO_DATA[27]

+VCCIO

IN_D2#[27]

IN_D2[27]

IN_D1#[27]

IN_D1[27]

IN_D0#[27]

IN_D0[27]

IN_CLK#[27]

IN_CLK[27]

TP2

TP3

4

IN_D2#

IN_D2

IN_D1#

IN_D1

IN_D0#

IN_D0

IN_CLK#

IN_CLK

DDPC_CTRLDATA

DDPD_CTRLDATA

R3 24.9/F_4

EDP_RCOMP

U1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

*SKL_ULT

REV = 1

SKL_ULT

DDI

DISPLAY SI DEBANDS

3

?

Need apply PN

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

2

need surport to UHD 3840x2160

C47

?1 OF 20

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

INT_EDP_T XN0

INT_EDP_T XP0

INT_EDP_T XN1

INT_EDP_T XP1

INT_EDP_T XN2

INT_EDP_T XP2

INT_EDP_T XN3

INT_EDP_T XP3

INT_EDP_A UXN

INT_EDP_A UXP

EDP_DISP_UTIL

HDMI_HPD_CON

ULT_EDP_HPD

PCH_LVDS_BLON

PCH_DPST_PWM

PCH_DISP_ON

INT_EDP_T XN0 [25]

INT_EDP_T XP0 [25]

INT_EDP_T XN1 [25]

INT_EDP_T XP1 [25]

INT_EDP_T XN2 [25]

INT_EDP_T XP2 [25]

INT_EDP_T XN3 [25]

INT_EDP_T XP3 [25]

INT_EDP_A UXN [25]

INT_EDP_A UXP [25]

TP1

HDMI_HPD_CON [27]

ULT_EDP_HPD [25]

PCH_LVDS_BLON [25]

PCH_DPST_PWM [25]

PCH_DISP_ON [25]

1

Reserve EDP_HPD opposites circuit!

+3V

R1

*10K/F_4

ULT_EDP_HPD

R2

100K_4

02

?

4 OF 20

Need apply PN

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

BOM

B61

XDP_TCK0

D60

XDP_TDI_CPU

A61

XDP_TDO_CPU

C60

XDP_TMS_CPU

B59

XDP_TRST#_CPU

B56

JTAG_TCK_PCH

D59

JTAG_TDI_PCH

A56

JTAG_TDO_PCH

C59

JTAG_TMS_PCH

C61

XDP_TRST#_CPU

A59

JTAGX_PCH

XDP_TCK0 [16]

XDP_TDI_CPU [16]

XDP_TDO_CPU [16]

XDP_TMS_CPU [16]

XDP_TRST#_CPU [2,16]

JTAG_TCK_PCH [16]

JTAG_TDI_PCH [16]

JTAG_TDO_PCH [16]

JTAG_TMS_PCH [16]

XDP_TRST#_CPU [2,16]

JTAGX_PCH [16]

2

Close to EC

PM_THRMTRIP#

Processor pull-up (CPU)

TO BE REPLACED WITH 1K OHMS FOR SKL .

470 OHM IS FOR I/P

PLACE NEAR CPU

XDP_TMS_CPU

XDP_TDI_CPU

XDP_TDO_CPU

H_PROCHOT#

XDP_TCK0

XDP_TRST#_CPU

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

BU5

BU5

BU5

Date: Sheet of

Date: Sheet of

Date: Sheet of

R5 1K_4

R17 *51_4

R19 *51_4

R20 *51_4

R21 1K_4

R22 51_4

R23 51_4

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

02 -- SKYPAKE 1/20(eDP/DDI)

02 -- SKYPAKE 1/20(eDP/DDI)

02 -- SKYPAKE 1/20(eDP/DDI)

1

+VCCSTPLL

+1.0V

+1.0V

247Tuesday, January 05, 2016

247Tuesday, January 05, 2016

247Tuesday, January 05, 2016

1A

1A

1A

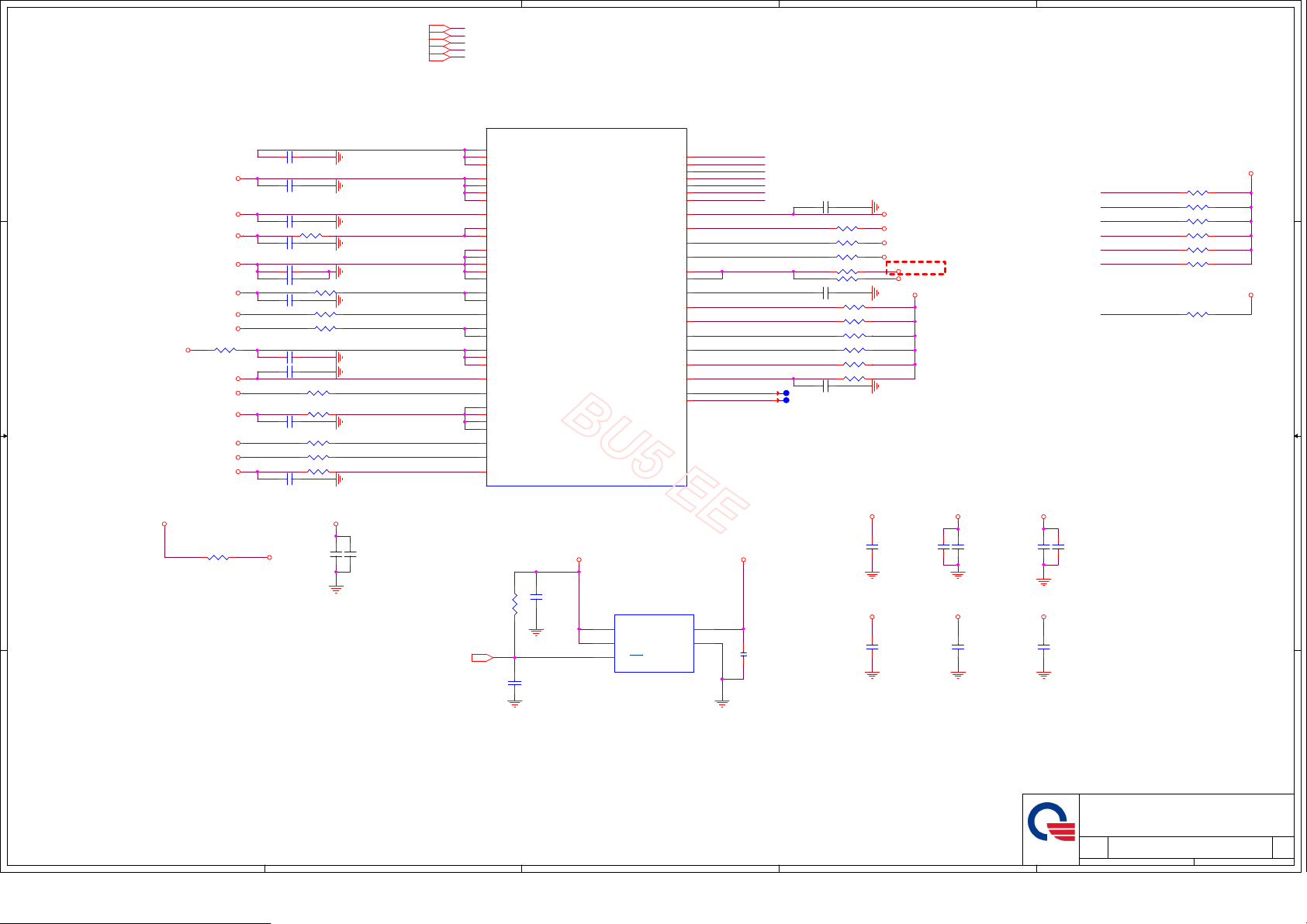

SKL_ULT

U1D

AT16

AU16

D63

A54

C65

C63

A65

C55

D55

B54

C56

BA5

AY5

H66

H65

A6

A7

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

CPU MISC

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

*SKL_ULT

REV = 1

3

CATERR#

H_PROCHOT#[33,39 ,47]

+VCCSTPLL

R6 *49.9/F_4

+1.0V

B B

A A

R9 0_4

CATERR#

R10 *51_4

R13 51_4

R15 51_4

R16 51_4

R18 51_4

Close to Chipset

5

JTAGX_PCH

JTAG_TMS_PCH

JTAG_TDI_PCH

JTAG_TDO_PCH

JTAG_TCK_PCH

R4 499/F_4

4

EC_PECI[33]

PM_THRMTRIP#[33]

XDP_BPM0[16]

XDP_BPM1[16]

TP113

TP4

TP5

TP6

R8 49.9/F_4

R11 49.9/F_4

R12 49.9/F_4

R14 49.9/F_4

EC_PECI

PROCHOT#

PM_THRMTRIP#

3D_FW_GPIO_R

CPU_GP1

CPU_GP2

CPU_GP3

PROC_POPIRCOMP

PCH_OPI_RCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

5

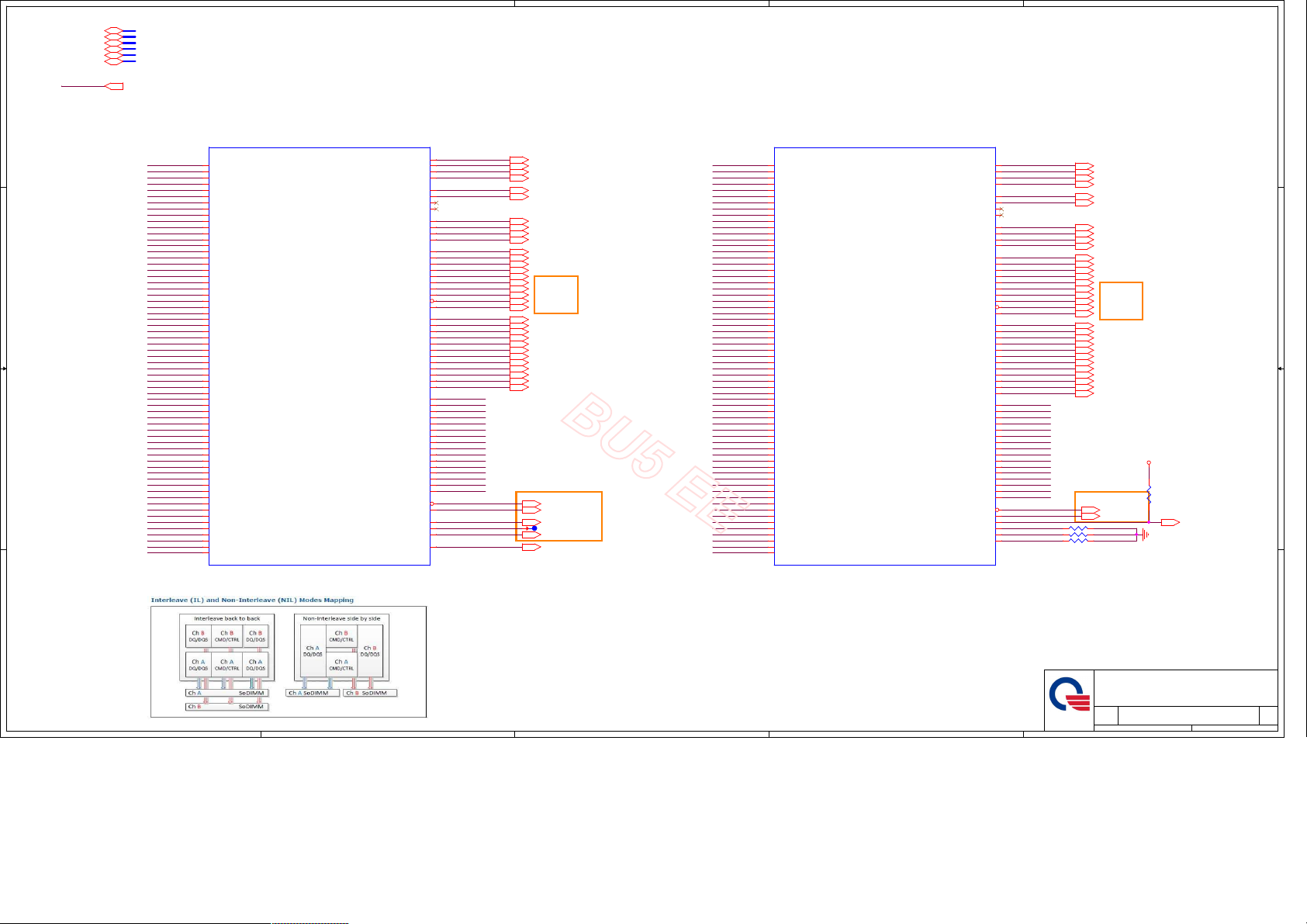

M_A_DQ SN[7:0 ][17]

M_A_DQ SP[7:0 ][17]

M_B_DQ SN[7:0 ][18]

M_B_DQ SP[7:0 ][18]

M_A_DQ [63:0][17]

M_B_DQ [63:0][18]

D D

C C

B B

+1.2VSUS [6,17,18,36,38,46]

AL71

M_A_DQ 0

AL68

M_A_DQ 1

AN68

M_A_DQ 2

AN69

M_A_DQ 3

AL70

M_A_DQ 4

AL69

M_A_DQ 5

AN70

M_A_DQ 6

AN71

M_A_DQ 7

AR70

M_A_DQ 8

AR68

M_A_DQ 9

AU71

M_A_DQ 10

AU68

M_A_DQ 11

AR71

M_A_DQ 12

AR69

M_A_DQ 13

AU70

M_A_DQ 14

AU69

M_A_DQ 15

AF65

M_B_DQ 0

AF64

M_B_DQ 1

AK65

M_B_DQ 2

AK64

M_B_DQ 3

AF66

M_B_DQ 4

AF67

M_B_DQ 5

AK67

M_B_DQ 6

AK66

M_B_DQ 7

AF70

M_B_DQ 8

AF68

M_B_DQ 9

AH71

M_B_DQ 10

AH68

M_B_DQ 11

AF71

M_B_DQ 12

AF69

M_B_DQ 13

AH70

M_B_DQ 14

AH69

M_B_DQ 15

BB65

M_A_DQ 16

AW65

M_A_DQ 17

AW63

M_A_DQ 18

AY63

M_A_DQ 19

BA65

M_A_DQ 20

AY65

M_A_DQ 21

BA63

M_A_DQ 22

BB63

M_A_DQ 23

BA61

M_A_DQ 24

AW61

M_A_DQ 25

BB59

M_A_DQ 26

AW59

M_A_DQ 27

BB61

M_A_DQ 28

AY61

M_A_DQ 29

BA59

M_A_DQ 30

AY59

M_A_DQ 31

AT66

M_B_DQ 16

AU66

M_B_DQ 17

AP65

M_B_DQ 18

AN65

M_B_DQ 19

AN66

M_B_DQ 20

AP66

M_B_DQ 21

AT65

M_B_DQ 22

AU65

M_B_DQ 23

AT61

M_B_DQ 24

AU61

M_B_DQ 25

AP60

M_B_DQ 26

AN60

M_B_DQ 27

AN61

M_B_DQ 28

AP61

M_B_DQ 29

AT60

M_B_DQ 30

AU60

M_B_DQ 31

U1B

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR1_DQ[0]/DDR0_DQ[16]

DDR1_DQ[1]/DDR0_DQ[17]

DDR1_DQ[2]/DDR0_DQ[18]

DDR1_DQ[3]/DDR0_DQ[19]

DDR1_DQ[4]/DDR0_DQ[20]

DDR1_DQ[5]/DDR0_DQ[21]

DDR1_DQ[6]/DDR0_DQ[22]

DDR1_DQ[7]/DDR0_DQ[23]

DDR1_DQ[8]/DDR0_DQ[24]

DDR1_DQ[9]/DDR0_DQ[25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

*SKL_ULT

REV = 1

Need apply PN

?

SKL_ULT

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

NIL-DDR CH A

2 OF 20

4

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

3

2

SkyLake ULT Processor (DDR4)

?

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

M_A_A5

BB54

M_A_A9

BA52

M_A_A6

AY52

M_A_A8

AW52

M_A_A7

AY55

M_A_BG #0

AW54

M_A_A12

BA54

M_A_A11

BA55

AY54

AU46

M_A_A13

AU48

AT46

AU50

AU52

AY51

M_A_A2

AT48

AT50

M_A_A10

BB50

M_A_A1

AY50

M_A_A0

BA50

M_A_A3

BB52

M_A_A4

AM70

M_A_DQ SN0

AM69

M_A_DQ SP0

AT69

M_A_DQ SN1

AT70

M_A_DQ SP1

AH66

M_B_DQ SN0

AH65

M_B_DQ SP0

AG69

M_B_DQ SN1

AG70

M_B_DQ SP1

BA64

M_A_DQ SN2

AY64

M_A_DQ SP2

AY60

M_A_DQ SN3

BA60

M_A_DQ SP3

AR66

M_B_DQ SN2

AR65

M_B_DQ SP2

AR61

M_B_DQ SN3

AR60

M_B_DQ SP3

AW50

M_A_ALE RT#

AT52

M_A_PAR ITY M_B_ALE RT#

AY67

SM_VREF

AY68

SMDDR_VREF_DQ0_M3

BA67

SMDDR_VREF_DQ1_M3

AW67

DDR_VTT_CNTL

M_A_CLK N0 [1 7]

M_A_CLK P0 [17 ]

M_A_CLK N1 [1 7]

M_A_CLK P1 [17 ]

M_A_CKE 0 [17]

M_A_CKE 1 [17]

M_A_CS# 0 [17]

M_A_CS# 1 [17]

M_A_DIM0 _ODT 0 [17]

M_A_DIM0 _ODT 1 [17] M_B_DIM0 _ODT 0 [18]

M_A_A5 [17]

M_A_A9 [17]

M_A_A6 [17]

M_A_A8 [17]

M_A_A7 [17]

M_A_BG #0 [17]

M_A_A12 [1 7]

M_A_A11 [1 7]

M_A_ACT # [17]

M_A_BG #1 [17]

M_A_A13 [1 7]

M_A_CAS # [17]

M_A_W E# [17]

M_A_RAS # [17]

M_A_BS# 0 [17]

M_A_A2 [17]

M_A_BS# 1 [17]

M_A_A10 [1 7]

M_A_A1 [17]

M_A_A0 [17]

M_A_A3 [17]

M_A_A4 [17]

M_A_ALE RT# [17 ]

M_A_PAR ITY [17]

SM_VREF [17]

TP7

SMDDR_VREF_DQ1_M3 [18]

DDR_VTT_CNTL [4,18]

20mils width

M_A_DQ 32

M_A_DQ 33

M_A_DQ 34

M_A_DQ 35

M_A_DQ 36

M_A_DQ 37

M_A_DQ 38

M_A_DQ 39

M_A_DQ 40

M_A_DQ 41

M_A_DQ 42

M_A_DQ 43

M_A_DQ 44

M_A_DQ 45

M_A_DQ 46

M_A_DQ 47

M_B_DQ 32

M_B_DQ 33

M_B_DQ 34

M_B_DQ 35

M_B_DQ 36

M_B_DQ 37

M_B_DQ 38

M_B_DQ 39

M_B_DQ 40

M_B_DQ 41

M_B_DQ 42

M_B_DQ 43

M_B_DQ 44

M_B_DQ 45

M_B_DQ 46

M_B_DQ 47

M_A_DQ 48

M_A_DQ 49

M_A_DQ 50

M_A_DQ 51

M_A_DQ 52

M_A_DQ 53

M_A_DQ 54

M_A_DQ 55

M_A_DQ 56

M_A_DQ 57

M_A_DQ 58

M_A_DQ 59

M_A_DQ 60

M_A_DQ 61

M_A_DQ 62

M_A_DQ 63

M_B_DQ 48

M_B_DQ 49

M_B_DQ 50

M_B_DQ 51

M_B_DQ 52

M_B_DQ 53

M_B_DQ 54

M_B_DQ 55

M_B_DQ 56

M_B_DQ 57

M_B_DQ 58

M_B_DQ 59

M_B_DQ 60

M_B_DQ 61

M_B_DQ 62

M_B_DQ 63

U1C

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

*SKL_ULT

REV = 1

SKL_ULT

Need apply PN

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

NIL-DDR CH B

3 OF 20

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

BOM

DDR1_PAR

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

BA38

AY38

AY34

BA34

AT38

AR38

AT32

AR32

BA30

AY30

AY26

BA26

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_A5

M_B_A9

M_B_A6

M_B_A8

M_B_A7

M_B_A12

M_B_A11

M_B_A13

M_B_A2

M_B_A10

M_B_A1

M_B_A0

M_B_A3

M_B_A4

M_A_DQ SN4

M_A_DQ SP4

M_A_DQ SN5

M_A_DQ SP5

M_B_DQ SN4

M_B_DQ SP4

M_B_DQ SN5

M_B_DQ SP5

M_A_DQ SN6

M_A_DQ SP6

M_A_DQ SN7

M_A_DQ SP7

M_B_DQ SN6

M_B_DQ SP6

M_B_DQ SN7

M_B_DQ SP7

M_B_PAR ITY

SM_DRAMRST#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

R25 121/F_4

R26 80.6/F_4

R27 100/F_4

M_B_CLK N0 [1 8]

M_B_CLK N1 [1 8]

M_B_CLK P0 [18 ]

M_B_CLK P1 [18 ]

M_B_CKE 0 [18]

M_B_CKE 1 [18]

M_B_CS# 0 [18]

M_B_CS# 1 [18]

M_B_DIM0 _ODT 1 [18]

M_B_A5 [18]

M_B_A9 [18]

M_B_A6 [18]

M_B_A8 [18]

M_B_A7 [18]

M_B_BG #0 [18]

M_B_A12 [1 8]

M_B_A11 [1 8]

M_B_ACT # [18]

M_B_BG #1 [18]

M_B_A13 [1 8]

M_B_CAS # [18]

M_B_W E# [18]

M_B_RAS # [18]

M_B_BS# 0 [18]

M_B_A2 [18]

M_B_BS# 1 [18]

M_B_A10 [1 8]

M_B_A1 [18]

M_B_A0 [18]

M_B_A3 [18]

M_B_A4 [18]

+1.2VSUS

M_B_ALE RT# [18 ]

M_B_PAR ITY [18]

1

R24

470/F_4

03

DDR3_DRAMRST# [17,18]

A A

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Custom

Custom

Custom

03 -- SKYPAKE 3/20(DDR3-A I/F)

03 -- SKYPAKE 3/20(DDR3-A I/F)

BU5

BU5

5

4

3

2

BU5

03 -- SKYPAKE 3/20(DDR3-A I/F)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1A

347Tuesday, January 05, 2016

347Tuesday, January 05, 2016

347Tuesday, January 05, 2016

5

+3V_DEEP_SUS[10,11,12,14,15,1 6,18]

+3V[2,10,11,12,13,14 ,15,16,17,18,19,20,21,25 ,26,27,28,29,30,31,32,33,39,43,44,47]

+3VS5[10,15,16,25,32,3 3,35,36,37,38,42,43,46,4 7]

+VCCSTPLL[2,5,6,9,38,39]

+1.0V[2,6,16,33,38]

+BAT_RTC[13,15,29,30,34,4 7]

+3V_RTC_2[13,15]

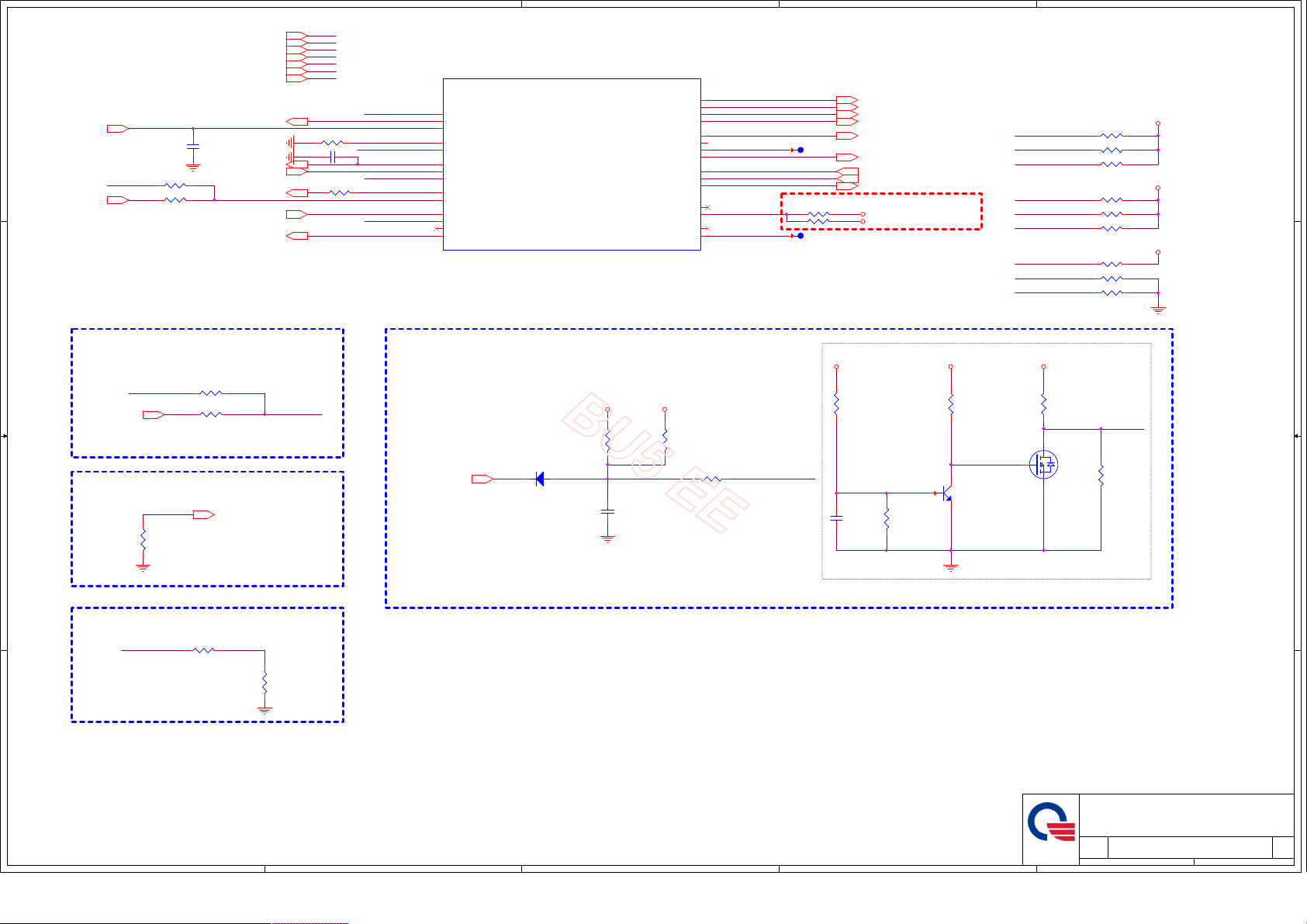

D D

RSMRST#[33]

SUSWARN#

SUSACK#_EC[33]

R32*0_4

R340_4

EC1

*220P/50V_4

SYS_RESET#[16]

R29 *10K_4

SYS_PWROK[16]

EC_PWROK[16,33]

SUSWARN#_EC[33]

PCIE_WAKE#[28,29,32,33]

DDR_VTT_CNTL[3,18]

C1 *0.1U/16V_4

R33 0_4

4

PLTRST#

SYS_RESET#

RSMRST#

PROCPWRGD

H_VCCST_PWRGD

SYS_PWROK

PCH_PWROK

DSWROK_EC_R

SUSWARN#

SUSACK#

PCIE_WAKE#

LAN_WAKE#

DDR_VTT_CNTL

U1K

SYSTEM POWER MANAGEMENT

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PW ROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

*SKL_ULT

REV = 1

SKL_ULT

?

11 OF 20

3

Need apply PN

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

GPP_B11/EXT_PWR_GATE#

INTRUDER #

GPP_B2/VRALERT#

2

1

04

AT11

PCH_SLP_S0_N

AP15

BA16

AY16

AN15

SLP_SUS#_EC

AW15

BB17

GPD9

AN16

BA15

DNBSWON#

AY15

AC_PRESENT_EC

AU13

RF_OFF_PCH

AU11

AP16

INTRUDER #_R

AM10

AM11

GPP_B2

?

TP8

Ra

R36 *1M_4

R305 1M_4

Rb

TP9

1005 Change +3V_RTC to +BAT_RTC

PCH_SLP_S0_N [16,33]

SUSB# [16,33]

SUSC# [16,33]

SLP_S5# [16]

SLP_SUS#_EC [33]

SLP_A# [16]

DNBSWON# [33]

AC_PRESENT_EC [33]

RF_OFF_PCH [32]

+BAT_RTC

+3V_RTC_2

Modify 0922

Main BAT -->Ra

Coin BAT -->Rb (default)

PCH Pull-high/low(CLG)

SUSWARN#

SUSACK#

RF_OFF_PCH

PCIE_WAKE#

AC_PRESENT_EC

LAN_WAKE#

SYS_RESET#

RSMRST#

DSWROK_EC

R28 *10K_4

R30 10K_4

R31 10K_4

R35 1K_4

R37 *10K_4

R38 *10K_4

R39 10K_4

R40 10K_4

R41 100K/F_4

+3V_DEEP_SUS

+3VS5

+3V

C C

For DS3 Sequence

For DS3 -->Ra

Non-DS3 -->Rb

RSMRST#

DSWROK_EC[33 ]

PLTRST#(CLG)

Check Rise/Fall time less than 100ns

R52

B B

100K/F_4

Rb

R42 *0_4

R46 0_4

Ra

PLTRST# [16,19,28,29,31,32,33]

DSWROK_EC_R

+1.0V

HWPG[16,33,35,36,37]

D1 MEK500V-40

21

Ra close to CPU side

H_VCCST_PWRGD trace 0.3" - 1.5"

H_VCCST_PWRGD_R

R47

1K_4

C3

*10P/50V_4

+VCCSTPLL

R48

*1K_4

Ra

R50 60.4/F_4

H_VCCST_PWRGD

System PWR_OK(CLG)

R53 0_4

A A

EC_PWROKSYS_PWROK

R54

10K/F_4

+1.0V +3VS5+5VS5

R43

15K/F_4

R51

100K_4

2

1 3

+1.0V_PWRGD_G1

C2

0.1U/16V_4

R44

100K_4

+1.0V_PWRGD_G2

Q2

METR3904-G

R45

10K_4

R49

100K_4

HWPG

3

Q1

2

2N7002K

1

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

04 -- SKYPAKE 5/20(Power Manger)

04 -- SKYPAKE 5/20(Power Manger)

BU5

BU5

5

4

3

2

BU5

04 -- SKYPAKE 5/20(Power Manger)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

447Tuesday, January 05, 2016

447Tuesday, January 05, 2016

447Tuesday, January 05, 2016

1A

1A

1A

5

+VCC_CORE[41]

+1.0V[2,4,6,16,33,38]

+VCCSTG[6 ]

+VCCSTPLL[2,4,6,9,38,39]

Under CPU

C9

22U/6.3V_6

C20

10U/6.3V_4

C35

22U/6.3V_6

C292

*1U/6.3V_4

C10

22U/6.3V_6

C21

10U/6.3V_4

C36

22U/6.3V_6

C291

*1U/6.3V_4

+VCC_EOPIO

C4

D D

C C

10U/6.3V_6

C19

10U/6.3V_6

C34

22U/6.3V_6

+VCC_EDRAM

+VCC_EDRAM

C5

22U/6.3V_6

C22

10U/6.3V_4

C37

22U/6.3V_6

+1.8V_DEEP_SUS

C290

*1U/6.3V_4

C298

*10U/6.3V_4

C14

47U/6.3VS_8

C23

10U/6.3V_4

C38

22U/6.3V_6

R275 *0_4

C293

*1U/6.3V_4

C299

*10U/6.3V_4

C16

22U/6.3V_6

C24

10U/6.3V_6

C39

22U/6.3V_6

C17

22U/6.3V_6

C25

10U/6.3V_4

VCCOPC_1.8

Close CPU

C295

C294

*1U/6.3V_4

*10U/6.3V_4

GT3e => Stuff

GT2 => Un-Stuff

C296

*1U/6.3V_4

C297

*1U/6.3V_4

+VCC_CORE

+VCC_CORE

C40

47U/6.3VS_8

4

?

SKL_ULT

A30

A34

A39

A44

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

K32

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

C42

47U/6.3VS_8

U1L

VCC_A30

VCC_A34

32A

VCC_A39

VCC_A44

VCC_AK33

VCC_AK35

VCC_AK37

VCC_AK38

VCC_AK40

VCC_AL33

VCC_AL37

VCC_AL40

VCC_AM32

VCC_AM33

VCC_AM35

VCC_AM37

VCC_AM38

VCC_G30

RSVD_K32

RSVD_AK32

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCC_OPC_1P8_H63

VCC_OPC_1P8_G61

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

*SKL_ULT

REV = 1

C43

47U/6.3VS_8

+VCC_CORE +VCC_CORE

C18

22U/6.3V_6

C41

47U/6.3VS_8

CPU POWER 1 OF 4

3.2A

50mA

2A

12 OF 20

C44

47U/6.3VS_8

Need apply PN

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

BOM

C45

47U/6.3VS_8

47U/6.3VS_8

C46

U

?

3

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

H_CPU_SVIDALRT#

A63

VR_SVID_CLK_R

D64

H_CPU_SVIDDAT

G20

C47

47U/6.3VS_8

C6

1U/6.3V_4

C26

1U/6.3V_4

C7

1U/6.3V_4

C27

1U/6.3V_4

R55 100/F_4

R56 100/F_4

+VCCSTG

2

Under CPU

C8

1U/6.3V_4

C28

1U/6.3V_4

C11

1U/6.3V_4

C29

1U/6.3V_4

+VCC_CORE

VCC_SENSE [39]

VSS_SENSE [39]

C12

1U/6.3V_4

C30

1U/6.3V_4

C13

1U/6.3V_4

C31

1U/6.3V_4

Close CPU

C15

1U/6.3V_4

C32

1U/6.3V_4

C33

1U/6.3V_4

100- ±1%

pull-up to VCC

near processor.

Layout note: need routing together and ALERT need between CLK and DATA.

+VCCSTPLL

CLOSE TO CPU

PLACE THE PU RESISTORS

H_CPU_SVIDALRT#

R58 220/F_4

R57

56.2/F_4

C48

*0.1U/16V_4

SVID ALERT

1

05

VR_SVID_ALERT# [39]

R61

100/F_4

+VCCSTPLL

R59

*54.9/F_4

SVID CLK

VR_SVID_CLK [39]

R62 0_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

BU5

BU5

BU5

Date: Sheet of

Date: Sheet of

Date: Sheet of

SVID DATA

VR_SVID_DATA [39]

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

05 -- SKYPAKE 6/20 (POWER-1)

05 -- SKYPAKE 6/20 (POWER-1)

05 -- SKYPAKE 6/20 (POWER-1)

1

1A

1A

547Tuesday, January 05, 2016

547Tuesday, January 05, 2016

547Tuesday, January 05, 2016

1A

C49

B B

A A

5

10U/6.3V_4

C50

10U/6.3V_4

C51

10U/6.3V_6

4

C52

10U/6.3V_4

C53

10U/6.3V_4

C54

10U/6.3V_4

C55

10U/6.3V_4

C56

10U/6.3V_6

3

PLACE THE PU RESISTORS

CLOSE TO VR

PULL UP IS IN THE VR MODULE

CLOSE TO CPU

PLACE THE PU RESISTORS

VR_SVID_CLK_R

H_CPU_SVIDDAT

2

R60 0_4

+VCCSTPLL

5

+VCCSTPLL [2,4,5,9,38,39]

+VCCSA [39,41]

+1.2VSUS [3,17,18,36,38,46]

+1.0V_DEEP_SUS [9,13,15,16,37,38]

+1.0V [2,4,16,33,38]

+3VPCU [13,30,32,33,34,35,42,47]

Under CPU

D D

10U/6.3V_6

C60

10U/6.3V_6

10U/6.3V_6

C74

C73

10U/6.3V_6

10U/6.3V_6

C62

C61

1U/6.3V_4

C76

C75

10U/6.3V_6

Close CPU

+VCCSTPLL

+1.0V

+VCCIO

C C

+1.2V_VCCPLL_OC

R63 0_4

R64 *0_4

R65 *0_4

R68 *0_6

R69 0_6

R70 0_6

+VCCSTG

+VCCPLL_OC+1.2VSUS

+VCCPLL+VCCSTPLL

Under CPU

+VCCSTG +VCCPLL_OC

C99

1U/6.3V_4

C100

1U/6.3V_4

Close A18 Ball

+VCCSTPLL

B B

C104

*1U/6.3V_4

C105

*22U/6.3V_6

+1.2VSUS

C57

C58

1U/6.3V_4

*10U/6.3V_4

1U/6.3V_4

C91

C59

1U/6.3V_4

C92

1U/6.3V_4

Close CPU Under CPU

IO Thrm Protect

+3VPCU

R71

20K/F_4

For 75 degree, 1.2v limit, (HW)

THER_CPU

R74

100K_4 NTC

C101

0.1U/16V_4

1 2

4

+VCCSTPLL

+VCCSTG

+VCCPLL_OC

+VCCPLL

THRM_MOINTOR2 [33]

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

AL23

A18

A22

K20

K21

SKL_ULT

U1N

CPU POWER 3 OF 4

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

*SKL_ULT

REV = 1

?

2.8A

60mA

20mA

120mA

130mA

14 OF 20

Need apply PN

VCCIO

3.1A

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

5.1A

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

+3VPCU

3

Under CPU Close CPU

AK28

AK30

AL30

AL42

C63

1U/6.3V_4

+VCCSA

C77

1U/6.3V_4

C64

1U/6.3V_4

C78

1U/6.3V_4

C93

10U/6.3V_6

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

VCCIO_VCCSENSE

VCCIO_VSSSENSE

For PIPE USEFor CPU USE

R73

20K/F_4

For 75 degree, 1.2v limit, (HW)

THER_PIPE

R76

100K_4 NTC

C103

0.1U/16V_4

1 2

THRM_MOINTOR1 [33]

C65

C66

1U/6.3V_4

10U/6.3V_4

C80

C79

1U/6.3V_4

1U/6.3V_4

C95

C94

10U/6.3V_6

10U/6.3V_6

VSSSA_SENSE [39]

VCCSA_SENSE [39]

C67

10U/6.3V_4

C81

1U/6.3V_4

C96

10U/6.3V_6

C68

10U/6.3V_4

C82

1U/6.3V_4

C97

10U/6.3V_4

VCCIO_VCCSENSE

VCCIO_VSSSENSE

2

C69

1U/6.3V_4

Under CPU

C83

1U/6.3V_4

C98

10U/6.3V_4

C70

1U/6.3V_4

C84

10U/6.3V_4

Close CPU

R66 100/F_4

R67 100/F_4

C71

1U/6.3V_4

C85

10U/6.3V_6

+VCCIO

C72

1U/6.3V_4

C86

10U/6.3V_4

+VCCIO

C87

10U/6.3V_6

C88

10U/6.3V_4

1

C89

10U/6.3V_6

C90

10U/6.3V_6

06

Close CPU

C107

1U/6.3V_4

C109

10U/6.3V_6

+VCCPLL

5

C110

10U/6.3V_6

C111

10U/6.3V_6

C112

10U/6.3V_6

C113

10U/6.3V_6

C114

1U/6.3V_4

C115

1U/6.3V_4

4

C116

1U/6.3V_4

C117

1U/6.3V_4

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

06 -- SKYPAKE 7/20 (POWER-2)

06 -- SKYPAKE 7/20 (POWER-2)

BU5

BU5

3

2

BU5

06 -- SKYPAKE 7/20 (POWER-2)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

647Tuesday, January 05, 2016

647Tuesday, January 05, 2016

647Tuesday, January 05, 2016

1A

1A

1A

+VCCSTPLL

C106

1U/6.3V_4

+1.2VSUS

A A

C108

10U/6.3V_6

Close to CPU

5

+VCCGT [39,40]

+VCC_CORE [5,41]

+1.2VSUS [3,6,17,18,36,38,46]

Under CPU

D D

C146

1U/6.3V_4

C152

C C

B B

1U/6.3V_4

C119

10U/6.3V_6

C130

10U/6.3V_4

C147

1U/6.3V_4

C153

1U/6.3V_4

C120

10U/6.3V_4

C131

10U/6.3V_6

C148

1U/6.3V_4

C154

1U/6.3V_4

10U/6.3V_6

10U/6.3V_6

C149

1U/6.3V_4

C155

1U/6.3V_4

4

?

SKL_ULT

57A

BOM

13 OF 20

7A

Need apply PN

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

M62

N63

N64

N66

N67

N69

A48

A53

A58

A62

A66

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

J70

J69

U1M

CPU POWER 2 OF 4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

*SKL_ULT

REV = 1

+VCCGT

10U/6.3V_4

C138

10U/6.3V_6

C150

1U/6.3V_4

C156

1U/6.3V_4

VCCGT_SENSE[39]

VSSGT_SENSE[39]

C128

10U/6.3V_6

C139

10U/6.3V_4

C151

1U/6.3V_4

C157

1U/6.3V_4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

3

+VCCGT

Close CPU

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

C122

47U/6.3VS_8

C129

22U/6.3V_6

C142

22U/6.3V_6

+VCCGTX

C300

*22U/6.3V_6

R276 *0_8

R277 *0_8

GT3e => Stuff

GT2 => Un-Stuff

C123

47U/6.3VS_8C118

C132

22U/6.3V_6C137

C143

22U/6.3V_6

C301

*22U/6.3V_6

C124

47U/6.3VS_8

C133

22U/6.3V_6

C144

22U/6.3V_6

C302

*22U/6.3V_6

+VCCGT+VCCGTX

C125

47U/6.3VS_8C121

C134

22U/6.3V_6

C145

22U/6.3V_6

C303

*22U/6.3V_6

2

C126

47U/6.3VS_8

C135

22U/6.3V_6

C304

*22U/6.3V_6

C127

47U/6.3VS_8

C136

22U/6.3V_6

C140

22U/6.3V_6

C141

22U/6.3V_6

1

07

A A

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

07 -- SKYPAKE 8/20 (POWER-3)

07 -- SKYPAKE 8/20 (POWER-3)

BU5

BU5

5

4

3

2

BU5

07 -- SKYPAKE 8/20 (POWER-3)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

747Tuesday, January 05, 2016

747Tuesday, January 05, 2016

747Tuesday, January 05, 2016

1A

1A

1A

5

4

3

2

1

08

AT63

AT68

AT71

AU10

AU15

AU20

AU32

AU38

AV68

AV69

AV70

AV71

AW10

AW12

AW14

AW16

AW18

AW21

AW23

AW26

AW28

AW30

AW32

AW34

AW36

AW38

AW41

AW43

AW45

AW47

AW49

AW51

AW53

AW55

AW57

AW6

AW60

AW62

AW64

AW66

AW8

AY66

BA10

BA14

BA18

BA23

BA28

BA32

BA36

BA45

AV1

B10

B14

B18

B22

B30

B34

B39

B44

B48

B53

B58

B62

B66

B71

BA1

BA2

F68

U1Q

SKL_ULT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

*SKL_ULT

REV = 1

GND 2 OF 3

?

17 OF 20

Need apply PNNeed apply PN

BA49

VSS

BA53

VSS

BA57

VSS

BA6

VSS

BA62

VSS

BA66

VSS

BA71

VSS

BB18

VSS

BB26

VSS

BB30

VSS

BB34

VSS

BB38

VSS

BB43

VSS

BB55

VSS

BB6

VSS

BB60

VSS

BB64

VSS

BB67

VSS

BB70

VSS

C1

VSS

C25

VSS

C5

VSS

D10

VSS

D11

VSS

D14

VSS

D18

VSS

D22

VSS

D25

VSS

D26

VSS

D30

VSS

D34

VSS

D39

VSS

D44

VSS

D45

VSS

D47

VSS

D48

VSS

D53

VSS

D58

VSS

D6

VSS

D62

VSS

D66

VSS

D69

VSS

E11

VSS

E15

VSS

E18

VSS

E21

VSS

E46

VSS

E50

VSS

E53

VSS

E56

VSS

E6

VSS

E65

VSS

E71

VSS

F1

VSS

F13

VSS

F2

VSS

F22

VSS

F23

VSS

F27

VSS

F28

VSS

F32

VSS

F33

VSS

F35

VSS

F37

VSS

F38

VSS

F4

VSS

F40

VSS

F42

VSS

BA41

VSS

BOM

?

AA65

AA68

AB15

AB16

AB18

AB21

AD13

AD16

AD19

AD20

AD21

AD62

AE64

AE65

AE66

AE67

AE68

AE69

AF10

AF15

AF17

AF63

AG16

AG17

AG18

AG19

AG20

AG21

AG71

AH13

AH63

AH64

AH67

AJ15

AJ18

AJ20

AK11

AK16

AK18

AK21

AK22

AK27

AK63

AK68

AK69

AL28

AL32

AL35

AL38

AL45

AL48

AL52

AL55

AL58

AL64

A67

A70

AA2

AA4

AB8

AD8

AF1

AF2

AF4

AH6

AJ4

AK8

AL2

AL4

U1P

A5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

*SKL_ULT

REV = 1

SKL_ULT

GND 1 OF 3

Need apply PN

?

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

16 OF 20

?

AL65

AL66

AM13

AM21

AM25

AM27

AM43

AM45

AM46

AM55

AM60

AM61

AM68

AM71

AM8

AN20

AN23

AN28

AN30

AN32

AN33

AN35

AN37

AN38

AN40

AN42

AN58

AN63

AP10

AP18

AP20

AP23

AP28

AP32

AP35

AP38

AP42

AP58

AP63

AP68

AP70

AR11

AR15

AR16

AR20

AR23

AR28

AR35

AR42

AR43

AR45

AR46

AR48

AR5

AR50

AR52

AR53

AR55

AR58

AR63

AR8

AT2

AT20

AT23

AT28

AT35

AT4

AT42

AT56

AT58

U1R

?

D D

C C

B B

SKL_ULT

GND 3 OF 3

F8

VSS

G10

VSS

G22

VSS

G43

VSS

G45

VSS

G48

VSS

G5

VSS

G52

VSS

G55

VSS

G58

VSS

G6

VSS

G60

VSS

G63

VSS

G66

VSS

H15

VSS

H18

VSS

H71

VSS

J11

VSS

J13

VSS

J25

VSS

J28

VSS

J32

VSS

J35

VSS

J38

VSS

J42

VSS

J8

VSS

K16

VSS

K18

VSS

K22

VSS

K61

VSS

K63

VSS

K64

VSS

K65

VSS

K66

VSS

K67

VSS

K68

VSS

K70

VSS

K71

VSS

L11

VSS

L16

VSS

L17

VSS

18 OF 20

*SKL_ULT

REV = 1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L18

L2

L20

L4

L8

N10

N13

N19

N21

N6

N65

N68

P17

P19

P20

P21

R13

R6

T15

T17

T18

T2

T21

T4

U10

U63

U64

U66

U67

U69

U70

V16

V17

V18

W13

W6

W9

Y17

Y19

Y20

Y21

?

A A

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

8 -- SKYPAKE 9/20 (GND-1)

8 -- SKYPAKE 9/20 (GND-1)

BU5

BU5

5

4

3

2

BU5

8 -- SKYPAKE 9/20 (GND-1)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

847Tuesday, January 05, 2016

847Tuesday, January 05, 2016

847Tuesday, January 05, 2016

1A

1A

1A

5

4

3

2

1

09

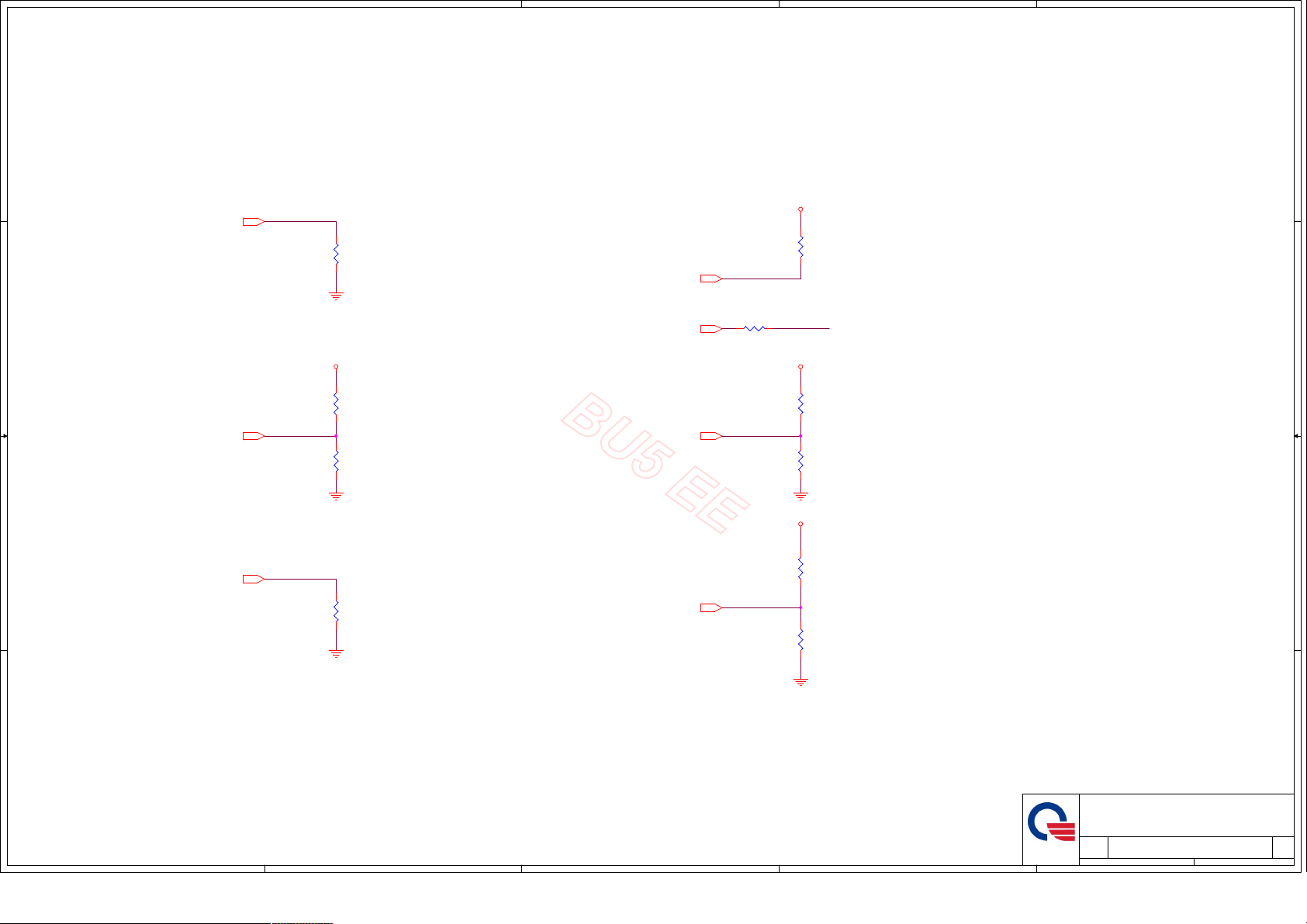

?

U1S

CFG0-19 need Reserve TP

D D

+1.0V_DEEP_SUS

C C

CFG0[16]

CFG1[16]

CFG2[16]

CFG3[16]

CFG4[16]

CFG5[16]

CFG6[16]

CFG7[16]

CFG8[16]

CFG9[16]

CFG10[16]

CFG11[16]

CFG12[16]

CFG13[16]

CFG14[16]

CFG15[16]

CFG16[16]

CFG17[16]

CFG18[16]

CFG19[16]

R78 49.9/F_4

R79 *1K_4

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG_RCOMP

AL25

AL27

BA70

BA68

G69

G68

G71

G70

AY2

AY1

G65

E68

B67

D65

D67

E70

C68

D68

C67

F71

F70

H70

H69

E63

F63

E66

F66

E60

E8

D1

D3

K46

K45

C71

B70

F60

A52

J71

J68

F65

F61

E61

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMOD E

RSVD_AY2

RSVD_AY1

RSVD_D1

RSVD_D3

RSVD_K46

RSVD_K45

RSVD_AL25

RSVD_AL27

RSVD_C71

RSVD_B70

RSVD_F60

RSVD_A52

RSVD_TP_BA70

RSVD_TP_BA68

RSVD_J71

RSVD_J68

VSS_F65

VSS_G65

RSVD_F61

RSVD_E61

SKL_ULT

RESERVED SIGNALS -1

BOM

B B

*SKL_ULT

REV = 1

19 OF 20

Need apply PN

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

RSVD_BB2

RSVD_BA3

RSVD_D5

RSVD_D4

RSVD_B2

RSVD_C2

RSVD_B3

RSVD_A3

RSVD_AW1

RSVD_E1

RSVD_E2

RSVD_BA4

RSVD_BB4

RSVD_A4

RSVD_C4

RSVD_A69

RSVD_B69

RSVD_AY3

RSVD_D71

RSVD_C70

RSVD_C54

RSVD_D54

VSS_AY71

RSVD_TP_AW71

RSVD_TP_AW70

PROC_SELECT#

ZVM#

MSM#

TP5

TP6

TP4

TP1

TP2

?

BB68

BB69

AK13

AK12

BB2

BA3

AU5

AT5

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

BB5

A69

B69

AY3

R80 0_4

D71

C70

C54

D54

AY4

BB3

AY71

R81 0_4

AR56

AW71

AW70

AP56

C64

R82 *100K_4

+VCCSTPLL

+1.8V_DEEP_SUS

R77 *0_4

C158

*1U/6.3V_4

Close to CPU

within 100mil

AW69

AW68

AU56

AW48

C7

U12

U11

H11

U1T

RSVD_AW69

RSVD_AW68

RSVD_AU56

RSVD_AW48

RSVD_C7

RSVD_U12

RSVD_U11

RSVD_H11

*SKL_ULT

REV = 1

SKL_ULT

?

SPARE

20 OF 20

Need apply PN

F6

RSVD_F6

E3

RSVD_E3

C11

RSVD_C11

B11

RSVD_B11

A11

RSVD_A11

D12

RSVD_D12

C12

RSVD_C12

F52

RSVD_F52

?

Processor Strapping

CFG3

(Physcial Debug E nable)

DFX Privacy

CFG4

(DP Presence Strap)

A A

5

The CFG signals have a default value of '1' if not terminated on the board.

1 0

Disable: Enable: Set DFX Enable in DFX interface MSR

Disable; No physical DP attached to eDP

4

Enable; An ext DP device is connected to eDP

3

CFG3

CFG4

Circuit

R83 *1K_4

R84 1K_4

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

9 -- SKYPAKE 12/20 (RSV-1)

9 -- SKYPAKE 12/20 (RSV-1)

BU5

BU5

2

BU5

9 -- SKYPAKE 12/20 (RSV-1)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

947Tuesday, January 05, 2016

947Tuesday, January 05, 2016

947Tuesday, January 05, 2016

1A

1A

1A

5

+3V_DEEP_SUS [4,11,12,14,15,16,18]

+3V [2,4,11,12,13,14,15,16,17,18,19,20,21,25,26,27,28,29,30,31,32,33,39,43,44,47]

+5V [25,26,27,30,32,43]

+1.0V [2,4,6,16,33,38]

+3VS5 [4,15,16,25,32,33,35,36,37,38,42,43,46,47]

D D

C C

4

3

2

1

10

?

U1E

SPI - FLASH

PCH_SPI1_CLK

PCH_SPI1_SO

PCH_SPI1_SI

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CS0#

SPI1_CLK

TP13

SIO_EXT_SMI#[33]

PCI_SERR#[33]

EC_RCIN#[33]

SIO_EXT_SMI#

PCI_SERR#

SPI1_IO2

SPI1_IO3

TP14

SPI1_CS#

TP15

TP16

SERIRQ[31,33]

AW3

AW2

AW13

AY11

AV2

AV3

AU4

AU3

AU2

AU1

M2

M3

J4

V1

V2

M1

G3

G2

G1

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

*SKL_ULT

REV = 1

SKL_ULT

5

LPC

PDC

5 OF 20

Need apply PN

SMBUS, SMLINK

GPP_A14/SUS_STAT#/ ESPI_RESET#

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI _IO0

GPP_A2/LAD1/ESPI _IO1

GPP_A3/LAD2/ESPI _IO2

GPP_A4/LAD3/ESPI _IO3

GPP_A5/LFRAME#/ESPI _CS#

GPP_A9/CLKOUT_LPC0/ESP I_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

?

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

SMB_PCH_CLK

SMB_PCH_DAT

SML0ALERT#

SMB_ME0_CLK

SMB_ME0_DAT

SML1ALERT#

SMB_ME1_CLK

SMB_ME1_DAT

GPP_B23

CLK_PCI_EC_R

CLK_PCI_LPC_R

CLKRUN#

LAD0 [31,32,33]

LAD1 [31,32,33]

LAD2 [31,32,33]

LAD3 [31,32,33]

LFRAME# [31,32,33]

CLKRUN# [33]

SML0ALERT# [11]

SML1ALERT# [11]

TP12

R85 22/F_4

R86 22/F_4

R87 *22/F_4

EC2 18P/50V_4

EC3 18P/50V_4

EC4

*18P/50V_4

CLK_24M_KBC [33]

CLK_24M_DEBUG [32]

EMI(near PCH)

CLK_PCI_TPM [31]

EMI(near PCH)

GPIO Pull UP

+3V +3V_DEEP_SUS

SERIRQ

CLKRUN#

SIO_EXT_SMI#

EC_RCIN#

PCI_SERR#

B B

R88 10K_4

R90 8.2K/F_4

R92 10K_4

R94 10K_4

R96 10K_4

SMB_PCH_CLK

SMB_PCH_DAT

SMB_ME0_CLK

SMB_ME0_DAT

SMB_ME1_CLK

SMB_ME1_DAT

ACC_LED#[12,32]

R89 2.2K_4

R91 2.2K_4

R93 499/F_4

R95 499/F_4

R97 1K_4

R98 1K_4

R99 10K_4

PCH SPI ROM(CLG)

Vender P/N

EON

Winbond

GigaDevice

Socket

Size

8MB

8MB

PCH_SPI_CS0#_R[33]

PCH_SPI1_CLK_R[33]

PCH_SPI1_SI_R[33]

PCH_SPI1_SO_R[33]

AKE3EZ N0Q01 ( EN25QH64 -104HIP)8MB

AKE3EF P0N07 ( W25Q64FV SSIQ)

AKE3EG N0Q01 ( GD25B64B SIGR)

DFHS08FS023

PCH_SPI_CS0#_R

PCH_SPI1_CLK_R

PCH_SPI1_SI_R

PCH_SPI1_SO_R

need place to TOP

PCH_SPI_CS0#_R

TP17

PCH_SPI1_CLK_R

TP18

PCH_SPI1_SI_R

TP19

PCH_SPI1_SO_R

TP20

BIOS_WP#

TP21

HOLD#

TP22

PCH SPI ROM(CLG)

R100 *0_4

+3VS5

HOLD#

VDD

VSS

R101 0_4

8

+3VSPI

7

HOLD#

4

PCH_SPI_IO3BIOS_WP#

BU5

BU5

BU5

R105 1K_4

R107 15/F_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

+3V_DEEP_SUS

U3

PCH_SPI_CS0#

SMBus/Pull-up(CLG)

Q3

MBCLK2[18,33]

MBDATA2[18,33]

A A

R110 4.7K_4

+3V

SMB_RUN_DAT[16,17,18,30]

R111 4.7K_4

+3V

SMB_RUN_CLK[16,17,18,30]

5

4 3

1

*2N7002DW

Q4

4 3

1

2N7002KDW

+3V

5

SMB_ME1_CLK

2

6

SMB_ME1_DAT

+3V

5

SMB_PCH_DAT

2

6

SMB_PCH_CLK

CPU heat pipe local thermal sensor

DDR thermal sensor

EC

Touch Pad

XDP

DDR4

4

3

C161 1U/6.3V_4

PCH_SPI_IO2

1005 Change P/N to DFHS08FS023(Socket)

PCH_SPI1_CLK

+3VSPI

R108 1K_4

R109 15/F_4

R102 15/F_4

R103 15/F_4

R104 15/F_4

R106 15/F_4

PCH_SPI_CS0#_R

PCH_SPI1_CLK_R

PCH_SPI1_SI_RPCH_SPI1_SI

PCH_SPI1_SO_RPCH_SPI1_SO

C159

22P/50V_4

2

1

CE#

6

SCK

5

SI

2

SO

3

WP#

W25Q64FVSSIQ

AKE3EFP0N07

+3VSPI

C160

0.1U/16V_4

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

10 -- SKYPAKE 14/20(SPI/LPC/SMBUS)

10 -- SKYPAKE 14/20(SPI/LPC/SMBUS)

10 -- SKYPAKE 14/20(SPI/LPC/SMBUS)

1

10 47Tuesday, January 05, 2016

10 47Tuesday, January 05, 2016

10 47Tuesday, January 05, 2016

1A

1A

1A

5

4

3

2

1

11

D D

DESIGN NOTE:

WEAK PULL UP RESISTOR PRESENT ON THIS NET

ACZ_SPKR[14,26]

C C

B B

GSPI1_MOSI[14]

ACZ_SPKR

GSPI1_MOSI

R112

*20K/F_4

+3V_DEEP_SUS

R115

1K_4

R117

*20K/F_4

R120

*20K/F_4

Functional Strap Definitions

TOP SWAP OVERRIDE

HIGH - TOP SWAP ENABLE

LOW-DISABLED

HIGH: LPC SELECTED FOR SYSTEM FLASH

WEAK INTERNAL PD

No Boot:

The signal has a weak internal pull-down.

0 = Disable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (no confidentiality).

1 = Enable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (with confidentiality). Must be

pulled up to support Intel AMT with TLS and Intel

SBA (Small Business Advantage) with TLS.

No Boot:

The signal has a weak internal pull-down.

This field determines the destination of accesses to the

BIOS memory range. Also controllable using Boot BIOS

Destination bit (Chipset Configuration Registers: Offset

3410h:Bit 10). This strap is used in conjunction with Boot

BIOS Destination Selection 0 strap.

Bit 10 Boot BIOS Destination

0 SPI

1 LPC

ACZ_SDOUT[14]

GPIO33_EC[33]

GPP_B18[14]SML0ALERT#[10]

SML1ALERT#[10]

ACZ_SDOUT

R114 1K_4

GPP_B18SML0ALERT#

+3V_DEEP_SUS

SML1ALERT#

+3V_DEEP_SUS

R113

*4.7K_4

ACZ_SDOUT

+3V

R116

*4.7K_4

R118

10K_4

R119

*10K_4

R121

20K/F_4

No Boot:

The signal has a weak internal pull-down.

0 = Enable security measures defined in the Flash

Descriptor.

1 = Disable Flash Descriptor Security (override). This

strap should only be asserted high using external

pull-up in manufacturing/debug environments ONLY.

This function is useful when running ITP/XDP.

No Boot:

The signal has a weak internal pull-down.

0 = Disable No Reboot mode.

1 = Enable No Reboot mode

(PCH will disable the TCO

Timer system reboot feature).

This function is useful when running ITP/XDP.

No Boot:

The signal has a weak internal pull-down.

0 = LPC Is selected for EC.

1 = eSPI Is selected for EC.

A A

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

11 -- SKYPAKE 15/20(HDA)

11 -- SKYPAKE 15/20(HDA)

BU5

BU5

5

4

3

2

BU5

11 -- SKYPAKE 15/20(HDA)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

11 47Tuesday, January 05, 2016

11 47Tuesday, January 05, 2016

11 47Tuesday, January 05, 2016

1A

1A

1A

5

+3V [2,4,10,11,13,14,15,16,17,18,19,20,21,25,26,27,28,29,30,31,32,33,39,43,44,47]

+3VS5 [4,10,15,16,25,32,33,35,36,37,38,42,43,46,47]

+3V_DEEP_SUS [4,10,11,14,15,16,18]

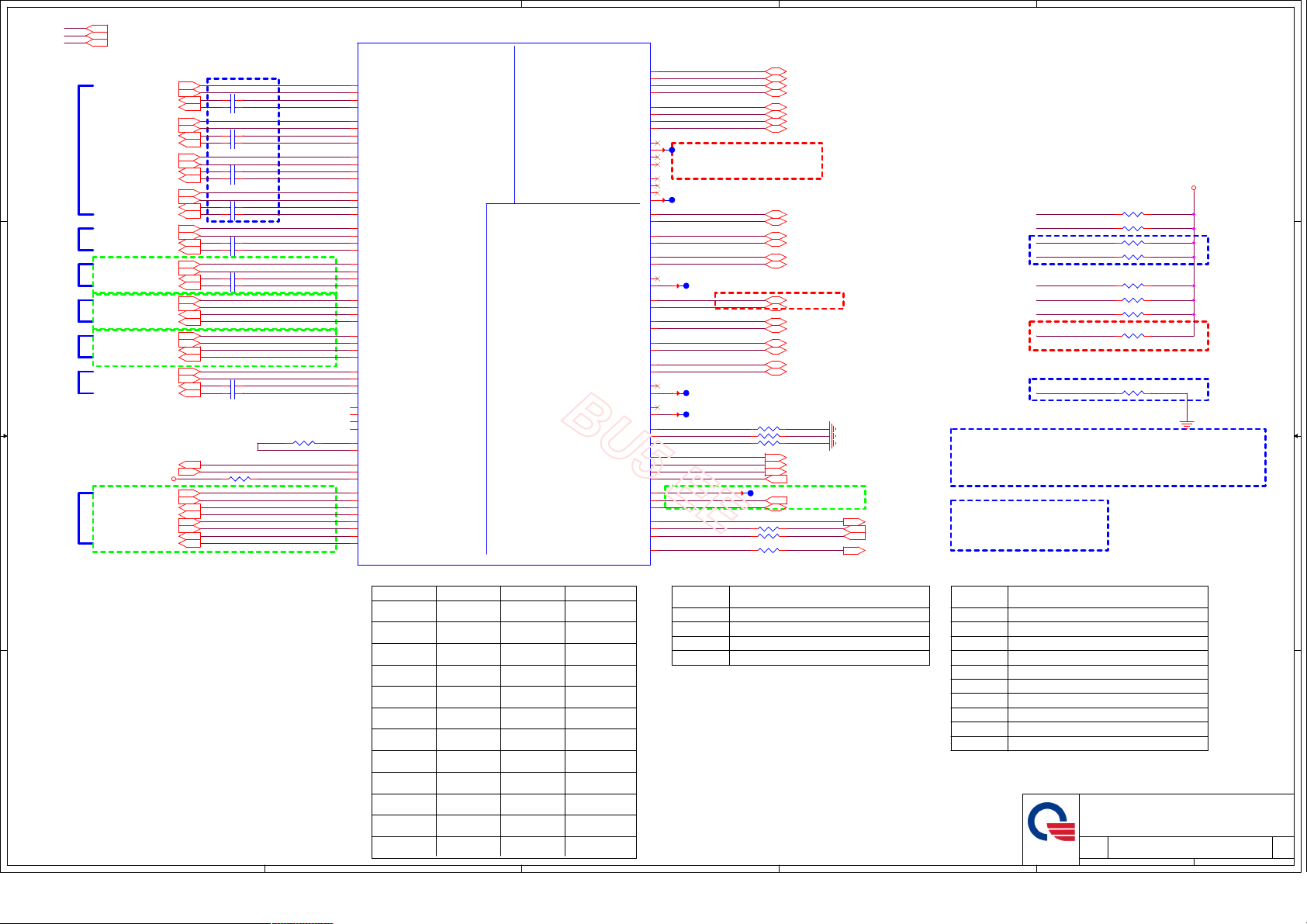

PEG_RXN1[19]

DIS only

PEG_RXP1[19]

PEG_TXN1[19 ]

D D

dGPU

Cardreader

LAN

HDD

C C

ODD

WLAN

SSDx2

SSDx2/

(SATA2)

B B

A A

PEG_TXP1[19]

PEG_RXN2[19]

PEG_RXP2[19]

PEG_TXN2[19 ]

PEG_TXP2[19]

PEG_RXN3[19]

PEG_RXP3[19]

PEG_TXN3[19 ]

PEG_TXP3[19]

PEG_RXN4[19]

PEG_RXP4[19]

PEG_TXN4[19 ]

PEG_TXP4[19]

PCIE_RXN5_CARD[29]

PCIE_RXP5_CARD[29]

PCIE_TXN5_CARD[29]

PCIE_TXP5_CARD[29 ]

PCIE_RXN10_LAN[28]

PCIE_RXP10_LAN[28]

PCIE_TXN10_LAN[28]

PCIE_TXP10_LAN[28]

SATA_RXN1B[32]

SATA_RXP1B[32]

SATA_TXN1B[32]

SATA_TXP1B[32]

SATA_RXN2[32]

SATA_RXP2[32]

SATA_TXN2[32]

SATA_TXP2[32]

PCIE_RXN9_WLAN[32]

PCIE_RXP9_WLAN[32]

PCIE_TXN9_WLAN[32]

PCIE_TXP9_WLAN[32]

XDP_PRDY#_CPU[16]

XDP_PREQ#_CPU[16]

+3V_DEEP_SUS

PCIE_RXN8_SSD[31]

PCIE_RXP8_SSD[31]

PCIE_TXN8_SSD[31]

PCIE_TXP8_SSD[31]

PCIE_RXN7_SSD[31]

PCIE_RXP7_SSD[31]

PCIE_TXN7_SSD[31]

PCIE_TXP7_SSD[31]

5

C162 0.22U/10V_4

C163 0.22U/10V_4

C164 0.22U/10V_4

C165 0.22U/10V_4

C167 0.22U/10V_4

C166 0.22U/10V_4

C168 0.22U/10V_4

C169 0.22U/10V_4 R122 *10K_4

C170 0.1U/16V_4

C171 0.1U/16V_4

C174 0.1U/16V_4

C175 0.1U/16V_4

C172 0.1U/16V_4

C173 0.1U/16V_4

R132 10K_4

PCIE_TXN5_CARD_C

PCIE_TXP5_CARD_C

PCIE_TXN10_LAN_C

PCIE_TXP10_LAN_C

PCIE_TXN9_WLAN_C

PCIE_TXP9_WLAN_C

R131 100/F_4

PIRQA#

PEG_TXN1_C

PEG_TXP1_C

PEG_TXN2_C

PEG_TXP2_C

PEG_TXN3_C

PEG_TXP3_C

PEG_TXN4_C

PEG_TXP4_C

BB11

H13

G13

B17

A17

G11

F11

D16

C16

H16

G16

D17

C17

G15

F15

B19

A19

F16

E16

C19

D19

G18

F18

D20

C20

F20

E20

B21

A21

G21

F21

D21

C21

E22

E23

B23

A23

F25

E25

D23

C23

F5

E5

D56

D61

E28

E27

D24

C24

E30

F30

A25

B25

4

U1H

PCIE/USB3/SATA

PCIE1_RXN/USB3_5_RXN

PCIE1_RXP/USB3_5_RXP

PCIE1_TXN/USB3_5_TXN

PCIE1_TXP/USB3_5_TXP

PCIE2_RXN/USB3_6_RXN

PCIE2_RXP/USB3_6_RXP

PCIE2_TXN/USB3_6_TXN

PCIE2_TXP/USB3_6_TXP

PCIE3_RXN

PCIE3_RXP

PCIE3_TXN

PCIE3_TXP

PCIE4_RXN

PCIE4_RXP

PCIE4_TXN

PCIE4_TXP

PCIE5_RXN

PCIE5_RXP

PCIE5_TXN

PCIE5_TXP

PCIE6_RXN

PCIE6_RXP

PCIE6_TXN

PCIE6_TXP

PCIE7_RXN/SATA0_RXN

PCIE7_RXP/SATA0_RXP

PCIE7_TXN/SATA0_TXN

PCIE7_TXP/SATA0_TXP

PCIE8_RXN/SATA1A_RXN

PCIE8_RXP/SATA1A_RXP

PCIE8_TXN/SATA1A_TXN

PCIE8_TXP/SATA1A_TXP

PCIE9_RXN

PCIE9_RXP

PCIE9_TXN

PCIE9_TXP

PCIE10_RXN

PCIE10_RXP

PCIE10_TXN

PCIE10_TXP

PCIE_RCOMPN

PCIE_RCOMPP

PROC_PRDY#

PROC_PREQ#

GPP_A7/PIRQA#

PCIE11_RXN/SATA1B_RXN

PCIE11_RXP/SATA1B_RXP

PCIE11_TXN/SATA1B_TXN

PCIE11_TXP/SATA1B_TXP

PCIE12_RXN/SATA2_RXN

PCIE12_RXP/SATA2_RXP

PCIE12_TXN/SATA2_TXN

PCIE12_TXP/SATA2_TXP

*SKL_ULT

PCI-E Port Mapping Table

PCI-E Port

Port1

Port2

Port3

Port4

Port5

Port6

Port7

Port8

Port9

Port10

Port11

Port12

4

SKL_ULT

Function

dGPU

dGPU

dGPU

dGPU

CardReader

LAN

HDD

ODD

WLAN

Un-used

SSDx2

SSDx2/

SATA2

?

USB2

PDC

CLK RQ Port

Port0

Port1

Port2

Port3

Port4

Port5

Need apply PN

SSIC / USB3

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

?8 OF 20REV = 1

Function

VGA

CR

SSD

WLAN

LAN

Un-used

3

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB30_RX1USB30_RX1+

USB30_TX1USB30_TX1+

USB30_RX2USB30_RX2+

USB30_TX2USB30_TX2+

TP8502

TP112

TP25

TP29

Ra

TP31

USB2_COMP

USB2_ID

USB2_VBUSSENSE

DGPU_HOLD_RST#

GPU_EVENT #

DGPU_PWR_EN

DGPU_PWROK

OCP_OC#

GC6_FB_EN

DEVSLP0

ODD_PRSN T#_R

GPIO35_R

USBP1USBP1+

USBP2USBP2+

USBP3USBP3+

USBP5USBP5+

USBP6USBP6+

USBP7USBP7+

USBP8USBP8+

R130 113/F_4

R303 1K_4

R304 1K_4

R133 *0_4

R302 0_4

R134 0_4

USB30_RX1- [29]

USB30_RX1+ [29]

USB30_TX1- [29]

USB30_TX1+ [29]

USB30_RX2- [29]

USB30_RX2+ [29]

USB30_TX2- [29]

USB30_TX2+ [29]

USBP1- [29]

USBP1+ [29]

USBP2- [29]

USBP2+ [29]

USBP3- [25]

USBP3+ [25]

USBP5- [30]

USBP5+ [30]

USBP6- [29]

USBP6+ [29]

USBP7- [32]

USBP7+ [32]

USBP8- [25]

USBP8+ [25]

DGPU_HOLD_RST# [19]

GPU_EVENT # [22]

DGPU_PWR_EN [20,46]

DGPU_PWROK [21,33,45]

TP35

GC6_FB_EN [20,22]

DEVSLP0 [31]

1005 Add USB3.0 TXP TP

PLACE 'Ra' WITHIN 500 MILS

FROM USB2_COMP PIN WITH

TRACE IMPEDANCE LESS THAN 0.5 OHMS

SATA_LED#SATA_LED#_R

USB3.0 Port Mapping Table

USB3.0 Function

PORT-1

PORT-2

PORT-3

PORT-4

1005 Change Name from DEVSLP2 to DEVSLP0

DEVSLP0 and GC6_FB_EN SWAP

1005 GPIO35 and ACC_LED# SWAP

3

USB3.0 MB-1

Cobime USB3.0 Small Board

NC

NC

2

USB3.0 (M/B-1)

USB3.0 Small Board

Combo USB3.0 MB-1

Combo USB3.0 Smal l Board

Camera

1015 Add USB2.0 PORT5

IR CAM

Combo USB3.0 Smal l Board

WLAN

Touch Screen

If OTG is not implemented on the platform,

then USB2_ID and USB2_VBUSSENSE should both

be connected to ground.

ACC_LED# [10,32]

ZERO_ODD_DP# [32]

GPIO35 [31]

SATA_LED# [32]

GPIO35:

SSD SATA IF => High

SSD PCIE IF => Low

USB2.0 Port Mapping Table

USB2.0 Function

PORT-1

PORT-2

PORT-3

PORT-4

PORT-5

PORT-6

PORT-7

PORT-8

PORT-9

PORT-10

2

1

+3V

GPU_EVENT #

DGPU_HOLD_RST#

DGPU_PWR_EN

DGPU_PWROK

SATA_LED#

GC6_FB_EN

ODD_PRSN T#_R

GPIO35

R123 *10K_4

R124 10K_4

R125 10K_4

R126 10K_4

R127 *10K_4

R128 10K_4

R400 10K_4

1005 GPIO35 Add R400 10K PU to +3V

DGPU_HOLD_RST#

R129 100K_4

Cobime USB3.0 MB-1

Cobime USB3.0 Small Board

Camera

NC

IR CAM

Cobime USB3.0 Small Board

WLAN

Touch Screen

NC

NC

PROJECT : G34A

PROJECT : G34A

PROJECT : G34A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

12 -- SKYPAKE 16/20 (PCIE/USB)

12 -- SKYPAKE 16/20 (PCIE/USB)

BU5

BU5

BU5

12 -- SKYPAKE 16/20 (PCIE/USB)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

12

DIS ONLY

DIS ONLY

12 47Tuesday, January 05, 2016

12 47Tuesday, January 05, 2016

12 47Tuesday, January 05, 2016

1A

1A

1A

5

4

3

2

1

+3V_RTC_2 [4,15]

+BAT_RTC [4,15,29,30,34,47]

+1.8V_DEEP_SUS [5,9,15,37,47]

+3V [2,4,10,11,12,14,15,16,17,18,19,20,21,25,26,27,28,29,30,31,32,33,39, 43,44,47]

?

10 OF 20

?

PDC

9 OF 20

Need apply PN

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XCLK_BIASREF

TBT

Need apply PN

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

?