Page 1

1

2

3

4

5

6

7

8

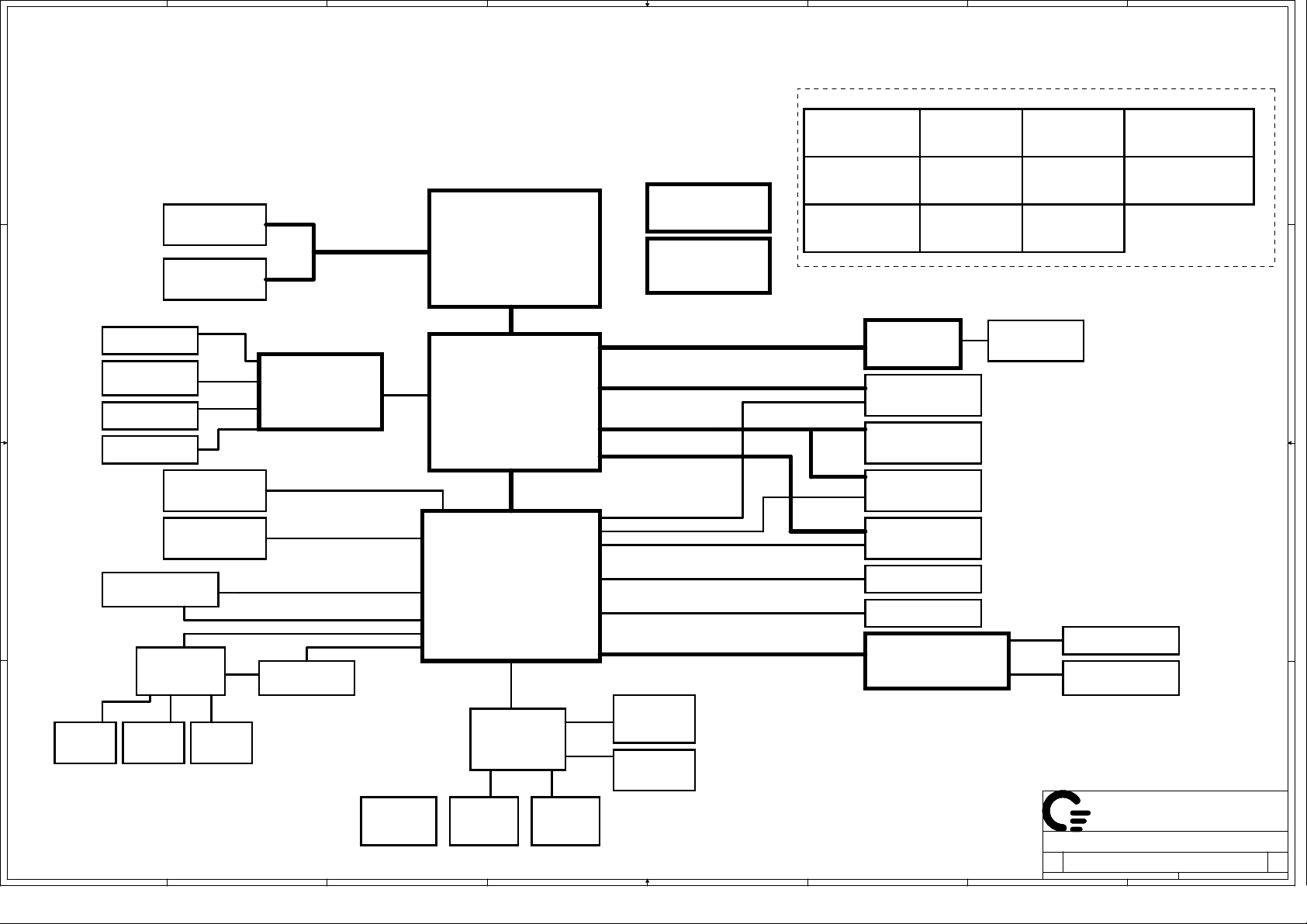

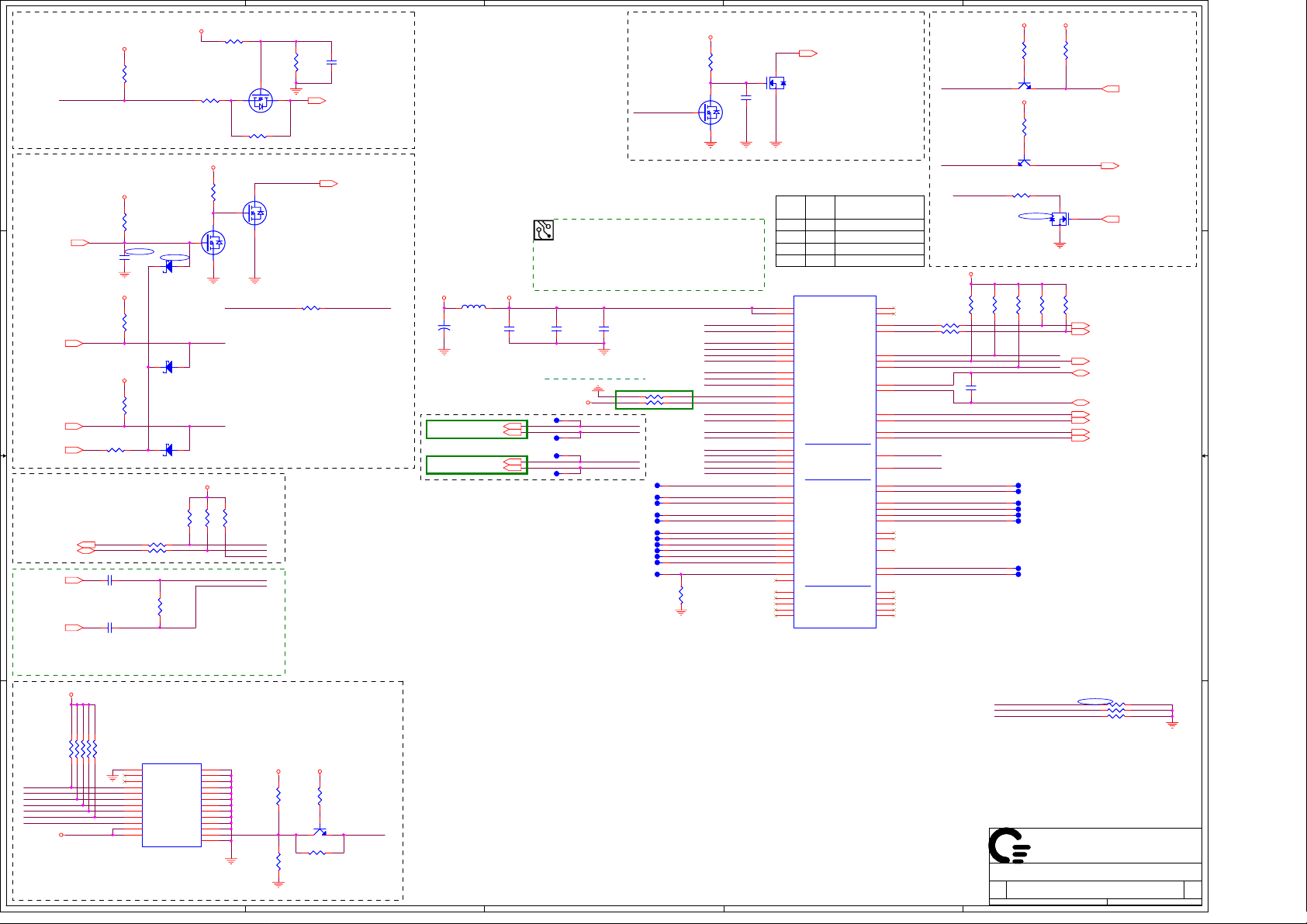

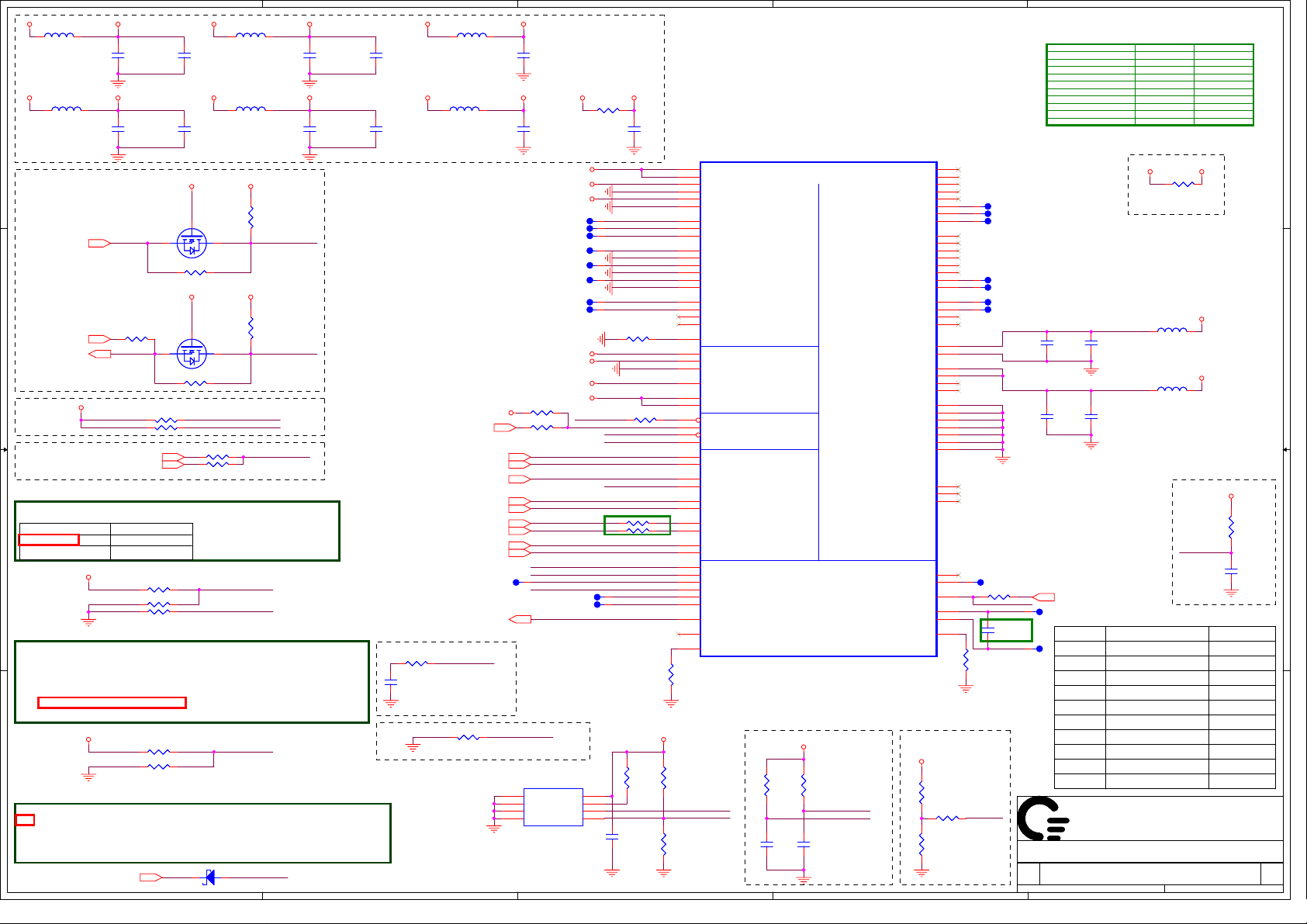

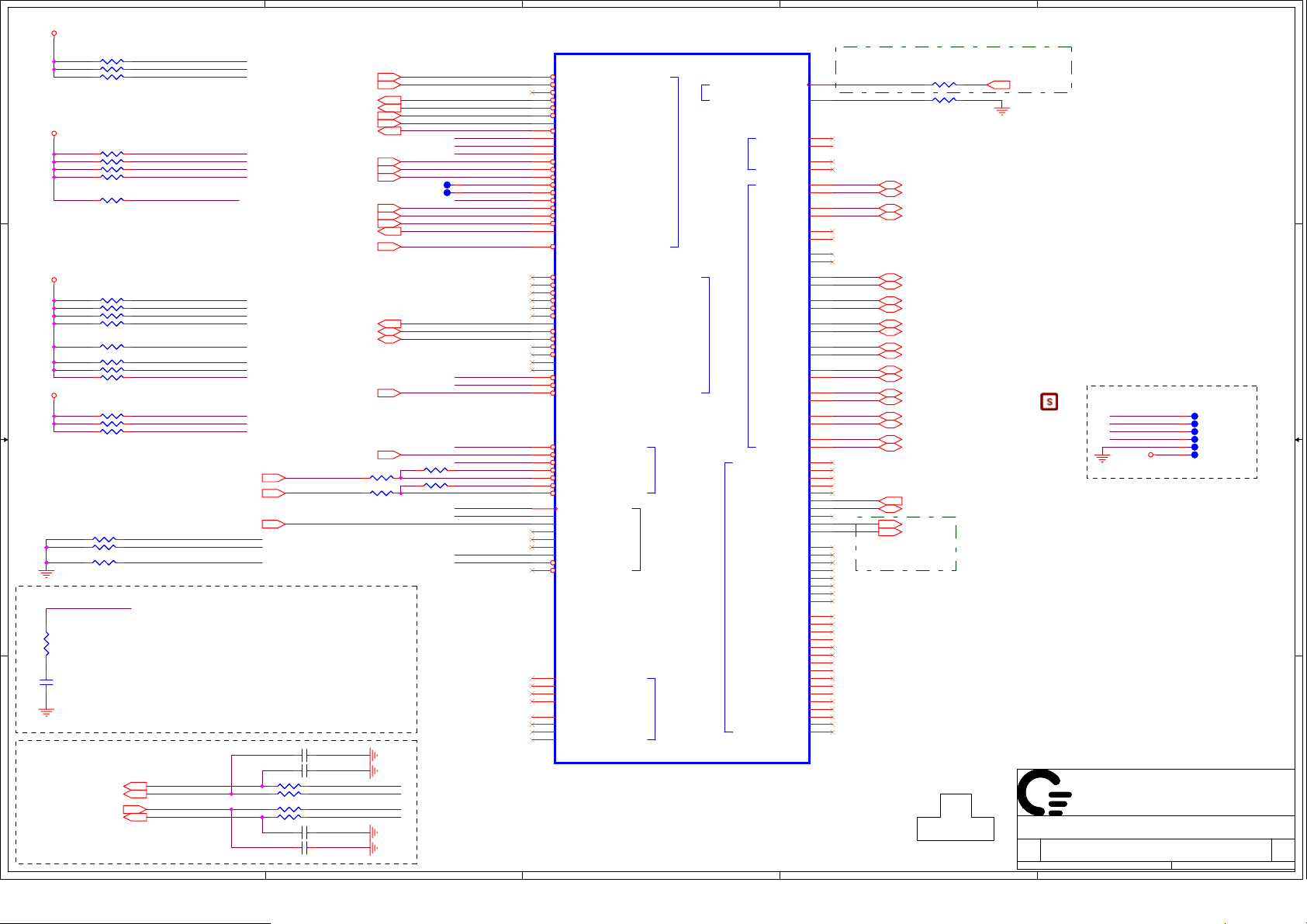

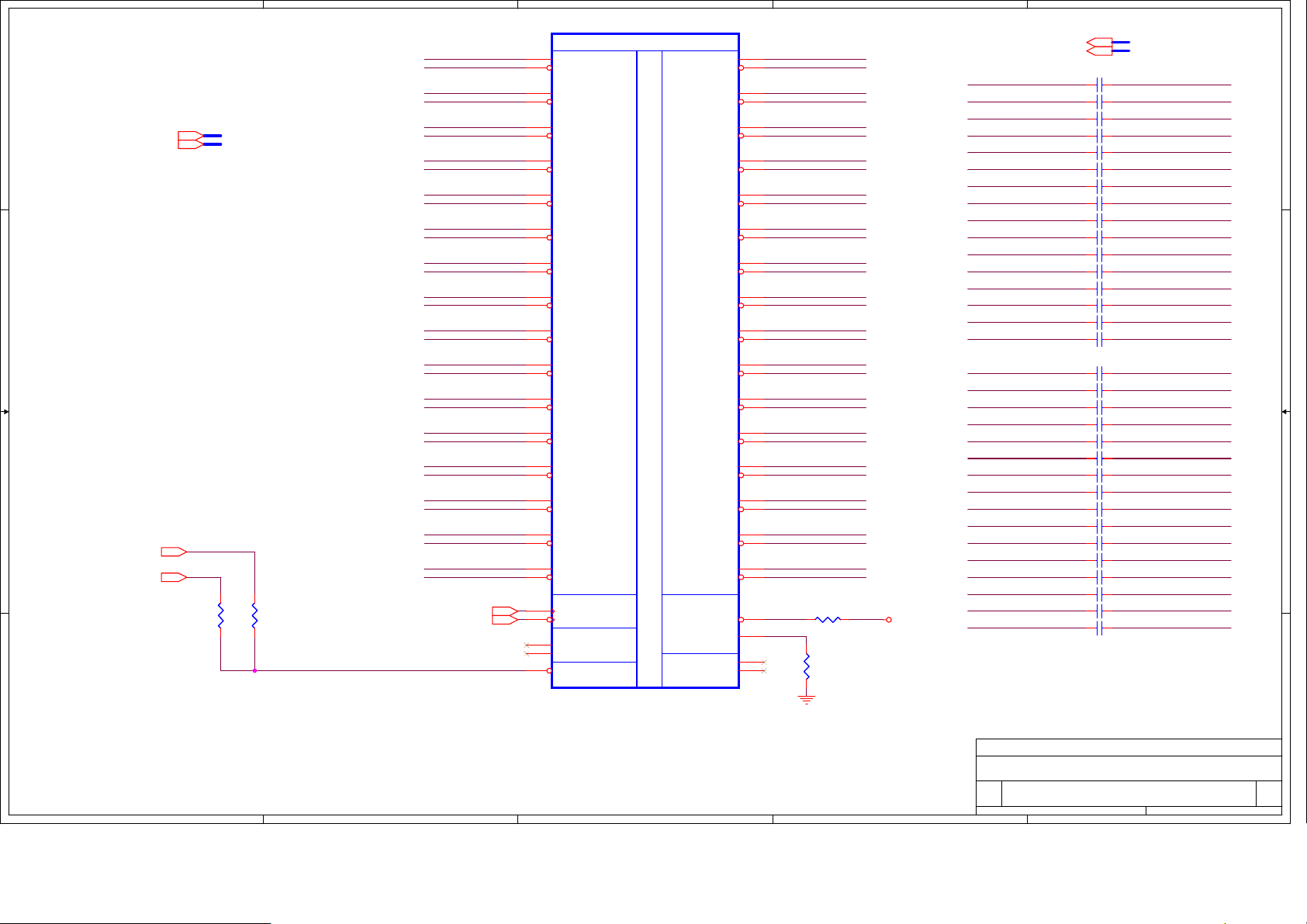

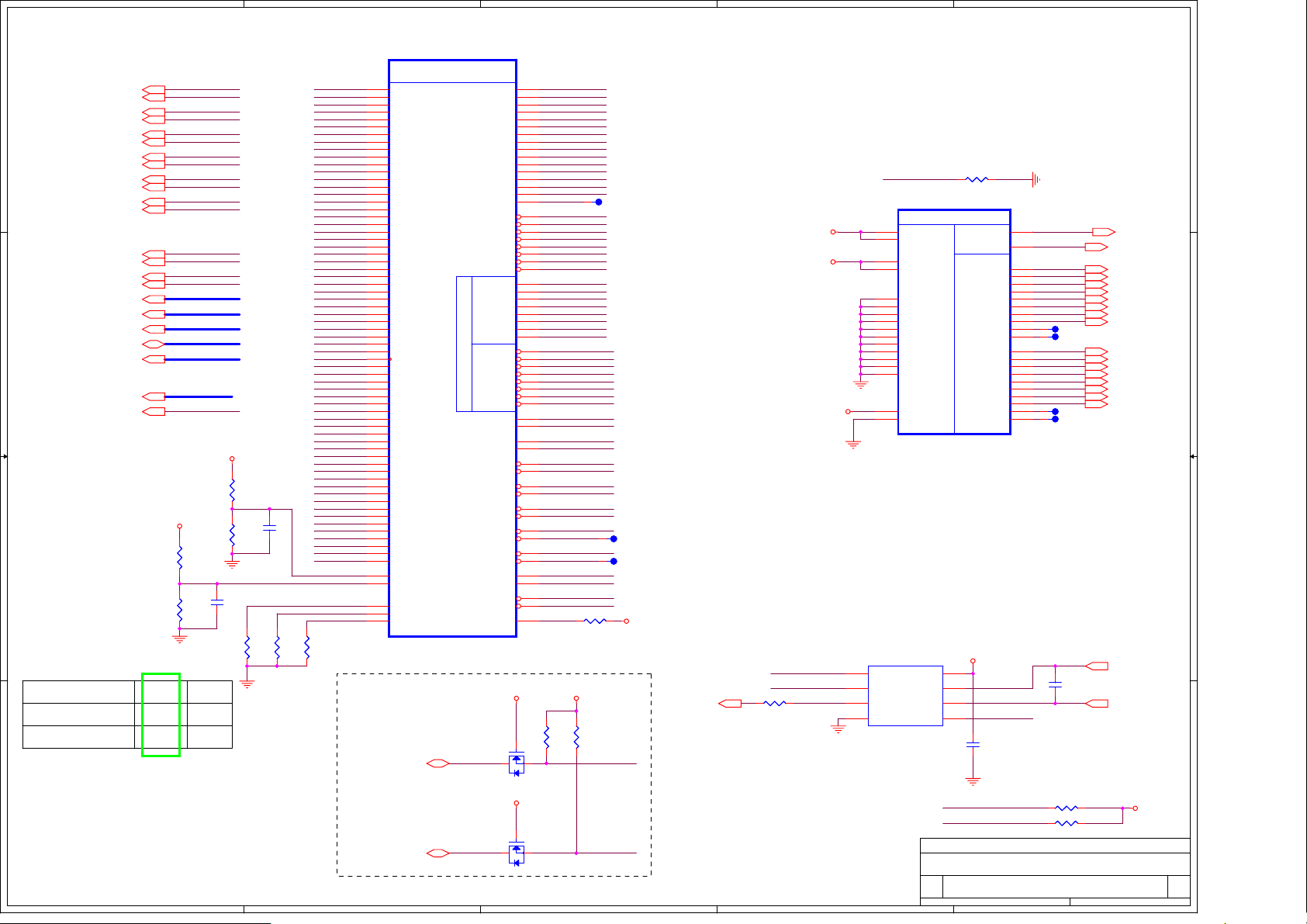

Hepburn AMD Discrete GFX

A A

VER : A00

FAN & THERMAL

DDRII-SODIMM1

PG 16,17

DDRII-SODIMM2

PG 16,17

B B

C C

Panel Connector

PG 26

HDMI CONN.

PG 28

CRT CONN.

PG 27

VRAM

PG 23

E-SATA+USB CONN

PG 38

LVDS

HDMI

VGA

SATA - HDD

Fixed SATA ODD

PG 30

PG 30

PG 18,19,20,21,

22

800 MHz DDR II

LVDS

M82-S

632 BGA

25mmX25mm

SATA

SATA

PCIEx16

SATA

USB2.0

Azalia

USB2.0

AUDIO/AMP

IDT_92HD73C

PG 31

A-MIC

PG 32

D D

SPK conn

PG 31 PG 32

Audio

Jacks x3

Camera + D-MIC

PG 32

USER

INTERFACE

PG 44

1

2

3

AMD S1G2

64 X2

(638 S1 socket)

PG 3,4,5,6

HT_LINK

RS780M

528 FCBGA

21mmX21mm

PG 7,8,9,10,11

A_LINK

SB700

528 BGA

21mmX21mm

PG 12,13,14,15

KBC

ITE8512

FLASH

16Mbits

PG 41

LPC

PG 42

18X8

PS/2SPI

Touchpad

PG 43

4

CLOCK

SLG8SP628VTR(QFN)

PCIEx1

PCIEx1

PCIEx2

PCIEx1

USB2.0

USB2.0

USB2.0

USB2.0 x 4

USB2.0

33MHz PCI

CIR

PG 43

TSOP36136TS

Keyboard

PG 43

EMC1423

PG 29

PG 25

5

POWER

REGULATOR

+1.5V_RUN/+1.1V_RUN

PG 50

REGULATOR

+1.8V_SUS/+1.2V_ALW

/+0.9V_DDR_VTT

CPU VR

PG 53

DC/DC

+3.3V_ALW/+5V_ALW

+15V_ALW/+5V_SUS

PG 52

1.2V_ALW_SUS

PG 51,54 PG 60 PG 55

LAN

PG 33

5784M

EXPRESS-CARD

R5538

MINI-CARD

WLAN

MINI-CARD

WWAN

MINI-CARD

WPAN

USB conn x 4

Biometric

PG 37

PG 39

PG 40

PG 39

PG 38

PG 44

SYSTEM

RESET CIRCUIT

AC/BATT

CONNECTOR

M82_POWER+2.5V_RUNVCC_NB

RJ45/Magnetics

PG 34

1394

8-in-1 Card Reader

R5C833

6

PG 35

BATT

CHARGER

PG 47PG 45

RUN POWER SW

+5V/+3.3V/+1.8V/+1.2V_RUN

+3.3V/+1.2V_SUS

1394 CONN.

Card Reader CONN.

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FX6 3A

FX6 3A

FX6 3A

Date: Sheet

Date: Sheet

Date: Sheet

7

PG 36

PG 36

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

PG 46PG 54PG 49

170Tuesday, May 20, 2008

170Tuesday, May 20, 2008

170Tuesday, May 20, 2008

of

of

of

8

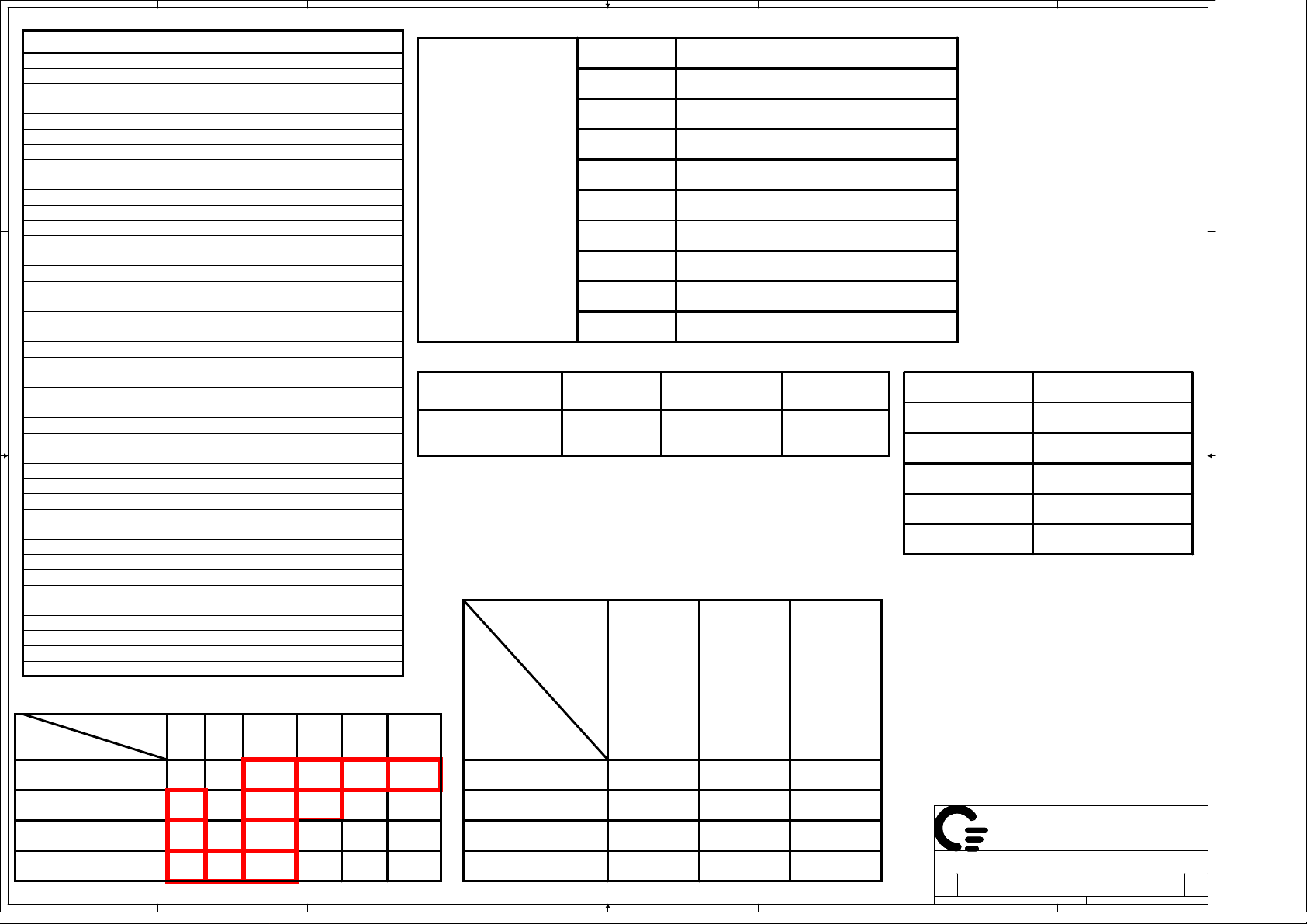

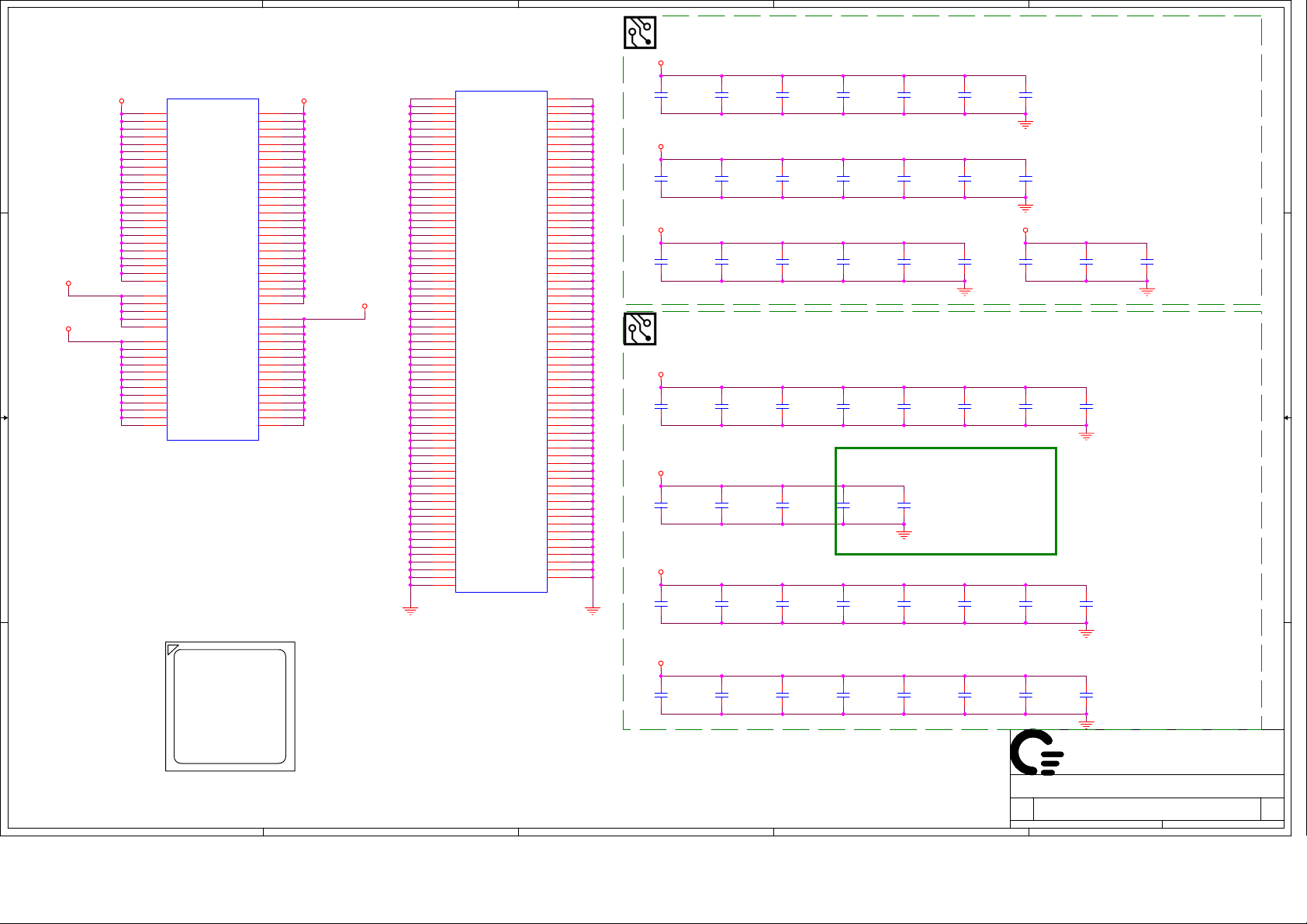

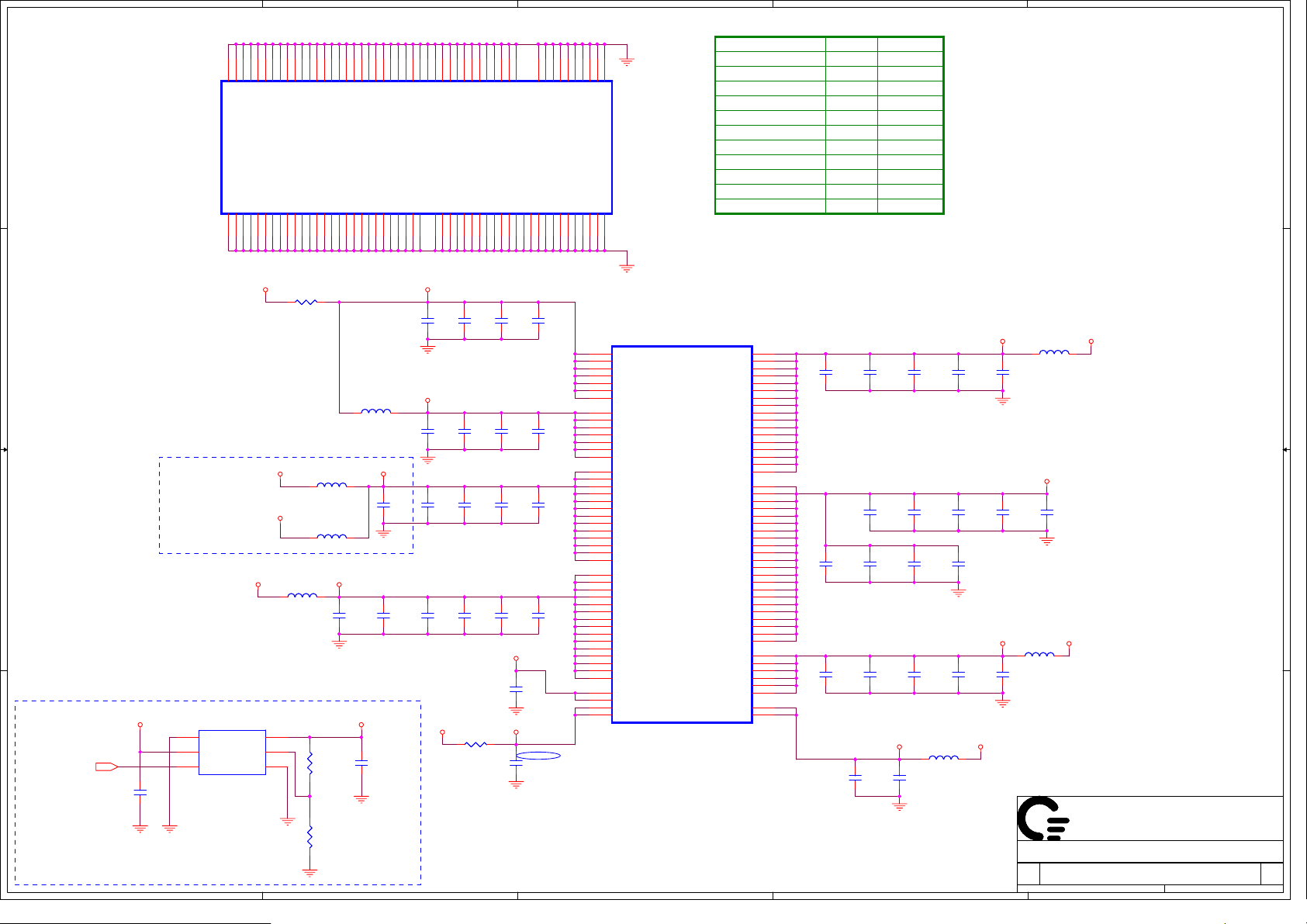

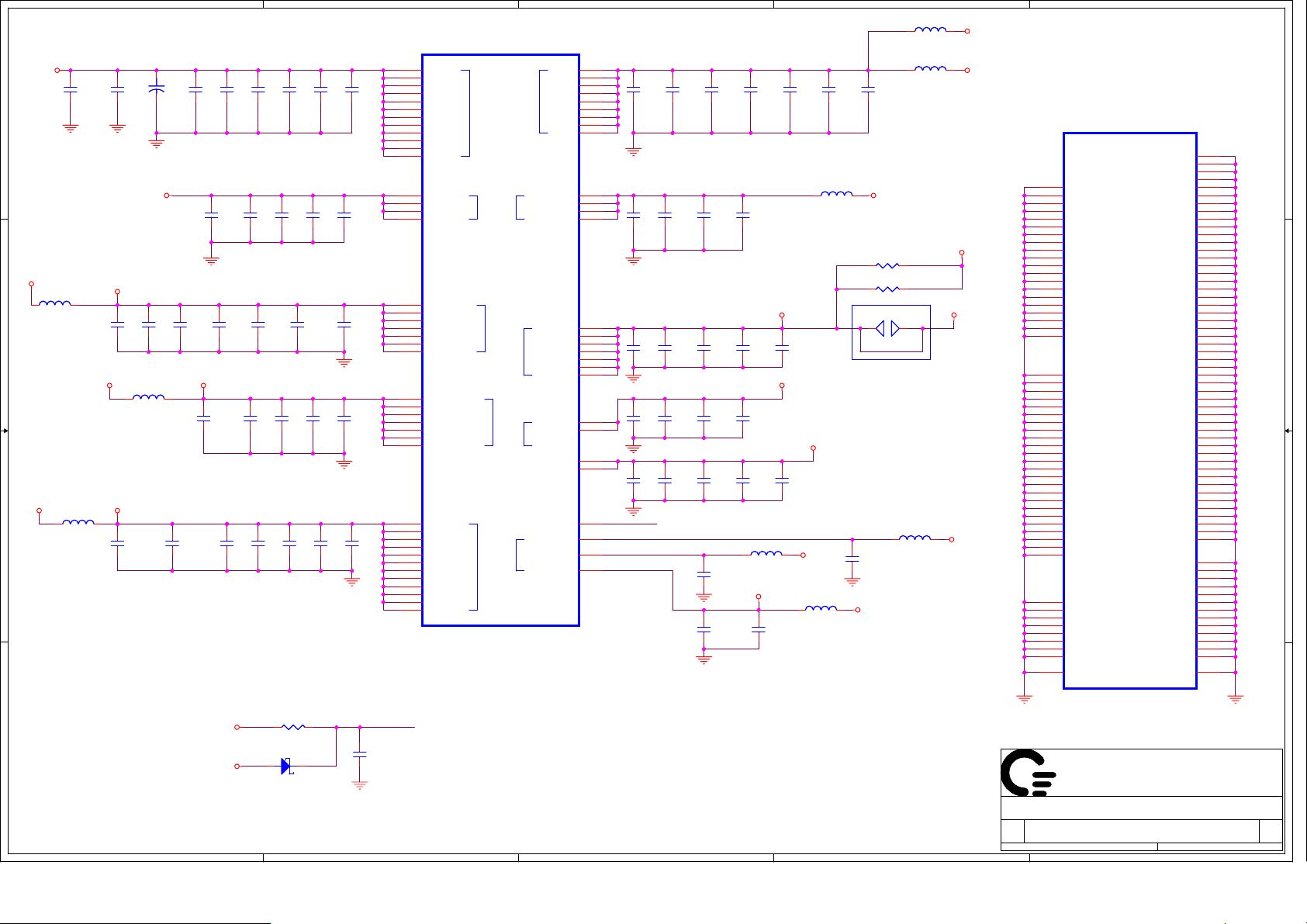

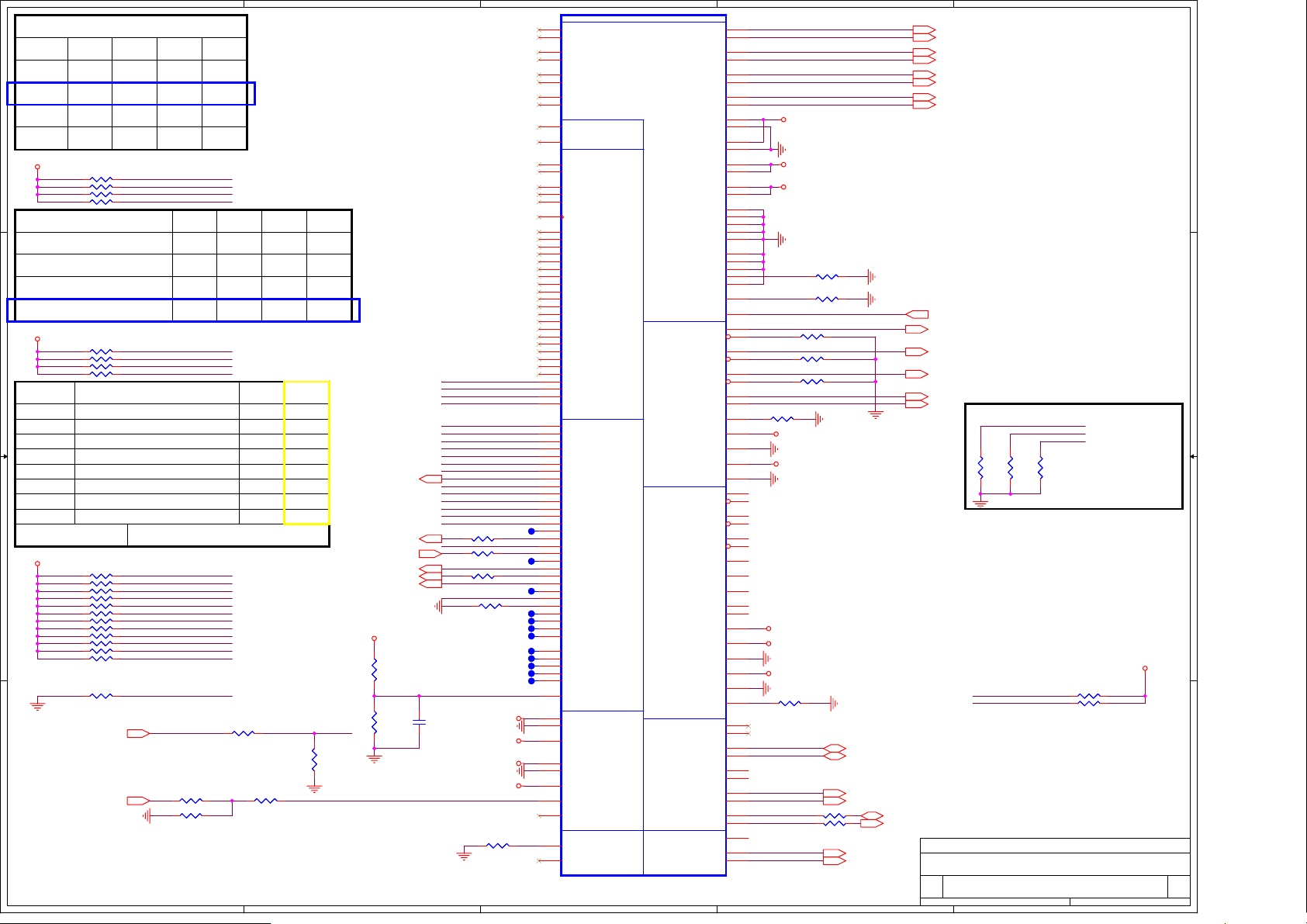

Page 2

1

INDEX

Pg# Description

Schematic Block Diagram

1

Index/Power States and USB/PCI/PCIe map

2

CPU page

3-6

RS780M page

7-11

12-15

A A

B B

C C

SB700 page

DDRII SO-DIMM(200P)

16-17

M82-S

18-23

24

LCD/CRT HYBRID

Clock Generator

25

LCD Conn.

26

CRT Conn

27

HDMI

28

FAN /THERMAL

29

SATA (HDD&CD_ROM)

30

31-32

Audio CODEC(92HD73)/Phone Jack

LOM /Switch

33-34

PC CARD/1394

35-36

EXPRESS

37

USB

38

Mini Card

39

WWAN

40

Flash ROM, RTC

41

ITE8512

42

43

TP/KB/CIR/BT

Switch,Keyboard & LED

44

System Reset Circuit

45

RUN POWER

46

Battery Charger

47

DCIN,Batt

48

1.8V_SUS,0.9VTT

49

1.5V_RUN AND 1.1V_RUN

50

51

+VCC_NB

+3.3V_ALW/+5V_SUS

52

VCC_VCORE

53

54

+1.2V_ALW_SUS

55

VGA_M82

Power Rail for system

56

Power Sequence Diagram

57

SMBUS BLOCK

58

59 Stitch caps and Screw hole.

POWER STATES

State

Signal

SLP

S3#

SLP

S5#

2

ALWAYS

PLANE

SUS

PLANE

RUN

PLANE

3

4

USB PORT#

0

1

2

3

SB700

4

5

6

7

10

11

PCI TABLE

REQ#/GNT#

CardBus AD17 REQ#1/GNT#1

PM TABLE

CLOCKS

State

power

plane

+15V_ALW

+5V_ALW

+3.3V_ALW +1.8V_SUS +1.5V_RUN

5

DESTINATION

Left side USB.

Left side USB.

IO board

IO board

WLAN

WWAN

WPAN

EXPRESS

Biometric

Camera

+5V_SUS

+3.3V_SUS

+0.9V_DDR_VTT

+1.2V_ALW_SUS

6

PIRQPCI DEVICE IDSEL

IRQ_SERIRQ

IRQD

+5V_RUN

+3.3V_RUN

+2.5V_RUN

+1.8V_RUN

+1.2V_RUN

+VCC_CORE

+NB_VCORE

7

8

PCI EXPRESS DESTINATION

Lane 1

Lane 2

Lane 3

Lane 4

WLAN

WPAN

LOM

EXPRESS CARD

Lane 5 WWAN

S0 (Full ON)

D D

S3 (Suspend to RAM)

S4 (Suspend to DISK) ON OFF

S5 (SOFT OFF) ON OFFLOW LOW

1

HIGH

HIGH

ON

LOW HIGH ON ON OFF

LOW HIGH

2

ON ON ON

OFF

OFF

OFF

OFF

OFF

3

S0

S3

S5 S4/AC

S5 S4 on Battery

4

ON

ON

ON

ON ON

ON

OFF

OFFOFF

5

OFF

OFF

OFF

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

6

Date: Sheet

COMPUTER

Index

Index

Index

FX6 3A

FX6 3A

FX6 3A

7

of

of

of

270Tuesday, May 20, 2008

270Tuesday, May 20, 2008

270Tuesday, May 20, 2008

8

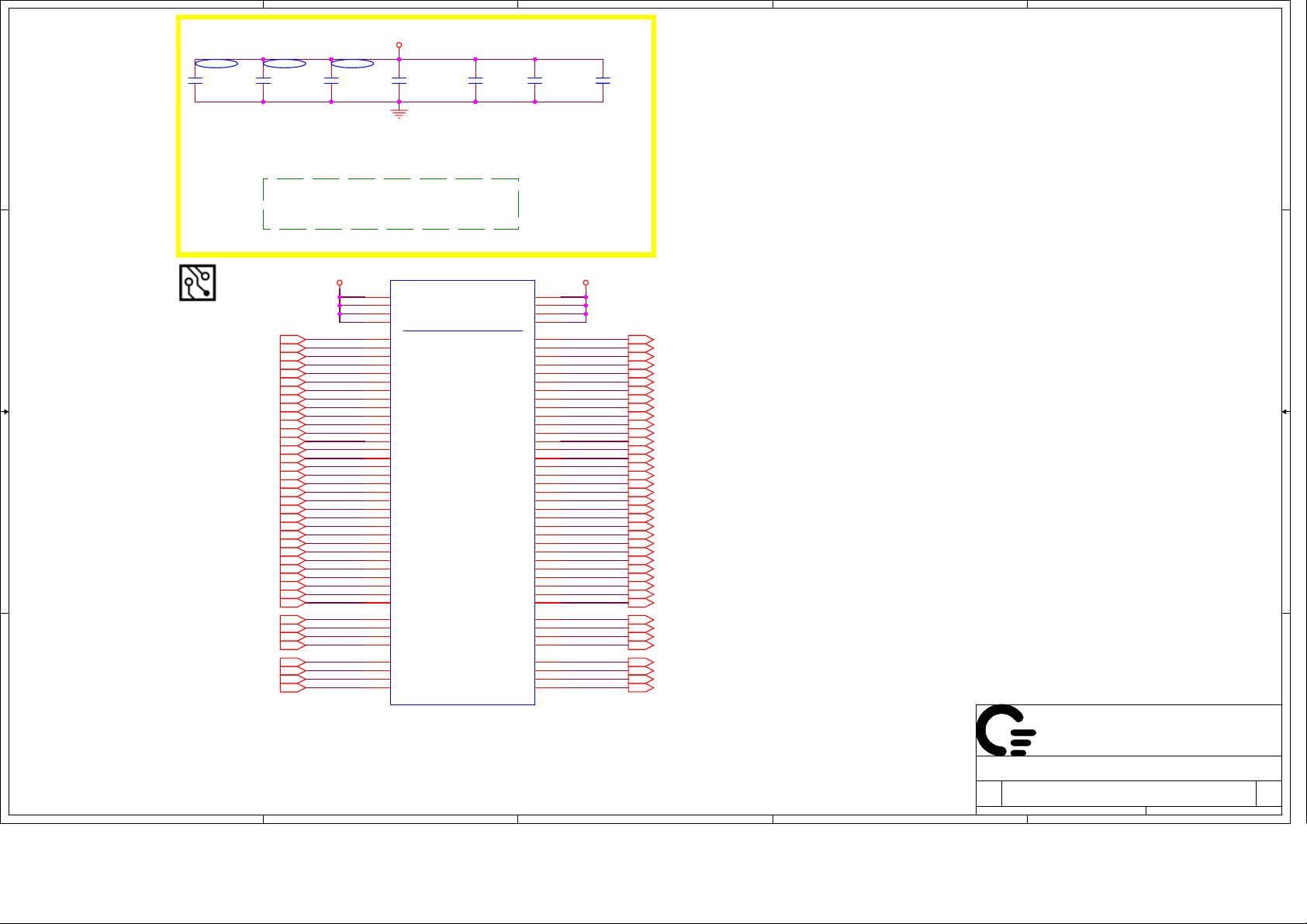

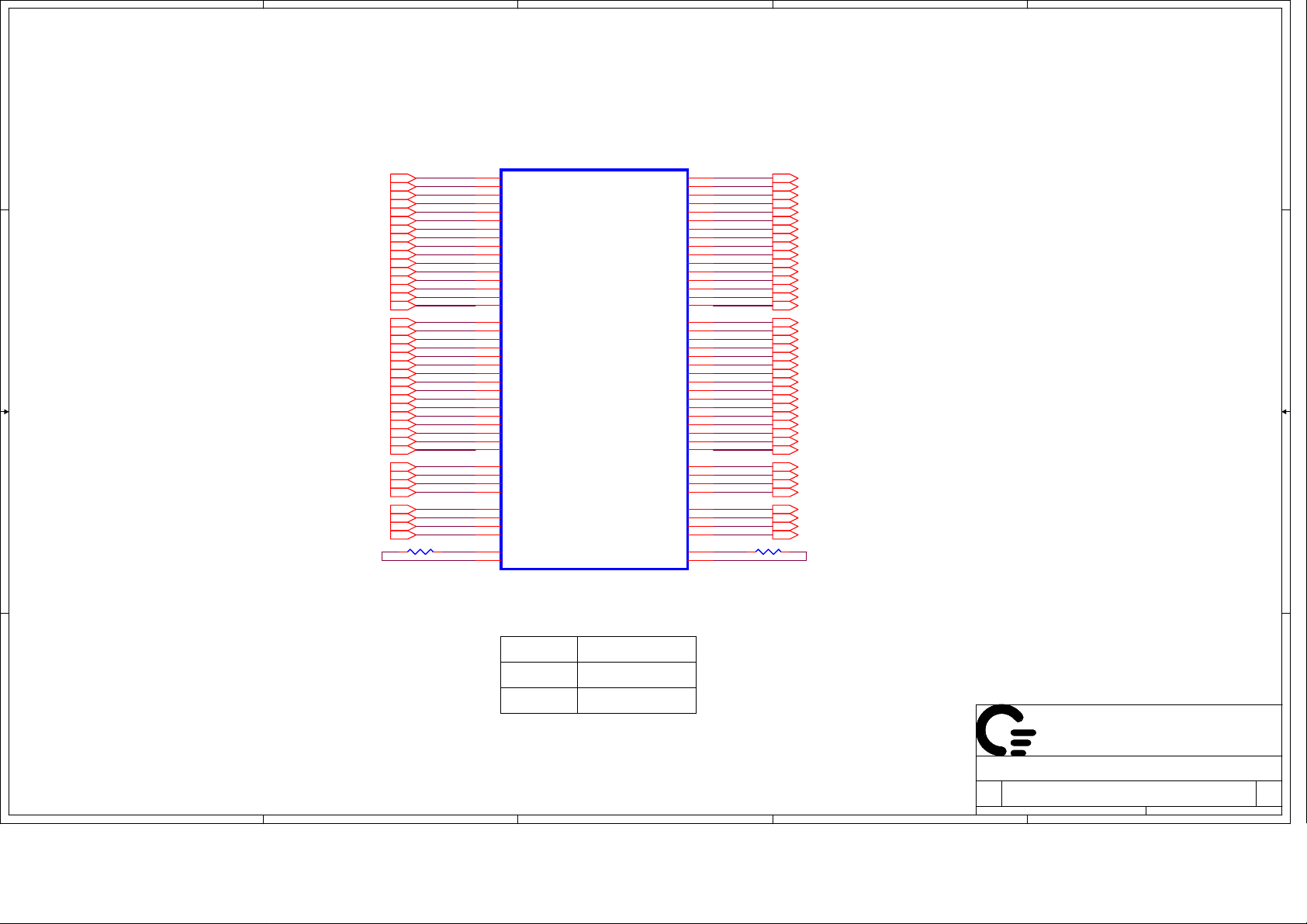

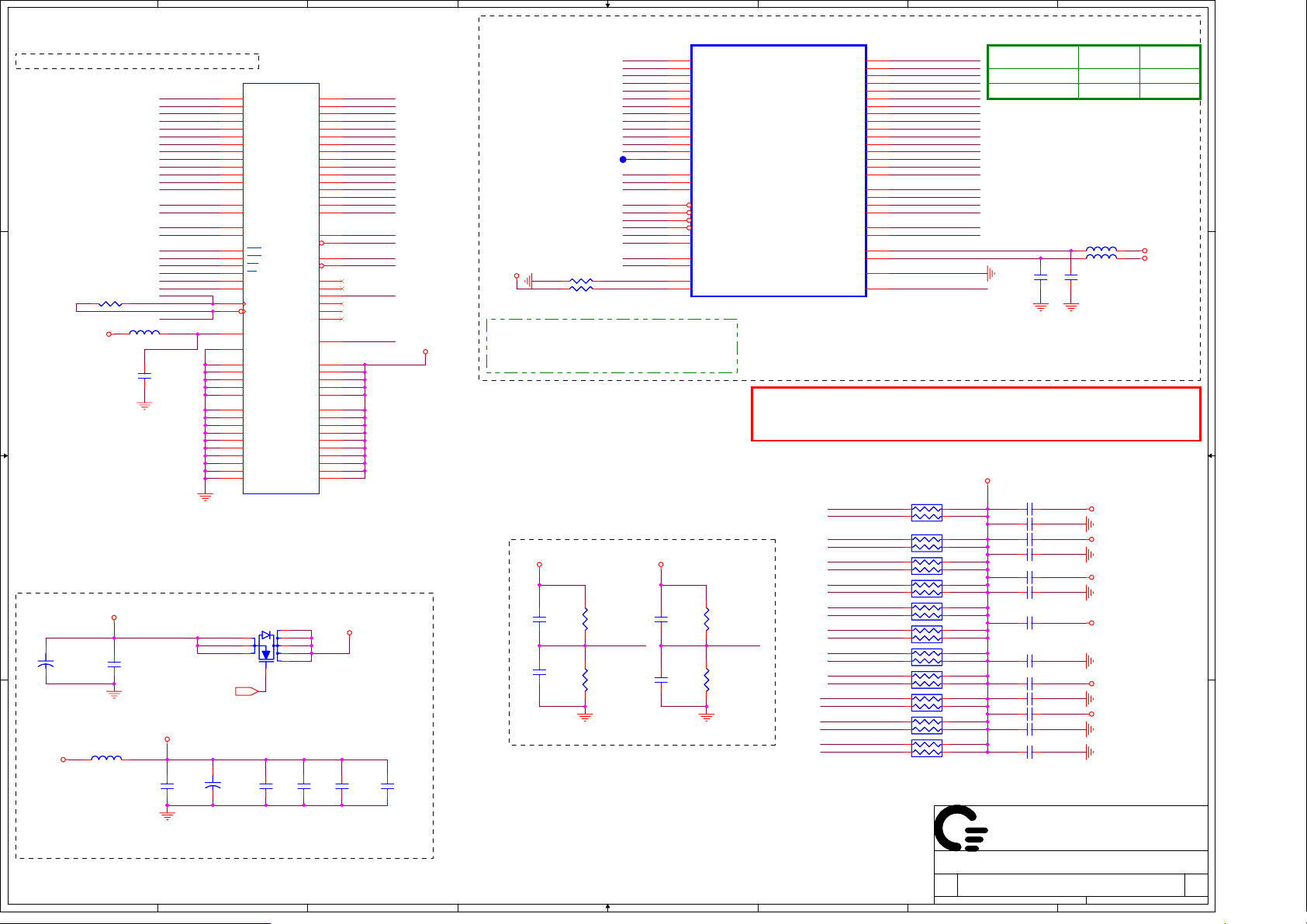

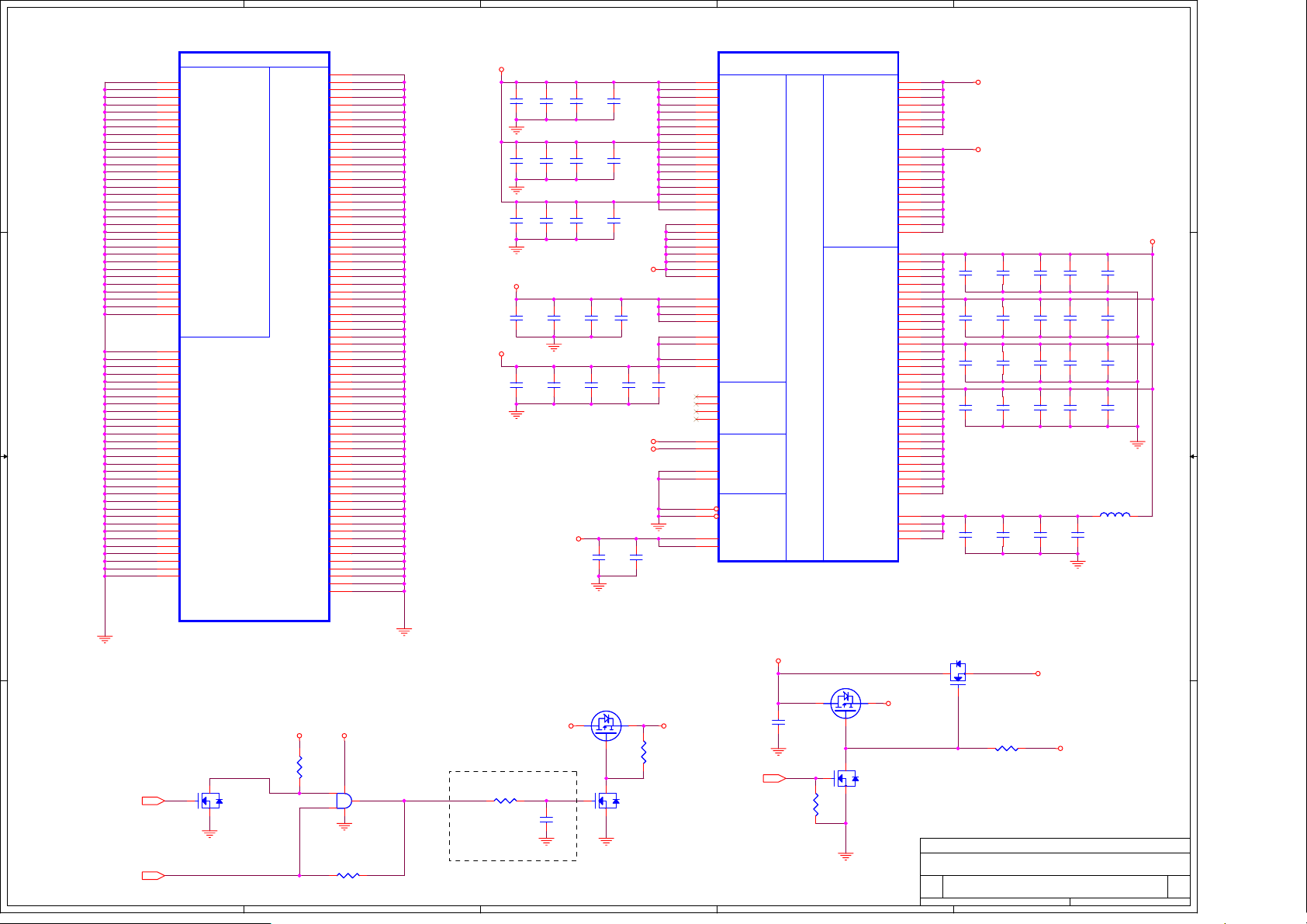

Page 3

5

C672

C665

(19)

D D

C665

10U

10U

10

10

X7R

X7R

0805

0805

C672

10U

10U

10

10

X7R

X7R

0805

0805

C673

C673

10U

10U

10

10

X7R

X7R

0805

0805

4

+1.2V_RUN

C666

C666

0.22U

0.22U

10

10

X7R

X7R

0603

0603

C671

C671

0.22U

0.22U

10

10

X7R

X7R

0603

0603

C669

C669

180P

180P

50

50

NPO

NPO

C674

C674

180P

180P

50

50

NPO

NPO

3

2

1

Place close to socket

* If VLDT is connected only on one side,

one 4.7uF C101 cap should be added to

the island side

U30A

+1.2V_RUN +1.2V_RUN

C C

HT_CADIN07

HT_CADIN#07

HT_CADIN17

HT_CADIN#17

HT_CADIN27

HT_CADIN#27

HT_CADIN37

HT_CADIN#37

HT_CADIN47

HT_CADIN#47

HT_CADIN57

HT_CADIN#57

HT_CADIN67

HT_CADIN#67

HT_CADIN77

HT_CADIN#77

HT_CADIN87

HT_CADIN#87

HT_CADIN97

HT_CADIN#97

B B

A A

5

HT_CADIN107

HT_CADIN#107

HT_CADIN117

HT_CADIN#117

HT_CADIN127

HT_CADIN#127

HT_CADIN137

HT_CADIN#137

HT_CADIN147

HT_CADIN#147

HT_CADIN157

HT_CADIN#157

HT_CLKIN07

HT_CLKIN#07

HT_CLKIN17

HT_CLKIN#17

HT_CTLIN07

HT_CTLIN#07

HT_CTLIN17

HT_CTLIN#17

U30A

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

FOX_PZ6382A-284S-41F

FOX_PZ6382A-284S-41F

4

HT LINK

HT LINK

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

500mA

HT_CADOUT0 7

HT_CADOUT#0 7

HT_CADOUT1 7

HT_CADOUT#1 7

HT_CADOUT2 7

HT_CADOUT#2 7

HT_CADOUT3 7

HT_CADOUT#3 7

HT_CADOUT4 7

HT_CADOUT#4 7

HT_CADOUT5 7

HT_CADOUT#5 7

HT_CADOUT6 7

HT_CADOUT#6 7

HT_CADOUT7 7

HT_CADOUT#7 7

HT_CADOUT8 7

HT_CADOUT#8 7

HT_CADOUT9 7

HT_CADOUT#9 7

HT_CADOUT10 7

HT_CADOUT#10 7

HT_CADOUT11 7

HT_CADOUT#11 7

HT_CADOUT12 7

HT_CADOUT#12 7

HT_CADOUT13 7

HT_CADOUT#13 7

HT_CADOUT14 7

HT_CADOUT#14 7

HT_CADOUT15 7

HT_CADOUT#15 7

HT_CLKOUT0 7

HT_CLKOUT#0 7

HT_CLKOUT1 7

HT_CLKOUT#1 7

HT_CTLOUT0 7

HT_CTLOUT#0 7

HT_CTLOUT1 7

HT_CTLOUT#1 7

3

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

COMPUTER

S1G2 HT I/F

S1G2 HT I/F

S1G2 HT I/F

FX6 3A

FX6 3A

FX6 3A

of

of

of

370Tuesday, May 20, 2008

370Tuesday, May 20, 2008

370Tuesday, May 20, 2008

1

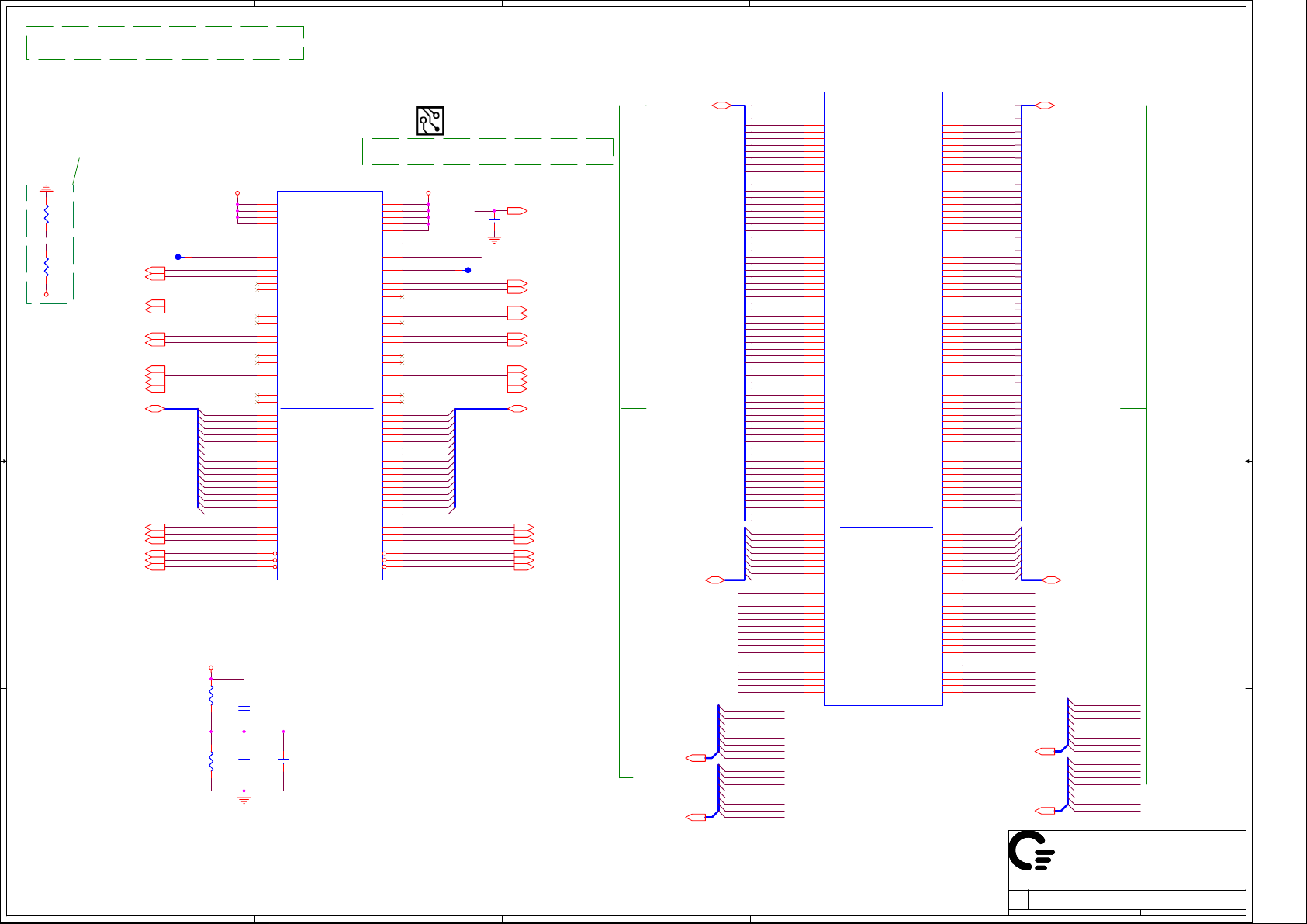

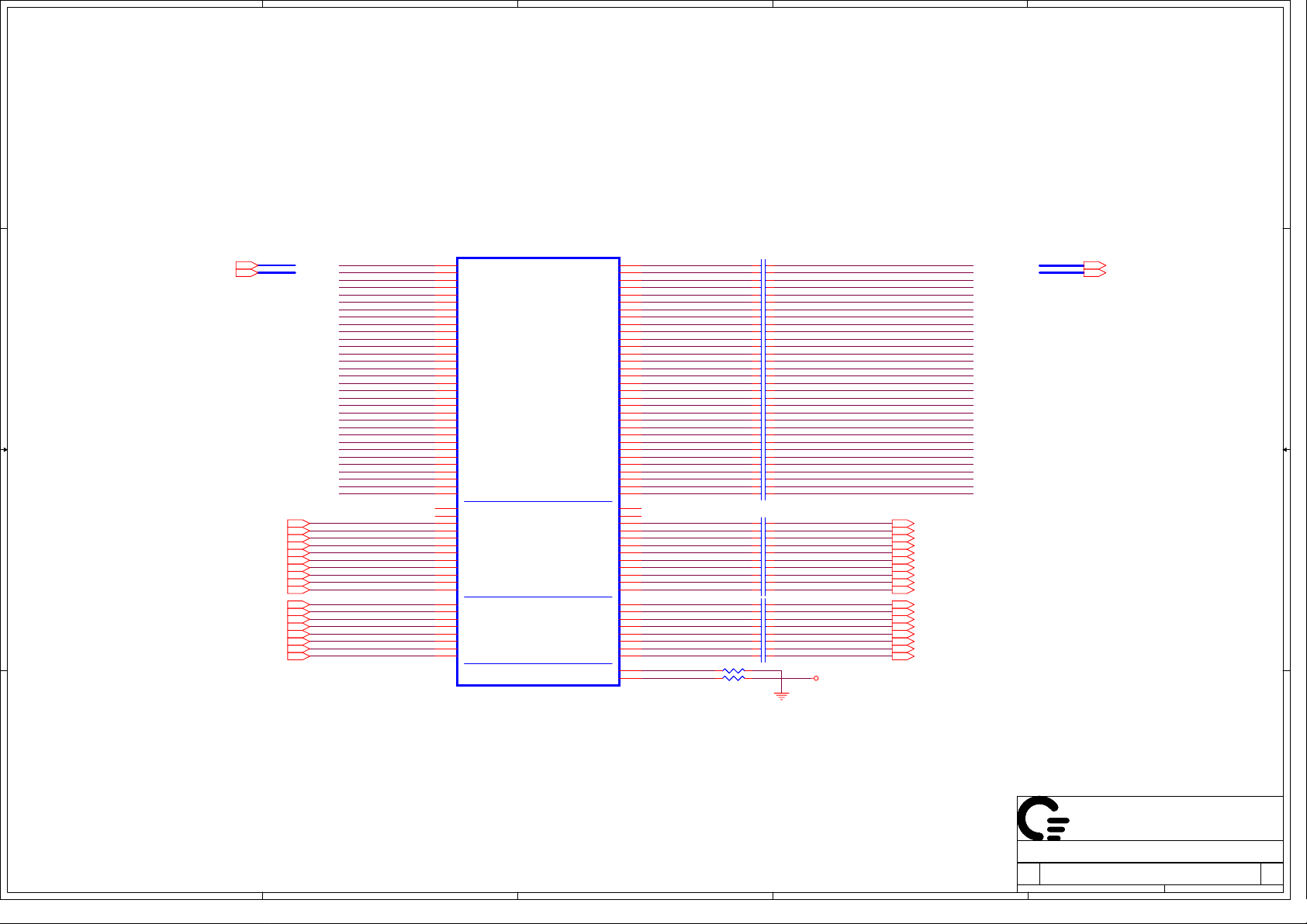

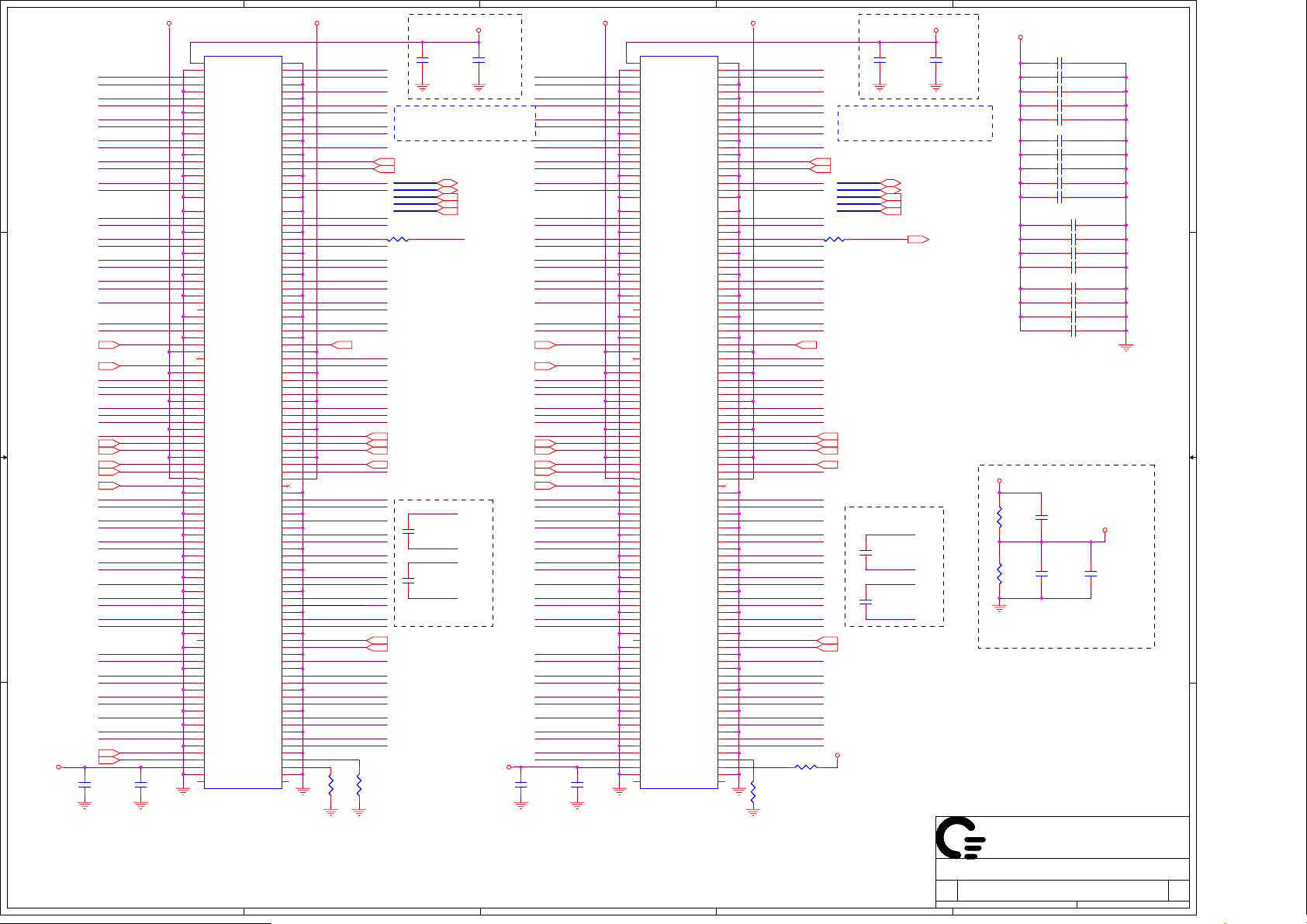

Page 4

A

B

C

D

E

Notes for the SODIMM locations:

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

CPU_VTT_SUS_SENSE

should be routed as 10mils

4 4

KEEP TRACE TO RESISTORS LESS

THAN 1.0" FROM CPU PIN

+1.8V_SUS

3 3

2 2

1 1

and 10mils spacing from any

adjacent signals in X, Y, Z

directions.

U30B

U30B

D10

C235

C235

0.1U

0.1U

C240

C240

0.1U

0.1U

AD10

AF10

AE10

AA16

10

10

X7R

X7R

10

10

X7R

X7R

C10

B10

H16

T19

V22

U21

V19

T20

U19

U20

V20

J22

J20

N19

N20

E16

F16

Y16

P19

P20

N21

M20

N22

M19

M22

L20

M24

L21

L19

K22

R21

L22

K20

V24

K24

K19

R20

R23

J21

R19

T22

T24

VTT1

VTT2

VTT3

VTT4

MEMZP

MEMZN

RSVD_M1

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_CKE0

MA_CKE1

MA_CLK_H5

MA_CLK_L5

MA_CLK_H1

MA_CLK_L1

MA_CLK_H7

MA_CLK_L7

MA_CLK_H4

MA_CLK_L4

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_RAS_L

MA_CAS_L

MA_WE_L

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

FOX_PZ6382A-284S-41F

FOX_PZ6382A-284S-41F

+0.9V_CPU_M_VREF_SUS

C290

C290

1000P

1000P

50

50

X7R

X7R

39.2/F

39.2/F

R518

R518

M_ZP

M_ZN

39.2/F

39.2/F

R513

R513

DDR_CS0_DIMMA#16,17

DDR_CS1_DIMMA#16,17

DDR_CKE0_DIMMA16,17

DDR_CKE1_DIMMA16,17

M_CLK_DDR016

M_CLK_DDR#016

M_CLK_DDR116

M_CLK_DDR#116

DDR_A_MA[0..15]16,17 DDR_B_MA[0..15] 16,17

DDR_A_BS016,17

DDR_A_BS116,17

DDR_A_BS216,17

DDR_A_RAS#16,17

DDR_A_CAS#16,17

DDR_A_WE#16,17

T49T49

M_ODT016,17

M_ODT116,17

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

+1.8V_SUS

R151

R151

1K/F

1K/F

0603

0603

R192

R192

1K/F

1K/F

0603

0603

PLACE CLOSE TO CPU

sensing point for

op-amp feedback

routed near CPU

A

Place Capacitors for +0.9V_CPU_M_VREF_SUS < 1" from the RS780.

+0.9V_CPU_M_VREF_SUS trace length < 6", trace width > 15mils and

20mils spacing from any adjacent signals in X, Y, Z directions.

+0.9V_DDR_VTT+0.9V_DDR_VTT

W10

VTT5

VTT6

VTT7

VTT8

VTT9

VTT_SENSE

MEMVREF

RSVD_M2

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

B

1750mA

CPU_VTT_SUS_SENSE

+0.9V_CPU_M_VREF_SUSMEM_MA_RESET#

MEM_MB_RESET#

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

C523

C523

*470P_NC

*470P_NC

50

50

X7R

X7R

T50T50

CPU_VTT_SUS_SENSE 49

M_ODT2 16,17

M_ODT3 16,17

DDR_CS0_DIMMB# 16,17

DDR_CS1_DIMMB# 16,17

DDR_CKE2_DIMMB 16,17

DDR_CKE3_DIMMB 16,17

M_CLK_DDR2 16

M_CLK_DDR#2 16

M_CLK_DDR3 16

M_CLK_DDR#3 16

DDR_B_BS0 16,17

DDR_B_BS1 16,17

DDR_B_BS2 16,17

DDR_B_RAS# 16,17

DDR_B_CAS# 16,17

DDR_B_WE# 16,17

DIMMA = CN5

DIMMB = CN6

Processor DDR2 Memory Interface

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

To SODIMM socket B (Near/TOP)

DDR_B_DM[0..7]16 DDR_A_DM[0..7] 16

DDR_B_DQS[0..7]16

DDR_B_DQS#[0..7]16

C

DDR_B_D62

DDR_B_D63

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

U30C

U30C

C11

MB_DATA0

A11

MB_DATA1

A14

MB_DATA2

B14

MB_DATA3

G11

MB_DATA4

E11

MB_DATA5

D12

MB_DATA6

A13

MB_DATA7

A15

MB_DATA8

A16

MB_DATA9

A19

MB_DATA10

A20

MB_DATA11

C14

MB_DATA12

D14

MB_DATA13

C18

MB_DATA14

D18

MB_DATA15

D20

MB_DATA16

A21

MB_DATA17

D24

MB_DATA18

C25

MB_DATA19

B20

MB_DATA20

C20

MB_DATA21

B24

MB_DATA22

C24

MB_DATA23

E23

MB_DATA24

E24

MB_DATA25

G25

MB_DATA26

G26

MB_DATA27

C26

MB_DATA28

D26

MB_DATA29

G23

MB_DATA30

G24

MB_DATA31

AA24

MB_DATA32

AA23

MB_DATA33

AD24

MB_DATA34

AE24

MB_DATA35

AA26

MB_DATA36

AA25

MB_DATA37

AD26

MB_DATA38

AE25

MB_DATA39

AC22

MB_DATA40

AD22

MB_DATA41

AE20

MB_DATA42

AF20

MB_DATA43

AF24

MB_DATA44

AF23

MB_DATA45

AC20

MB_DATA46

AD20

MB_DATA47

AD18

MB_DATA48

AE18

MB_DATA49

AC14

MB_DATA50

AD14

MB_DATA51

AF19

MB_DATA52

AC18

MB_DATA53

AF16

MB_DATA54

AF15

MB_DATA55

AF13

MB_DATA56

AC12

MB_DATA57

AB11

MB_DATA58

Y11

MB_DATA59

AE14

MB_DATA60

AF14

MB_DATA61

AF11

MB_DATA62

AD11

MB_DATA63

A12

MB_DM0

B16

MB_DM1

A22

MB_DM2

E25

MB_DM3

AB26

MB_DM4

AE22

MB_DM5

AC16

MB_DM6

AD12

MB_DM7

C12

MB_DQS_H0

B12

MB_DQS_L0

D16

MB_DQS_H1

C16

MB_DQS_L1

A24

MB_DQS_H2

A23

MB_DQS_L2

F26

MB_DQS_H3

E26

MB_DQS_L3

AC25

MB_DQS_H4

AC26

MB_DQS_L4

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF12

MB_DQS_H7

AE12

MB_DQS_L7

FOX_PZ6382A-284S-41F

FOX_PZ6382A-284S-41F

MEM:DATA

MEM:DATA

Athlon 64 S1

Processor Socket

D

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_DQS[0..7]16

DDR_A_DQS#[0..7]16

Title

Title

Title

S1G2 DDRII MEMORY

S1G2 DDRII MEMORY

S1G2 DDRII MEMORY

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FX6 3A

FX6 3A

FX6 3A

Date: Sheet

Date: Sheet

Date: Sheet

DDR_A_D[0..63] 16DDR_B_D[0..63]16

To SODIMM socket A (Far/Bottom)

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

E

of

of

of

470Tuesday, May 20, 2008

470Tuesday, May 20, 2008

470Tuesday, May 20, 2008

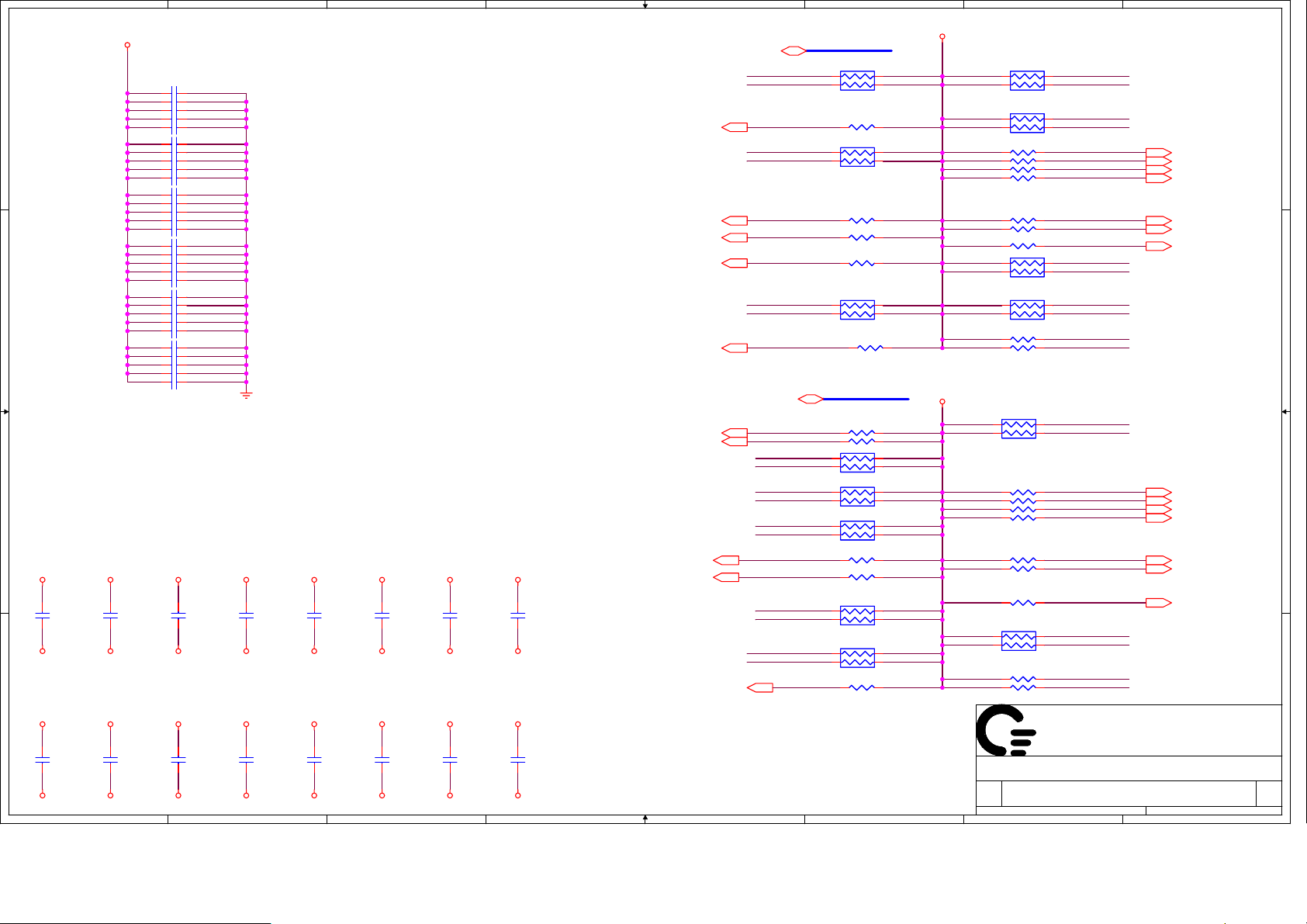

Page 5

5

+3.3V_RUN

R117

R107 0R107 0

+5V_ALW2

3

2

1

LDT_RST#

+1.8V_SUS

R484

R484

R492

R492

390

390

390

390

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

R117

*20K_NC

*20K_NC

R135

R135

10K

10K

Q29

Q29

FDV301N

FDV301N

R4941KR494

1K

CPU_SIC

CPU_SID

CPU_ALERT

2

1

Q25

Q25

*FDV301N_NC

*FDV301N_NC

R101 0R101 0

CPU_PWRGD_SVID_REG

3

Q31

Q31

FDV301N

FDV301N

2

1

R116

R116

*34.8K_NC

*34.8K_NC

3

R131 *0_NCR131 *0_NC

+1.8V_RUN

R103

R103

300

300

CPU_LDT_REQ#_R

D D

+1.8V_RUN

R132

R132

300

300

+1.8V_RUN

+1.8V_RUN

SCLK3

SDATA3

C947

C947

*0.1U_NC

*0.1U_NC

16

16

X7R

X7R

R149

R149

300

300

R143

R143

300

300

R481 *0_NCR481 *0_NC

R487 *0_NCR487 *0_NC

50

50

X7R

X7R

50

50

X7R

X7R

CPU_PWRGD

D4

D4

*RB500V-40_NC

*RB500V-40_NC

LDT_STOP#

D9

RB500V-40D9RB500V-40

D6

RB500V-40D6RB500V-40

R502

R502

169/F

169/F

CPU_PWRGD12

LDT_STOP#9,12

C C

LDT_RST#9,12

SB_PWRGD13,45

B B

CPU_CLK25

CPU_CLK#25

1.KEEP TRACE TO RESISTOR LESS THAN 600MILS FROM CPU

PIN AND TRACE TO AC CAPS LESS THAN 1.2".

2.CPUCLK and CPUCLK# mismatch < 35 mils.

SCLK313

SDATA313

+1.8V_SUS

(20)

R142 0R142 0

C681 3900P

C681 3900P

C679 3900P

C679 3900P

4

C176

C176

*0.1U_NC

*0.1U_NC

10

10

X7R

X7R

CPU_LDT_REQ# 9

CPU_PWRGD_SVID_REG 53

CPU_PWRGD_SVID_REGCPU_PWRGD

L23 is filtered with a 30-300 nH

ferrite bead. and a current rating

of at least 3000mA.

L24

L24

BLM18PG330SN1B

BLM18PG330SN1B

0603

0603

C116

C116

100U

100U

6.3

6.3

Polymer

Polymer

3528

3528

+2.5V_CPU_VDDA_RUN

+2.5V_RUN

+

+

Place R151 and R152 < 1.5".

Route CPU_HTREF1/0 with 5mils trace

width and 10mils spacing from other

signals in X, Y, Z directions

CPU_VDD0_RUN_FB_H53

CPU_VDD0_RUN_FB_L53

CPU_VDD1_RUN_FB_H53

CPU_VDD1_RUN_FB_L53

3

CPU_THERMTRIP#

+2.5V_CPU_VDDA_RUN

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

This trace should be kept at least 20 mils away from all other signals.

C120

C120

4.7U

4.7U

10

10

X7R

X7R

0805

0805

+2.5V_CPU_VDDA_RUN

C125

C125

0.22U

0.22U

10

10

X7R

X7R

0603

0603

+1.2V_RUN

T48T48

T47T47

T27T27

T26T26

C124

C124

3300P

3300P

50

50

X7R

X7R

R92 44.2/FR92 44.2/F

R94 44.2/FR94 44.2/F

CPU_VDD0_RUN_FB_H

CPU_VDD0_RUN_FB_L

CPU_VDD1_RUN_FB_H

CPU_VDD1_RUN_FB_L

T100T100

T97T97

T101T101

T102T102

CPU_TEST23_TSTUPD

CPU_TEST18_PLLTEST1

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST27_SINGLECHAIN

CPU_TEST9_ANALOGIN

R4710R471

0

T46T46

T44T44

T38T38

T36T36

T33T33

T35T35

T40T40

T95T95

+3.3V_RUN

R7761MR776

1M

3

Q106

Q106

FDV301N

FDV301N

2

1

40mA

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

LDT_RST#

CPU_PWRGD

LDT_STOP#

CPU_LDT_REQ#_R

CPU_SIC

CPU_SID

CPU_ALERT

CPU_HTREF0

CPU_HTREF1

CPU_VDD0_RUN_FB_H

CPU_VDD0_RUN_FB_L

CPU_VDD1_RUN_FB_H

CPU_VDD1_RUN_FB_L

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

31

Q105

Q105

2

2N7002W-7-F

2N7002W-7-F

C964

C964

0.1U

0.1U

10

10

X7R

X7R

SVC SVD

0 1.1V

0 1.0V

1 0.9V

1

F8

F9

A9

A8

B7

A7

F10

C6

AF4

AF5

AE6

R6

P6

F6

E6

Y6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

G9

E9

E8

AB8

AF7

AE7

AE8

AC8

AF8

C2

AA6

A3

A5

B3

B5

C1

2

H_THERMTRIP# 52

2-Bit Boot VID Codes

Voltage Output

(CPU Power)

0

1

0

1

0.8V

U30D

U30D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

SIC

SID

ALERT_L

HT_REF0

HT_REF1

VDD0_FB_H

VDD0_FB_L

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

TEST19

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TEST6

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

KEY1

KEY2

SVC

SVD

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

FOX_PZ6382A-284S-41F

FOX_PZ6382A-284S-41F

CPU_MEMHOT#_L

CPU_THERMTRIP#_1.8V CPU_THERMTRIP#

CPU_PROCHOT#

+1.8V_SUS

M11

W18

CPU_SVC_R

A6

CPU_SVD_R

A4

AF6

AC7

AA8

W7

W8

W9

Y9

H6

G6

E10

AE9

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

R122 0R122 0

R97 0R97 0

CPU_THERMTRIP#_1.8V

CPU_PROCHOT#

CPU_MEMHOT#_L

H_THERMDC

H_THERMDA

Place C212< 100mils from CPU.

CPU_DBREQ#

CPU_TDO

CPU_TEST28_H_PLLCHRZ_P

CPU_TEST28_L_PLLCHRZ_N

CPU_TEST17_BP3CPU_TEST19_PLLTEST0

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

R799 0R799 0

(16)

R503

R503

R93

R93

300

300

300

300

C185

C185

*220P/50V_NC

*220P/50V_NC

CPU_TEST23_TSTUPD

CPU_TEST21_SCANEN

CPU_TEST24_SCANCLK1

+1.8V_SUS

R87

R87

10K

10K

Q22

Q22

2

MMBT3904

MMBT3904

+1.8V_SUS

R493

R493

10K

10K

Q81

Q81

2

MMBT3904

MMBT3904

1 3

2N7002W-7-F

2N7002W-7-F

R86

R86

300

300

T19T19

T29T29

T24T24

T23T23

T30T30

T25T25

T34T34

T28T28

13

Q110

Q110

+3.3V_RUN

R1211KR121

1K

R90

R90

*680_NC

*680_NC

31

R991KR99

1K

1

CPU_MEMHOT# 16

CPU_THERMTRIP# 13

2

BID1 42

CPU_SVC 53

CPU_SVD 53

CPU_PROCHOT# 12

H_THERMDC 29

H_THERMDA 29

CPU_VDDIO_SUS_FB_H 49

CPU_VDDIO_SUS_FB_L 49

CPU_VDDNB_RUN_FB_H 53

CPU_VDDNB_RUN_FB_L 53

(18)

R791 *300_NCR791 *300_NC

R777 300R777 300

R778 300R778 300

HDT CONNECTOR

CN1

CN1

R177 *220_NCR177 *220_NC

R171 *220_NCR171 *220_NC

R179 *220_NCR179 *220_NC

R175 *220_NCR175 *220_NC

R164 300R164 300

CPU_DBREQ#

CPU_DBRDY

A A

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

+1.8V_SUS

GND1GND

Resreved13GND

Resreved25GND

DBREQ_L7GND

DBRDY9GND

11

TCK

13

TMS

15

TDI

TRST_L17GND

19

TDO

VDDIO121GND

VDDIO223RESET_L

GND

GND

GND

GND

GND

*HDT conn_NC

*HDT conn_NC

2

4

6

8

10

12

*4.7K_NC

*4.7K_NC

14

16

18

20

22

24

25

*100K_NC

*100K_NC

NOTE:HDT TERMINATION IS REQUIRED FOR REV.Ax SILICON ONLY.

5

R145

R145

R146

R146

+1.8V_RUN+3.3V_RUN

2

R147 0R147 0

R148

R148

*4.7K_NC

*4.7K_NC

Q34

Q34

*MMBT3904_NC

*MMBT3904_NC

13

LDT_RST#CPU_RESET#

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

S1G2 CTRL & DEBUG

S1G2 CTRL & DEBUG

S1G2 CTRL & DEBUG

FX6 3A

FX6 3A

FX6 3A

1

570Tuesday, May 20, 2008

570Tuesday, May 20, 2008

570Tuesday, May 20, 2008

of

of

of

Page 6

5

4

3

2

1

PROCESSOR POWER AND GROUND

U30F

U30E

+CPU_VDD0_RUN +CPU_VDD1_RUN

D D

+CPU_VDDNB_RUN

C C

B B

+1.8V_SUS

U30E

G4

VDD0_1

H2

VDD0_2

J9

VDD0_3

J11

VDD0_4

J13

VDD0_5

J15

VDD0_6

K6

VDD0_7

K10

VDD0_8

K12

VDD0_9

K14

VDD0_10

L4

VDD0_11

L7

VDD0_12

L9

VDD0_13

L11

VDD0_14

L13

VDD0_15

L15

VDD0_16

M2

VDD0_17

M6

VDD0_18

M8

VDD0_19

M10

VDD0_20

N7

VDD0_21

N9

VDD0_22

N11

VDD0_23

K16

VDDNB_1

M16

VDDNB_2

P16

VDDNB_3

T16

VDDNB_4

V16

VDDNB_5

H25

VDDIO1

J17

VDDIO2

K18

VDDIO3

K21

VDDIO4

K23

VDDIO5

K25

VDDIO6

L17

VDDIO7

M18

VDDIO8

M21

VDDIO9

M23

VDDIO10

M25

VDDIO11

N17

VDDIO12

FOX_PZ6382A-284S-41F

FOX_PZ6382A-284S-41F

A1

P8

VDD1_1

P10

VDD1_2

R4

VDD1_3

R7

VDD1_4

R9

VDD1_5

R11

VDD1_6

T2

VDD1_7

T6

VDD1_8

T8

VDD1_9

T10

VDD1_10

T12

VDD1_11

T14

VDD1_12

U7

VDD1_13

U9

VDD1_14

U11

VDD1_15

U13

VDD1_16

U15

VDD1_17

V6

VDD1_18

V8

VDD1_19

V10

VDD1_20

V12

VDD1_21

V14

VDD1_22

W4

VDD1_23

Y2

VDD1_24

AC4

VDD1_25

AD2

VDD1_26

Y25

VDDIO27

V25

VDDIO26

V23

VDDIO25

V21

VDDIO24

V18

VDDIO23

U17

VDDIO22

T25

VDDIO21

T23

VDDIO20

T21

VDDIO19

T18

VDDIO18

R17

VDDIO17

P25

VDDIO16

P23

VDDIO15

P21

VDDIO14

P18

VDDIO13

Athlon 64 S1

Processor Socket

+1.8V_SUS

A26

S1g2

uPGA638

A A

Top View

AF1

5

4

U30F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

FOX_PZ6382A-284S-41F

FOX_PZ6382A-284S-41F

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

Athlon 64 S1

Processor Socket

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

BOTTOMSIDE DECOUPLING

+CPU_VDD0_RUN

C202

C191

C191

22U

22U

4

4

X6S

X6S

0805

0805

+CPU_VDD1_RUN

C190

C190

22U

22U

4

4

X6S

X6S

0805

0805

+1.8V_SUS

C309

C309

22U

22U

4

4

X6S

X6S

0805

0805

C202

22U

22U

4

4

X6S

X6S

0805

0805

C207

C207

22U

22U

4

4

X6S

X6S

0805

0805

C233

C233

22U

22U

4

4

X6S

X6S

0805

0805

C213

C213

22U

22U

4

4

X6S

X6S

0805

0805

C214

C214

22U

22U

4

4

X6S

X6S

0805

0805

C225

C225

0.22U

0.22U

10

10

X7R

X7R

0603

0603

C218

C218

22U

22U

4

4

X6S

X6S

0805

0805

C220

C220

22U

22U

4

4

X6S

X6S

0805

0805

C236

C236

0.22U

0.22U

10

10

X7R

X7R

0603

0603

C219

C219

0.22U

0.22U

10

10

X7R

X7R

0603

0603

C184

C184

0.22U

0.22U

10

10

X7R

X7R

0603

0603

C238

C238

180P

180P

50

50

NPO

NPO

C212

C212

0.01U

0.01U

16

16

X7R

X7R

C195

C195

0.01U

0.01U

16

16

X7R

X7R

C234

C234

180P

180P

50

50

NPO

NPO

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.8V_SUS

C293

C293

4.7U

4.7U

10

10

X7R

X7R

0805

0805

+1.8V_SUS

C227

C227

0.01U

0.01U

16

16

X7R

X7R

+0.9V_DDR_VTT

C179

C179

4.7U

4.7U

10

10

X7R

X7R

0805

0805

+0.9V_DDR_VTT

C701

C701

1000P

1000P

50

50

X7R

X7R

3

C778

C778

4.7U

4.7U

10

10

X7R

X7R

0805

0805

C323

C323

0.01U

0.01U

16

16

X7R

X7R

C694

C694

4.7U

4.7U

10

10

X7R

X7R

0805

0805

C704

C704

1000P

1000P

50

50

X7R

X7R

C292

C292

4.7U

4.7U

10

10

X7R

X7R

0805

0805

C306

C306

180P

180P

50

50

NPO

NPO

C683

C683

4.7U

4.7U

10

10

X7R

X7R

0805

0805

C196

C196

1000P

1000P

50

50

X7R

X7R

C777

C777

4.7U

4.7U

10

10

X7R

X7R

0805

0805

C322,and C237 to be evenly spaced along

the VDDIO/VSS plane split

C322

C322

180P

180P

50

50

NPO

NPO

C161

C161

4.7U

4.7U

10

10

X7R

X7R

0805

0805

C187

C187

1000P

1000P

50

50

X7R

X7R

C284

C284

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C237

C237

180P

180P

50

50

NPO

NPO

C685

C685

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C204

C204

180P

180P

50

50

NPO

NPO

2

C768

C768

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C684

C684

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C245

C245

180P

180P

50

50

NPO

NPO

C194

C194

180P

180P

50

50

NPO

NPO

C203

C203

180P

180P

50

50

NPO

NPO

+CPU_VDDNB_RUN

C223

C217

C217

22U

22U

4

4

X6S

X6S

0805

0805

C285

C285

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C691

C691

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C686

C686

180P

180P

50

50

NPO

NPO

Title

Title

Title

S1G2 PWR & GND

S1G2 PWR & GND

S1G2 PWR & GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FX6 3A

FX6 3A

FX6 3A

Date: Sheet

Date: Sheet

Date: Sheet

C223

22U

22U

4

4

X6S

X6S

0805

0805

C767

C767

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C692

C692

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C689

C689

180P

180P

50

50

NPO

NPO

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

C224

C224

22U

22U

4

4

X6S

X6S

0805

0805

1

of

of

of

670Tuesday, May 20, 2008

670Tuesday, May 20, 2008

670Tuesday, May 20, 2008

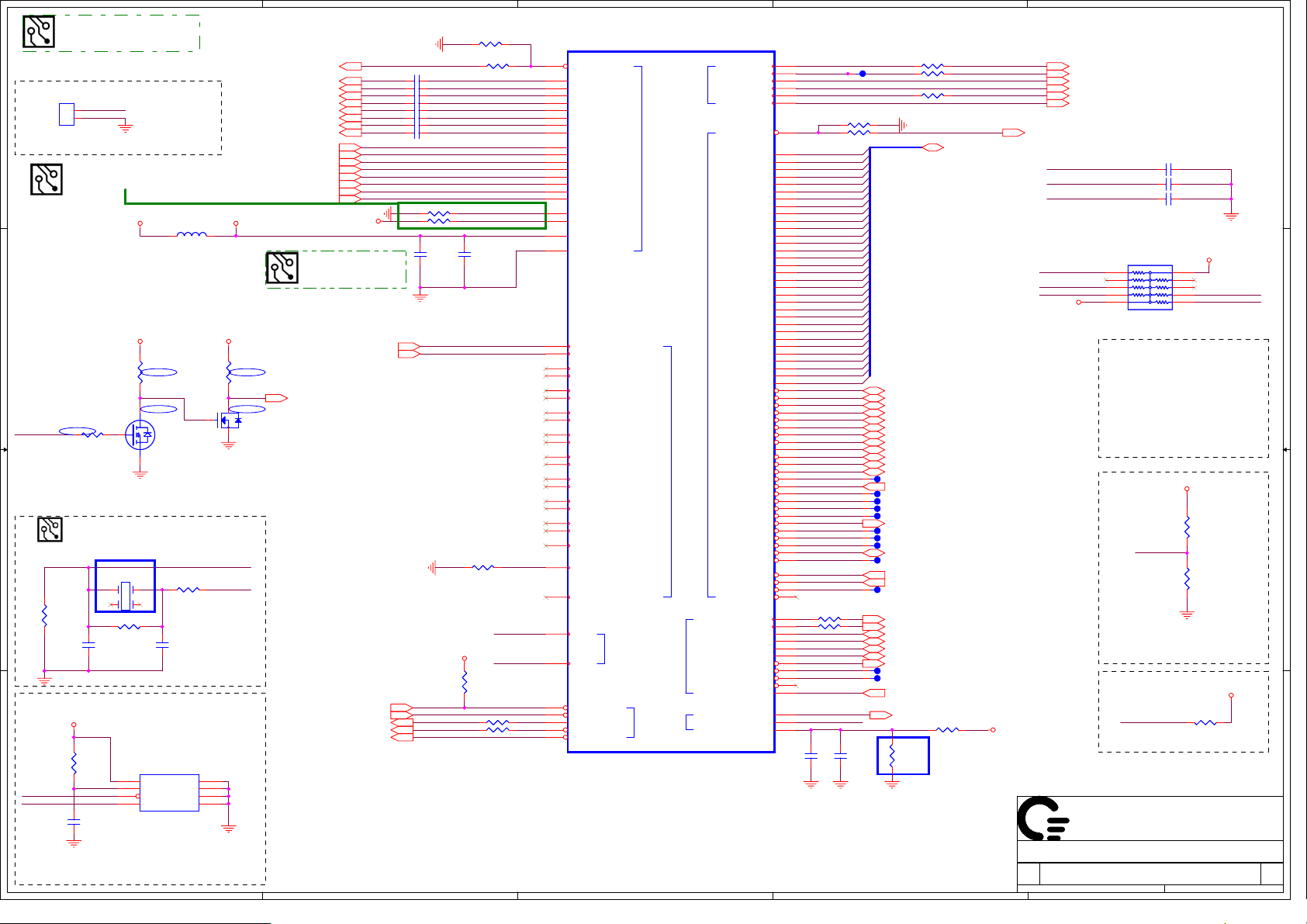

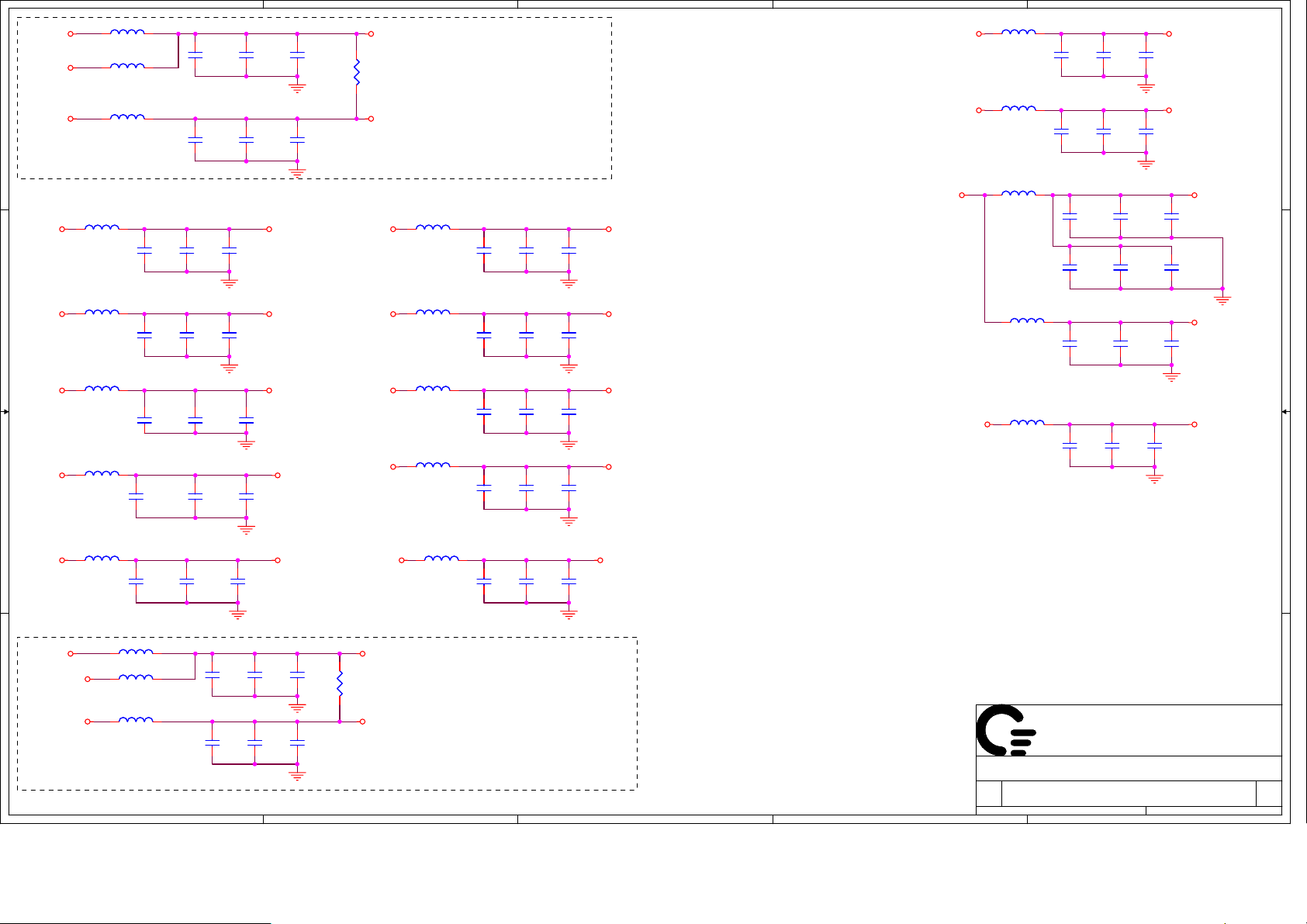

Page 7

5

D D

HT_CADOUT03

HT_CADOUT#03

HT_CADOUT13

HT_CADOUT#13

HT_CADOUT23

HT_CADOUT#23

HT_CADOUT33

HT_CADOUT#33

HT_CADOUT43

HT_CADOUT#43

HT_CADOUT53

HT_CADOUT#53

HT_CADOUT63

HT_CADOUT#63

HT_CADOUT73

C C

B B

HT_CADOUT#73

HT_CADOUT83

HT_CADOUT#83

HT_CADOUT93

HT_CADOUT#93

HT_CADOUT103

HT_CADOUT#103

HT_CADOUT113

HT_CADOUT#113

HT_CADOUT123

HT_CADOUT#123

HT_CADOUT133

HT_CADOUT#133

HT_CADOUT143

HT_CADOUT#143

HT_CADOUT153

HT_CADOUT#153

HT_CLKOUT03

HT_CLKOUT#03

HT_CLKOUT13

HT_CLKOUT#13

HT_CTLOUT03

HT_CTLOUT#03

HT_CTLOUT13

HT_CTLOUT#13

4

R438 300/FR438 300/F

Y25

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

AC24

AC25

AB25

AB24

AA24

AA25

Y22

Y23

W21

W20

V21

V20

U20

U21

U19

U18

T22

T23

AB23

AA22

M22

M23

R21

R20

C23

A24

U22A

U22A

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS780M A13

RS780M A13

3

PART 1 OF 6

PART 1 OF 6

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

F21

G21

G20

H21

J20

J21

J18

K17

L19

J19

M19

L18

M21

P21

P18

M18

H24

H25

L21

L20

M24

M25

P19

R18

B24

B25

R440 300/FR440 300/F

Rev.A13

HT_CADIN0 3

HT_CADIN#0 3

HT_CADIN1 3

HT_CADIN#1 3

HT_CADIN2 3

HT_CADIN#2 3

HT_CADIN3 3

HT_CADIN#3 3

HT_CADIN4 3

HT_CADIN#4 3

HT_CADIN5 3

HT_CADIN#5 3

HT_CADIN6 3

HT_CADIN#6 3

HT_CADIN7 3

HT_CADIN#7 3

HT_CADIN8 3

HT_CADIN#8 3

HT_CADIN9 3

HT_CADIN#9 3

HT_CADIN10 3

HT_CADIN#10 3

HT_CADIN11 3

HT_CADIN#11 3

HT_CADIN12 3

HT_CADIN#12 3

HT_CADIN13 3

HT_CADIN#13 3

HT_CADIN14 3

HT_CADIN#14 3

HT_CADIN15 3

HT_CADIN#15 3

HT_CLKIN0 3

HT_CLKIN#0 3

HT_CLKIN1 3

HT_CLKIN#1 3

HT_CTLIN0 3

HT_CTLIN#0 3

HT_CTLIN1 3

HT_CTLIN#1 3

2

1

R438,R440

RS780

301

RX780 1.21K

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

RS780-HT LINK I/F

RS780-HT LINK I/F

RS780-HT LINK I/F

FX6 3A

FX6 3A

FX6 3A

of

of

of

770Tuesday, May 20, 2008

770Tuesday, May 20, 2008

770Tuesday, May 20, 2008

1

Page 8

5

D D

4

3

2

1

U22B

AE3

AD4

AE2

AD3

AD1

AD2

AA8

AA7

AA5

AA6

D4

C4

A3

B3

C2

C1

E5

F5

G5

G6

H5

H6

J6

J5

J7

J8

L5

L6

M8

L8

P7

M7

P5

M5

R8

P8

R6

R5

P4

P3

T4

T3

V5

W6

U5

U6

U8

U7

Y8

Y7

W5

Y5

U22B

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

GPP_RX4P

GPP_RX4N

GPP_RX5P

GPP_RX5N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

RS780M A13

RS780M A13

PART 2 OF 6

PART 2 OF 6

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

PCIE I/F GFX

PCIE I/F GFX

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

PCE_CALRP(PCE_BCALRP)

PCE_CALRN(PCE_BCALRN)

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

PCIE_MTX_GRX_P0

A5

PCIE_MTX_GRX_N0

B5

PCIE_MTX_GRX_P1

A4

PCIE_MTX_GRX_N1

B4

PCIE_MTX_GRX_P2

C3

PCIE_MTX_GRX_N2

B2

PCIE_MTX_GRX_P3

D1

PCIE_MTX_GRX_N3

D2

PCIE_MTX_GRX_P4

E2

PCIE_MTX_GRX_N4

E1

PCIE_MTX_GRX_P5

F4

PCIE_MTX_GRX_N5

F3

PCIE_MTX_GRX_P6

F1

PCIE_MTX_GRX_N6

F2

PCIE_MTX_GRX_P7

H4

PCIE_MTX_GRX_N7

H3

PCIE_MTX_GRX_P8

H1

PCIE_MTX_GRX_N8

H2

PCIE_MTX_GRX_P9

J2

PCIE_MTX_GRX_N9

J1

PCIE_MTX_GRX_P10

K4

PCIE_MTX_GRX_N10

K3

PCIE_MTX_GRX_P11

K1

PCIE_MTX_GRX_N11

K2

PCIE_MTX_GRX_P12

M4

PCIE_MTX_GRX_N12

M3

PCIE_MTX_GRX_P13

M1

PCIE_MTX_GRX_N13

M2

PCIE_MTX_GRX_P14

N2

PCIE_MTX_GRX_N14

N1

PCIE_MTX_GRX_P15

P1

PCIE_MTX_GRX_N15

P2

AC1

AC2

PCIE_TXP1_C

AB4

PCIE_TXN1_C

AB3

PCIE_TXP2_C

AA2

PCIE_TXN2_C

AA1

GLAN_TXP_C

Y1

GLAN_TXN_C

Y2

PCIE_TXP4_C

Y4

PCIE_TXN4_C

Y3

PCIE_TXP5_C

V1

PCIE_TXN5_C

V2

ALINK_NBTX_SBRX_P0

AD7

ALINK_NBTX_SBRX_N0

AE7

ALINK_NBTX_SBRX_P1

AE6

ALINK_NBTX_SBRX_N1

AD6

ALINK_NBTX_SBRX_P2

AB6

ALINK_NBTX_SBRX_N2

AC6

ALINK_NBTX_SBRX_P3

AD5

ALINK_NBTX_SBRX_N3

AE5

PCE_PCAL

AC8

PCE_NCAL

AB8

PCIE_MRX_GTX_P[0..15]18 PCIE_MTX_C_GRX_P[0..15] 18

PCIE_MRX_GTX_N[0..15]18

C C

WLAN <---- WPAN <----- ----->WPAN

B B

GIGA LAN <-----

WWAN <----- ----->WWAN

PCIE_RX1+39

PCIE_RX1-39

PCIE_RX2+39

PCIE_RX2-39

PCIE_RX3-/GLAN_RX-33

PCIE_RX4+37

PCIE_RX4-37

PCIE_RX5+40

PCIE_RX5-40

ALINK_NBRX_SBTX_P012

ALINK_NBRX_SBTX_N012

ALINK_NBRX_SBTX_P112

ALINK_NBRX_SBTX_N112

ALINK_NBRX_SBTX_P212

ALINK_NBRX_SBTX_N212

ALINK_NBRX_SBTX_P312

ALINK_NBRX_SBTX_N312

PCIE_MRX_GTX_P0

PCIE_MRX_GTX_N0

PCIE_MRX_GTX_P1

PCIE_MRX_GTX_N1

PCIE_MRX_GTX_P2

PCIE_MRX_GTX_N2

PCIE_MRX_GTX_P3

PCIE_MRX_GTX_N3

PCIE_MRX_GTX_P4

PCIE_MRX_GTX_N4

PCIE_MRX_GTX_P5

PCIE_MRX_GTX_N5

PCIE_MRX_GTX_P6

PCIE_MRX_GTX_N6

PCIE_MRX_GTX_P7

PCIE_MRX_GTX_N7

PCIE_MRX_GTX_P8

PCIE_MRX_GTX_N8

PCIE_MRX_GTX_P9

PCIE_MRX_GTX_N9

PCIE_MRX_GTX_P10

PCIE_MRX_GTX_N10

PCIE_MRX_GTX_P11

PCIE_MRX_GTX_N11

PCIE_MRX_GTX_P12

PCIE_MRX_GTX_N12

PCIE_MRX_GTX_P13

PCIE_MRX_GTX_N13

PCIE_MRX_GTX_P14

PCIE_MRX_GTX_N14

PCIE_MRX_GTX_P15

PCIE_MRX_GTX_N15

Place near RS780

C581 0.1U/10VC581 0.1U/10V

C583 0.1U/10VC583 0.1U/10V

C575 0.1U/10VC575 0.1U/10V

C578 0.1U/10VC578 0.1U/10V

C572 0.1U/10VC572 0.1U/10V

C573 0.1U/10VC573 0.1U/10V

C535 0.1U/10VC535 0.1U/10V

C534 0.1U/10VC534 0.1U/10V

C550 0.1U/10VC550 0.1U/10V

C556 0.1U/10VC556 0.1U/10V

C555 0.1U/10VC555 0.1U/10V

C557 0.1U/10VC557 0.1U/10V

C544 0.1U/10VC544 0.1U/10V

C543 0.1U/10VC543 0.1U/10V

C536 0.1U/10VC536 0.1U/10V

C545 0.1U/10VC545 0.1U/10V

C551 0.1U/10VC551 0.1U/10V

C552 0.1U/10VC552 0.1U/10V

C538 0.1U/10VC538 0.1U/10V

C537 0.1U/10VC537 0.1U/10V

C547 0.1U/10VC547 0.1U/10V

C539 0.1U/10VC539 0.1U/10V

C554 0.1U/10VC554 0.1U/10V

C553 0.1U/10VC553 0.1U/10V

C559 0.1U/10VC559 0.1U/10V

C560 0.1U/10VC560 0.1U/10V

C540 0.1U/10VC540 0.1U/10V

C541 0.1U/10VC541 0.1U/10V

C563 0.1U/10VC563 0.1U/10V

C561 0.1U/10VC561 0.1U/10V

C546 0.1U/10VC546 0.1U/10V

C542 0.1U/10VC542 0.1U/10V

C19 .1U/10VC19 .1U/10V

C13 .1U/10VC13 .1U/10V

C571 .1U/10VC571 .1U/10V

C570 .1U/10VC570 .1U/10V

C567 .1U/10VC567 .1U/10V

C566 .1U/10VC566 .1U/10V

C569 .1U/10VC569 .1U/10V

C568 .1U/10VC568 .1U/10V

C564 .1U/10VC564 .1U/10V

C565 .1U/10VC565 .1U/10V

C584 .1U/10VC584 .1U/10V

C585 .1U/10VC585 .1U/10V

C582 .1U/10VC582 .1U/10V

C579 .1U/10VC579 .1U/10V

C15 .1U/10VC15 .1U/10V

C16 .1U/10VC16 .1U/10V

C574 .1U/10VC574 .1U/10V

C576 .1U/10VC576 .1U/10V

R40 1.27K/FR40 1.27K/F

R36 2K/FR36 2K/F

+NB_VDD_MUX

PCIE_MTX_C_GRX_P0

PCIE_MTX_C_GRX_N0

PCIE_MTX_C_GRX_P1

PCIE_MTX_C_GRX_N1

PCIE_MTX_C_GRX_P2

PCIE_MTX_C_GRX_N2

PCIE_MTX_C_GRX_P3

PCIE_MTX_C_GRX_N3

PCIE_MTX_C_GRX_P4

PCIE_MTX_C_GRX_N4

PCIE_MTX_C_GRX_P5

PCIE_MTX_C_GRX_N5

PCIE_MTX_C_GRX_P6

PCIE_MTX_C_GRX_N6

PCIE_MTX_C_GRX_P7

PCIE_MTX_C_GRX_N7

PCIE_MTX_C_GRX_P8

PCIE_MTX_C_GRX_N8

PCIE_MTX_C_GRX_P9

PCIE_MTX_C_GRX_N9

PCIE_MTX_C_GRX_P10

PCIE_MTX_C_GRX_N10

PCIE_MTX_C_GRX_P11

PCIE_MTX_C_GRX_N11

PCIE_MTX_C_GRX_P12

PCIE_MTX_C_GRX_N12

PCIE_MTX_C_GRX_P13

PCIE_MTX_C_GRX_N13

PCIE_MTX_C_GRX_P14

PCIE_MTX_C_GRX_N14

PCIE_MTX_C_GRX_P15

PCIE_MTX_C_GRX_N15

PCIE_TX1+ 39

PCIE_TX1- 39

PCIE_TX2+ 39

PCIE_TX2- 39

PCIE_TX3+/GLAN_TX+ 33PCIE_RX3+/GLAN_RX+33

PCIE_TX3-/GLAN_TX- 33

PCIE_TX4+ 37

PCIE_TX4- 37

PCIE_TX5+ 40

PCIE_TX5- 40

ALINK_NBTX_C_SBRX_P0 12

ALINK_NBTX_C_SBRX_N0 12

ALINK_NBTX_C_SBRX_P1 12

ALINK_NBTX_C_SBRX_N1 12

ALINK_NBTX_C_SBRX_P2 12

ALINK_NBTX_C_SBRX_N2 12

ALINK_NBTX_C_SBRX_P3 12

ALINK_NBTX_C_SBRX_N3 12

PCIE_MTX_C_GRX_N[0..15] 18

----->WLAN

----->GIGA LAN

----->EXPRESS CARDEXPRESS CARD <-----

A A

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

COMPUTER

RS780-PCIE I/F

RS780-PCIE I/F

RS780-PCIE I/F

FX6 3A

FX6 3A

FX6 3A

1

870Tuesday, May 20, 2008

870Tuesday, May 20, 2008

870Tuesday, May 20, 2008

of

of

of

Page 9

C21

C21

*10U/10V/0805_NC

*10U/10V/0805_NC

+1.8V_HTPLL

C86

C86

*10U/10V/0805_NC

*10U/10V/0805_NC

R39 0R39 0

PLTRST#12,14,18,37,39,45

LDT_RST#5,12

5

R38 *4.7K_NCR38 *4.7K_NC

R37 *4.7K_NCR37 *4.7K_NC

+1.8V_RUN

L3

L3

BLM15AG221SN1D

BLM15AG221SN1D

+1.8V_RUN

L13

L13

BLM15AG221SN1D

BLM15AG221SN1D

D D

220 ohm @ 100MHz

LDT_STOP#5,12

CPU_LDT_REQ#5

C C

ALLOW_LDTSTOP12

+3.3V_RUN

+1.8V_RUN

1

R757 0R757 0

1

R758 0R758 0

+NB_VDD_MUX

BLM15AG221SN1D

BLM15AG221SN1D

C20

C20

2.2U

2.2U

220 ohm @ 100MHz220 ohm @ 100MHz

10

10

X5R

X5R

0603

0603

BLM15AG221SN1D

BLM15AG221SN1D

C84

C84

2.2U

2.2U

220 ohm @ 100MHz

10

10

X5R

X5R

0603

0603

Q68

Q68

*BSS138_NL_NC

*BSS138_NL_NC

2

3

Q15

Q15

*BSS138_NL_NC

*BSS138_NL_NC

2

3

DDC_CLK0/AUX0P

PE_GPIO2

R32 0R32 0

R31 *0_NCR31 *0_NC

L63

L63

L8

L8

+VDDG_NB

R414

R414

*4.7K_NC

*4.7K_NC

NB_LDT_STOP#

+VDDG_NB+1.8V_RUN

R42

R42

*4.7K_NC

*4.7K_NC

NB_ALLOW_LDTSTOP

SYSRESET#

+PLLVDD

C591

C591

*10U/10V/0805_NC

*10U/10V/0805_NC

+PLLVDD18+1.8V_RUN

C69

C69

*10U/10V/0805_NC

*10U/10V/0805_NC

STRAP_DEBUG_BUS_GPIO_ENABLEb

Enables the Test Debug Bus using GPIO.

RX780:NB_TV_C; RS740:RS740_DFT_GPIO5; RS780:VSYNC#

RS740/RS780 RX780

1 Disable Enable

0 Enable Disable

B B

+3.3V_RUN

R759 *3K_NCR759 *3K_NC

R418 *3K_NCR418 *3K_NC

R442 *3K_NCR442 *3K_NC

INT_VGAVSYNC

NB_TV_C

RS740/RS780: Enables Side port memory

RS740:RS740_DFT_GPIO0

RS780:HSYNC#

Selects if Memory SIDE PORT is available or not

1 = Memory Side port Not available

0 = Memory Side port available

Register Readback of strap: NB_CLKCFG:CLK_TOP_SPARE_D[1]

+3.3V_RUN

R419 *3K_NCR419 *3K_NC

R420 3KR420 3K

A A

DFT_GPIO1: LOAD_EEPROM_STRAPS

Selects Loading of STRAPS from EPROM

1 : Bypass the loading of EEPROM straps and use Hardware Default Values

0 : I2C Master can load strap values from EEPROM if connected, or use

default values if not connected

RS740/RX780: RS780_AUX_CAL RS780:SUS_STAT

PLTRST#12,14,18,37,39,45

5

INT_VGAHSYNC

D2

D2

SUS_STAT#_R

21

*SDMK0340L-7-F_NC

*SDMK0340L-7-F_NC

4

150mA 135mA

100mA

+3.3V_RUN

C593

C593

2.2U

2.2U

10

10

X5R

X5R

0603

0603

+1.8V_RUN

C65

C65

2.2U

2.2U

10

10

220 ohm @ 100MHz

X5R

X5R

0603

0603

R46 0R46 0

C42

C42

49.9/F

49.9/F

L5

L5

BK1608HS220-T

BK1608HS220-T

0603

0603

220 ohm @ 100MHz

L10

L10

BLM21PG221SN1D

BLM21PG221SN1D

0805

0805

+1.8V_RUN

NB_PWRGD45

HT_REFCLK25

HT_REFCLK#25

CLK_NB_14M25

CLK_NB_GFX25

CLK_NB_GFX#25

CLK_GPP_REFCLK25

CLK_GPP_REFCLK#25

CLK_NB_SBLINK25

CLK_NB_SBLINK#25

T130T130

STRP_DATA51

CLK_NB_14M

AC Term closely

clock pin for

length: 50 mils

R786 *4.7K_NCR786 *4.7K_NC

NOTE: ACCESS TO STRAP_DATA and I2C_CLK PINS IS MANDATORY.

4

+3.3V_AVDD+VDDA18PCIEPLL

C40

C40

2.2U

2.2U

10

10

X5R

X5R

0603

0603

+1.8V_AVDDQ

C80

C80

2.2U

2.2U

10

10

X5R

X5R

0603

0603

+3.3V_AVDD

+1.8V_AVDD

+1.8V_AVDDQ

+PLLVDD

+PLLVDD18

+1.8V_HTPLL

+VDDA18PCIEPLL

R416 300R416 300

R417 0R417 0

RX780->Pop

SUS_STAT#_R

U1

U1

1

NC

2

A1

3

A2

4

VSS

*AT24C04N-10SU-2.7_NC

*AT24C04N-10SU-2.7_NC

+1.8V_RUN +1.8V_AVDD

C72

C72

2.2U

2.2U

10

10

X5R

X5R

0603

0603

100mA

NB_TV_C

INT_VGAHSYNC

INT_VGAVSYNC

R444 715/FR444 715/F

+PLLVDD

+PLLVDD18

+VDDA18PCIEPLL

R33 0R33 0

NB_LDT_STOP#

NB_ALLOW_LDTSTOP

CLK_NB_14M

REFCLK_N

R28 *0_NCR28 *0_NC

R27 *0_NCR27 *0_NC

INT_LCD_DDCCLK

INT_LCD_DDCDAT

DDC_CLK0/AUX0P

PE_GPIO2

R18

R18

*10K_NC

*10K_NC

C8

C8

*0.1U_NC

*0.1U_NC

16

16

X7R

X7R

T6T6

T12T12

T4T4

T5T5

T7T7

T10T10

T90T90

T89T89

SYSRESET#

T85T85

T86T86

VCC

WP

SCL

SDA

R56

R56

0/0805

0/0805

8

7

6

5

3

+VDDG_NB

3

U22C

U22C

F12

AVDD1(NC)

E12

AVDD2(NC)

F14

AVDDDI(NC)

G15

AVSSDI(NC)

H15

AVDDQ(NC)

H14

AVSSQ(NC)

E17

C_Pr(DFT_GPIO5)

F17

Y(DFT_GPIO2)

F15

COMP_Pb(DFT_GPIO4)

G18

RED(DFT_GPIO0)

G17

REDb(NC)

E18

GREEN(DFT_GPIO1)

F18

GREENb(NC)

E19

BLUE(DFT_GPIO3)

F19

BLUEb(NC)

A11

DAC_HSYNC(PWM_GPIO4)

B11

DAC_VSYNC(PWM_GPIO6)

E8

DAC_SDA(PCE_TCALRN)

F8

DAC_SCL(PCE_RCALRN)

G14

DAC_RSET(PWM_GPIO1)

A12

PLLVDD(NC)

D14

PLLVDD18(NC)

B12

PLLVSS(NC)

H17

VDDA18HTPLL

D7

VDDA18PCIEPLL1

E7

VDDA18PCIEPLL2

D8

SYSRESETb

A10

POWERGOOD

C10

LDTSTOPb

C12

ALLOW_LDTSTOP

C25

HT_REFCLKP

C24

HT_REFCLKN

E11

REFCLK_P/OSCIN(OSCIN)

F11

REFCLK_N(PWM_GPIO3)

T2

GFX_REFCLKP

T1

GFX_REFCLKN

U1

GPP_REFCLKP

U2

GPP_REFCLKN

V4

GPPSB_REFCLKP(SB_REFCLKP)

V3

GPPSB_REFCLKN(SB_REFCLKN)

B9

I2C_CLK

A9

I2C_DATA

A8

DDC_CLK0/AUX0P(NC)

B8

DDC_DATA0/AUX0N(NC)

B7

DDC_CLK1/AUX1P(NC)

A7

DDC_DATA1/AUX1N(NC)

B10

STRP_DATA

G11

RSVD

C8

AUX_CAL(NC)

R35

R35

*150/F_NC

*150/F_NC

R14

R14

*2K_NC

*2K_NC

INT_LCD_DDCCLK

STRP_DATA

R112KR11

2K

C11

C11

R30

R30

*4.7K_NC

*4.7K_NC

*10P/50V_NC

*10P/50V_NC

PART 3 OF 6

PART 3 OF 6

TXOUT_L2N(DBG_GPIO0)

TXOUT_L3N(DBG_GPIO2)

TXOUT_U1P(PCIE_RESET_GPIO3)

TXOUT_U1N(PCIE_RESET_GPIO2)

TXOUT_U3P(PCIE_RESET_GPIO5)

CRT/TVOUT

CRT/TVOUT

TXCLK_UP(PCIE_RESET_GPIO4)

TXCLK_UN(PCIE_RESET_GPIO1)

LVTM

LVTM

PM

PM

LVDS_DIGON(PCE_TCALRP)

LVDS_BLON(PCE_RCALRP)

LVDS_ENA_BL(PWM_GPIO2)

CLOCKs PLL PWR

CLOCKs PLL PWR

MIS.

MIS.

+VDDG_NB

R34

R34

*4.7K_NC

*4.7K_NC

INT_LCD_DDCCLK

INT_LCD_DDCDAT

C14

C14

*10P/50V_NC

*10P/50V_NC

2

TXOUT_L0P(NC)

TXOUT_L0N(NC)

TXOUT_L1P(NC)

TXOUT_L1N(NC)

TXOUT_L2P(NC)

TXOUT_L3P(NC)

TXOUT_U0P(NC)

TXOUT_U0N(NC)

TXOUT_U2P(NC)

TXOUT_U2N(NC)

TXOUT_U3N(NC)

TXCLK_LP(DBG_GPIO1)

TXCLK_LN(DBG_GPIO3)

VDDLTP18(NC)

VSSLTP18(NC)

VDDLT18_1(NC)

VDDLT18_2(NC)

VDDLT33_1(NC)

VDDLT33_2(NC)

VSSLT1(VSS)

VSSLT2(VSS)

VSSLT3(VSS)

VSSLT4(VSS)

VSSLT5(VSS)

VSSLT6(VSS)

VSSLT7(VSS)

TMDS_HPD(NC)

HPD(NC)

TVCLKIN(PWM_GPIO5)

THERMALDIODE_P

THERMALDIODE_N

TESTMODE

RS780M A13

RS780M A13

+1.1V_RUN

2

A22

B22

A21

B21

B20

A20

A19

B19

B18

A18

A17

B17

D20

D21

D18

D19

B16

A16

D16

D17

A13

B13

A15

B15

A14

B14

C14

D15

C16

C18

C20

E20

C22

E9

F7

G12

D9

D10

D12

AE8

AD8

D13

+LPVDD_NB

+LVDDR18D

R47 0R47 0

SUS_STAT#_R

R49

R49

1.8K/F

1.8K/F

T91T91

T8T8

T9T9

T11T11

T13T13

T15T15

T14T14

180mA

T2T2

NB_THERMDA

C590

C590

*220P_NC

*220P_NC

50

50

NB_THERMDC

Place C590 close to U22.

R51

R51

Only for RS780

4.7K

4.7K

REFCLK_N

R48 0R48 0

R50

R50

4.7K

4.7K

1

RS740/RX780/RS780 POWER DIFFERENCE

TABLE

PIN NAME

AVDDDI

AVDDQ

PLLVDD19

VDDA18HTPLL +1.8V +1.8V

VDDLTP18

VDDLT18

VDDLT33

C597

C597

C598

C598

2.2U/10V

2.2U/10V

0.1U/10V

0.1U/10V

0603

0603

C62

C62

C63

C63

0.1U/10V

0.1U/10V

4.7U/6.3V

4.7U/6.3V

0603

0603

SUS_STAT# 13

T88T88

RX780/RS780 DEBUG PIN MAPPING

DEBUG_OUT0

T87T87

DEBUG_OUT1

DEBUG_OUT2

DEBUG_OUT3

DEBUG_OUT4

DEBUG_OUT5

DEBUG_OUT6

DEBUG_OUT7

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

COMPUTER

RS780-LVDS

RS780-LVDS

RS780-LVDS

FX6 3A

FX6 3A

FX6 3A

RX780 RS780

NC +3.3VAVDD

NC +1.8V

NC +1.8V

NC

+1.8V +1.8VVDDA18PCIEPLL

NC

NC NC

+VDDG_NB+3.3V_RUN

R29 0R29 0

+1.8V_RUN

L64

L64

BLM15AG221SN1D

BLM15AG221SN1D

220 ohm @ 100MHz

+1.8V_RUN

L7

L7

BLM15AG221SN1D

BLM15AG221SN1D

220 ohm @ 100MHz

SUS_STAT#

RED(DFT_GPIO0)

GREEN(DFT_GPIO1)

Y(DFT_GPIO2)

BLUE(DFT_GPIO3)

TXOUT_L2N(DBG_GPIO0)

TXCLK_LP(DBG_GPIO1)

TXOUT_L3N(DBG_GPIO2)

TXCLK_LN(DBG_GPIO3)

COMB_Pb(DFT_GPIO4)

C_Pr(DFT_GPIO5)

1

+1.1VPLLVDD NC

+1.8V

+1.8VNC

+1.8V

+3.3V_RUN

R52

R52

4.7K

4.7K

C52

C52

RS780RX780

LVDS_DIGON

LVDS_ENA_BL

LVDS_BLON

TMDS_HPD

AUX1N

AUX1P

HPD

AUX_CAL

X

X

970Tuesday, May 20, 2008

970Tuesday, May 20, 2008

970Tuesday, May 20, 2008

of

of

of

*10P/50V_NC

*10P/50V_NC

Page 10

5

4

3

2

1

RS740/RX780/RS780 POWER DIFFERENCE TABLE

PIN NAME

VDDHT

D11

E14

E15

J12

K14

VSS3G8VSS4

VSS27

Y18

VSS28

AB11

(21)

VSS5

VSS29

AB15

J15

VSS6

VSS30

AB17

VSS7

VSS31

AB19

M11

L15

U22F

U22F

RS780M A13

RS780M A13

VSS8

VSS9

VSS10

VSS32

VSS34

VSS33

K11

AE20

AB21

U22E

U22E

J17

VDDHT_1

K16

VDDHT_2

L16

VDDHT_3

M16

VDDHT_4

P16

VDDHT_5

R16

VDDHT_6

T16

VDDHT_7

H18

VDDHTRX_1

G19

VDDHTRX_2

F20

VDDHTRX_3

E21

VDDHTRX_4

D22

VDDHTRX_5

B23

VDDHTRX_6

A23

VDDHTRX_7

AE25

VDDHTTX_1

AD24

VDDHTTX_2

AC23

VDDHTTX_3

AB22

VDDHTTX_4

AA21

VDDHTTX_5

Y20

VDDHTTX_6

W19

VDDHTTX_7

V18

VDDHTTX_8

U17

VDDHTTX_9

T17

VDDHTTX_10

R17

VDDHTTX_11

P17

VDDHTTX_12

M17

VDDHTTX_13

J10

VDDA18PCIE_1

P10

VDDA18PCIE_2

K10

VDDA18PCIE_3

M10

VDDA18PCIE_4

L10

VDDA18PCIE_5

W9

VDDA18PCIE_6

H9

VDDA18PCIE_7

T10

VDDA18PCIE_8

R10

VDDA18PCIE_9

Y9

VDDA18PCIE_10

AA9

VDDA18PCIE_11

AB9

VDDA18PCIE_12

AD9

VDDA18PCIE_13

AE9

VDDA18PCIE_14

U10

VDDA18PCIE_15

F9

VDDG18_1(VDD18_1)

G9

VDDG18_2(VDD18_2)

AE11

VDD18_MEM1(NC)

AD11

VDD18_MEM2(NC)

RS780M A13

RS780M A13

PART 5/6

PART 5/6

J4

R7

L1

L2

L4

L7

M6

N4

P6

R1

R2

R4

V7

U4

V8

V6

W1

W2

W4

W7

W8

Y6

AA4

AB5

AB1

AB7

H7

D D

C C

220 ohm @ 100MHz, 2A

B B

+3.3V_RUN

1.2V_RUN_ON42,45,46

A A

C87

C87

*2.2U_NC

*2.2U_NC

10

10

X5R

X5R

0603

0603

VSSAPCIE1A2VSSAPCIE2B1VSSAPCIE3D3VSSAPCIE4D5VSSAPCIE5E4VSSAPCIE6G1VSSAPCIE7G2VSSAPCIE8G4VSSAPCIE9

PART 6/6

PART 6/6

VSSAHT1

VSSAHT2

VSSAHT3

A25

E22

D23

G22

+1.1V_RUN +NB_VDD_MUX

+1.8V_RUN +VDDA18PCIE

220 ohm @ 100MHz, 2A

U6

U6

3

GND1

IN

EN

*TPS72501_NC

*TPS72501_NC

OUT

RESET#/FB

GND2

2

1

VSSAPCIE10

VSSAPCIE11

VSSAPCIE12

VSSAPCIE13

VSSAPCIE14

VSSAPCIE15

VSSAPCIE16

VSSAPCIE17

VSSAPCIE18

VSSAHT4

VSSAHT5

VSSAHT6

VSSAHT7

VSSAHT8

VSSAHT9

VSSAHT10

VSSAHT11

VSSAHT12

VSSAHT13

VSSAHT14

VSSAHT15

VSSAHT16

VSSAHT17

VSSAHT18

J22

L17

L22

L24

L25

H19

G24

G25

+1.2V_RUN +VDDHTTX

+1.35V_HT_VCC

BLM21PG221SN1D

BLM21PG221SN1D

0805

0805

4

5

6

P20

N22

R19

R22

R24

M20

R80

R80

0/0805

0/0805

BLM21PG221SN1D

BLM21PG221SN1D

*BLM21PG221SN1D_NC

*BLM21PG221SN1D_NC

L4

L4

80 ohm(4A)

BLM21PG221SN1D

BLM21PG221SN1D

0805

0805

220 ohm @ 100MHz, 2A

L71

L71

0805

0805