Page 1

1

2

3

4

5

6

7

8

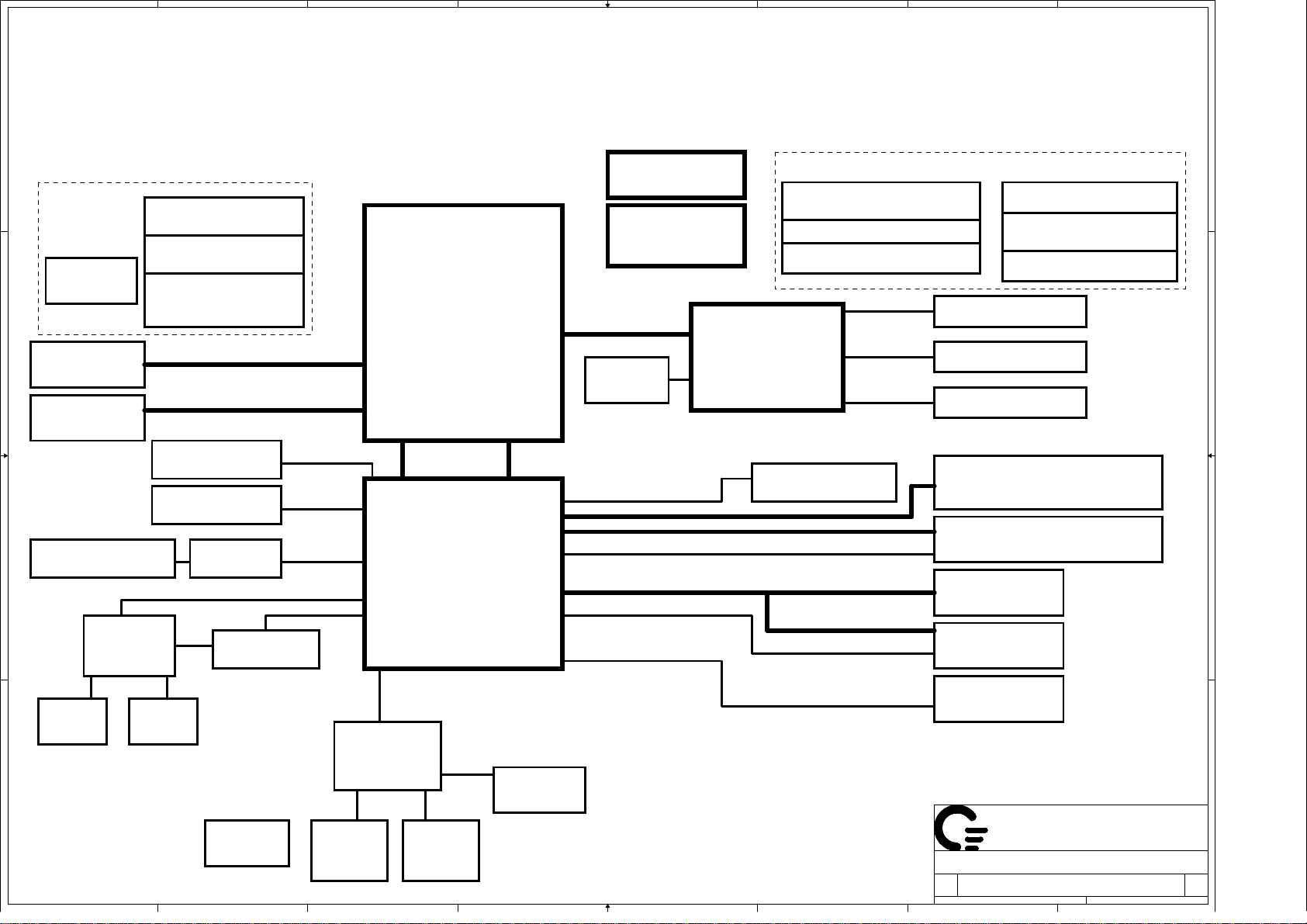

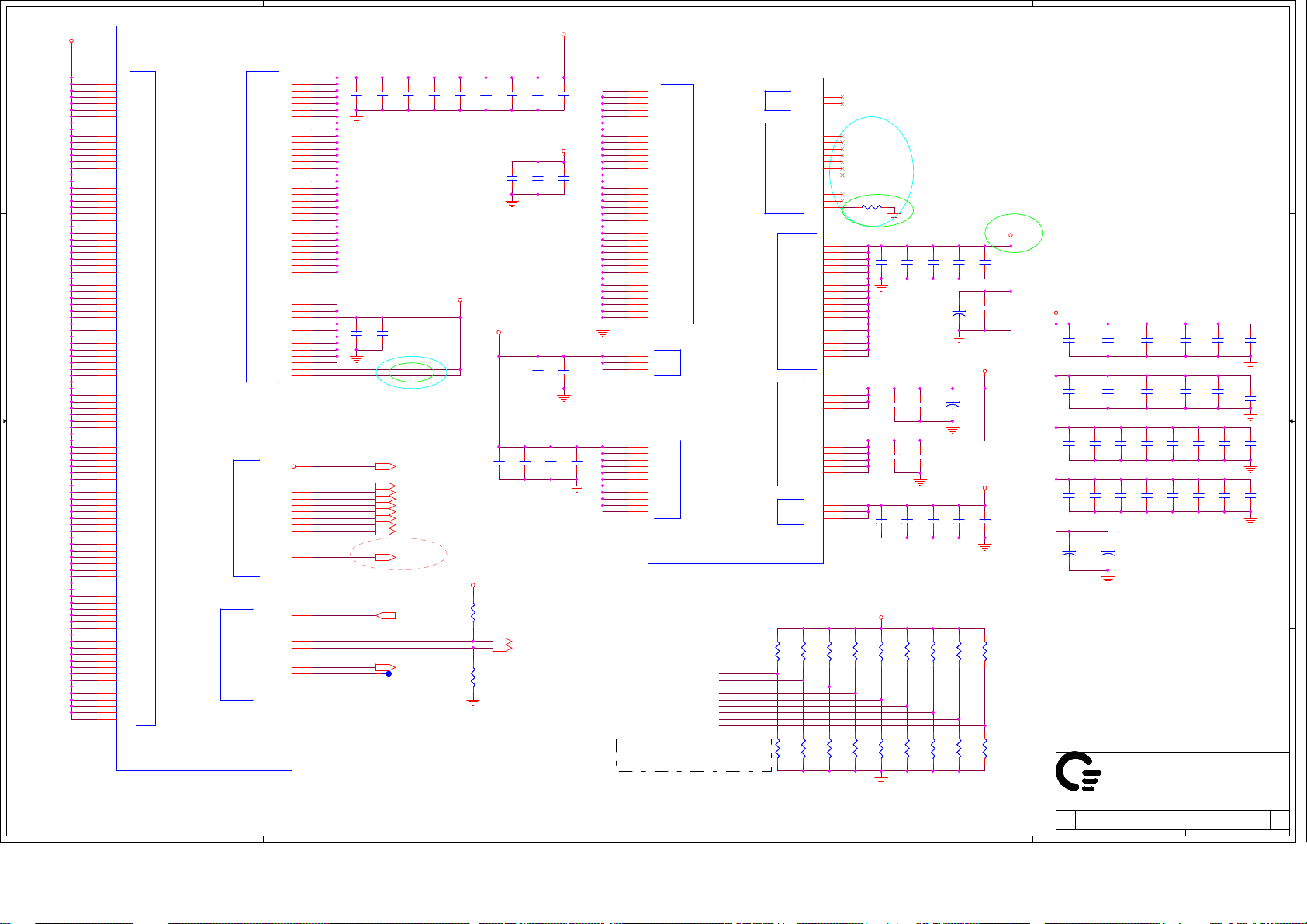

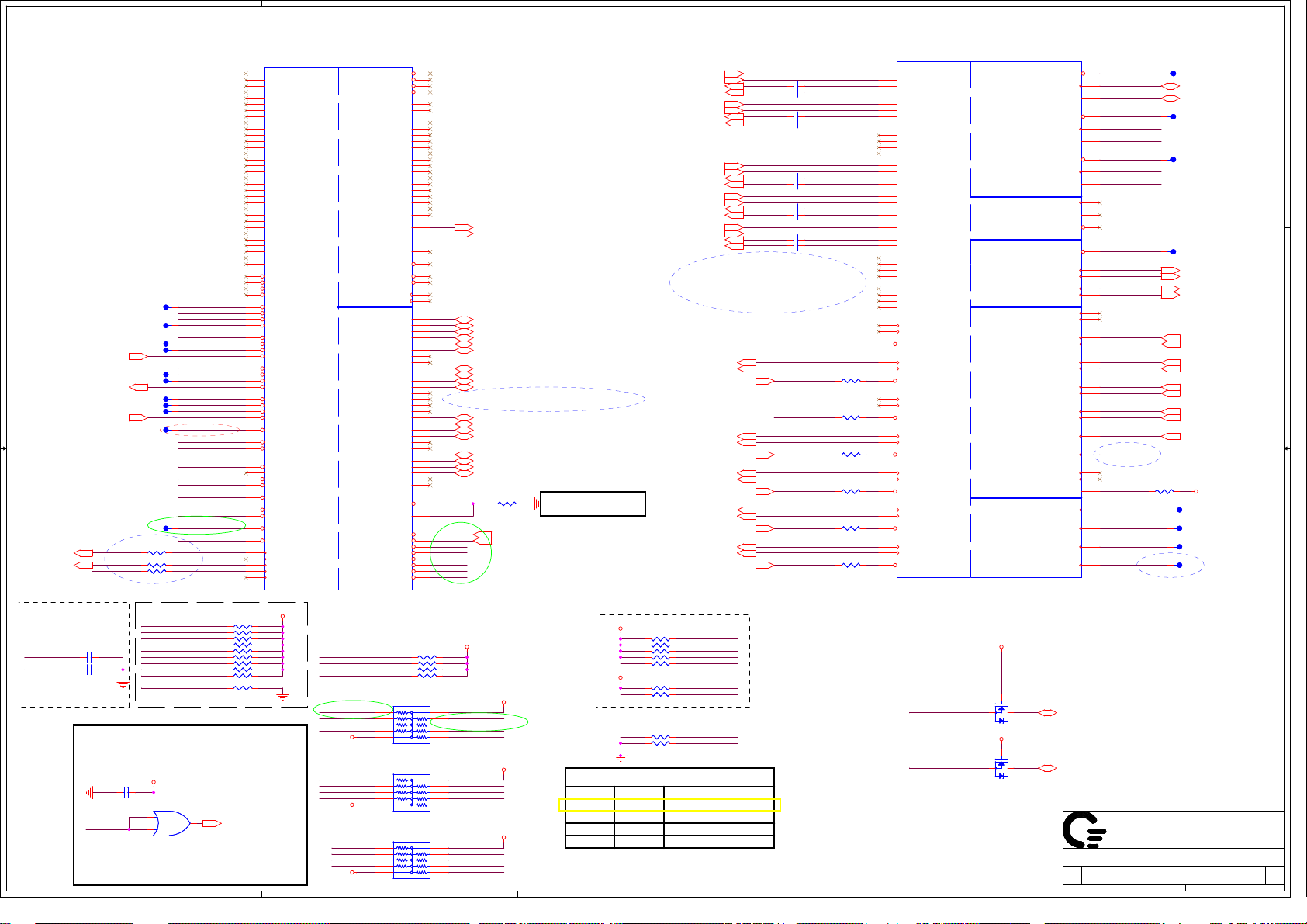

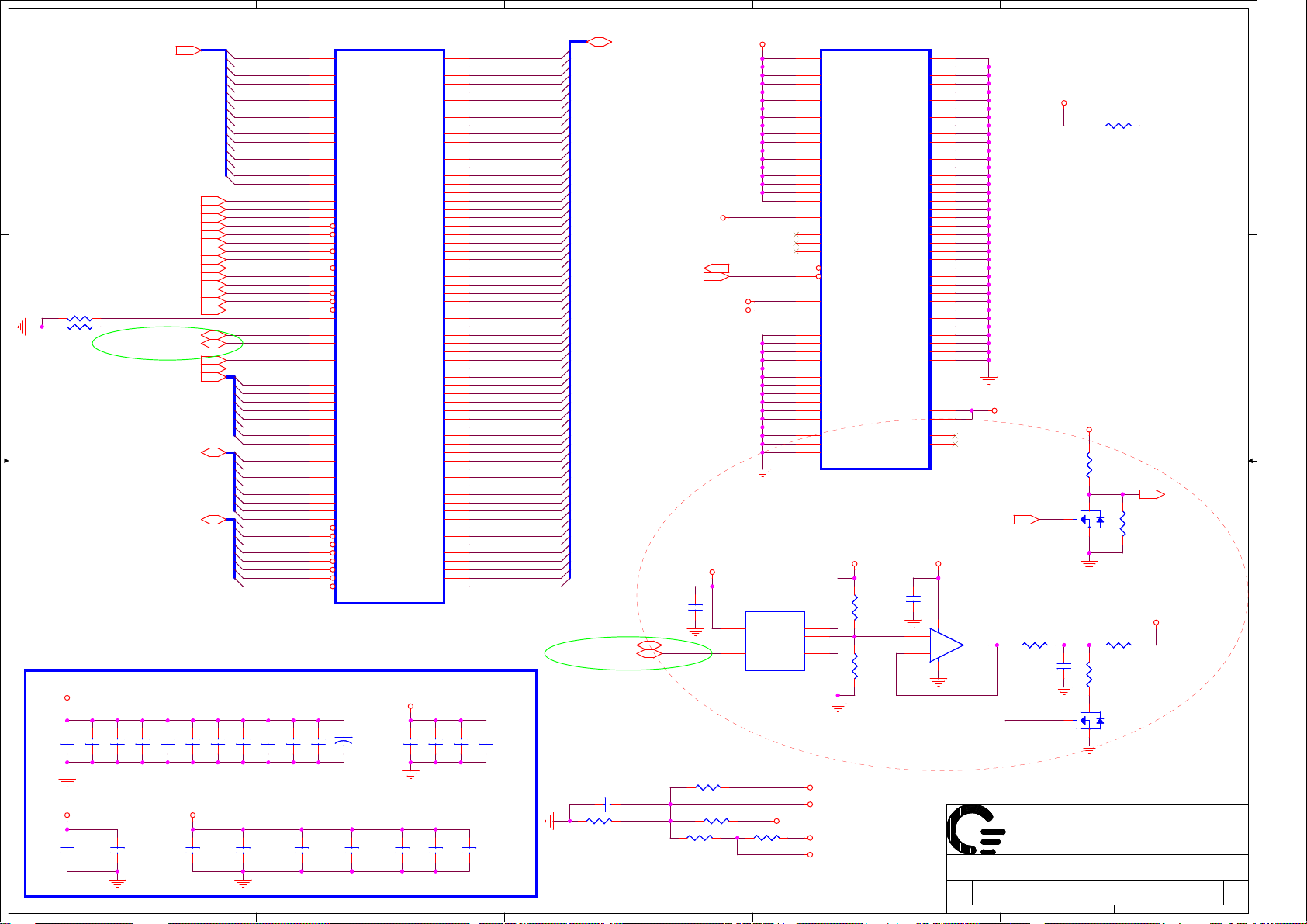

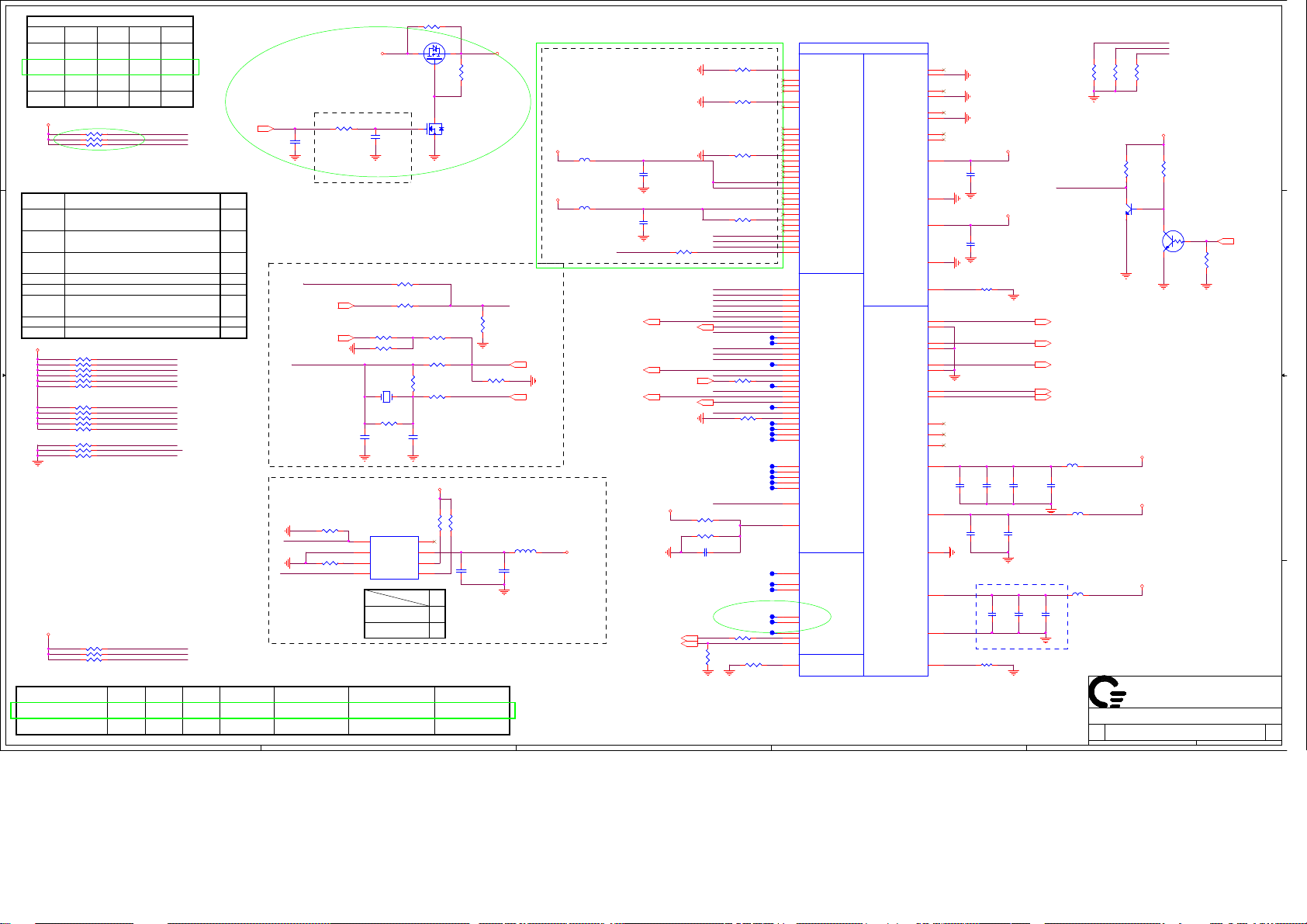

FM9 XXXX Intel Discrete GFX

VER : 1A

PWA:

A A

FAN & THERMAL

SMSC1422

POWER

AC/BATT

CONNECTOR

PG 53

B B

DDR3-SODIMM1

PG 13

DDR3-SODIMM2

PG 14

E-SATA Combo

C C

with USB CONN

SYSTEM

RESET CIRCUIT

BATT

CHARGER

RUN POWER SW

+3.3V_SUS/+5V_SUS

+5V/+3.3V/+1.8V

Dual Channel DDR3

800/1067/1333 1.5V

SATA-ODD

SATA-HDD

& Fall Sensor

PI2EQX3211BHE

PG 35

PG 35

PG 33PG 33

PG 42

PG 45

PG 52

SATA

SATA

SATA

IHDA

USB2.0

Auburndale/

Clarksfield

( rPGA 989 )

PG 3,4,5,6

PCH

CLOCK

SLG8SP585VTR

(QFN-32)

PCIEx16

DDR3 x 4

(512M 64bits)

PG 20

DMI X 4FDI

USB2.0 x 3

PCIEx1

PCIEx1

USB2.0

PCIEx2

USB2.0

PG 38

PG 15

ATI M92-XT

PCI EXPRESS GFX

PG 16,17,18,19,21,22

POWER

+1.5V_SUS/+0.75V_DDR_VTT

+1.05V

+1.1V_DDR_VTT

LVDS

HDMI

VGA

USB conn x 3

PG 33, 34

AUDIO/AMP

92HD73C

PG 39

Audio

SPK conn

Audio

Jacks x3

PG 39 PG 40

D D

1

Camera + D-MIC

PG 40

USER

INTERFACE

PG 37

2

KBC

ITE8502

SPI PS/2

FLASH

2Mbyts

PG 30

LPC

3

PG 29

Touchpad

PG 36

PG 7,8,9,10,11,12

17X8

Keyboard

4

PG 36

USB2.0

5

6

PWB:

PG 47

PG 48

PG 49

Panel Connector

HDMI CONN.

CRT CONN.

DC/DC

+3.3V_ALW/+5V_ALW/

+15V_ALW

VGA Core

PG 24

PG 24

PG 25

LAN

RTL8111DL\RJ45\Transformer

EXPRESS/Card Reader CONN.

MINI-CARD

CPU VRREGULATOR

WLAN

MINI-CARD

WWAN

Bluetooth BTB Conn

Title

Title

Title

Schematic Block Diagram1

Schematic Block Diagram1

Schematic Block Diagram1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FM9 1A

FM9 1A

FM9 1A

Date: Sheet of

Date: Sheet of

Date: Sheet of

PG 32

PG 31

PG 32

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

7

PG 51

PG 46

PG 50

PG 41

PG 28

1 64Thursday, February 26, 2009

1 64Thursday, February 26, 2009

1 64Thursday, February 26, 2009

8

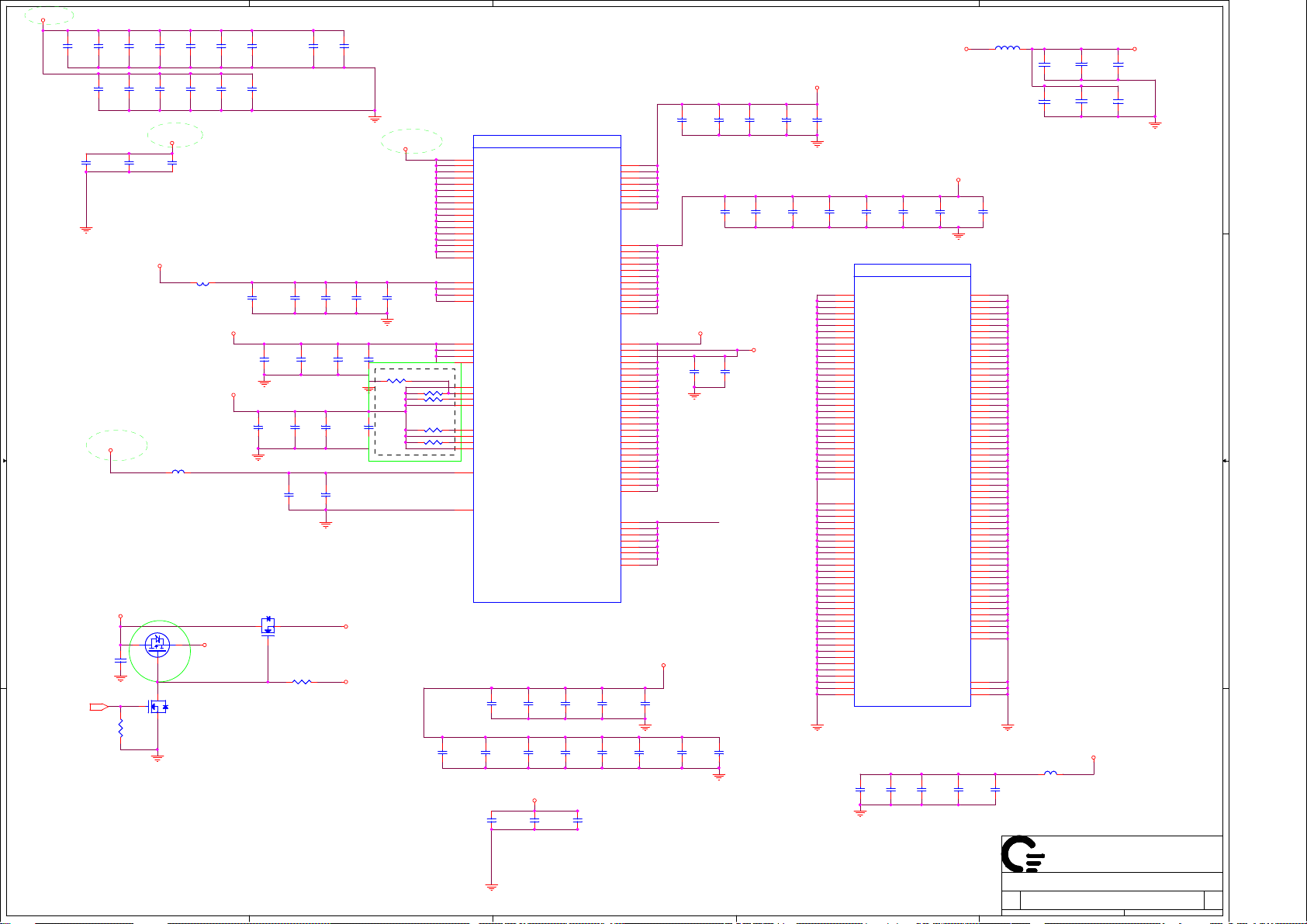

Page 2

1

2

3

4

5

6

7

8

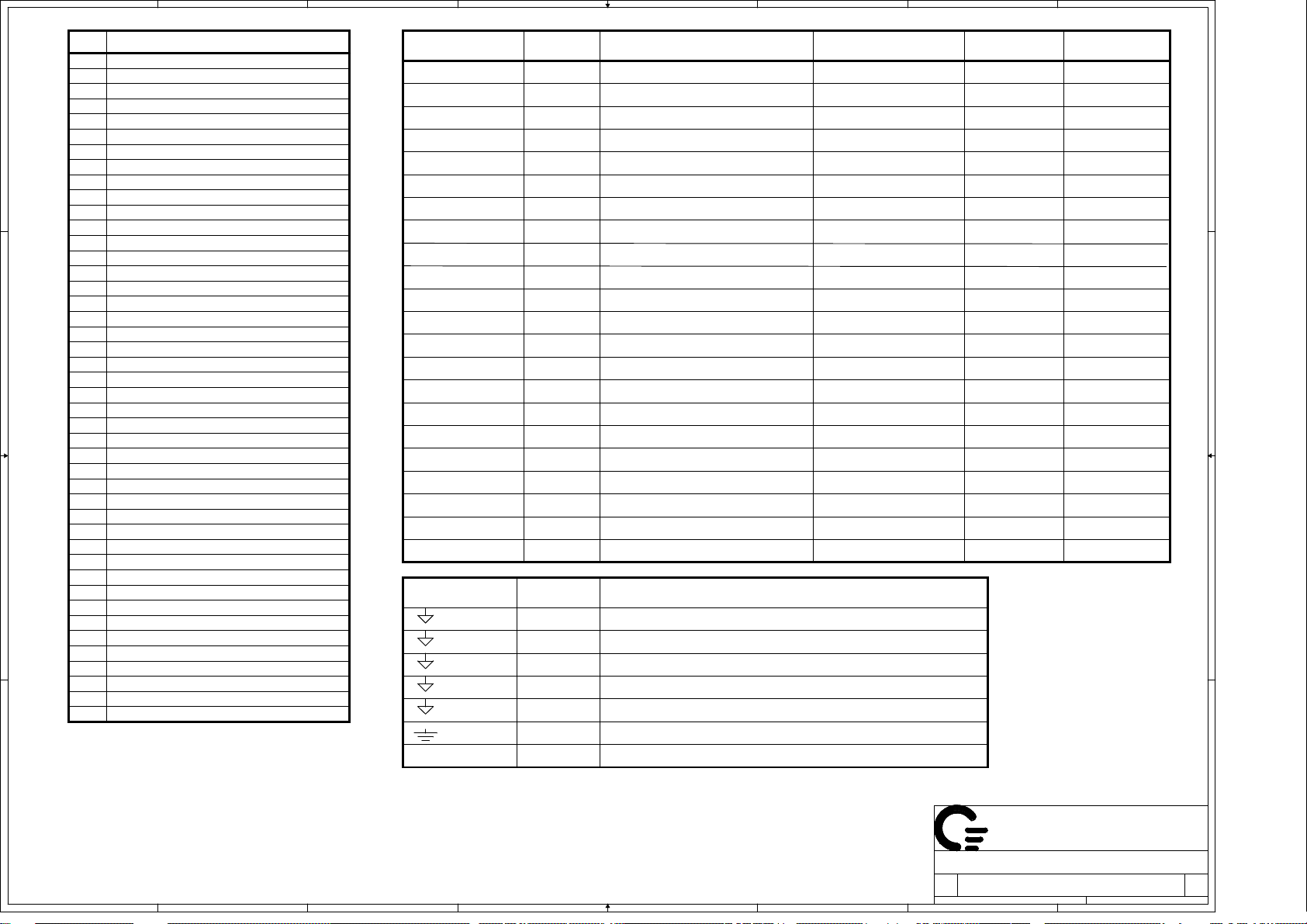

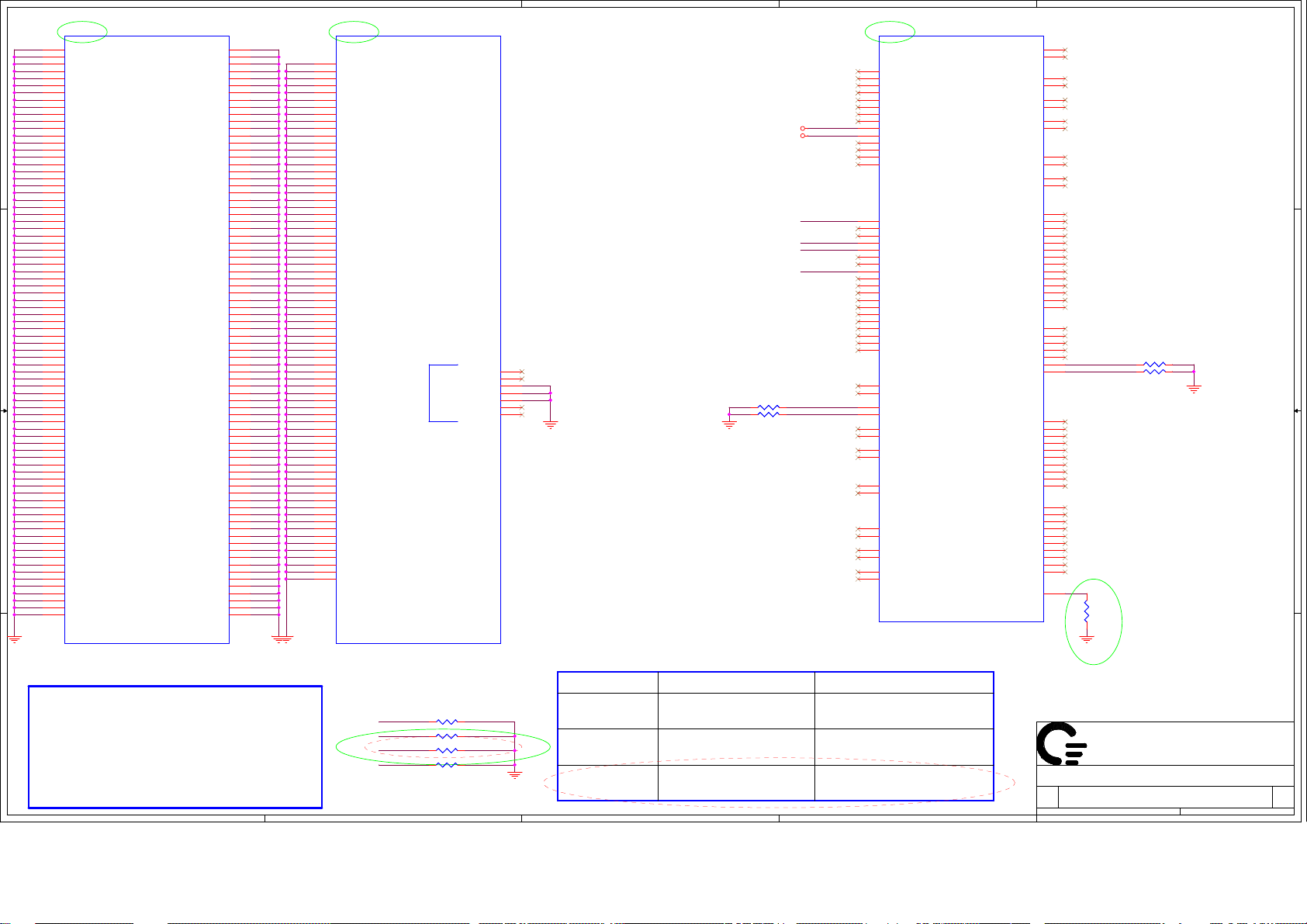

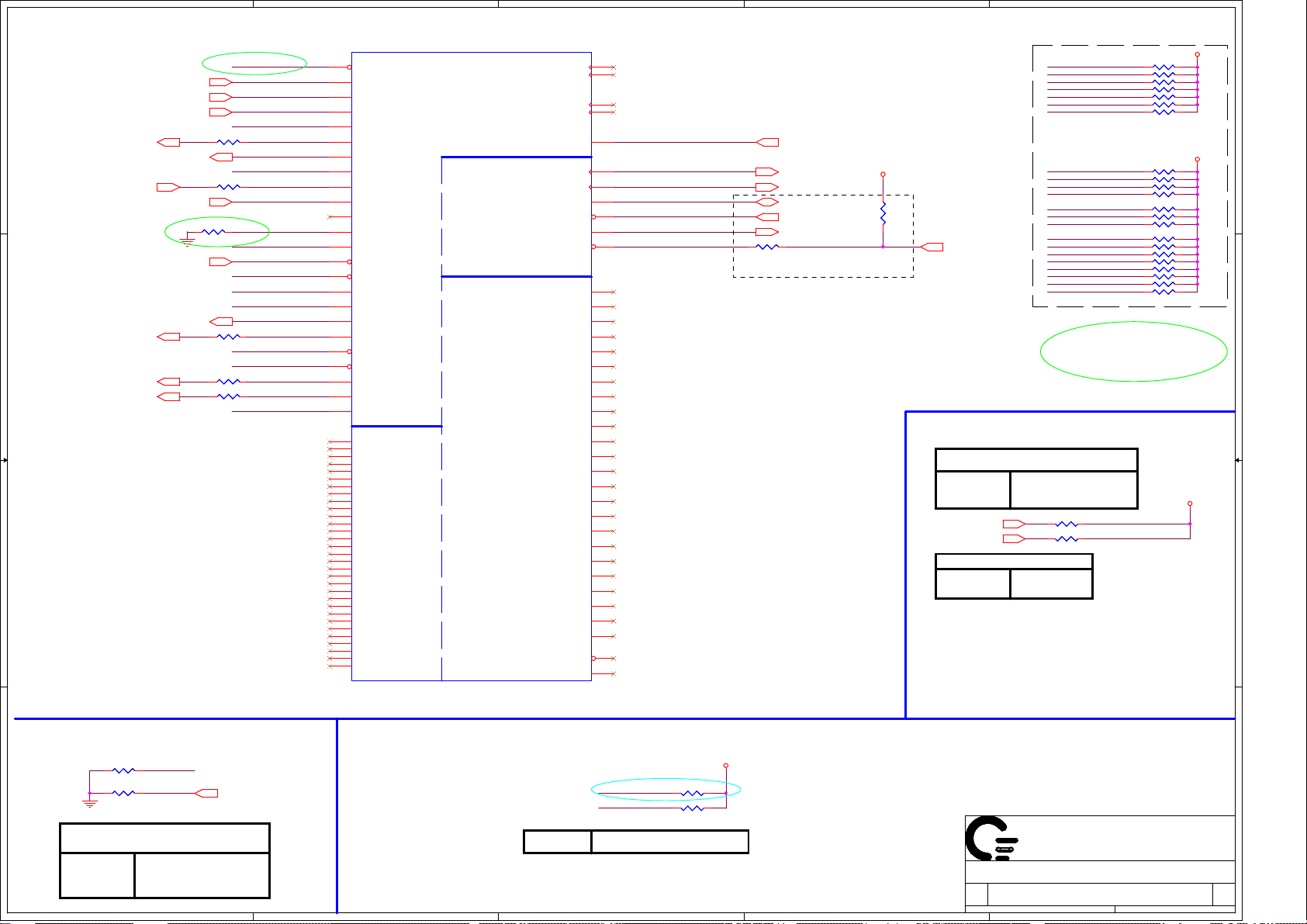

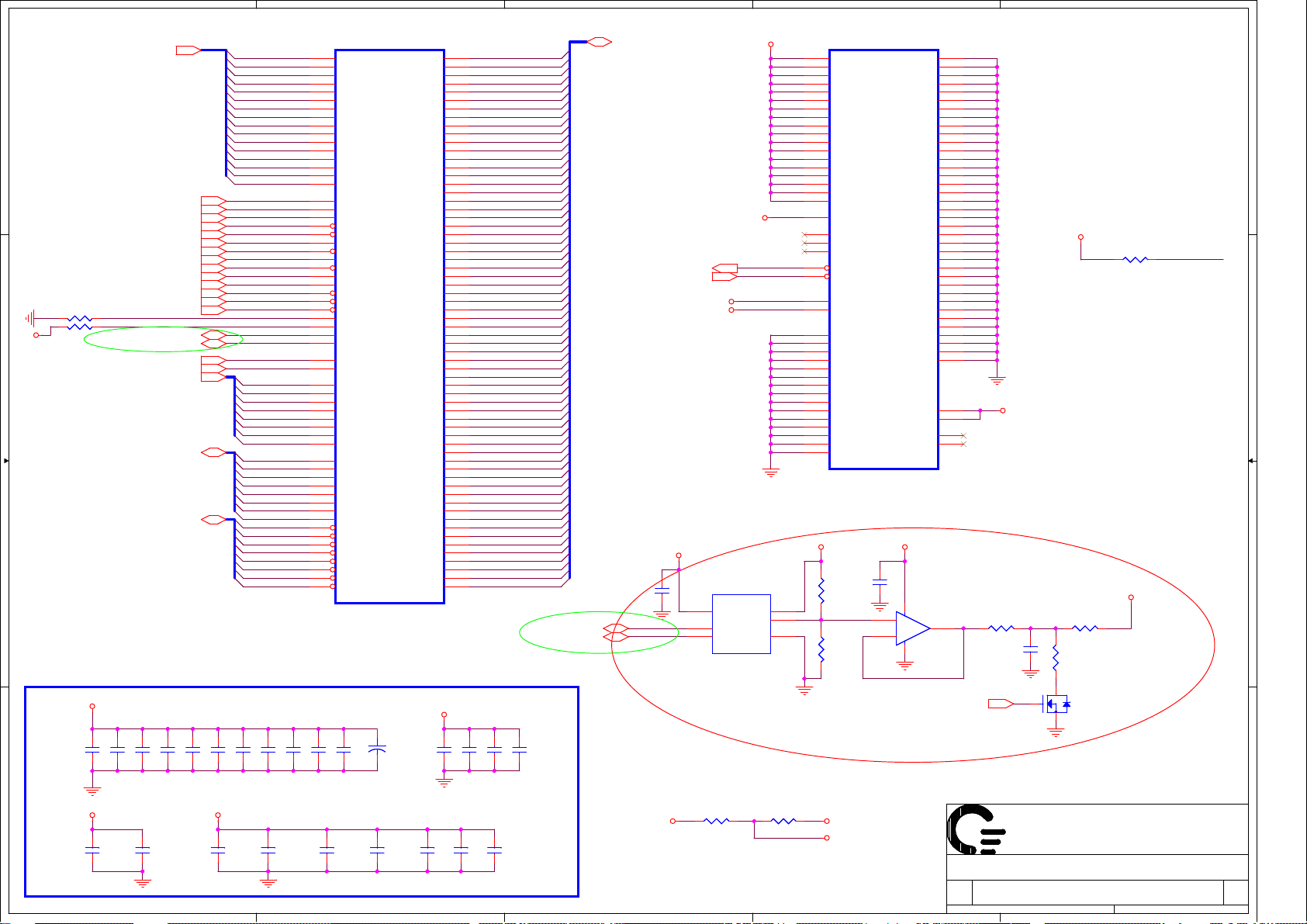

Table of Contents Power States

PAGE DESCRIPTION

1

Schematic Block Diagram

2

Front Page

3-6

Clarksfield/Auburndale

7-12

PCH

13-14

A A

B B

C C

DDRIII SO-DIMM(204P)

15

Clock Generator

16-22

M92-S2-XT

23

BLANK PAGE

24

LCD CONN / HDMI CONN

25

CRT CONN

26

OZ888GS0L3N

BLANK PAGE

27

28

Express/CRard/1394

29

SIO (ITE8512)

30

FLASH / RTC

31

MINI-Card (WWAN)

32

MINI-Card (WLAN\WPAN)

Left PUSB/ESATA

33

34

Right USB

SATA (HDD & CD_ROM)

35

TP / KEYBOARD

36

SWITCH / /LED

37

38

FAN / THERMAL

Azelia CODEC

39

40

AUDIO CONN

41

LAN(RTL8111DL/RJ-45)

42

System Reset Circuit

43

Blank Page

44451.8V_RUN(RT9018/RT9024)

Charger (ISL88731)

46

3V/5V (TPS51427A)

1.5_DDR/0.75(TPS51116)

47

1.05V_PCH(TPS51218)

48

1.1_VTT(TPS51218)

49

50

VGA_M92-XT(MAX8792)

51

V_CORE(ISL62882)

52

Run Power Switch

53

DCin & Batt

54

PAD & SCREW

55

EMI CAP

56

SMBUS BLOCK

57

THERMAL MAP

58

Power Block Diagram

59

XDP

POWER PLANE

+PWR_SRC

+RTC_CELL

+3.3V_ALW

+5V_ALW2

+3.3V_LAN

+5V_SUS

+3.3V_SUS

+1.5V_SUS

+0.75V_DDR_VTT

+5V_RUN

+3.3V_RUN

+1.8V_RUN

+1.5V_RUN

+1.8V_RUN_GFX

+VCC_GFX_CORE

+1.05V_PCH

+VCC_CORE

+LCDVCC

+5V_MOD

+5V_HDD

+1.1V_VTT 03,05,10,11,49,59+1.1V

+1.1V_GFX_PCIE

10V~+19V

+3.0V~+3.3V

+3.3V

+5V

+3.3V

+5V

+3.3V

+1.8V

+0.9V

+5V

+3.3V

+1.8V

+1.5V

+1.25V

+0.9V~+1.2V RUN_ON

+1.05V 08,09,11,15,48

+0.7V~+1.77V

+3.3V

+5V

+5V

+1.1V 18,50

GND PLANE PAGE

GND_CHG

GND_1.05V

GND_VGA

GND_SIGNAL

AGND_DC/DC

GND

46

47

50

51

52

ALL

24,30,45,46,47,48,49,50,51

08,11,29,30

08,29,30,35,36,37,42,44,45,46,47,52,53

37,46,53

41

11,33,34,35,37,51,52

7,09,10,11,13,14,19,24,26,28,29,37,41,42,44

,48,49,50,51,52

03,05,13,14,47,50,52

13,14,47,52

11,18,24,25,35,36,38,39,40,52

3,7,8,9,10,11,13,14,15,17,24,25,26,28,29,30

,31,32,33,35,37,38,39,40,41,42,46,51,52,59

05,11,26,44,52

11,18,19,20,28,31,32,52

17,18,21,22,44,52

18,21,50

05,51

26

36

36

DESCRIPTION

DESCRIPTION

MAIN POWER

RTC

8051 POWER

LARGE POWER

LAN POWER

SLP_S5# CTRLD POWER

SLP_S5# CTRLD POWER

SODIMM POWER

SODIMM POWER

SLP_S3# CTRLD POWER

SLP_S3# CTRLD POWER

SDVO POWER

CALISTOGA/ICH9 POWER

VGA POWER

VGA POWER

CPU/CALISTOGA/ICH8 POWER

CPU CORE POWER

LCD Power

Module Power

HDD Power

CONTROL

SIGNAL

ALWON

RUN_ON

AUX_ON

SUS_ON

SUS_ON

SUS_ON

RUN_ON

RUN_ON

RUN_ON

RUN_ON

RUN_ON

RUN_ON

1.05V_RUN_ON

IMVP_VR_ON

LCDVCC_TST_EN

& ENVDD

MODC_EN

HDDC_EN

ACTIVE INVOLTAGE PAGE

S0~S5

S0~S5

S0~S5

S0~S5

D D

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

COMPUTER

Index & Power Status

Index & Power Status

Index & Power Status

FM9 1A

FM9 1A

FM9 1A

7

2 64Thursday, February 26, 2009

2 64Thursday, February 26, 2009

2 64Thursday, February 26, 2009

8

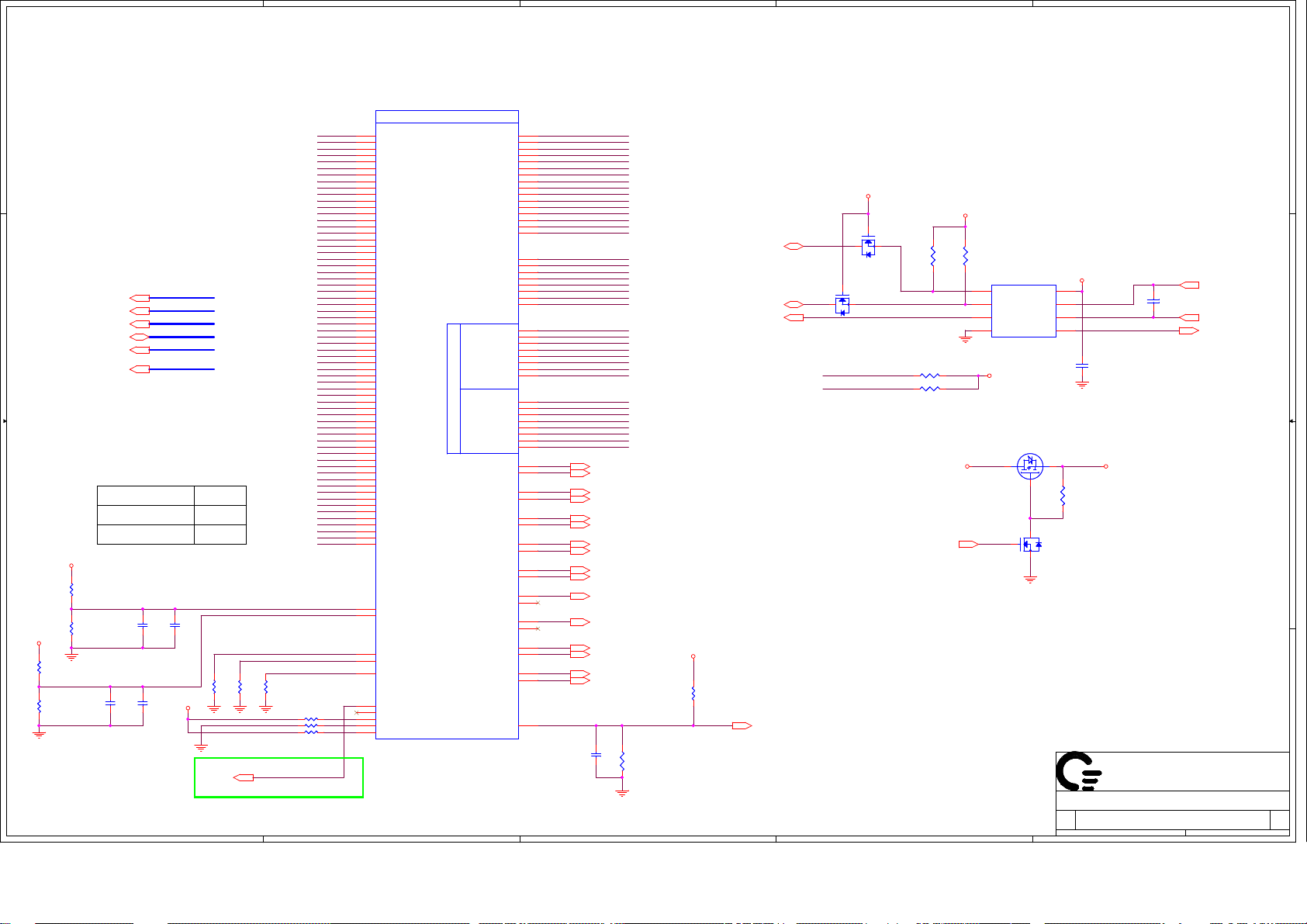

Page 3

5

4

3

2

1

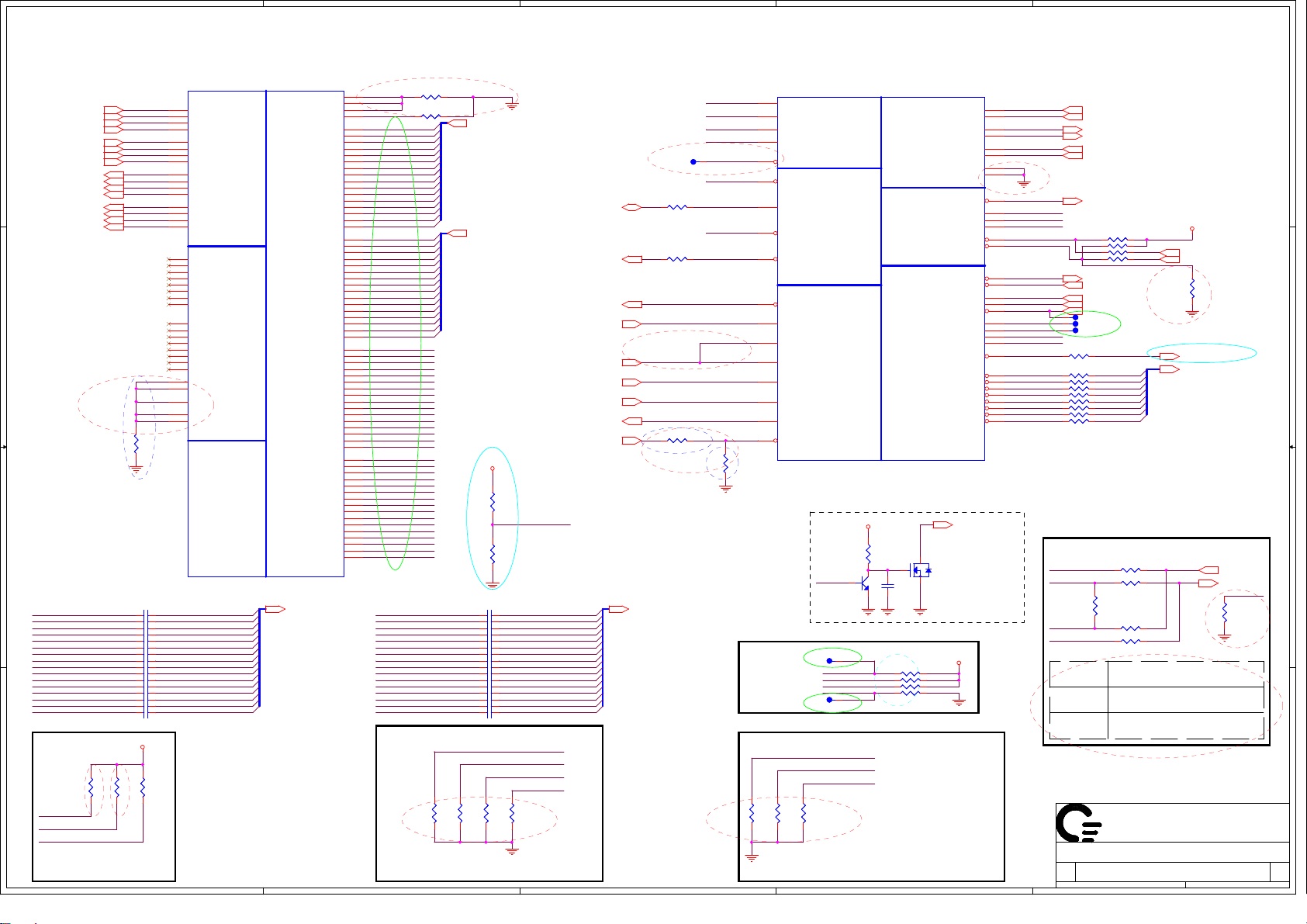

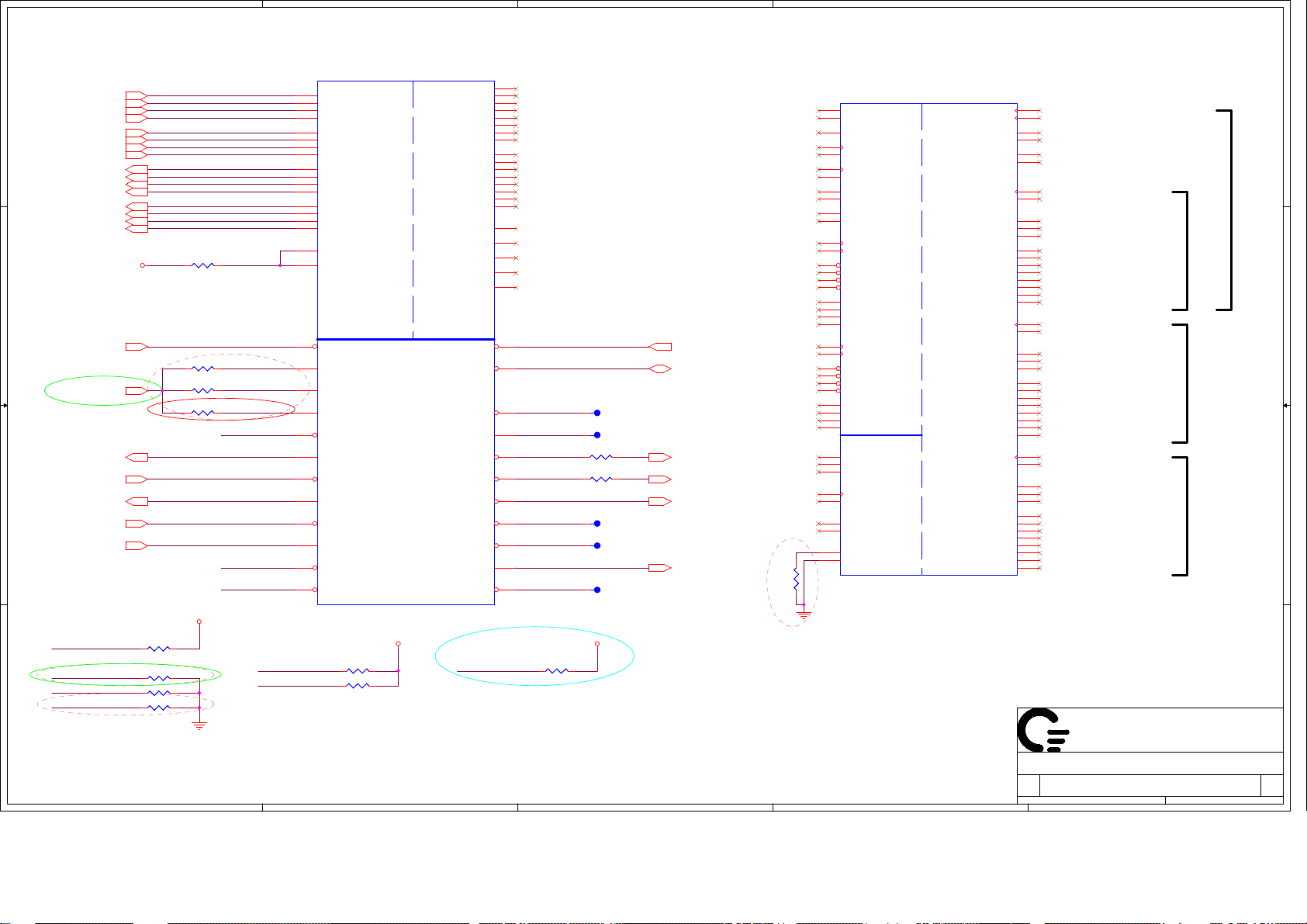

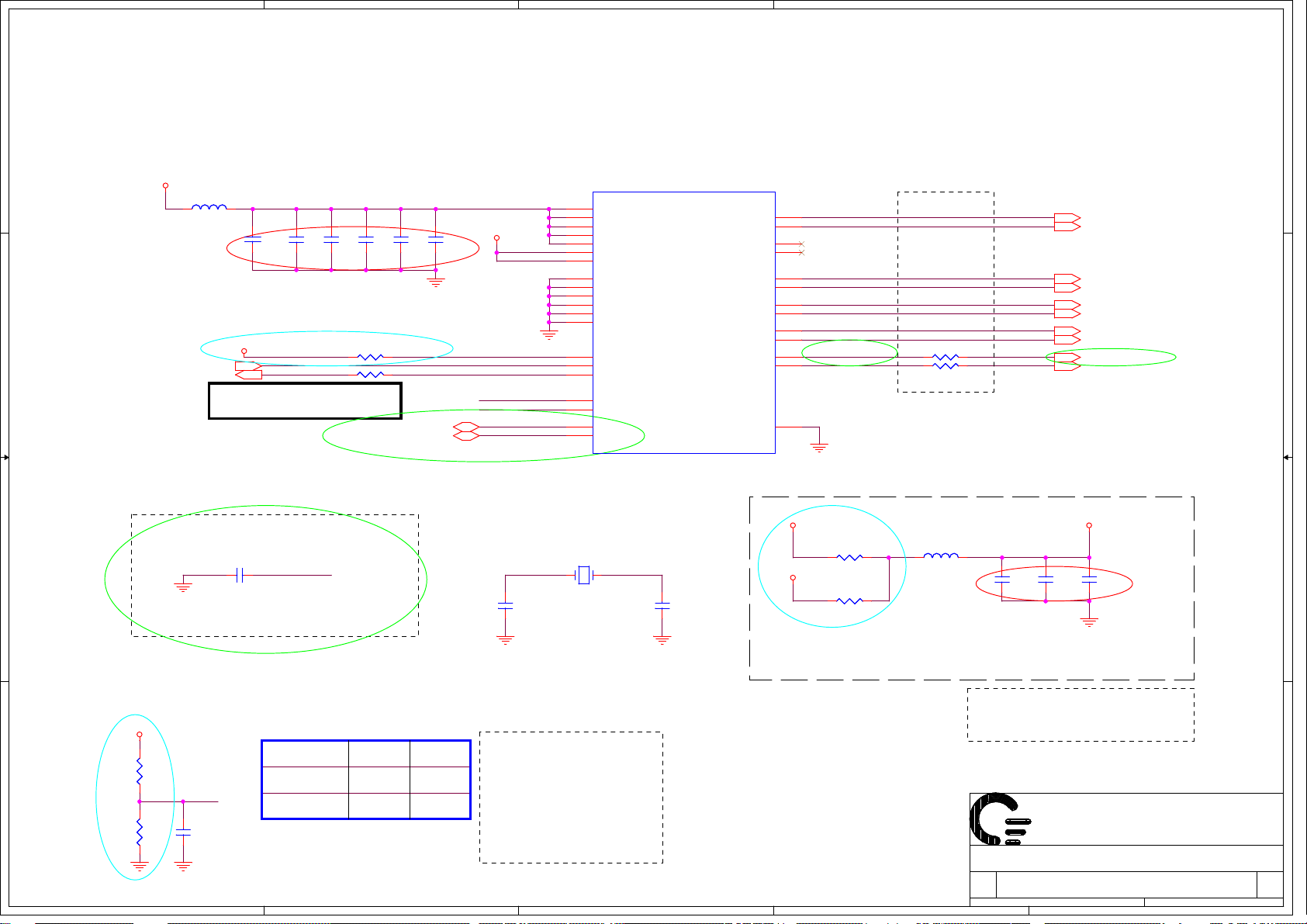

AUBURNDALE/CLARKSFIELD PROCESSOR (DMI,PEG,FDI) AUBURNDALE/CLARKSFIELD PROCESSOR (CLK,MISC,JTAG)

SC(V1.0),P11: Should be shorted at the pins

and then routed to one end of the 49.9-Ω ±1%

resistor, pulled-down to GND on the board.

U3031A

U3031A

R7621KR762

1K

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

DMI_TXN07

D D

C C

DMI_TXN17

DMI_TXN27

DMI_TXN37

DMI_TXP07

DMI_TXP17

DMI_TXP27

DMI_TXP37

DMI_RXN07

DMI_RXN17

DMI_RXN27

DMI_RXN37

DMI_RXP07

DMI_RXP17

DMI_RXP27

DMI_RXP37

0214

DG(V1.0),P79: should be tied to GND

(through 1K ±5% resistors),

if these signals are left floating,

there are nofunctional impacts

but a small amount of power (~15 mW)

maybe wasted.

DG(V1.1) P83:

FDI_FSYNC[0], FDI_FSYNC[1],

FDI_LSYNC[0],FDI_LSYNC[1]

B B

can be ganged together

with one resistor.

PCIE_MTX_GRX_C_N0

PCIE_MTX_GRX_C_N1

PCIE_MTX_GRX_C_N2

PCIE_MTX_GRX_C_N3

PCIE_MTX_GRX_C_N4

PCIE_MTX_GRX_C_N5

PCIE_MTX_GRX_C_N6

PCIE_MTX_GRX_C_N7

PCIE_MTX_GRX_C_N8

PCIE_MTX_GRX_C_N9

PCIE_MTX_GRX_C_N10

PCIE_MTX_GRX_C_N11

PCIE_MTX_GRX_C_N12

PCIE_MTX_GRX_C_N13

PCIE_MTX_GRX_C_N14

PCIE_MTX_GRX_C_N15

Processor

Pullups

A A

H_CATERR#

H_PROCHOT#_D

H_CPURST#

R793

R793

49.9/F

49.9/F

C1175 0.1U10 C1175 0.1U10

C1177 0.1U10 C1177 0.1U10

C1179 0.1U10 C1179 0.1U10

C1181 0.1U10 C1181 0.1U10

C1183 0.1U10 C1183 0.1U10

C1185 0.1U10 C1185 0.1U10

C1187 0.1U10 C1187 0.1U10

C1189 0.1U10 C1189 0.1U10

C1191 0.1U10 C1191 0.1U10

C1193 0.1U10 C1193 0.1U10

C1195 0.1U10 C1195 0.1U10

C1197 0.1U10 C1197 0.1U10

C1199 0.1U10 C1199 0.1U10

C1201 0.1U10 C1201 0.1U10

C1203 0.1U10 C1203 0.1U10

C1205 0.1U10 C1205 0.1U10

+1.1V_VTT

R794

R794

49.9/F

49.9/F

5

Clarksfield/Auburndale

Clarksfield/Auburndale

PCIE_MTX_GRX_N0

PCIE_MTX_GRX_N1

PCIE_MTX_GRX_N2

PCIE_MTX_GRX_N3

PCIE_MTX_GRX_N4

PCIE_MTX_GRX_N5

PCIE_MTX_GRX_N6

PCIE_MTX_GRX_N7

PCIE_MTX_GRX_N8

PCIE_MTX_GRX_N9

PCIE_MTX_GRX_N10

PCIE_MTX_GRX_N11

PCIE_MTX_GRX_N12

PCIE_MTX_GRX_N13

PCIE_MTX_GRX_N14

PCIE_MTX_GRX_N15

SC(1.0V),P17:

H_PROCHOT#D

use: pull to 68 ohm

R795

R795

if it isn'tt used: pull to 50 ohm

*68_NC

*68_NC

SC(1.0V),P17:

H_CATERR#

49.9-Ω ±1% Pull-Up to the VTT rail

(+V1.1S_VTT)

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PCIE_MTX_GRX_N[0..15] 16 PCIE_MTX_GRX_P[0..15] 16

PEG_ICOMPI

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

R742 49.9/FR742 49.9/F

R744 750/FR744 750/F

PCIE_MRX_GTX_N15

PCIE_MRX_GTX_N14

PCIE_MRX_GTX_N13

PCIE_MRX_GTX_N12

PCIE_MRX_GTX_N11

PCIE_MRX_GTX_N10

PCIE_MRX_GTX_N9

PCIE_MRX_GTX_N8

PCIE_MRX_GTX_N7

PCIE_MRX_GTX_N6

PCIE_MRX_GTX_N5

PCIE_MRX_GTX_N4

PCIE_MRX_GTX_N3

PCIE_MRX_GTX_N2

PCIE_MRX_GTX_N1

PCIE_MRX_GTX_N0

PCIE_MRX_GTX_P15

PCIE_MRX_GTX_P14

PCIE_MRX_GTX_P13

PCIE_MRX_GTX_P12

PCIE_MRX_GTX_P11

PCIE_MRX_GTX_P10

PCIE_MRX_GTX_P9

PCIE_MRX_GTX_P8

PCIE_MRX_GTX_P7

PCIE_MRX_GTX_P6

PCIE_MRX_GTX_P5

PCIE_MRX_GTX_P4

PCIE_MRX_GTX_P3

PCIE_MRX_GTX_P2

PCIE_MRX_GTX_P1

PCIE_MRX_GTX_P0

PCIE_MTX_GRX_C_N15

PCIE_MTX_GRX_C_N14

PCIE_MTX_GRX_C_N13

PCIE_MTX_GRX_C_N12

PCIE_MTX_GRX_C_N11

PCIE_MTX_GRX_C_N10

PCIE_MTX_GRX_C_N9

PCIE_MTX_GRX_C_N8

PCIE_MTX_GRX_C_N7

PCIE_MTX_GRX_C_N6

PCIE_MTX_GRX_C_N5

PCIE_MTX_GRX_C_N4

PCIE_MTX_GRX_C_N3

PCIE_MTX_GRX_C_N2

PCIE_MTX_GRX_C_N1

PCIE_MTX_GRX_C_N0

PCIE_MTX_GRX_C_P15

PCIE_MTX_GRX_C_P14

PCIE_MTX_GRX_C_P13

PCIE_MTX_GRX_C_P12

PCIE_MTX_GRX_C_P11

PCIE_MTX_GRX_C_P10

PCIE_MTX_GRX_C_P9

PCIE_MTX_GRX_C_P8

PCIE_MTX_GRX_C_P7

PCIE_MTX_GRX_C_P6

PCIE_MTX_GRX_C_P5

PCIE_MTX_GRX_C_P4

PCIE_MTX_GRX_C_P3

PCIE_MTX_GRX_C_P2

PCIE_MTX_GRX_C_P1

PCIE_MTX_GRX_C_P0

PCIE_MTX_GRX_C_P0

PCIE_MTX_GRX_C_P1

PCIE_MTX_GRX_C_P2

PCIE_MTX_GRX_C_P3

PCIE_MTX_GRX_C_P4

PCIE_MTX_GRX_C_P5

PCIE_MTX_GRX_C_P6

PCIE_MTX_GRX_C_P7

PCIE_MTX_GRX_C_P8

PCIE_MTX_GRX_C_P9

PCIE_MTX_GRX_C_P10

PCIE_MTX_GRX_C_P11

PCIE_MTX_GRX_C_P12

PCIE_MTX_GRX_C_P13

PCIE_MTX_GRX_C_P14

PCIE_MTX_GRX_C_P15

PCIE_MRX_GTX_N[0..15] 16

PCIE_MRX_GTX_P[0..15] 16

SC(V1.0),P17,35:

This signal should be connected to

the processor's VCCPWRGOOD_1

and VCCPWRGOOD_0 input to

indicate when the

processor power is valid.

VTTPWRGOOD

SC(V1.0)P18:

VTT_1.1 VR power good signal

to processor. Signal voltage level

is 1.1 V.

1

+1.5V_SUS

R778

R778

4.75K/F

4.75K/F

R779

R779

12K/F

12K/F

C1176 0.1U10 C1176 0.1U10

C1178 0.1U10 C1178 0.1U10

C1180 0.1U10 C1180 0.1U10

C1182 0.1U10 C1182 0.1U10

C1184 0.1U10 C1184 0.1U10

C1186 0.1U10 C1186 0.1U10

C1188 0.1U10 C1188 0.1U10

C1190 0.1U10 C1190 0.1U10

C1192 0.1U10 C1192 0.1U10

C1194 0.1U10 C1194 0.1U10

C1196 0.1U10 C1196 0.1U10

C1198 0.1U10 C1198 0.1U10

C1200 0.1U10 C1200 0.1U10

C1202 0.1U10 C1202 0.1U10

C1204 0.1U10 C1204 0.1U10

C1206 0.1U10 C1206 0.1U10

Processor Compensation Signals

R796

R796

R797

R797

49.9/F

49.9/F

49.9/F

49.9/F

DG(V1.0),P17:

COMP[0.1] 49.9-Ω ±1% pull-down to GND

COMP[2.3] 20-Ω ±1% pull-down to GND

4

R798

R798

20/F

20/F

PM_DRAM_PWRGD

PCIE_MTX_GRX_P0

PCIE_MTX_GRX_P1

PCIE_MTX_GRX_P2

PCIE_MTX_GRX_P3

PCIE_MTX_GRX_P4

PCIE_MTX_GRX_P5

PCIE_MTX_GRX_P6

PCIE_MTX_GRX_P7

PCIE_MTX_GRX_P8

PCIE_MTX_GRX_P9

PCIE_MTX_GRX_P10

PCIE_MTX_GRX_P11

PCIE_MTX_GRX_P12

PCIE_MTX_GRX_P13

PCIE_MTX_GRX_P14

PCIE_MTX_GRX_P15

H_COMP0

H_COMP1

H_COMP2

H_COMP3

R799

R799

20/F

20/F

U3031B

SC(V1.0),P17:

SKTOCC#

Can be left No Connect

or tied to GND

T182T182

H_PECI10

H_THERM10

H_CPURST#60

PM_SYNC7

H_PWRGOOD10,60

PM_DRAM_PWRGD7

H_VTTPWRGD42

H_PWRGD_XDP60

PLTRST#9,16,26,28,29,31,32,41

RSTIN#:

DG(V1.11)(Doc.# 414044),P10:

Need a voltage divider

network to scale down from

3.3V (PCH driven) to 1.05V/1.1V (Clarksfield/Auburndale)

SM_DRAMPWROK:

DG(V1.0) P311&SC(V1.0) P18:recommend 4.75-kΩ

pull-up to DDR3 Power Rail (VDDQ) of +V1.5U

and a 12-kΩ pull-down to ground to convert

to processor’s VTT level.

CRB(V1.0) P11:CRB uses a 3.3V (always ON) rail

with 2K and 1K combination. CRB Implementation

is different for the Calpella Platform Design Guide.

Customers to

follow the latest Calpella Platform Design

Guide for DRAMPWROK Implementation.

R751 0R751 0

R755 0R755 0

R776 1.5K/FR776 1.5K/F

SM_DRAMPWROK:(Intell Feedback)

Either way works.

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP_SKT0CC#

H_CATERR#

H_PECI_ISO

H_PROCHOT#_D

H_CPURST#

PM_DRAM_PWRGD

R777

R777

750/F

750/F

U3031B

AT23

AT24

G16

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

Clarksfield/Auburndale

Clarksfield/Auburndale

0214

CRB(V1.0) P11:

is it necessery?

DDR3 Compensation Signals

R800

R800

130/F

130/F

3

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

H_THERM

MMST3904-7-F

MMST3904-7-F

T188T188

T187T187

R801

R801

R802

R802

24.9/F

24.9/F

100/F

100/F

DG(V1.0),P83:

SM_RCOMP[0] 100-Ω ±1% pull-down to GND

SM_RCOMP[1] 24.9-Ω ±1% pull-down to GND

SM_RCOMP[2] 130-Ω ±1% pull-down to GND

MISC THERMAL

MISC THERMAL

PWR MANAGEMENT

PWR MANAGEMENT

+3.3V_RUN

R28

R28

10M

10M

2

Q7

Q7

1 3

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TCLK

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

Layout Note: Place

these resistors

near Processor

12

R787 *51_NCR787 *51_NC

R788 *51_NCR788 *51_NC

R789 *51_NCR789 *51_NC

R790 *51_NCR790 *51_NC

CLOCKS

CLOCKS

DDR3

DDR3

JTAG & BPM

JTAG & BPM

2

C24

C24

0.1U

0.1U

10

10

MISC

MISC

31

2

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

PM_THRMTRIP# 46

Q6

Q6

2N7002W-7-F

2N7002W-7-F

+1.1V_VTT

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

SM_RCOMP_0

AL1

SM_RCOMP_1

AM1

SM_RCOMP_2

AN1

AN15

AP15

AT28

XDP_PREQ#

AP27

XDP_TCLK

AN28

TCK

XDP_TMS

AP28

TMS

XDP_TRST#

AT27

XDP_TDI_R

AT29

TDI

XDP_TDO_R

AR27

TDO

XDP_TDI_M

AR29

XDP_TDO_M

AP29

H_DBR#_R

AN25

XDP_OBS0_R

AJ22

XDP_OBS1_R

AK22

XDP_OBS2_R

AK24

XDP_OBS3_R

AJ24

XDP_OBS4_R

AJ25

XDP_OBS5_R

AH22

XDP_OBS6_R

AK23

XDP_OBS7_R

AH23

DBR#:

SC(V1.0) P22:Connected to the DBR# pin of the Processor.50-Ω to 5-kΩ pull-up to 3.3VS

CRB(V1.0) P11,P71:CRB uses a 1-kΩ pull-up to 3.3VS.

On the CRB this signal is ANDed with Master Reset to generate SYS_RESET.

DBR#:(Intell fe edback)

Nothing wrong w / CRB design. I f you want to

connect it to PCH directly, make sure pull high

to 3.3V (S0) ma in power.

CLK_CPU_BCLK 10

CLK_CPU_BCLK# 10

BCLK_ITP 60

BCLK_ITP# 60

CLK_PCIE_3GPLL 9

CLK_PCIE_3GPLL# 9

DPLL_REF_SSCLK and DPLL_REF_SSCLK# can be connected to GND

on Auburndale d irectly if moth erboard

only supports d iscrete graphic s.

DDR3_DRAMRST# 13,14

R1065

R1065

*12.4K/F_NC

*12.4K/F_NC

+1.1V_VTT

PM_EXTTS#0 13

PM_EXTTS#1 14

XDP_DBRESET# 7,60

XDP_OBS[0:7] 60

R759 0R759 0

R758 0R758 0

R760 0R760 0

R761 0R761 0

R763 0R763 0

R764 0R764 0

R766 0R766 0

R767 0R767 0

R769 0R769 0

R752 10K/FR752 10K/F

R753 10K/FR753 10K/F

R754 0R754 0

R756 0R756 0

XDP_PRDY# 60

XDP_PREQ# 60

XDP_TCLK 60

XDP_TMS 60

XDP_TRST# 60

T186T186

T168T168

T169T169

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

JTAG MAPPING

XDP_TDI_R

XDP_TDO_M

XDP_TDI_M

XDP_TDO_R

Scan Chain

(Default)

CPU Only

GMCH Only

DG(v1.0) table 27

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

R780 0R780 0

R781 *0_NCR781 *0_NC

R7830R783

0

R785 *0_NCR785 *0_NC

R786 0R786 0

STUFF -> R780, R783, R786

NO STUFF -> R781, R785

STUFF -> R780, R781

NO STUFF -> R783, R785, R786

STUFF -> R785, R786

NO STUFF -> R780, R781, R783

TRST#

SC(V1.0)P22:

should be route d as a single

daisy chain to all loads and

terminated at the end of the trace.

51 Ω ± 5% pull down resistor.

CRB()V1.0)P11

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

AUBURNDA 1/4

AUBURNDA 1/4

AUBURNDA 1/4

FM9 1A

FM9 1A

FM9 1A

1

CRB(v0.71) P.11

2

XDP_TDI 60

XDP_TDO 60

XDP_TRST#

R78451R784

51

3 64Thursday, February 26, 2009

3 64Thursday, February 26, 2009

3 64Thursday, February 26, 2009

Page 4

5

4

3

2

1

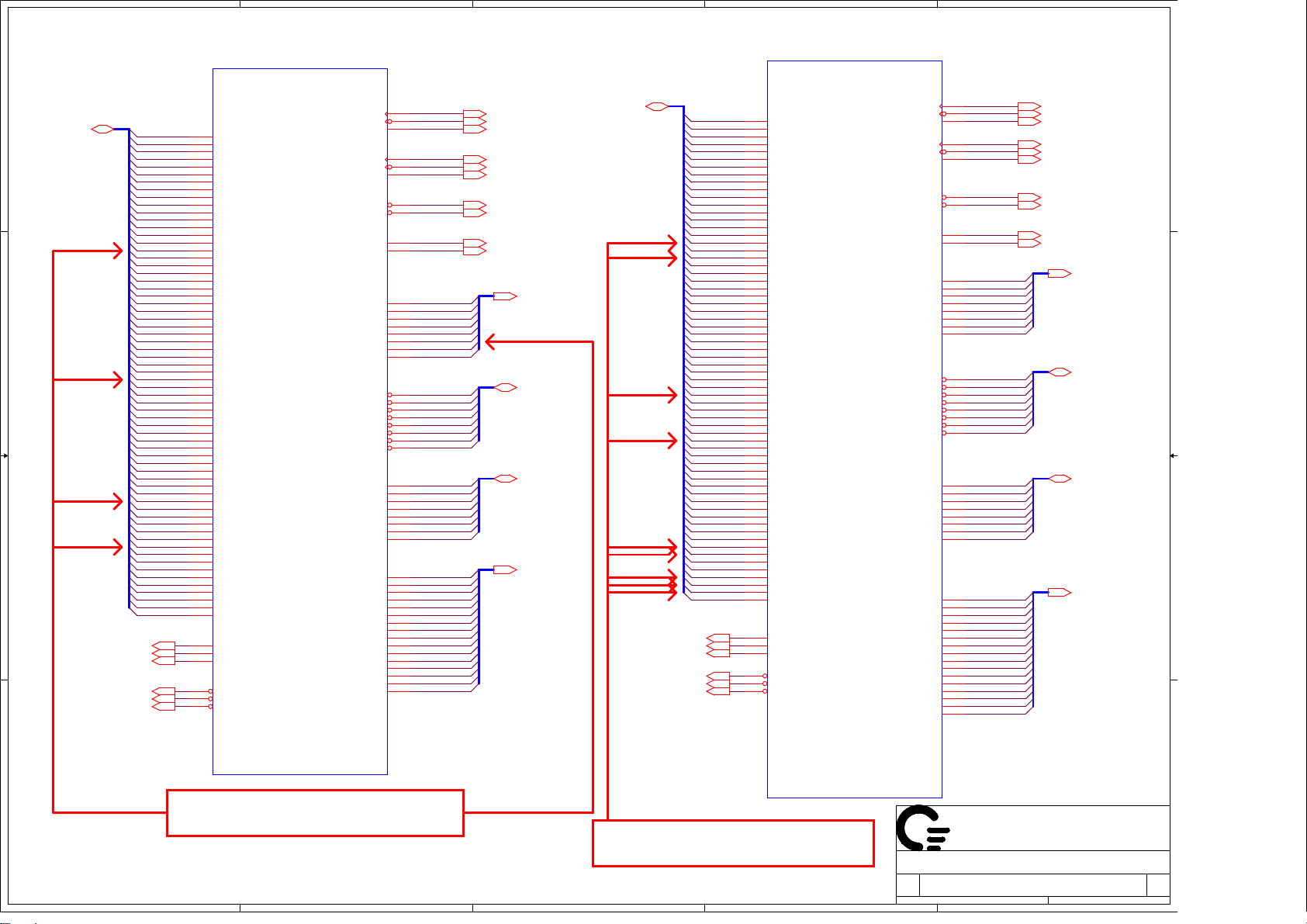

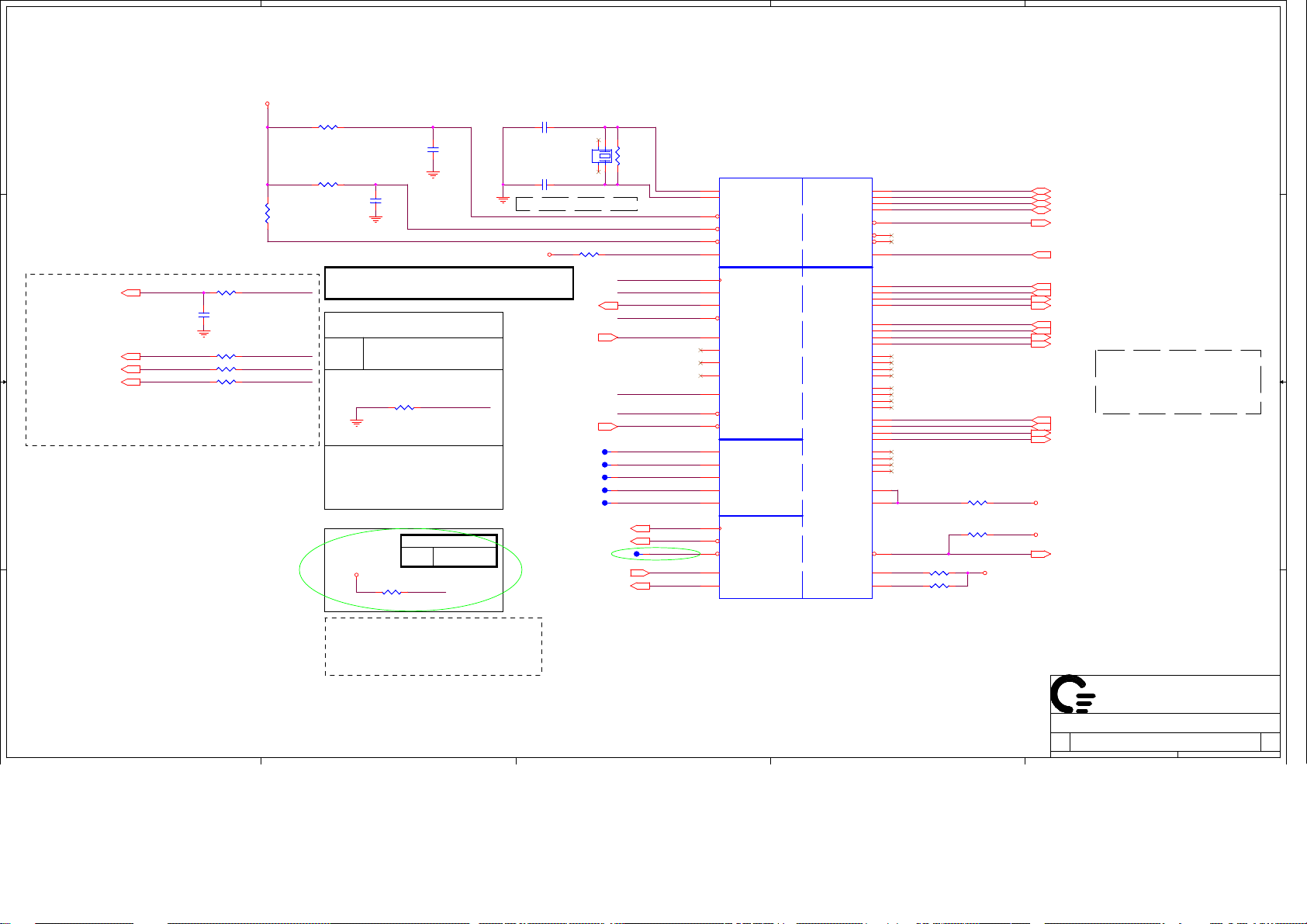

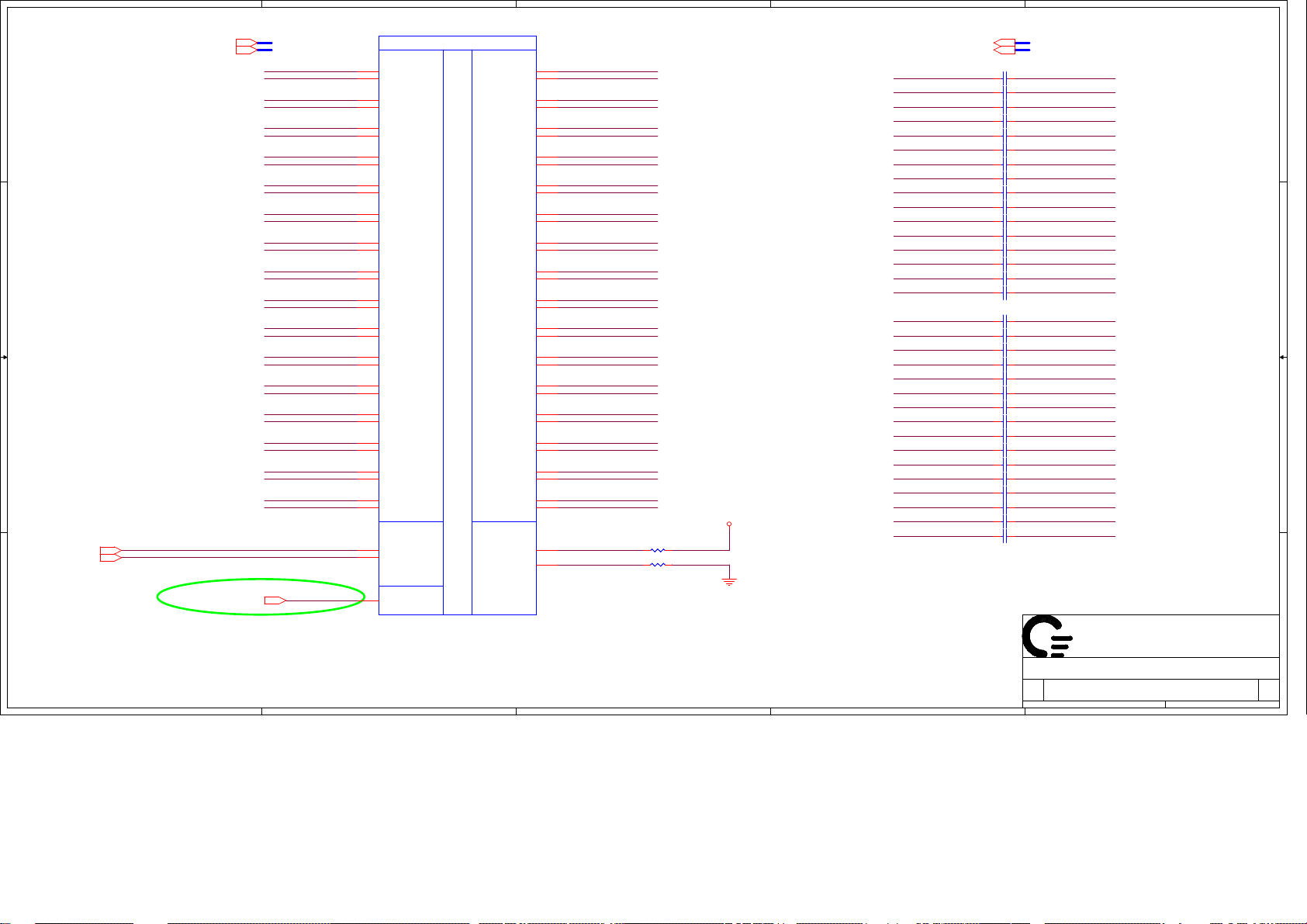

AUBURNDALE/CLARKSFIELD PROCESSOR (DDR3)

U3031D

AF3

AG1

AJ3

AK1

AG4

AG3

AJ4

AH4

AK3

AK4

AM6

AN2

AK5

AK2

AM4

AM3

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AR10

AT10

AB1

AC5

AC6

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

G1

G5

K2

M1

K5

K4

M4

N5

W5

R7

Y7

J6

J3

J2

J1

J5

L3

U3031D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

W8

SB_CK[0]

W9

SB_CK#[0]

M3

SB_CKE[0]

V7

SB_CK[1]

V6

SB_CK#[1]

M2

SB_CKE[1]

AB8

SB_CS#[0]

AD6

SB_CS#[1]

AC7

SB_ODT[0]

AD1

SB_ODT[1]

M_B_DM0

D4

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CLK0 14

M_B_CLK0# 14

M_B_CKE0 14

M_B_CLK1 14

M_B_CLK1# 14

M_B_CKE1 14

M_B_CS0# 14

M_B_CS1# 14

M_B_ODT0 14

M_B_ODT1 14

M_B_DM[7:0] 14

M_B_DQS#[7:0] 14

M_B_DQS[7:0] 14

M_B_A[15:0] 14

U3031C

U3031C

AA6

SA_CK[0]

D D

M_A_DQ[63:0]13

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS013

M_A_BS113

M_A_BS213

M_A_CAS#13

M_A_RAS#13

M_A_WE#13

C10

D10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

B10

E10

F10

J10

AJ7

AJ6

AJ9

AL7

AL8

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

G8

K7

J8

G7

J7

L7

M6

M8

L9

L6

K8

N8

P9

U7

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLK0 13

M_A_CLK0# 13

M_A_CKE0 13

M_A_CLK1 13

M_A_CLK1# 13

M_A_CKE1 13

M_A_CS0# 13

M_A_CS1# 13

M_A_ODT0 13

M_A_ODT1 13

M_A_DM[7:0] 13

M_A_DQS#[7:0] 13

M_A_DQS[7:0] 13

M_A_A[15:0] 13

M_B_DQ[63:0]14

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60M_A_A0

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS014

M_B_BS114

M_B_BS214

M_B_CAS#14

M_B_RAS#14

M_B_WE#14

Clarksfield/Auburndale

Clarksfield/Auburndale

A A

5

Channel A DQ[15,32,48,54], DM[5]

Requires minimum 12mils spacing

with all other signals, including data signals.

4

Channel B DQ[16,18,36,42,56,57,60,61,62]

Requires minimum 12mils spacing

with all other signals, including data signals.

3

Clarksfield/Auburndale

Clarksfield/Auburndale

2

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

COMPUTER

AUBURNDA 2/4

AUBURNDA 2/4

AUBURNDA 2/4

FM9 1A

FM9 1A

FM9 1A

4 64Thursday, February 26, 2009

4 64Thursday, February 26, 2009

4 64Thursday, February 26, 2009

1

Page 5

5

U3031F

CPU Core Power

+VCC_CORE

D D

C C

B B

A A

U3031F

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

Clarksfield/Auburndale

Clarksfield/Auburndale

AH14

VTT0_1

AH12

VTT0_2

AH11

VTT0_3

AH10

VTT0_4

J14

VTT0_5

J13

VTT0_6

H14

VTT0_7

H12

VTT0_8

G14

VTT0_9

G13

VTT0_10

G12

VTT0_11

G11

VTT0_12

F14

VTT0_13

F13

VTT0_14

F12

VTT0_15

F11

VTT0_16

E14

VTT0_17

E12

VTT0_18

D14

VTT0_19

D13

VTT0_20

D12

VTT0_21

D11

VTT0_22

C14

VTT0_23

C13

VTT0_24

C12

VTT0_25

C11

VTT0_26

B14

VTT0_27

B12

VTT0_28

A14

VTT0_29

A13

VTT0_30

A12

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

+VTT_43

J16

+VTT_44

J15

VTT0_43,VTT0_44:

CRB(V1.0)P13

Why add 0ohm?? Is it trace width control??

VTT0_43,VTT0_44:(Intel feedback)

They are connected to hidden page for

intel validation purpose.

AN33

PSI#

VID0

AK35

VID1

AK33

VID2

AK34

VID3

AL35

VID4

AL33

VID5

AM33

VID6

AM35

DPRSLPVR

AM34

G15

AN35

AJ34

AJ35

B15

TP_VSS_SENSE_VTT

A15

VSS_SENSE_VTT:

SC(V1.0)P20

Connect VSS_SENSE_VTT to GND

or can be left floating.

Note: CRB has the VSS_SENSE_VTT floating.

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

AUBURNDALE/CLARKSFIELD PROCESSOR (POWER)

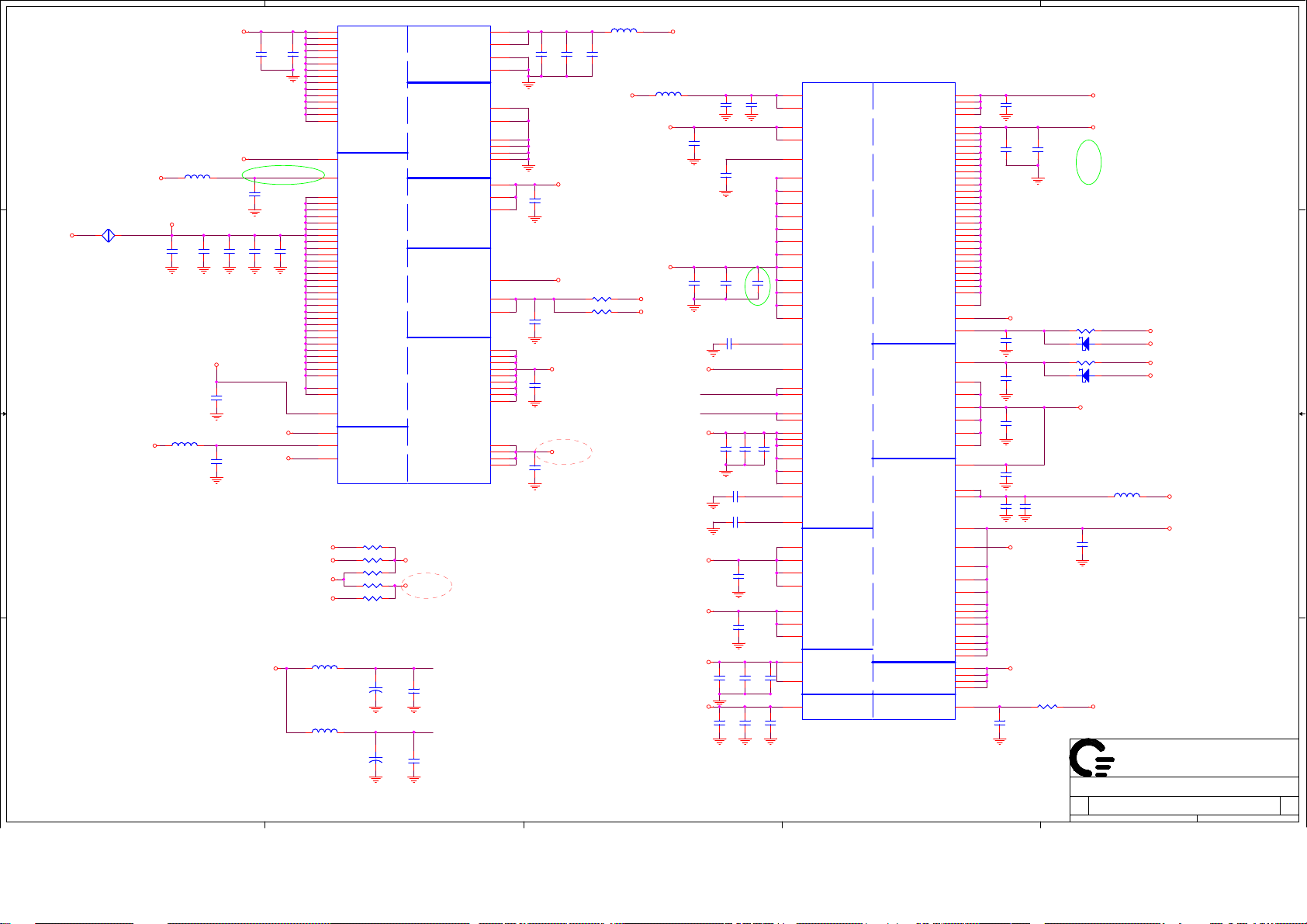

5

C1207

C1207

10U

10U

C1234

C1234

22U

22U

4

C1208

C1208

10U

10U

C1235

C1235

22U

22U

H_PSI# 51

VID0 51

VID1 51

VID2 51

VID3 51

VID4 51

VID5 51

VID6 51

DPRSLPVR 51

H_VTTVID1 49

I_MON 51

VTT_SENSE 49

T196T196

4

+1.1V_VTT

C1212

C1209

C1209

10U

10U

C1210

C1210

10U

10U

+1.1V_VTT

C1211

C1211

10U

10U

C1212

10U

10U

+1.1V_VTT

C1213

C1213

10U

10U

C1217

C1217

22U

22U

C1214

C1214

*10U_NC

*10U_NC

+1.1V_VTT

C1222

C1222

22U

22U

3

C1237

C1237

22U

22U

C1269

C1270

C1270

22U

22U

22U

22U

VTT_SELECT:

High level 1.05V for Auburndale

Low level 1.1V for Clarksfield

+VCC_CORE

VCC_SENSE & VSS_SENSE:

SC(V1.0)P19

R807

R807

100- ±1% pull-down to GND near processor

100/F

100/F

VCCSENSE 51

VSSSENSE 51

R819

R819

100/F

100/F

PROC_DPRSLPVR:

SC(V1.0)P19:

It is important to have the resistor stuffing options

in the design f or the Turbo fu nctionality.

The stuffing an d no-stuffing o f the resistors

will depend on the POC configu ration of AUB

and CFD

CRB(V1.0)P67:

uses 1K pull-up and pull-down resistors

CRB default set ting is "1"

C1273

C1273

22U

22U

C1215

C1215

*10U_NC

*10U_NC

C1223

C1223

22U

22U

C1238

C1238

22U

22U

3

AUBURNDALE/CLARKSFIELD PROCESSOR (GRAPHICS POWER)

U3031G

U3031G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

C1274

C1274

22U

22U

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

Clarksfield/Auburndale

Clarksfield/Auburndale

Note:

For Validating IMVP VR R814 should be STUFF

and R827 NO_STUFF

3

2

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

R8101KR810

1K

R820

R820

*1K_NC

*1K_NC

R8111KR811

1K

R821

R821

*1K_NC

*1K_NC

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

R803 *1K/F_NCR803 *1K/F_NC

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

R8121KR812

1K

R822

R822

*1K_NC

*1K_NC

+1.1V_VTT

R813

R813

*1K_NC

*1K_NC

R8231KR823

1K

4

GFX_VID[0..6],GFX_VR_EN,GFX_DPRSLPVR,GFX_IMON:

Could this be left unconnected when not in use?

GFX_VID[0..6],GFX_VR_EN,GFX_DPRSLPVR,GFX_IMON:(Intel feedback)

Yes, see DG rev1.5

+1.5V_SUS

C1248

C1248

10U

10U

C1272

C1272

22U

22U

C12191UC1219

1U

C1277

C1277

2.2U

2.2U

R816

R816

*1K_NC

*1K_NC

R8261KR826

1K

+

+

+

+

C1258

C1258

*330U_NC

*330U_NC

7343

7343

2.5

2.5

C12201UC1220

1U

C1224

C1224

330U

330U

7343

7343

2.5

2.5

+1.1V_VTT

+1.8V_RUN

C1278

C1278

4.7U

4.7U

R8171KR817

1K

R827

R827

*1K_NC

*1K_NC

C12211UC1221

1U

C1225

C1225

22U

22U

C1279

C1279

22U

22U

R818

R818

*1K_NC

*1K_NC

R8281KR828

1K

+VCC_CORE

C1226

C1226

22U

22U

C1227

C1227

22U

22U

C1239

C1239

22U

22U

C1250

C1250

C1249

C1249

10U

10U

10U

10U

C1262

C1262

C1261

C1261

10U

10U

10U

10U

+

+

+

+

C1507

C1507

*470U_NC

*470U_NC

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

COMPUTER

AUBURNDA 3/4

AUBURNDA 3/4

AUBURNDA 3/4

FM9 1A

FM9 1A

FM9 1A

C12161UC1216

1U

C12751UC1275

1U

R814

R814

*1K_NC

*1K_NC

R8241KR824

1K

C1247

C1247

10U

10U

C1271

C1271

22U

22UC1269

2

C12181UC1218

1U

C12761UC1276

1U

R8151KR815

1K

R825

R825

*1K_NC

*1K_NC

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GRAPHICS

GRAPHICS

GFX_DPRSLPVR

GRAPHICS VIDs

GRAPHICS VIDs

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

VID0

VID1

VID2

VID3

VID4

VID5

VID6

DPRSLPVR

H_PSI#

C1228

C1228

22U

22U

C1240

C1240

22U

22U

C1251

C1251

10U

10U

C1263

C1263

10U

10U

C1508

C1508

*470U_NC

*470U_NC

C1229

C1229

22U

22U

C1241

C1241

22U

22U

C1252

C1252

10U

10U

C1264

C1264

10U

10U

1

C1231

C1231

C1232

C1230

C1230

22U

22U

C1242

C1242

22U

22U

C1254

C1254

C1253

C1253

10U

10U

10U

10U

C1265

C1265

C1266

C1266

10U

10U

10U

10U

1

C1232

22U

22U

22U

22U

C1243

C1243

C1244

C1244

22U

22U

22U

22U

C1256

C1256

C1255

C1255

10U

10U

10U

10U

C1267

C1267

C1268

C1268

10U

10U

10U

10U

5 64Thursday, February 26, 2009

5 64Thursday, February 26, 2009

5 64Thursday, February 26, 2009

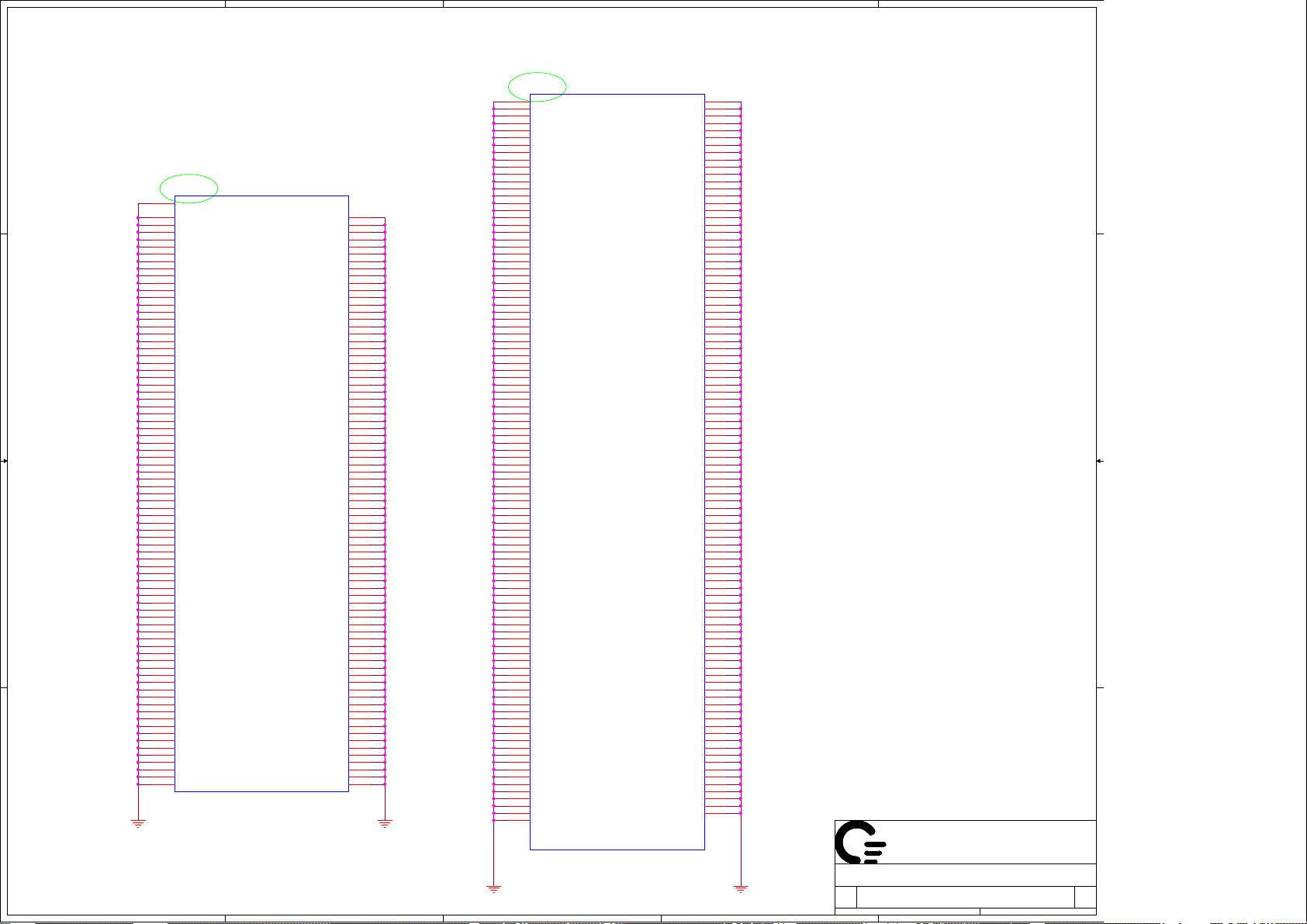

Page 6

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (GND) AUBURNDALE/CLARKSFIELD PROCESSOR( RESERVED, CFG)

U3031H

U3031H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

VSS8

AR17

D D

C C

B B

VSS9

AR15

VSS10

AR12

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

AP20

VSS15

AP17

VSS16

AP13

VSS17

AP10

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

AN34

VSS22

AN31

VSS23

AN23

VSS24

AN20

VSS25

AN17

VSS26

AM29

VSS27

AM27

VSS28

AM25

VSS29

AM20

VSS30

AM17

VSS31

AM14

VSS32

AM11

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

AL34

VSS37

AL31

VSS38

AL23

VSS39

AL20

VSS40

AL17

VSS41

AL12

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

AK29

VSS46

AK27

VSS47

AK25

VSS48

AK20

VSS49

AK17

VSS50

AJ31

VSS51

AJ23

VSS52

AJ20

VSS53

AJ17

VSS54

AJ14

VSS55

AJ11

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

AH35

VSS60

AH34

VSS61

AH33

VSS62

AH32

VSS63

AH31

VSS64

AH30

VSS65

AH29

VSS66

AH28

VSS67

AH27

VSS68

AH26

VSS69

AH20

VSS70

AH17

VSS71

AH13

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

AG10

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

AE35

VSS80

Clarksfield/Auburndale

Clarksfield/Auburndale

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

U3031I

U3031I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

Clarksfield/Auburndale

Clarksfield/Auburndale

VSS

VSS

NCTF

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

+M_VREF_DQ_DIMM0

+M_VREF_DQ_DIMM1

R833 0R833 0

R834 0R834 0

CFG0

CFG3

CFG4

CFG7

TP_RSVD17_R

TP_RSVD18_R

U3031E

U3031E

AP25

RSVD1

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

J17

SA_DIMM_VREF

H17

SB_DIMM_VREF

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

AL32

CFG[3]

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]

AN30

CFG[12]

AN32

CFG[13]

AJ32

CFG[14]

AJ29

CFG[15]

AJ30

CFG[16]

AK30

CFG[17]

H16

RSVD_TP_86

B19

RSVD15

A19

RSVD16

A20

RSVD17

B20

RSVD18

U9

RSVD19

T9

RSVD20

AC9

RSVD21

AB9

RSVD22

C1

RSVD_NCTF_23

A3

RSVD_NCTF_24

J29

RSVD26

J28

RSVD27

A34

RSVD_NCTF_28

A33

RSVD_NCTF_29

C35

RSVD_NCTF_30

B35

RSVD_NCTF_31

Clarksfield/Auburndale

Clarksfield/Auburndale

RESERVED

RESERVED

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD_NCTF_37

RSVD38

RSVD39

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD58

RSVD_TP_59

RSVD_TP_60

KEY

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

VSS

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

RSVD64_R

RSVD65_R

Can be left NC is Intel CRM

R8390R839

implementation; ESD/DG

0

recommendation to GND

R831 0R831 0

R832 0R832 0

1 0

CFG4

A A

The Clarkfield processor's PCI Express interface may

not meet PCI Express 2.0 jitter specifications. Intel

recommends placing a 3.01K +/- 5% pull down resistor to

VSS on CFG[7] pin for both rPGA and BGA components.

This pull down resistor should be removed when this

issue is fixed.

CFG4

CFG0

CFG3

CFG7

R835 *3.01K/F_NCR835 *3.01K/F_NC

R836 *3.01K/F_NCR836 *3.01K/F_NC

R837 3.01K/FR837 3.01K/F

R838 *3.01K/F_NCR838 *3.01K/F_NC

PCIE LANE is Lane Numbers Reversed

5

4

(Display Port

Presence)

CFG0

(PCI-Epress

Configuration Select)

CFG3

(PCI-Epress Static

Lane Reversal)

Disabled; No Physical Display Port

attached to Embedded Diplay Port

Single PEG

Normal Operation Lane Numbers Reversed

3

Enabled; An external Display port

device is connected to the Embedded

Display port

Bifurcation enabled

2

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

COMPUTER

AUBURNDA 4/4

AUBURNDA 4/4

AUBURNDA 4/4

FM9 1A

FM9 1A

FM9 1A

1

6 64Thursday, February 26, 2009

6 64Thursday, February 26, 2009

6 64Thursday, February 26, 2009

Page 7

5

4

3

2

1

IBEX PEAK-M (DMI,FDI,GPIO)

U3035C

U3035C

DMI_RXN03

D D

CS(V1.0) P32

PWROK and SYS_PWROK should be tied

together on the platform.MEPWROK can be connected

C C

to PCH_PWROK pin on PCH when Intel AMT

is not enabled.

B B

MEPWROK

SC(V1.0)P32:

It can be connected to PCH_PWROK pin

on PCH when Intel AMT is not enabled.

A A

DMI_RXN13

DMI_RXN23

DMI_RXN33

DMI_RXP03

DMI_RXP13

DMI_RXP23

DMI_RXP33

DMI_TXN03

DMI_TXN13

DMI_TXN23

DMI_TXN33

DMI_TXP03

DMI_TXP13

DMI_TXP23

DMI_TXP33

+1.05V_VCCIO

XDP_DBRESET#3,60

PCH_PWRGD29

PM_DRAM_PW RGD3

ICH_RSMRST#29

SUS_PWR_ACK29

SIO_PWRBTN#29

AC_PRESENT29

CLKRUN#

PCH_PWRGD

ICH_RSMRST#

LAN_RST#

LAN_RST#

DG(V1.0) P311

If integrated LAN is not used, recommend

to connect LAN_RST# to GND via an 8.2-kΩ

to 10-kΩ pull-down resistor.

EDS(V1.0)P64

must be grounded if Intel LAN is disabled.

R842 49.9/FR842 49.9/F

R1062 0R1062 0

R1063 0R1063 0

R846 0R846 0

+3.3V_RUN

R580 10K/FR580 10K/F

R1075 10K/FR1075 10K/F

R861 10K/FR861 10K/F

R1013 10K/FR1013 10K/F

5

DMI_ZCOMP

SYS_PWROK

PWROK

MEPWROK

LAN_RST#

ICH_RSMRST#

PM_BATLOW#

PM_RI#

BC24

DMI0RXN

BJ22

DMI1RXN

AW20

DMI2RXN

BJ20

DMI3RXN

BD24

DMI0RXP

BG22

DMI1RXP

BA20

DMI2RXP

BG20

DMI3RXP

BE22

DMI0TXN

BF21

DMI1TXN

BD20

DMI2TXN

BE18

DMI3TXN

BD22

DMI0TXP

BH21

DMI1TXP

BC20

DMI2TXP

BD18

DMI3TXP

BH25

DMI_ZCOMP

BF25

DMI_IRCOMP

T6

SYS_RESET#

M6

SYS_PWROK

B17

PWROK

K5

MEPWROK

A10

LAN_RST#

D9

DRAMPWROK

C16

RSMRST#

M1

SUS_PWR_DN_ACK / GPIO30

P5

PWRBTN#

P7

ACPRESENT / GPIO31

A6

BATLOW# / GPIO72

F14

RI#

IbexPeak-M_R1P0

IbexPeak-M_R1P0

PM_RI#

PCIE_WAKE#

PWROK

SC(V1.0)P32:

8.2 kΩ to 10 kΩ pull-down resistor to GND.

PWROK and SYS_PWROK should be tied together on the platform.

R858 10K/FR858 10K/F

R860 1KR860 1K

System Power Management

System Power Management

+3.3V_SUS

4

DMI

FDI

DMI

FDI

CLKRUN# / GPIO32

SUS_STAT# / GPIO61

SUSCLK / GPIO62

SLP_S5# / GPIO63

SLP_LAN# / GPIO29

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

BA18

FDI_RXN0

FDI_RXN1

FDI_RXN2

FDI_RXN3

FDI_RXN4

FDI_RXN5

FDI_RXN6

FDI_RXN7

FDI_RXP0

FDI_RXP1

FDI_RXP2

FDI_RXP3

FDI_RXP4

FDI_RXP5

FDI_RXP6

FDI_RXP7

FDI_INT

WAKE#

SLP_S4#

SLP_S3#

SLP_M#

TP23

PMSYNCH

PM_BATLOW#

PM_BATLOW#:

EDS(V1.0)P95: 15K~40K (+3.3V_SUS)

CRB(V1.0)P25: 8.2K (+3.3V_ALW)

PM_BATLOW#:(Intel feedback)

15K ~ 40K is a simulation result,

the expected value should be 20K

internal pull high in PCH.

8.2K is external pull high.

DG(V1.0)P185:

BH17

BD16

If the LVDS interface is not implemented,

BJ16

all signals associated with the interface can

BA16

be left as No Connects. The supply pins

BE14

VccTX_LVDS and VCCA_LVD can be

BA14

connected to ground.

BC12

DG(V1.1) P83:FDI_FSYNC[0], FDI_FSYNC[1],

BB18

FDI_LSYNC[0], FDI_LSYNC[1], and FDI_INT

BF17

signals on PCH side can be left as

BC16

no connect without any power

BG16

or functional impact.

AW16

BD14

BB14

BD12

BJ14

BF13

BH13

BJ12

BG14

J12

CLKRUN#

Y1

RSV_LPCPD#

P8

ICH_SUSCLK

F3

SLP_S5#_R

E4

SLP_S4#_R

H7

SLP_S3#_R

P12

SLP_M#_R

K8

N2

BJ10

PM_SLP_LAN#_R

F6

R859 8.2K/FR859 8.2K/F

T221T221

T222T222

R1073 0R1073 0

R1074 0R1074 0

T223T223

T224T224

T225T225

+3.3V_SUS

PCIE_WAKE# 28,31,32,41

CLKRUN# 29

SIO_SLP_S5# 29

SIO_SLP_S4# 13

SIO_SLP_S3# 29

PM_SYNC 3

5

3

DG(V1.0)P189:

If the CRT interface is not implemented,

all signals associated with the interface can

be left as No Connects. The pins

CRT_IRTN Connect this signals to GND

and DAC_IREF Connect to GND

via a 1.0 k ±0.5% pull-down resistor

R8561KR856

1K

IBEX PEAK-M (LVDS,DDI)

U3035D

U3035D

Y48

AB48

Y45

AB46

V48

AP39

AP41

AT43

AT42

AV53

AV51

BB47

BA52

AY48

AV47

BB48

BA50

AY49

AV48

AP48

AP47

AY53

AT49

AU52

AT53

AY51

AT48

AU50

AT51

AA52

AB53

AD53

V51

V53

Y53

Y51

AD48

AB51

T48

T47

L_BKLTEN

L_VDD_EN

L_BKLTCTL

L_DDC_CLK

L_DDC_DATA

L_CTRL_CLK

L_CTRL_DATA

LVD_IBG

LVD_VBG

LVD_VREFH

LVD_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSA_DATA#0

LVDSA_DATA#1

LVDSA_DATA#2

LVDSA_DATA#3

LVDSA_DATA0

LVDSA_DATA1

LVDSA_DATA2

LVDSA_DATA3

LVDSB_CLK#

LVDSB_CLK

LVDSB_DATA#0

LVDSB_DATA#1

LVDSB_DATA#2

LVDSB_DATA#3

LVDSB_DATA0

LVDSB_DATA1

LVDSB_DATA2

LVDSB_DATA3

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_VSYNC

DAC_IREF

CRT_IRTN

IbexPeak-M_R1P0

IbexPeak-M_R1P0

SDVO_TVCLKINN

SDVO_TVCLKINP

SDVO_STALLN

SDVO_STALLP

SDVO_CTRLCLK

SDVO_CTRLDATA

DDPB_AUXN

DDPB_AUXP

LVDS

LVDS

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPC_AUXN

DDPC_AUXP

Digital Display Interface

Digital Display Interface

DDPD_CTRLCLK

DDPD_CTRLDATA

DDPD_AUXN

DDPD_AUXP

CRT

CRT

2

BJ46

BG46

BJ48

BG48

BF45

SDVO_INTN

BH45

SDVO_INTP

T51

T53

BG44

BJ44

AU38

DDPB_HPD

BD42

DDPB_0N

BC42

DDPB_0P

BJ42

DDPB_1N

BG42

DDPB_1P

BB40

DDPB_2N

BA40

DDPB_2P

AW38

DDPB_3N

BA38

DDPB_3P

Y49

AB49

BE44

BD44

AV40

DDPC_HPD

BE40

DDPC_0N

BD40

DDPC_0P

BF41

DDPC_1N

BH41

DDPC_1P

BD38

DDPC_2N

BC38

DDPC_2P

BB36

DDPC_3N

BA36

DDPC_3P

U50

U52

BC46

BD46

AT38

DDPD_HPD

BJ40

DDPD_0N

BG40

DDPD_0P

BJ38

DDPD_1N

BG38

DDPD_1P

BF37

DDPD_2N

BH37

DDPD_2P

BE36

DDPD_3N

BD36

DDPD_3P

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

SDVO

Display port BDisplay port CDisplay port D

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

IBEX PEAK-M 2/6

IBEX PEAK-M 2/6

IBEX PEAK-M 2/6

FM9 1A

FM9 1A

FM9 1A

7 64Thursday, February 26, 2009

7 64Thursday, February 26, 2009

7 64Thursday, February 26, 2009

1

Page 8

5

4

3

2

1

C1284

C1284

*27P_NC

*27P_NC

50

50

+RTC_CELL

ACZ_BIT_CLK

ACZ_SYNC

ACZ_RST#

ACZ_SDOUT

R8671MR867

1M

R864 20K/FR864 20K/F

C12821UC1282

1U

R865 20K/FR865 20K/F

C12811UC1281

1U

INTVRMEN(Internal Voltage Regulator Enable) :

This signal enables the internal 1.05 V regulators.

This signal must be always pulled-up to VccRTC.

Flash Descriptor Security Override

Low = Enabled

GPIO33

High = Disabled

R503 *10K/F_NCR503 *10K/F_NC

1 2

GPIO33

(Internal 20K/F pull high to +3.3V_RUN)

Note : GPIO33 is a signal used for Flash

Descriptor Security Override/ME Debug

Mode.This signal should be only asserted

lowthrough an external pull-down in

manufacturing or debug environments

ONLY.

No Reboot strap.

Low = Default.

SPKR

+3.3V_RUN

1 2

R221 *1K_NCR221 *1K_NC

High = No Reboot.

SPKR

C1280

C1280

18PF

18PF

Y5

32.768KHZY532.768KHZ

C1283

C1283

18PF

18PF

Cap values depend on Xtal

+RTC_CELL

R868 330KR868 330K

SPKR39

ICH_AZ_CODEC_SDIN039

KB_LED_DET36

T183T183

T180T180

T178T178

T174T174

T175T175

23

SPI_CLK30

SPI_CS0#30

SPI_SI30

4 1

T185T185

SPI_SO30

R866

R866

10M

10M

RTC_X1

RTC_X2

RTC_RST#

SRTC_RST#

SM_INTRUDER#

PCH_INVRMEN

ACZ_BIT_CLK

ACZ_SYNC

SPKR

ACZ_RST#

ACZ_SDOUT

GPIO33

PCH_JTAG_TCK_BUF

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_RST#

IBEX PEAK-M (HDA,JTAG,SATA)

U3035A

U3035A

SPI_CLK

SPI_CS0#

SPI_CS1#

SPI_SI

SPI_SO

B13

RTCX1

D13

RTCX2

C14

RTCRST#

D17

SRTCRST#

A16

INTRUDER#

A14

INTVRMEN

A30

HDA_BCLK

D29

HDA_SYNC

P1

SPKR

C30

HDA_RST#

G30

HDA_SDIN0

F30

HDA_SDIN1

E32

HDA_SDIN2

F32

HDA_SDIN3

B29

HDA_SDO

H32

HDA_DOCK_EN# / GPIO33

J30

HDA_DOCK_RST# / GPIO13

M3

JTAG_TCK

K3

JTAG_TMS

K1

JTAG_TDI

J2

JTAG_TDO

J4

TRST#

BA2

SPI_CLK

AV3

SPI_CS0#

AY3

SPI_CS1#

AY1

SPI_MOSI

AV1

SPI_MISO

IbexPeak-M_R1P0

IbexPeak-M_R1P0

RTCIHDA

RTCIHDA

SPI JTAG

SPI JTAG

FWH4 / LFRAME#

LDRQ1# / GPIO23

LPC

LPC

SATA

SATA

SATA0GP / GPIO21

SATA1GP / GPIO19

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

LDRQ0#

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATALED#

D33

B33

C32

A32

C34

A34

F34

AB9

AK7

AK6

AK11

AK9

AH6

AH5

AH9

AH8

AF11

AF9

AF7

AF6

AH3

AH1

AF3

AF1

AD9

AD8

AD6

AD5

AD3

AD1

AB3

AB1

AF16

AF15

T3

Y9

V1

SATA port 2/3 are not support in HM55 .

They are only in PM 55

SATA_COMP

SATA_ACT#

R881 10K/FR881 10K/F

1 2

R882 10K/FR882 10K/F

1 2

R877 37.4/FR877 37.4/F

R51 100KR51 100K

+3.3V_RUN

+1.05V_PCH

+3.3V_RUN

LPC_LAD0 29,32

LPC_LAD1 29,32

LPC_LAD2 29,32

LPC_LAD3 29,32

LPC_LFRAME# 29,32

IRQ_SERIRQ 29

SATA_RX0- 35

SATA_RX0+ 35

SATA_TX0- 35

SATA_TX0+ 35

SATA_RX1- 35

SATA_RX1+ 35

SATA_TX1- 35

SATA_TX1+ 35

SATA_RX4- 33

SATA_RX4+ 33

SATA_TX4- 33

SATA_TX4+ 33

SATA_ACT# 29

SATA HDD

SATA ODD

Distance between the PCH and

cap on the "P" signal should be

identical distace between the

PCH and cap on the "N" signal

for the same pair.

E-SATA

D D

C C

ICH_AZ_CODEC_BITCLK39

ICH_AZ_CODEC_SYNC39

ICH_AZ_CODEC_RST #29,39

ICH_AZ_CODEC_SDOUT39

Place all series terms close to PCH except for SDIN input

lines,which should be close to source.Placement of R773, R775,

R776 & R777 should equal distance to the T split trace point.

Basically, keep the same distance from T for all series

termination resistors.

B B

R869 33R869 33

R871 33R871 33

R872 33R872 33

R873 33R873 33

JTAG

Test Pads are need to put on

A A

5

the same side of mother board.

4

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

COMPUTER

IBEX PEAK-M 1/6

IBEX PEAK-M 1/6

IBEX PEAK-M 1/6

FM9 1A

FM9 1A

FM9 1A

1

8 64Thursday, February 26, 2009

8 64Thursday, February 26, 2009

8 64Thursday, February 26, 2009

Page 9

5

4

3

2

1

IBEX PEAK-M (PCI,USB,NVRAM)

Place TX DC blocking caps close PCH.

U3035E

U3035E

H40

AD0

N34

AD1

C44

AD2

A38

AD3

C36

AD4

J34

AD5

A40

AD6

D45

D D

PCI_PIRQA#

T172T172

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

T173T173

C C

USB_MCARD1_DET#32

GNT3#10

PCH_IRQH_GPIO535

PCIRST#:

DG(V1.0) P277

Can be left unconnected.

PAR:

SC(V1.0) P36

Can be left unconnected

if not using PCI.

PME:

DG(V1.0) P277

Can be left unconnected.

CLK_LPC_DEBUG32

B B

CLK_PCI_851229

CLKOUT_PCI[0..4]:

22 ohm series resistor is recommend

(single & double load) on PDG v1.1

Reserve capacitor pads for

improving WWAN.

CLK_LPC_DEBUG

CLK_PCI_8512

0214

R892 22/FR892 22/F

R896 22/FR896 22/F

CLK_PCI_FB CLK_PCI_FB_C

R898 22/FR898 22/F

50

50

C1287 *27P_NC

C1287 *27P_NC

50

50

C1289 *27P_NC

C1289 *27P_NC

Non-iAMT

A A

C1290 0.047U

C1290 0.047U

PCI_PLTRST#

10

10

PCI_REQ0#

REQ1#

T234T234

SB_WWAN_PCIE_RST#

T239T239

USB_MCARD1_DET#

PCI_GNT0#

GNT#1

T235T235

GNT#2

T236T236

SB_WPAN_PCIE_RST#

T240T240

SB_WLAN_PCIE_RST#

T241T241

PIRQG#

T243T243

PCH_IRQH_GPIO5

PCI_RST#

T237T237

PCI_SERR#

PCI_PERR#

PCI_IRDY#

PCI_DEVSEL#

PCI_FRAME#

PCI_PLOCK#

PCI_STOP#

PCI_TRDY#

PME#

T238T238

PCI_PLTRST#

CLK_LPC_DEBUG_C

CLK_PCI_8512_C

RSV_SMBALERT#

RSV_ICH_CL_RST1#

ICH_SMBCLK

ICH_SMBDATA

SMB_CLK_ME0

SMB_DATA_ME0

SMB_CLK_ME1

SMB_DATA_ME1

LPD_SPI_INTR#

PEG_CLKREQ#

Add Buffers as needed for

Loading and fanout concerns.

+3.3V_SUS

5

U56

U56

2

1

5

4

TC7SZ32FU(T5L,F,T)

TC7SZ32FU(T5L,F,T)

AD7

E36

AD8

H48

AD9

E40

AD10

C40

AD11

M48

AD12

M45

AD13

F53

AD14

M40

AD15

M43

AD16

J36

AD17

K48

AD18

F40

AD19

C42

AD20

K46

AD21

M51

AD22

J52

AD23

K51

AD24

L34

AD25

F42

AD26

J40

AD27

G46

AD28

F44

AD29

M47

AD30

H36

AD31

J50

C/BE0#

G42

C/BE1#

H47

C/BE2#

G34

C/BE3#

G38

PIRQA#

H51

PIRQB#

B37

PIRQC#

A44

PIRQD#

F51

REQ0#

A46

REQ1# / GPIO50

B45

REQ2# / GPIO52

M53

REQ3# / GPIO54

F48

GNT0#

K45

GNT1# / GPIO51

F36

GNT2# / GPIO53

H53

GNT3# / GPIO55

B41

PIRQE# / GPIO2

K53

PIRQF# / GPIO3

A36

PIRQG# / GPIO4

A48

PIRQH# / GPIO5

K6

PCIRST#

E44

SERR#

E50

PERR#

A42

IRDY#

H44

PAR

F46

DEVSEL#

C46

FRAME#

D49

PLOCK#

D41

STOP#

C48

TRDY#

M7

PME#

D5

PLTRST#

N52

CLKOUT_PCI0

P53

CLKOUT_PCI1

P46

CLKOUT_PCI2

P51

CLKOUT_PCI3

P48

CLKOUT_PCI4

IbexPeak-M_R1P0

IbexPeak-M_R1P0

+3.3V_SUS

R90010K/F R90010K/F

R90210K/F R90210K/F

R9032.2K/F R9032.2K/F

R9052.2K/F R9052.2K/F

R9072.2K/F R9072.2K/F

R9102.2K/F R9102.2K/F

R9112.2K/F R9112.2K/F

R91310K/F R91310K/F

R91610K/F R91610K/F

PLTRST# 3,16,26,28,29,31,32,41

NV_DQ0 / NV_IO0

NV_DQ1 / NV_IO1

NV_DQ2 / NV_IO2

NV_DQ3 / NV_IO3

NV_DQ4 / NV_IO4

NV_DQ5 / NV_IO5

NV_DQ6 / NV_IO6

NV_DQ7 / NV_IO7

NV_DQ8 / NV_IO8

NV_DQ9 / NV_IO9

NV_DQ10 / NV_IO10

NV_DQ11 / NV_IO11

NVRAM

NVRAM

NV_DQ12 / NV_IO12

NV_DQ13 / NV_IO13

NV_DQ14 / NV_IO14

NV_DQ15 / NV_IO15