Page 1

5

4

3

2

1

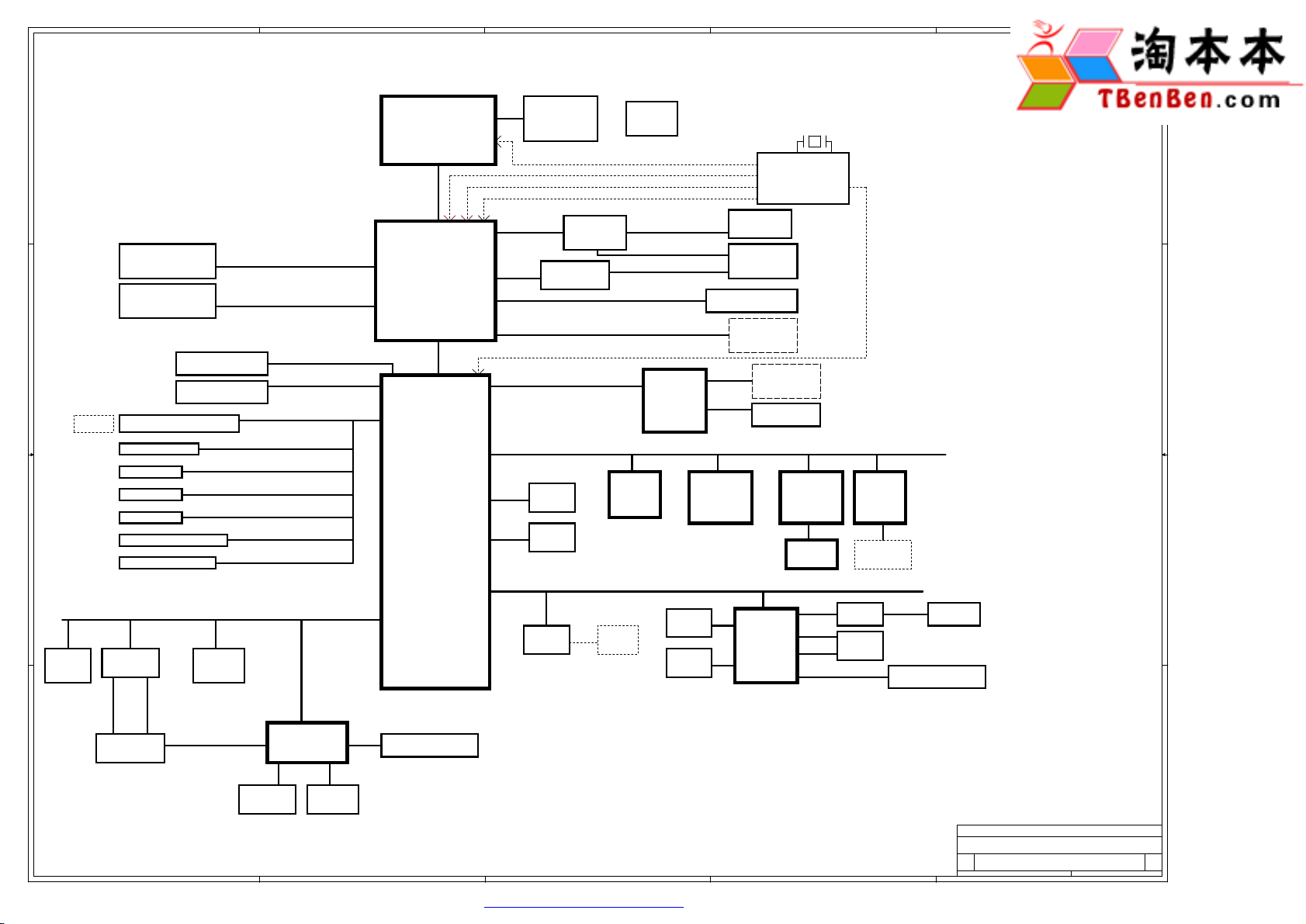

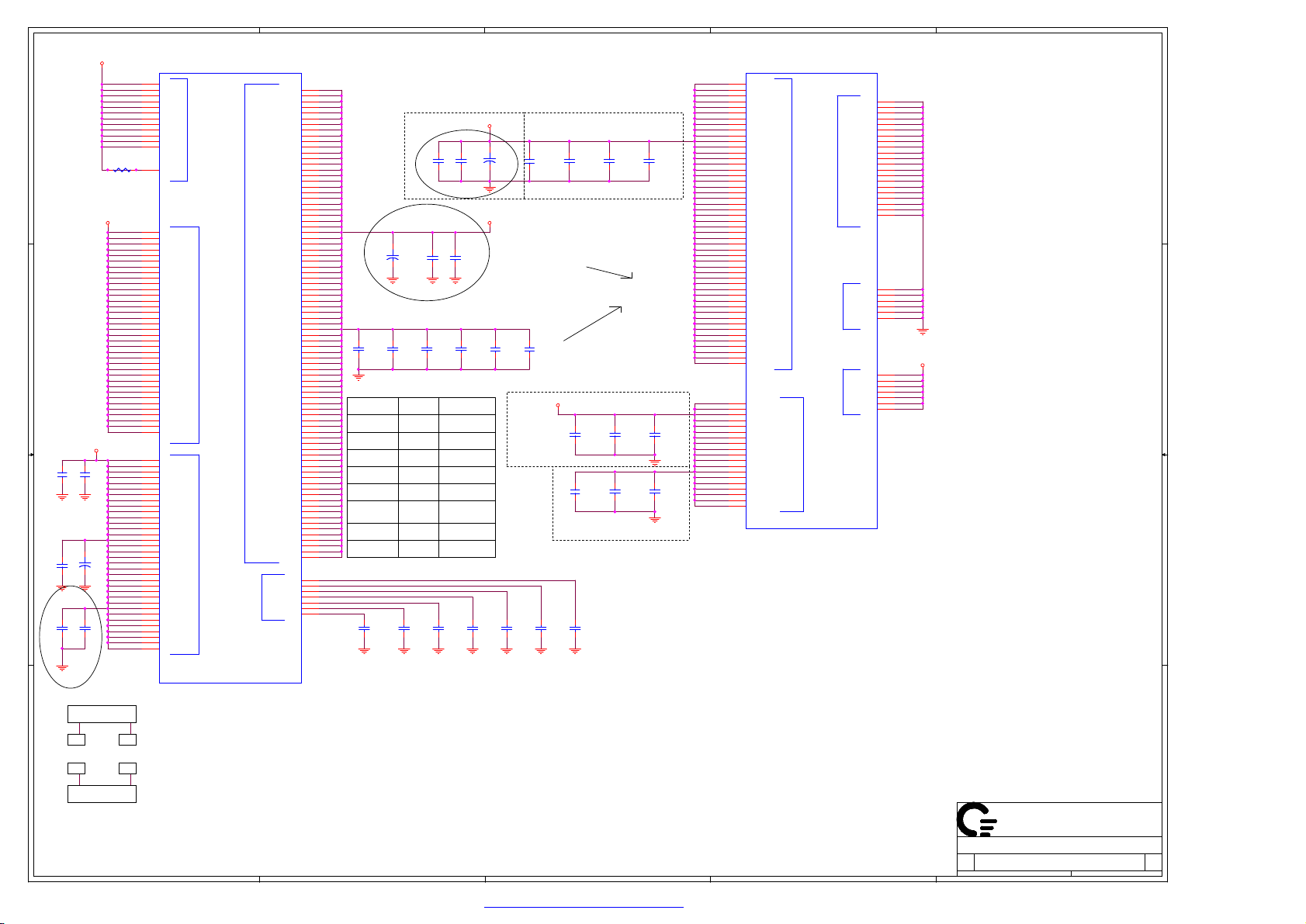

FJ1 BLOCK DIAGRAM

CPU

DD

DDRII-SODIMM1

DDRII 667 /800 MHz

PAG 13,14

DDRII-SODIMM2

DDRII 667/800 MHz

PAG 13,14

CC

USB2.0 I/O Ports

X1

CPR2 port

Finger print

Bluetooth

CAMERA

Mini_PCI_E for 3G

BB

PCI EXPRESS

SATA - HDD

PAG 31

PATA ODD

PAG 31

BAY

X2

PAG 30

PAG 30

PAG 26

PAG 19

PAG 26

PAG 29

PAG 24

SATA0 150MB

(100/133)

PATA

0,1,2

5

6

7

9

8

4

USB2.0

Merom

478P (uPGA)/35W

NORTH BRIDGE

Crestline

965GM/GML

PAG

7,8,9,10,11,12

SOUTH BRIDGE

PAG 15,16,17,18

PAG 4,5

DMI LINK

ICH-8M

CPU THERMAL

SENSOR

PAG 6

DVI

SDVO

SI1368

PCI BUS / 33MHz

PCI-E BUS

Flash

SPI

PAG 24

Flash

SPI

PAG 24

FAN

PAG 6

CLK_CPU_BCLK,CLK_CPU_BCLK#

CLK_MCH_BCLK,CLK_MCH_BCLK#

DREFCLK,DREFCLK#

DREFSSCLK,DREFSSCLK#

CRT SW

PAG 20

TMDS

PAG 21

LVDS

TVOUT

Express

Card

PAG 29

CardBus

OZ711

/MP1/SP2

PAG 27,28

CRT PORT

CPR2 PORT

LCD CNN

Mini PCI-E

Card

WLAN

PAG26

ICS9LPR365DGLF

64pinsTSSOP

PAG 30

S-OUT

SmartCard

Slot

MS/SD Slot

14.318MHz

CLOCK GEN

PAG19

PAG19

PAG 27

PAG 27

Mini PCI-E

Card

PAG26

SIM slot

PAG 26

PAG 3

3G

LAN

Marvell

88E8055

PAG 32

RJ45

PAG 32

01

HDA 24MHz

LPC

MDC1.5RJ11

TPM

V1.2

PAG 31

Super I/O

LPC47N217

PAG 22

Serial

CPR2 port

PAG 30

AA

5

ASIC

BENN

PAG 25

Parallel

PS2

PMU&KBC

LUNA2

PAG 33

ST-LCDG-Sensor

Keyboard

Touch Pad

PAG 30

PAG 30PAG 30

4

PAG 31

3

IntMic

Stereo

Analog

In

Audio

Codec

ALC262

PAG 34,35

Out

In

In

AMP

CPR2

port

PAG 30

Speaker

Analog Out

Title

Title

Title

FJ1 BLOCK DIAGRAM

FJ1 BLOCK DIAGRAM

FJ1 BLOCK DIAGRAM

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

FJ1 MAIN BOARD

FJ1 MAIN BOARD

FJ1 MAIN BOARD

Date:Sheet of

Date:Sheet of

2

Date:Sheet of

1

144Friday, June 22, 2007

144Friday, June 22, 2007

144Friday, June 22, 2007

1A

1A

1A

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

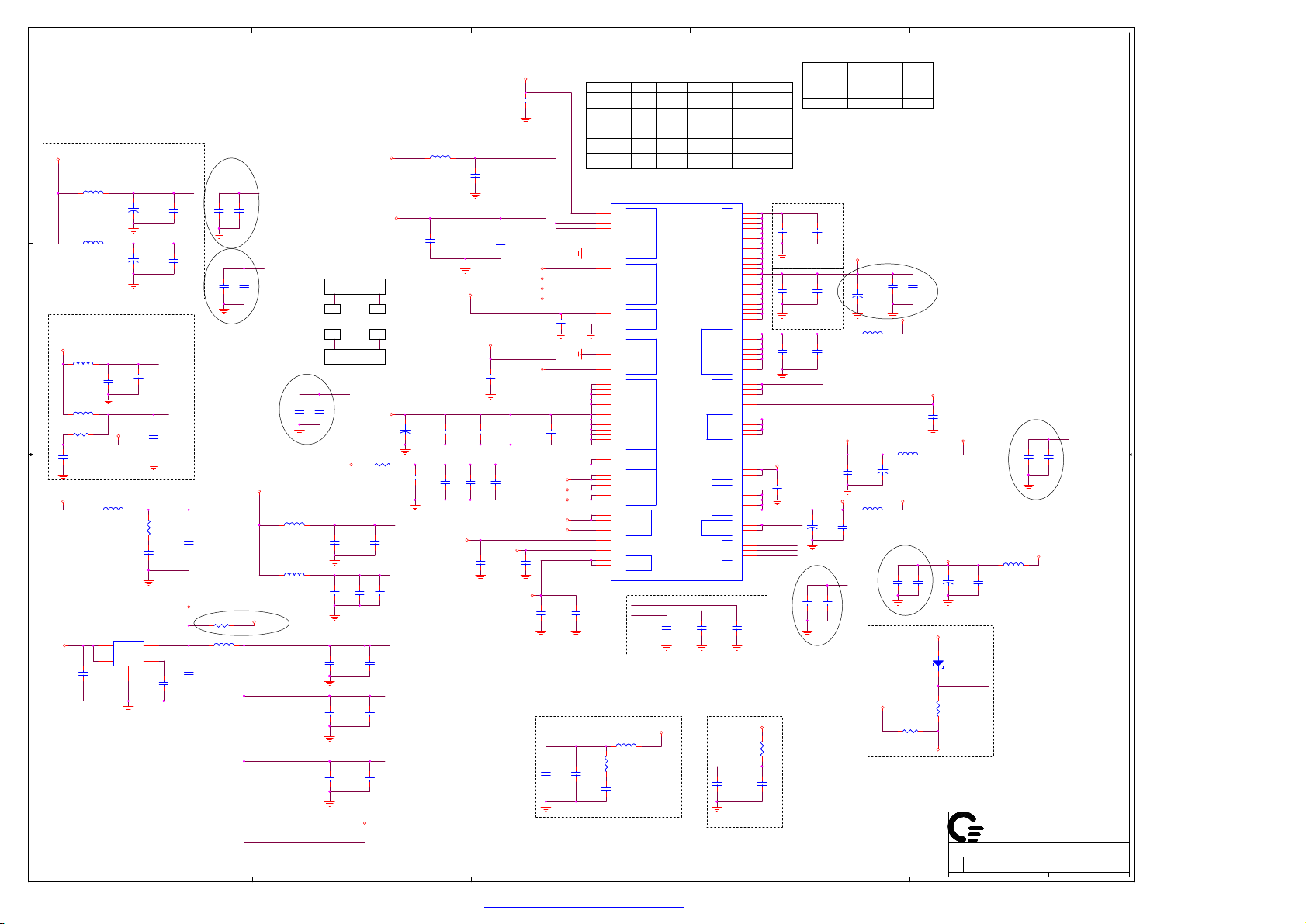

Page 2

5

4

3

2

1

02

DD

PAGE LIST

01--System Block Diagram

02--SCHEMATIC PAGE LIST

03--CLOCK G_ICS365

04--Merom CPU (POWER/NC)

05--Merom Processor(Power/NC)

06--Thermal Sensor and FAN

07--Crestline_A(HOST)

08--Crestline_B(VGA,DMI)

09--Crestline_C(DDR2)

10--Crestline_D(VCC,NCTF)

11--Crestline_E(Power)

12--Crestline_F(VSS)

13--DDRII RES.ARRAY

14--DDRII SO-DIMM(200P)

15--ICH8-M HOST(1 of 4)

CC

BB

16--ICH8-M PCIE(2 of 4)

17--ICH8-M GPIO(3 of 4)

18--ICH8-M Power(4 of 4)

19--LVDS/CRT

20--CRT SW/GLIDE PAD/StickPoint

21--DVI Transfer SI 1368

22--SUPER I/O

23--COM /PARALLEL PORT

SPI BIOS/USB port/TV CONN

25--BENN

POWER_Control_Tree

26--MINI PCIE /SIM/BTOOTH

27--OZ711 (1/2)/3 IN1 / SMART CARD CONN

28--OZ711 (2/2) NC

29--NEW CARD

30--DOCKING CN/ KB /LCM/SW

31--SATA/MDC/TPM/GSENSOR/ ODD

32--LAN_MARVELL 88E8055

33--EC Controller

34--AUDIO AL262 1/2

35--AUDIO AL262 2/2

36--RESET

37--CPU CORE POWER

38--LDO/SWITCH

39--BATTERY

40--CHARGER

41--5VPMU/5VSTD/3VPMU/3VSTD

42--1.8V_DIMM

43--BATTERY CN

44--1.05V/ETC0

45--A stage to B stage change list

AC-IN

PWR_3VSTD

RSMRST#

SUSC#

Delay

5VSUS

Delay

DLY_SUSB#

3VSUS/1.8VSUS

PWROK_3VSUS

1.5VMAIN/2.5VMAIN/3VMAIN/5VMAIN

POWER_VRM PWROK_3VSUS

AA

COREON CPUCORE/1.05VMAIN

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

Date:Sheet of

Date:Sheet of

5

4

3

2

Date:Sheet of

SCHEMATIC PAGE LIST

SCHEMATIC PAGE LIST

SCHEMATIC PAGE LIST

FJ1 MAIN BOARD

FJ1 MAIN BOARD

Monday, June 25, 2007

Monday, June 25, 2007

Monday, June 25, 2007

FJ1 MAIN BOARD

1A

1A

244

244

1

244

1A

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

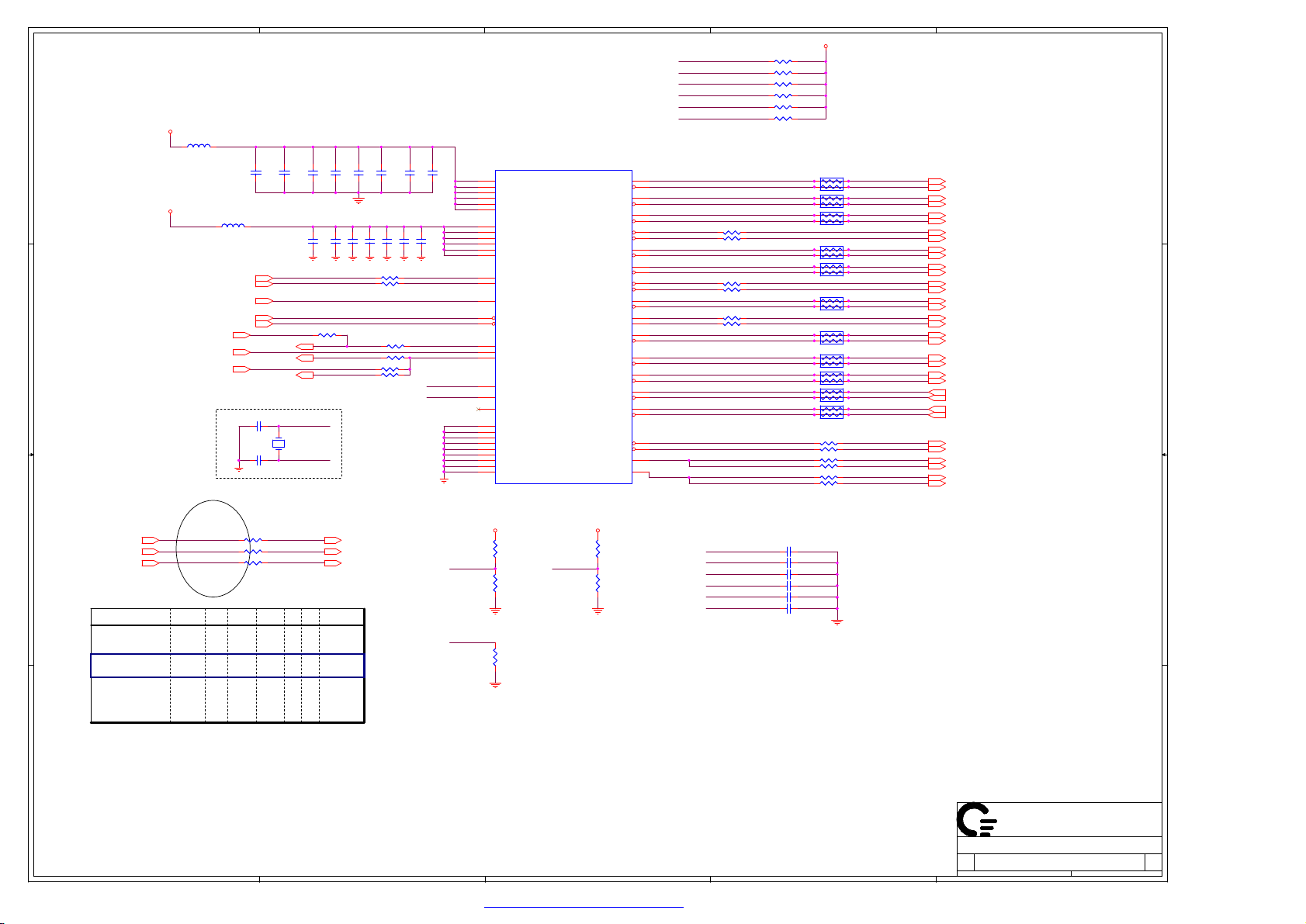

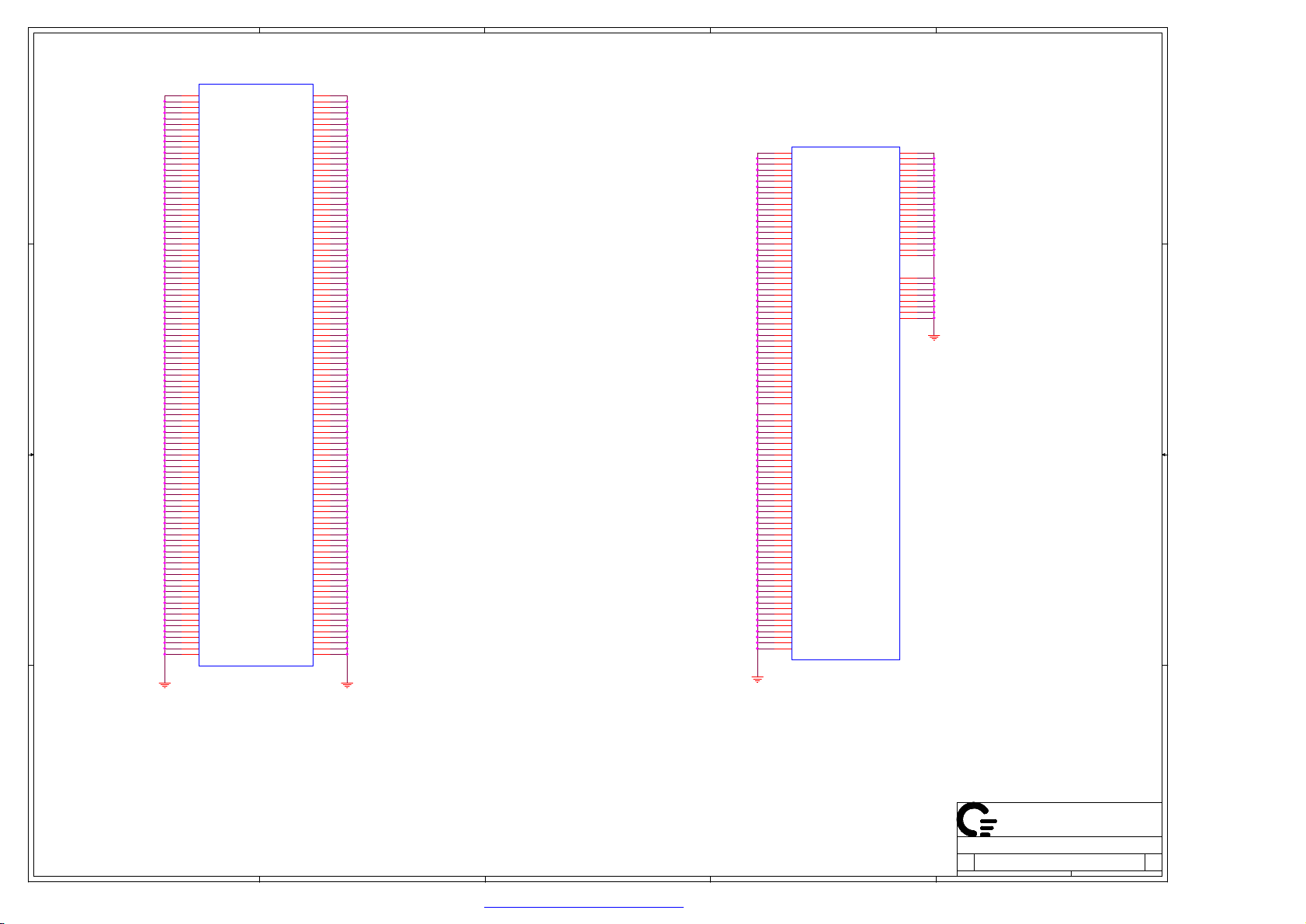

Page 3

5

PWR_1.8VSUS

L1

DD

CC

CPU Clock select

L1

1 2

BLM21PG600SN1D(60,3A)

BLM21PG600SN1D(60,3A)

PWR_3VSUS

20mil

L2

L2

20mil

BLM21PG600SN1D(60,3A)

BLM21PG600SN1D(60,3A)

SMB_DATA_SUS6,14

SMB_CLK_SUS6,14

CLK_PWROK17

PM_STPPCI#17

PM_STPCPU#17

CLK_BSEL04

CLK_BSEL14

CLK_BSEL24

12

C1

10UC110U

20mil

CLK_48M_ICH17

CLK_14M_ICH17

CLK_14M_SIO22

14.318MHz

XTL-5_3X3_2-3_8-1_2H

XTL-5_3X3_2-3_8-1_2H

BG614318Q33

BG614318Q33

C1633PC1633P

C1733PC1733P

12

ICS_3VS

21

C2

10UC210U

R132.2KR132.2K

CLK_XIN

Y1

Y1

14.318MHZ/20P

14.318MHZ/20P

CLK_XOUT

12

C3

0.1UC30.1U

C9

10UFC910UF

EC1

0

0

1

0

011

1

1

CPU_BSEL2

CPU_BSEL1

CPU_BSEL0

FSAFSBFSC

0

266.66

1

133.33

0

200.00

1

166.66

0

333.33

100.00

0

400.00

1

200.0010033.33

CLK_BSEL24

BB

CLK_BSEL14

CLK_BSEL04

BSEL2BSEL1BSEL0CPU

0

0

0

*

0

1

1

1

1

R261KR261K

R271KR271K

R281KR281K

SRC

PCI

100

33.33

100

33.3314.3184896

100

33.3314.3184896

100

33.3314.3184896

100

33.3314.3184896

100

33.3314.3184896

100

33.3314.3184896

MCH_BSEL2

MCH_BSEL1

MCH_BSEL0

REF

USB48DOT

14.318

14.3184896

96

Spread

0.5 Down

0.5 Down

0.5 Down

0.5 Down

0.5 Down

0.5 Down

0.5 Down

0.5 Down

4

12

12

12

C6

C4

C5

0.1UC60.1U

0.1UC40.1U

0.1UC50.1U

C10

C10

0.1U

0.1U

C13

C13

C12

C12

C11

C11

0.1U

0.1U

0.1U

0.1U

0.1U

0.1U

R933R933

R1033R1033

R1433R1433

R1522R1522

R172.2KR172.2K

R1622R1622

FCE P/N:BG614318F84

P/N:BG614318Q33

MCH_BSEL28

MCH_BSEL18

MCH_BSEL08

%

C14

C14

0.1U

0.1U

12

12

C8

C7

0.1UC80.1U

0.1UC70.1U

C15

C15

0.1U

0.1U

CLK_USB48

CLK_14M_REF

26

45

36

12

20

49

61

39

9

2

55

16

63

64

56

38

37

10

57

62

CLK_XIN

60

59

48

8

11

15

19

23

29

42

58

52

PWR_3VMAIN PWR_3VMAIN

CLK_33_ASIC CLK_33_PMU

CLK_PCIF_ICH

U1

U1

VDDSRC_IO

VDDSRC_IO

VDDSRC_IO

VDD96_IO

VDDPLL3_IO

VDDCPU_IO

VDDREF

VDDSRC

VDD48

VDDPCI

VDDCPU

VDDPLL3

SDATA

SCLOCK

CK_PWRGD/PD#

PCI_STOP#

CPU_STOP#

USB_48MHZ/FSLA

FSLB/TEST_MODE

REF0/FSLC/TEST_SEL

XTAL_IN

XTAL_OUT

NC

GNDPCI

GND48

GND

GND

GNDSRC

GNDSRC

GNDSRC

GNDREF

GND_CPU

ICS9PRS365BGLF

ICS9PRS365BGLF

ALPRS365K13

ALPRS365K13

P/N:ALLPR363K00 VER:D

R29

R29

*10K

*10K

R33

R33

10K

10K

R35

R35

10K

10K

3

CPUT_F

CPUC1_F

CPUT0

CPUC0

CPUT2_ITP/SRCT8

CPUT2_ITP/SRCC8

SRCT11/CR#_H

SRCC11/CR#_G

SRCT10

SRCC10

SRCT9

SRCC9

SRCT7/CR#_F

SRCC7/CR#_E

SRCT6

SRCC6

PCI4/27_Select

PCI_F5/ITP_EN

SRCT4

SRCC4

SRCT3/ CR#_C

SRCC3/ CR#_D

SRCT2/SATAT

SRCC2/SATAC

27MHz_NonSS/SRCT1_SE1

27MHz_SS/SRCC1_SE2

SRCT0/DOTT_96

SRCC0/DOTC_96

PCI0/CR#_A

PCI1/CR#_B

PCI2/TME

R30

R30

10K

10K

R34

R34

*10K

*10K

PCI3

ICS_MCH_BCLK

51

ICS_MCH_BCLK#

50

ICS_CPU_BCLK

54

ICS_CPU_BCLK#

53

ICS_PCIE_EXPCARD

47

ICS_PCIE_EXPCARD#

46

CR#_H

33

CR#_G

32

ICS_PCIE_MINICARD1

34

ICS_PCIE_MINICARD1#

35

ICS_PCIE_MINICARD

30

ICS_PCIE_MINICARD#

31

CR#_F

44

CR#_E

43

ICS_PCIE_LAN

41

ICS_PCIE_LAN#

40

27_SELECT

6

ITP_EN

7

ICS_PCIE_3GPLL

27

ICS_PCIE_3GPLL#

28

ICS_PCIE_ICH

24

ICS_PCIE_ICH#

25

ICS_PCIE_SATA

21

ICS_PCIE_SATA#

22

ICS_DREFSSCLK

17

ICS_DREFSSCLK#CLK_XOUT

18

ICS_DREFCLK

13

ICS_DREFCLK#

14

1

3

ICS_PCI2

4

5

ICS_PCI3

CLKREQ#_GMCH

CLKREQ#_SATA

CLKREQ#_LAN

PLL_CLKREQ#_EXC

CLKREQ#_MINIC0

CLKREQ#_MINIC1

R8475/FR8475/F

R7475/FR7475/F

R12475/FR12475/F

R11475/FR11475/F

R8433R8433

R45333R45333

CLK_33_ASIC

CLK_PCIF_ICH

CLK_33_PMU

CLK_33_PCIC

CLK_33_SIO

CLK_33_TPM

R110KR110K

R210KR210K

R310KR310K

R410KR410K

R510KR510K

R64.7KR64.7K

RP84P2R-S-33RP84P2R-S-33

C185PC185P

C195PC195P

C205PC205P

C215PC215P

C225PC225P

C235PC235P

For EMI

2

PWR_3VMAIN

RP14P2R-S-33RP14P2R-S-33

RP24P2R-S-33RP24P2R-S-33

RP34P2R-S-33RP34P2R-S-33

RP44P2R-S-33RP44P2R-S-33

RP54P2R-S-33RP54P2R-S-33

RP64P2R-S-33RP64P2R-S-33

RP94P2R-S-33RP94P2R-S-33

RP104P2R-S-33RP104P2R-S-33

RP114P2R-S-33RP114P2R-S-33

RP124P2R-S-33RP124P2R-S-33

241

241

241

241

241

241

241

241

241

241

241

R19475/FR19475/F

R18475/FR18475/F

R2122R2122

R2022R2022

R2322R2322

R2222R2222

3

3

3

3

3

3

3

3

3

3

3

CLK_33_PMU

CLK_33_PCIC

CLK_33_ASIC

CLK_PCIF_ICH

CLK_MCH_BCLK7

CLK_MCH_BCLK#7

CLK_CPU_BCLK4

CLK_CPU_BCLK#4

CLK_PCIE_EXPCARD29

CLK_PCIE_EXPCARD#29

CLKREQ#_MINIC126

CLKREQ#_MINIC026

CLK_PCIE_MINICARD126

CLK_PCIE_MINICARD1#26

CLK_PCIE_MINICARD026

CLK_PCIE_MINICARD0#26

PLL_CLKREQ#_EXC29

CLKREQ#_LAN32

CLK_PCIE_LAN32

CLK_PCIE_LAN#32

CLK_33_ASIC25,26

CLK_PCIF_ICH16

CLK_PCIE_3GPLL8

CLK_PCIE_3GPLL#8

CLK_PCIE_ICH16

CLK_PCIE_ICH#16

CLK_PCIE_SATA15

CLK_PCIE_SATA#15

DREFSSCLK8

DREFSSCLK#8

DREFCLK8

DREFCLK#8

CLKREQ#_SATA17

CLKREQ#_GMCH8

CLK_33_PMU33

CLK_33_PCIC27

CLK_33_SIO22

CLK_33_TPM31

1

03

AA

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

Date:Sheet of

Date:Sheet of

5

4

3

2

Date:Sheet of

CLOCK G_ICS365

CLOCK G_ICS365

CLOCK G_ICS365

Monday, June 25, 2007

Monday, June 25, 2007

Monday, June 25, 2007

FJ1 MAIN BOARD

FJ1 MAIN BOARD

FJ1 MAIN BOARD

1

344

344

344

1A

1A

1A

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

Page 4

5

H_A#[3..35]7

H_ADSTB#07

DD

H_REQ#[0..4]7

H_A#[3..35]7

H_ADSTB#17

H_A20M#15

H_FERR#15

H_IGNNE#15

H_STPCLK#15

H_INTR15

H_NMI15

H_SMI#15

CC

No stub on H_STPCLK

H_A#[3..35]

H_REQ#[0..4]

H_A#[3..35]

XDP P/U & P/D

XDP_DBRESET#

H_CPURST#

H_IERR#

XDP_TMS

XDP_TDI

XDP_BPM#5

H_DPSLP#

BB

H_DPRSTP#

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

XDP_TRST#

XDP_TCK

CN1A

CN1A

J4

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

D22

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

Merom Ball-out Rev 1a

Merom Ball-out Rev 1a

1K

R47*56R47*56

R4656R4656

R4939.2/FR4939.2/F

R48150R48150

R5154.9/FR5154.9/F

R50*56R50*56

R101*56R101*56

R52649/FR52649/F

R5327R5327

R451KR45

PWR_1.05VMAIN

ADDR GROUP 0

ADDR GROUP 0

CONTROLXDP/ITP SIGNALS

CONTROLXDP/ITP SIGNALS

ADDR GROUP 1

ADDR GROUP 1

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

ICH

THERMTRIP#

H CLK

H CLK

RESERVED

RESERVED

PWR_3VMAIN

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

DBR#

BCLK[0]

BCLK[1]

H1

E2

G5

H5

F21

E1

F1

D20

B3

INIT#

H4

C1

F3

F4

G3

G2

G6

HIT#

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

TCK

AA6

TDI

AB3

TDO

AB5

TMS

AB6

C20

D21

A24

B25

C7

A22

A21

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TMS

XDP_TRST#

XDP_DBRESET#

H_IERR#

R3668/F R3668/F

4

H_ADS#7

H_BNR#7

H_BPRI#7

H_DEFER#7

H_DRDY#7

H_DBSY#7

H_BREQ#07

H_INIT#15

H_LOCK#7

H_CPURST#7

H_RS#07

H_RS#17

H_RS#27

H_TRDY#7

H_HIT#7

H_HITM#7

PWR_1.05VMAIN

H_PROCHOT#37

H_THERMDA6

H_THERMDC6

PM_THRMTRIP#8,15

CLK_CPU_BCLK3

CLK_CPU_BCLK#3

H_D#[0..63]7

12

C354

C354

100PF

100PF

Layout Note:

Place voltage

divider within

0.5" of GTLREF

pin

PWR_1.05VMAIN

R37

R37

1K/F

1K/F

1 2

10mils

12

C24

C24

R38

R38

2K/F

2K/F

*0.1U

*0.1U

1 2

ITP disable guidelines

Signal Resistor ValueConnect ToResistor Placement

150 ohm +/- 5%

TDI

39 ohm +/- 1%

TMS

500-680ohm +/- 5%

TRST#

27 ohm +/- 1%

TCK

150 ohm +/- 5%

TDO

H_DSTBN#07

H_DSTBP#07

H_DINV#07

H_D#[0..63]7

H_DSTBN#17

H_DSTBP#17

H_DINV#17

Place C close to the

CPU_TEST4 pin. Make sure

CPU_TEST4 routing is

reference to GND and away

from other noisy signal.

FSB

BCLK

533

667

166

800

200

H_D#[0..63] H_D#[0..63]

H_D#[0..63]

CLK_BSEL03

CLK_BSEL13

CLK_BSEL23

R39*1KR39*1K

1 2

R40*1KR40*1K

1 2

C25*0.1UC25*0.1U

12

BSEL2BSEL1BSEL0

00

1

0

0

1

Within 2.0" of the ITPVTT

VTT

Within 2.0" of the ITP

GND

Within 2.0" of the ITP

GND

Within 2.0" of the ITP

VTT

Within 2.0" of the ITP

3

GTLREF

H_TEST1

H_TEST2

H_TEST4

1133

1

0

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_TEST1

H_TEST2

H_TEST4

CN1B

CN1B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Merom Ball-out Rev 1a

Merom Ball-out Rev 1a

H_D#32

Y22

D[32]#

H_D#33

AB24

D[33]#

H_D#34

V24

D[34]#

H_D#35

V26

D[35]#

H_D#36

V23

D[36]#

H_D#37

T22

D[37]#

H_D#38

U25

D[38]#

H_D#39

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

MISC

MISC

U23

D[39]#

H_D#40

Y25

D[40]#

H_D#41

W22

D[41]#

H_D#42

Y23

D[42]#

H_D#43

W24

D[43]#

H_D#44

W25

D[44]#

H_D#45

AA23

D[45]#

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

H_D#46

AA24

D[46]#

H_D#47

AB25

D[47]#

Y26

AA26

U22

AE24

D[48]#

AD24

D[49]#

AA21

D[50]#

AB22

D[51]#

AB21

D[52]#

AC26

D[53]#

AD20

D[54]#

AE22

D[55]#

AF23

D[56]#

AC25

D[57]#

AE21

D[58]#

AD21

D[59]#

AC22

D[60]#

AD23

D[61]#

AF22

D[62]#

AC23

D[63]#

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

SLP#

AE6

PSI#

Comp0,2 connect with Zo=27.4ohm,Comp1,3

connect with Zo=55ohm, make those traces

length shorter than 0.5".Trace should be

at least 25 mils away from any other

toggling signal.

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

COMP0

COMP1

COMP2

COMP3

H_D#[0..63]

1 2

R41

R41

54.9/F

54.9/F

2

H_D#[0..63]7

H_DSTBN#27

H_DSTBP#27

H_DINV#27

H_D#[0..63]7

H_DSTBN#37

H_DSTBP#37

H_DINV#37

H_DPRSTP#8,15,37

H_DPSLP#15

H_DPWR#7

H_PWRGD15

H_CPUSLP#7

PSI#37

R42

R42

27.4/F

27.4/F

1 2

1

04

R44

R44

R43

R43

27.4/F

27.4/F

54.9/F

54.9/F

1 2

1 2

Note: Populate R5, R8, C372 & R430 when ITP connector is populated.

AA

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

5

4

3

2

Date:Sheet of

Merom Processor (HOST BUS)

Merom Processor (HOST BUS)

Merom Processor (HOST BUS)

Custom

Custom

Custom

Monday, June 25, 2007

Monday, June 25, 2007

Monday, June 25, 2007

FJ1 MAIN BOARD

FJ1 MAIN BOARD

FJ1 MAIN BOARD

1A

1A

444

444

1

444

1A

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

Page 5

5

PWR_CPUCORE

12

12

12

C41

C41

C26

C26

10U

10U

10U

10U

PWR_CPUCORE

DD

12

12

C42

C42

C29

C29

10U

10U

10U

10U

12

C34

C34

C27

C27

10U

10U

10U

10U

12

12

C30

C30

C31

C31

10U

10U

10U

10U

12

C28

C28

10U

10U

12

C32

C32

10U

10U

8 inside cavity, north side, secondary layer.

PWR_CPUCORE

12

C43

C43

10U

10U

PWR_CPUCORE

12

C45

C45

10U

10U

DEL C33,C35,C37,C39,C40,C44,C46,C48,C49,C58

12

C38

C38

10U

10U

8 inside cavity, south side, secondary layer.

PWR_CPUCORE

CC

12

C47

C47

10U

10U

PWR_CPUCORE

12

12

C56

C56

C55

C55

10U

10U

10U

10U

8 inside cavity, north side, primary layer.

PWR_1.05VMAIN

12

12

C62

C62

C61

C61

0.1U

0.1U

0.1U

BB

0.1U

Layout out:

Place these inside socket cavity on North side secondary.

12

C50

C50

10U

10U

12

C57

C57

10U

10U

8 inside cavity, south side, primary layer.

12

12

C63

C63

C64

C64

0.1U

0.1U

0.1U

0.1U

PWR_CPUCORE6,37

PWR_1.5VMAIN11,15,18,26,29,38,41

PWR_1.05VMAIN4,7,10,11,15,18,41,44

12

12

C52

C52

C51

C51

10U

10U

10U

10U

12

12

C59

C59

C60

C60

10U

10U

10U

10U

12

12

C66

C66

C65

C65

0.1U

0.1U

0.1U

0.1U

4

PWR_CPUCORE PWR_CPUCORE

CN1C

CN1C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Merom Ball-out Rev 1a

Merom Ball-out Rev 1a

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

Via:2.5A >100mils

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

CPU_VCC_SENSE

AF7

CPU_VSS_SENSE

AE7

.

.

CPU_VCC_SENSE

CPU_VSS_SENSE

3

ICCODE:

for Merom processors

recommended design

target is 44A

12

+

+

C36

C36

*220U/2.5V

*220U/2.5V

ICCP:

1before vccore stable

peak current is 4.5A

2.after vccore stable

continue current is

2.5A

EC8

PWR_1.05VMAIN

12

12

C135

C135

C58

C58

10U

10U

10U

10U

ICCA 130mA

12

C53

Layout Note:

Place C105 near PIN

B26.

PWR_CPUCORE

12

R54

R54

100/F

100/F

12

R55

R55

100/F

100/F

C53

0.01U

0.01U

CPU_VID037

CPU_VID137

CPU_VID237

CPU_VID337

CPU_VID437

CPU_VID537

CPU_VID637

CPU_VCC_SENSE37

CPU_VSS_SENSE37

Route VCCSENSE and VSSSENSE

traces at 27.4ohms and

length matched to within 25

mil. Place PU and PD within

2 inch of CPU.

PWR_1.5VMAIN

12

C54

C54

10U

10U

CN1D

CN1D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Merom Ball-out Rev 1a

Merom Ball-out Rev 1a

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

2

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

.

1

05

AA

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

Date:Sheet of

Date:Sheet of

5

4

3

2

Date:Sheet of

Merom Processor (Power/NC)

Merom Processor (Power/NC)

Merom Processor (Power/NC)

FJ1 MAIN BOARD

FJ1 MAIN BOARD

Monday, June 25, 2007

Monday, June 25, 2007

Monday, June 25, 2007

FJ1 MAIN BOARD

1

544

544

544

1A

1A

1A

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

Page 6

5

4

3

2

1

Thermal Senser

RP47

RP47

10KX4

10KX4

C694

C694

0.1U

0.1U

R36310K R36310K

R36510K R36510K

R36210K R36210K

R3660R3660

PWR_3VMAIN

ADFANONTEMP_TACH_CPU

PWR_3VSUS

THERM_PMU#

PM_EXTTS#08

THERM_PMU#33

RP45

RP45

100KX4

100KX4

TEMP_TACH_CPU

U46

123456

2

78

1 3

U46

6

TACH1

7

TACH2

1

SCL

16

SDA

13

D1+

12

D1-

11

D2+

10

D2-

14

VCCP(Monitor_Voltage)

ADT7473ARQZ-REEL QSOP 16P

ADT7473ARQZ-REEL QSOP 16P

RP48

RP48

10KX4

10KX4

2

Q23

Q23

MMBT3904

MMBT3904

PWM1/XTO

PWM2/SMBALERT#

PWM3

SMBALT#/GPIO

TACH3

15

5

8

9

4

3

VCC

2

GND

123456

78

DD

SMB_CLK_THERM

SMB_DATA_THERM

C693

C693

*1000P

*1000P

H_THERMDA4

H_THERMDC4

PWR_CPUCORE

PWR_CPUCORE5,37

CC

SMB_CLK_STD17

SMB_DATA_STD17

C692

C692

1000P

1000P

PWR_3VMAIN

1 3

Q22

Q22

MMBT3904

MMBT3904

R36410K R36410K

PWR_3VSUS

78

123456

PWR_3VSUS

PWR_5VSUS

PWR_PMU

123456

78

RP46

RP46

100KX4

100KX4

put on near EC controller

EC31

12

C695

C695

C689

C689

*0.01U

*0.01U

10U

10U

ADFANON

UMT_213-3-1_3

UMT_213-3-1_3

BA144EUAZ04

BA144EUAZ04

1

R368

R368

470K

470K

2

2

1 3

SMB_CLK_SUS3,14

SMB_DATA_SUS3,14

SMB_DATA_PMU33

FAN CONN

PWR_FAN_CPU

3

Q21

Q21

SI2301BDS

SI2301BDS

R360

R360

47K

47K

Q19

Q19

DTC144EUA

DTC144EUA

R36710R367

10

12

C6881UC688

1U

12

C165

C165

*22U/10V

*22U/10V

CON11

CON11

TEMP_TACH_CPU

12

C691

C691

C321

C321

*3300P

*3300P

*4.7U

*4.7U

3

2

1

85205-0300L

85205-0300L

06

SMB_CLK_PMU33

SMB_CLK_LCD19,26

SMB_DATA_LCD19,26

SMB_CLK_THERM033

SMB_DATA_THERM033

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

Date:Sheet of

Date:Sheet of

2

Date:Sheet of

Thermal Sensor and Fan

Thermal Sensor and Fan

Thermal Sensor and Fan

FJ1 MAIN BOARD

FJ1 MAIN BOARD

Monday, June 25, 2007

Monday, June 25, 2007

Monday, June 25, 2007

FJ1 MAIN BOARD

1A

1A

644

644

1

644

1A

BB

SMB_CLK_THERM

SMB_DATA_THERM

AA

EC23

5

1 3

Q26

Q26

MMBT3904

MMBT3904

2

2

1 3

Q27

Q27

2

MMBT3904

MMBT3904

1 3

Q28

Q28

2

MMBT3904

MMBT3904

1 3

Q29

Q29

MMBT3904

MMBT3904

4

3

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

Page 7

5

4

3

2

1

07

U2A

R630R63

0

H_DVREF

AD12

AC14

AD11

AC11

AE11

AH12

AH13

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

M10

N12

N9

H5

P13

K9

M2

W10

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

AE3

AD9

AC9

AC7

AB2

AD7

AB1

Y3

AC6

AE2

AC5

AG3

AJ9

AH8

AJ14

AE9

AJ5

AH5

AJ6

AE7

AJ7

AJ2

AE5

AJ3

AH2

B3

C2

W1

W2

B6

E5

B9

A9

U2A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRESTLINE_1p0

CRESTLINE_1p0

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

HOST

HOST

H_DPWR#

H_DRDY#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

965GM P/N:AJ0QN120T45

965PM P/N:AJ0QN140T46

H_HIT#

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_A#3

J13

H_D#[0..63]4

DD

PWR_1.05VMAIN

12

R56

R56

221/F

221/F

H_SWING

12

R57

R57

100/F

100/F

PWR_1.05VMAIN

12

R58

CC

BB

R58

54.9/F

54.9/F

H_RCOMP

12

R60

R60

24.9/F

24.9/F

Layout Note:

H_RCOMP trace should be

10-mil wide with 20-mil

spacing.

C67

C67

0.1U

0.1U

1 2

impedance 55 ohm

12

R59

R59

54.9/F

54.9/F

H_SCOMP

H_SCOMP#

PWR_1.05VMAIN

R61

R61

1K/F

1K/F

1 2

12

R62

R62

2K/F

2K/F

H_D#[0..63]

H_CPURST#4

H_CPUSLP#4

H_AVREF

12

C68

C68

0.1U

0.1U

Layout Note:

Place the 0.1 uF

decoupling capacitor

within 100 mils from

GMCH pins.

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

12

H_A#[3..35]

H_ADS#4

H_ADSTB#04

H_ADSTB#14

H_BNR#4

H_BPRI#4

H_BREQ#04

H_DEFER#4

H_DBSY#4

CLK_MCH_BCLK3

CLK_MCH_BCLK#3

H_DPWR#4

H_DRDY#4

H_HIT#4

H_HITM#4

H_LOCK#4

H_TRDY#4

H_DINV#04

H_DINV#14

H_DINV#24

H_DINV#34

H_DSTBN#04

H_DSTBN#14

H_DSTBN#24

H_DSTBN#34

H_DSTBP#04

H_DSTBP#14

H_DSTBP#24

H_DSTBP#34

H_REQ#04

H_REQ#14

H_REQ#24

H_REQ#34

H_REQ#44

H_RS#04

H_RS#14

H_RS#24

H_A#[3..35]4

AA

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

Date:Sheet of

Date:Sheet of

5

4

3

2

Date:Sheet of

Crestline_A (HOST)

Crestline_A (HOST)

Crestline_A (HOST)

Monday, June 25, 2007

Monday, June 25, 2007

Monday, June 25, 2007

FJ1 MAIN BOARD

FJ1 MAIN BOARD

FJ1 MAIN BOARD

1

744

744

744

1A

1A

1A

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

Page 8

5

DD

CC

BB

WW22 update

--- MA14 needs

to be routed if

customers are

planning on

using 2Gb

technology and

width=8 (by 8)

DIMMs

M_A_A1413,14

M_B_A1413,14

CRESTLINE

new pin

define

Layout Note:

Location of all MCH_CFG strap

resistors needs to be close to

minmize stub.

MCH_BSEL03

MCH_BSEL13

MCH_BSEL23

PM_BMBUSY#17

H_DPRSTP#4,15,37

PM_EXTTS#06

PM_EXTTS#114

PWROK_3VMAIN17,36

PLT_RST#16,21,22,25,33,36

PM_THRMTRIP#4,15

DPRSLPVR17,37

GMCH pwrok is 3.3v

tolerant

PWR_3VMAIN

R9310KR9310K

1 2

R9510KR9510K

1 2

PWR_3VMAIN

R96*1KR96*1K

1 2

R98*4.02K/FR98*4.02K/F

1 2

R99*4.02K/FR99*4.02K/F

12

R102*4.02K/FR102*4.02K/F

12

R104*2.2KR104*2.2K

1 2

R105*4.02K/FR105*4.02K/F

1 2

T33PADT33PAD

T34PADT34PAD

T35

T35

PAD

PAD

T36

T36

PAD

PAD

T37

T37

PAD

PAD

T38

T38

PAD

PAD

T39

T39

PAD

PAD

T10

T10

PAD

PAD

T9

PADT9PAD

T12

T12

PAD

PAD

T11

T11

PAD

PAD

T13

T13

PAD

PAD

T14

T14

PAD

PAD

PM_EXTTS#0

PM_EXTTS#1

MCH_CFG18

MCH_CFG19

MCH_CFG20

MCH_CFG5

MCH_CFG9

MCH_CFG16

PM_BMBUSY#_R

ICH_DPRSTP#_R

PM_EXTTS#0

PM_EXTTS#1

R810R810

R820R820

R86100R86100

R890R890

R880R880

DMI X2 Select

MCH_CFG5Low = DMIX2

High = IDMIX4(Default)

FSB Dynamic ODT

MCH_CFG16Low = ODT Disable

AA

High = ODT Enable(Default)

U2B

U2B

P36

RSVD1

P37

RSVD2

R35

RSVD3

N35

RSVD4

AR12

RSVD5

AR13

RSVD6

AM12

RSVD7

AN13

RSVD8

J12

RSVD9

AR37

RSVD10

AM36

RSVD11

AL36

RSVD12

AM37

RSVD13

D20

RSVD14

H10

RSVD20

B51

RSVD21

BJ20

RSVD22

BK22

RSVD23

BF19

RSVD24

BH20

RSVD25

BK18

RSVD26

BJ18

RSVD27

BF23

RSVD28

BG23

RSVD29

BC23

RSVD30

BD24

RSVD31

BJ29

SA-MA14

BE24

SB_MA14

BH39

RSVD34

AW20

RSVD35

BK20

RSVD36

C48

LVDSA_DATA#_3

D47

LVDSA_DATA_3

B44

RSVD39

C44

RSVD40

A35

RSVD41

B37

RSVD42

B36

RSVD43

B34

RSVD44

C34

RSVD45

P27

CFG_0

N27

CFG_1

N24

CFG_2

CFG3

C21

CFG_3

CFG4

C23

CFG_4

CFG5MCH_CFG5

F23

CFG_5

CFG6

N23

CFG_6

CFG7

G23

CFG_7

CFG8

J20

CFG_8

CFG9MCH_CFG9

C20

CFG_9

CFG10

R24

CFG_10

CFG11

L23

CFG_11

J23

CFG_12

CFG13

E23

CFG_13

CFG14

E20

CFG_14

CFG15

K23

CFG_15

CFG16MCH_CFG16

M20

CFG_16

CFG17

M24

CFG_17

CFG18MCH_CFG18

L32

CFG_18

CFG19MCH_CFG19

N33

CFG_19

CFG20MCH_CFG20

L35

CFG_20

G41

PM_BM_BUSY#

L39

PM_DPRSTP#

L36

PM_EXT_TS#_0

J36

PM_EXT_TS#_1

AW49

PWROK

AV20

RSTIN#

N20

THERMTRIP#

G36

DPRSLPVR

BJ51

NC_1

BK51

NC_2

BK50

NC_3

BL50

NC_4

BL49

NC_5

BL3

NC_6

BL2

NC_7

BK1

NC_8

BJ1

NC_9

E1

NC_10

A5

NC_11

C51

NC_12

B50

NC_13

A50

NC_14

A49

NC_15

BK2

NC_16

CRESTLINE_1p0

CRESTLINE_1p0

PCI Express Graphics

MCH_CFG9Low = Reverse Lane

High = Normal operation(Default)

DMI Lane Reversal

MCH_CFG19Low = Normal operation(Default)

High = Reverse Lane

DDR MUXINGCLKDMI

DDR MUXINGCLKDMI

CFGRSVD

CFGRSVD

PM

PM

GRAPHICS VIDME

GRAPHICS VIDME

NC

NC

MISC

MISC

4

AV29

SM_CK_0

BB23

SM_CK_1

BA25

SM_CK_3

AV23

SM_CK_4

AW30

SM_CK#_0

BA23

SM_CK#_1

AW25

SM_CK#_3

AW23

SM_CK#_4

BE29

SM_CKE_0

AY32

SM_CKE_1

BD39

SM_CKE_3

BG37

SM_CKE_4

BG20

SM_CS#_0

BK16

SM_CS#_1

BG16

SM_CS#_2

BE13

SM_CS#_3

BH18

SM_ODT_0

BJ15

SM_ODT_1

BJ14

SM_ODT_2

BE16

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF_0

SM_VREF_1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

TEST_1

TEST_2

BL15

BK14

BK31

BL31

AR49

AW4

B42

C42

H48

H47

K44

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

E35

A39

C38

B39

E36

AM49

AK50

AT43

AN49

AM50

H35

K36

G39

G40

A37

R32

M_RCOMP

M_RCOMP#

M_RCOMP_VOH

M_RCOMP_VOL

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

MCH_CLVREF

1 2

SDVO/PCIE Concurrent operation

MCH_CFG20

M_CLK_DDR014

M_CLK_DDR114

M_CLK_DDR214

M_CLK_DDR314

M_CLK_DDR#014

M_CLK_DDR#114

M_CLK_DDR#214

M_CLK_DDR#314

M_CKE013,14

M_CKE113,14

M_CKE213,14

M_CKE313,14

M_CS#013,14

M_CS#113,14

M_CS#213,14

M_CS#313,14

M_ODT013,14

M_ODT113,14

M_ODT213,14

M_ODT313,14

C700.1UC700.1U

M_VREF1

R106

R106

20K

20K

1 2

Low = Only SDVO or PCIE X1 is

operational(Default)

High = SDVO andPCIE X1 are operating

simultaneously via the PEG port

C690.1UC690.1U

R700R700

DREFCLK3

DREFCLK#3

DREFSSCLK3

DREFSSCLK#3

CLK_PCIE_3GPLL3

CLK_PCIE_3GPLL#3

DMI_TXN[3:0]16

DMI_TXP[3:0]16

DMI_RXN[3:0]16

DMI_RXP[3:0]16

R781.27KR781.27K

<check lisr & CRB>

For Calero : 255

For Cresstline:1.3K/F

For external VGA:0

ohm

IV&EV Dis/Enable setting

CL_CLK017

CL_DATA017

CL_PWROK17

CL_RST#017

SDVO_CTRL_CLK21

SDVO_CTRL_DATA21

CLKREQ#_GMCH3

MCH_ICH_SYNC#17

MCH_TEST1

R1070R107

0

PWR_3VMAIN

LCDEN19,25

<check list & CRB>

For Calero : 1.5K

For

Cresstline:2.4K

M_VREF14,42

TVA_DAC24

TVB_DAC24

TVC_DAC24

PWR_3VMAIN

GM_CRT_BLUE20

GM_CRT_GREEN20

GM_CRT_RED20

CRT_DDC_CLK19

CRT_DDC_DATA19

CRT_HSYNC19

CRT_VSYNC19

<FAE>

Flexible and safe

R83120/FR83120/F

R85120/FR85120/F

R87120/FR87120/F

SDVO_CTRL_CLK

SDVO_CTRL_DATA

3

GM_BL_VOL19

GM_BLEN25

R720R720

R692.37K/FR692.37K/F

LVDS_TXCLK_LN19

LVDS_TXCLK_LP19

LVDS_TXCLK_UN19

LVDS_TXCLK_UP19

LVDS_TXOUT_L0N19

LVDS_TXOUT_L1N19

LVDS_TXOUT_L2N19

LVDS_TXOUT_U0N19

LVDS_TXOUT_U1N19

LVDS_TXOUT_U2N19

LVDS_TXOUT_U0P19

LVDS_TXOUT_U1P19

LVDS_TXOUT_U2P19

R77*2.2KR77*2.2K

R76*2.2KR76*2.2K

<FAE>

If no use can be NC

TVA_DAC1

TVB_DAC1

TVC_DAC1

R100

R100

1 2

5.6K

5.6K

R113

R113

1 2

R64100KR64100K

GM_BLEN

R6510KR6510K

R7110KR7110K

R672.2KR672.2K

R682.2KR682.2K

LVDS_TXOUT_L0P19

LVDS_TXOUT_L1P19

LVDS_TXOUT_L2P19

R730/5milR730/5mil

R750/5milR750/5mil

R740/5milR740/5mil

GM_CRT_BLUE

GM_CRT_GREEN

GM_CRT_RED

R7930.1/FR7930.1/F

R8030.1/FR8030.1/F

PWR_3VMAIN

12

R97

R97

316/F

316/F

12

R1081KR108

1K

PWR_3VMAIN

12

R112

R112

316/F

316/F

5.6K

5.6K

12

R1151KR115

1K

GM_LCDON

LVDS_IBG

*PAD

*PAD

T32

T32

TVA_DAC1

TVB_DAC1

TVC_DAC1

TV_DCONSEL_0

TV_DCONSEL_1

REFSET

U2C

U2C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

G50

LVDSA_DATA_0

E50

LVDSA_DATA_1

F48

LVDSA_DATA_2

G44

LVDSB_DATA#_0

B47

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LVDSB_DATA_2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

CRESTLINE_1p0

CRESTLINE_1p0

PWR_1.25VMAIN PWR_1.8VSUS

12

R90

R90

1K/F

1K/F

MCH_CLVREF

C79

C79

0.1U

0.1U

1 2

M_RCOMP_VOH

12

C80

C80

0.01U

0.01U

M_RCOMP_VOL

12

C82

C82

0.01U

0.01U

M_RCOMP

M_RCOMP#

12

R92

R92

392/F

392/F

PWR_1.8VSUS

12

12

12

C81

C81

2.2U/10V

2.2U/10V

12

12

C83

C83

2.2U/10V

2.2U/10V

LVDS

LVDS

TV VGA

TV VGA

R109

R109

1K/F

1K/F

R111

R111

3.01K/F

3.01K/F

R114

R114

1K/F

1K/F

R91

R91

20/F

20/F

R94

R94

20/F

20/F

2

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

12

12

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

<check list>

For EV@

Connect to GND

CRT R/G/B

TV A/B/C

HSYNC/VSYNC

PEG_COMP

N43

M43

J51

L51

N47

T45

T50

U40

Y44

Y40

AB51

W49

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

C720.1UC720.1U

N45

C710.1UC710.1U

U39

C730.1UC730.1U

U47

C740.1UC740.1U

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

C760.1UC760.1U

M45

C750.1UC750.1U

T38

C770.1UC770.1U

T46

C780.1UC780.1U

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

IV&EV Dis/Enable setting

<check list>

SDVO/PCIE/LVDS not

implement

16 lanes NC

GM_CRT_BLUE

GM_CRT_GREENMCH_TEST2

GM_CRT_RED

R6624.9/FR6624.9/F

1 2

SDVOB_INT-21

SDVOB_INT+21

C5353PC535

3P

1 2

VCC_PEG

SDVOB_RED-21

SDVOB_GREEN-21

SDVOB_BLUE-21

SDVOB_CLK-21

SDVOB_RED+21

SDVOB_GREEN+21

SDVOB_BLUE+21

SDVOB_CLK+21

<check list>

For IV@

Connect to 150ohm

CRT R/G/B

TV A/B/C

Connect to 0ohm

HSYNC/VSYNC

C5533PC553

3P

1 2

1 2

1

08

C5523PC552

3P

PWR_1.8VSUS3,10,11,14,41,42

PWR_1.25VMAIN11,18,38,41

PWR_3VMAIN3,4,6,11,15,16,17,18,19,20,21,22,24,25,26,27,29,31,32,33,34,35,36,37,38

5

4

3

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

Date:Sheet of

Date:Sheet of

2

Date:Sheet of

Crestline_B (VGA,DMI)

Crestline_B (VGA,DMI)

Crestline_B (VGA,DMI)

Monday, June 25, 2007

Monday, June 25, 2007

Monday, June 25, 2007

FJ1 MAIN BOARD

FJ1 MAIN BOARD

FJ1 MAIN BOARD

1

844

844

844

1A

1A

1A

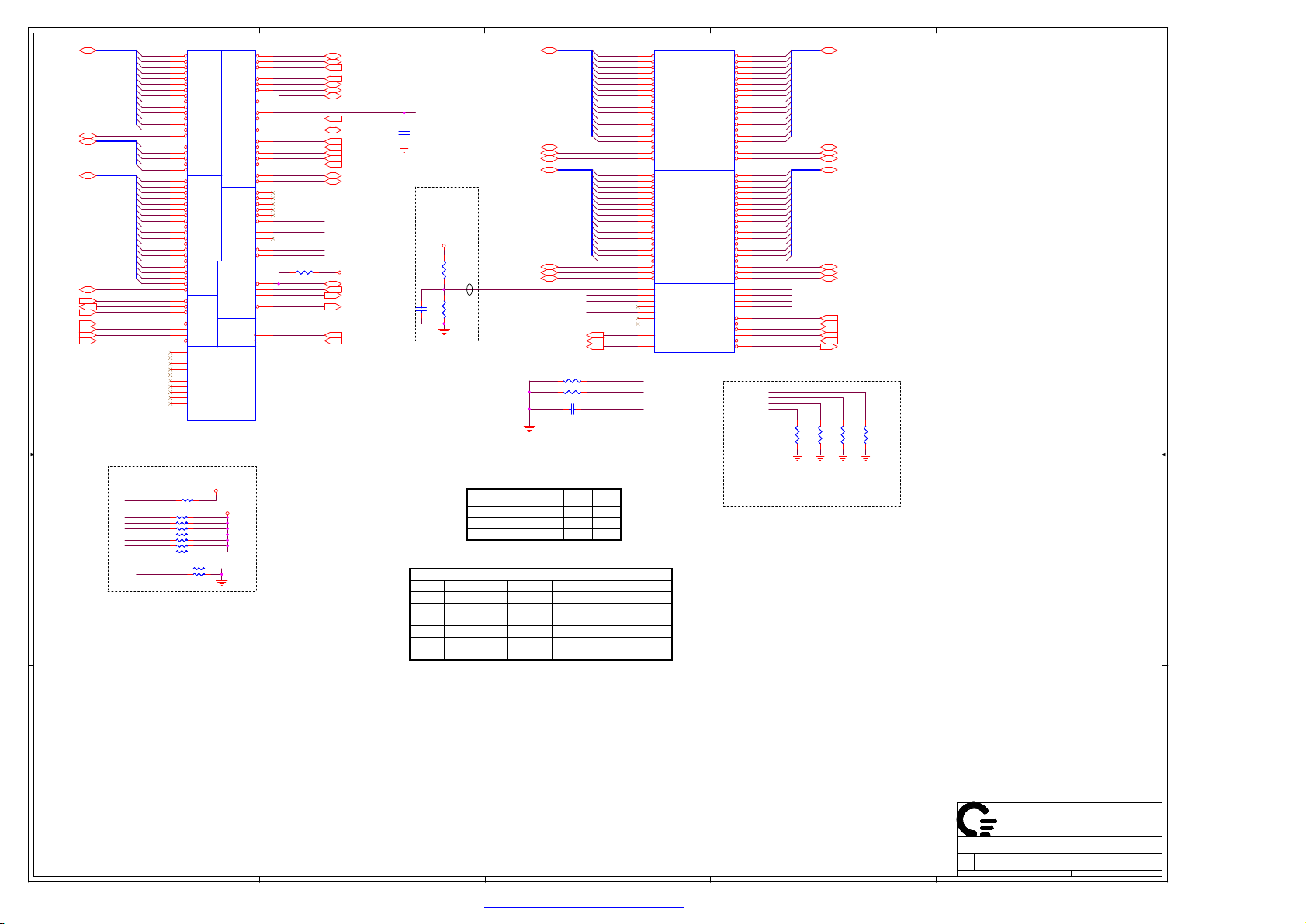

Page 9

5

4

3

2

1

09

M_A_DQ[63:0]14

DD

CC

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AW44

AW47

AW43

AW40

AW36

AW41

AW11

AR43

BA45

AY46

AR41

AR45

AT42

BB45

BF48

BG47

BB47

BG50

BH49

BE45

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AT39

AY41

AV38

AT38

AV13

AT13

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BG10

AN10

AN11

BJ45

BD8

AY9

AW9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AT9

AN9

AM9

U2D

U2D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

CRESTLINE_1p0

CRESTLINE_1p0

BB19

SA_BS_0

BK19

SA_BS_1

BF29

SA_BS_2

BL17

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVEN#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_WE#

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BE18

AY20

BA19

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

T15T15

M_A_BS013,14

M_A_BS113,14

M_A_BS213,14

M_A_CAS#13,14

M_A_DM[0..7]14

M_A_DQS[7:0]14

M_A_DQS#[7:0]14

M_A_A[14:0]8,13,14

M_A_RAS#13,14

M_A_WE#13,14

M_B_DQ[63:0]14

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BK10

BL9

BK5

BL5

BK9

BJ8

BJ6

BF4

BH5

BG1

BC2

BK3

BE4

BD3

BJ2

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

U2E

U2E

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

CRESTLINE_1p0

CRESTLINE_1p0

AY17

SB_BS_0

BG18

SB_BS_1

BG36

SB_BS_2

BE17

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

SB_WE#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_BS013,14

M_B_BS113,14

M_B_BS213,14

M_B_CAS#13,14

M_B_DM[0..7]14

M_B_DQS[7:0]14

M_B_DQS#[7:0]14

M_B_A[14:0]8,13,14

M_B_RAS#13,14

T16T16

M_B_WE#13,14

BB

AA

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

5

4

3

2

Date:Sheet of

Custom

Custom

Custom

Monday, June 25, 2007

Monday, June 25, 2007

Monday, June 25, 2007

Crestline_C (DDR2)

Crestline_C (DDR2)

Crestline_C (DDR2)

FJ1 MAIN BOARD

FJ1 MAIN BOARD

FJ1 MAIN BOARD

1

944

944

944

1A

1A

1A

PDF created with FinePrint pdfFactory Pro trial version http://www.fineprint.com

Page 10

5

4

3

2

1

PWR_1.05VMAIN

DD

IVCCSM supply

current 1

channel

1.615A 2

PWR_1.8VSUS

channel

3.318A

CC

PWR_1.05VMAIN

12

12

C99

C99

C100

C100

10U

10U

10U

10U

12

12

+

BB

+

C105

C105

C104

C104

*330U/2.5V

*330U/2.5V

0.1U

0.1U

12

12

C342

C342

C341

C341

10U

10U

10U

10U

U2G

U2G

AT35

VCC_1

AT34

VCC_2

AH28

VCC_3

AC32

VCC_5

AC31

VCC_4

AK32

VCC_6

AJ31

VCC_7

AJ28

VCC_8

AH32

VCC_9

AH31

VCC_10

AH29

VCC_11

AF32

VCC_12

VCC CORE

R116

R116

R30

0 /15mil

0 /15mil

AU32

AU33

AU35

AV33

AW33

AW35

AY35

BA32

BA33

BA35

BB33

BC32

BC33

BC35

BD32

BD35

BE32

BE33

BE35

BF33

BF34

BG32

BG33

BG35

BH32

BH34

BH35

BJ32

BJ33

BJ34

BK32

BK33

BK34

BK35

BL33

AU30

R20

T14

W13

W14

Y12

AA20

AA23

AA26

AA28

AB21

AB24

AB29

AC20

AC21

AC23

AC24

AC26

AC28

AC29

AD20

AD23

AD24

AD28

AF21

AF26

AA31

AH20

AH21

AH23

AH24

AH26

AD31

AJ20

AN14

VCC_13

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_AXG_1

VCC_AXG_2

VCC_AXG_3

VCC_AXG_4

VCC_AXG_5

VCC_AXG_6

VCC_AXG_7

VCC_AXG_8

VCC_AXG_9

VCC_AXG_10

VCC_AXG_11

VCC_AXG_12

VCC_AXG_13

VCC_AXG_14

VCC_AXG_15

VCC_AXG_16

VCC_AXG_17

VCC_AXG_18

VCC_AXG_19

VCC_AXG_20

VCC_AXG_21

VCC_AXG_22

VCC_AXG_23

VCC_AXG_24

VCC_AXG_25

VCC_AXG_26

VCC_AXG_27

VCC_AXG_28

VCC_AXG_29

VCC_AXG_30

VCC_AXG_31

VCC_AXG_32

VCC_AXG_33

VCC_AXG_34

VCC CORE

POWER

POWER

VCC SMVCC GFX

VCC SMVCC GFX

VCC_AXG_NCTF_1

VCC_AXG_NCTF_2

VCC_AXG_NCTF_3

VCC_AXG_NCTF_4

VCC_AXG_NCTF_5

VCC_AXG_NCTF_6

VCC_AXG_NCTF_7

VCC_AXG_NCTF_8

VCC_AXG_NCTF_9

VCC_AXG_NCTF_10

VCC_AXG_NCTF_11

VCC_AXG_NCTF_12

VCC_AXG_NCTF_13

VCC_AXG_NCTF_14

VCC_AXG_NCTF_15

VCC_AXG_NCTF_16

VCC_AXG_NCTF_17

VCC_AXG_NCTF_18

VCC_AXG_NCTF_19

VCC_AXG_NCTF_20

VCC_AXG_NCTF_21

VCC_AXG_NCTF_22

VCC_AXG_NCTF_23

VCC_AXG_NCTF_24

VCC_AXG_NCTF_25

VCC_AXG_NCTF_26

VCC_AXG_NCTF_27

VCC_AXG_NCTF_28

VCC_AXG_NCTF_29

VCC_AXG_NCTF_30

VCC_AXG_NCTF_31

VCC_AXG_NCTF_32

VCC_AXG_NCTF_33

VCC_AXG_NCTF_34

VCC_AXG_NCTF_35

VCC_AXG_NCTF_36

VCC_AXG_NCTF_37

VCC_AXG_NCTF_38

VCC_AXG_NCTF_39

VCC_AXG_NCTF_40

VCC_AXG_NCTF_41

VCC_AXG_NCTF_42

VCC_AXG_NCTF_43

VCC_AXG_NCTF_44

VCC_AXG_NCTF_45

VCC_AXG_NCTF_46

VCC_AXG_NCTF_47

VCC_AXG_NCTF_48

VCC_AXG_NCTF_49

VCC_AXG_NCTF_50

VCC_AXG_NCTF_51

VCC_AXG_NCTF_52

VCC_AXG_NCTF_53

VCC_AXG_NCTF_54

VCC_AXG_NCTF_55

VCC GFX NCTF

VCC GFX NCTF

VCC_AXG_NCTF_56

VCC_AXG_NCTF_57