1

2

3

4

5

6

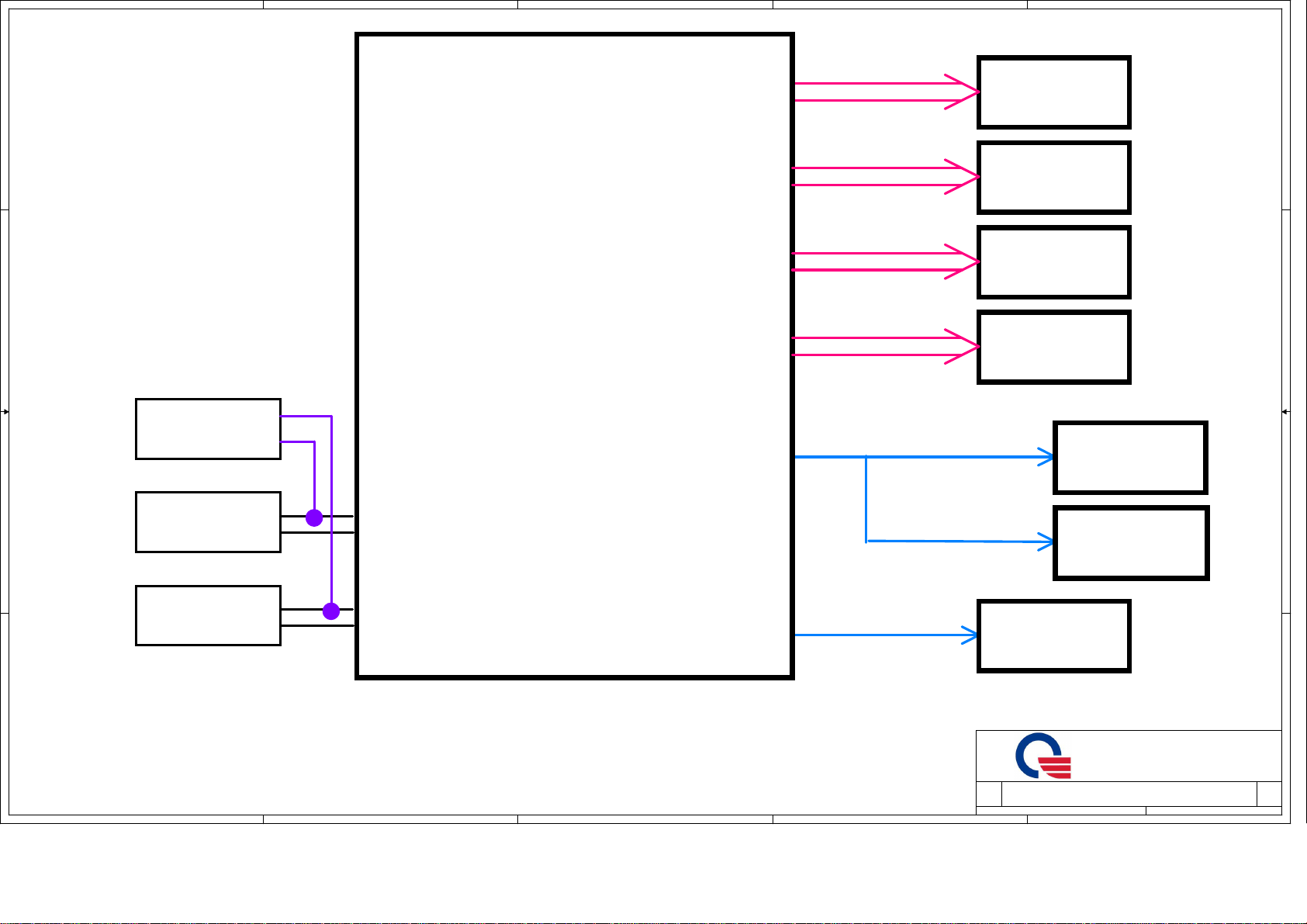

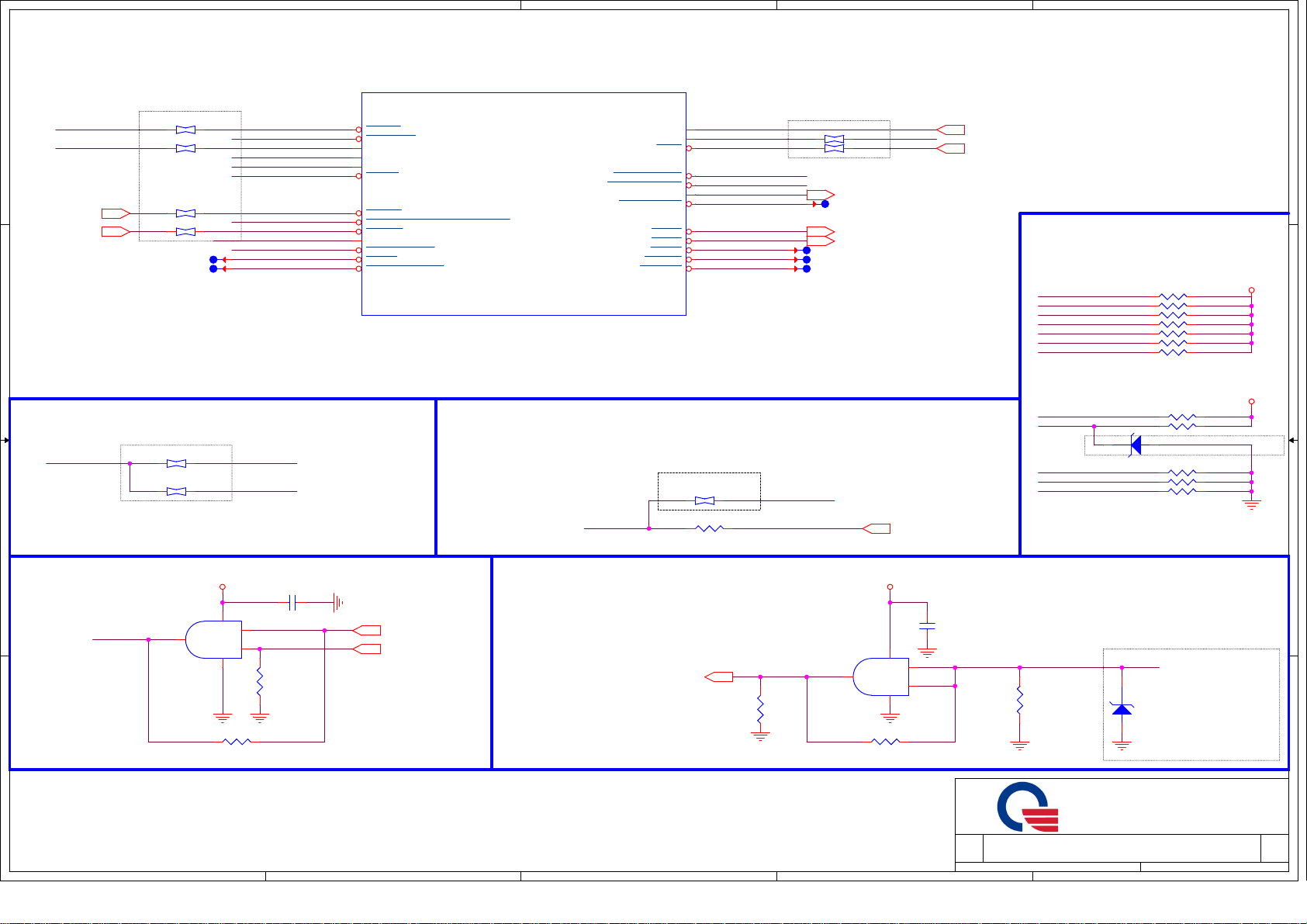

FH9 DIS (15.6") Broadwell Platform Block Diagram

7

8

01

A A

PCI-E x 4 lane

DDR3L SO-DIMM1

Max 8GB

PCB Stackups

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : SVCC

B B

C C

LAYER 6 : BOT

Wireless Dongle WEBCAM

P36 P34P28

RTS5227E-GRT

Card Reader

Max 8GB

USB3.0 Port x 1

Power off USB Charger

IC : SIL55584

P32

Touch Screen

RTL8111GS-CG

DDR3L 1333/1600 MT/s

P18

Channel A

DDR3L 1333/1600 MT/sDDR3L SO-DIMM2

P19

Channel B

USB3.0 Interface

P32 P32

USB3.0 Port x 2

USB2.0 Interface

P35

USB2.0 Port x 1

PCI-E Interface

WLAN / BT Combo

P29P30

NGFF 2230 CONLAN Controller

P34

P32

DDR3L CHA

DDR3L CHB

Broadwell U

USB3.0

Processor : Daul Core

Power : 15/28 (Watt)

Package : BGA1168

Size : 40 x 24 (mm)

USB2.0

PCI-E

INTEL

Processor

P6 ~ 17

eDP

DDI

I2C

SATA

EDP Interface

DDI Interface

NFC(Felica)

SATA Interface

HDD/SSD/Hybrid HDD

AMD Topaz-S3 XT (64b)

Power : 25 Watt

Package : FCBGA631

Size : 23 x 23 mm

P20 ~ 24

27MHz

RTD2132N-CG

eDP to LVDS Converter

RTD2168N-CG

PS8407A

Level shifter

ODD

P33P33

VRAM DDR3 256Mx16bitx4pcs

Max 2GB

Package : FCBGA96

LVDS Interface LCD Conn

P27

VGA Interface

P26

P25

15.6” FHD/HD panel

VGA ConnDP to VGA Converter

HDMI Conn

P28

P26

P28P28

Green CLK

25MHz

P31

Azalia

HDA

Green CLK

24MHz

SPI

Green CLK

32.768KHz

BIOS/EC ROM

4

Combo Jack

(Mic-in/HP-out)

P31

ALC283

Audio Codec

Speaker x 2

D D

1

2

P31

3

LPC

P10

LPC Interface

IT8587E/FX

Embedded Controller

5

P37

Keyboard

FAN Control

Touch Pad

HALL Sensor

6

P35

P35

P35

P34

TPM CON

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

P35

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

FH9

FH9

PROJECT :

PROJECT :

PROJECT :

FH9

1 48Wednesday, November 19, 2014

1 48Wednesday, November 19, 2014

1 48Wednesday, November 19, 2014

8

2A

2A

2A

1

2

3

4

5

6

7

8

02

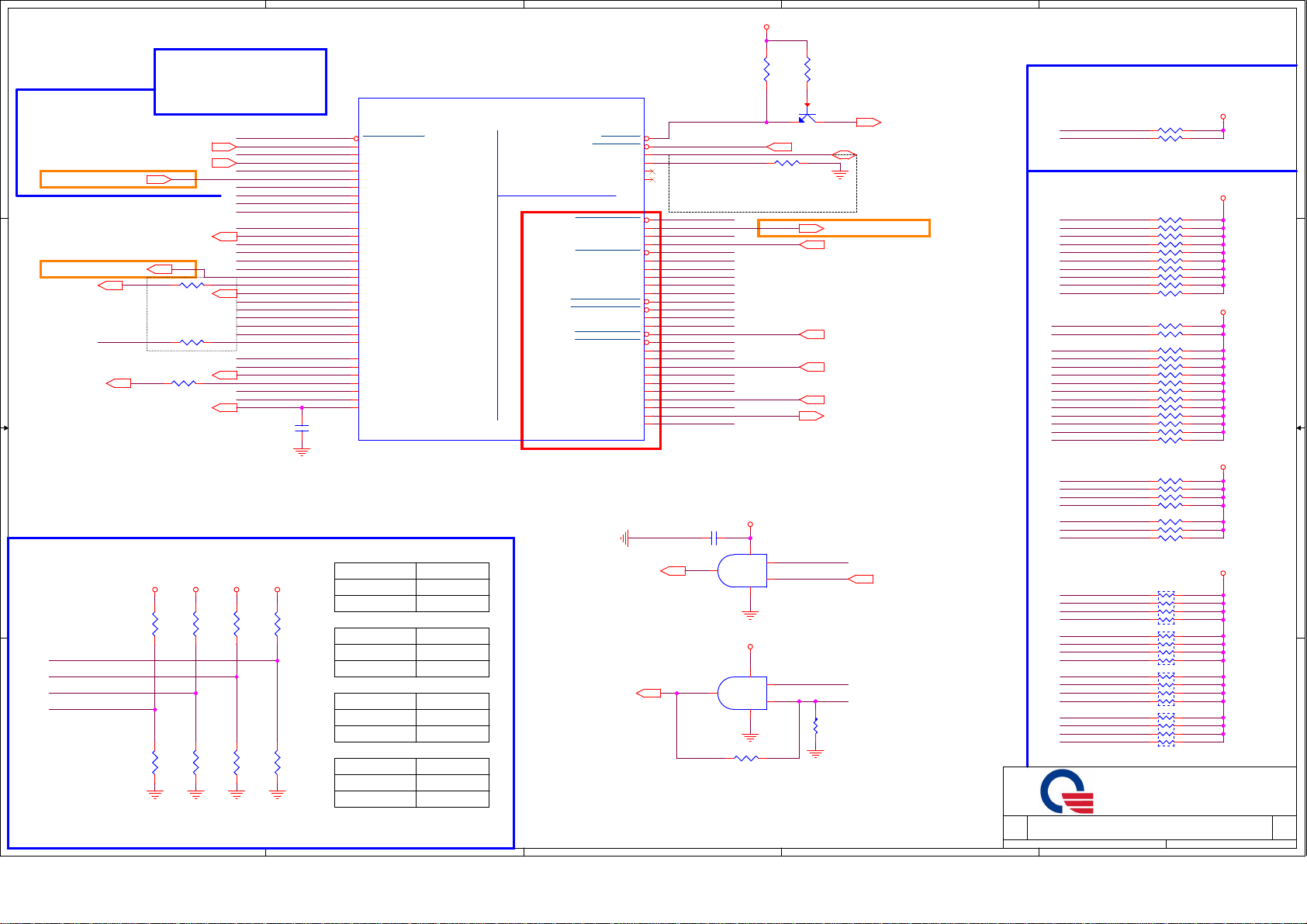

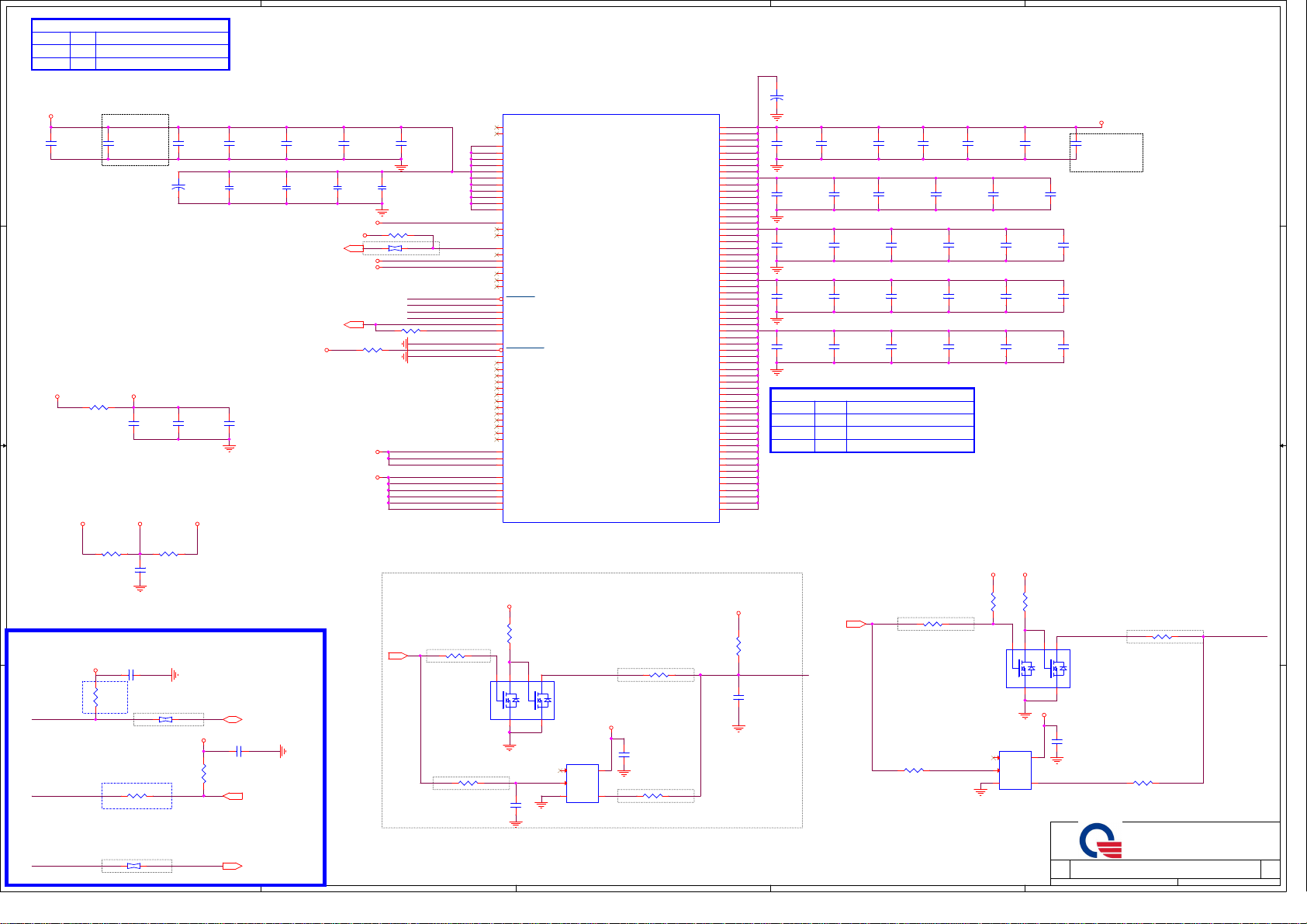

Table of Contents

PAGE DESCRIPTION

Block Diagram

01

A A

B B

C C

D D

Front Page

02

Power Sequence

03

Clock Distribution

04

SMBus Address

05

BDW MCP(Display/eDP)

06

BDW MCP(Memory)

07

BDW PCH(GPIO/LPIO/MISC)

08

BDW PCH(PCIE/USB)

09

BDW PCH(RTC/HDA/SATA)

10

BDW PCH(CLK/LPC/SPI/SMB)

11

BDW PCH(Power management)

12

BDW MCP(Power)

13

BDW MCP(GND/DAISY/RSVD)

14

BDW MCP(CFG)

15

BDW PCH(Power)

16

BDW MCP(Sideband)

17

DDR3L DIMM-1-RVS(H4.0)

18

DDR3L DIMM-2-RVS(H4.0)

19

TOPAZ_S3_PCIE_Interface

20

TOPAZ_S3_Main/DP Power

21

TOPAZ_S3_GND/LVDS/Strap

22

TOPAZ_S3_Power

23

TOPAZ_S3_MEM_Interface

24

TOPAZ_S3_VRAM_DDR3 BGA96

25

DP to VGA (RTD2168)/CRT

26

eDP to LVDS (RTD2132N-CG)

27

HDMI/LVDS

28

LAN RTL8111GS/RJ45 conn

29

Card Reader (RTS5227E)

30

Audio ALC283

31

USB3.0/Charger/USB2.0

32

HDD/ODD/LED

33

WLAN/BT/ NFC/MMB/PWR

34

KB/FAN/TP/TPM/TS

35

G-CLK/WL Dongle/HOLE

36

EC_IT8587

37

VIN/CHARGER-ISL88732

38

SYSTEM 5V/3V(TPS51225RUK)

39

1.05V-G5335

40

DDR3L 1.35V(RT8231AGQW)

41

SWITCH

42

CPU_CORE[NCP81101B) 28W

43

VGA CORE(INTERSIL 62771)

44

1.5GPU/0.95_GPU(RT8068A)

45

1.8V_GPU&3V_GPU

46

PWR Delivery/RESET/PWROK

47

Change History

48

1

Voltage Rails

Power S0

3V_RTC

VIN 19V

5V_AUX 5V

3V_S5

5V_S3

3VDUAL_LAN

3V_WLAN

5V_S0

3V_S0

1.5V_S0 1.5V

1.05V_S0

VGA_CORE

3V_GPU

1.8V_GPU

1.5V_GPU

0.95V_GPU

2

S4

3V

ON

ON ON

ON ON ON

ON

ON ON OFF

S5

G3

ON ON ON ON OFF

3.3V

5V5V_S5

3.3V

1.35V1.35V_S3

5V

3.3V

3.3V

5V S0_ON_1

3.3V

ON ON ON ON OFF

ON

ON ON

ON

ON OFF

ON ON

OFF

OFF OFF

ON

ON

OFFOFFONON

OFF

OFF

OFF

OFFOFFONON

OFF

ON OFF OFFOFFOFF

OFFON OFF OFF OFF

OFF

ON

OFF

OFF

OFF

ON OFF OFF OFF OFF

1.05V

1.05V1.05V_VCCST

0.675VDDR_VTERM

1.7VVCC_CORE

1V

3.3V

1.8V

1.5V

0.95V

OFF OFF OFF

ON

ON

ON

OFF OFF OFF OFF

OFF

OFFOFFOFFOFF

ON OFF OFF OFF OFF

OFF OFF OFFON OFF

OFF OFF OFFON OFF

OFF

OFF OFFON OFF

OFF

OFF OFFON OFF

OFF

OFF OFFON OFF

3

4

Ctl SignalS3Voltage

Adaptor in

Adaptor in

Adaptor in3V_AUX

S5_ON

S5_ON

S3_ON

S3_ON

LAN_ON_EC

WLAN_ON

S0_ON_2

S0_ON_3

S0_ON_1

S0_ON_1

DDR_PG

H_VR_EN_MCP

1.8VGPU_PG

GPU_ON

GPU_ON

1.8VGPU_PG

GPU_ON

Function List

USB2

Co-lay USB3.0

Port 0

Port 1

Co-lay USB3.0

Port 2

Co-lay USB3.0

Touch screen

Port 3

Port 4

Port 5

Port 6

Port 7

Camera

USB2.0 Conn

Bluetooth

USB HUB

Function Select

TOPAZ + VRAM

S@

RTD2132N-CG

L@

Internal eDP

E@

RTD2168

V@

NFC

N@

MMB

M@

Touch screen

TS@

Wireless Dongle

WL@

5

PCIE

Port 1 Card Reader eDP Port 1

Port 2 USB3.0 Conn eDP Port 2

Port 3 WLAN

Port 4

GLAN

Port 5 GPU(TOPAZ)

6

DDI Port 1

DDI Port 2

LVDS or eDP

NC

HDMI

CRT

USB3Display

Port 1

USB3.0 Conn Port 0

Port 2

USB3.0 Conn

Port 3

Card Reader

Port 4 USB3.0 Conn

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

Port 1

Port 2

Port 3 NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

FRONT PAGE

FRONT PAGE

FRONT PAGE

SATA

FH9

FH9

FH9

8

HDD

ODD

NC

2A

2A

2 48Wednesday, November 19, 2014

2 48Wednesday, November 19, 2014

2 48Wednesday, November 19, 2014

2A

5

4

3

2

1

FH9

FH9

FH9

03

3 48Wednesday, November 19, 2014

3 48Wednesday, November 19, 2014

3 48Wednesday, November 19, 2014

2A

2A

2A

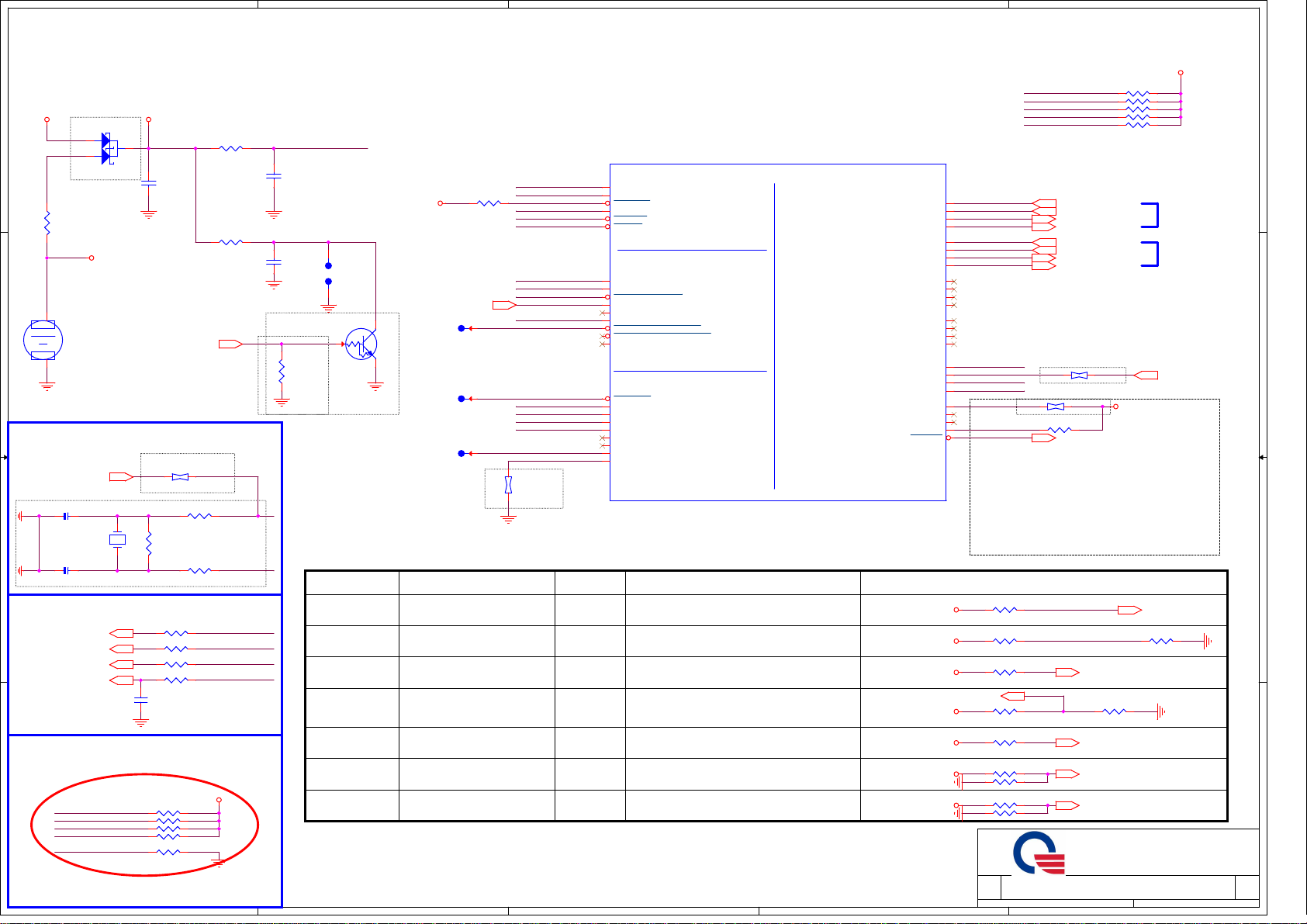

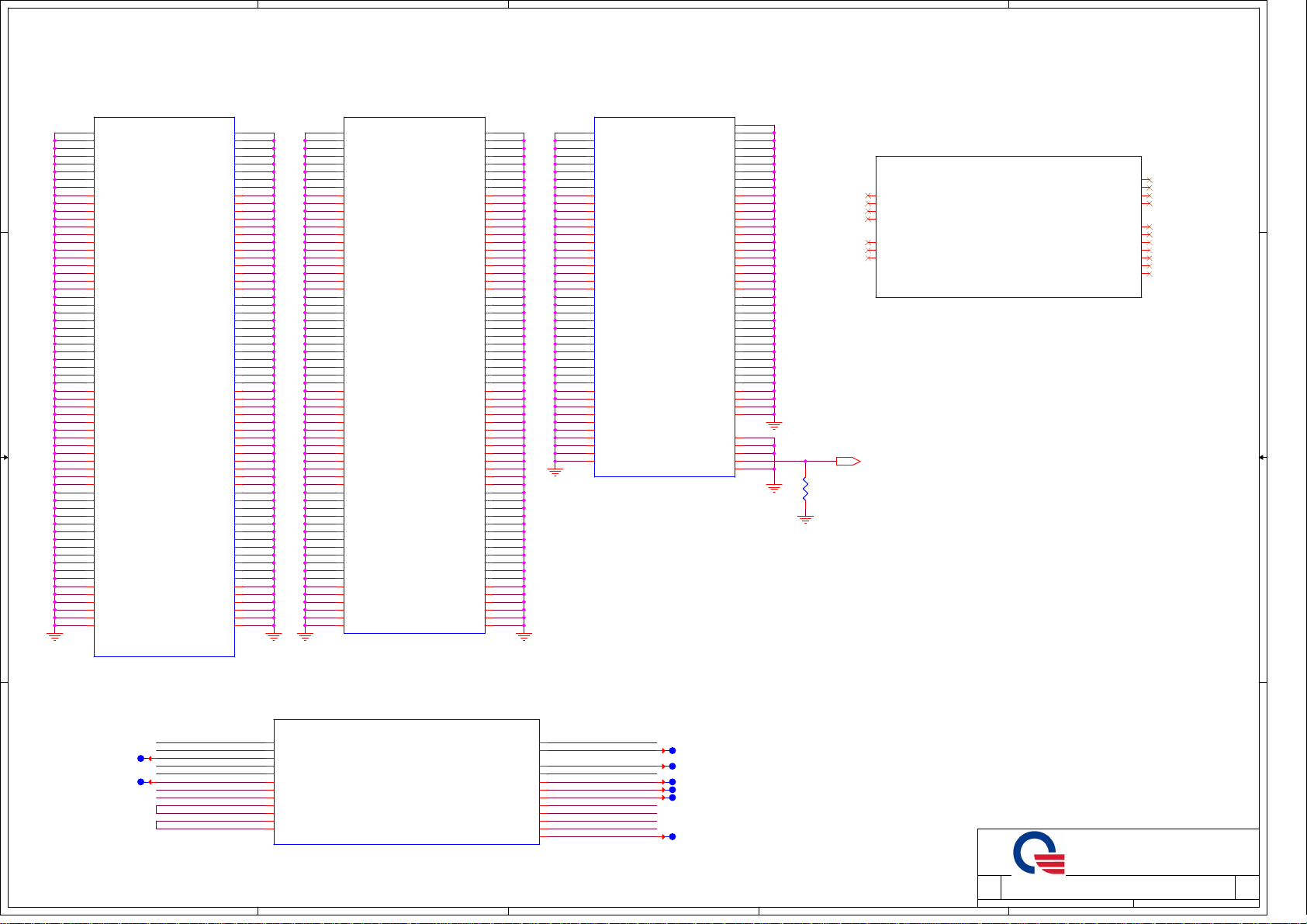

System Power On Sequencing Timing Diagram

3V_RTC

RTC_RST#

D D

VIN

5V_AUX/3V_AUX

NBSWON#

S5_ON

5V_S5/3V_S5

RSMRST#

SUSCLK

DNBSWON#

SUSC#

SUSB#

C C

S3_ON

5V_S3/1.35V_S3

S0_ON_1

1.05V_S0/5V_S0

DDR_VTERM

S0_ON_2

3V_S0

S0_ON_3

1.5V_S0

HWPG

B B

H_VR_EN_MCP

MPWROK

VCC_CORE

IMVP_PWRGD

Clock outputs

H_CPUPWRGD

SYS_PWROK

SUS_STAT#

PLTRST#

A A

System Power Sequence

T1: S5_ON TO RSMRST# = 20ms (spec:mini 10ms)

T2: S0_ON_1 TO S0_ON_2 = 500us

T3: S0_ON_2 TO VRON = 10ms

T4: HWPG TO MPWROK = 110ms (spec:>5~ 99ms)

T5: H_CPUPWRGD to PLTRST# >1ms

5

Coin Battey PCH

+3V_RTC Delay PCH

AC/DC IN All VR Input

VR Always Power

Power Button EC

EC S5 Enable

VR

EC

PCH EC

EC

PCH

PCH

EC

VR

EC

VR

DDR Power VR

EC

VR

EC

VR

All System PWROK

CPU

EC

CPU Core Power VR

CPU Core Power VR

PCH

PCH

PCH

PCH

T1

T2

T3

T4

valid

T5

4

S5 Power

PCH RSMRST#

PCH PWRBTN#

S4/S5

S3

S3 Enable

S3 Power

S0 Enable

S0 Power

Memory VREF Power

S0 Enable

S0 Power

S0 Enable

S0 Power

EC

PWM

PCH PWROK

CPU Core Power

CPU

System Clock

CPU PROCPWRGOOD

PCH SYS_PWROK

Platform Reset

3

dGPU Power On/Off Sequencing Timing Diagram

GPU_ON

3V_GPU

1.8V_GPU

1.8VGPU_PG

0.95V_GPU

1.5V_GPU/VGA_CORE

dGPU Power Sequence

T6:1.8V_GPU to 1.5V_GPU > 10us

T7:3V_GPU to 1.5V_GPU < 20ms

T8:1.5V_GPU to 3V_GPU < 20ms

2

T6

T7

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power Sequence

Power Sequence

Power Sequence

T8

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

5

4

3

2

1

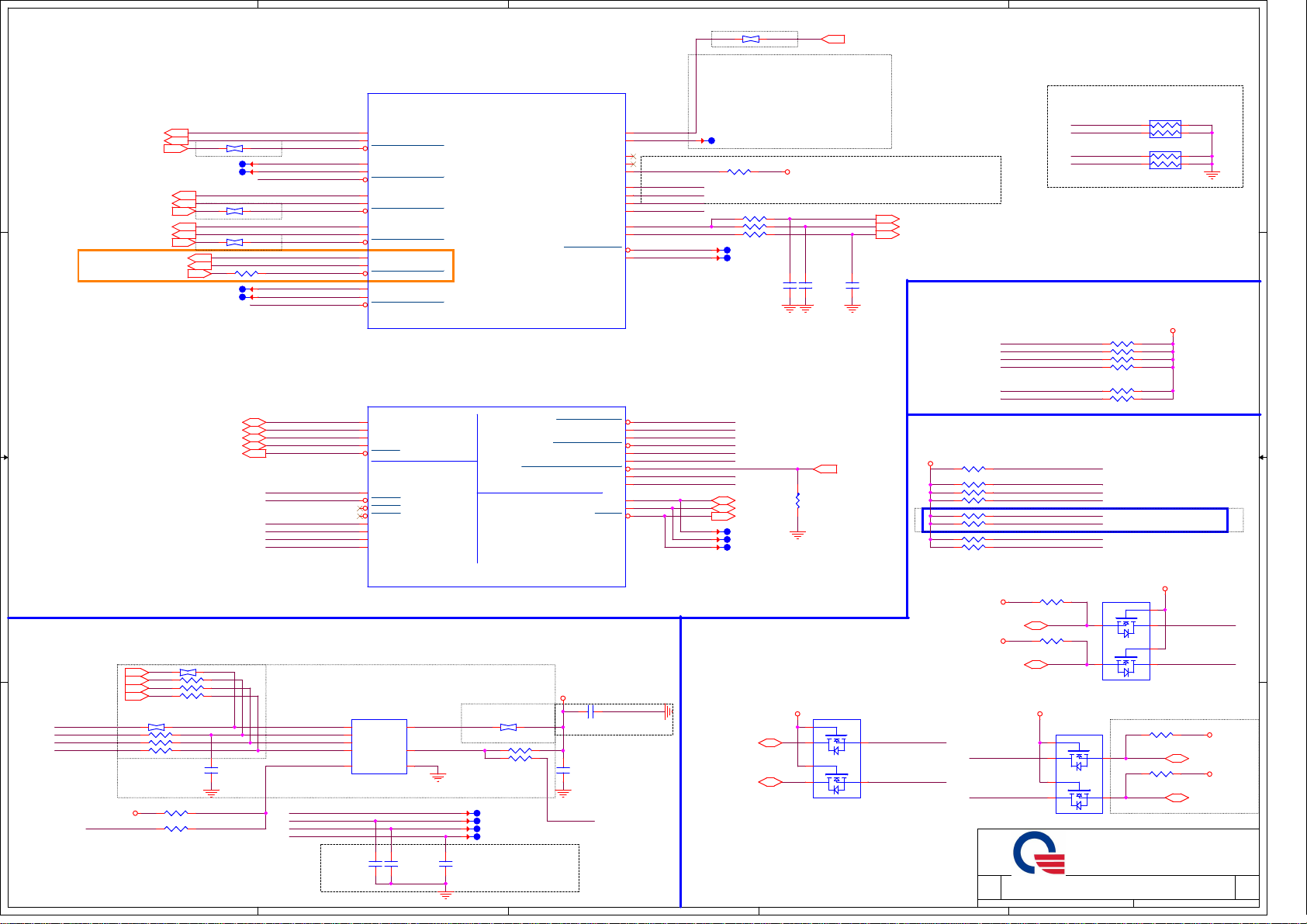

CLKOUT_PCIE_P2

CLKOUT_PCIE_N2

D D

CLKOUT_PCIE_P3

CLKOUT_PCIE_N3

CLK_PCIE_WLANP

100MHz PCIE

CLK_PCIE_WLANN

CLK_PCIE_LANP

100MHz PCIE

CLK_PCIE_LANN

WLAN

REFCLK+

REFCLK-

LAN

REFCLK+

REFCLK-

04

Broadwell-U

CLKOUT_PCIE_P0

CLKOUT_PCIE_N0

C C

CLKOUT_PCIE_P4

CLKOUT_PCIE_N4

CLK_PCIE_CARDP

100MHz PCIE

CLK_PCIE_CARDN

CLK_PCIE_DGPUP

100MHz PCIE

CLK_PCIE_DGPUN

Card Reader

REFCLK+

REFCLK-

GPU

REFCLK+

REFCLK-

Buffered mode

G-CLK

CLKOUT_LPC_0

B B

24Mhz

Xtal

PCLK_DEBUG

33MHz PCI

PCLK_TPM

33MHz PCI

DEBUG CARD

RESERVED

TPM

LCLK

32.768Khz

Xtal

A A

5

4

3

CLKOUT_LPC_1

CLK_33M_KBC

33MHz PCI

2

EC ITE 8587

LPCCLK

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

Clock Distribution

Clock Distribution

Clock Distribution

FH9

FH9

FH9

4 48Wednesday, November 19, 2014

4 48Wednesday, November 19, 2014

4 48Wednesday, November 19, 2014

1

2A

2A

2A

5

4

3

2

1

SMB_RUN_CLK

SMB_RUN_DAT

05

3V_S0 3V_S0

D D

3V_S0

R R

G

S

D

NMOS

S

D

NMOS

3V_AUX 3V_AUX

CHARGER

BQ24707RGRR

BATTERY

3V_S0 3V_S0

R R

CGCLK_SMB

CGDAT_SMB

Address

:

0x94,0x96, 0x6A

LCD Converter

3V_S0

R R

G

EC

ITE

C C

IT8587E/EX

(128 Pin LQFP)

16mm x 16 mm

MBCLK0

MBDATA0

MBCLK1

S

S

NMOS

NMOS

D

D

R R

CIIC_SCL

CIIC_SDA

Address:0x64,0x68

DP to VGA

MBDATA1

3V_GPU

3V_GPU

Address:0X41h

AMD TOPAZ

23 x 23 (mm)

3V_S5

3V_S5

3V_S0 3V_S0

Address:0xA0h Address:0xA4h

SO-DIMM A

SO-DIMM B

3V_GPU

G

NMOS

NMOS

R

R

DS

DS

MBCLK_GPU

MBDATA_GPU

3V_S0

R R

G

B B

SMB_PCH_CLK

SMB_PCH_DAT

NMOS

S

NMOS

3V_S5

DS

D

3V_S5

R R

SMB_RUN_CLK

SMB_RUN_DAT

3V_AUX 3V_AUX

R R

MBDATA0

MBCLK0

INTEL

Broadwell

40 x 24 (mm)

A A

5

SMB_ME1_DAT

SMB_ME1_CLK

3V_S5

SMB_ME0_CLK

SMB_ME0_DAT

R R

3V_S5

R R

4

3V_S5

G

NMOS

NMOS

3V_S0

G

S D

NMOS

NMOS

DS

DS

DS

R R

3V_S0 3V_S0

R R

NFC_SCL

NFC_SDA

Address:0x29h

NFC

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

SMBUS Address

SMBUS Address

SMBUS Address

FH9

FH9

FH9

5 48Wednesday, November 19, 2014

5 48Wednesday, November 19, 2014

1

5 48Wednesday, November 19, 2014

2A

2A

2A

5

4

3

2

1

06

Broadwell Type-U ULT (DISPLAY)

PCIE

BDW_ULT_DDR3L

1 OF 19

BDW_ULT_DDR3L

9 OF 19

EDPDDI

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_COMP

DP_UTIL

CRT_SCL

CRT_SDA

R373

100K_4

EDP_TXN0 27

EDP_TXP0 27

EDP_TXN1 28

EDP_TXP1 28

T25

T24

T29

T27

EDP_AUXN 27

T6

T5

T30

R364

V@100K_4

EDP_AUXP 27

INT_HDMI_SCL 28

INT_HDMI_SDA 28

CRT_AUXN 26

CRT_AUXP 26

INT_HDMI_HPD 28

CRT_HPD 26

EDP_HPD 27,28

R135 24.9/F_4

EDP_RCOMP

24.9 +/- 1% pull to VCCIOA_OUT

Trace Width: 20mils(trace)

Spacing: 25mils

Length: 100mils Max

+VCCIOA_OUT

GPIO PU/PD

PCH_GPIO77

PCH_GPIO78

PCH_GPIO79

PCH_GPIO80

PCH_GPIO54

PCH_GPIO55

PCH_GPIO52

PCH_GPIO51

PCH_GPIO53

CRT_SCL

CRT_SDA

R150 10K_4

R434 10K_4

R149 10K_4

R428 10K_4

R413 10K_4

R168 10K_4

R419 10K_4

R153 10K_4

R417 10K_4

R131 V@2.2K_4

R363 V@2.2K_4

3V_S0

U31A

D D

INT_HDMI_TXDN228

INT_HDMI_TXDP228

INT_HDMI_TXDN128

INT. HDMI

VGA

C C

INT_HDMI_TXDP128

INT_HDMI_TXDN028

INT_HDMI_TXDP028

INT_HDMI_TXCN28

INT_HDMI_TXCP28

CRT_TXDN026

CRT_TXDP026

CRT_TXDN126

CRT_TXDP126

PCH_BRIGHT27,28

PCH_BLON28,37

PCH_VDDEN28

T26

T28

PCH_GPIO77

PCH_GPIO78

PCH_GPIO79

PCH_GPIO80

PCH_GPIO55

PCH_GPIO52

PCH_GPIO54

PCH_GPIO51

PCH_GPIO53

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

AD4

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U31I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

Core

Core

Core

Core

Core

eDP SIDEBAND

Core

Core

Core

Core

B B

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

BDW MCP(DISPLAY/eDP)

BDW MCP(DISPLAY/eDP)

BDW MCP(DISPLAY/eDP)

FH9

FH9

FH9

2A

2A

2A

6 48Wednesday, November 19, 2014

6 48Wednesday, November 19, 2014

6 48Wednesday, November 19, 2014

1

5

4

3

2

1

Boardwell Type-U ULT (DDR3L CHA)

BDW_ULT_DDR3L

3 OF 19

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_CLKN0

M_A_CLKP0

M_A_CLKN1

M_A_CLKP1

M_A_CKE0

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_RAS#

M_A_WE#

M_A_CAS#

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_CLKN0 18

M_A_CLKP0 18

M_A_CLKN1 18

M_A_CLKP1 18 M_B_CLKN1 19

M_A_CKE0 18

M_A_CKE1 18

M_A_CS#0 18

M_A_CS#1 18

T16

M_A_RAS# 18

M_A_WE# 18

M_A_CAS# 18

M_A_BS#0 18

M_A_BS#1 18

M_A_BS#2 18

M_A_A[15:0] 18

M_A_DQSN[7:0] 18

M_A_DQSP[7:0] 18

SM_VREF_CA 19

SM_VREF_DQ0 18

SM_VREF_DQ1 19

M_B_DQ[63:0]19

M_A_DQ[63:0]18

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

U31C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

Boardwell Type-U ULT (DDR3L CHB)

BDW_ULT_DDR3L

4 OF 19

DDR CHANNEL B

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

U31D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_B_CLKN0

M_B_CLKP0

M_B_CLKN1

M_B_CLKP1

M_B_CKE0

M_B_CKE1

M_B_CS#0

M_B_CS#1

M_B_RAS#

M_B_WE#

M_B_CAS#

M_B_BS#0

M_B_BS#1

M_B_BS#2

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_CLKN0 19

M_B_CLKP0 19

M_B_CLKP1 19

M_B_CKE0 19

M_B_CKE1 19

M_B_CS#0 19

M_B_CS#1 19

T15

M_B_RAS# 19

M_B_WE# 19

M_B_CAS# 19

M_B_BS#0 19

M_B_BS#1 19

M_B_BS#2 19

M_B_A[15:0] 19

07

M_B_DQSN[7:0] 19

M_B_DQSP[7:0] 19

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

BDW MCP(LPDDR3)

BDW MCP(LPDDR3)

BDW MCP(LPDDR3)

FH9

FH9

FH9

7 48Wednesday, November 19, 2014

7 48Wednesday, November 19, 2014

1

7 48Wednesday, November 19, 2014

2A

2A

2A

5

4

3

1.05V_VCCST

2

1

Broadwell Type-U ULT(GPIO,LPIO,MISC)

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

FH9

FH9

FH9

08

3V_S0

3V_S5

3V_S0

3V_S5

3V_S0

8 48Wednesday, November 19, 2014

8 48Wednesday, November 19, 2014

8 48Wednesday, November 19, 2014

2A

2A

2A

GPIO27

2

1 3

Q28

PMBT3904

EC_RCIN# 37

GPU_PWRGD

PLTRST#

PLTRST#

NFC_RST#

R411

1K_4

S5_ON 37,39

SERIRQ 35,37

GPU_ON_PCH 20,37

BBS 10

ODD_DM#_PCH 33

NFC_DETECT# 34

PCH_GPIO66 10

ODD_PWR_EN 33

PLTRST# 12,20,29,30,34,35,37

R275

100K_4

For GPU use

2

CPU MISC PU/PD

EC_RCIN#

SERIRQ

R183 10K_4

R161 10K_4

GPIO PU/PD

PCH_GPIO58

PCH_GPIO44

PCH_GPIO24

PCH_GPIO13

SIO_EXT_SWI#

PCH_GPIO56

PCH_GPIO45

PCH_GPIO9

PCH_GPIO14

PCH_GPIO59

GPU_PWRGD

ODD_PWR_EN

ODD_DM#_PCH

PCH_GPIO38

PCH_GPIO39

PCH_GPIO5

GPU_RST#_PCH

GPU_ON_PCH

PCH_GPIO16

SIO_EXT_SCI#

SIO_EXT_SMI#_49

NFC_DETECT#

PCH_GPIO7

NFC_DWL_REQ_R

PCH_GPIO27

PCH_GPIO12

PCH_GPIO25

PCH_GPIO26

PCH_GPIO10

PCH_GPIO47

SIO_EXT_SMI#_46

PCH_GPIO88

PCH_GPIO85

PCH_GPIO87

PCH_GPIO83

PCH_GPIO89

PCH_GPIO90

PCH_GPIO91

PCH_GPIO92

PCH_GPIO71

PCH_GPIO64

PCH_GPIO93

PCH_GPIO94

PCH_GPIO76

PCH_GPIO67

PCH_GPIO69

PCH_GPIO65

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

R224 10K_4

R464 10K_4

R180 10K_4

R504 10K_4

R493 10K_4

R211 10K_4

R202 10K_4

R468 10K_4

R217 10K_4

R510 10K_4

R156 *10K_4

R387 10K_4

R403 10K_4

R409 10K_4

R144 10K_4

R177 10K_4

R467 *10K_4

R151 10K_4

R447 10K_4

R433 10K_4

R450 10K_4

R147 10K_4

R143 10K_4

R129 10K_4

R227 10K_4

R507 10K_4

R231 10K_4

R476 10K_4

R216 10K_4

R195 10K_4

R191 10K_4

1

3

5

7

1

3

5

7

RN4 10KX4

1

3

5

7

RN1 10KX4

1

3

5

7

RN3 10KX4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BDW PCH(GPIO/LPIO/MISC)

BDW PCH(GPIO/LPIO/MISC)

BDW PCH(GPIO/LPIO/MISC)

1

With Intel LAN:

Connect to LANWAKE# pin on the LAN

Without Intel LAN:

Used to wake event from DSx

D D

PCH_GPIO76

SIO_EXT_SWI#37

For GPU use

GPU_PWRGD37,44,45

PCH_GPIO1510

MOUSE_CNCT#36

For GPU use

GPU_RST#_PCH20,37

SIO_EXT_SMI#37

C C

NFC_DWL_REQ34

B B

SIO_EXT_SMI#

R583 *0_4

SIO_EXT_SCI#37

R584 0_4

B-34

DEVSLP033

R130 N@0_4

ACZ_SPKR10,31

SIO_EXT_SWI#

PCH_GPIO12

PCH_GPIO16

GPU_PWRGD

PCH_GPIO24

PCH_GPIO27

NFC_RST#

PCH_GPIO26

PCH_GPIO56

PCH_GPIO58

PCH_GPIO59

PCH_GPIO44

PCH_GPIO47

GPU_RST#_PCH

SIO_EXT_SMI#_49

SIO_EXT_SCI#

PCH_GPIO71

PCH_GPIO13

PCH_GPIO14

PCH_GPIO25

PCH_GPIO45

SIO_EXT_SMI#_46

PCH_GPIO9

PCH_GPIO10

NFC_DWL_REQ_R

PCH_GPIO38

PCH_GPIO39

C283

*100P/50V_4

U31J

P1

BMBUSY/GPIO76

AU2

AM7

AD6

AD5

AN5

AD7

AN3

AG6

AP1

AL4

AT5

AK4

AB6

AT3

AH4

AM4

AG5

AG3

AM3

AM2

Y1

T3

U4

Y3

P3

Y2

P2

C4

L2

N5

V2

Sus

GPIO8

LAN_PHY_PWR_CTRL/GPIO12

Sus

GPIO15

Core

GPIO16

Core

GPIO17

Sus

GPIO24

DSW

GPIO27

Sus

GPIO28

Sus

GPIO26

Sus

GPIO56

Sus

GPIO57

Sus

GPIO58

Sus

GPIO59

Sus

GPIO44

Sus

GPIO47

Core

GPIO48

Core

GPIO49

Core

GPIO50

HSIOPC/GPIO71

Sus

GPIO13

Sus

GPIO14

DSW

GPIO25

Sus

GPIO45

Sus

GPIO46

Sus

GPIO9

Sus

GPIO10

DEVSLP0/GPIO33

SDIO_POWER_EN/GPIO70

DEVSLP1/GPIO38

DEVSLP2/GPIO39

SPKR/GPIO81

Board ID:

3V_S0

3V_S0

3V_S0 3V_S0

R408

R393

*10K_4

*10K_4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

A A

5

R394

10K_4

R415

10K_4

R157

R397

*10K_4 RN2 10KX4

*10K_4

R155

R399

10K_4

10K_4

BOARD_ID0

UMA

DIS

BOARD_ID1

LVDS

eDP

BOARD_ID2

VGA

Non-VGA

BOARD_ID3

TOUCH

Non-TOUCH

4

BDW_ULT_DDR3L

SERIRQ

RSVD

RSVD

D60

V4

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

Core

DSW

GPIO

Core

Core

Core

Core

Core

10 OF 19

Core

Note:

GSPI,UART,I2C and SDIO are only supported on

the system that enable Connected Stanby

CPU/

MISC

Core

SERIAL IO

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

Core

PCH_GPIO0

THRMTRIP

Core

RCIN/GPIO82

PCH_OPI_RCOMP

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

GPU_PWRGD_SVID_REG44

0

1

PCH_GPIO1

0

1

PCH_GPIO3

NFC_RST_BUFF#34

0

1

PCH_GPIO4

0

1

3

PCH_THRMTRIP#

EC_RCIN#

SERIRQ

PCH_OPIRCOMP

PCH_OPI_RCOMP

50 +/- 1% pull to VSS

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

PCH_GPIO83

GPU_ON_PCH

PCH_GPIO85

PCH_GPIO87

PCH_GPIO88

PCH_GPIO89

PCH_GPIO90

PCH_GPIO91

PCH_GPIO92

PCH_GPIO93

PCH_GPIO94

BOARD_ID0

BOARD_ID1

ODD_DM#_PCH

BOARD_ID2

BOARD_ID3

PCH_GPIO5

NFC_DETECT#

PCH_GPIO7

PCH_GPIO64

PCH_GPIO65

PCH_GPIO67

ODD_PWR_EN

PCH_GPIO69

C263S@0.1U/10V_4_X7R

4

U15

*N@TC7SH08FU

4

R277 N@0_4

R400

1K_4

R512 49.9/F_4

3V_S0

2

1

U10

3 5

S@TC7SH08FU(F)

3V_S0

2

1

3 5

5

4

3

2

1

Broadwell Type-U ULT (PCIE,USB)

09

BDW_ULT_DDR3L

USB debug port

11 OF 19

PCIE USB

Sus

Sus

Sus

Sus

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

RSVD

RSVD

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB3_RXN1

USB3_RXP1

USB3_TXN1

USB3_TXP1

USB3_RXN2

USB3_RXP2

USB3_TXN2

USB3_TXP2

USB_BIAS

USB_OC0#

USB_OC1#

USB_OC3#

USBP0- 32

USBP0+ 32

USBP1- 32

USBP1+ 32

USBP2- 32

USBP2+ 32

USB_TS# 35

USB_TS 35

USB_C# 28

USB_C 28

USB_BT# 34

USB_BT 34

USB_Conn# 32

USB_Conn 32

USB_WL# 36

USB_WL 36

USB3_RXN1 32

USB3_RXP1 32

USB3_TXN1 32

USB3_TXP1 32

USB3_RXN2 32

USB3_RXP2 32

USB3_TXN2 32

USB3_TXP2 32

R198 22.6/F_4

USB_OC0# 32

MOUSE_ON 36

USB2.0 Port (Co-lay USB3.0)

USB2.0 Port (Co-lay USB3.0)

USB2.0 Port (Co-lay USB3.0)

Touch screen

Camera

Bluetooth

USB2.0 Port

Wireless Dongle

USB3.0

USB3.0

USBBIAS & USBBIAS#

Short the USBRBIAS and the USBRBIAS# pins and one end of 22.6 +/- 1% to GND

Route signal using 50 ohm single-ended impedance

Spacing: 15mils

Length: 500mils Max

3V_S5

USB_OC3#

USB_OC0#

USB_OC1#

R233 10K_4

R469 10K_4

R230 10K_4

G10

G11

G13

G17

G15

F10

E10

C23

C22

B23

A23

H10

B21

C21

B22

A21

F11

C29

B30

F13

B29

A29

F17

C30

C31

F15

B31

A31

E15

E13

A27

B27

U31K

F8

E8

E6

F6

PERN5_L0

PERP5_L0

PETN5_L0

PETP5_L0

PERN5_L1

PERP5_L1

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

PERN1/USB3RN3

PERP1/USB3RP3

PETN1/USB3TN3

PETP1/USB3TP3

PERN2/USB3RN4

PERP2/USB3RP4

PETN2/USB3TN4

PETP2/USB3TP4

RSVD

RSVD

PCIE_RCOMP

PCIE_IREF

For GPU use

PEG_RXN020

PEG_RXP020

D D

TOPAZ

WLAN(NGFF)

GLAN

C C

Card Reader

USB3.0

B B

PEG_TXN020

PEG_TXP020

PEG_RXN120

PEG_RXP120

PEG_TXN120

PEG_TXP120

PEG_RXN220

PEG_RXP220

PEG_TXN220

PEG_TXP220

PEG_RXN320

PEG_RXP320

PEG_TXN320

PEG_TXP320

PCIE_RXN_WLAN34

PCIE_RXP_WLAN34

PCIE_TXN_WLAN34

PCIE_TXP_WLAN34

PCIE_RXN_LAN29

PCIE_RXP_LAN29

PCIE_TXN_LAN29

PCIE_TXP_LAN29

PCIE_RXN_CARD30

PCIE_RXP_CARD30

PCIE_TXN_CARD30

PCIE_TXP_CARD30

USB3_RXN432

USB3_RXP432

USB3_TXN432

USB3_TXP432

PCIE_RCOMP

3K+/- 1% pull to VCCUSB3PLL

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

PCIE_IREF

Directly connect to VCCUSB3PLL

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

C141 S@0.1uF/16V/X7R_4

C152 S@0.1uF/16V/X7R_4

C131 S@0.1uF/16V/X7R_4

C138 S@0.1uF/16V/X7R_4

C166 S@0.1uF/16V/X7R_4

C170 S@0.1uF/16V/X7R_4

C156 S@0.1uF/16V/X7R_4

C164 S@0.1uF/16V/X7R_4

C466 0.1uF/16V/X7R_4

C467 0.1uF/16V/X7R_4

C468 0.1uF/16V/X7R_4

C469 0.1uF/16V/X7R_4

C465 0.1uF/16V/X7R_4

C471 0.1uF/16V/X7R_4

+V1.05S_AUSB3PLL

R117 3K/F_4

R120 *SHORT_4

B-9

PEG_TXN0_C

PEG_TXP0_C

PEG_TXN1_C

PEG_TXP1_C

PEG_TXN2_C

PEG_TXP2_C

PEG_TXN3_C

PEG_TXP3_C

PCIE_TXN_WLAN_C

PCIE_TXP_WLAN_C

PCIE_TXN_LAN_C

PCIE_TXP_LAN_C

PCIE_TXN_CARD_C

PCIE_TXP_CARD_C

PCIE_RCOMP

PCIE_IREF

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

BDW PCH(PCIE/USB)

BDW PCH(PCIE/USB)

BDW PCH(PCIE/USB)

FH9

FH9

FH9

2A

2A

2A

9 48Wednesday, November 19, 2014

9 48Wednesday, November 19, 2014

9 48Wednesday, November 19, 2014

1

5

4

3

2

1

HDD (Base)

NGFF SSD/HDD (Slate)

RTC Circuitry(RTC)

D D

VCCRTC_1

20MIL

A+-36

R569

1K/F_4

VCCRTC_2

20MIL

12

CN19

C C

LTS_AAA-BAT-054-K01

RTC XTAL 32.768KHz

CLKGEN_RTC_X136

A+-20

B-8

*18P/50V_4C520

*32.768KHZ/20PPM

B B

*18P/50V_4C522

HDA Audio (CLG)

ACZ_SYNC_AUDIO31

ACZ_RST#_AUDIO31

ACZ_SDOUT_AUDIO31

ACZ_BITCLK_AUDIO31

D34

BAT54CW

VCCRTC_2

Y5

3V_RTC3V_AUX

MP1-1

R506 *SHORT_4

2 1

R519 33_4

R513 33_4

R520 33_4

R528 33_4

C535

*0.1U/10V_4

20MIL

C526

1U/10V_4

CLR_CMOS37

R575 *0_4

R503

*10M_4

R576 *0_4

R501 20K/F_6

R505 20K/F_6

RTC_X1

RTC_X2

HDA_SYNC

HDA_RST#

HDA_SDOUT

HDA_BITCLK

SRTC_RST#

C514

1U/10V_4

RTC_RST#

C518

1U/10V_4

R582

*100K/F_4

CL1_CL2

*PAD

1 2

2

Q25

PDTC144EU

PCH Strap Table

Pin Name Strap description Sampled Configuration Schematic

HDA_SDO/I2S0_TXD

INTVRMEN

DSWVRMEN

GPIO15

RTC_X1

RTC_X2

3V_RTC

1 3

R526 1M_4

ACZ_SDIN0_AUDIO31

T52

T51

B-24C-1

T46

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BITCLK

HDA_SYNC

HDA_RST#

HDA_SDOUT

PCH_XDP_TRST_CPU_N

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAGX

PCH_EDM

R489

*SHORT_4

Flash Descriptor Security Override

Integrated 1.05V VRM enable ALWAYS

DeepSx Well On-Die VRM Enable ALWAYS

TLS Confidentiality RSMRST#

Broadwell Type-U ULT (RTC,HDA,JTAG,SATA)

BDW_ULT_DDR3L

RTC

AUDIO SATA

5 OF 19

JTAG

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

Core

SATA0GP/GPIO34

Core

SATA1GP/GPIO35

Core

SATA2GP/GPIO36

Core

SATA3GP/GPIO37

SATA_RCOMP

SATA_IREF

RSVD

RSVD

SATALED

3V_S5

3V_RTC

3V_RTC

3V_S5

B-9

AW5

AW8

AV11

AY10

AU12

AU11

AW10

AV10

AU62

AE62

AD61

AE61

AD62

AL11

AE63

PWROK

AY5

AU6

AV7

AV6

AU7

AU8

AY8

AC4

AV2

U31E

RTCX1

RTCX2

INTRUDER

INTVRMEN

SRTCRST

RTCRST

HDA_BCLK/I2S0_SCLK

HDA_SYNC/I2S0_SFRM

HDA_RST/I2S_MCLK

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_SDO/I2S0_TXD

HDA_DOCK_EN/I2S1_TXD

HDA_DOCK_RST/I2S1_SFRM

I2S1_SCLK

PCH_TRST

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

RSVD

RSVD

JTAGX

RSVD

0 = Enable Flash Descriptor security. (Int PD)

1 = Disable Flash Descriptor Security

0 = DCPSUSx are powered from an ext. power source

1 = Integrated VRM enabled (330K PU VccRTC)

0 = Disable Integrated DSW On-Die VRM

1 = Enable Integrated DSW On-Die VRM (Must be PU)

0 = Disable Intel ME Crypto TLS cipher suite (Int PD)

1 = Enable Intel ME Crypto Transport

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

PCH_GPIO34

V1

ODD_DP#_PCH_R

U1

PCH_GPIO36

V6

PCH_GPIO37

AC1

SATA_IREF

A12

L11

K10

SATA_RCOMP

C12

SATA_LED#

U3

R518 *1K_4

R515 330K_4

R514 330K_4

PCH_GPIO158

R197 8.2K_4

SATA_LED#

PCH_GPIO34

ODD_DP#_PCH_R

PCH_GPIO36

PCH_GPIO37

R174 10K_4

R445 10K_4

R440 10K_4

R171 10K_4

R456 10K_4

SATA_RXN2 33

SATA_RXP2 33

SATA_TXN2 33

SATA_TXP2 33

SATA_RXN1 33

SATA_RXP1 33

SATA_TXN1 33

SATA_TXP1 33

B-9

R439 *SHORT_4

B-9

R355 *SHORT_4

R356 3K/F_4

SATA_LED# 33

SATA_IREF

Directly connect to VCCASATA3PLL

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

SATA_RCOMP

3K+/- 1% pull to VCCASATA3PLL

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

HDA_SDOUT

PCH_INTVRMEN

+V1.05S_ASATA3PLL

DSWVRMEN 12

R200 *1K_4

R517 *330K_4

10

3V_S0

SATA HDD

SATA ODD

ODD_DP#_PCH 33

HDA_SDOUT 37

SPKR/GPIO81

No reboot mode setting PWROK

PCH JTAG Debug (CLG)

GSPI0_MOSI/GPIO86

A A

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAGX

PCH_JTAG_TCK

R486 *51_4

R487 *51_4

R215 *51_4

R485 *1K_4

R478 *51_4

5

1.05V_S0

SDIO_D0/GPIO66

Boot BIOS Strap Bit PWROK 0 = Boot from SPI

Top Swap Override PWROK 0 = Disable Top Swap mode. (Int PD)

4

0 = Disable No Reboot mode (Int PD).

1 = Enable No Reboot mode.

1 = Boot from LPC

1 = Enable Top Swap mode.

3

+V3.3S_1.8S_LPSS_SDIO

2

3V_S0

3V_S0

R181 *1K_4

R392 *1K_4

R396 *1K_4

R391 *1K_4

R389 1K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

ACZ_SPKR 8,31

BBS 8

PCH_GPIO66 8

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BDW PCH(RTC/HDA/SATA)

BDW PCH(RTC/HDA/SATA)

BDW PCH(RTC/HDA/SATA)

FH9

FH9

FH9

10 48Wednesday, November 19, 2014

10 48Wednesday, November 19, 2014

10 48Wednesday, November 19, 2014

1

2A

2A

2A

5

4

3

2

1

B-9

R358 *SHORT_4

PCH_XTAL24_IN 36

11

Broadwell Type-U ULT (CLK)

U31F

D D

Card

Reader

WLAN

LAN

Topaz

C C

CLK_PCIE_CARDN30

CLK_PCIE_CARDP30

PCIE_CLKREQ_CARD#30

CLK_PCIE_WLANN34

CLK_PCIE_WLANP34

PCIE_CLKREQ_WLAN#34

CLK_PCIE_LANN29

CLK_PCIE_LANP29

PCIE_CLKREQ_LAN#29

CLK_PCIE_DGPUN20

CLK_PCIE_DGPUP20

PCIE_CLKREQ_DGPU#21

For GPU use

R438 *SHORT_4

B-9

T3

T4

R190 *SHORT_4

R420 *SHORT_4

R154 S@0_4

T23

T22

PCIE_CLK_REQ0#

CLK_PCIE_N1

CLK_PCIE_P1

PCIE_CLK_REQ1#

PCIE_CLK_REQ2#

B-9

PCIE_CLK_REQ3#

B-9

PCIE_CLK_REQ4#

CLK_PCIE_N5

CLK_PCIE_P5

PCIE_CLK_REQ5#

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

Broadwell Type-U ULT (LPC/SPI/SMB/CLINK)

U31G

LPC_LAD034,35,37

LPC_LAD134,35,37

LPC_LAD234,35,37

LPC_LAD334,35,37

LPC_LFRAME#34,35,37

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

B B

PCH Dual SPI

EC & BIOS & ME F/W ROM 8MB

EC_CE#37

EC_SCK37

EC_SI37

EC_SO37

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

A A

3V_S5

PCH_SPI_IO2

R484 *SHORT_4

R451 0_4

R444 0_4

R481 0_4

R482 *SHORT_4

R418 33_4

R430 33_4

R483 33_4

R460 1K_4

R474 33_4

5

B-69

C490

*22P/50V_4

Use one 33-Ω series-resistor per device if using two SPI devices.

B-9B-25

15-Ω series resistor required if a single device is used.

PCH_SPI_CS0#_R

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_W P#

AU14

AW12

AY12

AW11

AV12

1

6

5

2

3

SOCKET PN:DG008000031

PCH_SPI_CS0#_R

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

*10P/50V_4

LAD0

LAD1

LAD2

LAD3

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

U32

CE#

SCK

SI

SO

HOLD#

WP#

W25Q64FVSSIQ

C476

VDD

VSS

4

8

7

4

C493

*10P/50V_4

BDW_ULT_DDR3L

Core

Core

Core

Core

Core

Core

BDW_ULT_DDR3L

LPC

PCH_SPI_HOLD#

C503

*10P/50V_4

CLOCK

SIGNALS

6 OF 19

SMBUS

Sus

SML1ALERT/PCHHOT/GPIO73

C-LINKSPI

7 OF 19

MP1-2

R432 *SHORT_4

R459 1K_4

R463 33_4

TP81

TP62

TP66

TP82

Reserve for RF

Sus

Sus

Sus

Sus

PCH_SPI_IO3

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

3V_S5

C255 *3.3P/50V/C0G_4

Reserve for RF

C488

0.1U/10V_4

XTAL24_IN

A25

XTAL24_OUT

B25

K21

M21

XCLK_BIASREF

C26

TESTLOW _0

C35

TESTLOW _1

C34

TESTLOW _2

AK8

TESTLOW _3

AL8

AN15

AP15

B35

A35

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

3

CLK_PCI_LPC

CLK_PCI_EC

SMBALERT#

SMB_PCH_CLK

SMB_PCH_DAT

SML0ALERT

SMB_ME0_CLK

SMB_ME0_DAT

SMB_ME1_CLK

SMB_ME1_DAT

T54

R114 3K/F_4

R250 22_4

R251 22_4

R521 22_4

T1

T2

C341

*10P/50V_4

CL_CLK 34

CL_DAT 34

CL_RST# 34

TP27

TP28

TP26

MBCLK137

MBDATA137

+V1.05S_AXCK_LCPLL

C340

*10P/50V_4

R276

100K_4

3V_S5

5

2

6

Q32

2N7002KDW/60V/115MA

B-38

B-8

DIFFCLK_BIASREF

3K+/- 1% pull to+1.05V

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

PCLK_DEBUG 34

PCLK_TPM 35

CLK_33M_KBC 37

C530

*10P/50V_4

CLK REQ PU (CLG)

SMBus

NFC_IRQ 34

SMB_ME1_CLK

43

SMB_ME1_DAT

1

2

PCIE_CLK_REQ1#

PCIE_CLK_REQ0#

PCIE_CLK_REQ2#

PCIE_CLK_REQ5#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

3V_S5

R212 10K_4

R470 10K_4

R488 2.2K_4

R475 2.2K_4

R480 499/F_4

R465 499/F_4

R492 2.2K_4

R490 2.2K_4

SMBus/Pull-up(CLG)

R477 4.7K_4

3V_S0

SMB_RUN_DAT18,19,27

R479 4.7K_4

3V_S0

SMB_RUN_CLK18,19,27

SMB_ME0_CLK

SMB_ME0_DAT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Do not short

the testlow pins together.

TESTLOW _0

TESTLOW _1

TESTLOW _2

TESTLOW _3

R201 10K_4

R437 10K_4

R189 10K_4

R443 10K_4

R423 10K_4

R165 10K_4

SMBALERT#

SML0ALERT

SMB_PCH_CLK

SMB_PCH_DAT

SMB_ME0_CLK

SMB_ME0_DAT

SMB_ME1_CLK

SMB_ME1_DAT

4 3

1

3V_S0

5

2

6

Q9

N@2N7002KDW/60V/115MA

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BDW PCH(CLK/LPC/SPI/SMB)

BDW PCH(CLK/LPC/SPI/SMB)

BDW PCH(CLK/LPC/SPI/SMB)

3

1

RP2 10KX2

1

3

RP1 10KX2

Normal Mode -> 2.2K ohm

Fast Mode -> 499 ohm

Q31

2N7002KDW/60V/115MA

B-37

43

1

1

3V_S0

3V_S0

5

2

6

FH9

FH9

FH9

R213N@1K/F_4

R274N@1K/F_4

11 48Wednesday, November 19, 2014

11 48Wednesday, November 19, 2014

11 48Wednesday, November 19, 2014

4

2

2

4

B-37

SMB_PCH_DAT

SMB_PCH_CLK

NFC_SCL 34

NFC_SDA 34

3V_S0

3V_S0

2A

2A

2A

5

4

3

2

1

Broadwell U-Type ULT (SYSTEM POWER MANAGEMENT)

12

B-9

D D

C C

SUSPWRDNACK# DSWVRMEN

SYS_PWROK

RSMRST#37

DNBSWON#37

R497 *SHORT_4

R203 *SHORT_4

R531 *SHORT_4

R199 *SHORT_4

A+-18

T45

T48

PCH_SUSACK#

SYS_PWROK_R

PCH_PWROK

PCH_APWROK

PLTRST#_R

PCH_RSMRST#

SUSPWRDNACK#

PCH_PWRBTN#

AC_PRESENT

PM_BATLOW#

SLP_S0#

SLP_WLAN#_R

U31H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

PCH PWROK (CLG)

MPWROK

R527 *SHORT_4

R188 *SHORT_4

B-9

B B

PCH_PWROK

PCH_APWROK

BDW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

Sus

DSW

DSW

DSW

8 OF 19

DSW Circuit

Core

CLKRUN/GPIO32

Sus

SUS_STAT/GPIO61

Sus

DSW

DPWROK

DSWVRMEN

DPWROK

WAKE

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

B-9

Non Deep Sx

R522 *SHORT_4

AW7

DPWROK_RSYS_RESET#

AV5

PCIE_WAKE#_R

AJ5

PCH_GPIO32

V5

SUS_STAT#

AG4

SUS_CLK

AE6

SLP_S5

AP5

AJ6

AT4

SLP_A#

AL5

SLP_SUS#

AP4

SLP_LAN#

AJ7

R524 *0_4

B-9

R525 *SHORT_4

R223 *SHORT_4

T18

T17

T20

PCH_RSMRST#

SUS_CLK 34

T19

SUSC# 36,37

SUSB# 37

DPWROK

HWPG_3/5V 37,39

DSWVRMEN 10

PCIE_WAKE# 21,29,34

PCH PU/PD (CLG)

SUSPWRDNACK#

SUS_STAT#

PCIE_WAKE#_R

AC_PRESENT

PM_BATLOW#

PCH_SUSACK#

PCH_PWRBTN#

PCH_GPIO32

SYS_RESET#

A+-8

PCH_RSMRST#

PCH_PWROK

SYS_PWROK

R496 10K_4

R206 *10K_4

R225 10K_4

R234 10K_4

R214 10K_4

R498 *10K_4

R205 10K_4

R184 10K_4

R187 10K_4

Reserve for ESD

D6 *TVS_AZ5123-01F

21

R523 10K_4

R516 10K_4

R204 *10K_4

3V_S5

3V_S0

SYS PWROK (CLG) PLTRST (CLG)

SYS_PWROK

TC7SH08FU

A A

5

3V_S5 3V_S5

C531*0.1U/10V_4

U35

4

R530 *0_4

2

1

MPWROK

3 5

R529

10K_4

IMVP_PWRGD 13,43

MPWROK 13,37

4

PLTRST#8,20,29,30,34,35,37

R226

*100K_4

3

U11

TC7SH08FU

4

R228 *0_4

C321

*0.1U/10V_4

2

1

3 5

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PLTRST#_R

R232

100K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BDW PCH(PWR MANAGEMENT)

BDW PCH(PWR MANAGEMENT)

BDW PCH(PWR MANAGEMENT)

D8

*TVS_AZ5123-01F

Reserve for ESD

2 1

FH9

FH9

FH9

1

12 48Wednesday, November 19, 2014

12 48Wednesday, November 19, 2014

12 48Wednesday, November 19, 2014

A+-8

2A

2A

2A

5

4

3

2

1

VDDQ Output Decoupling Recommendations

330uFx2 7343

22uFx11

10uFx10

1.35V_S3

D D

C C

1.05V_VCCST

Need to short rework after build

VCCIO_OUT OPTIONS

BOT socket side

5 onTOP, 6 on BOT inside socket cavity

0805

5 onTOP, 5 on BOT inside socket cavity

0805

Reserve for RF

R194 *0_8S

C300

*3.3P/50V/C0G_4

1.05V_VCCST1.05V_S0

C299

4.7U/6.3V_4

+

C332

10u/6.3V/X5R/6

+VCCIOA_OUT +VCCIO_OUT 1.05V_S0

C334

10u/6.3V/X5R/6

C528

*470u/2V_7343

C307

0.1U/10V/X5R/4

Broadwell U-Type ULT MCP(POWER)

BDW_ULT_DDR3L

HSW ULT POWER

12 OF 19

C36

VCC

C40

VCC

C44

VCC

C48

VCC

C52

VCC

C56

VCC

E23

VCC

E25

VCC

E27

VCC

E29

VCC

E31

VCC

E33

VCC

E35

VCC

E37

VCC

E39

VCC

E41

VCC

E43

VCC

E45

VCC

E47

VCC

E49

VCC

E51

VCC

E53

VCC

E55

VCC

E57

VCC

F24

VCC

F28

VCC

F32

VCC

F36

VCC

F40

VCC

F44

VCC

F48

VCC

F52

VCC

F56

VCC

G23

VCC

G25

VCC

G27

VCC

G29

VCC

G31

VCC

G33

VCC

G35

VCC

G37

VCC

G39

VCC

G41

VCC

G43

VCC

G45

VCC

G47

VCC

G49

VCC

G51

VCC

G53

VCC

G55

VCC

G57

VCC

H23

VCC

J23

VCC

K23

VCC

K57

VCC

L22

VCC

M23

VCC

M57

VCC

P57

VCC

U57

VCC

W57

VCC

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

AC58

AB23

AD23

AA23

AE59

AD60

AD59

AA59

AE60

AC59

AG58

AC22

AE22

AE23

AB57

AD57

AG57

L59

J58

F59

N58

E63

A59

E20

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

U59

V59

C24

C28

C32

U31L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

1.35V_S3 1.4A

C534

*10u/6.3V/X5R/6

C309

2.2U/6.3V_4 C286

C308

0.1U/10V/X5R/4

C533

*10u/6.3V/X5R/6

C305

2.2U/6.3V_4

H_VR_EN_MCP43

1.05V_VCCST

VCC_CORE

VCC_SENSE43

C529

*10u/6.3V/X5R/6

C303

2.2U/6.3V_4

VCC_CORE

+VCCIO_OUT

+VCCIOA_OUT

R185 150_4

VCCST (0.1A)

1.05V_VCCST

VCC_CORE

C339

10u/6.3V/X5R/6

C304

2.2U/6.3V_4

R406 100/F_4

R410 *SHORT_4

H_CPU_SVIDART#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

VCCST_PWRGD_MCP

R164 10K_4

PWR_DEBUG#

VCC_SENSE_R

B-9

VR_READY

+

C438

*470u/2V_7343

C244

22U/6.3V_6

C278

22u/6.3V/X5R/6

C249

22u/6.3V/X5R/6

C266

*22U/6.3V_6

C258

22U/6.3V_6

C264

22u/6.3V/X5R/6

C294

22u/6.3V/X5R/6

C280

22u/6.3V/X5R/6

C269

*22U/6.3V_6

C276

22U/6.3V_6

C302

22u/6.3V/X5R/6

C285

22u/6.3V/X5R/6

C259

22u/6.3V/X5R/6

C245

*22u/6.3V/X5R/6

C274

22u/6.3V/X5R/6

VCC Output Decoupling Recommendations

470uFx4 7343

22uFx8

22uFx11

10uFx11

TOP socket side

4 on TOP, 4 on BOT near socket edge

0805

0805

TOP, inside socket cavity

0805

BOT, inside socket cavity

C267

22U/6.3V_6

22u/6.3V/X5R/6

VCC_CORE 32A

C277

22u/6.3V/X5R/6

C291

22u/6.3V/X5R/6

C247

22u/6.3V/X5R/6

C262

*22u/6.3V/X5R/6

C292

22u/6.3V/X5R/6

C284

22u/6.3V/X5R/6

C248

22U/6.3V_6

C268

*22U/6.3V_6

C270

22U/6.3V_6

C293

*3.3P/50V/C0G_4

Reserve for RF

C260

22u/6.3V/X5R/6

C261

22u/6.3V/X5R/6

C243

22u/6.3V/X5R/6

C275

*22u/6.3V/X5R/6

13

VCC_CORE

C289 *0.1U/10V_4

R179

130/F_4

R178 *SHORT_4

Place PU resistor

close to CPU

R175 43_4

R173 *SHORT_4

5

R390 *0_8

C473

4.7U/6.3V_4

1.05V_VCCST

B-9

B-9

C279 *0.1U/10V_4

R176

75_4

VR_SVID_DATA 43

VR_SVID_ALERT# 43

VR_SVID_CLK 43

B-68

3V_S5

R453

C499

*100K_4

B-9

6

2

5

Q23

*2N7002KDW/60V/115MA

1

4 3

U30

1

VCC5NC

2

IN

GND3OUT

74LVC1G07GW

R436 *0_6

3V_S5

C487

0.1u/10V/X5R_4

C-9

4

R435 *0/short_4

C-9

3

B-9

MPWROK12,37

4

C-9

R449 *0_6

C-9

R454 *0/short_4

0.1u/10V/X5R_4

1.05V_VCCST

VCCST_PWRGD_MCPVCCST_PWRGD

R448

10K_4

C495

*680P/50V/X7R_4

IMVP_PWRGD12,43

R141 *0/short_6

R146 *0_4

2

B-9

R139

100K_4

5

U9

1

2

IN

GND3OUT

*74LVC1G07GW

3V_S53V_S0

R113

100K_4

VR_READY_C VR_READY

6

2

Q8

2N7002KDW /60V/115MA

1

4 3

3V_S5

C217

*0.1u/10V/X5R_4

VCC5NC

4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

B-9

R132 *0/short_6

R160 *0_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BDW MCP(POWER)

BDW MCP(POWER)

BDW MCP(POWER)

1

FH9

FH9

FH9

2A

2A

13 48Wednesday, November 19, 2014

13 48Wednesday, November 19, 2014

13 48Wednesday, November 19, 2014

2A

B B

SVID

Place PU resistor

close to CPU

H_CPU_SVIDDAT

A A

H_CPU_SVIDART#

H_CPU_SVIDCLK

R388 *0_8

Layout note: need routing together

and ALERT need between CLK and DATA.

1.05V_VCCST

5

4

3

2

1

14

Broadwell U-Type ULT (RSVD,GND)

BDW_ULT_DDR3L

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

A11

A14

A18

A24

A28

A32

A36

A40

A44

A48

A52

A56

U31N

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

14 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

D D

C C

B B

U31O

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

BDW_ULT_DDR3L

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

G18

G22

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D50

D51

D53

D54

D55

D57

D59

D62

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

H13

U31P

D5

D8

G3

G5

G6

G8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

BDW_ULT_DDR3L

16 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_SENSE

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

R412

100/F_4

U31R

AT2

RSVD

AU44

RSVD

AV44

RSVD

D15

RSVD

F22

RSVD

H22

RSVD

J21

RSVD

VSS_SENSE 43

BDW_ULT_DDR3L

18 OF 19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

U31Q

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

5

TP_DC_TEST_AY60

DC_TEST_AY61_AW 61

DC_TEST_AY62_AW 62

TP_DC_TEST_B2

DC_TEST_A3_B3

DC_TEST_A61_B61

DC_TEST_B62_B63

DC_TEST_C1_C2

T53

T31

A A

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61

DAISY_CHAIN_NCTF_AY61

AY62

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B61

DAISY_CHAIN_NCTF_B61

B62

DAISY_CHAIN_NCTF_B62

B63

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

BDW_ULT_DDR3L

17 OF 19

4

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW1

DAISY_CHAIN_NCTF_AW2

DAISY_CHAIN_NCTF_AW3

DAISY_CHAIN_NCTF_AW61

DAISY_CHAIN_NCTF_AW62

DAISY_CHAIN_NCTF_AW63

A3

A4

A60

A61

A62

AV1

AW1

AW2

AW3

AW61

AW62

AW63

DC_TEST_A3_B3

TP_DC_TEST_A4

TP_DC_TEST_A60

DC_TEST_A61_B61

TP_DC_TEST_A62

TP_DC_TEST_AV1

TP_DC_TEST_AW 1

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

DC_TEST_AY61_AW 61

DC_TEST_AY62_AW 62

TP_DC_TEST_AW 63

3

T7

T32

T34

T47

T49

T50

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Quanta Computer Inc.

Quanta Computer Inc.