Page 1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

01

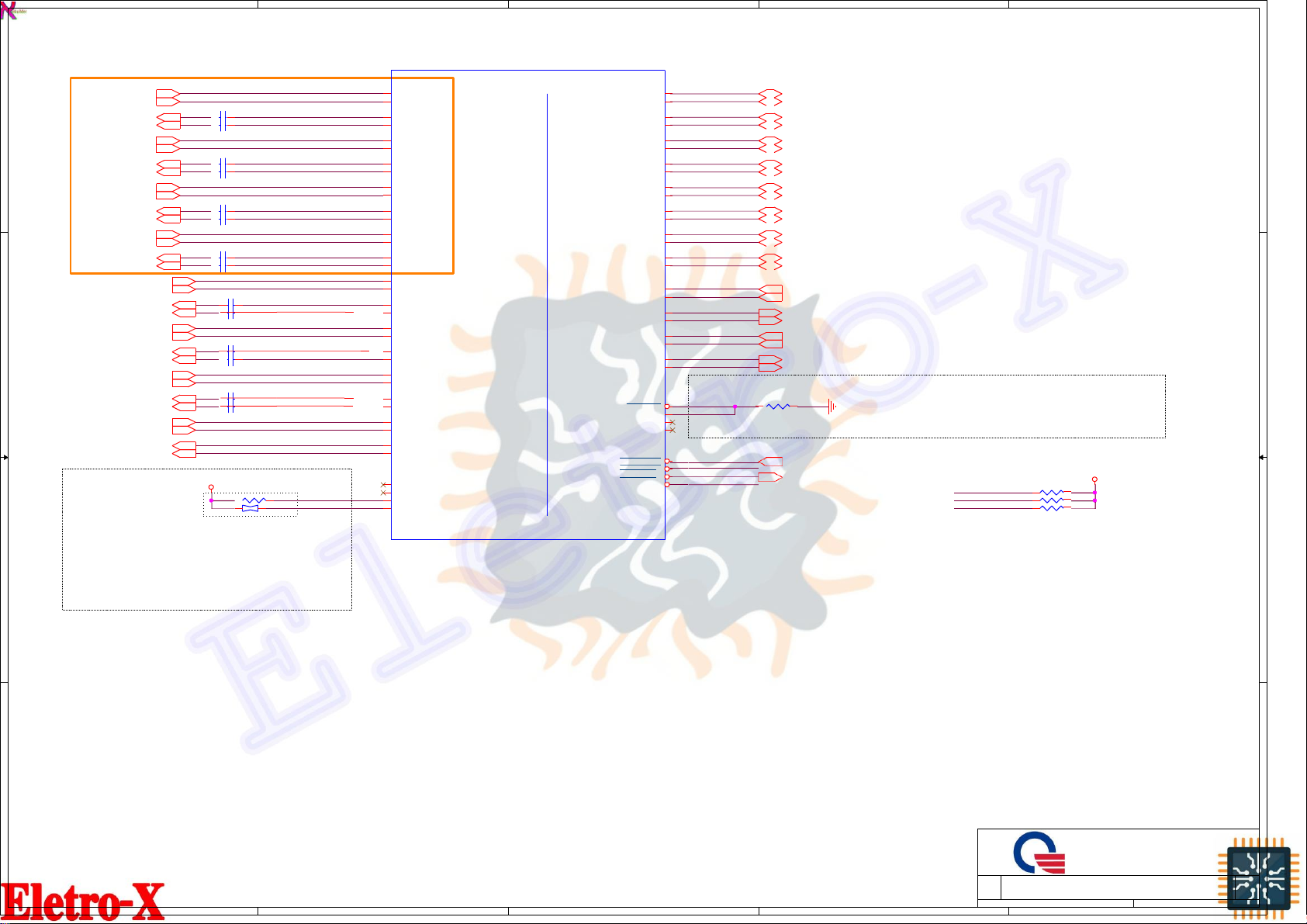

Green CLK

32.768KH z

PCI -E x 4 lane

DDR3L SO-DIMM1

Max 8GB

DDR3L 1333/1600 MT/sDDR3L SO-DIMM2

Max 8GB

Channel A

Channel B

DDR3L 1333/1600 MT/s

VRAM DDR3 256Mx16bitx4pcs

Max 2GB

Package : FCBGA96

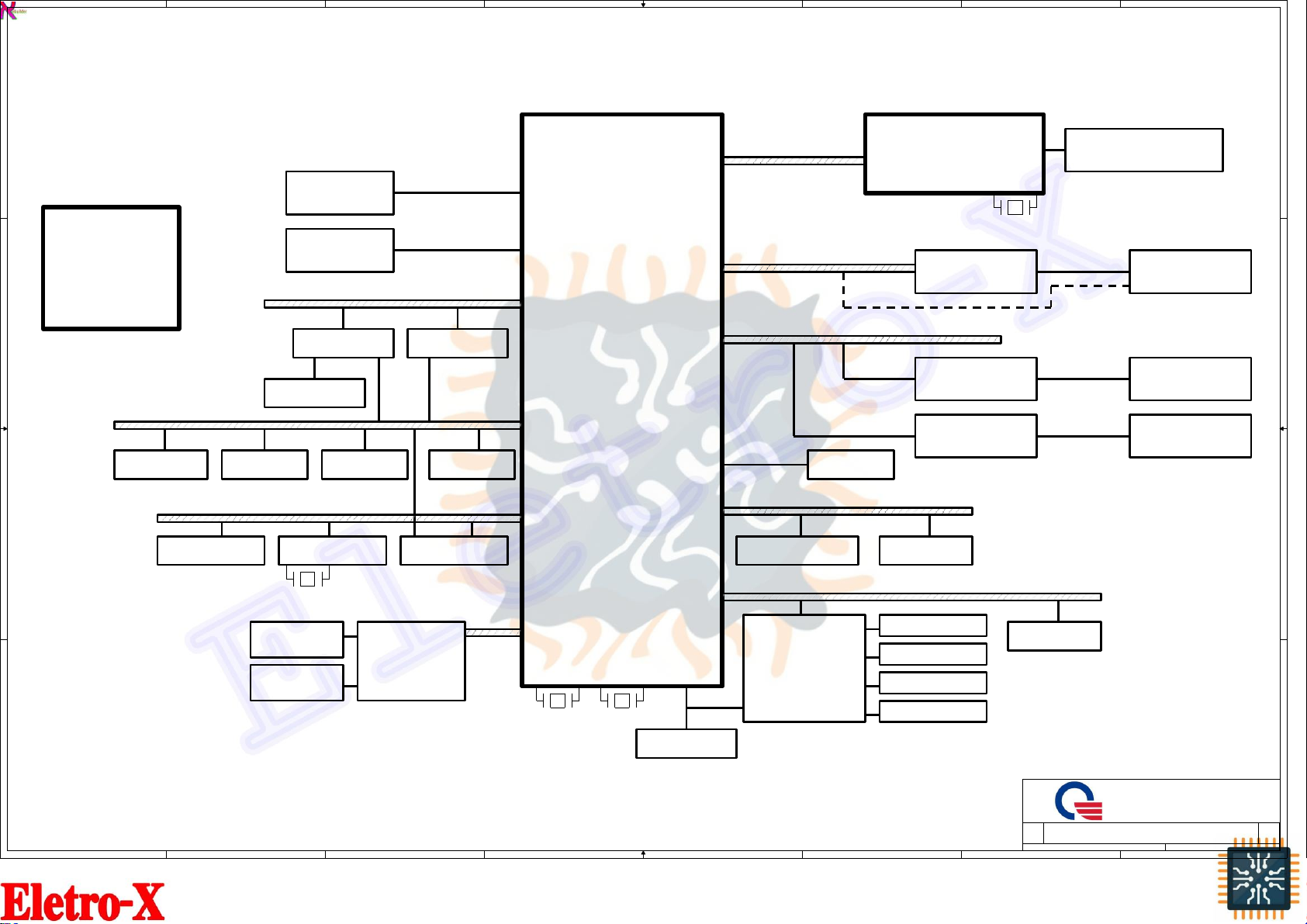

INTEL

DDR3L CHA

DDR3L CHB

eDP

DDI

USB3.0

Broadwell U

Processor

SATA

LPC

PCI-E

Processor : Daul Core

Power : 15/28 (Watt)

Package : BGA1168

USB2.0 Size : 40 x 24 (mm)

HDA

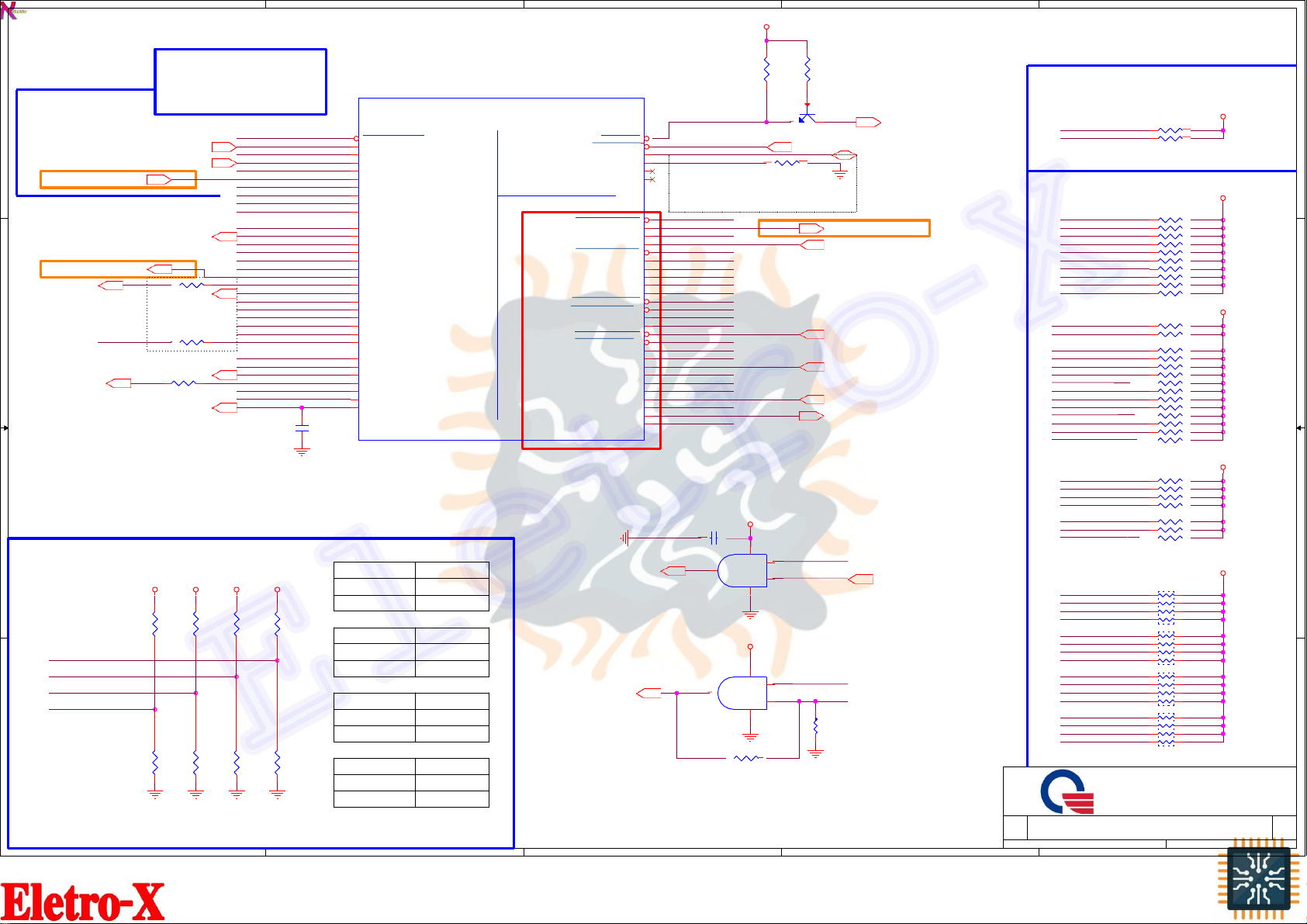

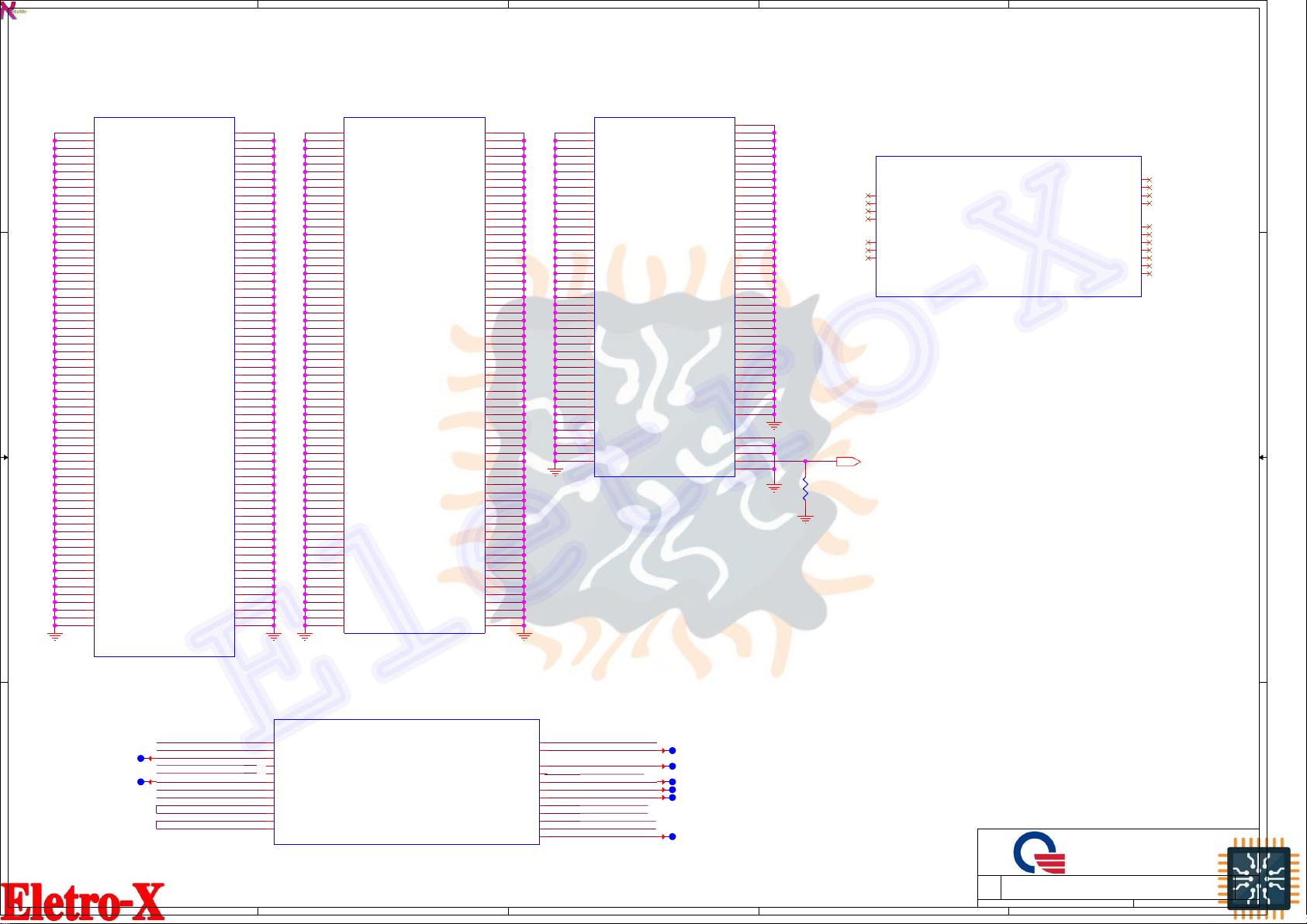

FH9 DIS (15.6") Broadwell Platform Block Diagram

AMD Topaz-S3 XT (64b)

Power : 25 Watt

Package : FCBGA631

Size : 23 x 23 mm

PCB Stackups

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : SVCC

LAYER 6 : BOT

27MH z

USB2.0 Interface

RTS5227E-GRT

Card Reader

Green CLK

25MH z

PCI-E Interface

Power off USB Char ger

IC : SIL55584

USB3.0 Interface

Azalia

Green CLK

24MH z

SPI

LVDS Interface

LCD Conn

15.6” FHD/HD panel

EDP Interface

VGA Interface

VGA Conn

DDI Interface

SATA Interface

ODD

LPC Interface

IT8587E/FX

Embedded Controller

Keyboard

Touch Pad

FAN Control

HALL Sensor

TPM CON

HDMI Conn

PS8407A

Level shifter

ALC283

Audio Codec

Combo Jack

(Mic-in/HP-out)

Speaker x 2

P6 ~ 17

P18

P19

P20 ~24

P25

RTD2132N-CG

eDP to LVDS Converter

P27

P28

P26

P28P28

P31

P35

P35

P35

Touch Screen

P35

P35

RTL8111GS-CG

LAN Controller

P29

P30

USB3.0 Port x 1

P32

USB3.0 Port x 2

P32

P32

WLAN / BT Combo

NGFF 2230 CON

P34

Wireless Dongle

P36

NFC(Felica)

P34

WEBCAM

P28

P33

HDD/SSD/Hybrid HDD

P33

P37

BIOS/EC ROM

P10

P31

P31

USB2.0 Port x 1

P32

P34

RTD2168N-CG

DP to VGA Converter

P26

I2C

Siiize DocumentNumber

BLOCK DIAGRAM

2A

Sheet 1 of 48Date: Wednesday, November 19, 2014

Quanta Computer Inc.

PROJECT :

FH9

Rev

Page 2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

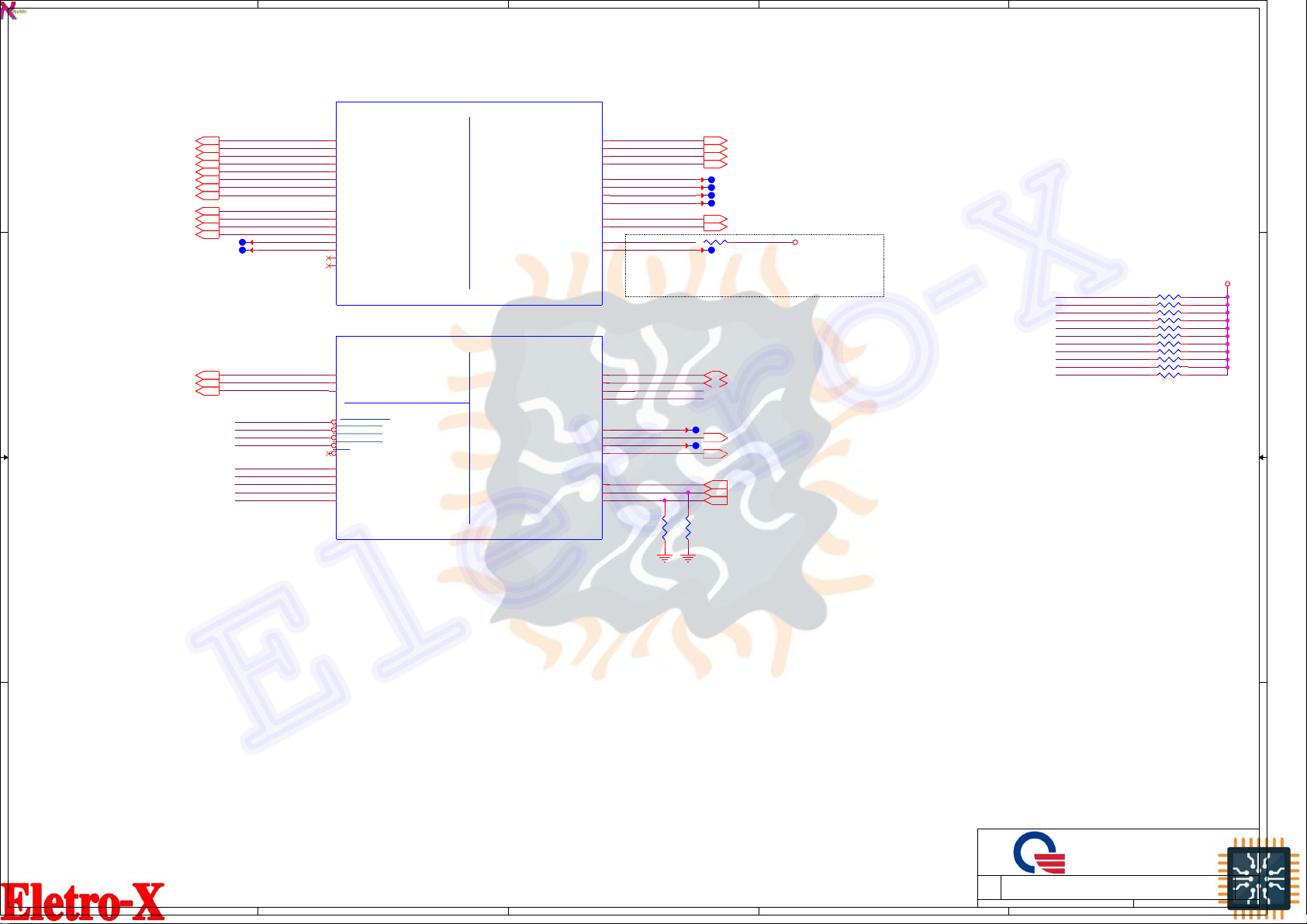

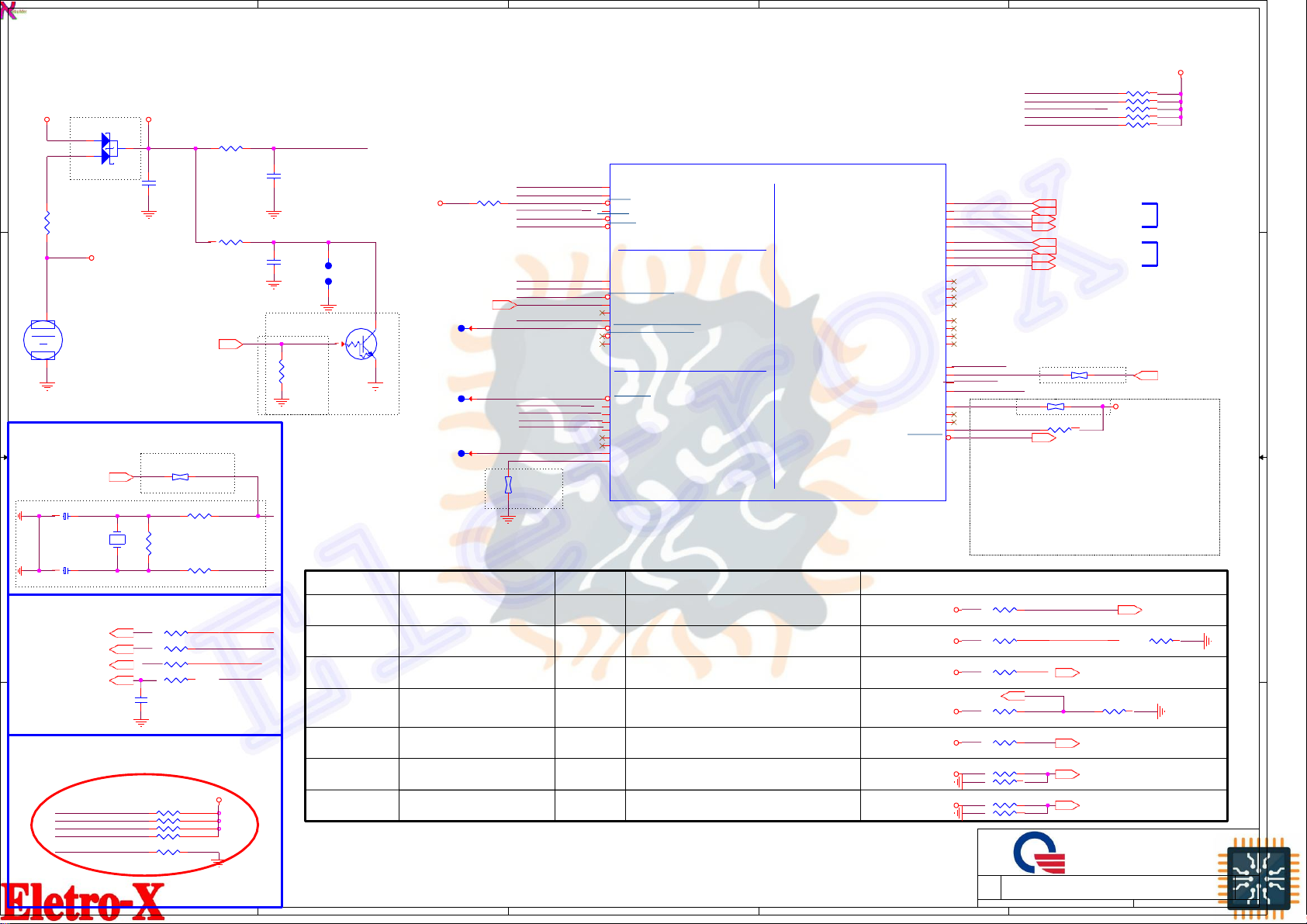

Broadwell ULT

GPU

AMDTOPAZ-XT

VRAM

1

RTC

VCCRTC

ITE

ITE8587

EC

PWRBTN#

4

Controlsignal

RTCPower

AUXPower

S5 Power

SUS Power

S0 Power

VIN

DC Jack

USB 2.0 Port

LAN

USB 3.0 Port

Card reader

Audio

NGFF card

HDD

ODD

WebCam

eDP to LVDS

Converter

Touch Screen

AND

DP to VGA

Converter

NFC

Wireless Dongle

Touch Pad

3 13

3V_S0

3V_AUX

3V_RTC

S5_ON

TPS51225RUKR

HWPG

3V_S5

LAN_ON_EC

47

5V_S3

3VDUAL_LAN

Fuse

SUSB#

NBSWON#

RSMRST#

3VDUAL_LAN

S

Power SW

D

OP

G

S0_ON_2

3V_S0

S

Power SW

D

OP

G

MOS

S

D

G

WLAN_ON

3V_WLAN

D

S

G

LDO

OP

S0_ON_3

1.5V_S0

S

Power SW

D

OP

G

5V_S5

S3_ON

5V_S3

S

Power SW

D

OP

G

S0_ON_1

5V_S0

5V_S3

S

G

Power SW

D

USB_Charge

USB_Charge

G5335QT1U

S0_ON_1

5V_Mouse

5V_Mouse

S5_ON

S3_ON

1.05V_S0

1.8VGPU_PG

ISL62771HRTZ-T

VGA_CORE

MOS

S

D

G

0.95V_GPU

GPU_ON

3V_AUX

5V_AUX

S3_ON

RT8231AGQW

1.35V_S3

ISL95812HRZ-T

CPU_CORE

H_VR_EN_MCP

DDR_PG

DDR_VTERM

MOS

S

D

G

3V_GPU

S

Power SW

D

OP

G

GPU_ON

1.8V_GPU

1.8VGPU_PG

1.8VGPU_PG

ISL62771HRTZ-T

1.5V_GPU

3V_WLAN

5V_S0

S

Power SW

D

OP

G

CCD_KIIL

CCD_POWER

CCD_POWER

3V_S0

PLTRST#

3V_S0

1.5V_S0

3V_S0

3V_S0

5V_S0

MOS

S

D

G

ODD_5V

ODD_PWR_EN

ODD_5V

3V_S0

3V_S0

3V_S0

TPM

LCD_BK_POWER

DDR

3

1.5V_GPU

1.8V_GPU

0.95V_GPU

VGA_CORE

GPU_RST#

3V_GPU

DDR_VTERM

1.35V_S3

PLTRST#

PLTRST#

HWPG_3/5V

HWPG_3/5V

HWPG_1.35V

HWPG_VTT

S0_ON_1

S0_ON_2

ODD_PWR_EN

VR_ON

GPU_ON_PCH

GPU_ON

AND

GPU_ON_PCH

GPU_ON_EC

GPU_ON_EC

CCD_KIIL

HWPG

SYS_PWROK

AND

MPWROK

IMVP_PWRGD

IMVP_PWRGD

MPWROK

GPU_RST#

AND

GPU_RST#_PCH

PLTRST#

GPU_RST#_EC

GPU_RST#_EC

GPU_RST#_PCH

USB_CHARGE#

CEN#

R

USB_CHARGE#

MOUSE_ON

1.35V_S3

VGA_CORE

1.05V_S0

3V_S0

3V_S5

1.05V_S0

Power Delivery/RESET/PWROK

MOS

S

D

G

ISL88732R5601

Battery

D/C#

LAN_RST#

LAN_RST#

AND

PLTRST#

LAN_ON_EC

NFC_RST_BUFF#

NFC_RST_BUFF#

AND

NFC_RST#

PLTRST#

R

NFC_RST#

WLAN_ON

D/C#

D/C#

PLTRST#

SUSC#

HWPG_VTT

MOS

S

D

G

MOUSE_ON

SUSC#

GPU_ON

D

S

OP

G

LCDVCC

PCH_VDDEN

(eDP)

PCH_VDDEN

SYS_PWROK

PANEL_VCC

Power SW

(LVDS)

MOS

S

D

G

Siiizzzeee Docuuument Nuuumbbbeeerrr

Powerrr Dellliiiverrry///RESET///PWROK

222A

Daaattteee::: Weeedddnnneeesssddday,,,Nooovvvemberrr 1119, 201444 Sheet444777 ooofff 444888

Quanta Computer Inc.

PROJECT : F H9

Reeevvv

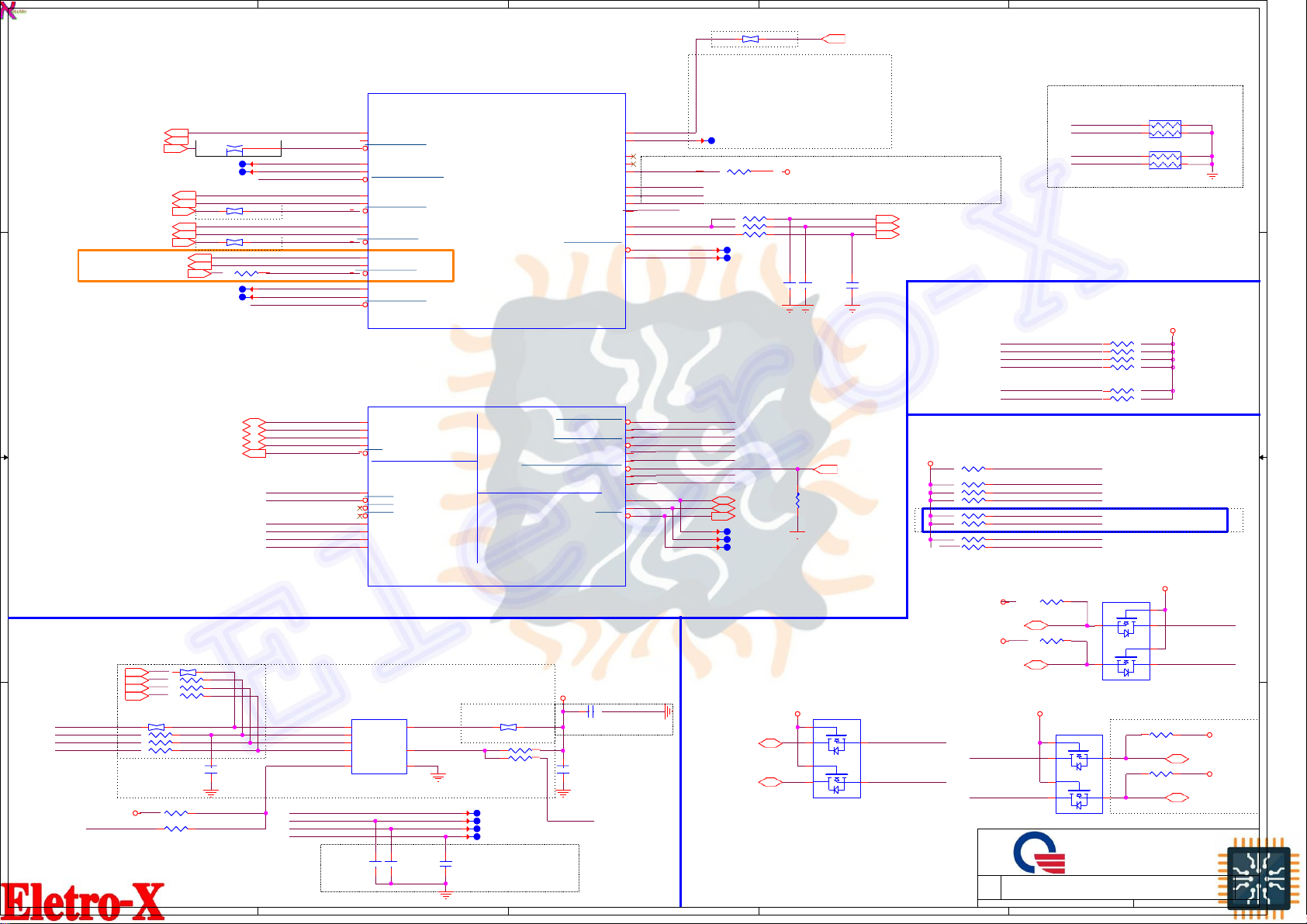

Page 3

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

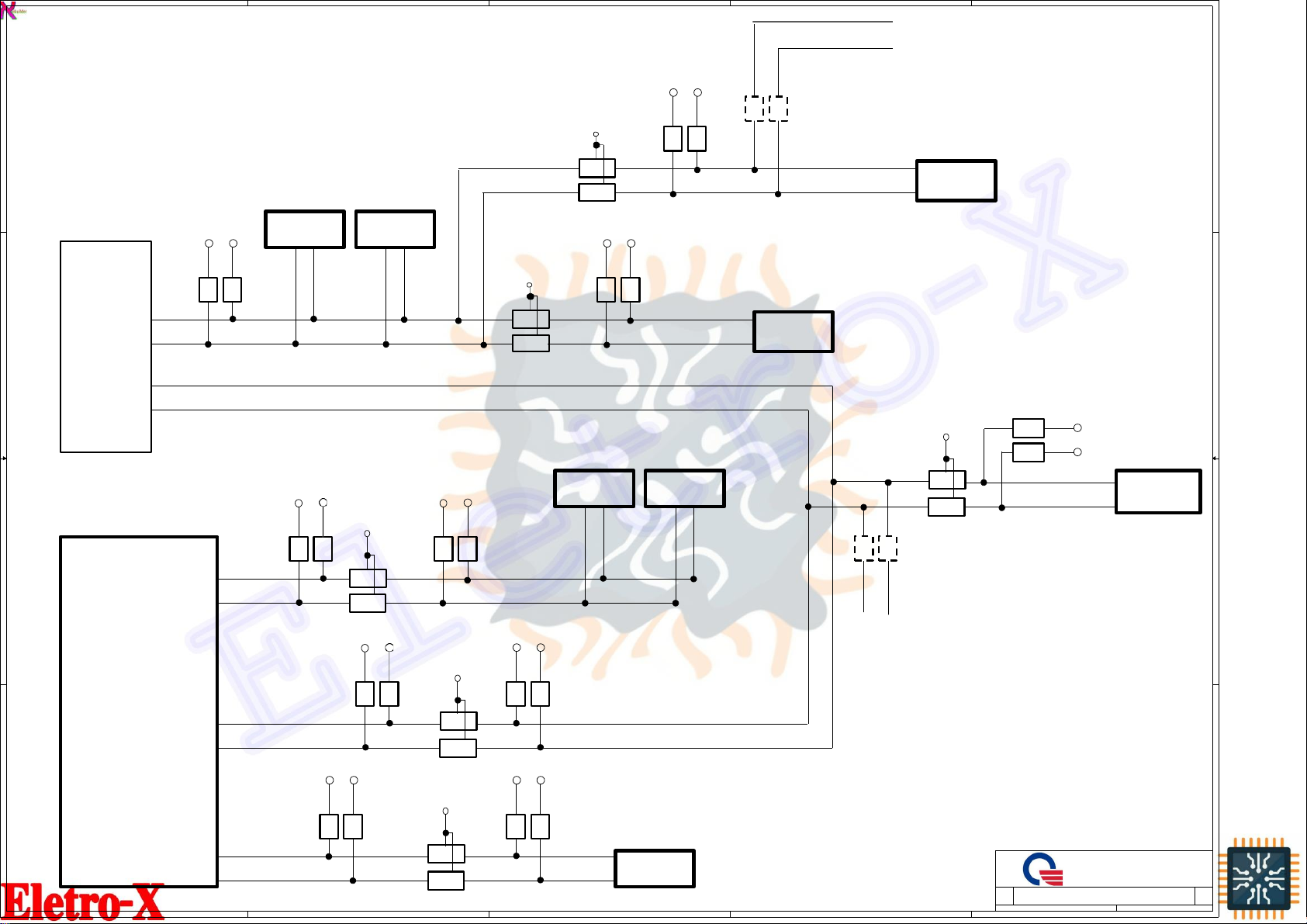

04

100MHz PCIE

CLKOUT_LPC_0

CLK_PCIE_WLANN

CLK_PCIE_WLANP

PCLK_DEBUG

33MHz PCI

CLKOUT_LPC_1

CLK_33M_KBC

33MHz PCI

WLAN

REFCLK+

REFCLK-

DEBUG CARD

RESERVED

EC ITE 8587

LPCCLK

Broadwell-U

Buffered mode

PCLK_TPM

33MHz PCI

TPM

LCLK

100MHz PCIE

CLK_PCIE_LANN

CLK_PCIE_LANP

LAN

REFCLK+

REFCLK-

100MHz PCIE

CLK_PCIE_CARDN

CLK_PCIE_CARDP

Card Reader

REFCLK+

REFCLK-

CLKOUT_PCIE_P2

CLKOUT_PCIE_N2

CLKOUT_PCIE_P3

CLKOUT_PCIE_N3

CLKOUT_PCIE_P0

CLKOUT_PCIE_N0

100MHz PCIE

CLK_PCIE_DGPUN

CLK_PCIE_DGPUP

GPU

REFCLK+

REFCLK-

CLKOUT_PCIE_P4

CLKOUT_PCIE_N4

32.768Khz

Xtal

24Mhz

Xtal

G-CLK

Size DocumentNumber

Sheet of

Clock Distribution

Rev

2A

4 48Date: Wednesday, November 19, 2014

Quanta ComputerInc.

PROJECT :

FH9

Page 4

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

05

3V_S5

G

S

NMOS

D

S D

NMOS

3V_S5

3V_AUX 3V_AUX

R R

40 x 24(mm)

INTEL

Broadwell

3V_S5

SMB_PCH_CLK

SMB_PCH_DAT

3V_S0

S

NMOS

D

G

S D

NMOS

R R

3V_S5

SMB_ME1_DAT

SMB_ME1_CLK

SMB_ME0_CLK

SMB_ME0_DAT

R R

3V_S0 3V_S0

SO-DIMM A

3V_S5

R R

3V_S0

NMOS

G

NMOS

MBCLK1

MBDATA1

3V_AUX 3V_AUX

CHARGER

BQ24707RGRR

BATTERY

MBDATA0

MBCLK0

R R

S

S

EC

ITE

IT8587E/EX

(128 PinLQFP)

16mm x 16mm

SO-DIMM B

3V_S0 3V_S0

D

D

DP to VGA

R R

3V_S0

NMOS

G

NMOS

S

S

D

D

LCD Converter

3V_S0 3V_S0

R R

R R

SMB_RUN_CLK

SMB_RUN_DAT

SMB_RUN_CLK

SMB_RUN_DAT

CGCLK_SMB

CGDAT_SMB

CIIC_SCL

CIIC_SDA

Address:

0x94,0x96,0x6A

Address:0x64,0x68

Address:0xA0h Address:0xA4h

R R

3V_S5 3V_S5

R

R

3V_GPU

3V_GPU

Address:0X41h

3V_GPU

G

S

NMOS

D

S D

NMOS

AMD TOP AZ

23 x 23(mm)

MBDATA_GPU

MBCLK_GPU

R R

MBDATA0

MBCLK0

NFC

Address:0x29h

G

3V_S0

S

NMOS

D

S D

NMOS

3V_S0 3V_S0

R R

NFC_SCL

NFC_SDA

Siiize Document Number Rev

SMBUS Add ress

2A

Sheet 5 offf 48Date: Wednesday,,, November 19, 2014

Quanta Computer Inc.

PROJECT :

FH9

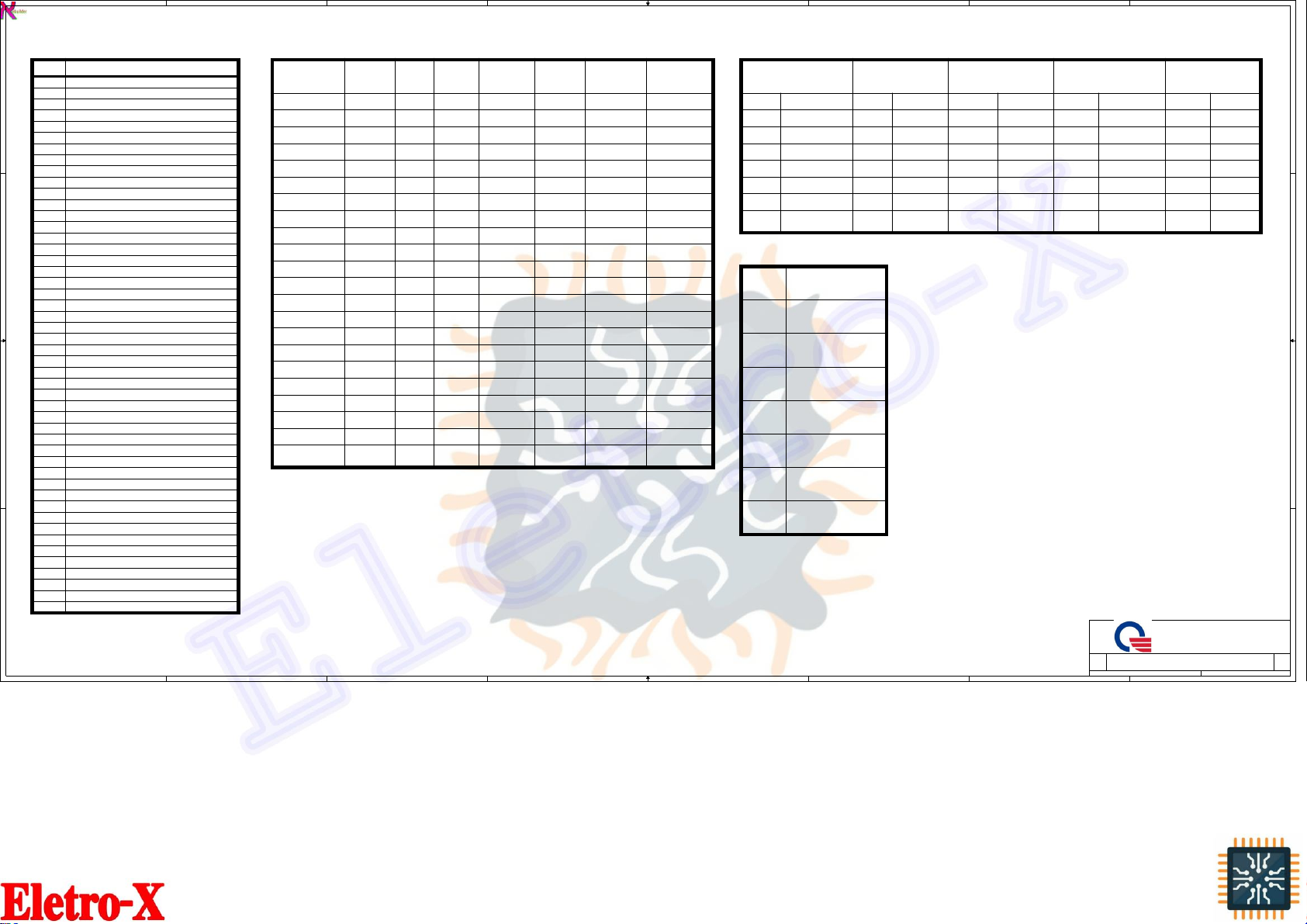

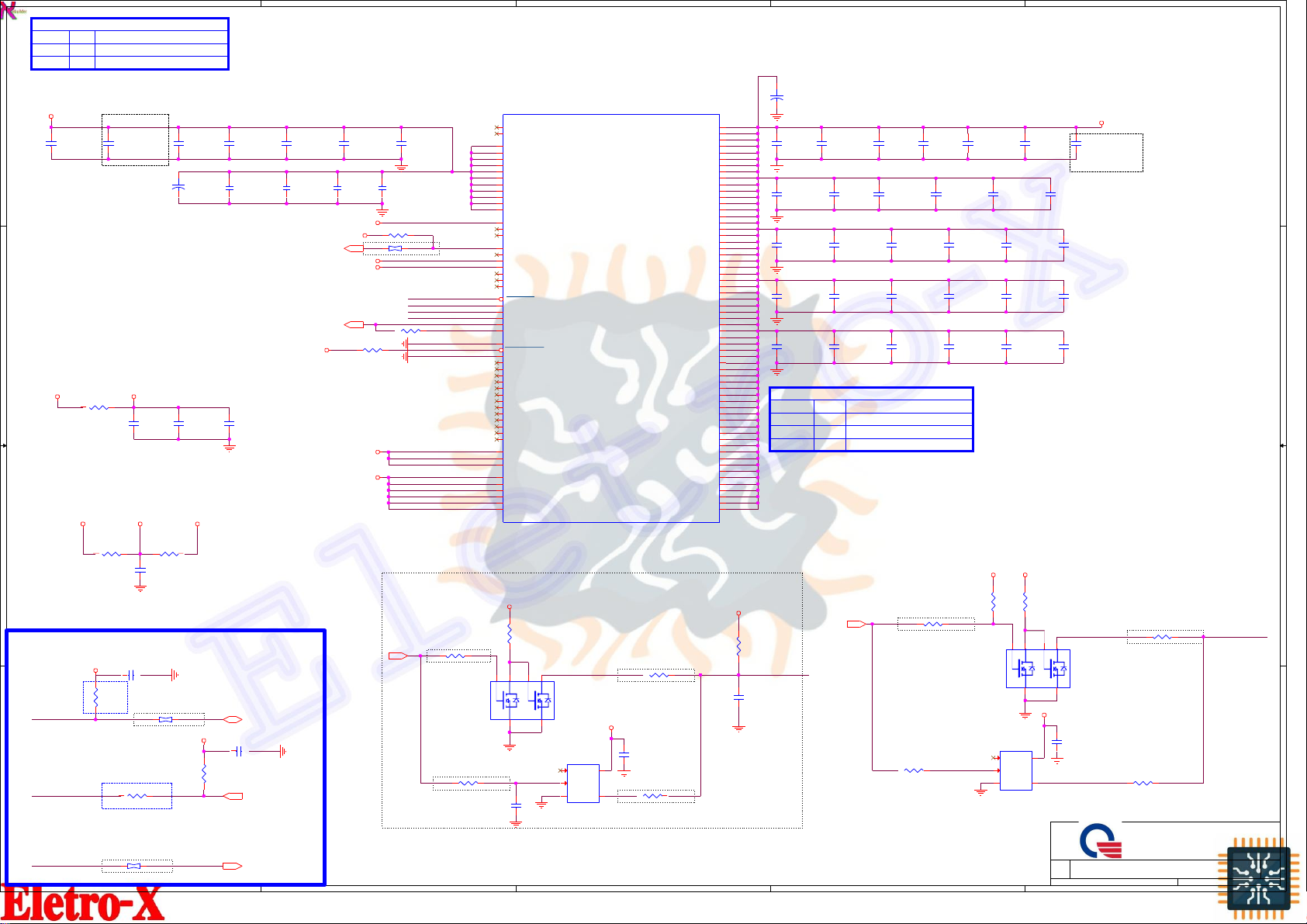

Page 5

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

02

Table of Contents

Power Voltage S0 S3 S4 S5 G3 Ctl Signal

3V_RTC 3V

ON ON ON ON ON

VIN 19V

ON ON ON ON OFF

Adaptor in

5V_AUX 5V

ON ON ON ON OFF

Adaptor in

3V_AUX 3.3V

ON ON ON ON OFF

Adaptor in

5V_S5 5V

ON ON ON ON OFF

S5_ON

3V_S5 3.3V

ON ON ON ON OFF

S5_ON

1.35V_S3 1.35V

ON ON OFF OFF OFF

S3_ON

5V_S3 5V

ON ON OFF OFF OFF

S3_ON

3VDUAL_LAN 3.3V

ON OFF OFF OFF OFF

LAN_ON_EC

3V_WLAN 3.3V

ON OFF OFF OFF OFF

WLAN_ON

5V_S0

5V

ON OFF OFF OFF OFF

S0_ON_1

3V_S0 3.3V

ON OFF OFF OFF OFF

S0_ON_2

1.5V_S0 1.5V

ON OFF OFF OFF OFF

S0_ON_3

1.05V_S0 1.05V

ON OFF OFF OFF OFF

S0_ON_1

1.05V_VCCST 1.05V

ON OFF OFF OFF OFF

S0_ON_1

DDR_VTERM 0.675V

ON OFF OFF OFF OFF

DDR_PG

VCC_CORE 1.7V

ON OFF OFF OFF OFF

H_VR_EN_MCP

VGA_CORE 1V

ON OFF OFF OFF OFF

1.8VGPU_PG

3V_GPU 3.3V

ON OFF OFF OFF OFF

GPU_ON

1.8V_GPU 1.8V

ON OFF OFF OFF OFF

GPU_ON

1.5V_GPU 1.5V

ON OFF OFF OFF OFF

1.8VGPU_PG

0.95V_GPU 0.95V

ON OFF OFF OFF OFF

GPU_ON

Voltage Rails Function List

USB2 PCIE Display USB3 SATA

Port 0 Co-lay USB3.0 Port 1 Card Reader eDP Port 1 LVDS or eDP Port 1 USB3.0 Conn Port0 HDD

Port 1 Co-lay USB3.0 Port 2 USB3.0 Conn eDP Port 2 NC Port 2 USB3.0 Conn Port 1 ODD

Port 2 Co-lay USB3.0 Port 3 WLAN DDI Port 1 HDMI Port 3 Card Reader Port 2 NC

Port 3 Touch screen Port 4 GLAN DDI Port 2 CRT Port 4 USB3.0 Conn Port 3 NC

Port 4 Camera Port 5 GPU(TOPAZ)

Port 5 USB2.0 Conn

Port 6 Bluetooth

Port 7 USB HUB

PAGE DESCRI PTIO N

01 Block Diagram

02 Front Page

03 Power Sequence

04 Clock Distribution

05 SMBus Address

06 BDW MCP(Display/eDP)

07 BDW MCP(Memory)

08 BDW PCH(GPIO/LPIO/MISC)

09 BDW PCH(PCIE/USB)

10 BDW PCH(RTC/HDA/SATA)

11 BDW PCH(CLK/LPC/SPI/SMB)

12 BDW PCH(Power management)

13 BDW MCP(Power)

14 BDW MCP(GND/DAISY/RSVD)

15 BDW MCP(CFG)

16 BDW PCH(Power)

17 BDW MCP(Sideband)

18 DDR3L DIMM-1-RVS(H4.0)

19 DDR3L DIMM-2-RVS(H4.0)

20 TOPAZ_S3_PCIE_Interface

21 TOPAZ_S3_Main/DP Power

22 TOPAZ_S3_GND/LVDS/Strap

23 TOPAZ_S3_Power

24 TOPAZ_S3_MEM_Interface

25 TOPAZ_S3_VRAM_DDR3 BGA96

26 DP to VGA (RTD2168)/CRT

27 eDP to LVDS (RTD2132N-CG)

28 HDMI/LVDS

29 LAN RTL8111GS/RJ45 conn

30 Card Reader (RTS5227E)

31 Audio ALC283

32 USB3.0/Charger/USB2.0

33 HDD/ODD/LED

34 WLAN/BT/ NFC/MMB/PWR

35 KB/FAN/TP/TPM/TS

36 G-CLK/WL Dongle/HOLE

37 EC_IT8587

38 VIN/CHARGER-ISL88732

39 SYSTEM 5V/3V(TPS51225RUK)

40 1.05V-G5335

41 DDR3L 1.35V(RT8231AGQW)

42 SWITCH

43 CPU_CORE[NCP81101B) 28W

44 VGA CORE(INTERSIL 62771)

45 1.5GPU/0.95_GPU(RT8068A)

46 1.8V_GPU&3V_GPU

47 PWR Delivery/RESET/PWROK

48 Change History

Function Select

S@

TOPAZ + VRAM

L@

RTD2132N-CG

E@

Internal eDP

V@

RTD2168

N@

NFC

M@

MMB

TS@

Touch screen

WL@

Wireless Dongle

Siiize D ocume nt Number

FRONTPAGE

Rev

2A

Date: Wednesday,,, November 19, 2014 Sheet 2 offf 48

Quanta Computer Inc.

PROJECT :

FH9

Page 6

5

5

4

4

3

3

2

2

1

1

D D

C C

B

A A

Power Button EC

EC S5Enable

VR

S5Power

Coin Battey PCH

+3V_RTC Delay PCH

AC/DC IN All VRInput

VR Always Power

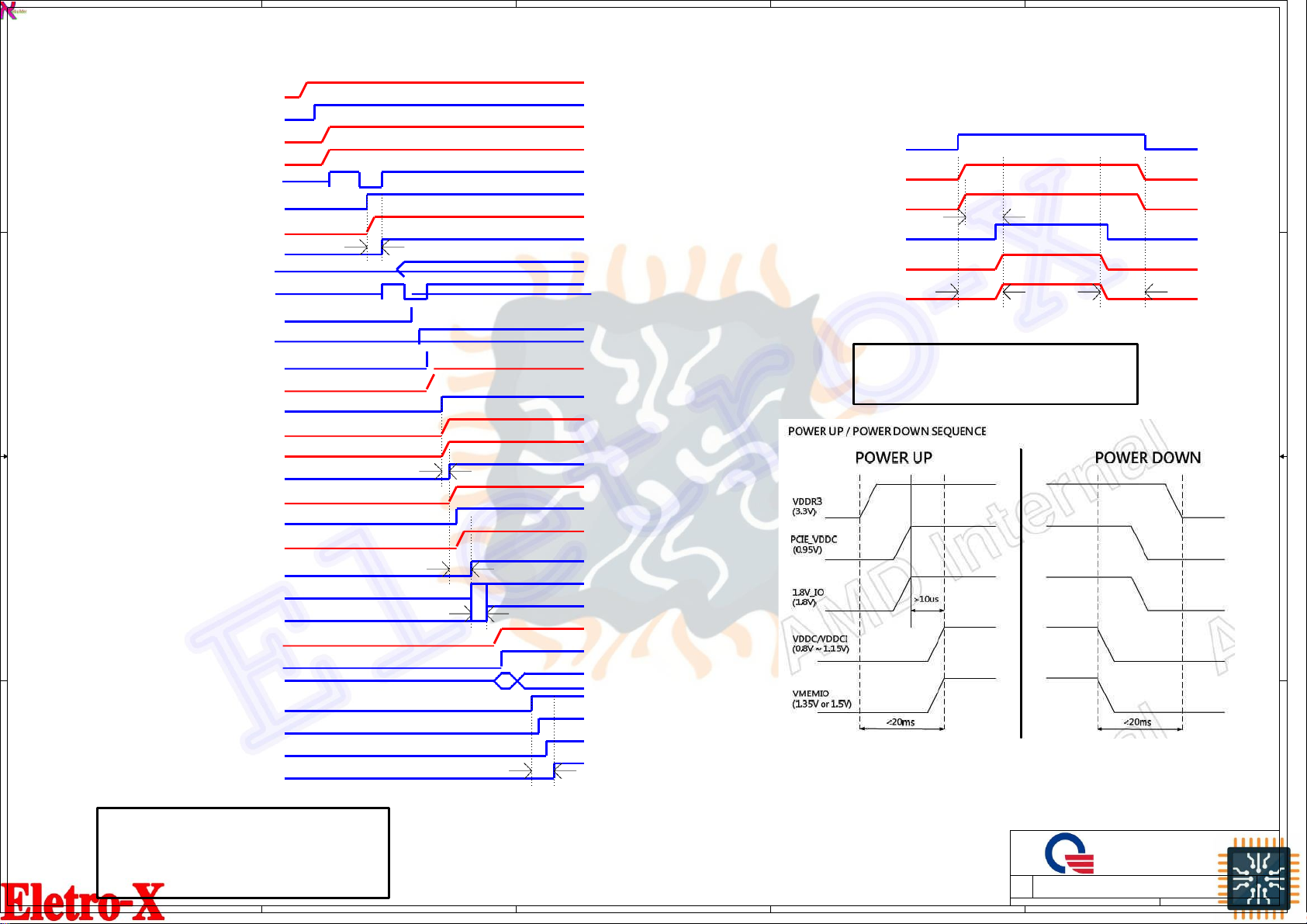

System Power On Sequencing TimingDiagram

EC

PCH EC

EC PCH PWRBTN#

PCH S4/S5

PCH S3

EC

VR

S0Power

S3Power

S3Enable

S0Enable

Memory VREF Power

EC

VR

DDR Power VR

EC

VR

S0Power

S0Enable

T1 PCH RSMRST#

T2

PCH

PCH

PCH SYS_PWROK

Platform Reset

CPU PROCPWRGOOD

PCH

CPU

CPU Core Power VR

valid

System Clock

PCH

PCH PWROK

EC

CPU Core Power VR

CPU Core Power

T3

T4

T5

System Power Sequence

T1: S5_ON TO RSMRST# = 20ms (spec:mini 10ms)

T2: S0_ON_1 TO S0_ON_2 = 500us

T3: S0_ON_2 TO VRON = 10ms

T4: HWPG TOMPWROK = 110ms (spec:>5~ 99ms)

T5: H_CPUPWRGD to PLTRST# >1ms

03

dGPU Power On/Off Sequencing Timing Diagram

GPU_ON

3V_GPU

1.8VGPU_PG

0.95V_GPU

dGPU Power Sequence

T7

1.8V_GPU

1.5V_GPU/VGA_CORE

T6:1.8V_GPU to 1.5V_GPU > 10us

T7:3V_GPU to 1.5V_GPU < 20ms

T8:1.5V_GPU to 3V_GPU < 20ms

T8

T6

All System PWROK

CPU

EC

PWM

EC

S0Power

VR

S0Enable

3V_RTC

RTC_RST#

VIN

5V_AUX/3V_AUX

NBSWON#

S5_ON

5V_S5/3V_S5

RSMRST#

SUSCLK

DNBSWON#

SUSC#

SUSB#

S3_ON

5V_S3/1.35V_S3

S0_ON_1

1.05V_S0/5V_S0

DDR_VTERM

S0_ON_2

3V_S0

S0_ON_3

1.5V_S0

B

HWPG

H_VR_EN_MCP

MPWROK

VCC_CORE

IMVP_PWRGD

Clock outputs

H_CPUPWRGD

SYS_PWROK

SUS_STAT#

PLTRST#

Siiize Document Number

Sheet

Power Sequence

2A

3 of 48Date: Wednesday, November 19, 2014

Quanta Computer Inc.

PROJECT :

FH9

Rev

Page 7

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

EDP_RCOMP

24.9 +/- 1% pull toVCCIOA_OUT

Trace Width: 20mils(trace)

Spacing: 25mils

Length: 100mils Max

Broadwell Type-U ULT (DISPLAY)

06

VGA

INT.HDMI

GPIOPU/PD

EDP_COMP

DP_UTIL

PCH_GPIO79

PCH_GPIO80

PCH_GPIO77

PCH_GPIO78

PCH_GPIO52

PCH_GPIO51

PCH_GPIO54

PCH_GPIO55

PCH_GPIO79

PCH_GPIO80

PCH_GPIO77

PCH_GPIO78

PCH_GPIO55

PCH_GPIO52

PCH_GPIO53

PCH_GPIO54

PCH_GPIO51

PCH_GPIO53

CRT_SCL

CRT_SDA

PCH_BRIGHT

PCH_BLON

PCH_VDDEN

27,28

28,37

28

INT_HDMI_SCL 28

INT_HDMI_SDA 28

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

27

27

28

28

EDP_AUXN

EDP_AUXP

27

27

INT_HDMI_HPD 28

CRT_HPD

EDP_HPD

26

27,28

CRT_AUXP 26

CRT_AUXN 26

CRT_TXDN0

CRT_TXDP0

CRT_TXDN1

CRT_TXDP1

26

26

26

26

INT_HDMI_TXDN2

INT_HDMI_TXDP2

INT_HDMI_TXDN1

INT_HDMI_TXDP1

INT_HDMI_TXDN0

INT_HDMI_TXDP0

INT_HDMI_TXCN

INT_HDMI_TXCP

28

28

28

28

28

28

28

28

+VCCIOA_OUT

3V_S0

Siiize DocumentNumber

BDW MCP(DISPLAY/eDP)

Rev

2A

6 of 48Date: Wednesday,November19, 2014 Sheet

Quanta ComputerInc.

PROJECT :

FH9

R364

V@100K_4

BDW_ULT_DDR3L

PCIE

DISPLAY

9 OF19

U31I

DDPC_AUXN

B6

DDPC_AUXP

A6

A9

EDP_BKLEN

L4

GPIO53

Core

R5

GPIO51

Core

L3

GPIO54

Core

L1

GPIO52

Core

U7

GPIO55

Core

AD4

PME

N2

PIRQD/GPIO80

Core

N4

PIRQC/GPIO79

Core

DDPB_CTRLCLK

B9

DDPB_CTRLDATA

C9

DDPC_CTRLCLK

D9

CRT_SCL

DDPC_CTRLDATA

D11

CRT_SDA

DDPB_HPD

C8

EDP_HPD

D6

DDPC_HPD

A8

C6

EDP_VDDEN

eDP SIDEBAND

B8

EDP_BKLCTL

U6

PIRQA/GPIO77

Core

P4

PIRQB/GPIO78

Core

R135 24.9/F_4

T26

T28

DDPB_AUXN

C5

T5

R150

R434

10K_4

10K_4

BDW_ULT_DDR3L

EDPDDI

1 OF19

U31A

C54

C55

B58

C58

B55

A55

A57

B46

C45

A47

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

B47

C47

C46

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

A49

B49

B45

EDP_AUXN

EDP_AUXP

A45

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

B57

B54

C50

C51

C53

C49

B50

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

A53

B53

D20

EDP_RCOMP

EDP_DISP_UTIL

A43

R373

100K_4

R413

R168

10K_4

10K_4

DDPB_AUXP

B5

T30

R417

R131

10K_4

V@2.2K_4

T25

T24

T29

T27

R363 V@2.2K_4

T6

R419

R153

10K_4

10K_4

R149

R428

10K_4

10K_4

Page 8

5

5

4

4

3

3

2

2

1

D D

C C

B B

A A

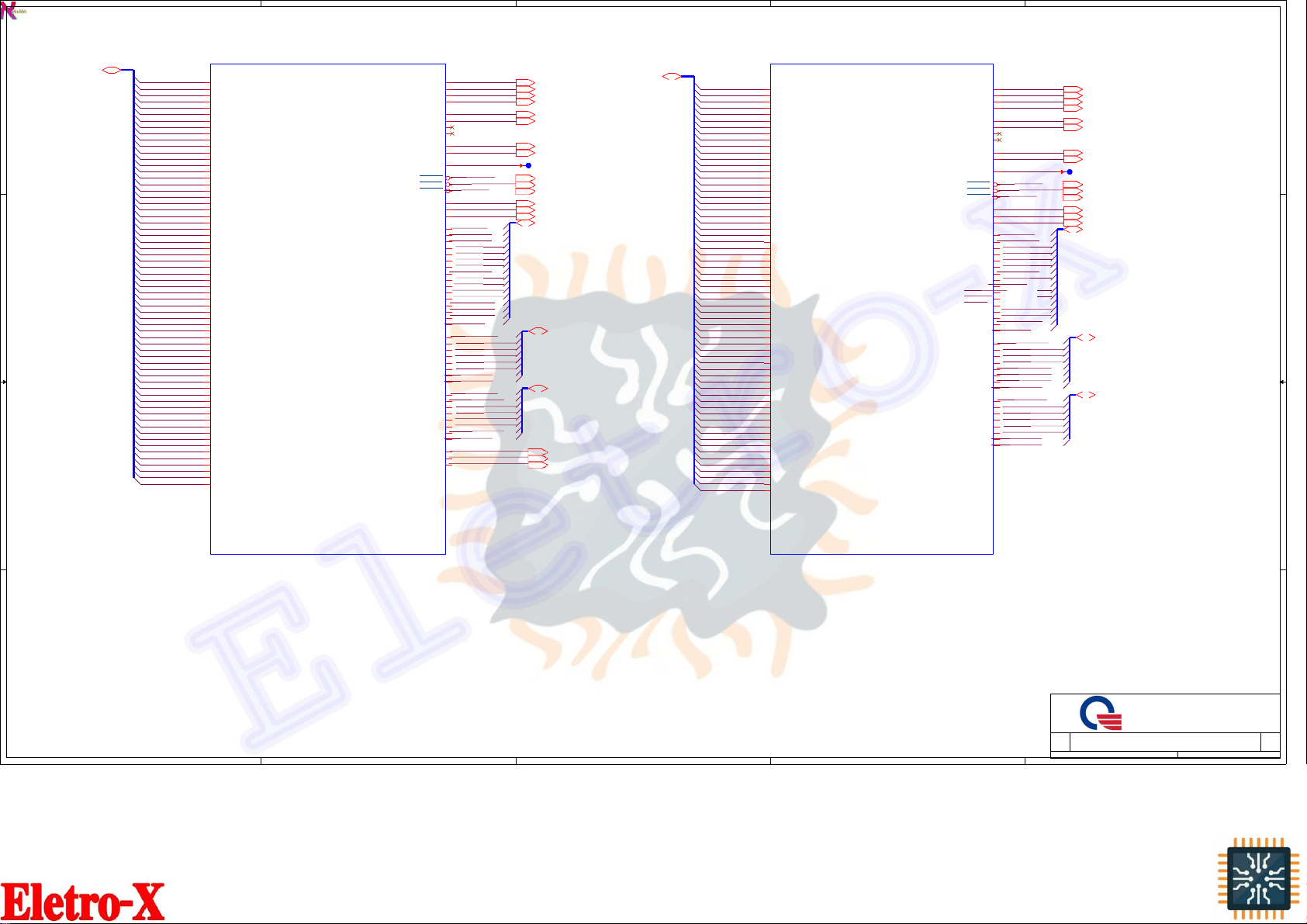

Boardwell Type-U ULT (DDR3L CHA)

07

Boardwell Type-U ULT (DDR3L CHB)

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ8

M_A_DQ9

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ30

M_A_DQ31

M_A_DQ28

M_A_DQ29

M_A_DQ26

M_A_DQ27

M_A_DQ24

M_A_DQ25

M_A_DQ16

M_A_DQ17

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ46

M_A_DQ47

M_A_DQ44

M_A_DQ45

M_A_DQ42

M_A_DQ43

M_A_DQ40

M_A_DQ41

M_A_DQ52

M_A_DQ53

M_A_DQ50

M_A_DQ51

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQ54

M_A_DQ55

M_A_DQ48

M_A_DQ49

M_A_DQ56

M_A_DQ57

M_A_DQ32

M_A_DQ33

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_A_RAS#

M_A_WE#

18

18

M_A_CAS# 18

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_A[15:0]

18

18

18

18

M_B_RAS#

M_B_WE#

19

19

M_B_CAS# 19

18

18

M_A_CKE0

M_A_CKE1

18

18

M_B_CS#0

M_B_CS#1

19

19

M_B_CKE0

M_B_CKE1

19

19

M_A_DQ[63:0]18

M_B_DQ[63:0] 19

M_A_CLKN0

M_A_CLKP0

M_A_CLKN1

M_A_CLKP1

18

18

18

18

M_B_CLKN0

M_B_CLKP0

M_B_CLKN1

M_B_CLKP1

19

19

19

19

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

19

18

19

M_A_DQSN[7:0] 18

M_A_DQSP[7:0] 18

M_B_DQSN[7:0] 19

M_B_DQSP[7:0] 19

M_B_BS#0 19

M_B_BS#1 19

M_B_BS#2 19

M_B_A[15:0] 19

Siiize Document Number

BDW MCP(LPDDR3)

2A

Date: Wednesday,,, November19,,, 2014 Sheettt 7 offf 48

1

Quanta Computer Inc.

PROJECT :

FH9

Rev

T15

M_A_CS#0

M_A_CS#1

T16

BD W_ ULT _D DR3 L

DDR CHANNELA

3 OF19

U31C

SM_VREF_DQ 1

SM_VREF_DQ0

AP51

SM_VREF_CA

AR51

AP49

SA_DQSP7

SA_DQSP6

AL49

M_A_DQSP7

AJ62

M_A_DQSP0

SA_DQSP0

AN61

M_A_DQSP1

SA_DQSP1

AN58

M_A_DQSP2

SA_DQSP2

AN55

M_A_DQSP3

SA_DQSP3

AW57

M_A_DQSP4

SA_DQSP4

AW53

M_A_DQSP5

SA_DQSP5

AL42

M_A_DQSP6

SA_DQSN 7

SA_DQSN 6

AL48

M_A_DQSN7

SA_DQSN0

AN62

M_A_DQSN1

SA_DQSN1

AM58

M_A_DQSN2

SA_DQSN2

AM55

M_A_DQSN3

SA_DQSN3

AV57

M_A_DQSN4

SA_DQSN4

AV53

M_A_DQSN5

SA_DQSN 5

AL43

M_A_DQSN6

AJ61

M_A_DQSN0

SA_MA15

SA_MA14

AU42

M_A_A15

AU36

M_A_A0

SA_MA0

AY37

M_A_A1

SA_MA1

AR38

M_A_A2

SA_MA2

AP36

M_A_A3

SA_MA3

AU39

M_A_A4

SA_MA4

AR36

M_A_A5

SA_MA5

AV40

M_A_A6

SA_MA6

AW39

M_A_A7

SA_MA7

AY39

M_A_A8

SA_MA8

AU40

M_A_A9

SA_MA9

AP35

M_A_A10

SA_MA10

AW41

M_A_A11

SA_MA11

AU41

M_A_A12

SA_MA12

AR35

M_A_A13

SA_MA13

AV42

M_A_A14

SA_BA2

SA_BA1

AY41

M_A_BS#2

SA_BA0

AV35

M_A_BS#1

AU35

M_A_BS#0

SA_CAS

SA_W E

AU34

M_A_CAS#

SA_RAS

AW 34

M_A_WE#

AY34

M_A_RAS#

SA_ODT0

AP32

AP33

M_A_CS#0

SA_CS#1

SA_CS#0

AR32

M_A_CS#1

SA_CKE3

AU43

M_A_CKE0

SA_CKE0

AW 43

M_A_CKE1

SA_CKE2

AY43

SA_CKE1

AY42

SA_DQ63

AK51

SA_DQ62

AM51

SA_DQ61

AK48

SA_DQ60

AM48

SA_DQ59

AK49

SA_DQ58

AM49

SA_DQ57

AK46

SA_DQ56

AM46

SA_DQ55

AM42

SA_DQ54

AM40

SA_DQ53

AK43

SA_DQ52

AK45

SA_DQ51

AM45

SA_DQ50

AM43

SA_DQ49

AK42

SA_DQ48

AK40

SA_DQ47

AU52

SA_DQ46

AV52

SA_DQ45

AU54

SA_DQ44

AV54

SA_DQ43

AW 52

SA_DQ42

AY52

SA_DQ41

AW 54

SA_DQ40

AY54

SA_DQ39

AU56

SA_DQ38

AV56

SA_DQ37

AU58

SA_DQ36

AV58

SA_DQ35

AW 56

SA_DQ34

AY56

SA_DQ33

AW 58

SA_DQ32

AY58

SA_DQ31

AN54

SA_DQ30

AR54

SA_DQ29

AK54

SA_DQ26

AP55

SA_DQ23

AN57

SA_DQ22

AR57

SA_DQ21

AK58

SA_DQ20

AL58

SA_DQ19

AK57

SA_DQ18

AM57

SA_DQ17

AR58

SA_DQ16

AP58

SA_DQ15

AP60

SA_DQ14

AP61

SA_DQ13

AM60

SA_DQ12

AM61

SA_DQ11

AP62

SA_DQ10

AP63

SA_DQ9

AM62

SA_DQ8

AM63

SA_DQ7

AK60

SA_DQ6

AK61

SA_DQ5

AK62

SA_DQ2

AK63

SA_DQ1

AH62

SA_DQ0

AH63 AU37

M_A_CLKN0

SA_CLK#0

AV37

M_A_CLKP0

SA_CLK0

AW 36

M_A_CLKN1

SA_CLK1

SA_CLK#1

AY36

M_A_CLKP1

AK55

SA_DQ28

AL55

SA_DQ27

AM54

SA_DQ25

AR55

SA_DQ24

AH60

SA_DQ4

AH61

SA_DQ3

BD W_ ULT _D DR3 L

DDR CHANNELB

4 OF19

U31D

SB_DQSN 7

SB_DQSP7

SB_DQSP6

AM18

M_B_DQSP7

AV30

M_B_DQSP0

SB_DQSP0

AW26

M_B_DQSP1

SB_DQSP1

AM28

M_B_DQSP2

SB_DQSP2

AM25

M_B_DQSP3

SB_DQSP3

AV22

M_B_DQSP4

SB_DQSP4

AW18

M_B_DQSP5

SB_DQSP5

AM21

M_B_DQSP6

SB_DQSN 6

AN18

M_B_DQSN7

SB_DQSN0

AV26

M_B_DQSN1

SB_DQSN1

AN28

M_B_DQSN2

SB_DQSN2

AN25

M_B_DQSN3

SB_DQSN 3

AW22

M_B_DQSN4

SB_DQSN 4

AV18

M_B_DQSN5

SB_DQSN 5

AN21

M_B_DQSN6

AW 30

M_B_DQSN0

SB_MA15

SB_MA14

AP46

M_B_A15

AP40

M_B_A0

SB_MA0

AR40

M_B_A1

SB_MA1

AP42

M_B_A2

SB_MA2

AR42

M_B_A3

SB_MA3

AR45

M_B_A4

SB_MA4

AP45

M_B_A5

SB_MA5

AW46

M_B_A6

SB_MA6

AY46

M_B_A7

SB_MA7

AY47

M_B_A8

SB_MA8

AU46

M_B_A9

SB_MA9

AK36

M_B_A10

SB_MA10

AV47

M_B_A11

SB_MA11

AU47

M_B_A12

SB_MA12

AK33

M_B_A13

SB_MA13

AR46

M_B_A14

SB_BA2

SB_CAS

SB_W E

AM33

M_B_CAS#

AL35

M_B_BS#0

SB_BA1

AU49

M_B_BS#2

SB_BA0

AM36

M_B_BS#1

SB_RAS

AK35

M_B_WE#

AM35

M_B_RAS#

SB_CS#1

SB_ODT0

AL32

SB_CS#0

AK32

M_B_CS#1

AM32

M_B_CS#0

SB_CKE1

AW 49

SB_CKE3

SB_CKE2

AV50

SB_CKE0

AU50

M_B_CKE1

AY49

M_B_CKE0

SB_CK1

SB_CK#1

AL38

M_B_CLKP1

SB_CK0

AK38

M_B_CLKN1

SB_CK#0

AN38

M_B_CLKP0

AM38

M_B_CLKN0

SB_DQ63

AP18

SB_DQ62

AR18

SB_DQ61

AR20

SB_DQ56

AK18

SB_DQ57

AL18

SB_DQ58

AM20

SB_DQ60

AK20

SB_DQ59

AN22

SB_DQ51

AP21

SB_DQ52

AK21

SB_DQ53

AN20

SB_DQ55

AK22

SB_DQ54

AU17

SB_DQ46

AR21

SB_DQ47

AR22

SB_DQ48

AM22

SB_DQ50

AL21

SB_DQ49

AV17

SB_DQ45

AY17

SB_DQ41

AW 17

SB_DQ42

AU19

SB_DQ44

AV19

SB_DQ43

AW 19

SB_DQ40

AU23

SB_DQ36

AV21

SB_DQ37

AY19

SB_DQ39

AU21

SB_DQ38

AV23

SB_DQ35

AY23

SB_DQ31

AW 23

SB_DQ32

AL25

SB_DQ30

AW 21

SB_DQ34

AY21

SB_DQ33

AR25

SB_DQ25

AP25

SB_DQ26

AK26

SB_DQ27

AK25

SB_DQ29

AM26

SB_DQ28

AN29

SB_DQ20

AR28

SB_DQ21

AP28

SB_DQ22

AR26

SB_DQ24

AN26

SB_DQ23

AU25

SB_DQ14

AM29

SB_DQ15

AK29

SB_DQ16

AL28

SB_DQ17

AR29

SB_DQ19

AK28

SB_DQ18

AW 25

SB_DQ10

AV25

SB_DQ13

AY27

SB_DQ7

AY25

SB_DQ9

AW 27

SB_DQ8

AY31

AW 31

SB_DQ0

AY29

SB_DQ1

AW 29

SB_DQ2

AU31

SB_DQ4

AV31

SB_DQ3

AU27

SB_DQ12

AV27

SB_DQ11

AU29

SB_DQ6

AV29

SB_DQ5

Page 9

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

GPIO27

With IntelLAN:

Connect to LANWAKE# pin on the LAN

Without IntelLAN:

Used to wake event from DSx

Broadwell Type-U ULT(GPIO,LPIO,MISC)

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

Board ID:

08

GPIOPU/PD

CPU MISCPU/PD

Note:

GSPI,UART,I2C and SDIO are only supported on

the system that enable Connected Stanby

Core

Core

Core

Core

Core

Core

Core

Core

Sus

Sus

Core

Core

Core

Core

Core

Core

Core

Core

For GPU use

For GPU use

For GPU use

BOARD_ID0 PCH_GPIO0

UMA 0

DIS 1

BOARD_ID1 PCH_GPIO1

LVDS 0

eDP 1

BOARD_ID2 PCH_GPIO3

VGA 0

Non-VGA 1

BOARD_ID3 PCH_GPIO4

TOUCH 0

Non-TOUCH 1

PCH_GPIO93

PCH_GPIO94

PCH_GPIO69

PCH_THRMTRIP#

SIO_EXT_SMI#_46

GPU_ON_PCH

PCH_GPIO85

EC_RCIN#

SERIRQ

PCH_GPIO24

PCH_GPIO27

PCH_GPIO25

PCH_GPIO45

NFC_DETECT#

PCH_GPIO7

PCH_GPIO83

SIO_EXT_SWI#

PCH_GPIO12

PCH_GPIO64

PCH_GPIO65

PCH_GPIO89

PCH_GPIO90

BOARD_ID3

PCH_GPIO5

PCH_GPIO91

PCH_GPIO92

PCH_GPIO24

PCH_GPIO13

PCH_GPIO45

PCH_GPIO9

EC_RCIN#

SERIRQ

PCH_GPIO25

PCH_GPIO26

PCH_GPIO27

PCH_GPIO12

PCH_GPIO87

PCH_GPIO88

PCH_GPIO13

PCH_GPIO14

PCH_GPIO56

SIO_EXT_SWI#

PCH_GPIO56

PCH_GPIO26

PCH_GPIO16

GPU_PWRGD

PCH_GPIO39

PCH_GPIO67

ODD_PWR_EN

PCH_GPIO14

PCH_GPIO59

ODD_DM#_PCH

PCH_GPIO38

PCH_GPIO76

ODD_DM#_PCH

BOARD_ID2

BOARD_ID0

BOARD_ID1

PCH_GPIO58

PCH_GPIO59

PCH_GPIO58

PCH_GPIO44

PCH_GPIO91

PCH_GPIO92

PCH_GPIO89

PCH_GPIO90

GPU_RST#_PCH

SIO_EXT_SMI#_49

GPU_PWRGD

ODD_PWR_EN

PCH_GPIO9

PCH_GPIO10

PCH_GPIO44

PCH_GPIO47

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

SIO_EXT_SCI#

PCH_GPIO71

NFC_DWL_REQ_R

PCH_GPIO38

NFC_RST#

PCH_GPIO88

PCH_GPIO85

PCH_GPIO87

PCH_GPIO83

PCH_GPIO93

PCH_GPIO94

PCH_GPIO71

PCH_GPIO64

PCH_GPIO76

PCH_GPIO67

PCH_GPIO69

PCH_GPIO65

ACZ_SPKR10,31

37

SERIRQ 35,37

PCH_GPIO66 10

PLTRST# 12,20,29,30,34,35,37

GPU_PWRGD_SVID_REG44

GPU_ON_PCH

BBS 10

20,37

37,44,45 GPU_PW RGD

ODD_PWR_EN 33

ODD_DM#_PCH 33

20,37 GPU_RST#_PCH

B-34

33 DEVSLP0

SIO_EXT_SWI#37

SIO_EXT_SCI#37

36 MOUSE_CNCT#

PCH_GPIO1510

NFC_RST_BUFF#34

NFC_DETECT# 34

NFC_DWL_REQ34

37 SIO_EXT_SMI#

3V_S0

3V_S5

3V_S0

3V_S0

3V_S5

3V_S0

3V_S0

3V_S0

1.05V_VCCST

3V_S0 3V_S0

3V_S0

S5_ON 37,39

Size Document Number

BDW PCH(GPIO/LPIO/MISC)

Rev

2A

8 of 48Date: W ednesday, November 19, 2014 Sheet

Quanta ComputerInc.

PROJECT :

FH9

BDW_ULT_DDR3L

GPIO

CPU/

MISC

U31J

RSVD

AB21

50 +/- 1% pull to VSS

RSVD

AF20

PCH_OPI_RCOMP

SERIRQ

T4

AM7

LAN_PHY_PWR_CTRL/GPIO12

DSW

AL4

GPIO58

Sus

AK4

GPIO44

Sus

P1

BMBUSY/GPIO76

Core

AU2

GPIO8

AD6

GPIO15

Sus

T3

GPIO17

Core

Y1

GPIO16

Core

AT5

GPIO59

Sus

U4

GPIO48

Core

AB6

GPIO47

Sus

Y3

GPIO49

Core

P3

GPIO50

Core

Y2

HSIOPC/GPIO71

AT3

GPIO13

Sus

AM4

GPIO25

DSW

AH4

GPIO14

Sus

AG3

GPIO46

Sus

AM2

GPIO10

Sus

AM3

GPIO9

P2

DEVSLP0/GPIO33

Core

C4

SDIO_POWER_EN/GPIO70

Core

L2

DEVSLP1/GPIO38

Core

V2

SPKR/GPIO81

N5

DEVSLP2/GPIO39

Core

THRMTRIP

D60

RCIN/GPIO82

V4

Core

GSPI0_CS/GPIO83

R6

Core

GSPI0_MISO/GPIO85

N6

Core

GSPI0_CLK/GPIO84

L6

Core

GSPI0_MOSI/GPIO86

L8

Core

GSPI1_CS/GPIO87

R7

Core

GSPI1_CLK/GPIO88

L5

Core

GSPI_MOSI/GPIO90

K2

Core

GSPI1_MISO/GPIO89

N7

Core

UART0_RXD/GPIO91

J1

UART0_RTS/GPIO93

J2

Core

UART0_TXD/GPIO92

K3

10 OF 19

SCEoRrIAeLIO

UART0_CTS/GPIO94

G1

UART1_TXD/GPIO1

G2

UART1_RXD/GPIO0

K4

I2C0_SCL/GPIO5

F3

I2C1_SDA/GPIO6

G4

I2C1_SCL/GPIO7

F1

Core

SDIO_CMD/GPIO65

F4

Core

SDIO_CLK/GPIO64

E3

SDIO_D0/GPIO66

D3

SDIO_D3/GPIO69

E2

SDIO_D2/GPIO68

C3

SDIO_D1/GPIO67

E4

AD7

GPIO28

Sus

AP1

GPIO57

Sus

AG6

GPIO56

Sus

AG5

GPIO45

Sus

AD5

GPIO24

Sus

AN5

GPIO27

DSW

AN3

GPIO26

Sus

UART1_RST/GPIO2

J3

I2C0_SDA/GPIO4

F2

UART1_CTS/GPIO3

J4

PCH_OPI_RCOMP

AW15

PCH_OPIRCOMP

SIO_EXT_SCI#

R433

SIO_EXT_SMI#_46

R191

PCH_GPIO7

R143

SIO_EXT_SMI#

R584 0_4

U10

S@TC7SH08FU(F)

2

GPU_PWRGD

1 PLTRST#

4

3

5

R512

EC_RCIN#

49.9/F_4

R583 *0_4

R231

R476

S@0.1U/10V_4_X7R C263

C283

*100P/50V_4

RN4

1

3

576

8

R183

R161

10K_4

10K_4

R277 N@0_4

NFC_DWL_REQ_R

R129

RN3 10KX4

1

3

576

8

R224

R464

R493

R211

RN2

10KX4

2

4

1

3

5

7

2

4

6

8

PMBT3904

2

1 3

Q28

R403

R409

R227

R507

R156

R387

R393 R408 R397 R157

*10K_4 *10K_4 *10K_4 *10K_4

R411

1K_4

R275

100K_4

GPU_RST#_PCH

R467

PCH_GPIO10

R216

PCH_GPIO47

R195

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

R180

R504

U15

*N@TC7SH08FU

2 PLTRST#

1

NFC_RST#

4

3

5

GPU_ON_PCH

R151

PCH_GPIO16

R447

R400

1K_4

R217

R510

RN1

10KX4

2

4

1

3

5

7

10KX4

2

4

6

8

R202

R468

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

R394 R415 R399 R155

10K_4 10K_4 10K_4 10K_4

R130 N@0_4

SIO_EXT_SMI#_49

R450

NFC_DETECT#

R147

PCH_GPIO39

R144

PCH_GPIO5

R177

*10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

*10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

Page 10

5

5

4

4

3

3

2

2

1

D D

C

B B

A A

PCIE_RCOMP

3K+/- 1% pull to VCCUSB3PLL

Trace Width: 12-15 mils(trace)

Spacing: 12mils

Length: 500mils Max

PCIE_IREF

Directly connect to VCCUSB3PLL

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

USBBIAS & USBBIAS#

Short the USBRBIAS and the USBRBIAS# pins and one end of 22.6 +/- 1% to GND

Route signal using 50 ohm single-ended impedance

Spacing: 15mils

Length: 500milsMax

USB debugport

Broadwell Type-U ULT (PCIE,USB)

09

Wireless Dongle

WLAN(NGFF)

Sus

C

GLAN

USB3.0

USB2.0 Port (Co-lay USB3.0)

USB2.0 Port (Co-lay USB3.0)

USB2.0 Port (Co-layUSB3.0)

Touchscreen

Camera

Bluetooth

USB2.0 Port

Card Reader

TOPAZ

USB3.0

USB3.0

For GPUuse

B-9

USB_BIAS

USB3_RXN2

USB3_RXN1

USB_OC3#

USB_OC0#

USB_OC1#

PEG_TXN0_C

PEG_TXP0_C

PEG_TXN1_C

PEG_TXP1_C

PEG_TXN2_C

PEG_TXP2_C

PEG_TXN3_C

PEG_TXP3_C

32

32

32

32

28

28

34

34

USB_OC0# 32

32

32

36

36

32

32

PCIE_RXN_WLAN

PCIE_RXP_WLAN

34

34

PCIE_RXN_LAN

PCIE_RXP_LAN

29

29

USB3_RXN1

USB3_RXP1

32

32

USB3_TXN1

USB3_TXP1

32

32

USB3_RXN2

USB3_RXP2

32

32

USB3_TXN2

USB3_TXP2

32

32

USB3_RXN4

USB3_RXP4

32

32

PCIE_RXN_CARD

PCIE_RXP_CARD

30

30

PCIE_TXN_CARD

PCIE_TXP_CARD

30

30

USB3_TXN4

USB3_TXP4

32

32

PCIE_TXN_LAN

PCIE_TXP_LAN

29

29

PCIE_TXN_WLAN

PCIE_TXP_WLAN

34

34

PEG_TXN3

PEG_TXP3

20

20

PEG_TXN2

PEG_TXP2

20

20

PEG_TXN1

PEG_TXP1

20

20

PEG_TXN0

PEG_TXP0

20

20

PEG_RXN0

PEG_RXP0

20

20

PEG_RXN1

PEG_RXP1

20

20

PEG_RXN2

PEG_RXP2

20

20

PEG_RXN3

PEG_RXP3

20

20

35

35

MOUSE_ON 36

+V1.05S_AUSB3PLL

3V_S5

Siiize DocumentNumber

Date:

BDW PCH(PCIE/USB)

Rev

2A

9 of 48Wednesday,November19, 2014 Sheet

1

Quanta ComputerInc.

PROJECT :

FH9

BDW_ULT_DDR3L

PCIE USB

11 OF19

U31K

RSVD

RSVD

AM10

USB2P1

AT7

USBP1+

USB2P0

AM8

USBP0+

G11

PERN3

C23

PETN5_L0

USBRBIAS

AJ10

USBRBIAS

AN10

AJ11

B23

PETN5_L1

A23

PETP5_L1

USB2N7

AR13

USB_WL#

USB2P7

AP13

USB_WL

USB2N6

AP11

USB_Conn#

USB2P5

AN13

USB_BT

USB2N5

AM13

USB_BT#

USB2P6

AN11

USB_Conn

USB2P4

AL15

USB_C

USB2N4

AM15

USB_C#

USB2P3

AT10

USB_TS

USB2N3

AR10

USB_TS#

USB2P2

AP8

USBP2+

USB2N2

AR8

USBP2-

USB2N1

AR7

USBP1-

USB2N0

AN8

USBP0-

PETP4

G13

PERP4

E6

PERN5_L3

F6

PERP5_L3

B21

PETN5_L2

G10

PERP5_L2

H10

PERN5_L2

OC0/GPIO40

Sus

AL3

USB_OC0#

AT1

USB_OC1#

OC1/GPIO41

Sus

AH2

OC3/GPIO43

OC2/GPIO42

Sus

AV3

USB_OC3#

PETN3

F11

PERP3

F8

PERN5_L1

B22

PETN5_L3

A21

PETP5_L3

E8

PERP5_L1

A29

PETN4

C22

PETP5_L0

E10

PERP5_L0

F10

PERN5_L0

F13

PERN4

PCIE_IREF

B27

PCIE_RCOMP

A27

RSVD

E13

C21

PETP5_L2

PERP1/USB3RP3

F17

PERN1/USB3RN3

G17

E15

RSVD

PETP1/USB3TP3

F15

PERN2/USB3RN4

PETP2/USB3TP4

A31

PETN2/USB3TN4

B31

G15

PERP2/USB3RP4

USB3RN1

G20

USB3_RXP1

USB3RP1

H20

USB3TN1

C33

USB3_TXN1

USB3TP1

B34

USB3_TXP1

USB3RN2

E18

USB3_RXP2

USB3RP2

F18

B33

USB3_TXN2

USB3TP2

USB3TN2

A33

USB3_TXP2

R198 22.6/F_4

C468

PCIE_TXN_LAN_C

B29

0.1uF/16V/X7R_4

PCIE_TXP_LAN_C

C166 S@0.1uF/16V/X7R_4

C170S@0.1uF/16V/X7R_4

R230

C4690.1uF/16V/X7R_4

C466 0.1uF/16V/X7R_4

PCIE_TXN_WLAN_C

C29

C141 S@0.1uF/16V/X7R_4

C152S@0.1uF/16V/X7R_4

C467 0.1uF/16V/X7R_4

PCIE_TXP_WLAN_C

B30

PETP3

C156 S@0.1uF/16V/X7R_4

C164S@0.1uF/16V/X7R_4

C471 0.1uF/16V/X7R_4

PCIE_TXP_CARD_C

C31

PETN1/USB3TN3

C131 S@0.1uF/16V/X7R_4

C138S@0.1uF/16V/X7R_4

C465 0.1uF/16V/X7R_4

PCIE_TXN_CARD_C

C30

R117

R120

3K/F_4

PCIE_RCOMP

*SHORT_4

PCIE_IREF

R233

R469

10K_4

10K_4

10K_4

Page 11

5

5

4

4

3

3

2

2

1

D D

C C

B B

A A

RTC Circuitry(RTC)

INTVRMEN

Integrated 1.05V VRMenable ALWAYS

PCH Strap Table

Pin Name Strap description

Sampled Configuration Schematic

SPKR/GPIO81

No reboot modesetting PWROK

HDA_SDO/I2S0_TXD Flash Descriptor SecurityOverride

PWROK

DSWVRMEN

DeepSx Well On-Die VRMEnable ALWAYS

GPIO15

TLS Confidentiality RSMRST#

GSPI0_MOSI/GPIO86

Boot BIOS Strap Bit PWROK

SDIO_D0/GPIO66

Top Swap Override PWROK

10

HDD (Base)

NGFF SSD/HDD(Slate)

SATA_RCOMP

3K+/- 1% pull toVCCASATA3PLL

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

Core

Core

Core

Core

20MIL

20MIL

HDA Audio(CLG)

PCH JTAG Debug(CLG)

SATAHDD

SATAODD

0 = Enable Flash Descriptor security. (Int PD)

1 = Disable Flash DescriptorSecurity

0 = DCPSUSx are powered from an ext. power source

1 = Integrated VRM enabled (330K PU VccRTC)

0 = Disable Integrated DSW On-DieVRM

1 = Enable Integrated DSW On-Die VRM (Must bePU)

0 = Disable Intel ME Crypto TLS cipher suite (Int PD)

1 = Enable Intel ME CryptoTransport

0 = Disable No Reboot mode (Int PD).

1 = Enable No Reboot mode.

0 = Boot from SPI

1 = Boot fromLPC

0 = Disable Top Swap mode. (Int PD)

1 = Enable Top Swapmode.

A+-36

B-9

B-9

B-9

B-24C-1

RTC XTAL 32.768KHz

MP1-1

RTC_X1

RTC_X2

SRTC_RST#

RTC_RST#

HDA_BITCLK

HDA_SYNC

HDA_RST#

HDA_SDOUT

PCH_JTAGX

PCH_EDM

SRTC_RST#

VCCRTC_1

PCH_JTAG_TDO

PCH_JTAGX

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TCK

PCH_GPIO36

PCH_GPIO37

VCCRTC_

2

RTC_RST#

DSWVRMEN 12

ACZ_SPKR 8,31

BBS 8

PCH_GPIO66 8

ACZ_SDIN0_AUDIO31

31 ACZ_SYNC_AUDIO

31 ACZ_RST#_AUDIO

31 ACZ_SDOUT_AUDIO

31 ACZ_BITCLK_AUDIO

HDA_SDOUT 37

ODD_DP#_PCH 33

SATA_RXN1

SATA_RXP1

SATA_TXN1

SATA_TXP1

33

33

33

33

SATA_RXN2

SATA_RXP2

SATA_TXN2

SATA_TXP2

33

33

33

33

37 CLR_CMOS

8 PCH_GPIO15

3V_S5

3V_RTC

3V_RTC

3V_S5

3V_S0

3V_S0

+V3.3S_1.8S_LPSS_SDIO

3V_S0

3V_RTC

+V1.05S_ASATA3PLL

3V_AUX 3V_RTC

1.05V_S0

VCCRTC_2

Siiize DocumentNumber

Date:

BDW PCH(RTC/HDA/SATA)

Rev

2A

Wednesday,November19, 2014 Sheet 10 of 48

1

Quanta ComputerInc.

PROJECT :

FH9

C526

1U/10V_4

R505 20K/F_6

R575 *0_4

RTC_X1

R506 *SHORT_4

SATA_RCOMP

R356

3K/F_4

SATA_LED# 33

SATA_IREF

Directly connect to VCCASATA3PLL

Trace Width: 12-15mils(trace)

Spacing: 12mils

Length: 500mils Max

36 CLKGEN_RTC_X1

A+-20 B-8

C520 *18P/50V_4

R518 *1K_4

HDA_SDOUT

ODD_DP#_PCH_R

R440

R576 *0_4

RTC_X2

T46

CN19

LTS_AAA-BAT-054-K01

1

2

C514

1U/10V_4

Y5

*32.768KHZ/20PPM

2 1

*18P/50V_4C522

R489

*SHORT_4

R439 *SHORT_4

R503

*10M_4

R171

R456

R478 *51_4

T51

C518

1U/10V_4

R215

R485

R197 8.2K_4

R181 *1K_4

R519

20MIL

R569

1K/F_4

R501 20K/F_6

Q25

PDTC144EU

1

3

2

C535

*0.1U/10V_4

R526 1M_4

SM_INTRUDER#

JTAG

RTC

AUDIO SATA

5 OF19

Broadwell Type-U ULT (RTC,HDA,JTAG,SATA)

U31E

BDW_ULT_DDR3L

RSVD

K10

PCH_JTAG_TCK

AE62

PCH_TRST

PCH_XDP_TRST_CPU_N

AU62

AV10

HDA_DOCK_RST/I2S1_SFRM

AW10

HDA_DOCK_EN/I2S1_TXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AY10

HDA_SDI0/I2S0_RXD

AU8

HDA_RST/I2S_MCLK

AV11

HDA_SYNC/I2S0_SFRM

AW8

HDA_BCLK/I2S0_SCLK

PCH_JTAG_TDI

AD61

PCH_TCK

PCH_JTAG_TDO

AE61

PCH_TDI

PCH_JTAG_TMS

AD62

PCH_TDO

AL11

PCH_TMS

RSVD

AY8

I2S1_SCLK

SATALED

AV2

JTAGX

AC4

RSVD

AE63

RSVD

AY5

RTCX2

SATA_RCOMP

U3

SATA_LED#

RSVD

C12

SATA_IREF

L11

SATA3GP/GPIO37

SATA2GP/GPIO36

AC1

PCH_GPIO37

SATA1GP/GPIO35

V6

PCH_GPIO36

SATA0GP/GPIO34

U1

ODD_DP#_PCH_R

V1

PCH_GPIO34

SATA_TP3/PETP6_L0

D17

SATA_TN3/PETN6_L0

C17

SATA_RP3/PERP6_L0

E5

SATA_RN3/PERN6_L0

F5

SATA_TP2/PETP6_L1

C15

SATA_TN2/PETN6_L1

B14

SATA_RN2/PERN6_L1

J6

SATA_RP2/PERP6_L1

H6

SATA_TP1/PETP6_L2

B17

SATA_TN1/PETN6_L2

A17

SATA_RN1/PERN6_L2

J8

SATA_RP1/PERP6_L2

H8

SATA_TP0/PETP6_L3

A15

SATA_TN0/PETN6_L3

B15

SATA_RP0/PERP6_L3

H5

SATA_RN0/PERN6_L3

J5

AW5

RTCX1

AU7

RTCRST

AV6

SRTCRST

PCH_INTVRMEN

AV7

INTVRMEN

AU6

INTRUDER

R520

R528

33_4

HDA_SDOUT

33_4

HDA_BITCLK

T52

R200 *1K_4

SATA_LED#

R174

PCH_GPIO34

R445

10K_4

10K_4

10K_4

10K_4

10K_4

*330K_4

R514 330K_4

R391

R389

*1K_4

1K_4

33_4

HDA_SYNC

33_4

HDA_RST#

R513

R582

*100K/F_4

A12

SATA_IREF

R355

*SHORT_4

CL1_CL2

*PAD

1

2

R486

R487

*51_4

*51_4

*51_4

*1K_4

R515 330K_4

PCH_INTVRMEN

R517

D34

BAT54CW

R392

R396

*1K_4

*1K_4

Page 12

5

5

4

4

3

3

2

2

1

D

C C

B B

A

Broadwell Type-U ULT (LPC/SPI/SMB/CLINK)

Broadwell Type-U ULT (CLK)

Do not short

the testlow pins together.

Length: 500milsMax

11

Sus

Sus

Sus

Sus

LAN

Normal Mode -> 2.2Kohm

Fast Mode -> 499 ohm

SMBus/Pull-up(CLG)

CLK REQ PU(CLG)

Use one 33-Ω series-resistor per device if using two SPI devices.

15-Ω series resistor required if a single device is used.

SOCKET PN:DG008000031

D

Card

For GPUuse

WLAN

Topaz

Reserve forRF

Reserve forRF

B-9

B-9

B-9

B-25 B-9

B-37

B-38

B-8

PCH Dual SPI

EC & BIOS & ME F/W ROM 8MB

B-69

MP1-2

TESTLOW_0

TESTLOW_1

TESTLOW_2

TESTLOW_3

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_IO2

PCH_SPI_IO3

SMBALERT#

SML0ALERT

SMB_ME1_CLK

SMB_ME1_DAT

SMB_ME0_DAT

SMB_PCH_CLK

SMB_PCH_DAT

SMBALERT#

SMB_ME0_CLK

PCH_SPI_IO3

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ1#

PCIE_CLK_REQ0#

PCIE_CLK_REQ2#

PCIE_CLK_REQ5#

SML0ALERT

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_CS0#_R

PCH_SPI_CLK_R

CLK_PCIE_N5

CLK_PCIE_P5

SMB_ME0_DAT

SMB_ME0_CLK

SMB_PCH_DAT

SMB_ME1_CLK

SMB_ME1_DAT

CLK_PCIE_N1

CLK_PCIE_P1

PCH_SPI_CS0#_R

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

PCLK_DEBUG 34

PCLK_TPM 35

CLK_33M_KBC 37

37 EC_CE#

37 EC_SCK

37 EC_SI

37 EC_SO

PCH_XTAL24_IN 36

NFC_IRQ 34

NFC_SDA 34 A

NFC_SCL 34

SMB_RUN_DAT18,19,27

SMB_RUN_CLK18,19,27

MBDATA137

MBCLK137

30 CLK_PCIE_CARDN

Reader

30 CLK_PCIE_CARDP

30 PCIE_CLKREQ_CARD#

34 CLK_PCIE_WLANN

34 CLK_PCIE_WLANP

34 PCIE_CLKREQ_WLAN#

29 CLK_PCIE_LANN

29 CLK_PCIE_LANP

29 PCIE_CLKREQ_LAN#

20 CLK_PCIE_DGPUN

20 CLK_PCIE_DGPUP

21 PCIE_CLKREQ_DGPU#

34,35,37 LPC_LFRAME#

3V_S5

3V_S0

3V_S0

3V_S0

3V_S0

3V_S5

3V_S0

3V_S0

CL_RST# 34

CL_DAT 34

CL_CLK 34

LPC_LAD0

LPC_LAD1

LPC_LAD2

34,35,37

34,35,37

34,35,37

34,35,37 LPC_LAD3

Siiize DocumentNumber

BDW PCH(CLK/LPC/SPI/SMB)

Rev

2A

Date: Wednesday,November19, 2014 Sheet 11 of 48

1

Quanta ComputerInc.

PROJECT :

FH9

Q9

N@2N7002KDW/60V/115MA

6

2

1

5

43

R432 *SHORT_4

R274N@1K/F_4

CLOCK

SIGNALS

BDW_ULT_DDR3L

6 OF19

U31F

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

PCIE_CLK_REQ1#

Y5

PCIECLKRQ1/GPIO19

Core

2

PCIECLKRQ0/GPIO18

Core

C42

CLKOUT_PCIE_P0

B35

AN15

CLK_PCI_LPC

CLKOUT_LPC_1

CLKOUT_LPC_0

AP15

CLK_PCI_EC

PCIECLKRQ4/GPIO22

B39

CLKOUT_PCIE_N4

A39

PCIECLKRQ3/GPIO21

Core

C43

CLKOUT_PCIE_N0

XTAL24_OUT

B25

XTAL24_OUT

XTAL24_IN

A25

XTAL24_IN

PCIE_CLK_REQ5#

T2

PCIECLKRQ5/GPIO23

Core

A37

CLKOUT_PCIE_P5

B37

CLKOUT_PCIE_N5

PCIE_CLK_REQ3#

N1

CLKOUT_PCIE_P3

C37

CLKOUT_PCIE_N3

B38

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

RSVD

K21

RSVD

M21

TESTLOW_C35

C35

TESTLOW_0

TESTLOW_C34

C34

TESTLOW_1

TESTLOW_AK8

AK8

TESTLOW_2

TESTLOW_AL8

AL8

TESTLOW_3

CLKOUT_ITPXDP_P

CLKOUT_ITPXDP

A35

C255 *3.3P/50V/C0G_4

C476 C493

*10P/50V_4 *10P/50V_4

0_4

0_4

*10P/50V_4

T1

T2

6

SMB_PCH_CLK

2

1

5

4 3

R154

S@0_4

PCIE_CLK_REQ4#

U5

CLKOUT_PCIE_P4

Core

R420 *SHORT_4

B-9

T3

T4

1K_4

22_4

C488

0.1U/10V_4

RP1 10KX2

2

4

1

3

3V_S5

R460

PCH_SPI_IO2

R474

33_4

TP81

TP62

SMBus

3V_S5

R212

10K_4

R430

R483

33_4

33_4

TP66

TP82

R190

*SHORT_4

PCIE_CLK_REQ2#

AD1

PCIECLKRQ2/GPIO20

Core

R459

R463

1K_4

33_4

R492

R490

2.2K_4

2.2K_4

Q32

2N7002KDW/60V/115MA

6

2

1

5

43

RP2 10KX2

4

2

3

1

R250

R251

R521

22_4

22_4

DIFFCLK_BIASREF

C26

XCLK_BIASREF

R114

DIFFCLK_BIASREF

3K/F_4

+V1.05S_AXCK_LCPLL

3K+/- 1% pullto+1.05V

Trace Width:12-15mils(trace)

Spacing: 12mils

R479 4.7K_4

2.2K_4

U32

W25Q64FVSSIQ

1

CE#

6

SCK

5

SI

2

SO

PCH_SPI_WP#

3

WP#

VDD

8

VSS

4

HOLD#

7

PCH_SPI_HOLD#

R276

100K_4

R358 *SHORT_4

3V_S0

R477 4.7K_4

T23

T22

R480

R465

499/F_4

499/F_4

R470

R488

R475

10K_4

2.2K_4

R201

R437

Q31

2N7002KDW/60V/115MA

B-37

N@1K/F_4 R213

C503

*10P/50V_4

T54

R438

*SHORT_4

PCIE_CLK_REQ0#

U

R423

R165

R482

R418

*SHORT_4

33_4

C341

C340

C530

*10P/50V_4

*10P/50V_4

TP27

TP28

TP26

C490

*22P/50V_4

BDW_ULT_DDR3L

LPC

SMBUS

C-LINKSPI

7 OF19

U31G

CL_RST

CL_DATA

AF4

CL_CLK

AD2

AF2

SML1DATA/GPIO74

SML1CLK/GPIO75

AH3

SMB_ME1_DAT

SML1ALERT/PCHHOT/GPIO73

AU3

SMB_ME1_CLK

SML0DATA

AU4

SML0CLK

AK1

SMB_ME0_DAT

AH1

SMB_PCH_DAT

SML0ALERT/GPIO60

AN1

SMB_ME0_CLK

SMBDATA

Sus

AL2

SMBCLK

AP2

SMB_PCH_CLK

SMBALERT/GPIO11

AN2

SPI_IO3

AF1

SPI_IO2

Y6

SPI_MISO

AA4

SPI_MOSI

AA2

SPI_CS2

AC2

SPI_CS1

AA3

Y4

SPI_CS0

Y7

SPI_CLK

LFRAME

AV12

LAD3

AW11

LAD2

AY12

AW12

LAD1

AU14

LAD0

R484

R451

R444

R481

*SHORT_4

0_4

R189

R443

10K_4

10K_4

10K_4

10K_4

10K_4

10K_4

Page 13

5

5

4

4

3

3

2

2

1

D D

C C

B B

A A

Broadwell U-Type ULT (SYSTEM POWER MANAGEMENT)

PCH PWROK (CLG)

SYS PWROK (CLG) PLTRST (CLG)

12

PCH PU/PD (CLG)

Core

Sus

DSW

DSW

DSW Circuit

Reserve for ESD

A+-8

A+-8

B-9

B-9

B-9

B-9

SUSPWRDNACK#

PLTRST#_R

SLP_A#

SLP_SUS#

SUSPWRDNACK#

SLP_LAN#

AC_PRESENT

PM_BATLOW#

SYS_RESET#

MPW ROK

SYS_PW ROK

AC_PRESENT

PM_BATLOW#

PCH_GPIO32

SYS_RESET#

PCH_RSMRST#

PCH_PWROK

SYS_PW ROK

SYS_PW ROK

PCH_RSMRST#

DPW ROK

PCH_PWROK

PCH_APW ROK

SLP_S0#

SLP_W LAN#_R

PLTRST#_R

PCH_SUSACK#

PCH_PWRBTN#

DNBSWON#37

DSWVRMEN 10

PCIE_WAKE# 21,29,34

SUSC#

SUSB#

36,37

37

IMVP_PWRGD 13,43

MPW ROK 13,37

PLTRST#8,20,29,30,34,35,37

HW PG_3/5V 37,39

RSMRST#37

34

3V_S5 3V_S5

3V_S5

3V_S0

Size DocumentNumber

Date: of

BDW PCH(PWRMANAGEMENT)

2A

48Wednesday, November 19, 2014 Sheet 12

1

Quanta Computer Inc.

PROJECT :

FH9

Rev

R226

*100K_4

C321

*0.1U/10V_4

R188 *SHORT_4

PCH_APWROK

U11

TC7SH08FU

2

1

4

3

5

R228 *0_4

R497 *SHORT_4

PCH_SUSACK#

SUS_CLK

T19

R498

R205

R204 *10K_4

*SHORT_4 DPWROK

D6 *TVS_AZ5123-01F

1

2

Reserve for ESD

R203 *SHORT_4

SYS_PWROK_R

R530 *0_4

R527 *SHORT_4

PCH_PWROK

T18

T17

T20

R531 *SHORT_4

PCH_RSMRST#

A+-18

T45

T48

R529

10K_4

*SHORT_4

R199 *SHORT_4

PCH_PWRBTN#

R524 *0_4

Non Deep Sx

R522

*SHORT_4

PCIE_WAKE#_R

R225

R184

R187

10K_4

10K_4

BDW _ULT_DDR3L

SYSTEM POWERMANAGEMENT

8 OF 19

U31H

AL5

AP4

AJ7

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

AJ6

AT4

SUSCLK/GPIO6 2

CLKRUN/GPIO32

SUS_STAT/GPIO61

Sus

V5

PCH_GPIO32

AG4

SUS_STAT#

AE6

SUS_CLK

AP5

SLP_S5

AJ5

PCIE_WAKE#_R

R223

DSWVRMEN

AW7 DSWVRMEN

DPWROK

WAKE

AV5

DPWROK_R

R525

SLP_WLAN/GPIO29

DSW

AM5

SLP_S0

SUSWARN/SUSPWRDNACK/GPIO30

Sus

PWRBTN

BATLOW/GPIO72

AN4

AF3

ACPRESENT/GPIO31

DSW

AL7

AJ8

RSMRST

AW6

AV4

SUSACK

AB5

AG7

AG2

AY7

SYS_RESET

SYS_PWROK

PCH_PWROK

APWROK

PLTRST

AK2

AC3

SUS_STAT#

R206

TC7SH08FU

2

1 MPWROK

4

3

5

R232

100K_4

SUSPWRDNACK# R496 10K_4

R523

R516

10K_4

10K_4

D8

*TVS_AZ5123-01F

2

1

R234

R214

*10K_4

10K_4

10K_4

10K_4

*10K_4

10K_4

*0.1U/10V_4 C531

U35

Page 14

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Need to short rework after build

Broadwell U-Type ULT MCP(POWER)

13

VCCST (0.1A)

SVID

Place PUresistor

close toCPU

Place PUresistor

close toCPU

VCC_CORE32A

VCC Output DecouplingRecommendations

470uFx4 7343 TOP socketside

22uFx8 0805 4 on TOP, 4 on BOT near socketedge

22uFx11 0805 TOP, inside socketcavity

10uFx11 0805 BOT, inside socketcavity

1.35V_S31.4A

VDDQ Output DecouplingRecommendations

330uFx

2

7343

BOT socketside

22uFx

11

0805

5 onTOP, 6 on BOT inside socketcavity

10uFx

10

0805

5 onTOP, 5 on BOT inside socketcavity

Reserve forRF

Reserve forRF

B-9

B-9

B-9

B-9

B-68

B-9 C-9

C-9

PWR_DEBUG#

H_CPU_SVIDART#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

H_CPU_SVIDCLK

H_CPU_SVIDART#

VCCST_PWRGD_MCPVCCST_PWRGD

B-9 C-9

VR_READY_C VR_READY

VCC_SENSE_R

B-9

H_CPU_SVIDDAT

VCCST_PWRGD_MCP

43 H_VR_EN_MCP

VR_SVID_DATA 43

VR_SVID_ALERT# 43

VR_SVID_CLK 43

43 VCC_SENSE

VCC_CORE

1.05V_VCCST

+VCCIO_OUT

+VCCIOA_OUT

VCC_CORE

VCC_CORE

VCCIO_OUT OPTIONS

+VCCIOA_OUT +VCCIO_OUT

1.05V_S0

1.05V_VCCST

VCC_CORE

1.05V_VCCST

1.35V_S3

3V_S5

1.05V_VCCST

3V_S0 3V_S5

3V_S5

3V_S5

MPWROK12,37

IMVP_PWRGD12,43

Siiize Document Number

Date:

BDWMCP(POWER)

2A

Wednesday,,, November 19,,, 2014 Sheettt 13 offf 48

Quanta Computer Inc.

PROJECT :

FH9

Rev

R132 *0/short_6

R173 *SHORT _4

C339

10u/6.3V/X5R/6

R164 10K_4

VR_READY

Q8

2N7002KDW/60V/115MA

6

2

1

543

C285

22u/6.3V/X5R/6

C277

22u/6.3V/X5R/6

R160 *0_4

R448

10K_4

C244

22U/6.3V_6

C259

22u/6.3V/X5R/6

C248

22U/6.3V_6

U30

74LVC1G07GW

1

NC VCC

5

3

GNDOUT

4

IN

2

C249

22u/6.3V/X5R/6

C473

4.7U/6.3V_4

C533

*10u/6.3V/X5R/6

R176

75_4

C270

22U/6.3V_6

R113

100K_4

C300

*3.3P/50V/C0G_4

1.05V_VCCST

1.05V_S0 1.05V_VCCST

R194 *0_8S

C264

22u/6.3V/X5R/6

R390 *0_8

R410 *SHORT _4

C275

*22u/6.3V/X5R/6

R139

100K_4

C305

2.2U/6.3V_4

C-9

R435

*0/short_4

C262

*22u/6.3V/X5R/6

R449 *0_6

C266

*22U/6.3V_6

C260

22u/6.3V/X5R/6

C291

22u/6.3V/X5R/6

Layout note: need routing together

and ALERT need between CLK andDATA.

1.05V_VCCST

C289 *0.1U/10V_4

C258

22U/6.3V_6

C293

*3.3P/50V/C0G_4

R178 *SHORT _4

R141 *0/short_6

R388 *0_8

R175 43_4

C299

4.7U/6.3V_4

R406 100/F_4

C261

22u/6.3V/X5R/6

C278

22u/6.3V/X5R/6

R453

*100K_4

C247

22u/6.3V/X5R/6

C279 *0.1U/10V_4

C303

2.2U/6.3V_4

C274

22u/6.3V/X5R/6

C217

*0.1u/10V/X5R_4

+

C438

*470u/2V_7343

C243

22u/6.3V/X5R/6

+

C528

*470u/2V_7343

C495

*680P/50V/X7R_4

C302

22u/6.3V/X5R/6

BD W_ ULT _D DR3 L

HSW ULTPOWER

12 OF19

U31L

A59

VCCIO_OUT

E20

VCCIOA_O UT

AD23

RSVD

AB23

RSVD

RSVD

F59

AY44

VDDQ

AY40

VDDQ

AY35

VDDQ

RSVD

V59

RSVD

AC22

VCCST

AY50

VDDQ

AC58

RSVD

N58

VCC

E63

VCC_SENSE

AA23

RSVD

AE59

RSVD

B59

VCCST_PWRGD

C59

VR_READY

F60

VR_EN

AR48

VDDQ

AP43

VDDQ

AN33

VDDQ

AJ37

VDDQ

AJ33

VDDQ

AJ31

VDDQ

VDDQ

AH26

J58

RSVD

L59

RSVD

C28

VCC

VCC

C32

VCC

C24

VCC

VCC

VCC

W5 7

VCC

M57

VCC

U57

VCC

P57

VCC

M23

VCC

L22

VCC

J23

VCC

H23

VCC

G57

VCC

G51

VCC

G55

VCC

G53

VCC

G49

VCC

G47

VCC

G45

VCC

G43

VCC

G41

VCC

G39

VCC

G37

VCC

G35

VCC

G33

VCC

G31

VCC

G29

VCC

G27

VCC

G25

G23

VCC

F52

VCC

F56

VCC

F48

VCC

F44

VCC

F40

VCC

F28

VCC

F32

VCC

F36

VCC

F24

VCC

E57

VCC

E51

VCC

E53

VCC

E55

VCC

E47

VCC

E49

VCC

E41

VCC

E43

VCC

E45

VCC

E37

VCC

E39

VCC

E31

VCC

E33

VCC

E35

VCC

E27

VCC

E29

VCC

C56

VCC

E23

VCC

E25

VCC

C48

VCC

C52

VCC

C36

VCC

C40

VCC

C44

VCC

K57

VCC

K23

AG57

VCC

AD57

AB57

VCC

VCCST

AE23

VCCST

AE22

L63

VIDSOUT

N63

VIDSCLK

VIDALERT

L62

P60

VSS

P61

RSVD_T P

N59

RSVD_T P

N61

RSVD_T P

T59

RSVD_T P

AD60

RSVD

AD59

RSVD

AA59

RSVD

AE60

RSVD

AC59

RSVD

AG58

RSVD

U59

RSVD

D63

P62

PWR_DEBUG

H59

VSS

R185 150_4

U9

*74LVC1G07GW

1

NC VCC

5

3

GNDOUT

4

2

IN

C292

22u/6.3V/X5R/6

C332

10u/6.3V/X5R/6

R146 *0_4

C269

*22U/6.3V_6

C245

*22u/6.3V/X5R/6

R454 *0/short_4

C284

22u/6.3V/X5R/6

C304

2.2U/6.3V_4

C268

*22U/6.3V_6

C276

22U/6.3V_6

C334

10u/6.3V/X5R/6

Q23

*2N7002KDW/60V/115MA

6

2

1

543

R436 *0_6

C280

22u/6.3V/X5R/6

C309

2.2U/6.3V_4 C286

22u/6.3V/X5R/6

C534

*10u/6.3V/X5R/6

C487

0.1u/10V/X5R_4

C294

22u/6.3V/X5R/6

C307 C308

0.1U/10V/X5R/4 0.1U/10V/X5R/4

R179

130/F_4

C529

*10u/6.3V/X5R/6

C267

22U/6.3V_6

C499

0.1u/10V/X5R_4

Page 15

5

5

4

4

3

3

2

2

1

D D

C C

B B

A A

14

Broadwell U-Type ULT (RSVD,GND)

DC_TEST_C1_C2

DC_TEST_B62_B63

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

TP_DC_TEST_AY60

TP_DC_TEST_B2

DC_TEST_A3_B3

DC_TEST_A61_B61

TP_DC_TEST_A60

TP_DC_TEST_A62

TP_DC_TEST_AV1

TP_DC_TEST_AW1

TP_DC_TEST_A4

TP_DC_TEST_AW63

VSS_SENSE 43

Siiize DocumentNumber

BDW MCP(GND/DAISY/RSVD)

Rev

2A

Date: Wednesday,November19, 2014 Sheet 14 of 48

1

Quanta ComputerInc.

PROJECT :

FH9

R412

100/F_4

BDW_ULT_DDR3L

16 OF19

U31P

VSS

Y63

VSS

Y59

VSS

Y10

VSS

V10

VSS

U9

VSS

U22

VSS

U61

VSS

U20

VSS

T58

VSS

T1

VSS

R22

VSS

R8

VSS

R10

VSS

P63

VSS

P59

VSS

N3

VSS

N10

VSS

M22

VSS

L61

VSS

L58

VSS

L20

VSS

L18

VSS

L17

VSS

L15

VSS

L13

VSS

K12

VSS

K1

VSS

J63

VSS

J59

VSS

J22

VSS

H17

F38

VSS

F50

VSS

VSS

AH16

F42

VSS

F34

VSS

G22

VSS

G6

VSS

D39

VSS

D38

VSS

D37

VSS

D35

VSS

D45

VSS

D46

VSS

D47

VSS

D50

VSS

D51

VSS

D53

VSS

D54

VSS

D55

VSS

D59

VSS

D57

VSS

D62

VSS

D8

VSS

E17

VSS

E11

VSS

F46

VSS

F54

VSS

F58

VSS

F61

VSS

G18

VSS

G3

VSS

G5

VSS

G8

VSS

H13

VSS

D43

VSS

D42

VSS

D41

VSS

VSS

H57

VSS

L7

D34

VSS

D33

VSS

J10

VSS

V58

VSS

AH46

VSS

V23

VSS_SENSE

E62

VSS

W22

VSS

W20

VSS

V7

VSS

V3

D5

VSS

D49

VSS

VSS

F30

VSS

F26

VSS

F20

VSS

T53

T50

T32

BDW_ULT_DDR3L

15 OF19

U31O

AV16

VSS

AV24

VSS

AV33

VSS

AV28

VSS

AV20

VSS

AU33

VSS

AU55

VSS

VSS

D26

VSS

D27

VSS

D25

VSS

D23

AV55

VSS

AP38

VSS

AP39

VSS

AP54

VSS

AR11

VSS

AP57

VSS

AR15

VSS

AR17

VSS

AR23

VSS

AR31

VSS

AR33

VSS

AR39

VSS

AR43

VSS

AR49

VSS

AR5

VSS

AR52

VSS

AT13

VSS

AT35

VSS

AT37

VSS

AT40

VSS

VSS

AT42

VSS

AT43

VSS

AT46

VSS

AT49

VSS

AT61

VSS

AT62

VSS

AT63

VSS

AU1

VSS

AU18

VSS

AU22

VSS

AU30

VSS

AU51

VSS

AU53

VSS

AU57

VSS

AU59

VSS

AV14

VSS

AV36

VSS

AV39

VSS

AV41

VSS

AV43

VSS

AV46

VSS

AV49

VSS

AV51

VSS

VSS

AW33

VSS

AW35

VSS

AW37

VSS

AW4

VSS

AW44

VSS

AW47

VSS

AW50

VSS

AW51

VSS

AW59

VSS

AY16

VSS

AY18

VSS

AY22

VSS

AY24

VSS

AY26

VSS

AY30

VSS

AY33

VSS

AY4

VSS

AY51

VSS

AY53

VSS

VSS

AY57

VSS

AY59

VSS

AY6

VSS

B20

VSS

B24

VSS

B26

VSS

B28

VSS

B32

VSS

B36

VSS

B4

VSS

B40

VSS

B44

VSS

B48

VSS

B52

VSS

B56

VSS

B60

VSS

C18

VSS

C20

VSS

C25

VSS

C27

VSS

C38

VSS

C39

VSS

C57

VSS

D12

VSS

D14

VSS

D18

VSS

D2

VSS

D21

VSS

D29

VSS

D30

VSS

D31

AV34

VSS

AV59

VSS

AV8

VSS

AW24

VSS

AW16

VSS

AW42

VSS

AW40

VSS

AY11

VSS

AW60

VSS

C11

VSS

C14

AU28

VSS

AU26

VSS

AU24

VSS

AU20

VSS

AU16

VSS

AP52

VSS

AP48

VSS

AP29

VSS

AP22

AP26

VSS

AP23

VSS

AP31

VSS

AP3

VSS

T34

T47

T49

T7

T31

BDW_ULT_DDR3L

18 OF19

U31R

RSVD

RSVD

AY14

AT2

AU44

RSVD

AV44

RSVD

RSVD

D15

RSVD

F22

H22

RSVD

RSVD

J21

RSVD

N23

RSVD

R23

RSVD

T23

AL1

RSVD

RSVD

U10

RSVD

AM11

RSVD

AP7

RSVD

AU10

RSVD

AU15

RSVD

AW14

BDW_ULT_DDR3L

17 OF19

U31Q

AY2

DAISY_CHAIN_NCTF_AY2

AY60

DAISY_CHAIN_NCTF_AY60

DC_TEST_AY61_AW 61

AY61

DAISY_CHAIN_NCTF_AY61

B2

DAISY_CHAIN_NCTF_B2

DAISY_CHAIN_NCTF_A3

A3

DC_TEST_A3_B3

DAISY_CHAIN_NCTF_A4

A4

DAISY_CHAIN_NCTF_A61

A61

DC_TEST_A61_B61

DAISY_CHAIN_NCTF_A60

A60

DAISY_CHAIN_NCTF_AW1

AW1

DAISY_CHAIN_NCTF_AV1

AV1

DAISY_CHAIN_NCTF_A62

A62

DAISY_CHAIN_NCTF_AW2

AW2

DC_TEST_AY2_AW2

DAISY_CHAIN_NCTF_AW3

AW3

DC_TEST_AY3_AW3

DAISY_CHAIN_NCTF_AW61

AW61

DC_TEST_AY61_AW61

DAISY_CHAIN_NCTF_AW63

AW63

DAISY_CHAIN_NCTF_AW62

AW62

DC_TEST_AY62_AW62

C1

DAISY_CHAIN_NCTF_C1

B62

DAISY_CHAIN_NCTF_B62

B3

DAISY_CHAIN_NCTF_B3

AY3

DAISY_CHAIN_NCTF_AY3

DC_TEST_AY62_AW 62

AY62

DAISY_CHAIN_NCTF_AY62

B61

DAISY_CHAIN_NCTF_B61

B63

DAISY_CHAIN_NCTF_B63

C2

DAISY_CHAIN_NCTF_C2

BDW_ULT_DDR3L

14 OF19

U31N

AH44

VSS

AH49

VSS

AH51

VSS

AH38

VSS

VSS

AP10

VSS

AN49

VSS

AN40

VSS

AN23

VSS

AM1

VSS

AL51

A11

A14

VSS

A18

VSS

A28

VSS

A24

VSS

A32

VSS

A36

VSS

A40

VSS

A44

VSS

A48

VSS

A52

VSS

A56

VSS

AA1

VSS

AA58

VSS

AB10

VSS

AB20

VSS

AB22

VSS

AB7

VSS

AC61

VSS

AD21

VSS

AD3

VSS

AD63

VSS

AE10

VSS

AE5

VSS

AE58

VSS

AF11

VSS

AF12

VSS

VSS

AF14

VSS

AF17

VSS

AG1

VSS

AG11

VSS

AG23

VSS

AG60

VSS

AG62

VSS

AG63

VSS

AH19

VSS

AH24

VSS

AH28

VSS

AH30

VSS

AH32

VSS

AH40

VSS

AH42

VSS

AH53

VSS

AH55

VSS

AH57

VSS

AJ13

VSS

AJ14

VSS

AJ23

VSS

AJ25

VSS

AJ27

VSS

AJ29

VSS

VSS

AJ45

VSS

AJ52

VSS

AJ58

VSS

AJ60

VSS

AJ63

VSS

AK23

VSS

AK3

VSS

AK52

VSS

AL10

VSS

AL13

VSS

AL17

VSS

AL20

VSS

AL22

VSS

AL23

VSS

AL26

VSS

AL29

VSS

AL31

VSS

AL33

VSS

AL36

VSS

VSS

AL39

VSS

AL40

VSS

AL45

VSS

AL46

VSS

AL52

VSS

AL54

VSS

AL57

VSS

AL60

VSS

AL61

VSS

AM17

VSS

AM23

VSS

AM31

VSS

AM52

VSS

AN17

VSS

AN31

VSS

AN32

VSS

AN35

VSS

AN36

VSS

AN39

VSS

AN42

VSS

AN43

VSS

AN45

VSS

AN46

VSS

AN48

VSS

AN51

VSS

AN52

VSS

AN60

VSS

AN63

VSS