Page 1

1

2

3

4

5

6

7

8

http://hobi-elektronika.net

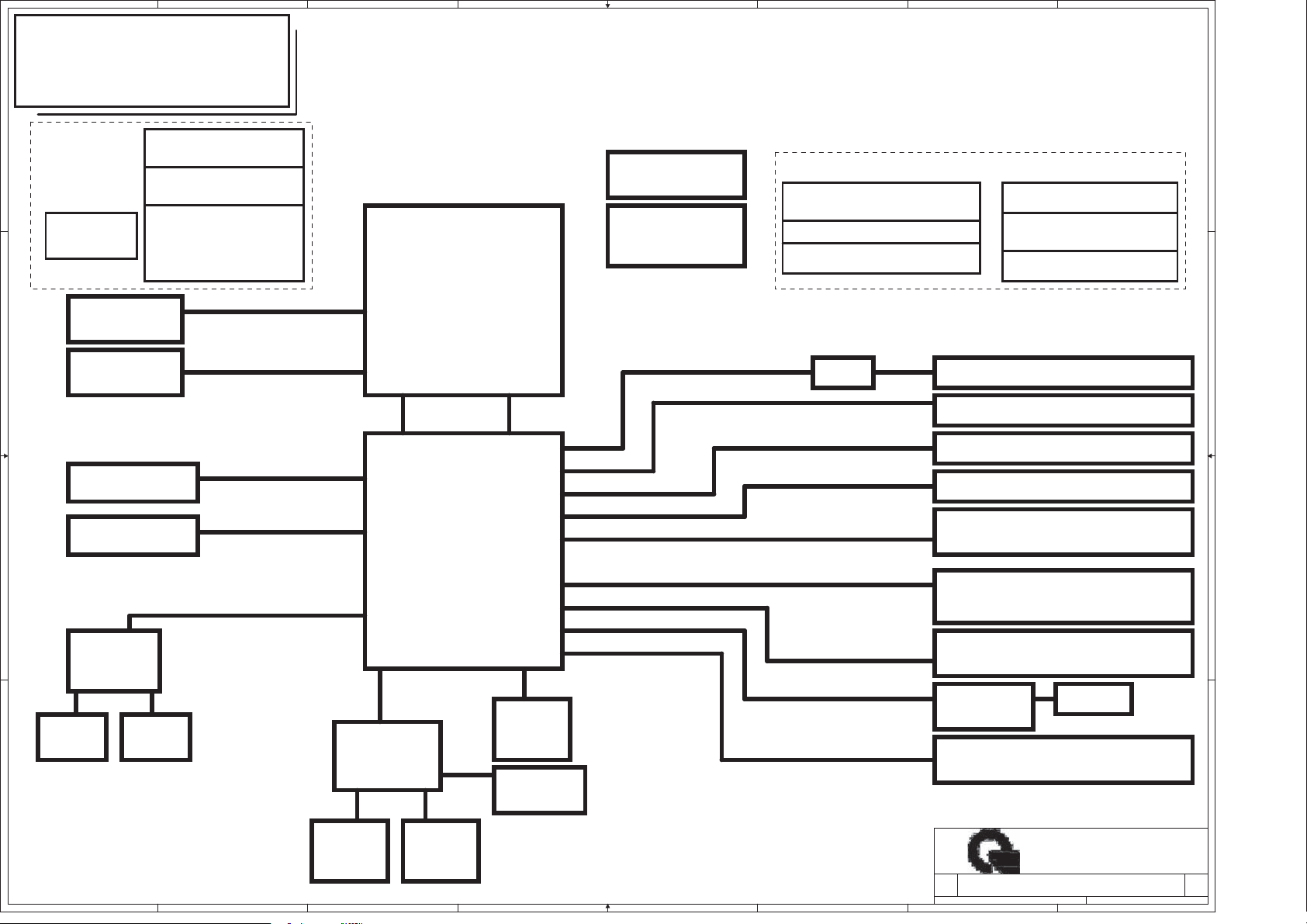

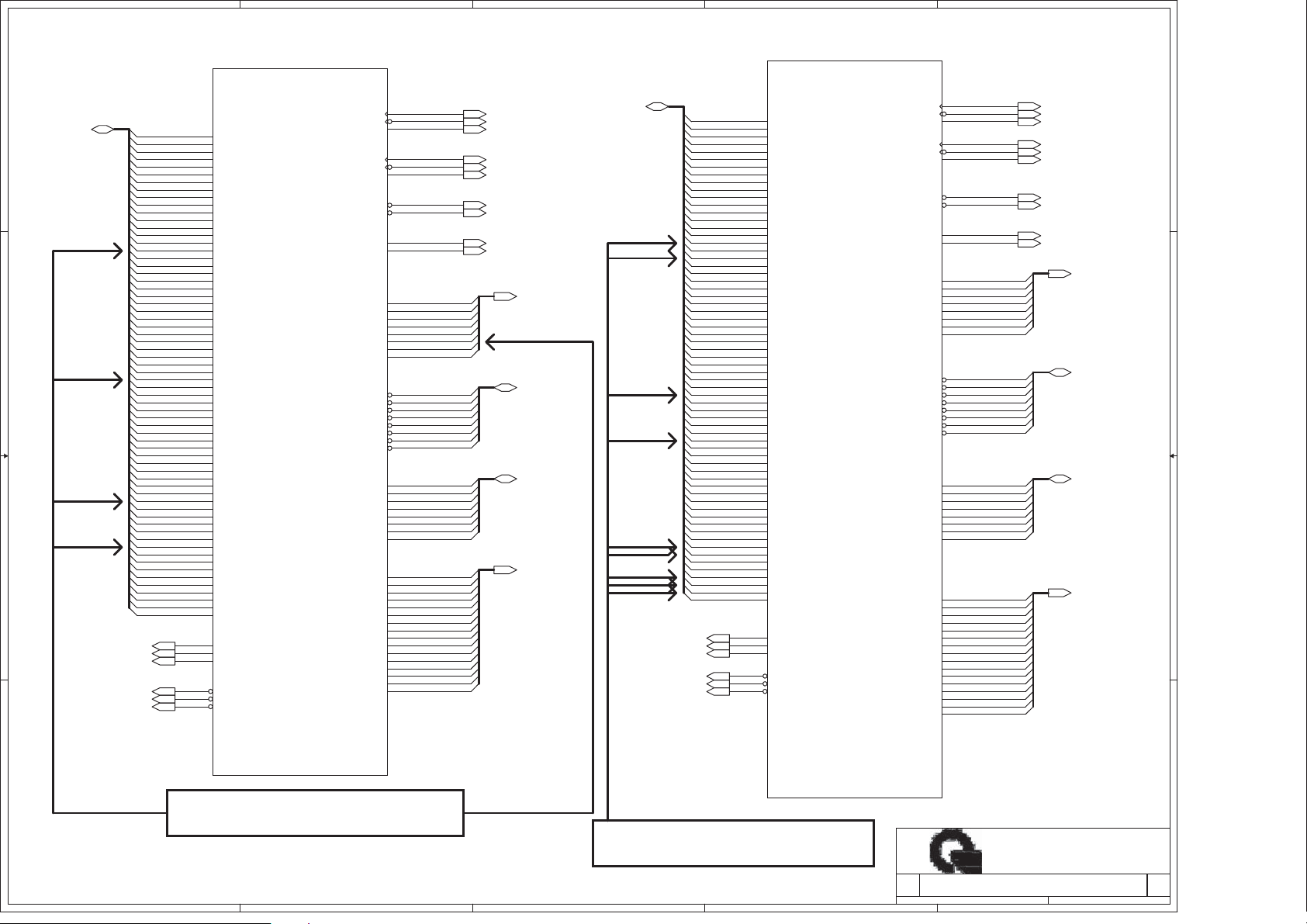

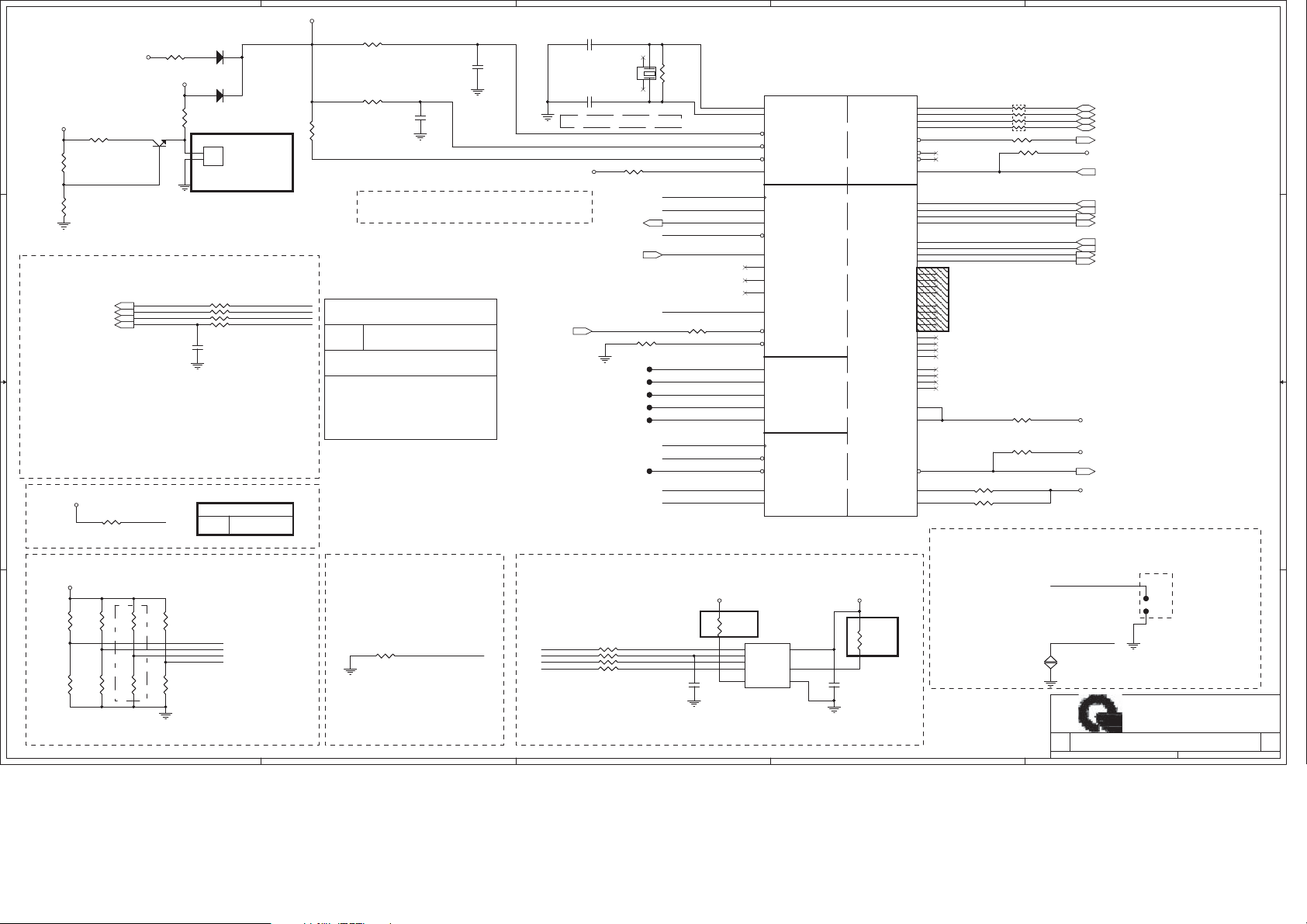

Intel Calpella

01

Intel Calpella Arrandale UMA

BlOCK DIAGRAM

A A

SYSTEM

POWER

CONNECTOR

RESET CIRCUIT

BATT

CHARGER

RUN POWER SW

+3V_S5/+5V_S5

+3V_SUS/+5V_SUS

+5V_RUN/+3V_RUN/+1.8V_RUN

CPU

Arrandale 35W

FAN & THERMAL

CLOCK

SLG8SP585VTR

(QFN-32)

POWER

+1.5V_SUS/+0.75V_DDR_VTT

+1.05V_PCH

+1.05V_VTT

CPU VRREGULATOR

DC/DCAC/BATT

+3VPCU/+5VPCU/

DDR3-SODIMM1

CHA

B B

Dual Channel DDR3

1066 1.5V

DDR3-SODIMM2

CHB

37.5mm X 37.5mm

( rPGA 989 )

PS8101

HDMI

Panel Connector

DMI X 4FDI

HDMI

SATA-ODD

SATA-HDD

C C

SATA

SATA

PCH

82801IBM

(HM55)

27mm X 25mm

LVDS

VGA

USB2.0 x 3

PCIEx1

CRT CONN.

USB conn x 3

Card Reader SD MS CARD

RTS5159

GLAN 10/100/1000 LAN

IHDA

PCIEx1

Realtek RTL8111E-GR

PCIEx1

AUDIO/AMP

ALC269

PCIEx1

MINI-CARD

WLAN

SPI

LPC

Audio

SPK conn

D D

Audio

Jacks

EC

ITE8502

SPI PS/2

18X8

FLASH

2Mbyts

Keyboard

NEW CARD

MINI-CARD

3G

W83L351YG

FLASH

2Mbyts

1

2

3

Touchpad

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Monday, December 21, 2009

Monday, December 21, 2009

Monday, December 21, 2009

Date: Sheet

Date: Sheet of

4

5

6

Date: Sheet of

7

PROJECT :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

FH2

FH2

FH2

of

138

138

138

8

1A

1A

1A

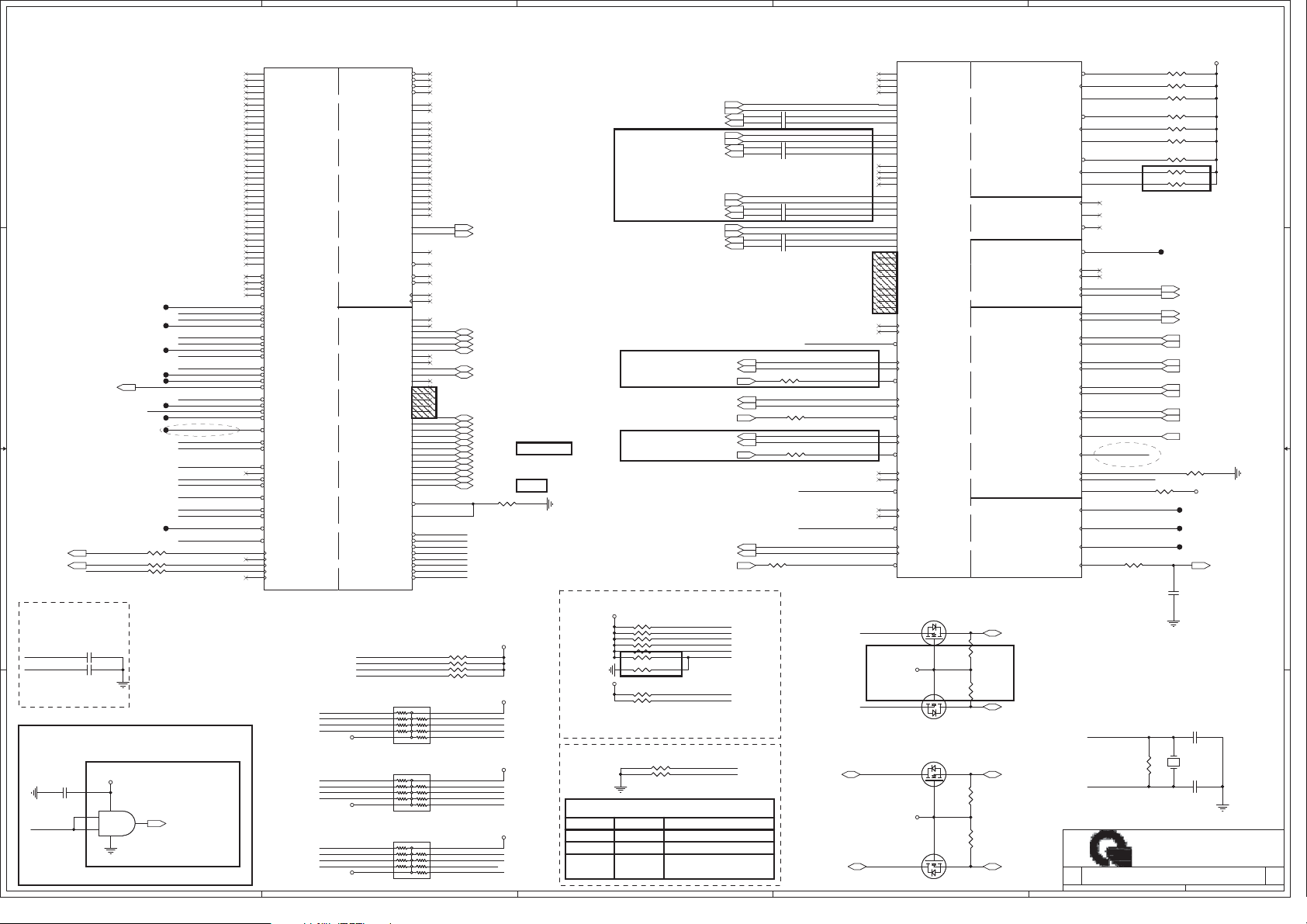

Page 2

1

Table of Contents

PAGE DESCRIPTION

Schematic Block Diagram

01

02

Front Page

Clock Generator

03

04-07

Arrandale

08-13

A A

B B

Ibex Peak-M

DDRIII SO-DIMM(204P)

14-15

16

LCD/CCD CONN

17

CRT CONN

Card Reader (RTS5159)

18

19

LAN RTL8111E-GR/RJ45

HDD/ODD/HOLE

20

USB/BLUE TOOTH

21

MINI-Card (WLAN/3G)/ XDP

22

KB/TOUCH PAD/LED

23

CODEC (ALC269)

24

EC_ ITE8502

25

FAN/SW/NEWCARD

26

+5V/+3V (RT8206B)

27

+1.05V/ +1.8V (RT8204C)

28

CPU Core ( ADP3212)

29

30

+1.05V_VTT (VT358)

UMA GPU CORE (RT8152C)

31

DDR3 (RT8207)

32

DISCHARGE/3VS5/5VS5/LAN

33

34

CHARGER (ISL88731)

35

Clock Distribution

36

Power Tree

37

SMBUS Address

2

3

4

5

6

7

8

http://hobi-elektronika.net

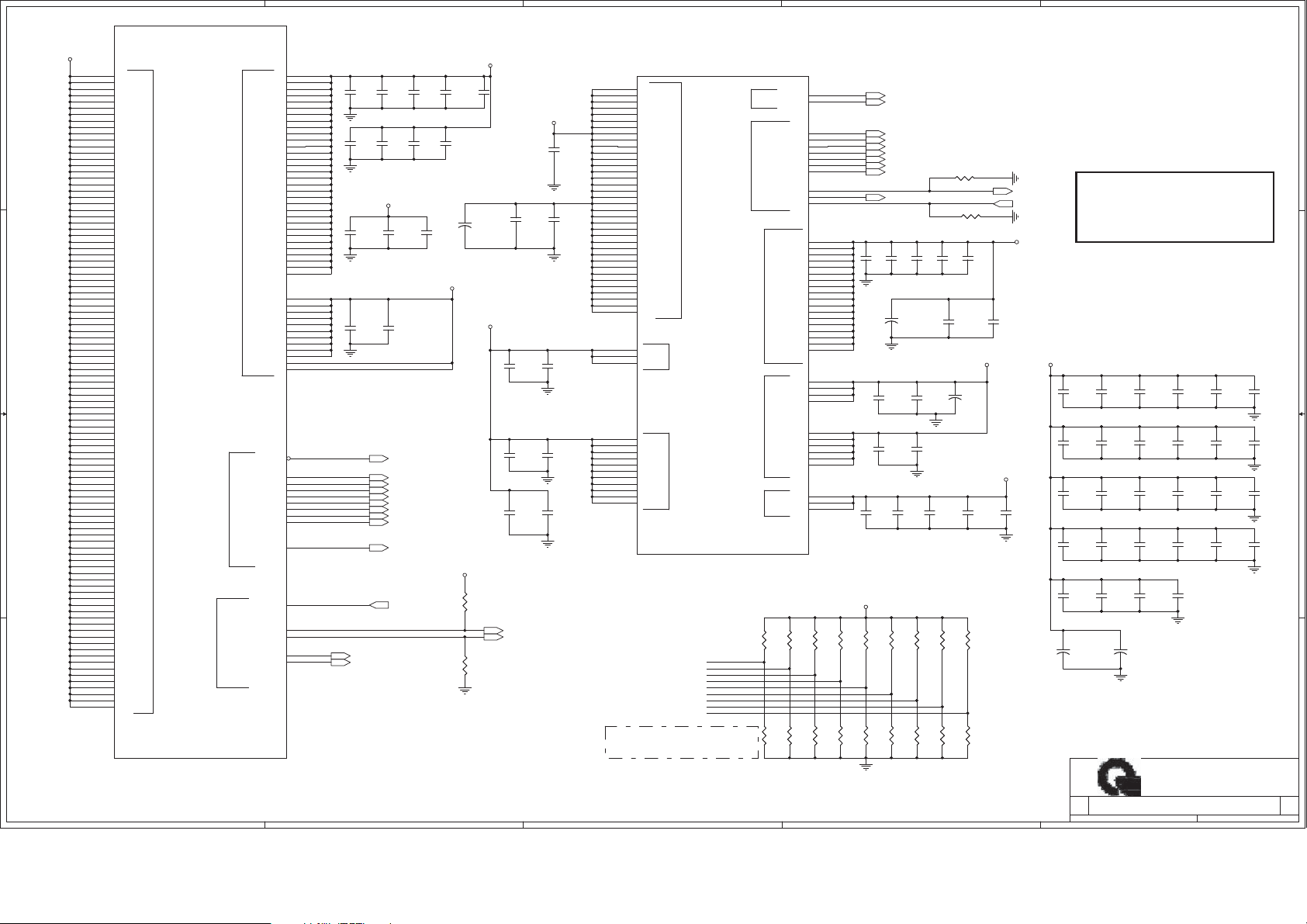

02

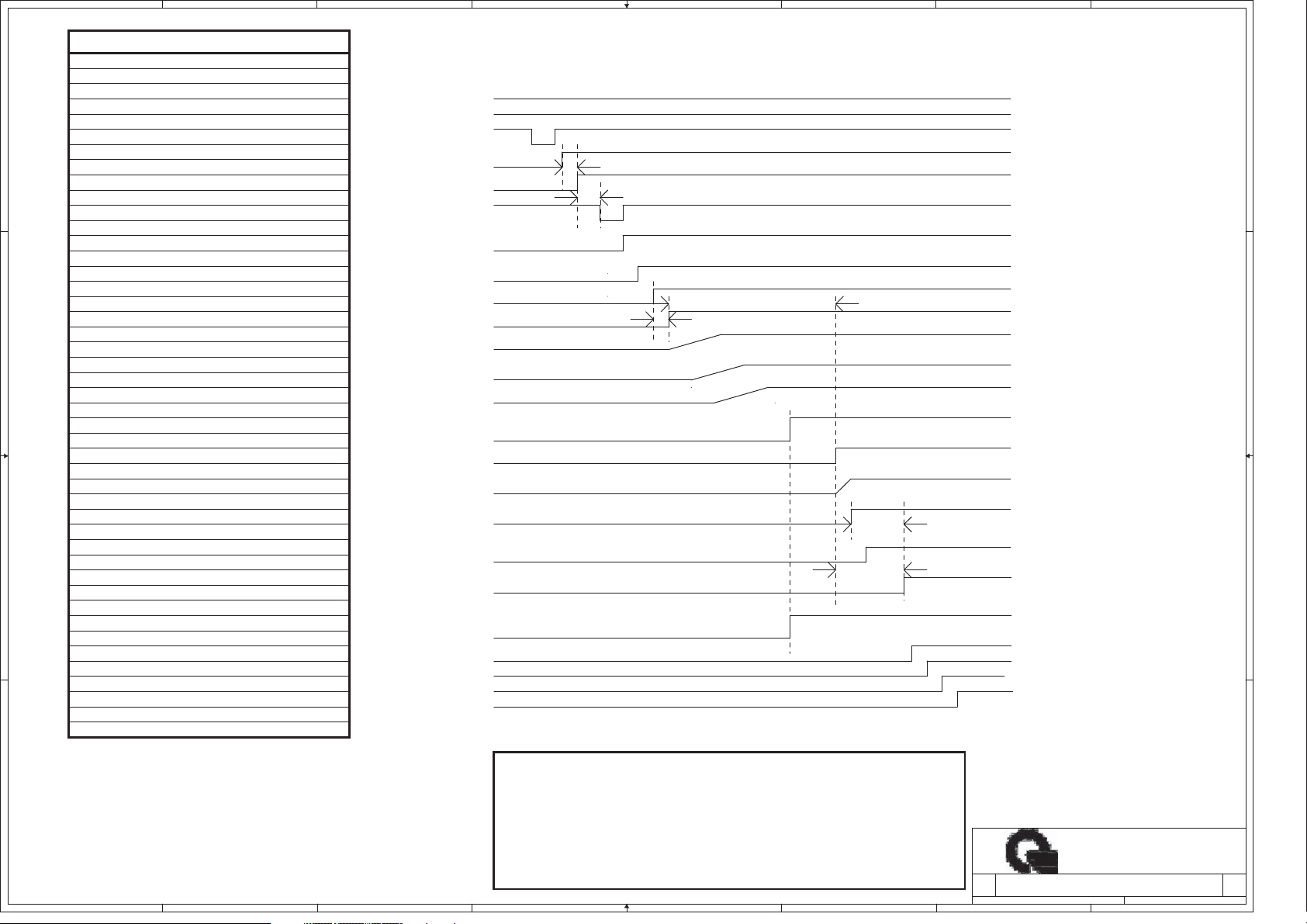

ACIN

+3VPCU/+5VPCU

NBSWON#

RVCC_ON

ICH_RSMRST#

DNBSWON#

SUSB#,SUSC#,SUSD#

SUSON

MAINON

MAINON2

+1.5VSUS/+3VSUS/+5VSUS

+1.5V_RUN/+1.8V_RUN

/+3V_RUN/+5V_RUN

+1.05V_PCH/+1.05V_VTT

/+0.75V_DDR_VTT

HWPG

VRON

+VCC_CORE

Power Sequence

T1

T2

T3

T5

VR_PWRGD_CLKEN#

C C

IMVP_PWRGD

MPWROK

H_VTTPWRGD

DRAMPWROK

VCCPPWRGOOD

PLTRST#

CPU_RST#

3ms~20ms

T4

T1: RVCCON TO RSMRST# = 30ms (spec:mini 10ms)

D D

T2: RSMRST# TO-DNBSWON = 110ms (spec:mini 100ms)

T3: MAINON2 TO VRON = 110ms (spec:mini 99ms)

T4: VRON TO MPWROK = 10ms (HWPG NEED TO BE HIGH at that time)

Note: IMVP_CLK_EN# (inverted) assertion to SYS_PWROK/PCH_PWROK assertion.

Quanta Computer Inc.

Quanta Computer Inc.

SPEC:3ms~20ms

T5: MAINON to MAINON2 =500us

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Monday, December 21, 2009

Monday, December 21, 2009

Monday, December 21, 2009

Date: Sheet

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

7

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Frontpage

Frontpage

Frontpage

FH2

FH2

FH2

238

238

238

8

1A

1A

1A

of

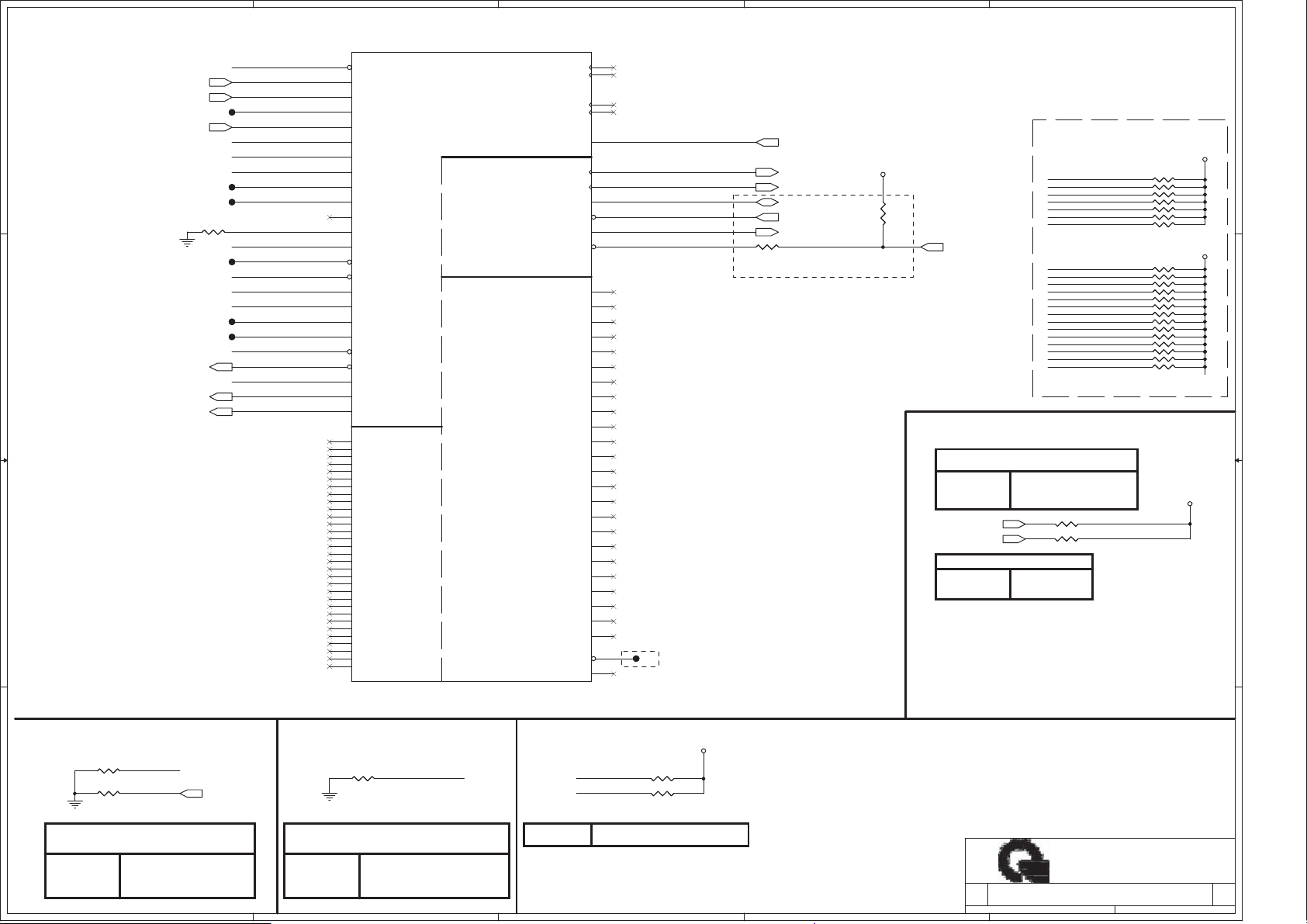

Page 3

5

4

3

2

1

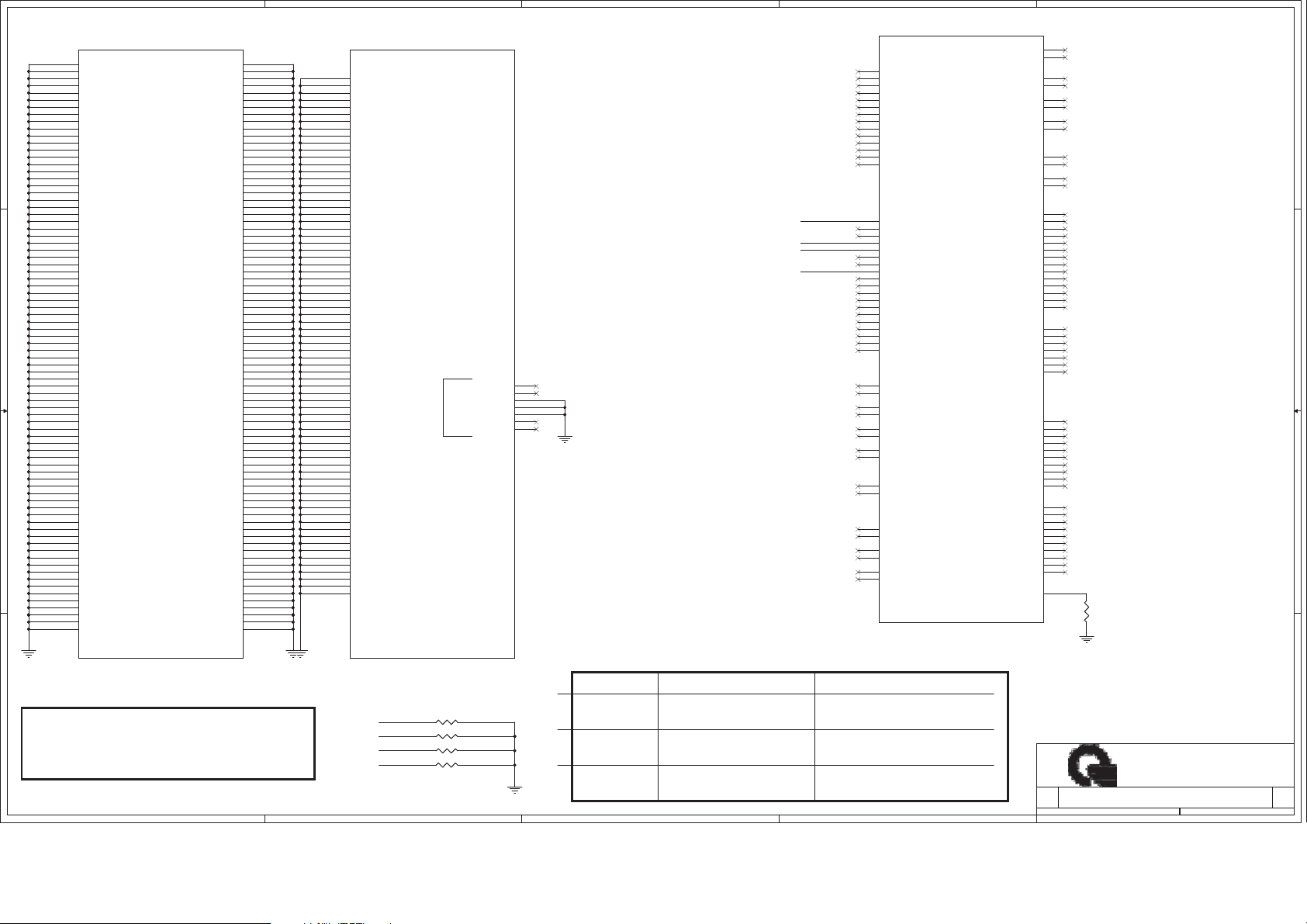

http://hobi-elektronika.net

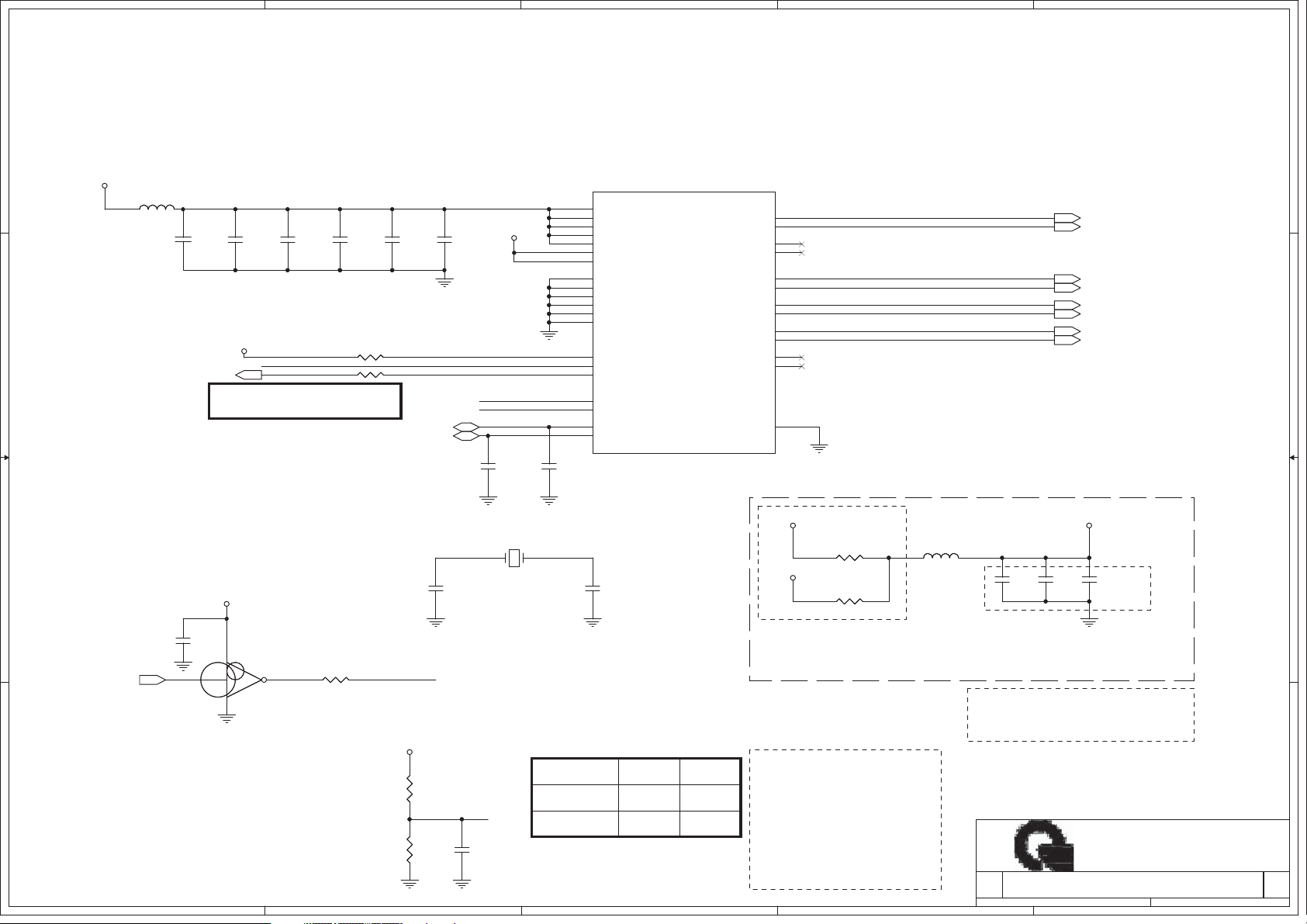

03

D D

+3V_RUN

L11 BLM21PG600SN1DL11 BLM21PG600SN1D

C148

C185

C185

10U/10V_8

10U/10V_8

C C

CLK_PCH_14M10

C149

C149

0.1U/16V_4

0.1U/16V_4

0.1uF near the every power pin.

+3V_RUN

Place the 33 ohm

resistors close to the CK 505

C148

0.1U/16V_4

0.1U/16V_4

CK_PWRGD_R

CLK_PCH_14M

40mil

C179

C179

0.1U/16V_4

0.1U/16V_4

R139 10K/J_4R139 10K/J_4

R125 33/J_4R125 33/J_4

CGDAT_SMB10,14,15

CGCLK_SMB10,14,15

C181

C181

0.1U/16V_4

0.1U/16V_4

C165

C165

0.1U/16V_4

0.1U/16V_4

+3.3V_CLK_VDD

+VDDIO_CLK

CPU_SEL

XTAL_OUT

XTAL_IN

C145

C145

*33P/50V_4

*33P/50V_4

1

5

17

24

29

15

18

9

2

8

12

21

26

16

25

30

27

28

31

32

C146

C146

*33P/50V_4

*33P/50V_4

SLG8SP585VTR

SLG8SP585VTR

VDD_USB

VDD_LCD

VDD_SRC

VDD_CPU

VDD_REF

VDD_SRC_IO

VDD_CPU_IO

VSS_SATA

VSS_USB

VSS_LCD

VSS_SRC

VSS_CPU

VSS_REF

CPU_STOP#

CK_PWRGD/PD#_3.3

REF_0/CPU_SEL

XOUT

XIN

SDATA

SCLK

CK505

CK505

QFN32

QFN32

CPU-0

CPU-0#

CPU-1

CPU-1#

DOT96T_LPR

DOT96C_LPR

SRC-2

SRC-2#

SRC-1/SATA

SRC-1#/SATA#

27MHz_nonSS

27MHz_SS

GND

CLK_BUF_BCLK_P

23

CLK_BUF_BCLK_N

22

20

19

CLK_BUF_DREFCLKP

3

CLK_BUF_DREFCLKN

4

CLK_BUF_PCIE_3GPLLP

13

CLK_BUF_PCIE_3GPLLN

14

CLK_BUF_DREFSSCLKP

10

CLK_BUF_DREFSSCLKN

11

6

7

33

U6

U6

CLK_BUF_BCLK_P 10

CLK_BUF_BCLK_N 10

CLK_BUF_DREFCLKP 10

CLK_BUF_DREFCLKN 10

CLK_BUF_PCIE_3GPLLP 10

CLK_BUF_PCIE_3GPLLN 10

CLK_BUF_DREFSSCLKP 10

CLK_BUF_DREFSSCLKN 10

Realtek: 0.1uFx3pcs, 22uFx1pcs

IDT: 0.1uFx2pcs, 10uFx1pcs

+3V_RUN

L12 BLM21PG600SN1D

Y1

XTAL_IN XTAL_OUT

B B

C166

+3V_S5

C166

33P/50V_4

33P/50V_4

Y1

21

14.318MHZ

14.318MHZ

C173

C173

33P/50V_4

33P/50V_4

1 2

R142 *0/J_8R142 *0/J_8

+1.05V_PCH

R144 0/J_8R144 0/J_8

L12 BLM21PG600SN1D

805

805

C186

C186

10U/10V_8

10U/10V_8

+VDDIO_CLK

40mil

C167

C167

0.1U/16V_4

0.1U/16V_4

C180

C180

0.1U/16V_4

0.1U/16V_4

HP: 10u x2pcs

C182

C182

0.1U/16V_4

0.1U/16V_4

5

R140 0/J_4R140 0/J_4

VR_PWRGD_CLKEN#29

TC7SZ04FU(T5L,F,T)

TC7SZ04FU(T5L,F,T)

A A

5

2

U8

U8

4

3

CK_PWRGD_R

+3V_RUN

1 2

CPU_SEL

1 2

4

R126

R126

*4.7K/J_4

*4.7K/J_4

R127

R127

4.7K/J_4

4.7K/J_4

C152

C152

*10P/50V_4

*10P/50V_4

EMI Capacitor

PIN 30 CPU_0 CPU_1

0(default)

1(0.7V-1.5V)

133MHz

100MHz 100MHz

3

133MHz

CPU_SEL:

SLG date sheet (V0.2) P15:

High Voltage: Min 0.7V, Max 1.5V.

Low Voltage: Min Vss-0.3V, Max 0.35V.

Realtek date sheet(V1.2) P11:

High Voltage: Min 0.7V, Max 1.5V.

Low Voltage: Min Vss-0.3V, Max 0.35V.

IDT date sheet(V0.7) P10:

High Voltage: Min 0.7V, Max 1.5V.

Low Voltage: Min Vss-0.3V, Max 0.35V.

SLG,IDT: +1.05V

Realtek: +3.3V

2

Place each 0.1uF cap as close as

possible to each VDD IO pin. Place

the 10uF caps on the VDD_IO plane.

+VDDIO_CLK:

SLG date sheet (V0.2) P15: Min 1.05V,Max3.465V.

Realtek date sheet(V1.2) P11: Min 1.05V,Max 3.3V.

IDT date sheet(V0.7) P10: Min 0.9975V,Max 3.465V.

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Monday, December 21, 2009

Monday, December 21, 2009

Monday, December 21, 2009

Date: Sheet of

Date: Sheet of

Date: Sheet

PROJECT :

Clock Generator

Clock Generator

Clock Generator

FH2

FH2

FH2

of

338

338

338

1

1A

1A

1A

Page 4

5

4

3

2

1

http://hobi-elektronika.net

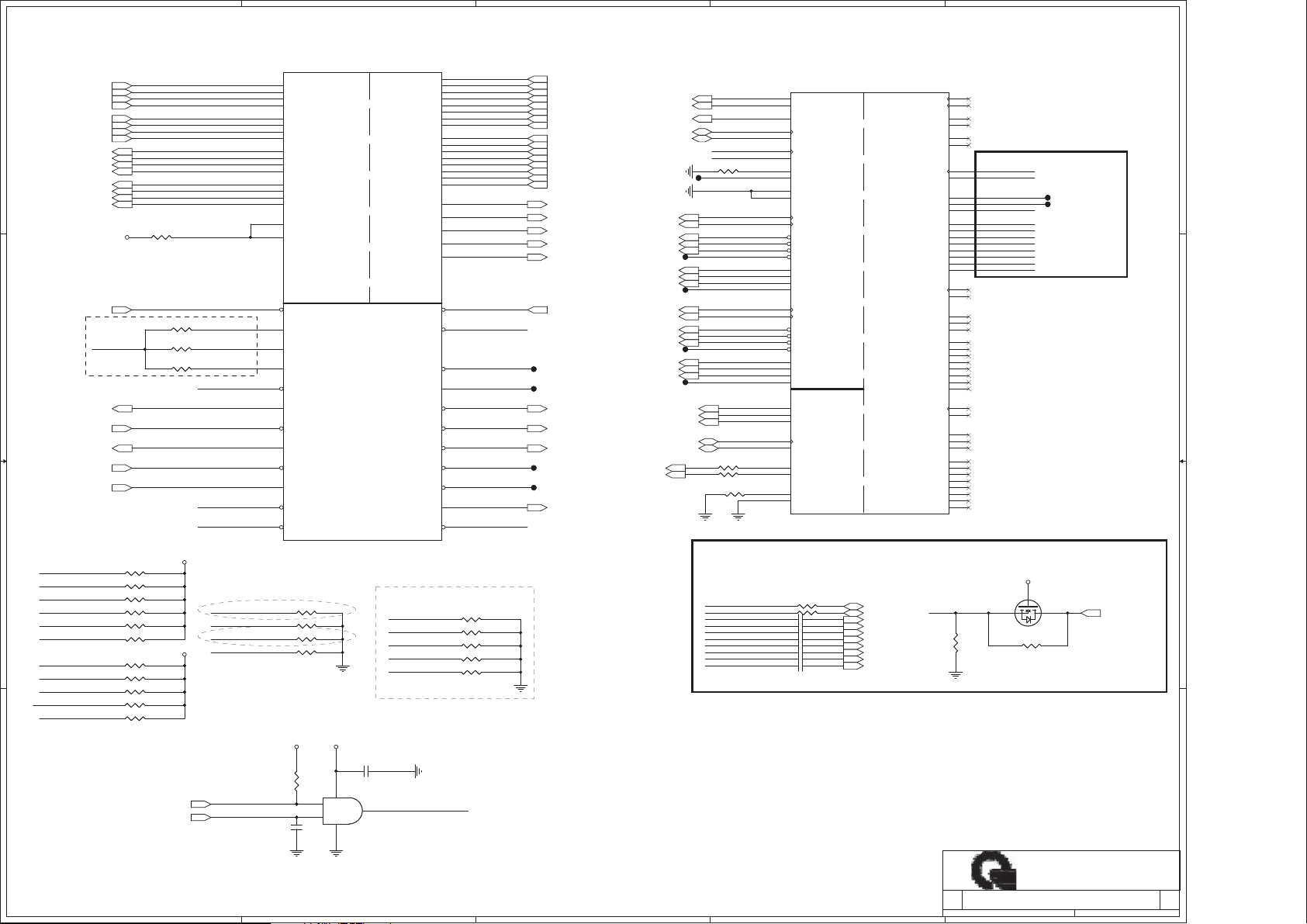

U19A

U19A

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

Clarksfield/Auburndale

Clarksfield/Auburndale

DMI_TXN08

D D

C C

B B

DMI_TXN18

DMI_TXN28

DMI_TXN38

DMI_TXP08

DMI_TXP18

DMI_TXP28

DMI_TXP38

DMI_RXN08

DMI_RXN18

DMI_RXN28

DMI_RXN38

DMI_RXP08

DMI_RXP18

DMI_RXP28

DMI_RXP38

FDI_TXN[7:0]8

FDI_TXP[7:0]8

FDI_FSYNC08

FDI_FSYNC18

FDI_INT8

FDI_LSYNC08

FDI_LSYNC18

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

Processor Pullups Processor Compensation Signals

+1.05V_VTT

R75

R75

49.9/F_4

49.9/F_4

H_CATERR#

H_PROCHOT#_D

A A

H_CPURST#

5

R58

R58

68/F_4

68/F_4

R64

R64

*68/J_4

*68/J_4

R48

R48

49.9/F_4

49.9/F_4

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

R65

R65

49.9/F_4

49.9/F_4

PEG_ICOMPI

R52

R52

20/F_4

20/F_4

R251 49.9/F_4R251 49.9/F_4

R254 750/F_4R254 750/F_4

H_COMP0

H_COMP1

H_COMP2

H_COMP3

R54

R54

20/F_4

20/F_4

4

HWPG

R271 0/J_4R271 0/J_4

H_PROCHOT#_D

H_THERM

H_CPURST#

PM_DRAM_PWRGD

H_VTTPWRGD

R101 1.5K/F_4R101 1.5K/F_4

R280

R280

2K/F_4

2K/F_4

H_PECI11

H_PROCHOT#_D29

H_THERM11

H_CPURST#22

PM_SYNC8

H_PWRGOOD11,22

PM_DRAM_PWRGD8

H_PWRGD_XDP22

PLTRST#10,18,19,22,26

HWPG25,27

DDR3 Compensation Signals

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

R114

R114

R113

R113

R112

T14T14

T7T7

R112

130/F_4

130/F_4

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TCLK

24.9/F_4

24.9/F_4

100/F_4

100/F_4

R59 *51/J_4R59 *51/J_4

R253 *51/J_4R253 *51/J_4

R61 *51/J_4R61 *51/J_4

R39 *51/J_4R39 *51/J_4

3

T13T13

R105 0/J_4R105 0/J_4

H_VTTPWRGD

+1.05V_VTT

R282

R282

1K/F_4

1K/F_4

R102

R102

750/F_4

750/F_4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP_SKT0CC#

H_CATERR#

H_PECI_ISO

+3V_RUN

U19B

U19B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

Clarksfield/Auburndale

Clarksfield/Auburndale

CPU THERMTRIP

IMVP_PWRGD8,29

H_THERM H_THERM_R

R76 33/J_4R76 33/J_4

PM_THRMTRIP# STUP AS SHORT AS PASSPBLE

CPU THERM SENSOR

R360

R360

*0_4

*0_4

C369

C369

*0.1U/10V_4

*0.1U/10V_4

R362

R362

*0_4

*0_4

MISC THERMAL

MISC THERMAL

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLOCKS

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

+1.05V_VTT

3

Q2

2

2N7002EQ22N7002E

1

R72 100K/J_4R72 100K/J_4 R329 *0/J_4R329 *0/J_4

R77

R77

1K/J_4

1K/J_4

2

Q1

1 3

MMBT3904Q1MMBT3904

U24

U24

VDD

CTRL

GND

*BDE0900G

*BDE0900G

Vtemp

5

OS

3

2

SYS_SHDN_1# SYS_SHDN#

R361 *0/J_4R361 *0/J_4

4

1

2

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

SYS_SHDN# 27

(6

A16

B16

AR30

AT30

E16

D16

A18

A17

DDR3_DRAMRST#_C

F6

SM_RCOMP_0

AL1

SM_RCOMP_1

AM1

SM_RCOMP_2

AN1

AN15

AP15

AT28

XDP_PREQ#

AP27

XDP_TCLK

AN28

XDP_TMS

AP28

XDP_TRST#

AT27

XDP_TDI_R

AT29

XDP_TDO_R

AR27

XDP_TDI_M

AR29

XDP_TDO_M

AP29

H_DBR#_R

AN25

XDP_OBS0_R

AJ22

XDP_OBS1_R

AK22

XDP_OBS2_R

AK24

XDP_OBS3_R

AJ24

XDP_OBS4_R

AJ25

XDP_OBS5_R

AH22

XDP_OBS6_R

AK23

XDP_OBS7_R

AH23

for S3 power reduction

R91 10K/J_4R91 10K/J_4

R86 10K/J_4R86 10K/J_4

T41T41

T38T38

T39T39

R43 0/J_4R43 0/J_4

R28 0/J_4R28 0/J_4

R37 0/J_4R37 0/J_4

R32 0/J_4R32 0/J_4

R29 0/J_4R29 0/J_4

R36 0/J_4R36 0/J_4

R30 0/J_4R30 0/J_4

R33 0/J_4R33 0/J_4

R31 0/J_4R31 0/J_4

XDP_TDI_R

XDP_TDO_M

XDP_TDI_M

XDP_TDO_R

R330 *0/J_4R330 *0/J_4

DDR3_DRAMRST#_C

R331

R331

100K/J_4

100K/J_4

+1.5V_RUN

R294

R294

*1.1K/F_4

*1.1K/F_4

R293

R293

750/F_4

750/F_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

Monday, December 21, 2009

Monday, December 21, 2009

Monday, December 21, 2009

CLK_CPU_BCLKP 11

CLK_CPU_BCLKN 11

CLK_BCLK_ITPP 22

CLK_BCLK_ITPN 22

CLK_PCIE_3GPLLP 10

CLK_PCIE_3GPLLN 10

CLK_DREFSSCLKP 10

CLK_DREFSSCLKN 10

12

12

R103 0/J_4R103 0/J_4

R83 0/J_4R83 0/J_4

XDP_PRDY# 22

XDP_PREQ# 22

XDP_TCLK 22

XDP_TMS 22

XDP_TRST# 22

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

R249 0/J_4R249 0/J_4

R41 *0/J_4R41 *0/J_4

R44

R44

0/J_4

0/J_4

R250 *0/J_4R250 *0/J_4

R257 0/J_4R257 0/J_4

For S3 power reduc t ion

2N7002W-7-F

2N7002W-7-F

Q16

Q16

PM_DRAM_PWRGD

R80

R80

*12.4K/F_4

*12.4K/F_4

+1.5V_SUS

31

2

R325 0/J_4R325 0/J_4

12

$

C370

C370

0.047u_4

0.047u_4

R288 1.5K/F_4R288 1.5K/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ARRANDALE 1/4

ARRANDALE 1/4

ARRANDALE 1/4

1

R332

R332

1K/F_4

1K/F_4

04

+1.05V_VTT

PM_EXTTS#0 14

PM_EXTTS#1 15

XDP_DBRESET# 8,22

XDP_OBS[0:7] 22

XDP_TDI 22

XDP_TDO 22

XDP_TRST#

R259

R259

51/J_4

51/J_4

DDR3_DRAMRST# 14,15

DDR3_CORL_EC 25

DDR3_CORL_PCH 11

HWPG

FH2

FH2

FH2

438

438

438

1A

1A

1A

of

Page 5

5

U19C

U19C

4

ARRANDALE PROCESSOR (DDR3)

http://hobi-elektronika.net

3

U19D

U19D

2

1

05

AA6

SA_CK[0]

D D

M_A_DQ[63:0]14

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS014

M_A_BS114

M_A_BS214

M_A_CAS#14

M_A_RAS#14

M_A_WE#14

A10

C10

B10

D10

E10

F10

H10

G10

J10

AH5

AF5

AK6

AK7

AF6

AG5

AJ7

AJ6

AJ10

AJ9

AL10

AK12

AK8

AL7

AK11

AL8

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

G8

K7

J8

G7

J7

L7

M6

M8

L9

L6

K8

N8

P9

U7

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLKP0 14

M_A_CLKN0 14

M_A_CKE0 14

M_A_CLKP1 14

M_A_CLKN1 14

M_A_CKE1 14

M_A_CS0# 14

M_A_CS1# 14

M_A_ODT0 14

M_A_ODT1 14

M_A_DM[7:0] 14

M_A_DQSN[7:0] 14

M_A_DQSP[7:0] 14

M_A_A[15:0] 14

M_B_DQ[63:0]15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60M_A_A0

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS015

M_B_BS115

M_B_BS215

M_B_CAS#15

M_B_RAS#15

M_B_WE#15

AF3

AG1

AK1

AG4

AG3

AH4

AK3

AK4

AM6

AN2

AK5

AK2

AM4

AM3

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AR10

AT10

AB1

AC5

AC6

AJ3

AJ4

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

M1

K5

K4

M4

N5

W5

R7

Y7

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CLKP0 15

M_B_CLKN0 15

M_B_CKE0 15

M_B_CLKP1 15

M_B_CLKN1 15

M_B_CKE1 15

M_B_CS0# 15

M_B_CS1# 15

M_B_ODT0 15

M_B_ODT1 15

M_B_DM[7:0] 15

M_B_DQSN[7:0] 15

M_B_DQSP[7:0] 15

M_B_A[15:0] 15

Clarksfield/Auburndale

Clarksfield/Auburndale

A A

5

Channel A DQ[15,32,48,54], DM[5]

Requires minimum 12mils spacing

with all other signals, including data signals.

4

Channel B DQ[16,18,36,42,56,57,60,61,62]

Requires minimum 12mils spacing

with all other signals, including data signals.

3

Clarksfield/Auburndale

Clarksfield/Auburndale

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Monday, December 21, 2009

Monday, December 21, 2009

Monday, December 21, 2009

Date: Sheet

Date: Sheet of

Date: Sheet of

PROJECT :

ARRANDALE 2/4

ARRANDALE 2/4

ARRANDALE 2/4

FH2

FH2

FH2

of

538

538

538

1

1A

1A

1A

Page 6

5

U19F

CPU Core Power

U19F

+VCC_CORE=4.8 max

+VCC_CORE

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

D D

C C

B B

A A

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

Clarksfield/Auburndale

Clarksfield/Auburndale

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

AH14

VTT0_1

AH12

VTT0_2

AH11

VTT0_3

AH10

VTT0_4

J14

VTT0_5

J13

VTT0_6

H14

VTT0_7

H12

VTT0_8

G14

VTT0_9

G13

VTT0_10

G12

VTT0_11

G11

VTT0_12

F14

VTT0_13

F13

VTT0_14

F12

VTT0_15

F11

VTT0_16

E14

VTT0_17

E12

VTT0_18

D14

VTT0_19

D13

VTT0_20

D12

VTT0_21

D11

VTT0_22

C14

VTT0_23

C13

VTT0_24

C12

VTT0_25

C11

VTT0_26

B14

VTT0_27

B12

VTT0_28

A14

VTT0_29

A13

VTT0_30

A12

VTT0_31

A11

VTT0_32

AF10

VTT0_33

AE10

VTT0_34

AC10

VTT0_35

AB10

VTT0_36

Y10

VTT0_37

W10

VTT0_38

U10

VTT0_39

T10

VTT0_40

J12

VTT0_41

J11

VTT0_42

J16

VTT0_43

J15

VTT0_44

VTT0_43,VTT0_44:(Intel feedback)

They are connected to hidden page for

intel validation purpose.

H_PSI#

AN33

PSI#

VID0

AK35

VID[0]

VID1

AK33

VID[1]

VID2

AK34

VID[2]

VID3

AL35

VID[3]

VID4

AL33

VID[4]

VID5

AM33

VID[5]

VID6

AM35

VID[6]

DPRSLPVR

AM34

G15

VTT_SELECT

AN35

ISENSE

AJ34

VCC_SENSE

AJ35

VSS_SENSE

B15

VTT_SENSE

A15

VSS_SENSE_VTT:

SC(V1.0)P20

Connect VSS_SENSE_VTT to GND

or can be left floating.

Note: CRB has the VSS_SENSE_VTT floating.

AUBURNDALE/CLARKSFIELD PROCESSOR (POWER)

5

4

+1.05V_VTT=1.8 max

C103

C103

C318

C318

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

C105

C105

C102

C102

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

+1.05V_VTT

C329

C329

C313

C313

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C308

C308

C96

C96

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

H_PSI# 29

VID0 29

VID1 29

VID2 29

VID3 29

VID4 29

VID5 29

VID6 29

DPRSLPVR 29

H_VTTVID1 30

I_MON 29

VTT_SENSE 30

VSS_SENSE_VTT 30

4

http://hobi-elektronika.net

+1.05V_VTT

C311

C311

C309

C107

C107

10U/6.3V_8

10U/6.3V_8

C326

C326

10U/6.3V_8

10U/6.3V_8

C304

C304

22U/6.3V_8

22U/6.3V_8

+1.05V_VTT

C309

*10U/6.3V_8

*10U/6.3V_8

*10U/6.3V_8

*10U/6.3V_8

+VCC_GFX_CORE

C99

C99

10U/6.3V_8

10U/6.3V_8

+

+

C88

C88

330U/2.5V_7343

330U/2.5V_7343

+VCC_CORE

R216

R216

100/F_4

100/F_4

R217

R217

100/F_4

100/F_4

PROC_DPRSLPVR:

SC(V1.0)P19:

It is important to have the resistor stuffing options

in the design for the Turbo functionality.

The stuffing and no-stuffing of the resistors

will depend on the POC configuration of AUB

and CFD

CRB(V1.0)P67:

uses 1K pull-up and pull-down resistors

CRB default setting is "1"

C98

C98

22U/6.3V_8

22U/6.3V_8

+1.05V_VTT

C319

C319

22U/6.3V_8

22U/6.3V_8

C317

C317

22U/6.3V_8

22U/6.3V_8

C331

C331

22U/6.3V_8

22U/6.3V_8

VCC_SENSE & VSS_SENSE:

SC(V1.0)P19

100- ±1% pull-down to GND near processor

VCCSENSE 29

VSSSENSE 29

C97

C97

10U/6.3V_8

10U/6.3V_8

C63

C63

22U/6.3V_8

22U/6.3V_8

C101

C101

22U/6.3V_8

22U/6.3V_8

C316

C316

22U/6.3V_8

22U/6.3V_8

C315

C315

22U/6.3V_8

22U/6.3V_8

3

ARRANDALE PROCESSOR (GRAPHICS POWER)

U19G

U19G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

Clarksfield/Auburndale

Clarksfield/Auburndale

Note:

For Validating IMVP VR R814 should be STUFF

and R827 NO_STUFF

3

GRAPHICS

GRAPHICS

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

VID0

VID1

VID2

VID3

VID4

VID5

VID6

DPRSLPVR

H_PSI#

SENSE

SENSE

VSSAXG_SENSE

LINES

LINES

GFX_DPRSLPVR

GRAPHICS VIDs

GRAPHICS VIDs

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

VAXG_SENSE

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

R225

R225

1K/J_4

1K/J_4

R226

R226

*1K/J_4

*1K/J_4

R227

R227

1K/J_4

1K/J_4

R228

R228

*1K/J_4

*1K/J_4

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

R230

R230

1K/J_4

1K/J_4

R231

R231

*1K/J_4

*1K/J_4

+1.05V_VTT

R233

R233

*1K/J_4

*1K/J_4

R234

R234

1K/J_4

1K/J_4

VGA_ON

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C125

C125

10U/6.3V_8

10U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C42

C42

R236

R236

*1K/J_4

*1K/J_4

R237

R237

1K/J_4

1K/J_4

2

VGAU_VCCSENSE 31

VGAU_VSSSENSE 31

VGAU_VID0 31

VGAU_VID1 31

VGAU_VID2 31

VGAU_VID3 31

VGAU_VID4 31

VGAU_VID5 31

VGAU_VID6 31

VGAU_DPRSLPVR 31

C127

C127

C124

C124

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

+

+

C122

C122

330U/2.5V_7343

330U/2.5V_7343

7343

7343

2.5

2.5

C106

C106

C104

C104

10U/6.3V_8

10U/6.3V_8

C330

C330

C314

C314

22U/6.3V_8

22U/6.3V_8

C50

C50

1U/6.3V_4

1U/6.3V_4

R239

R239

R243

R243

1K/J_4

1K/J_4

*1K/J_4

*1K/J_4

R244

R244

R240

R240

1K/J_4

1K/J_4

*1K/J_4

*1K/J_4

2

R67 4.7K_4R67 4.7K_4

R256 *1K/F_4R256 *1K/F_4

C128

C128

1U/6.3V_4

1U/6.3V_4

C121

C121

22U/6.3V_8

22U/6.3V_8

+

+

C110

C110

*330U/2.5V_7343

*330U/2.5V_7343

C65

C65

2.2U/6.3V_6

2.2U/6.3V_6

R208

R208

1K/J_4

1K/J_4

R213

R213

*1K/J_4

*1K/J_4

C126

C126

1U/6.3V_4

1U/6.3V_4

+1.05V_VTT

C66

C66

4.7U/6.3V_6

4.7U/6.3V_6

R209

R209

*1K/J_4

*1K/J_4

R214

R214

1K/J_4

1K/J_4

C120

C120

22U/6.3V_8

22U/6.3V_8

+1.8V_RUN

22U/6.3V_8

22U/6.3V_8

VGA_ON 31

VGAU_IMON

+1.5V_RUN

C297

C297

1

For S3 power reduction

Check to ensure that 4 stitching caps per SODIMM

connector between SODIMM 1.5V and GND are placed as

close as possible to t h e connectors – caps should be

evenl y distri buted between the connectors

+VCC_CORE

C302

C302

C54

C54

C281

C281

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C276

C276

C38

C38

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C56

C56

C79

C79

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

C300

C300

C301

C301

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

C37

C37

C57

C57

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

+

+

+

C277

C277

*470U/6.3V_7343

*470U/6.3V_7343

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

+

C90

C90

*470U/6.3V_7343

*470U/6.3V_7343

ARRANDALE 3/4

ARRANDALE 3/4

ARRANDALE 3/4

Monday, December 21, 2009

Monday, December 21, 2009

Monday, December 21, 2009

C52

C52

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C59

C59

C58

C58

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C36

C36

C81

C81

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

C286

C286

C80

C80

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

C303

C303

C78

C78

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

06

C291

C291

C53

C53

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C280

C280

C285

C285

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C55

C55

C299

C299

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

C82

C82

C35

C35

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

FH2

FH2

FH2

of

638

638

638

1A

1A

1A

Page 7

5

ARRANDALE PROCESSOR (GND) ARRANDALE PROCESSOR( RESERVED, CFG)

U19H

U19H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

D D

C C

B B

AR20

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

K27

K9

K6

K3

J32

J30

J21

J19

H35

H32

H28

H26

H24

H22

H18

H15

H13

H11

H8

H5

H2

G34

G31

G20

G9

G6

G3

F30

F27

F25

F22

F19

F16

E35

E32

E29

E24

E21

E18

E13

E11

E8

E5

E2

D33

D30

D26

D9

D6

D3

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

B8

B6

B4

A29

A27

A23

A9

U19I

U19I

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

4

VSS

VSS

NCTF

NCTF

3

http://hobi-elektronika.net

AT35

VSS_NCTF1

AT1

VSS_NCTF2

AR34

VSS_NCTF3

B34

VSS_NCTF4

B2

VSS_NCTF5

B1

VSS_NCTF6

A35

VSS_NCTF7

VSS_NCTF pins can be connected to GND or left as NC (floating).

When tied to GND they should be routed as trace and

not as a GND plane.

CFG0

CFG3

CFG4

CFG7

U19E

U19E

AP25

RSVD1

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

J17

SA_DIMM_VREF

H17

SB_DIMM_VREF

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

AL32

CFG[3]

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]

AN30

CFG[12]

AN32

CFG[13]

AJ32

CFG[14]

AJ29

CFG[15]

AJ30

CFG[16]

AK30

CFG[17]

H16

RSVD_TP_86

B19

RSVD15

A19

RSVD16

A20

RSVD17

B20

RSVD18

U9

RSVD19

T9

RSVD20

AC9

RSVD21

AB9

RSVD22

C1

RSVD_NCTF_23

A3

RSVD_NCTF_24

J29

RSVD26

J28

RSVD27

A34

RSVD_NCTF_28

A33

RSVD_NCTF_29

C35

RSVD_NCTF_30

B35

RSVD_NCTF_31

Clarksfield/Auburndale

Clarksfield/Auburndale

2

AJ13

RSVD32

AJ12

RSVD33

AH25

RSVD34

AK26

RSVD35

AL26

RSVD36

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD58

KEY

RSVD62

RSVD63

RSVD64

RSVD65

VSS

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

R215

R215

0/J_4

0/J_4

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD_TP_59

RSVD_TP_60

RESERVED

RESERVED

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

1

Can be left NC is Intel CRM

implementation; ESD/DG

recommendation to GND

07

Clarksfield/Auburndale

Clarksfield/Auburndale

Clarksfield/Auburndale

Clarksfield/Auburndale

10

CFG4

A A

The Clarkfield processor's PCI Express interface may

not meet PCI Express 2.0 jitter specifications. Intel

recommends placing a 3.01K +/- 5% pull down resistor to

VSS on CFG[7] pin for both rPGA and BGA components.

This pull down resistor should be removed when this

issue is fixed.

5

CFG0

CFG3

CFG4

CFG7

4

R245 *3.01K/F_4R245 *3.01K/F_4

R35 *3.01K/F_4R35 *3.01K/F_4

R34 *3.01K/F_4R34 *3.01K/F_4

R246 *3.01K/F_4R246 *3.01K/F_4

(Display Port

Presence)

CFG0

(PCI-Epress

Configuration Select)

CFG3

(PCI-Epress Static

Lane Reversal)

Disabled; No Physical Display Port

attached to Embedded Diplay Port

Single PEG

Normal Operation Lane Numbers Reversed

3

Enabled; An external Display port

device is connected to the Embedded

Display port

Bifurcation enabled

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

Monday, Decem ber 21, 2009

Monday, Decem ber 21, 2009

Monday, Decem ber 21, 2009

PROJECT :

ARRANDALE 4/4

ARRANDALE 4/4

ARRANDALE 4/4

FH2

FH2

FH2

of

738

738

1

738

1A

1A

1A

Page 8

5

4

3

2

1

http://hobi-elektronika.net

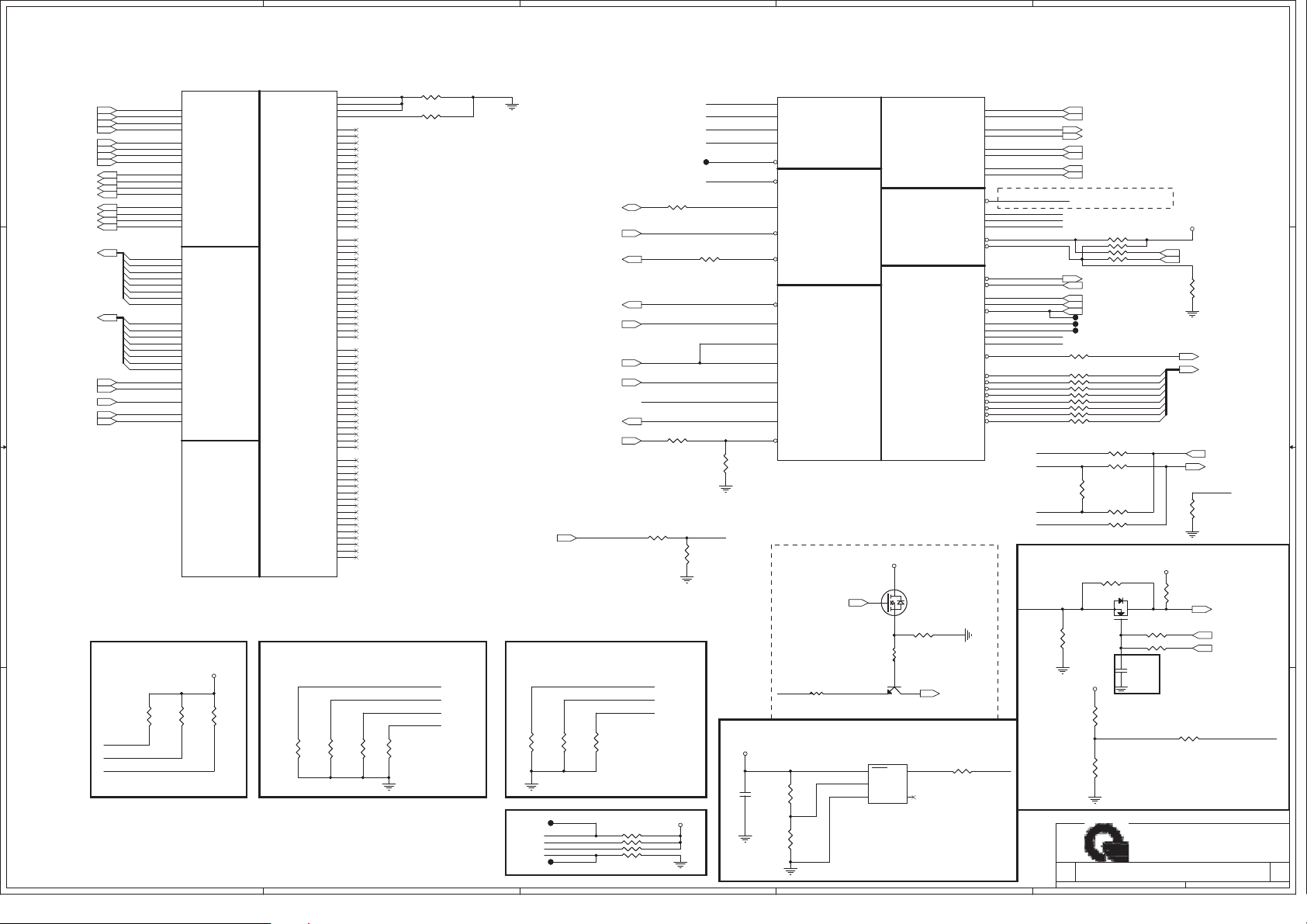

IBEX PEAK-M (DMI,FDI,GPIO)

U18C

U18C

PM_SLP_LAN#_R

BC24

DMI0RXN

BJ22

DMI1RXN

AW20

DMI2RXN

BJ20

DMI3RXN

BD24

DMI0RXP

BG22

DMI1RXP

BA20

DMI2RXP

BG20

DMI3RXP

BE22

DMI0TXN

BF21

DMI1TXN

BD20

DMI2TXN

BE18

DMI3TXN

BD22

DMI0TXP

BH21

DMI1TXP

BC20

DMI2TXP

BD18

DMI3TXP

BH25

DMI_ZCOMP

BF25

DMI_IRCOMP

T6

SYS_RESET#

M6

SYS_PWROK

B17

PWROK

K5

MEPWROK

A10

LAN_RST#

D9

DRAMPWROK

C16

RSMRST#

M1

SUS_PWR_DN_ACK / GPIO30

P5

PWRBTN#

P7

ACPRESENT / GPIO31

A6

BATLOW# / GPIO72

F14

RI#

IbexPeak-M_R1P0

IbexPeak-M_R1P0

R99 10K/J_4R99 10K/J_4

R263 10K/J_4R263 10K/J_4

R273 10K/J_4R273 10K/J_4

R85 10K/J_4R85 10K/J_4

+3V_RUN +3V_S5

DMI

FDI

DMI

FDI

CLKRUN# / GPIO32

SUS_STAT# / GPIO61

SUSCLK / GPIO62

SLP_S5# / GPIO63

System Power Management

System Power Management

SLP_LAN# / GPIO29

INT_CRT_BLU

INT_CRT_GRE

INT_CRT_RED

PANEL_BKEN

ENVDD

DMI_RXN04

DMI_RXN14

DMI_RXN24

DMI_RXN34

XDP_DBRESET#4,22

PM_DRAM_PWRGD4

ICH_RSMRST#25

SUS_PWR_ACK25

DNBSWON#25

AC_PRESENT25

CLKRUN#

LCD_DDCDAT

LCD_DDCCLK

L_CTRL_CLK

L_CTRL_DATA

XDP_DBRESET#

PM_RI#

PCIE_WAKE#

PM_BATLOW#

AC_PRESENT

SUS_PWR_ACK

DMI_RXP04

DMI_RXP14

DMI_RXP24

DMI_RXP34

DMI_TXN04

DMI_TXN14

DMI_TXN24

DMI_TXN34

DMI_TXP04

DMI_TXP14

DMI_TXP24

DMI_TXP34

+1.05V_PCH

PCH_PWRGD

R300 8.2K_4R300 8.2K_4

R24 2.2K/J_4R24 2.2K/J_4

R25 2.2K/J_4R25 2.2K/J_4

R26 10K/J_4R26 10K/J_4

R27 10K/J_4R27 10K/J_4

R296 1K/J_4R296 1K/J_4

R275 10K/J_4R275 10K/J_4

R81 10K/J_4R81 10K/J_4

R289 8.2K/J_4R289 8.2K/J_4

R111 8.2K/J_4R111 8.2K/J_4

R109 8.2K/J_4R109 8.2K/J_4

R57 49.9/F_4R57 49.9/F_4

R107 0/J_4R107 0/J_4

R265 0/J_4R265 0/J_4

R98 0/J_4R98 0/J_4

+3V_RUN

12

12

+3V_S5

DMI_ZCOMP

XDP_DBRESET#

SYS_PWROK

PWROK

MEPWROK

LAN_RST#

ICH_RSMRST#

SUS_PWR_ACK

AC_PRESENT

PM_BATLOW#

PM_RI#

PCH_PWRGD

ICH_RSMRST#

LAN_RST#

D D

C C

B B

BA18

FDI_RXN0

BH17

FDI_RXN1

BD16

FDI_RXN2

BJ16

FDI_RXN3

BA16

FDI_RXN4

BE14

FDI_RXN5

BA14

FDI_RXN6

BC12

FDI_RXN7

BB18

FDI_RXP0

BF17

FDI_RXP1

BC16

FDI_RXP2

BG16

FDI_RXP3

AW16

FDI_RXP4

BD14

FDI_RXP5

BB14

FDI_RXP6

BD12

FDI_RXP7

BJ14

FDI_INT

BF13

FDI_FSYNC0

BH13

FDI_FSYNC1

BJ12

FDI_LSYNC0

BG14

FDI_LSYNC1

PCIE_WAKE#

J12

WAKE#

CLKRUN#

Y1

RSV_LPCPD#

P8

ICH_SUSCLK

F3

E4

H7

SLP_S4#

P12

SLP_S3#

SLP_M#_R

K8

SLP_M#

N2

TP23

BJ10

PMSYNCH

PM_SLP_LAN#_R

F6

Close to VGA side

R219 150/F_4R219 150/F_4

R220 150/F_4R220 150/F_4

R221 150/F_4R221 150/F_4

R19 100K/J_4R19 100K/J_4

R20 100K/J_4R20 100K/J_4

FDI_TXN0 4

FDI_TXN1 4

FDI_TXN2 4

FDI_TXN3 4

FDI_TXN4 4

FDI_TXN5 4

FDI_TXN6 4

FDI_TXN7 4

FDI_TXP0 4

FDI_TXP1 4

FDI_TXP2 4

FDI_TXP3 4

FDI_TXP4 4

FDI_TXP5 4

FDI_TXP6 4

FDI_TXP7 4

FDI_INT 4

FDI_FSYNC0 4

FDI_FSYNC1 4

FDI_LSYNC0 4

FDI_LSYNC1 4

PCIE_WAKE# 19,26

T17T17

T25T25

SIO_SLP_S5# 25

SIO_SLP_S4# 25

SIO_SLP_S3# 25

T16T16

T51T51

PM_SYNC 4

PANEL_BKEN16

ENVDD16

BIA_PWM16

LCD_DDCCLK16

LCD_DDCDAT16

T9

TXLCLKOUT-16

TXLCLKOUT+16

TXLOUT0-16

TXLOUT1-16

TXLOUT2-16

PADT6PAD

T6

TXLOUT0+16

TXLOUT1+16

TXLOUT2+16

PADT3PAD

T3

TXUCLKOUT-16

TXUCLKOUT+16

TXUOUT0-16

TXUOUT1-16

TXUOUT2-16

PAD

PAD

T34

T34

TXUOUT0+16

TXUOUT1+16

TXUOUT2+16

PAD

PAD

T33

T33

INT_CRT_BLU17

INT_CRT_GRE17

INT_CRT_RED17

G_CLK_DDC217

G_DAT_DDC217

INT_CRT_HSYNC17

INT_CRT_VSYNC17

PANEL_BKEN

ENVDD

LCD_DDCCLK

LCD_DDCDAT

L_CTRL_CLK

L_CTRL_DATA

R50 2.37K/F_4R50 2.37K/F_4

LVDS_VBG

PADT9PAD

TXLCLKOUTTXLCLKOUT+

TXLOUT0TXLOUT1TXLOUT2INT_TXLOUTN3

TXLOUT0+

TXLOUT1+

TXLOUT2+

INT_TXLOUTP3

TXUCLKOUTTXUCLKOUT+

TXUOUT0TXUOUT1TXUOUT2INT_TXUOUTN3

TXUOUT0+

TXUOUT1+

TXUOUT2+

INT_TXUOUTP3

INT_CRT_BLU

INT_CRT_GRE

INT_CRT_RED

R218 33/J_4R218 33/J_4

R224 33/J_4R224 33/J_4

R38 1K/D_4R38 1K/D_4

A

UMA HDMI signals

DPB_CTRL_CLK

DPB_CTRL_DATA

12

12

12

12

12

DPB_LANE0_N

DPB_LANE0_P

DPB_LANE1_N

DPB_LANE1_P

DPB_LANE2_N

DPB_LANE2_P

DPB_LANE3_N

DPB_LANE3_P

IBEX PEAK-M (LVDS,DDI)

U18D

U18D

T48

L_BKLTEN

T47

L_VDD_EN

Y48

L_BKLTCTL

AB48

L_DDC_CLK

Y45

L_DDC_DATA

AB46

L_CTRL_CLK

V48

L_CTRL_DATA

AP39

LVD_IBG

AP41

LVD_VBG

AT43

LVD_VREFH

AT42

LVD_VREFL

AV53

LVDSA_CLK#

AV51

LVDSA_CLK

BB47

LVDSA_DATA#0

BA52

LVDSA_DATA#1

AY48

LVDSA_DATA#2

AV47

LVDSA_DATA#3

BB48

LVDSA_DATA0

BA50

LVDSA_DATA1

AY49

LVDSA_DATA2

AV48

LVDSA_DATA3

AP48

LVDSB_CLK#

AP47

LVDSB_CLK

AY53

LVDSB_DATA#0

AT49

LVDSB_DATA#1

AU52

LVDSB_DATA#2

AT53

LVDSB_DATA#3

AY51

LVDSB_DATA0

AT48

LVDSB_DATA1

AU50

LVDSB_DATA2

AT51

LVDSB_DATA3

AA52

CRT_BLUE

AB53

CRT_GREEN

AD53

CRT_RED

V51

CRT_DDC_CLK

V53

CRT_DDC_DATA

Y53

CRT_HSYNC

Y51

CRT_VSYNC

AD48

DAC_IREF

AB51

CRT_IRTN

IbexPeak-M_R1P0

IbexPeak-M_R1P0

R404 0_4R404 0_4

R405 0_4R405 0_4

C4564 .1U/10V_4C4564 .1U/10V_4

C4565 .1U/10V_4C4565 .1U/10V_4

C4566 .1U/10V_4C4566 .1U/10V_4

C4567 .1U/10V_4C4567 .1U/10V_4

C4568 .1U/10V_4C4568 .1U/10V_4

C4569 .1U/10V_4C4569 .1U/10V_4

C4570 .1U/10V_4C4570 .1U/10V_4

C4571 .1U/10V_4C4571 .1U/10V_4

SDVO_TVCLKINN

SDVO_TVCLKINP

SDVO_STALLN

SDVO_STALLP

SDVO_CTRLCLK

SDVO_CTRLDATA

LVDS

LVDS

DDPC_CTRLCLK

DDPC_CTRLDATA

Digital Display Interface

Digital Display Interface

DDPD_CTRLCLK

DDPD_CTRLDATA

CRT

CRT

SDVO_CLK 17

SDVO_DATA 17

IN_D2# 17

IN_D2 17

IN_D1# 17

IN_D1 17

IN_D0# 17

IN_D0 17

IN_CLK# 17

IN_CLK 17

SDVO_INTN

SDVO_INTP

DDPB_AUXN

DDPB_AUXP

DDPB_HPD

DDPB_0N

DDPB_0P

DDPB_1N

DDPB_1P

DDPB_2N

DDPB_2P

DDPB_3N

DDPB_3P

DDPC_AUXN

DDPC_AUXP

DDPC_HPD

DDPC_0N

DDPC_0P

DDPC_1N

DDPC_1P

DDPC_2N

DDPC_2P

DDPC_3N

DDPC_3P

DDPD_AUXN

DDPD_AUXP

DDPD_HPD

DDPD_0N

DDPD_0P

DDPD_1N

DDPD_1P

DDPD_2N

DDPD_2P

DDPD_3N

DDPD_3P

BJ46

BG46

BJ48

BG48

BF45

BH45

T51

T53

BG44

BJ44

AU38

BD42

BC42

BJ42

BG42

BB40

BA40

AW38

BA38

Y49

AB49

BE44

BD44

AV40

BE40

BD40

BF41

BH41

BD38

BC38

BB36

BA36

U50

U52

BC46

BD46

AT38

BJ40

BG40

BJ38

BG38

BF37

BH37

BE36

BD36

DPB_HPD_Q

R406

R406

100K_4

100K_4

DPB_CTRL_CLK

DPB_CTRL_DATA

DPB_HPD_Q

DPB_LANE0_N

DPB_LANE0_P

DPB_LANE1_N

DPB_LANE1_P

DPB_LANE2_N

DPB_LANE2_P

DPB_LANE3_N

DPB_LANE3_P

1

R407 0_4R407 0_4

+3V_RUN

2

TP1TP1

TP2TP2

Q23

Q23

*2N7002K

*2N7002K

3

08

A

HDMI_HPD_CON 17

C109 *0.1U/10V_4C109 *0.1U/10V_4

R115

R115

*2K_4

*2K_4

U5

U5

C111

C111

*0.1U_4

*0.1U_4

2

1

4

MC74VHC1G08DFT2G

MC74VHC1G08DFT2G

3 5

4

PCH_PWRGD

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Monday, December 21, 2009

Monday, December 21, 2009

Monday, December 21, 2009

Date: Sheet

Date: Sheet of

3

2

Date: Sheet of

PROJECT :

IBEX PEAK-M 1/6

IBEX PEAK-M 1/6

IBEX PEAK-M 1/6

FH2

FH2

FH2

1

1A

1A

1A

of

838

838

838

A A

IMVP_PWRGD4,29

MPWROK16,25

5

Page 9

5

+VCC_RTC

RTC BATTERY

D18

R348

R348

+3VPCU

1K/J_4

1K/J_4

D D

+5VPCU

R351 *2.2K/F_4R351 *2.2K/F_4

R349

R349

*4.7K_4

*4.7K_4

R350

R350

*15K_4

*15K_4

C C

ACZ_SYNC_R24

ACZ_RST#_R24

CODEC

ACZ_SDOUT_R24

ACZ_BIT_CLK_R24

Place all series terms close to PCH except for SDIN input

lines,which should be close to source.Placement of R773, R775,

R776 & R777 should equal distance to the T split trace point.

Basically, keep the same distance from T for all series

termination resistors.

B B

+3V_RUN

1 2

R295 *1K/J_4R295 *1K/J_4

+3V_S5

Res. of TDI near PCH

R315

R315

R306

R306

200/J_4

200/J_4

200/J_4

200/J_4

A A

R316

R316

100/J_4

100/J_4

R307

R307

100/J_4

100/J_4

R312

R312

200/J_4

200/J_4

R290

R290

100/J_4

100/J_4

*MMBT3904

*MMBT3904

PCBEEP

R305

R305

*20K/J_4

*20K/J_4

R304

R304

*10K/J_4

*10K/J_4

5

Q17

Q17

13

2

D18

2 1

CH501H-40

CH501H-40

+VCCRTC3

D17

D17

2 1

CH501H-40

CH501H-40

R347

R347

1K/J_4

1K/J_4

CON11

CON11

1

1

2

2

AAA-BAT-054-K01

AAA-BAT-054-K01

bat-23_2-4_2

bat-23_2-4_2

DFHS02FS012

DFHS02FS012

R252 33/J_4R252 33/J_4

R238 33/J_4R238 33/J_4

R258 33/J_4R258 33/J_4

R242 33/J_4R242 33/J_4

C295

C295

*27P/50V_4

*27P/50V_4

50

50

A

ACZ_SYNC

ACZ_RST#

ACZ_SDOUT

ACZ_BIT_ CLK

No Reboot strap.

Low = Default.

PCBEEP

High = No Reboot.

JTAG

Test Pads are need to put on

the same side of mother board.

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_RST#

NC all Res. when

PCH is

production stage.

Res. of TDO

PCH ES1 stage : NC

PCH ES2 stage : pop

R264

R264

1M/F_4

1M/F_4

Flash Descriptor Security Override

GPIO33

(Internal 20K/F pull high to +3.3V_RUN)

Note : GPIO33 is a signal used for Flash

Descriptor Security Override/ME Debug

Mode.This signal should be only asserted

lowthrough an external pull -down in

manufacturing or debug envir onm ents

ONLY.

4

R267 20K/F_4R267 20K/F_4

1U/6.3V_4

1U/6.3V_4

R266 20K/F_4R266 20K/F_4

Note : Only pop when PCH is production

stage & need "JTAG boundary Scan".

Remember to depop XDP side Res.

C306

C306

1U/6.3V_4

1U/6.3V_4

INTVRMEN(Internal Voltage Regulator Enable) :

This signal enables the internal 1.05 V regulators.

This signal must be always pulled-up to VccRTC.

Low = Enabled

High = Disabled

R308 51/J_4R308 51/J_4

PCH_JTAG_TCK_BUF

4

http://hobi-elektronika.net

C307

C307

MEFW_OVERRIDE25

3

C310

C310

15P/50V_4

15P/50V_4

23

Y5

R272

R272

10M/J_4

10M/J_4

4 1

C312

C312

32.768KHZY532.768KHZ

15P/50V_4

15P/50V_4

Cap values depend on Xtal

+VCC_RTC

CODEC

R270 330K/J_4R270 330K/J_4

PCBEEP24

ACZ_SDIN024

ME_FW_OVERRIDE

PR83 10K/F_4PR83 10K/F_4

T50T50

T49T49

T45T45

T47T47

T48T48

T20T20

ACZ_BIT_ CLK

ACZ_SYNC

PCBEEP

ACZ_RST#

ACZ_SDOUT

R53 1K/F_4R53 1K/F_4

GPIO13

PCH_JTAG_TCK_BUF

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_RST#

SPI_CLK

SPI_CS0#

SPI_CS1#

SPI_SI

SPI_SO

For PCH 32Mbit (4M Byte)

SPI_CS0#

SPI_CLK

SPI_SI

SPI_SO

R311 15/J_4R311 15/J_4

R292 15/J_4R292 15/J_4

R323 15/J_4R323 15/J_4

R313 15/J_4R313 15/J_4

SPI_CS0#_R

SPI_CLK_R

SPI_SI_R

SPI_SO_R

3

2

IBEX PEAK-M (HDA,JTAG,SATA)

U18A

B13

D13

C14

D17

A16

A14

A30

D29

C30

G30

F30

E32

F32

B29

H32

J30

BA2

AV3

AY3

AY1

AV1

A

R314

R314

3.3K/J_4

3.3K/J_4

U20

U20

1

CE#

6

SCK

5

SI

2

SO

3

WP#

MX25L1605DM2I

MX25L1605DM2I

U18A

RTCX1

RTCX2

RTCRST#

SRTCRST#

INTRUDER#

INTVRMEN

HDA_BCLK

HDA_SYNC

P1

SPKR

HDA_RST#

HDA_SDIN0

HDA_SDIN1

HDA_SDIN2

HDA_SDIN3

HDA_SDO

HDA_DOCK_EN# / GPIO33

HDA_DOCK_RST# / GPIO13

M3

JTAG_TCK

K3

JTAG_TMS

K1

JTAG_TDI

J2

JTAG_TDO

J4

TRST#

SPI_CLK

SPI_CS0#

SPI_CS1#

SPI_MOSI

SPI_MISO

IbexPeak-M_R1P0

IbexPeak-M_R1P0

8

VDD

7

HOLD#

4

VSS

RTCIHDA

RTCIHDA

SPI JTAG

SPI JTAG

+3V_RUN+3V_RUN

C327

C327

0.1U/10V_4

0.1U/10V_4

10

10

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

FWH4 / LFRAME#

LDRQ1# / GPIO23

LPC

LPC

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA

SATA

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATALED#

SATA0GP / GPIO21

SATA1GP / GPIO19

A

R291

R291

3.3K/J_4

3.3K/J_4

LDRQ0#

SERIRQ

2

RTC_RST#

SRTC_RST#

SM_INTRUDER#

PCH_INVRMEN

1 2

C328

C328

22P/50V_4

22P/50V_4

50

50

RTC_X1

RTC_X2

RP4

RP4

R_LAD0

D33

R_LAD1

B33

R_LAD2

C32

R_LAD3

A32

R_LFRAME#

C34

A34

F34

AB9

AK7

AK6

AK11

AK9

AH6

AH5

AH9

AH8

AF11

AF9

AF7

AF6

SATA port 2/3 are not support in HM55 .

AH3

AH1

AF3

AF1

AD9

AD8

AD6

AD5

AD3

AD1

AB3

AB1

AF16

SATA_COMP

AF15

T3

R66 10K/J_4R66 10K/J_4

Y9

1 2

R298 10K/J_4R298 10K/J_4

V1

1 2

1

2

3

4

5

6

7

8

R363 47/F_4R363 47/F_4

R327 10K/J_4R327 10K/J_4

R62 37.4/F_4R62 37.4/F_4

R319 10K/J_4R319 10K/J_4

47X4-0402

47X4-0402

RESET JUMP

RTC_RST#

SRTC_RST#

G1

G1

*SHORT_ PAD

*SHORT_ PAD

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

LAD0 22,25

LAD1 22,25

LAD2 22,25

LAD3 22,25

LFRAME# 22,25

+3V_RUN

IRQ_S ERIRQ 2 5

SATA_RXN0 20

SATA_RXP0 20

SATA_TXN0 20

SATA_TXP0 20

SATA_RXN1 20

SATA_RXP1 20

SATA_TXN1 20

SATA_TXP1 20

+1.05V_PCH

+3V_RUN

SATA_LED# 23

+3V_RUN

(Near ROOM DOOR)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

IBEX PEAK-M 2/6

IBEX PEAK-M 2/6

IBEX PEAK-M 2/6

Monday, December 21, 2009

Monday, December 21, 2009

Monday, December 21, 2009

12

T52

T52

1

PAD

PAD

1

SATA HDD

SATA ODD

FH2

FH2

FH2

09

1A

1A

1A

of

938

938

938

Page 10

5

N

D

4

3

2

1

IBEX PEAK-M (PCI,USB,NVRAM)

U18E

U18E

H40

AD0

N34

AD1

C44

AD2

A38

AD3

C36

AD4

J34

AD5

A40

AD6

D45

D D

PCI_PIRQA#

T10T10

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

T31T31

C C

GNT3#11

PCIRST#:

DG(V1.0) P277

Can be left unconnected.

PAR:

SC(V1.0) P36

Can be left unconnected

if not using PCI.

PME:

DG(V1.0) P277

Can be left unconnected.

0214

CLK_LPC_DEBUG22

B B

CLK_PCI_850225

CLKOUT_PCI[0..4]:

22 ohm series resistor is recommend

(single & double load) on PDG v1.1

Reserve capacitor pads for

improving WWAN.

CLK_LPC_DEBUG

CLK_PCI_8502

Non-iAMT

A A

C108 0.1U/16V_4C108 0.1U/16V_4

PCI_PLTRST#

CLK_LPC_DEBUG

CLK_PCI_FB CLK_PCI_FB_C

50

50

C33 *27P/50V_4

C33 *27P/50V_4

50

50

C31 *27P/50V_4

C31 *27P/50V_4

Add Buffers as needed for

Loading and fanout concerns.

A

+3V_RUN

U4

U4

2

1