Page 1

A

Page

Title of schematic page Rev. Date

01

Page List

02

Block Diagram

03

Change List

04

4 4

3 3

2 2

1 1

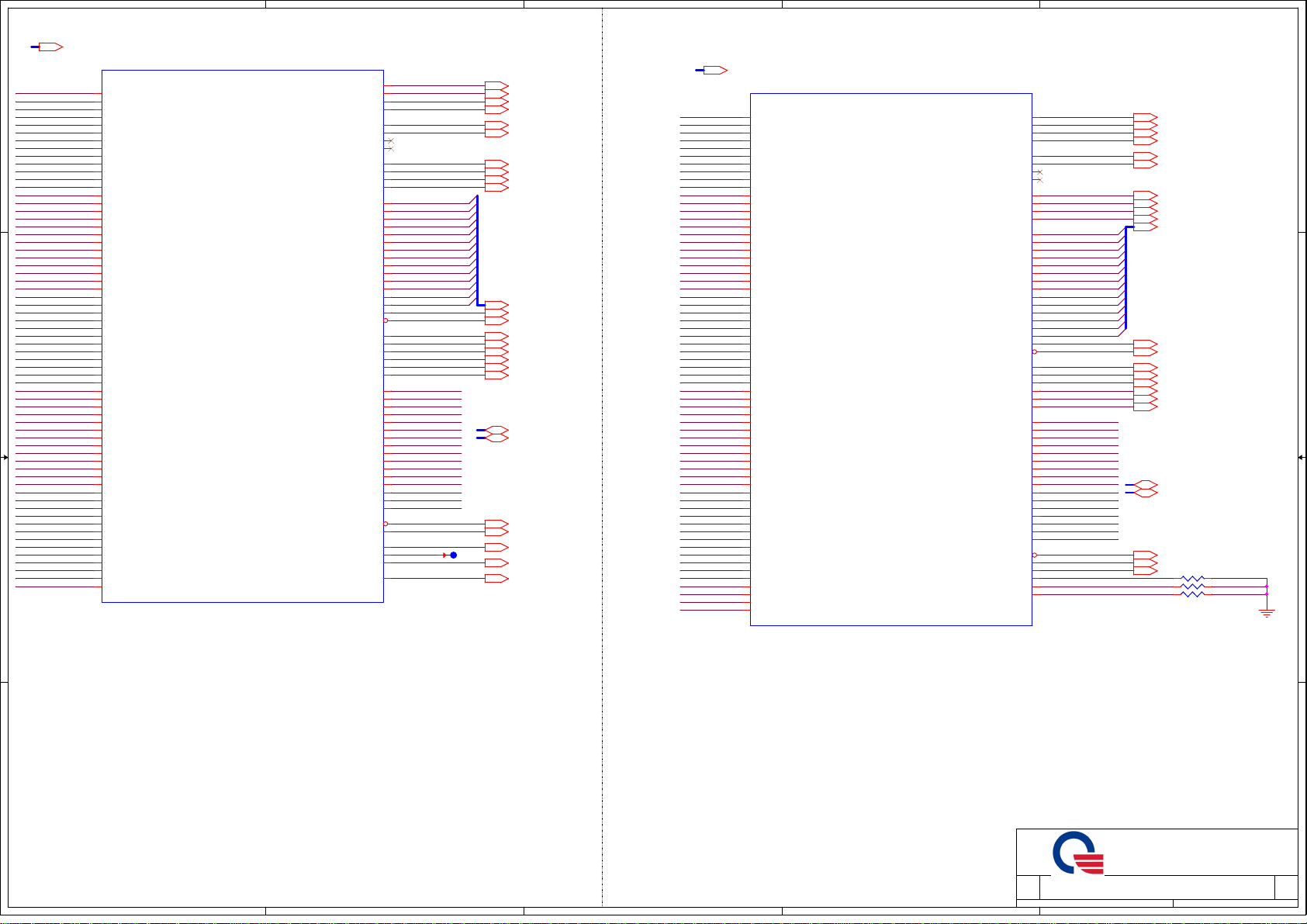

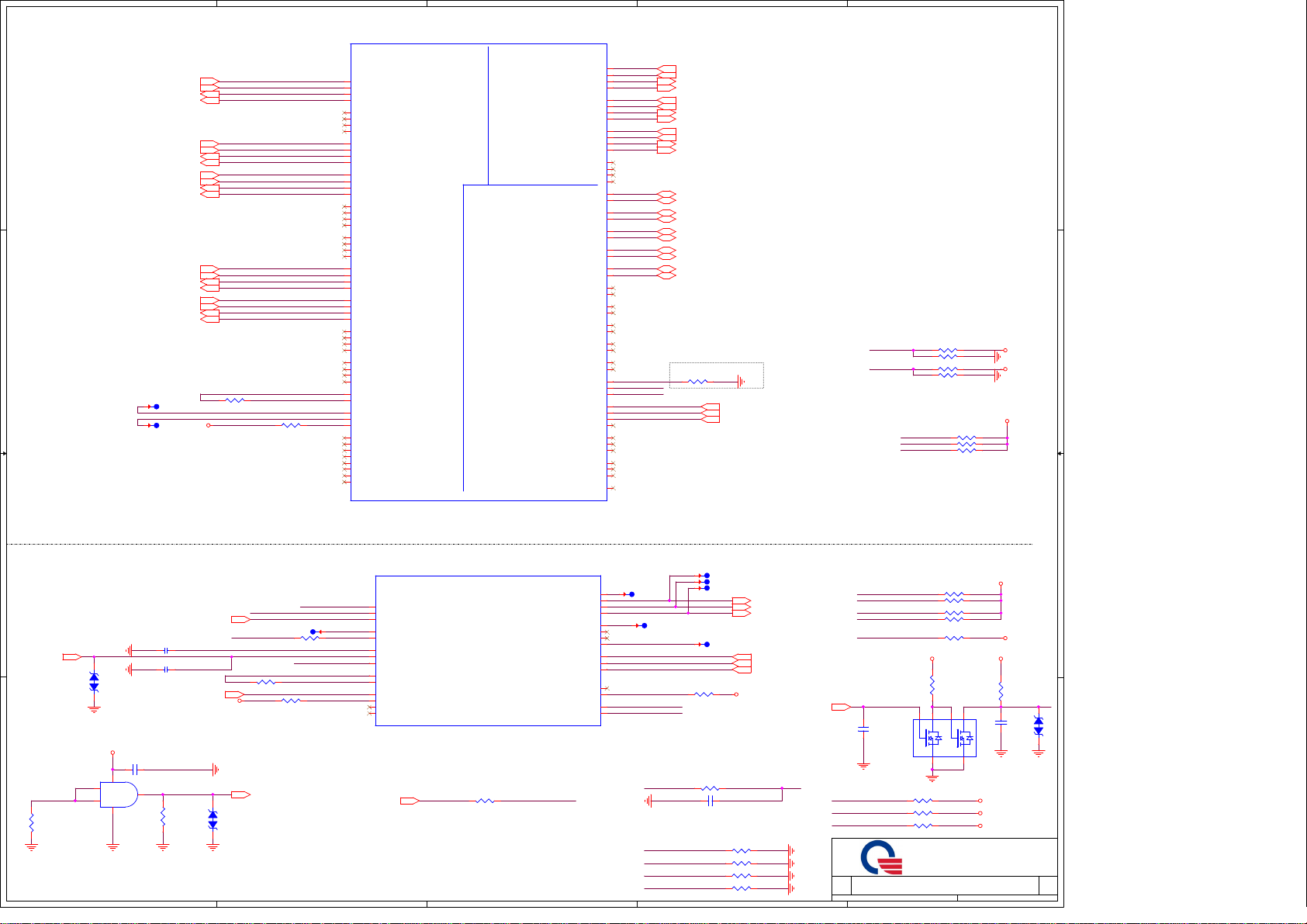

KBL MCP(DISPLAY/JTAG)

05

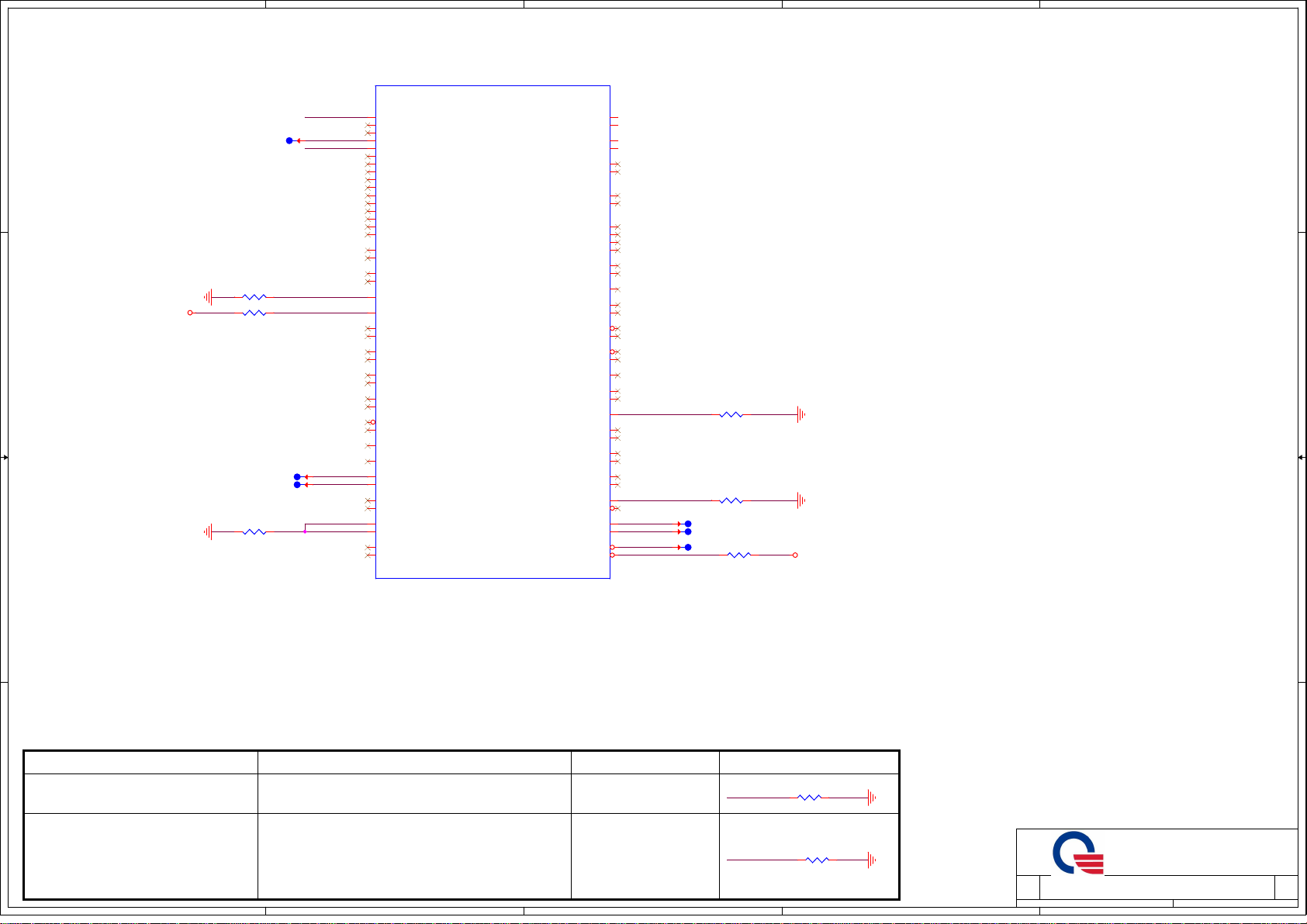

KBL MCP(MEMORY/CHA/CHB)

06

KBL MCP(CFG/RSVD)

07

KBL MCP(POWER-1)

08

KBL MCP(POWER-2)

09

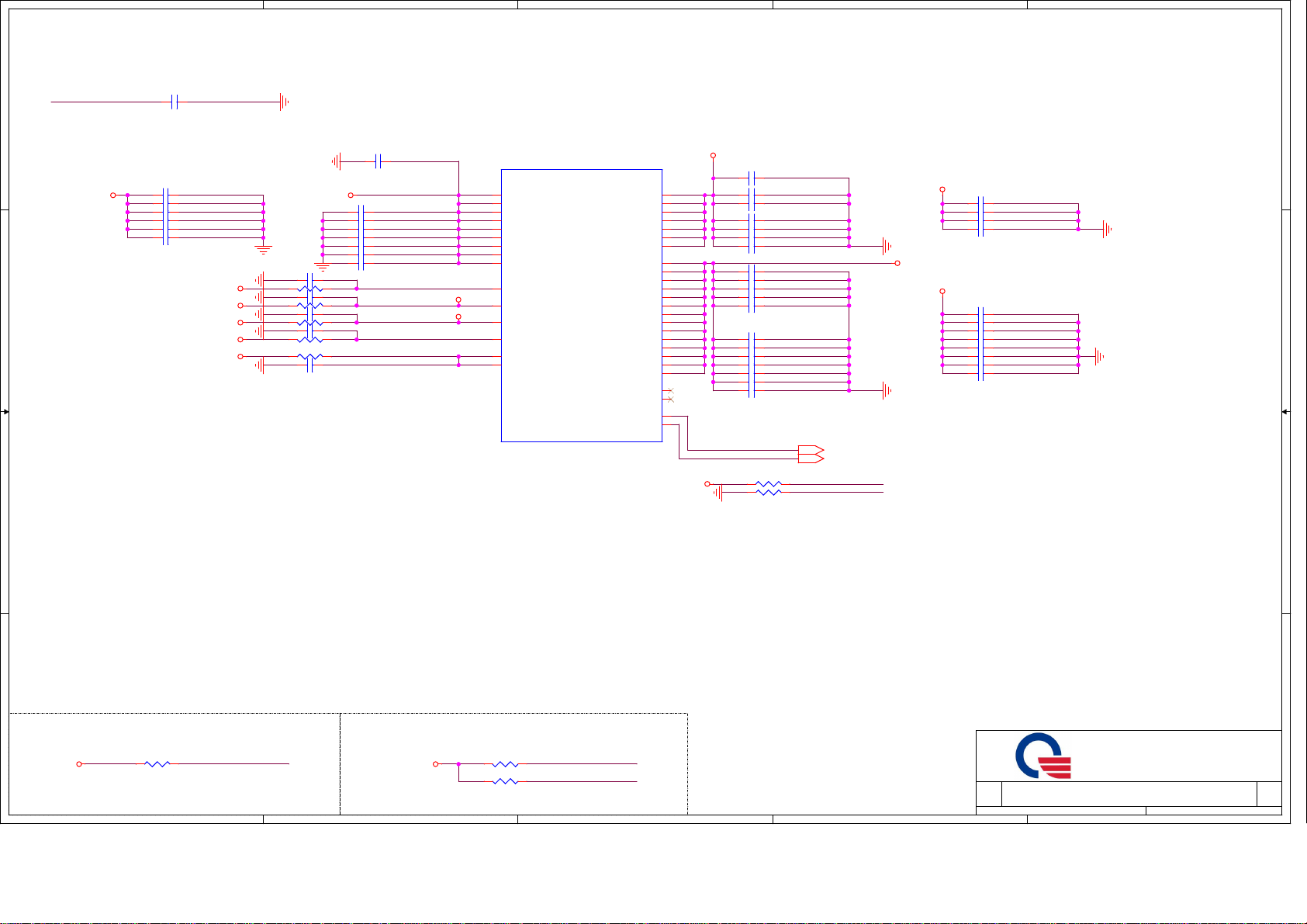

KBL PCH(RTC/CLK)

10

KBL PCH(PCIE/USB/SPM)

11

KBL PCH(HDA/LPC/SPI/SMB)

12

KBL PCH(GPIO/UART/I2C)

13

KBL PCH(POWER)

14

KBL PCH(GND)

15

DDR4 DIMM0-RVS

16

DDR4 DIMM1-STD

17

LCD/HDMI/DMIC/CAMERA

18

HDD/ODD/FAN/TP/Hall_S

19

CR RTS5227S &CR SOCKET

20

EC(IT8528/HX)/FLASH

21

WLAN/BT_M2

22

KB/HOLE

23

Azalia ALC298

24

LAN RTL8106E/RTL8111H

25

USB3.0

26

MB to SB and USB3.0 right

27

LED

28

PowerMAP

29

SMBUS

30

POWER DIAGRAM_V

31

VCCORE/GTCORE/VCCSA (ISL95859)

32

VCCORE/GTCORE/VCCSA (ISL95859)-1

POWER VCC3&VCC5(RT6575CGQW)

33

POWER 1.2VSUS/VTT_MEM

34

POWER 1.0V_S5/1.8_S5(G5335)

35

POWER CHARGE (BQ24780)

36

PWR AD IN/BAT IN/Thermal

37

Power Sequence

38

B

C

D

E

1

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

PCB STACK UP

6L

LAYER 1 : TOP

LAYER 2 : VCC

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : GND

LAYER 6 : BOT

F/W List

Location

BIOS/ME

EC

U3

KU4

BOM select

XDP@: XDP

* : No mount

Update method

Flash tool in Windows

Flash tool in Windows

A

B

C

D

E

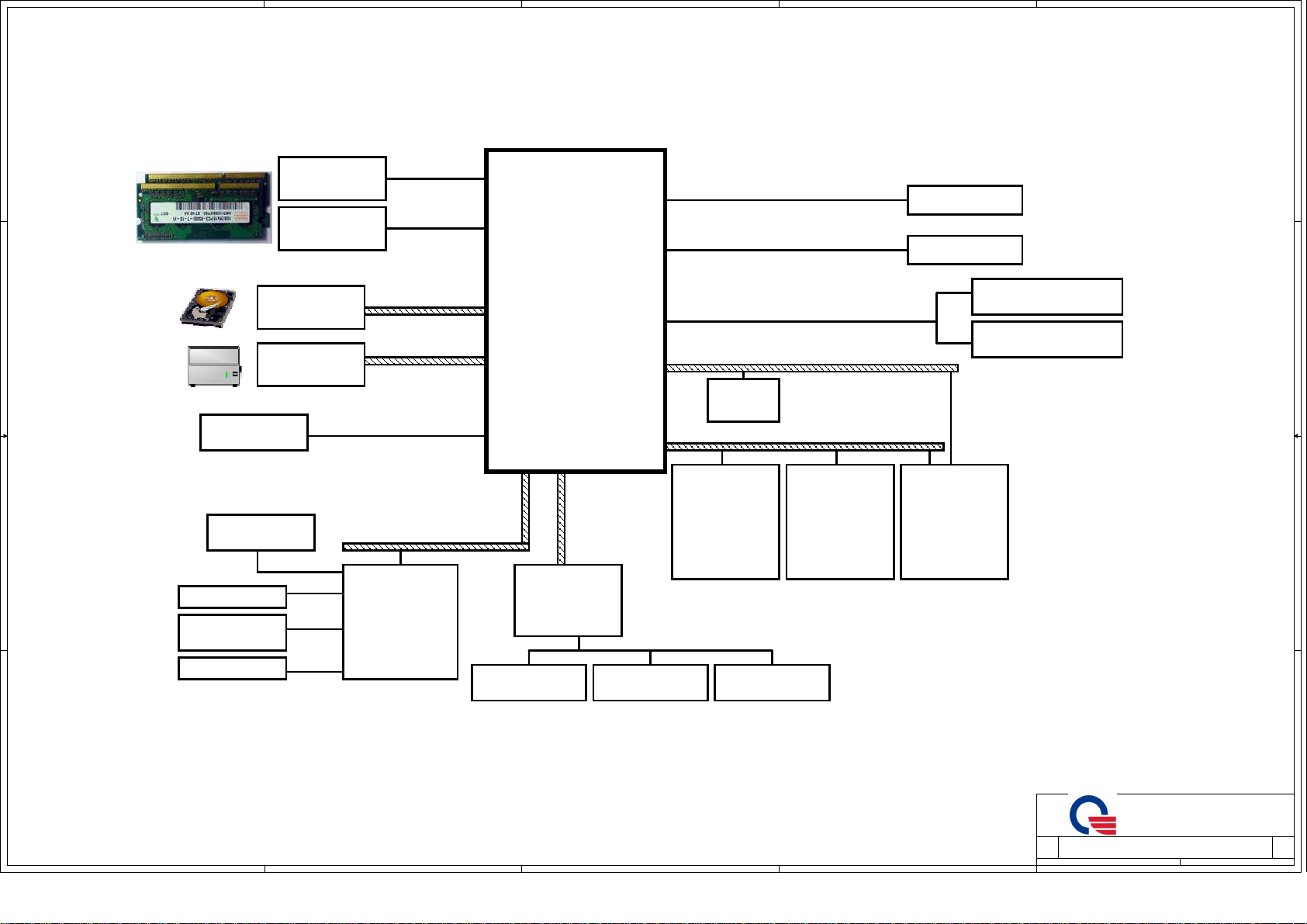

Page 2

5

laptoprepairsecrets@gmail.com

4

3

2

1

FFK 15.6"

D D

C C

B B

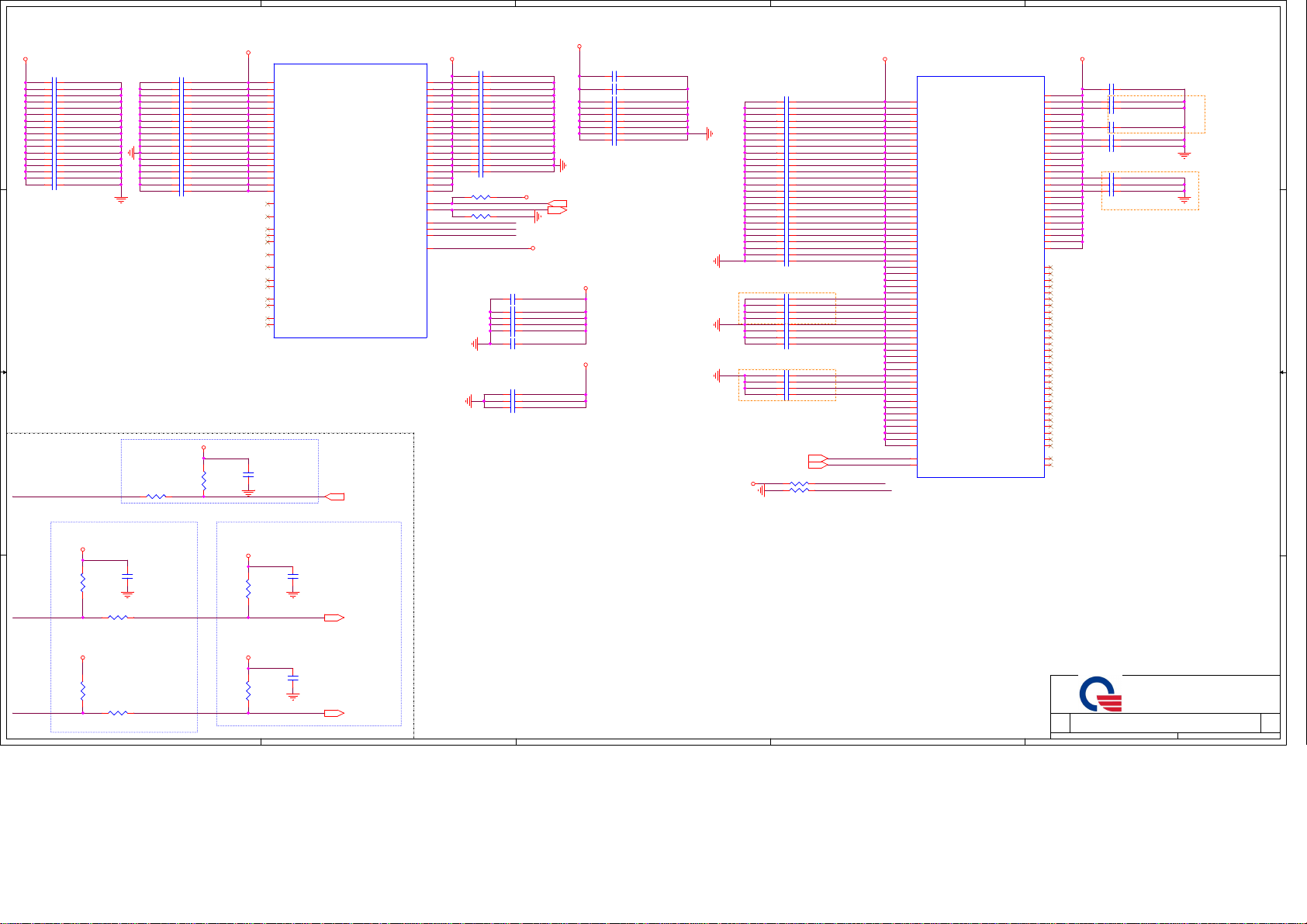

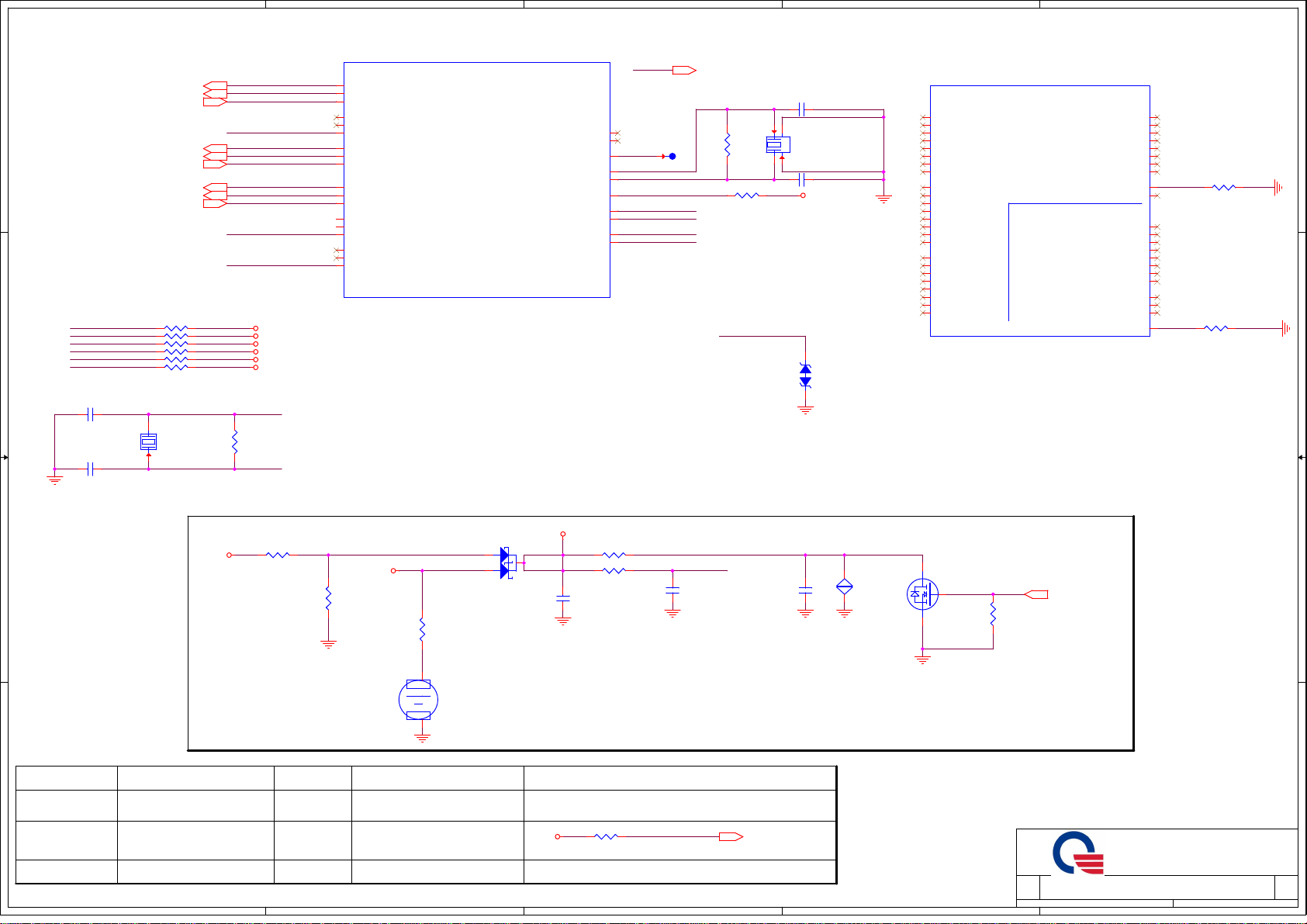

Intel Kaby Lake U Platform Block Diagram

System BIOS

SPI ROM

EC

SPI ROM

Keyboard

Touch Pad

SA869C-22H0

FAN

DDR4 SODIMM1

Maxima 16GBs

DDR4 SODIMM2

Maxima 16GBs

SATA - 1st HDD

Package : 9.5 (mm)

Power :

SATA ODD

Package : (mm)

Power :

PAGE 11

PAGE 20

PAGE 22

PAGE 18

PAGE 18

PAGE 15

PAGE 16

PAGE 18

PAGE 18

DDR4

DDR4

SATA0 GEN3 6GB/s

SATA2 GEN1 1.5GB/s

SPI Interface

LPC Interface

IT 8528E

Embedded Controller

Power :

Package : LQPF128

Size : 14 x 14 (mm)

PAGE 20

4"

4"

Kaby Lake -U

Processor : Daul Core

7"

Package : BGA1356

Size : 42 x 24 x1.27 (mm)

7"

6.5"

10" 14"

Digital MIC

Ultra/Slim

10"

6.5"

Power : 15 (Watt)

9"

12"

11"

PAGE 2~10

Azalia

Audio Codec

ALC298-CG

PAGE 23

Combo Jack

PAGE 26

iPHONE type

PAGE 26

eDP X2 Lane

DP Port 1

USB3.0 Interface

USB2.0 Interface

Camera

Port2

PAGE 17

PCIE Gen 1 x 1 Lane

Card Reader

RTS5227S-GRT

Power :

Package : LQPF48

Size : 7 x 7 (mm)

PAGE 19

Speaker

USB 3.0 Port 1,2(USB 2.0 Port 0,5)

LAN Controller

10/100 RTL8106E-CG

10/1000 RTL81111H

Power :

Package : OFN48

Size : 6 x 6 (mm)

PAGE 24

PAGE 23

M2 Card

WLAN / BT Combo

eDP

HDMI Conn

PAGE 17

PAGE 17

USB3.0 Port x 2(Left side)

PAGE 25

USB3.0 Port x 1 Right side)

PAGE 26

PAGE 21

01

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

5

4

3

2

Tuesday, January 24, 2017

PROJECT :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

FFK

FFK

FFK

3A

3A

2 38

2 38

1

2 38

3A

Page 3

5

Model

FFK MB

D D

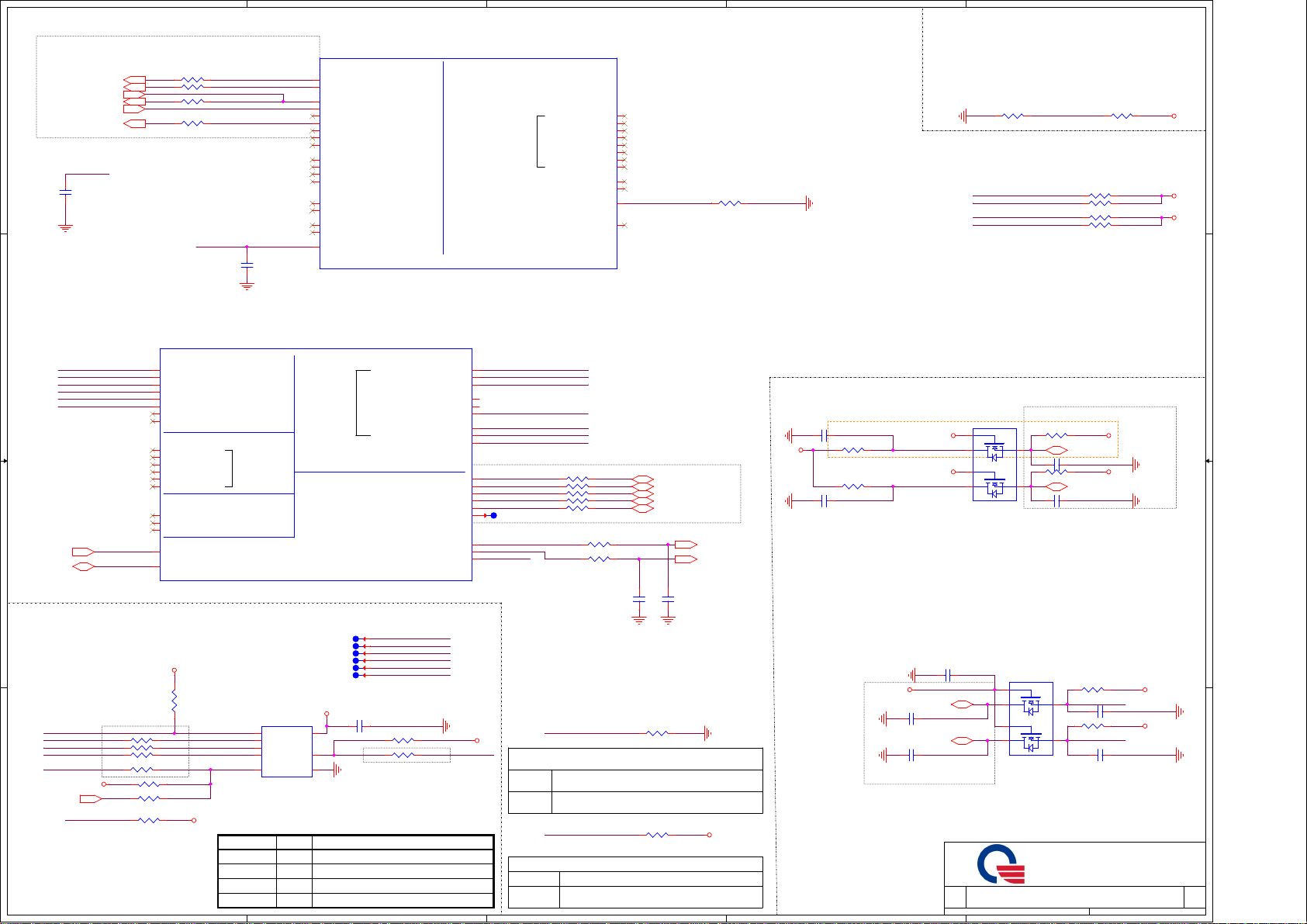

REV

CHANGE LIST

AR26, R5164, R5165, R5166, R5167 change to short pad1

2

CN27 2IN1 CARD change to footprint sdcard-psdbtm-09glbs1nn4hb-smt for correct

3

Change EMU_LID GPA5 to GPH1 (Open Drain) for BLON timing.

4

Stuff C597 0.01uf for VCCST_PWRGD understood issue.

5

Add KR83, KU6 & KC36, KC37 circuit location for tPLT18 timing issue with reserve

6

Stuff PR327 & PQ61, MAIND change to RUN_ON for tPLT18 timing issue.

ES2

7

change PR34 from 137k to 124k ohm to correct IMON

8

change PR11 from 2.26k to 1.96k to correct LL

9

change location PR1,PR2,PR36,PR37,PR53,PR55,PR352 to short pad from 0 ohm 0402 resistor for ES2 stage.

10

Del location PG1, PG18, PG14, PG15, PG16, PG17, PG2, PG8, PG13, PG3, PG10, PG9 and PG12, ER13 short PAD for FFK ES2 Verify schematic.

11

PC126 change to 220pf from 2200pf & PC121 change to 680pf from 560pf for audio sequence issue.

12

PC35 from 680pF to 1000pF to correct DVID reponse

4

3

2

1

3

13

14

15

16

C C

17

18

1

Chang PR180 0ohm to 100kohm & stuff PC142 0.01uF RC delay timing for meet +1.2V_SUS & +2.5V_SUS sequence timing

2

change PR48 from 4.32k to 6.8k ohm to correct DCR error at high temp .

PP

3

change PR49 from 316 to 365 ohm to set Min 44A OCP

4

change PR30 from 110k to 118k ohm to correct IMON.

5

change PR10 from 4.32k to 6.8k ohm to correct DCR error at high temp .

6

change PR11 from 1.96k to 2.1k ohm to correct LL.

7

change PR5 from 316 ohm to 340 ohm to correct LL and IMON.

8

change PR42 from 1.65k to 1.78k to correct LL

9

B B

10

11

12

13

14

15

16

17

18

19

1

MRT

2

A A

3

DOC NO.

PROJECT MODEL :

DATE:

PART NUMBER: DRAWING BY: REVISON:

5

4

2016/10/18FFK APPROVED BY:

3A

3

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Tuesday, January 2 4, 2017

Tuesday, January 2 4, 2017

Tuesday, January 2 4, 2017

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

FFK

PROJECT :

FFK

PROJECT :

FFK

Change List

Change List

Change List

3 38

3 38

3 38

3A

3A

3A

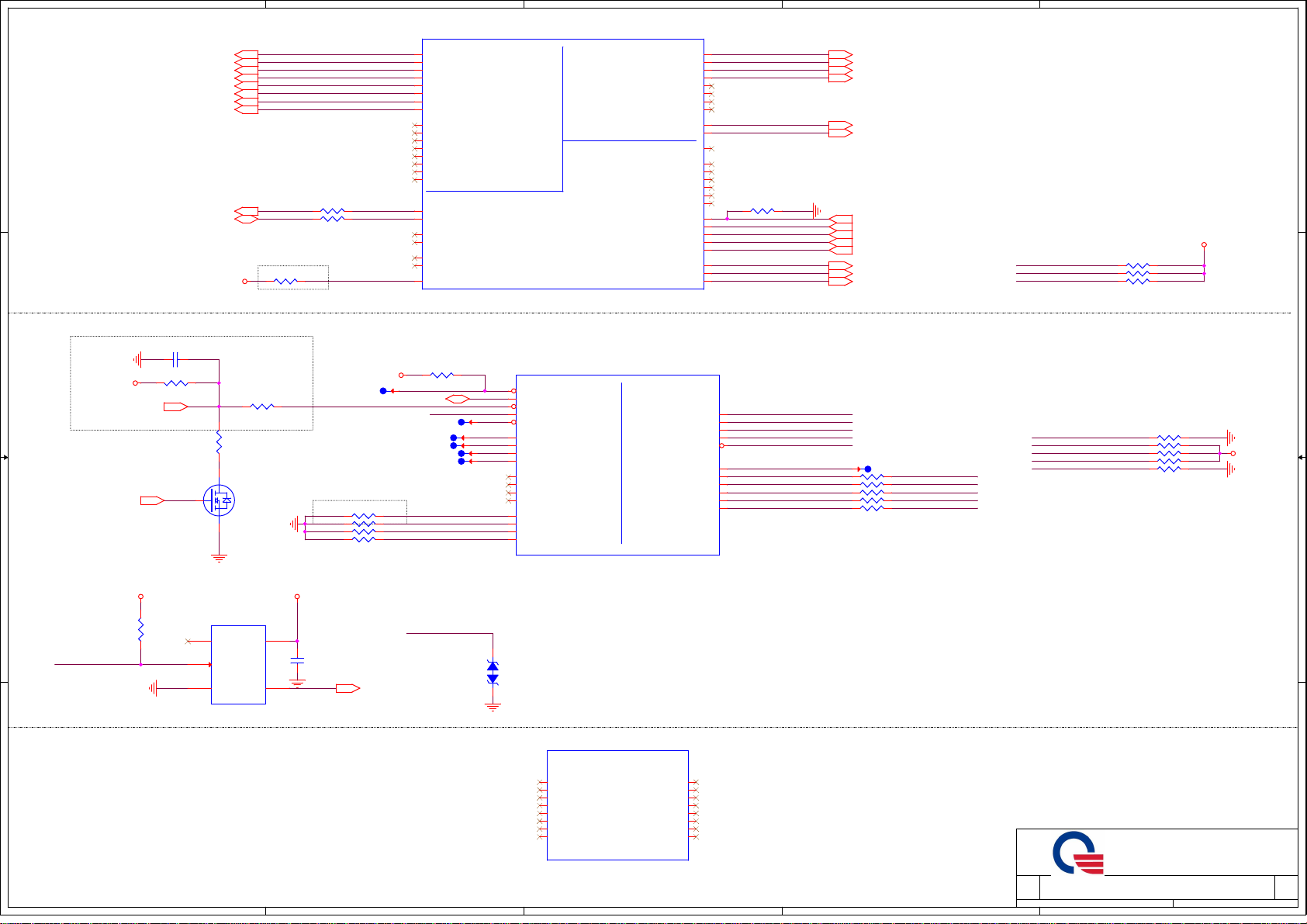

Page 4

5

INT. HDMI

INT_HDMI_TXDN217

INT_HDMI_TXDP217

INT_HDMI_TXDN117

INT_HDMI_TXDP117

INT_HDMI_TXDN017

INT_HDMI_TXDP017

INT_HDMI_TXCN17

D D

INT_HDMI_TXCP17

INT_HDMI_SCL17

INT_HDMI_SDA17

+1.0V_VCCIO

R562 33/J_4

R563 33/J_4

R7 24.9/F_4

EDP_COMP

4

U1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

KBL_ULT/BGA

3

KabyLake ULT (DISPLAY)

SKL_ULT

DDI

DISPLAY SIDEBANDS

1 OF 20

EDP

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

INT. eDP

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

R1 *20K/F_4

L9

L7

SWI#

L6

EC_EXT_SMI#

N9

SIO_EXT_SCI#

L10

R12

R11

U13

2

EDP_TX0# 17

EDP_TX0 17

EDP_TX1# 17

EDP_TX1 17

EDP_AUX# 17

EDP_AUX 17

INT_HDMI_HPD_Q 17

SWI# 20

EC_EXT_SMI# 20

SIO_EXT_SCI# 20

EDP_HPD 17

INT_LVDS_BLON 17,20

INT_LVDS_BRIGHT 17

INT_LVDS_VDDEN 17

1

www.laptoprepairsecrets.com

+3V_S5

SWI#

SIO_EXT_SCI#

EC_EXT_SMI#

R422 10K/F_4

R6 10K/F_4

R8 10K/F_4

4

C C

B B

A A

Put damping resistor close to CPU

C1 47P/50V/NPO_4_KEN

+1.0V_VCCSTG

PROCHOT_EC20

PCH_THRMTRIP#

R9 1K/F_4

H_PROCHOT#31,36

2

+1.0V_S5_VCCST +1.0V_S5_VCCST

R27

1K/F_4

2

5

R11 499/F_4

R833

75/F_4

3

Q1

2N7002K

1

U36

NC1VCC

A

GND3Y

74AUP1G07GW

5

12

4

TP59

CPU_PROCHOT#

R18 49.9/F_4

R19 49.9/F_4

R20 *49.9/F_4

R21 *49.9/F_4

C809

0.1U/10V/X7R_4_KEN

SHDN# 33,37

+1.0V_S5

R431 *10K/F_4

EC_PECI20

PCH_THRMTRIP#

TP60

TP127

TP128

TP121

TP122

PROC_OPI_COMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

SHDN#

4

AT16

AU16

1 2

D63

A54

C65

C63

A65

C55

D55

B54

C56

BA5

AY5

H66

H65

A6

A7

D58

*PESD5V0U1BB

C7

U12

U11

H11

SKL_ULT

CPU MISC

U1T

RSVD_AW69

RSVD_AW68

RSVD_AU56

RSVD_AW48

RSVD_C7

RSVD_U12

RSVD_U11

RSVD_H11

KBL_ULT/BGA

U1D

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

KBL_ULT/BGA

AW69

AW68

AU56

AW48

+3V

+3V

SKL_ULT

SPARE

4 OF 20

20 OF 20

JTAG

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

RSVD_F6

RSVD_E3

RSVD_C11

RSVD_B11

RSVD_A11

RSVD_D12

RSVD_C12

RSVD_F52

3

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

JTAGX

F6

E3

C11

B11

A11

D12

C12

F52

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

XDP_TCK_CPU

XDP_TDI_CPU

XDP_TDO_CPU

XDP_TMS_CPU

XDP_TRST_CPU

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TRST#

PCH_JTAGX

TP151

R882 *0_4_S

R762 *0_4_S

R883 *0_4_S

R760 *0_4_S

R763 *0_4_S

XDP_TDI_CPU

XDP_TDO_CPU

XDP_TMS_CPU

XDP_TRST_CPU

XDP_TCK_CPU

2

XDP_TCK_CPU

XDP_TDI_CPU

XDP_TDO_CPU

XDP_TMS_CPU

XDP_TRST_CPUPCH_JTAG_TCK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

R14 51/F_4

R12 *51/F_4

R10 100/F_4

R13 *51/F_4

R15 *51/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

KBL MCP(Display/eDP)

KBL MCP(Display/eDP)

KBL MCP(Display/eDP)

1

FFK

FFK

FFK

4 38

4 38

4 38

+1.0V_VCCSTG

3A

3A

3A

Page 5

5

KabyLake ULT (DDR4)

M_A_DQ[63:0] 15

U1B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

D D

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

C C

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

B B

M_A_DQ62

M_A_DQ63

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

KBL_ULT/BGA

SKL_ULT

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

2 OF 20

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

4

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

M_A_ODT0_CPU

AT43

M_A_ODT1_CPU

AY50

BB50

AY51

BA50

BB52

BA51

BA52

AW52

AY52

BB54

AT50

BA54

AW54

AU46

AY54

BA55

AT46

AU48

AU50

AU52

AT48

AY55

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BG#1

M_A_ACT#

M_A_WE#

M_A_CAS#

M_A_RAS#

M_A_BA#0

M_A_BA#1

M_A_BG#0

M_A_DQSN0

M_A_DQSP0

M_A_DQSN1

M_A_DQSP1

M_A_DQSN2

M_A_DQSP2

M_A_DQSN3

M_A_DQSP3

M_A_DQSN4

M_A_DQSP4

M_A_DQSN5

M_A_DQSP5

M_A_DQSN6

M_A_DQSP6

M_A_DQSN7

M_A_DQSP7

M_A_ALERT#

M_A_PARITY

TP63

M_A_CLKN0 15

M_A_CLKP0 15

M_A_CLKN1 15

M_A_CLKP1 15

M_A_CKE0 15

M_A_CKE1 15

M_A_CS#0 15

M_A_CS#1 15

M_A_ODT0_CPU 15

M_A_ODT1_CPU 15

M_A_A[13:0] 15

M_A_BG#1 15

M_A_ACT# 15

M_A_WE# 15

M_A_CAS# 15

M_A_RAS# 15

M_A_BA#0 15

M_A_BA#1 15

M_A_BG#0 15

M_A_DQSN[7:0] 15

M_A_DQSP[7:0] 15

M_A_ALERT# 15

M_A_PARITY 15

SM_VREF_CA 15

SM_VREF_DQ1 16

DDR_PG_CTRL 15

3

KabyLake ULT(DDR4)

M_B_DQ[63:0] 16

U1C

AF65

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

KBL_ULT/BGA

2

SKL_ULT

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

3 OF 20

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR1_PAR

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

BA46

AY46

AY47

BB46

BA47

AY48

BA48

AP48

BB48

AP50

AW46

AN48

AN50

BA43

AN52

AN53

AW44

AY43

AY44

BB44

BA44

AP52

AH66

AH65

AG6 9

AG7 0

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_ODT0_CPU

M_B_ODT1_CPU

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_BG#1

M_B_ACT#

M_B_RAS#

M_B_CAS#

M_B_WE#

M_B_BA#0

M_B_BA#1

M_B_BG#0

M_B_DQSN0

M_B_DQSP0

M_B_DQSN1

M_B_DQSP1

M_B_DQSN2

M_B_DQSP2

M_B_DQSN3

M_B_DQSP3

M_B_DQSN4

M_B_DQSP4

M_B_DQSN5

M_B_DQSP5

M_B_DQSN6

M_B_DQSP6

M_B_DQSN7

M_B_DQSP7

M_B_ALERT#

M_B_PARITY

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

1

M_B_CLKN0 16

M_B_CLKN1 16

M_B_CLKP0 16

M_B_CLKP1 16

M_B_CKE0 16

M_B_CKE1 16

M_B_CS#0 16

M_B_CS#1 16

M_B_ODT0_CPU 16

M_B_ODT1_CPU 16

M_B_A[13:0] 16

M_B_BG#1 16

M_B_ACT# 16

M_B_RAS# 16

M_B_CAS# 16

M_B_WE# 16

M_B_BA#0 16

M_B_BA#1 16

M_B_BG#0 16

M_B_DQSN[7:0] 16

M_B_DQSP[7:0] 16

M_B_ALERT# 16

M_B_PARITY 16

SM_DRAMRST# 16

R32 121/F_4

R33

1

R34 100/F_4

2

80.6/F_4

5

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

5

4

3

2

Tuesday, January 24, 2017

PROJECT :

KBL MCP(Memory)

KBL MCP(Memory)

KBL MCP(Memory)

1

FFK

FFK

FFK

5 38

5 38

5 38

3A

3A

3A

Page 6

5

4

3

2

1

6

U1S

E68

D D

+1.0V_S5

C C

B B

TP69

R35 49.9/F_4

R36 *1.5K/F_4

TP90

TP92

R515 *0_4_S

CFG0

CFG3

CFG4

CFG_RCOMP

AL25

AL27

BA70

BA68

B67

D65

D67

E70

C68

D68

C67

F71

G69

F70

G68

H70

G71

H69

G70

E63

F63

E66

F66

E60

AY2

AY1

K46

K45

C71

B70

F60

A52

F65

G65

F61

E61

E8

D1

D3

J71

J68

CFG[0 ]

CFG[1 ]

CFG[2 ]

CFG[3 ]

CFG[4 ]

CFG[5 ]

CFG[6 ]

CFG[7 ]

CFG[8 ]

CFG[9 ]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMODE

RSVD_AY2

RSVD_AY1

1

RSVD_D1

RSVD_D3

RSVD_K46

RSVD_K45

RSVD_AL25

RSVD_AL27

RSVD_C71

RSVD_B70

RSVD_F60

RSVD_A52

RSVD_TP_BA70

RSVD_TP_BA68

RSVD_J71

RSVD_J68

VSS_F65

VSS_G65

RSVD_F61

RSVD_E61

KBL_ULT/BGA

SKL_ULT

RESERVED SIGNALS-1

19 OF 20

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

RSVD_BB2

RSVD_BA3

TP5

TP6

RSVD_D5

RSVD_D4

RSVD_B2

RSVD_C2

RSVD_B3

RSVD_A3

RSVD_AW1

RSVD_E1

RSVD_E2

RSVD_BA4

RSVD_BB4

RSVD_A4

RSVD_C4

TP4

RSVD_A69

RSVD_B69

RSVD_AY3

RSVD_D71

RSVD_C70

RSVD_C54

RSVD_D54

TP1

TP2

VSS_AY71

ZVM#

RSVD_TP_AW71

RSVD_TP_AW70

MSM#

PROC_SELECT#

BB68

BB69

AK13

AK12

BB2

BA3

AU5

AT5

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

BB5

A69

B69

AY3

D71

C70

C54

D54

AY4

BB3

AY71

AR56

AW71

AW70

AP56

C64

RSVD_AY3

VSS_AY71

MSM#_SEL

R37 *0_4

R38 *0_4_S

TP94

TP95

TP111

R39 100K/F_4

+1.0V_S5_VCCST

Processor Strapping

1 0

CFG0

EAR-STALL/NOT STALL RESET SEQUENCE

A A

AFTER PCU PLL IS LOCKED

CFG4

eDP

enable:

5

DISABLED

4

STALL(DEFAULT) NORMAL OPERATION; NO STALL

ENABLED

3

CFG0

CFG4

R40 *1K/F_4

R41 1K/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

2

Tuesday, January 24, 2017

PROJECT :

KBL MCP(CFG)

KBL MCP(CFG)

KBL MCP(CFG)

1

FFK

FFK

FFK

6 38

6 38

6 38

3A

3A

3A

Page 7

5

KabyLake ULT MCP(POWER-1)

R54

56_4

+VCC_CORE

+VCC_CORE

D D

C C

SVID ALERT

B B

Backside Cap(TOP

side)

C769 1U/6.3V/X5R_2_KEN

C770 1U/6.3V/X5R_2_KEN

C771 1U/6.3V/X5R_2_KEN

C772 1U/6.3V/X5R_2_KEN

C774 1U/6.3V/X5R_2_KEN

C775 1U/6.3V/X5R_2_KEN

C776 1U/6.3V/X5R_2_KEN

C777 1U/6.3V/X5R_2_KEN

C778 1U/6.3V/X5R_2_KEN

C779 1U/6.3V/X5R_2_KEN

C780 1U/6.3V/X5R_2_KEN

C782 1U/6.3V/X5R_2_KEN

C783 1U/6.3V/X5R_2_KEN

C784 1U/6.3V/X5R_2_KEN

C785 1U/6.3V/X5R_2_KEN

H_CPU_SVIDALRT_N

Backside Cap(TOP

side)

C3 1U/6.3V/X5R_2_KEN

C6 1U/6.3V/X5R_2_KEN

C10 1U/6.3V/X5R_2_KEN

C14 1U/6.3V/X5R_2_KEN

C20 1U/6.3V/X5R_2_KEN

C26 1U/6.3V/X5R_2_KEN

C32 1U/6.3V/X5R_2_KEN

C38 1U/6.3V/X5R_2_KEN

C44 1U/6.3V/X5R_2_KEN

C50 1U/6.3V/X5R_2_KEN

C55 1U/6.3V/X5R_2_KEN

C60 1U/6.3V/X5R_2_KEN

C64 1U/6.3V/X5R_2_KEN

C68 1U/6.3V/X5R_2_KEN

C71 1U/6.3V/X5R_2_KEN

C74 1U/6.3V/X5R_2_KEN

C77 1U/6.3V/X5R_2_KEN

C80 1U/6.3V/X5R_2_KEN

close to CPU

R56 220_4

+1.0V_S5_VCCST

KabyLake ULT:22 15W IccMax :29A

SKL_ULT

U1L

VCC_A30

VCC_A34

VCC_A39

VCC_A44

VCC_AK33

VCC_AK35

VCC_AK37

VCC_AK38

VCC_AK40

VCC_AL33

VCC_AL37

VCC_AL40

VCC_AM32

VCC_AM33

VCC_AM35

VCC_AM37

VCC_AM38

VCC_G30

RSVD_K32

RSVD_AK32

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCC_OPC_1P8_H63

VCC_OPC_1P8_G61

1

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

KBL_ULT/BGA

CPU POWER 1 OF 4

A30

A34

A39

A44

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

K32

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

C131

0.1U/10V/X7R_4_KEN

4

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

? ?12 OF 20

VR_SVID_ALERT# 31

+VCC_CORE

C768 22U/6.3V/X5R_6_KEN

G32

C4 22U/6.3V/X5R_6_KEN

G33

C7 22U/6.3V/X5R_6_KEN

G35

C15 22U/6.3V/X5R_6_KEN

G37

C27 22U/6.3V/X5R_6_KEN

G38

C39 22U/6.3V/X5R_6_KENC773 1U/6.3V/X5R_2_KEN

G40

C45 22U/6.3V/X5R_6_KEN

G42

C766 22U/6.3V/X5R_6_KEN

J30

C767 22U/6.3V/X5R_6_KEN

J33

C46 10U/6.3V/X5R_4_KEN

J37

C69 10U/6.3V/X5R_4_KEN

J40

C81 10U/6.3V/X5R_4_KEN

K33

C40 10U/6.3V/X5R_4_KEN

K35

C51 10U/6.3V/X5R_4_KEN

K37

C12 10U/6.3V/X5R_4_KEN

K38

C61 10U/6.3V/X5R_4_KEN

K40

K42

K43

R42 100/F_4

E32

E33

R43 100/F_4

B63

H_CPU_SVIDALRT_N

A63

VR_SVID_CLK_R

D64

VR_SVID_DATA_R

G20

Backside

Cap(TOP

side)

+VCC_CORE

+1.0V_VCCSTG

Primary Cap(BOT side)

EC24 3.3P/50V/C0G_4_KEN

C49 47U/6.3V/X5R_8_KEN

C43 47U/6.3V/X5R_8_KEN

C2 47U/6.3V/X5R_8_KEN

C67 47U/6.3V/X5R_8_KEN

C59 47U/6.3V/X5R_8_KEN

Backside Cap(TOP

side)

C19 47U/6.3V/X5R_8_KEN

C25 47U/6.3V/X5R_8_KEN

C63 47U/6.3V/X5R_8_KEN

+VCC_CORE

Primary Cap(BOT side)

EC39 3.3P/50V/C0G_4_KEN

C8 10U/6.3V/X5R_4_KEN

C56 10U/6.3V/X5R_4_KEN

C22 10U/6.3V/X5R_4_KEN

C28 10U/6.3V/X5R_4_KEN

C34 10U/6.3V/X5R_4_KEN

C65 10U/6.3V/X5R_4_KEN

C72 10U/6.3V/X5R_4_KEN

VCC_SENSE 31

VSS_SENSE 31

+VCC_CORE

+VCC_CORE

3

Backside Cap(TOP

side)

C17 1U/6.3V/X5R_2_KEN

C23 1U/6.3V/X5R_2_KEN

C29 1U/6.3V/X5R_2_KEN

C35 1U/6.3V/X5R_2_KEN

C41 1U/6.3V/X5R_2_KEN

C47 1U/6.3V/X5R_2_KEN

C52 1U/6.3V/X5R_2_KENC78 10U/6.3V/X5R_4_KEN

C57 1U/6.3V/X5R_2_KEN

C62 1U/6.3V/X5R_2_KEN

C66 1U/6.3V/X5R_2_KENC781 1U/6.3V/X5R_2_KEN

C70 1U/6.3V/X5R_2_KEN

C73 1U/6.3V/X5R_2_KEN

C76 1U/6.3V/X5R_2_KEN

C79 1U/6.3V/X5R_2_KEN

C82 10U/6.3V/X5R_4_KEN

C83 10U/6.3V/X5R_4_KEN

C84 10U/6.3V/X5R_4_KEN

C109 10U/6.3V/X5R_4_KEN

C99 10U/6.3V/X5R_4_KEN

C87 10U/6.3V/X5R_4_KEN

C88 10U/6.3V/X5R_4_KEN

C90 10U/6.3V/X5R_4_KEN

C92 10U/6.3V/X5R_4_KEN

C93 10U/6.3V/X5R_4_KEN

C94 10U/6.3V/X5R_4_KEN

C96 10U/6.3V/X5R_4_KEN

Backside Cap(TOP

side)

C36 22U/6.3V/X5R_6_KEN

C48 22U/6.3V/X5R_6_KEN

C53 *22U/6.3V/X5R_6_KEN

C58 22U/6.3V/X5R_6_KEN

C114 22U/6.3V/X5R_6_KEN

C119 *22U/6.3V/X5R_6_KEN

C120 *22U/6.3V/X5R_6_KEN

C126 *22U/6.3V/X5R_6_KEN

Primary Cap(BOT side)

C127 22U/6.3V/X5R_6_KEN

C42 22U/6.3V/X5R_6_KEN

C124 *22U/6.3V/X5R_6_KEN

C118 22U/6.3V/X5R_6_KEN

VCCGFX_SENSE

VSSGFX_SENSE

VCCGFX_SENSE

VSSGFX_SENSE

+VCC_GFX

VCCGFX_SENSE31

VSSGFX_SENSE31

R55 100/F_4

R57 100/F_4

2

+VCC_GFX : 22 15W IccMax :31A

+VCC_GFX +VCC_GFX

?

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

?13 OF 20

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

A48

A53

A58

A62

A66

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M6 2

N63

N64

N66

N67

N69

J70

J69

SKL_ULT

U1M

CPU POWER 2 OF 4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

KBL_ULT/BGA

1

Backside Cap(TOP

side)

EC40 *3.3P/50V/C0G_4_KEN

C18 *47U/6.3V/X5R_8_KEN

C24 *47U/6.3V/X5R_8_KEN

C105 *47U/6.3V/X5R_8_KEN

C110 47U/6.3V/X5R_8_KEN

C112 47U/6.3V/X5R_8_KEN

Primary Cap(BOT side)

C30 *47U/6.3V/X5R_8_KEN

C102 47U/6.3V/X5R_8_KEN

C108 *47U/6.3V/X5R_8_KEN

7

SVID DATA

close to CPU close to VR PU1

+1.0V_S5_VCCST

+1.0V_S5_VCCST

R60

100/F_4

VR_SVID_DATA_R

SVID CLK

A A

VR_SVID_CLK_R

R423 *0_4_S

close to CPU

R471

*54.9_4

R424 *0_4_S

C132

0.1U/10V/X7R_4_KEN

5

R61

100/F_4

close to VR PU1

+1.0V_S5_VCCST+1.0V_S5_VCCST

R62

45.3_4

C133

0.1U/10V/X7R_4_KEN

C134

0.1U/10V/X7R_4_KEN

VR_SVID_DATA 31

VR_SVID_CLK 31

4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

3

2

Tuesday, January 24, 2017

PROJECT :

KBL MCP(Power-1)

KBL MCP(Power-1)

KBL MCP(Power-1)

FFK

FFK

FFK

7 38

7 38

1

7 38

3A

3A

3A

Page 8

5

4

3

2

1

KabyLake ULT MCP(POWER-2)

D D

C C

+1.2V_SUS_VDDQC

(+1.0V_S5_VCCST 0.12A)

(+1.0V_VCCSTG 0.04A)

(+1.2V_SUS_VCCPLL_OC 0.26A)

(+1.0V_S5_VCCPLL 0.12A)

C758 1U/6.3V/X5R_2_KEN

Backside Cap(TOP side)

C135 10U/6.3V/X5R_4_KEN

C137 10U/6.3V/X5R_4_KEN

C140 1U/6.3V/X5R_2_KEN

C143 1U/6.3V/X5R_2_KEN

C147 1U/6.3V/X5R_2_KEN

C151 1U/6.3V/X5R_2_KEN

+1.2V_SUS

+1.0V_S5

+1.0V_VCCIO

+1.2V_SUS

+1.0V_S5

(VDDQ : 2.8A)

EC25 3.3P/50V/C0G_4_KEN

+1.2V_SUS+1.2V_SUS

C141 10U/6.3V/X5R_4_KEN

C144 10U/6.3V/X5R_4_KEN

C148 10U/6.3V/X5R_4_KEN

C152 10U/6.3V/X5R_4_KEN

C731 22U/6.3V/X5R_6_KEN

C732 22U/6.3V/X5R_6_KEN

C745 22U/6.3V/X5R_6_KEN

C156 10U/6.3V/X5R_4_KEN

R63 *0_4S

C159 1U/6.3V/X5R_4_KEN

R64 *0_4

C162 1U/6.3V/X5R_2_KEN

R65 *0_4S

C167 1U/6.3V/X5R_2_KEN

R66 *0_4S

R68 *0_4

C175 1U/6.3V/X5R_4_KEN

+1.2V_SUS_VDDQC

+1.0V_S5_VCCST

+1.0V_S5_VCCST

+1.0V_VCCSTG

+1.2V_SUS_VCCPLL_OC

+1.0V_S5_VCCPLL

+1.0V_VCCSTG

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

A18

A22

AL23

K20

K21

SKL_ULT

U1N

CPU POWER 3 OF 4

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

KBL_ULT/BGA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

(+VCCIO : 3.1A)

+1.0V_VCCIO

?

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

?14 OF 20

+VCCSA

Backside Cap(TOP side)

EC26 3.3P/50V/C0G_4_KEN

C136 10U/6.3V/X5R_4_KEN

C138 10U/6.3V/X5R_4_KEN

C145 1U/6.3V/X5R_2_KEN

C149 1U/6.3V/X5R_2_KEN

C153 1U/6.3V/X5R_2_KEN

C154 1U/6.3V/X5R_2_KEN

(+VCCSA : 5.1A)

C155 10U/6.3V/X5R_4_KEN

C157 10U/6.3V/X5R_4_KEN

C160 10U/6.3V/X5R_4_KEN

C165 10U/6.3V/X5R_4_KEN

C174 10U/6.3V/X5R_4_KEN

C169 1U/6.3V/X5R_2_KEN

C171 1U/6.3V/X5R_2_KEN

C173 1U/6.3V/X5R_2_KEN

C176 1U/6.3V/X5R_2_KEN

C177 1U/6.3V/X5R_2_KEN

C178 1U/6.3V/X5R_2_KEN

C179 1U/6.3V/X5R_2_KEN

Backside

Cap

VSSSA_SENSE 31

VCCSA_SENSE 31

R71 100/F_4

R72 100/F_4

VCCSA_SENSE

VSSSA_SENSE

+1.0V_VCCIO

+VCCSA

+VCCSA

Backside Cap(TOP side)Backside Cap(TOP side)

C139 1U/6.3V/X5R_2_KEN

C142 1U/6.3V/X5R_2_KEN

C146 1U/6.3V/X5R_2_KEN

C150 1U/6.3V/X5R_2_KEN

Primary Cap

C158 10U/6.3V/X5R_4_KEN

C166 10U/6.3V/X5R_4_KEN

C168 10U/6.3V/X5R_4_KEN

C170 10U/6.3V/X5R_4_KEN

C163 10U/6.3V/X5R_4_KEN

C161 10U/6.3V/X5R_4_KEN

C172 10U/6.3V/X5R_4_KEN

C164 10U/6.3V/X5R_4_KEN

8

B B

A A

For Debug mode:+1.0V_VCCSTG will use +3V_S5 power rail

R514 *XDP@0_4

5

+1.0V_VCCSTG

For Load switch <=65usec full load ready

+1.0V_SUS_VCCST+1.0V_S5

4

R472 *0_4S

R473 *0_4S

+1.0V_S5_VCCST

+1.0V_S5_VCCPLL

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

3

2

Tuesday, January 24, 2017

PROJECT :

KBL PCH(Power-2)

KBL PCH(Power-2)

KBL PCH(Power-2)

1

FFK

FFK

FFK

8 38

8 38

8 38

3A

3A

3A

Page 9

5

CLK_PCIE_CRDN19

Card Reader

D D

WiFi/BT(NGFF)

LAN

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

C C

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

CLK_PCIE_CRDP19

PCIE_CLK_REQ0#19

CLK_PCIE_WIFIN21

CLK_PCIE_WIFIP21

PCIE_CLK_REQ2#21

CLK_PCIE_LANN24

CLK_PCIE_LANP24

PCIE_CLK_REQ3#24

R425 10K/F_4

R426 *10K/F_4

R427 10K/F_4

R428 10K/F_4

R429 *10K/F_4

R430 *10K/F_4

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

+3V

+3V

+3V

+3V

+3V

+3V

D42

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

AR10

GPP_B5/SRCCLKREQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/SRCCLKREQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/SRCCLKREQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/SRCCLKREQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/SRCCLKREQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10/SRCCLKREQ5#

4

KabyLake ULT (RTC/CLK)

SKL_ULT

CLOCK SIGNALS

+3V

+3V

+3V

+3V

+3V

+3V

?

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

SRTCRST#

U1J

KBL_ULT/BGA

RTCX1

RTCX2

RTCRST#

?10 OF 20 1

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

3

SUSCLK

SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTC_X1

RTC_X2

SRTC_RST#

RTC_RST#

SUSCLK 21

TP98

R75 2.7K/F_4

R73

1M/F_4

SRTC_RST#

C180 10P/50V/C0G_4_KEN

4

3

Y1

24MHz(7V24000007)

1

2

C181 10P/50V/C0G_4_KEN

+1.0V_S5

D74

*PESD5V0U1BB

2

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

U1I

CSI-2

CSI2_DN0

CSI2_ DP0

CSI2_DN1

CSI2_ DP1

CSI2_DN2

CSI2_ DP2

CSI2_DN3

CSI2_ DP3

CSI2_DN4

CSI2_ DP4

CSI2_DN5

CSI2_ DP5

CSI2_DN6

CSI2_ DP6

CSI2_DN7

CSI2_ DP7

CSI2_DN8

CSI2_ DP8

CSI2_DN9

CSI2_ DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

KBL_ULT/BGA

1

SKL_ULT

?

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

?9 OF 20

1

C37

D37

C32

D32

C29

D29

B26

A26

E13

R74 100/F_4

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

R76 200/F_4

9

C185

1 2

Q3

3

12

J1

*SHORT_ PAD1

*LU1L002SNFS8(SOT323)

2

EC_RCT_RST

1

R81

*100K/F_4

EC_RTC_RST 20

C182

15P/50V/C0G_4_KEN

C183

15P/50V/C0G_4_KEN

B B

12

Y2

32.768KHZ(9H03200042)

RTC_X1

R78

10M_4

RTC_X2

+3V_RTC

R529 2.7K/F_4 R79 20K/F_4

+3VPCU

R530

45.3K/F_4

RTC_3V

20MIL

R82

1K/F_4

20MIL

12

CON1

AAA-BAT-054-K01>1700day

D1

BAT54CW

1U/6.3V/X5R_4_KEN

C186

RTC Power trace width 20mils.

RTC_RST#

R80 20K/F_4

1U/6.3V/X5R_4_KEN

SRTC_RST#

C184

1U/6.3V/X5R_4_KEN

PCH Strap Table

Pin Name Strap description

A A

HDA_SDO

Flash Descriptor Security

Override / Intel ME Debug

Mode

5

Sampled

PWROK

Configuration note

0 = Security Effect (Int PD)

1 = Can be Override

4

+3V_S5

R84 *1K/F_4

ACZ_SDOUT_R

3

ACZ_SDOUT_R 11,20

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

2

Tuesday, January 24, 2017

PROJECT :

KBL PCH(RTC/CLK)

KBL PCH(RTC/CLK)

KBL PCH(RTC/CLK)

1

FFK

FFK

FFK

9 38

9 38

9 38

3A

3A

3A

Page 10

5

PCIE_RXN124

PCIE_RXP124

LAN

D D

WiFi/BT NGFF

Card Reader

HDD

ODD

C C

PCIE_TXN124

PCIE_RXN321

PCIE_RXN419

SATA_RXN 018

SATA_RXP 018

SATA_TXN018

SATA_TXP018

SATA_RXN 118

SATA_RXP 118

SATA_TXN118

SATA_TXP118

TP118

TP119

PCIE_TXP124

PCIE_RXP321

PCIE_TXN321

PCIE_RXP419

PCIE_TXN419

PCIE_TXP321

PCIE_TXP419

+3V

R91 100/F_4

R92 10K/F_4

PCIE_RCOMPN

PCIE_RCOMPP

4

H13

G13

B17

A17

G11

F11

D16

C16

H16

G16

D17

C17

G15

F15

B19

A19

F16

E16

C19

D19

G18

F18

D20

C20

F20

E20

B21

21

A

G21

F21

D21

C21

E22

E23

B23

A23

F25

E25

D23

C23

F5

E5

D56

D61

BB11

E28

E27

D24

C24

E30

F30

A25

B25

KabyLake ULT (PCIE,USB)

?

U1H

PCIE/USB3/SATA

PCIE1_RXN/USB3_5_RXN

PCIE1_RXP/USB3_5_RXP

PCIE1_TXN/USB3_5_TXN

PCIE1_TXP/USB3_5_TXP

PCIE2_RXN/USB3_6_RXN

PCIE2_RXP/USB3_6_RXP

PCIE2_TXN/USB3_6_TXN

PCIE2_TXP/USB3_6_TXP

PCIE3_RXN

PCIE3_RXP

PCIE3_TXN

PCIE3_TXP

PCIE4_RXN

PCIE4_RXP

PCIE4_TXN

PCIE4_TXP

PCIE5_RXN

PCIE5_RXP

PCIE5_TXN

PCIE5_TXP

PCIE6_RXN

PCIE6_RXP

PCIE6_TXN

1

PCIE6_TXP

PCIE7_RXN/SATA0_RXN

PCIE7_R XP/SATA0_RXP

PCIE7_TXN/SATA0_TXN

PCIE7_TXP/SATA0_TXP

PCIE8_RXN/SATA1A_RXN

PCIE8_R XP/SATA1A_RXP

PCIE8_T XN/SATA1A_TXN

PCIE8_T XP/SATA1A_TXP

PCIE9_RXN

PCIE9_RXP

PCIE9_TXN

PCIE9_TXP

PCIE10_RXN

PCIE10_RXP

PCIE10_TXN

PCIE10_TXP

PCIE_RCOMPN

PCIE_RCOMPP

PROC_PRDY#

PROC_PREQ#

GPP_A7/PIRQA#

PCIE11_RXN/SATA1B_RXN

PCIE11_RXP/SATA1B_RXP

PCIE11_TXN/SATA1B_TXN

PCIE11_TXP/SATA1B_TXP

PCIE12_RXN/SATA2_RXN

PCIE12_RXP/SATA2_RXP

PCIE12_TXN/SATA2_TXN

PCIE12_TXP/SATA2_TXP

KBL_ULT/BGA

SKL_ULT

SSIC / USB3

USB2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

3

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

?8 OF 20

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB1 0

AD6

AD7

AH3

AJ3

AD9

AD1 0

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB_BIAS

USB_OTG_ID

VBUS_SENSE

USB_OC0#

USB_OC1#

USB_OC2#

USB3_RX1- 25

USB3_RX1+ 25

USB3_TX1- 25

USB3_TX1+ 25

USB3_RX2- 25

USB3_RX2+ 25

USB3_TX2- 25

USB3_TX2+ 25

USB3_RX3- 26

USB3_RX3+ 26

USB3_TX3- 26

USB3_TX3+ 26

USBP1- 25

USBP1+ 25

USBP2- 25

USBP2+ 25

USBP3- 26

USBP3+ 26

USBP4- 21

USBP4+ 21

USBP5- 17

USBP5+ 17

R90 113/F_4

2

USB3.0 Port 1

USB3.0 Port 2

USB3.0 Port 3

USB3.0 Port 1

USB3.0 Port 2

USB3.0 Port 3 Right side

WLAN/BT NGFF

CAMERA

USB_OC0# 25

USB_OC1# 25

USB_OC2# 26

USB_OTG_ID

VBUS_SENSE

R86 *100K/F_4

R87 1K/F_4

R88 *100K_4

R89 1K/F_4

USB_OC1#

USB_OC2#

USB_OC0#

1

R404 10K/F_4

R405 10K/F_4

R406 10K/F_4

10

+3V_S5

+3V_S5

+3V_S5

B B

PCI_PLTRST#

SYS_RESET#

RSMRST#20

1 2

+3V_S5

D46

*PESD5V0U1BB

VCCST_PWRGD

R486 *0_4

PLTRST# 19,20,21,24

EC_PWROK20

1 2

A A

PCI_PLTRST#

R114

100K/F_4

2

1

C201 220P/50V_4

C202 220P/50V_4

D49

*PESD5V0U1BB

+3V_S5

C203 0.1U/10V/X7R_4_KEN

4

U2

3 5

TC7SH08FU

5

R112

100K/F_4

PCIE_WAKE#19,21,24

RSMRST#

TP104

R104 59/F_4

PCH_PWROK_EC

EC_PWROK

DPWROK_R

SUSWARN#

SUSACK#

PCIE_WAKE#

R107 20K/F_4

GDP2

4

U1K

AN1 0

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR1 3

GPP_A13/SUSWARN#/SUSPWRDNACK

AP1 1

GPP_A15/SUSACK#

BB15

WAKE#

AM1 5

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT1 5

GPD7/RSVD

KBL_ULT/BGA

PCH_PWROK_EC_R20

SYSTEM POWER MANAGEMENT

SKL_ULT

+3V

R761 *0_4S

?

+3V

GPP_B12/SLP_S0#

GPD10/SLP_S5#

GPD9/SLP_WLAN#

DSW

GPD3/PWRBTN#

GPD1/ACPRESENT

DSW

GPD0/BATLOW#

DSW

GPP_A11/PME#

+3V

GPP_B11/EXT_PWR_GATE#

GPP_B2/VRALERT#

PCH_PWROK_EC

3

GPD4/SLP_S3#

GPD5/SLP_S4#

SLP_SUS#

SLP_LAN#

GPD6/SLP_A#

INTRUDER#

?11 OF 201

AT1 1

AP1 5

BA16

AY16

AN1 5

AW15

BB17

AN1 6

BA15

AY15

AU1 3

AU1 1

AP1 6

AM1 0

AM1 1

TP103

TP113

DNBSWON#

AC_PRESENT

PM_BATLOW#

SM_INTRUDER#

EXT_PWR_GATE#

PCH_CORE_HOT#

RSMRST#

DPWROK_R

RSMRST#

PCH_PWROK_EC

EC_PWROK

TP100

TP102

TP101

TP107

R106 1M/F_4

R117 *0_4S

C205 *220P/50V/COG_4

+3V_RTC

R115 *100K/F_4

R118 10K/F_4

R120 *10K_4

R121 10K/F_4

2

SLP_S3# 20,33

SLP_S4# 20

SLP_S5# 20

DNBSWON# 20

AC_PRESENT 20

PM_BATLOW# 20

DPWROK_R

KabyLake ULT (SYSTEM POWER MANAGEMENT)

PCH Pull-high/low(CLG)

DNBSWON#

PCIE_WAKE#

AC_PRESENT

PM_BATLOW#

SUSWARN#

VR_ ON20,31

C597

0.01U/25V/X7R_4_KEN

SYS_RESET#

EXT_PWR_GATE#

PCH_CORE_HOT#

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

R556 10K/F_4

R101 1K/F_4

R102 10K/F_4

R103 10K/F_4

R105 10K/F_4

R410

10K/F_4

6

2

5

Q18

1

4 3

2N7002KDW

R110 10K/F_4

R111 20K/F_4

R113 10K/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

KBL PCH(PCIE/USB/SPM)

KBL PCH(PCIE/USB/SPM)

KBL PCH(PCIE/USB/SPM)

FFK

FFK

FFK

1

+3V_S5

+1.0V_S5_VCCST+3V_S5

VCCST_PWRGD

C598

*10P/50V_4

+3V_S5

+3V_S5

+3V_S5

10 38

10 38

10 38

+3V_S5

R411

1K/F_4

D45

1 2

3A

3A

3A

*PESD5V0U1BB

Page 11

5

Put damping resistor close to CPU

C206

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK10

AW5

J5

AK7

AK6

AK9

H5

D7

D8

C8

ACZ_SYNC23

ACZ_BITCLK23

ACZ_SDOUT_R9,20

ACZ_SDOUT23

D D

ACZ_SDIN023

ACZ_RST#20,23

ACZ_BITCLK

C1205

22P/50V/NPO_4_KEN

R122 33_4

R123 33_4

R124 33_4

R127 33_4

HDA_SYNC_C

HDA_BITCLK_C

ACZ_SDOUT_R

HDA_RST#_C

SPKR

*100P/50V/X7R_4

4

KabyLake ULT (HDA/SDXC)

1.8V

1.8V

1.8V

1.8V

3.3V/1.8V

3.3V/1.8V

3.3V/1.8V

3.3V/1.8V

SKL_ULT

3.3V/1.8V

3.3V/1.8V

7 OF 20

3.3V/1.8V

GPP_A17/SD_PWR_EN#/ISH_GP7

U1G

AUDIO

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

GPP_D23/I2S_MCLK

I2S1_SFRM

I2S1_TXD

GPP_F1/I2S2_SFRM

GPP_F0/I2S2_SCLK

GPP_F2/I2S2_TXD

GPP_F3/I2S2_RXD

GPP_D19/DMIC_CLK0

GPP_D20/DMIC_DATA0

GPP_D17/DMIC_CLK1

GPP_D18/DMIC_DATA1

GPP_B14/SPKR

KBL_ULT/BGA

3.3V/1.8V

SDIO/SDXC

GPP_A16/SD_1P8_SEL

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

SD_RCOMP

GPP_F23

1.8V

3

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

SD_RCOMP

R129 200/F_4

AF13

2

GPPC5: ESPI or LPC SEL

HIGH: ESPI interface

LOW: LPC interface(default)INT DN

R125 20K/F_4

CLKRUN#

EC_RCIN#

GPPB23

SERIRQ#

1

GPPC5

R126 *10K/F_4

R136 8.2K_4

R134 10K/F_4

R133 150K_4

R135 10K/F_4

11

+3V_S5

+3V

+3V

KabyLake ULT (LPC/SPI/SMB/CLINK)

3.3V/1.8V

SPI FLASH

U3

1

CE#

6

SCK

5

SI

2

SO

3

WP#

W25Q64FVSSIQ

SKL_ULT

SMBUS, SMLINK

3.3V/1.8V

3.3V/1.8V

LP C

3.3V/1.8V

3.3V/1.8V

3.3V/1.8V

3.3V/1.8V

VDD

HOLD#

VSS

GPP_B23/SML1ALERT#/PCHHOT#

3.3V/1.8V

3.3V/1.8V

3.3V/1.8V

3.3V/1.8V

5 OF 20

TP need place to TOP

TP30

TP31

TP32

TP33

TP34

TP35

+3V_S5

C220 0.1U/10V/X7R_4_KEN

8

7

HOLD#

4

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

PCH_SPI_CS0#

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_WP#

HOLD#

R159 1K/F_4

1 2

R162 22/F_4

Size

AKE3EZN0Z00 (MX25L6473EM2I-10G)

8MB

AKE3EFP0N07 (W25Q64FVSSIQ)

DFHS08FS023

4

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A8/CLKRUN#

PCH_SPI_IO3

R7

R8

R10

R9

W2

W1

W3

V3

AM7

SMB_PCH_CLK

SMB_PCH_DAT

GPPC2

GPPC5

SMB_ME1_CLK

SMB_ME1_DAT

GPPB23

SPD

EC

Put damping resistor close to CPU

AY13

LPC_AD0-0

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

+3V_S5

LPC_AD0-1

LPC_AD0-2

LPC_AD0-3

LPC_FRAME

TP108

LPC_CLK_0

LPC_CLK_1

CLKRUN#

R140 33/J_4

R141 33/J_4

R143 33/J_4

R144 33/J_4

R421 33/J_4

1 2

R146 22/F_4

R147 33/J_4

56P/50V/NPO_4_KEN

GPPC2

C212

R157 10K/F_4

LPC_AD0 20,21

LPC_AD1 20,21

LPC_AD2 20,21

LPC_AD3 20,21

LPC_FRAME# 20,21

TLS CONFIDENTIALITY STRAP(GPP_C2)

DefaultNC

PU EN

SPKR

SPKR/GPP_B14

PU

Disable(Default)

PD

internal week pull-down

R166 *10K/F_4

Top-Block Swap

Enable

3

CLK_PCI_EC 20

CLK_PCI_LPC 21

C213

22P/50V/NPO_4_KEN

+3V

C207 *22P/50V/NPO_4

+3V_S5

R138 2.2K_4

R142 2.2K_4

C209 *22P/50V/NPO_4

ES2-21

2

SMB_PCH_CLK

SMB_PCH_DAT

C215 *0.1U/10V/X7R_4

MBCLK220

C217 *22P/50V/NPO_4

MBDATA220

C218 *22P/50V/NPO_4

close to KU1

SMBus/Pull-up(CLG)

close to CON3

Q4

5

2

6

2N7002KDW

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

R137 4.7K_4

43

1

5

2

6

*2N7002KDW

SMB_RUN_CLK 15,16,18

C208 *22P/50V/NPO_4

R139 4.7K_4

SMB_RUN_DAT 15,16,18

C210 *22P/50V/NPO_4

Q6

R154 2.2K_4

43

SMB_ME1_CLK

C216 *22P/50V/NPO_4

R155 2.2K_4

1

SMB_ME1_DAT

C219 *22P/50V/NPO_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

KBL PCH(HDA/LPC/SPI/SMB)

KBL PCH(HDA/LPC/SPI/SMB)

KBL PCH(HDA/LPC/SPI/SMB)

1

+3V+3V

+3V+3V

FFK

FFK

FFK

11 38

11 38

11 38

+3V_S5+3V_S5

+3V_S5

3A

3A

3A

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

M2

M3

J4

V1

V2

M1

G3

G2

G1

AW13

AY11

1 2

1 2

1 2

1 2

U1E

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

KBL_ULT/BGA

+3V_S5

R156

*10K/F_4

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

+3V_S5

3.3V/1.8V 3.3V/1.8V

3.3V/1.8V

Put damping resistor close to CPU

C C

PCH_SPI_CLK

PCH_SPI_SO

PCH_SPI_SI

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CS0#

EC_RCIN#20

SERIRQ#20

B B

EC_RCIN#

SERIRQ#

close to CPU

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2 PCH_SPI_WP#

SPI_WP_PCH#20

A A

R158 22/F_4

R160 22/F_4

R161 22/F_4

R163 22/F_4

+3V_S5

PCH_SPI_SI

R164 1K/F_4

R165 *0_4

R516 1K/F_4

Vender P/N

MACRONIX

Winbond 8MB

Socket

5

Page 12

5

4

3

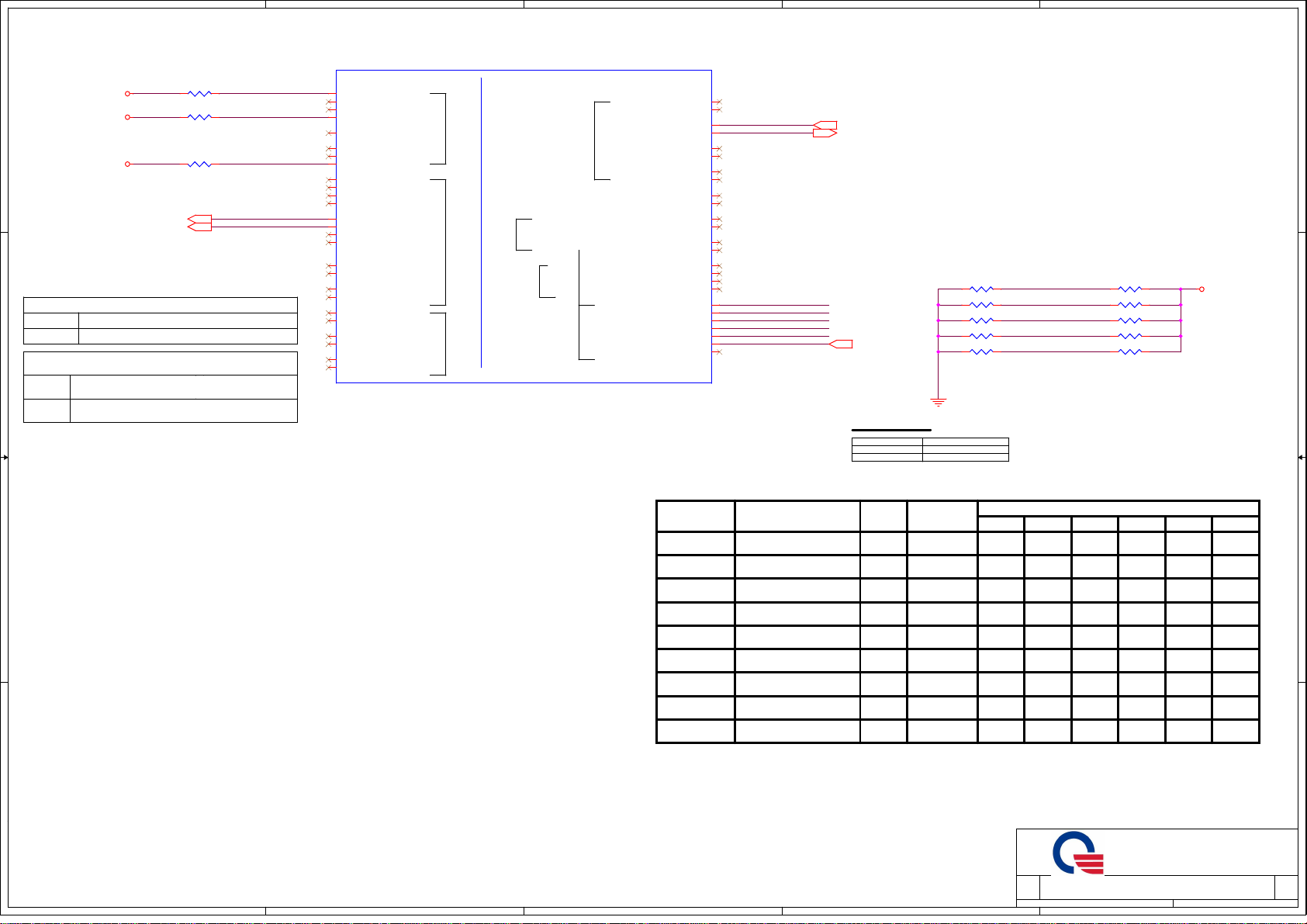

KabyLake ULT(GPIO,LPIO,MISC)

2

1

12

U1F

LPSS IS H

GPPB18

GPP_B22

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

KBL_ULT/BGA

+3V

D D

+3V

+3V

R167 *4.7K_4

R171 *10K/F_4

R177 *1K/F_4

UART0_RXD25

UART0_TXD25

GPP_B22(Boot BIOS)

PUPDLPC

C C

SPI (Default IPD)

No Reboot Strap(GPP_B18)

NC

PU

B B

Default

EN

SKL_ULT

P2

GPP_D9

P3

GPP_D10

P4

GPP_D11

P1

3.3V

3.3V

3.3V

1

3.3V

1.8V

6 OF 20

3.3V

1.8V

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

1.8V

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

?

3.3V

GPP_A12/BM_BUSY#/ISH_GP6

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

INT_TP# 18

USB_UART_SEL 25

Panel_ID 17

GPIO Pull-up/Pull-down(CLG)

R566 *10K_4

R235 10K_4

R565 10K_4 R240 *10K_4

R241 10K_4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

R234 10K_4

R568 *10K_4

R567 *10K_4R569 10K_4

R564 *10K_4

+3V

PANEL ID

PANEL_ID

Project

FusionK-H

FusionK-H

FusionK-L

Celeron

Pentium/I3/I5/I7

Celeron

H

L

LAN

GLAN

GLAN

100M

Web CameraCPU BGA

2 DMIC

2 DMIC

1 DMIC

HD

FHD

BOARD_ID4

0

0

MB ID

0

0

BOARD_ID1BOARD_ID2BOARD_ID3

0

0

BOARD_ID0

0000

0

1

1

00

FusionK-H

FusionK-H

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

5

4

3

2

Tuesday, January 24, 2017

PROJECT :

KBL PCH(GPIO/UART/I2S)

KBL PCH(GPIO/UART/I2S)

KBL PCH(GPIO/UART/I2S)

1

FFK

FFK

FFK

12 38

12 38

12 38

3A

3A

3A

Page 13

5

4

3

2

1

C602 0.1U/10V/X7R_4_KEN

+1.0V_S5

+1.0V_S5

D D

+1.0V_S5

+1.0V_S5

R493 *0_6_S

+1.0V_S5

+1.0V_S5

+3V_S5

+3V_S5

C C

+3V_S5

+1.0V_S5

+3V_S5

+1.0V_S5

+1.0V_S5

R494 *0_6_S

(0.7A)

(+PCH_CORE_S5 2.57A)

(0.022A)

(+1.0V_S5_MPHY 2.766A)

(0.088A)

(0.026A)

+3V_S5_DSW 0.118A)

(0.068A)

(0.011A)

(0.642A)

(0.075A)

(0.033A)

C221 1U/6.3V/X5R_2_KEN

C603 10U/6.3V/X5R_4_KEN

C604 10U/6.3V/X5R_4_KEN

C222 1U/6.3V/X5R_2_KEN

C605 0.1U/10V/X7R_4_KEN

C223 1U/6.3V/X5R_4_KEN

C226 1U/6.3V/X5R_2_KEN

C229 1U/6.3V/X5R_2_KEN

C606 22U/6.3V/X5R_6_KEN

C607 22U/6.3V/X5R_6_KEN

C612 *22U/6.3V/X5R_6_KEN

C233 1U/6.3V/X5R_4_KEN

C608 0.1U/10V/X7R_4_KEN

C235 *47U/6.3V/X5R_8_KEN

C236 0.1U/10V/X7R_4_KEN

C609 0.1U/10V/X7R_4_KEN

C239 1U/6.3V/X5R_2_KEN

VCCAMPHYPLL

C240 0.1U/10V/X7R_4_KEN

C241 0.1U/10V/X7R_4_KEN

C242 *1U/6.3V/X5R_2_KEN

C243 *0.1u/10V/X5R_4_KEN

C244 0.1U/10V/X7R_4_KEN

C245 0.1U/10V/X7R_4_KEN

C246 1U/6.3V/X5R_2_KEN

C610 0.1U/10V/X7R_4_KEN

TP109

VCCAPLL

U1O

AB19

VCCPRIM_1P0

AB20

VCCPRIM_1P0

P18

VCCPRIM_1P0

AF18

VCCPRIM_CORE

AF19

VCCPRIM_CORE

V20

VCCPRIM_CORE

V21

VCCPRIM_CORE

AL1

DCPDSW_1P0

K17

VCCMPHYAON_1P0

L1

VCCMPHYAON_1P0

N15

VCCMPHYGT_1P0_N15

N16

VCCMPHYGT_1P0_N16

N17

VCCMPHYGT_1P0_N17

P15

VCCMPHYGT_1P0_P15

P16

VCCMPHYGT_1P0_P16

K15

VCCAMPHYPLL_1P0

L15

VCCAMPHYPLL_1P0

V15

VCCAPLL_1P0

AB17

VCCPRIM_1P0_AB17

Y18

VCCPRIM_1P0_Y18

AD17

VCCDSW_3P3_AD17

AD18

VCCDSW_3P3_AD18

AJ17

VCCDSW_3P3_AJ17

AJ19

VCCHDA

AJ16

VCCSPI

AF20

VCCSRAM_1P0

AF21

VCCSRAM_1P0

T19

VCCSRAM_1P0

T20

VCCSRAM_1P0

AJ21

VCCPRIM_3P3_AJ21

AK20

VCCPRIM_1P0_AK20

N18

VCCAPLLEBB

KBL_ULT/BGA

SKL_ULT

CPU POWER 4 OF 4

VCCPGPPA

+3V

VCCPGPPB

VCCPGPPC

VCCPGPPD

VCCPGPPE

VCCPGPPF

VCCPGPPG

VCCPRIM_3P3_V19

VCCPRIM_1P0_T1

VCCATS_1P8

VCCRTCPRIM_3P3

VCCRTC_AK19

VCCRTC_BB14

DCPRTC

VCCCLK1

VCCCLK2

VCCCLK3

VCCCLK4

VCCCLK5

VCCCLK6

GPP_B0/CORE_VID0

GPP_B1/CORE_VID1

15 OF 20

AK15

+3V_S5_VCCPGPPA

AG1 5

+3V_S5_VCCPGPPB

Y16

+3V_S5_VCCPGPPC

Y15

+3V_S5_VCCPGPPD

T16

+3V_S5_VCCPGPPE

AF16

AD15

+3V_S5_VCCPGPPG

C224 0.1U/10V/X7R_4_KEN

V19

C225 0.1U/10V/X7R_4_KEN

T1

C227 0.1U/10V/X7R_4_KEN

AA1

C228 0.1U/10V/X7R_4_KEN

AK17

C741 1U/6.3V/X5R_2_KEN

AK19

BB14

C232 0.1U/10V/X7R_4_KEN

C747 1U/6.3V/X5R_2_KEN

BB10

C234 0.1U/10V/X7R_4_KEN

A14

+1.0V_S5_VCCCLK1

K19

+1.0V_S5_VCCCLK2

L21

+1.0V_S5_VCCCLK3

N20

+1.0V_S5_VCCCLK4

L19

+1.0V_S5_VCCCLK5

A10

+1.0V_S5_VCCCLK6

AN11

AN13

R189 *0_4S

R190 *0_4S

R191 *0_4S

R192 *0_4S

R193 *0_4S

R195 *0_4S

R197 *0_6_S

C237 0.1U/10V/X7R_4_KEN

C622 22U/6.3V/X5R_6_KEN

R483 *0_6_S

C238 1U/6.3V/X5R_4_KEN

C623 22U/6.3V/X5R_6_KEN

C614 22U/6.3V/X5R_6_KEN

R484 *0_6_S

C613 1U/6.3V/X5R_4_KEN

TP116

TP117

(0.02A)

(0.04A)

(0.06A)

(0.08A)

(0.06A)

(0.161A)

+1.8V_S5

(0.041A)

+3V_S5

+3V_S5

+1.0V_S5

(0.068A)

+1.8V_S5

+3V_S5

+3V_RTC

(<0.001A)

+1.0V_S5_VCCCLK2

+1.0V_S5_VCCCLK4

+1.0V_S5_VCCCLK5

VCCAMPHYPLL

+3V_S5_VCCPGPPB

+3V_S5

+3V_S5_VCCPGPPC

+3V_S5_VCCPGPPE

+3V_S5_VCCPGPPA

+3V_S5_VCCPGPPD

+3V_S5_VCCPGPPG

R485 *0_6_S

R491 *0_6_S

R492 *0_6_S

C759 22U/6.3V/X5R_6_KEN

C760 22U/6.3V/X5R_6_KEN

C761 22U/6.3V/X5R_6_KEN

C762 22U/6.3V/X5R_6_KEN

C742 1U/6.3V/X5R_2_KEN

C743 1U/6.3V/X5R_2_KEN

C744 1U/6.3V/X5R_2_KEN

C763 1U/6.3V/X5R_2_KEN

C764 1U/6.3V/X5R_2_KEN

C765 1U/6.3V/X5R_2_KEN

(0.035A)

(0.029A)

(0.024A)

(0.033A)

(0.004A)

(0.010A)

13

+1.0V_S5

+1.0V_S5

+1.0V_S5

+1.0V_S5

+1.0V_S5

+1.0V_S5

B B

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

Tuesday, January 24, 2017

Date: Sheet of

5

4

3

2

Tuesday, January 24, 2017

PROJECT :

KBL PCH(Power)

KBL PCH(Power)

KBL PCH(Power)

1

FFK

FFK

FFK

13 38

13 38

13 38

3A

3A

3A

Page 14

5

4

3

2

1

14

D D

SKL_ULT

AT63

VSS

AT68

VSS

AT71

VSS

AU10

VSS

AU15

VSS

AU20

VSS

AU32

VSS

AU38

VSS

AV1

VSS

AV68

VSS

AV69

VSS

AV70

VSS

AV71

VSS

AW10

VSS

AW12

VSS

AW14

VSS

AW16

VSS

C C

B B

A A

AW18

AW21

AW23

AW26

AW28

AW30

AW32

AW34

AW36

AW38

AW41

AW43

AW45

AW47

AW49

AW51

AW53

AW55

AW57

AW6

AW60

AW62

AW64

AW66

AW8