Page 1

1

2

3

4

5

6

7

8

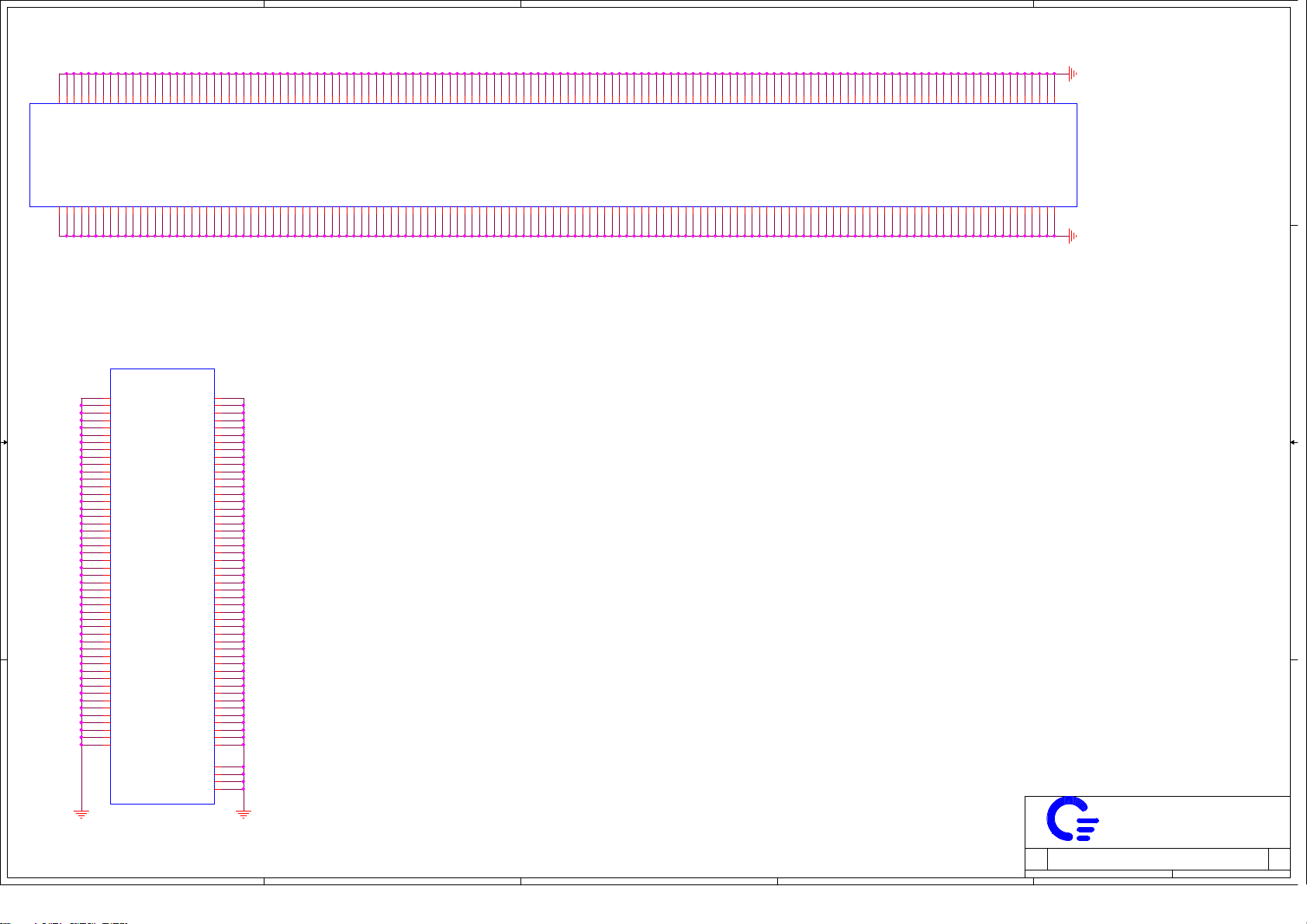

Daughter

Board

01

VCC_CORE

GMCH_CORE

A A

VCC1.1

VCC1.2

VCC1.5

1.5VSUS

VCC3

3V_STBY

VCC5

SATA - HDD(2.5)

5V_STBY

+12V

B B

BT KB/Mouse

Page 27

C C

SATA - HDD(3.5)

SATA - ODD

Page 22

Page 22

Page 22

eSATA

Page 22

WLAN

Page 25

Camera

Page 19

Bluetooth

Page 26

USB*4(Rear)

Page 27

TV

Page 25

USB*2(Side)

Page 26

Touch Screen

Page 27

USB-10

USB-1

USB-2

USB-6,7

8,9

USB-11

USB-3,5

USB-0

SATA 4

SATA 1

SATA 2

SATA 3

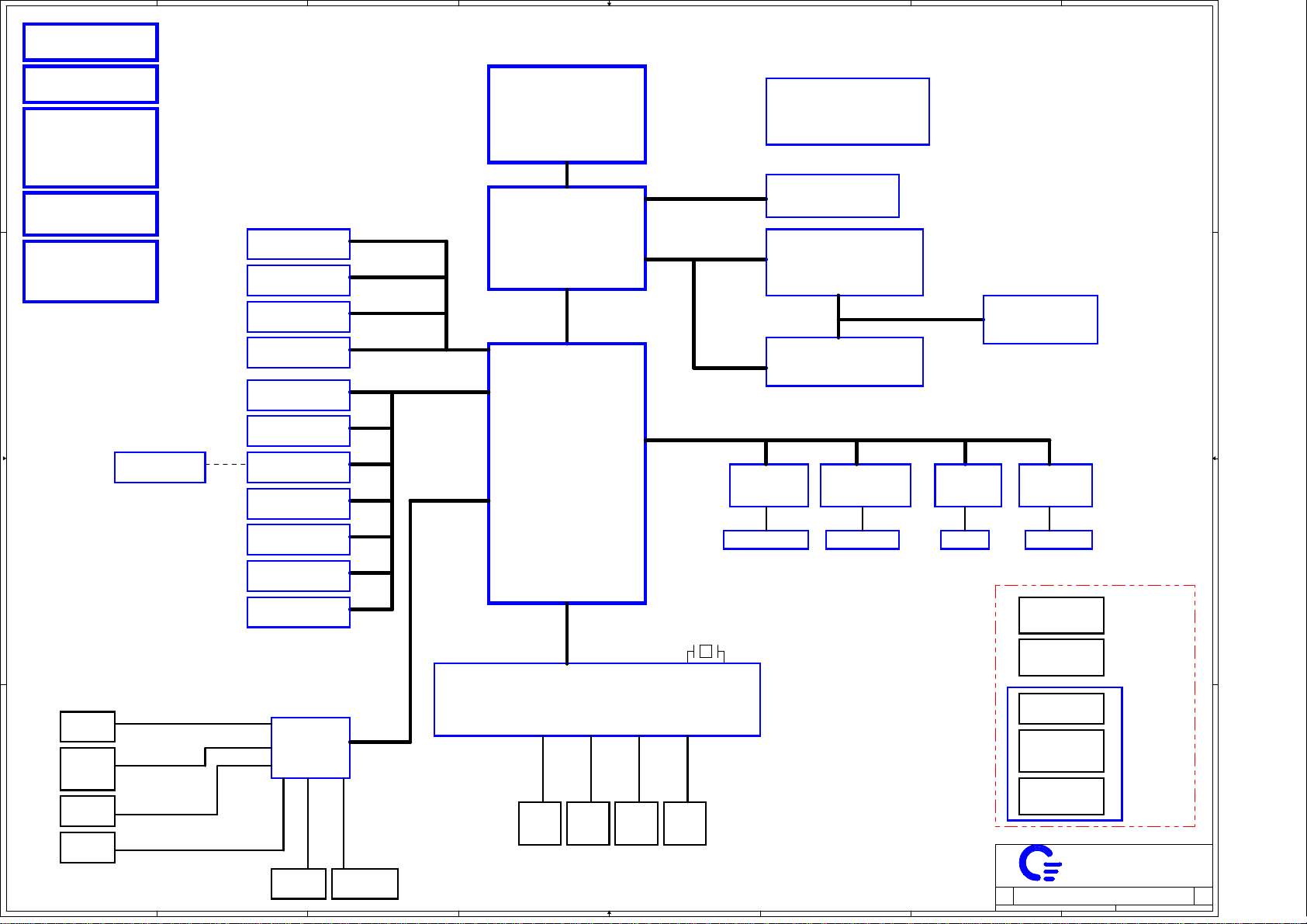

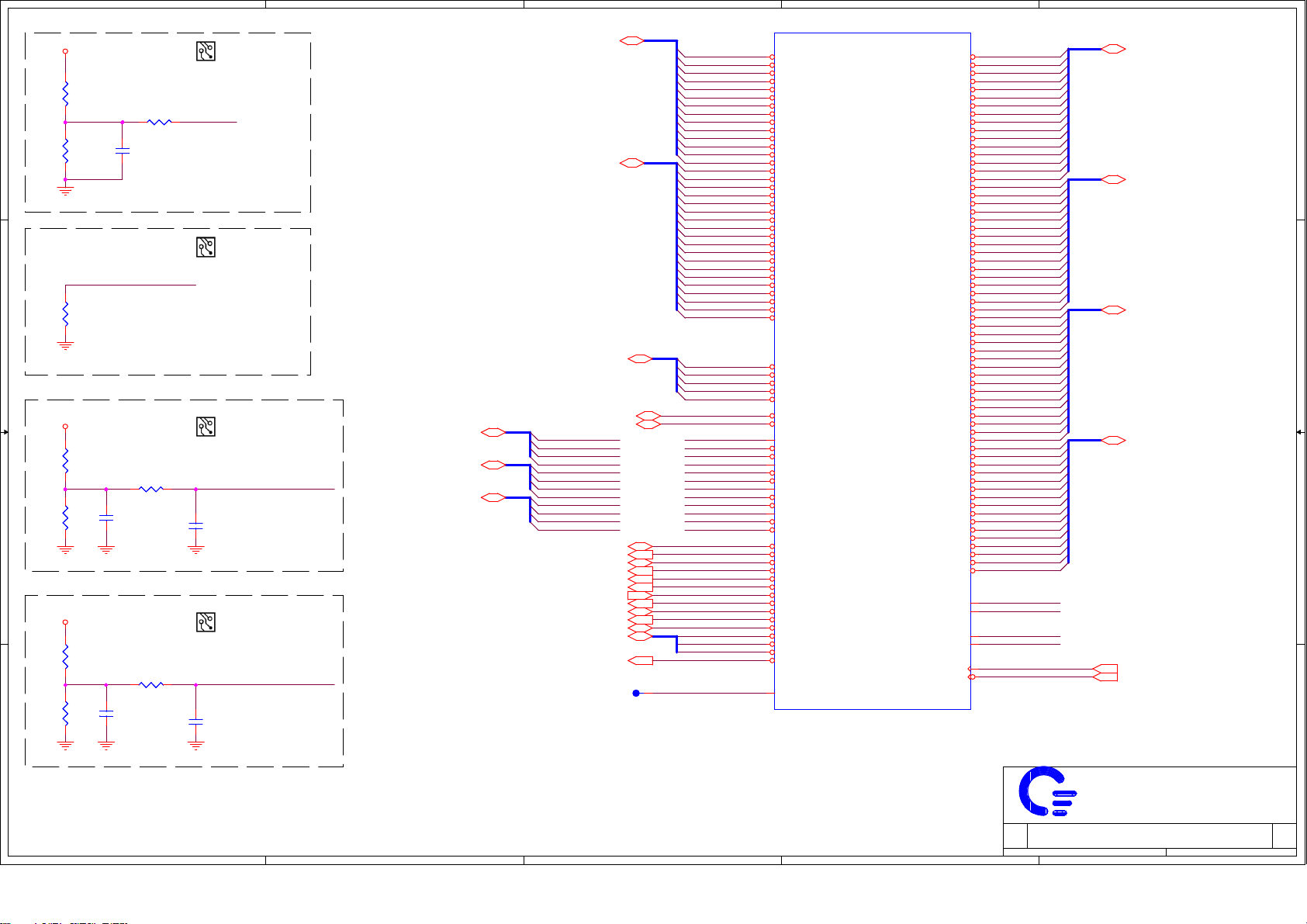

EL8 Block Diagram

Intel

Yorkfield/Wolfdale

Q9000/E8000

USB 2.0

Azalia

LGA775

NB

Eaglelake

G45/P43

1254 pin

SB

ICH10

676 pin

LPC

Page 3,4

FSB(800/1067/1333HZ)

Page 5,7,8,9

DMI

Page 10,11,12,13

800/1067 MHZ DDR III

PCI-E 2.0 16X

SDVO

PCI-Express 1X

PCIE-2 PCIE-1

MINI CARD-1

WLAN

32.768KHz

CLOCK GENERATOR

CK505

CV193

CH A: DDRIII-UDIMM0/1

CH B: DDRIII-UDIMM0/1

Page 14,15,16,17

MXM CONNECTOR

LVDS

LVDS Transmitter

CH7308B

PCIE-3

MINI CARD-2

Page 25

TV card

TV antennaWLAN antenna

Page 25

Page 2

Page 18

Page 19

LAN

RTL8111DL

Page 26

RJ45

LCD PANEL

23" Full HD

PCIE-4

Card Reader

JMB385

Page 27

Media Slot

MXM module

B-CAS board

314 pin

10 pin

ITE8512

HP

Page 30

MIC IN

Page 30

D D

INT SPK

Page 29

DMIC IN

Page 30

AUDIO CODEC

ALC888S-VC2

Page 29

IR

Blaster

Page 3

FAN

Page 26

FLASH

ROM

Page 28 Page 28

CIR

LINE IN 5.1 Channel

1

2

3

4

Page 26

5

6

Card Reader

20 pin

HP/MIC

Light SW

10 pin

Power button

LED

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

TBD

PROJECT : EL8

PROJECT : EL8

Quanta Computer Inc.

Quanta Computer Inc.

1 34Monday, March 09, 2009

1 34Monday, March 09, 2009

1 34Monday, March 09, 2009

8

1A

1A

1A

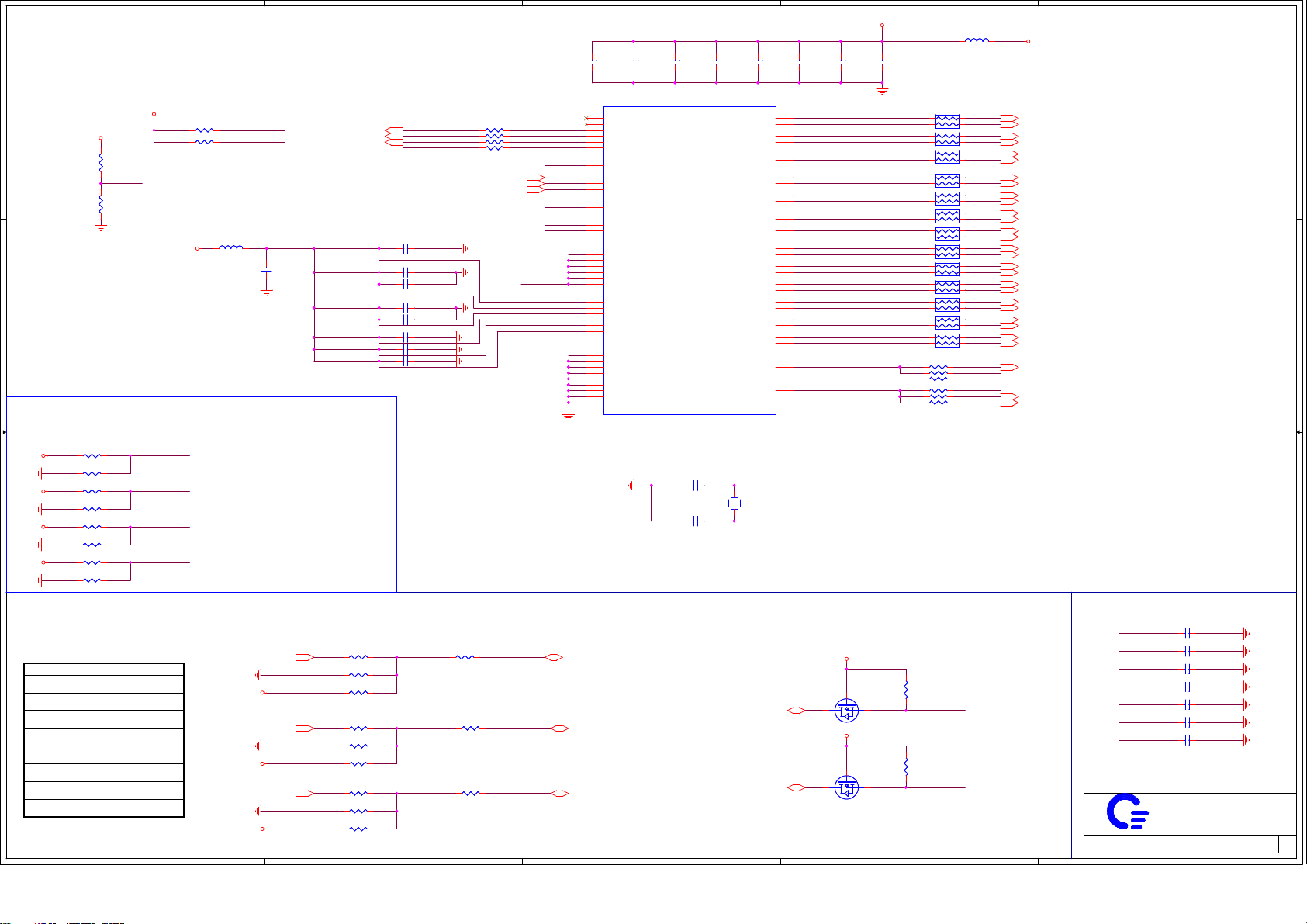

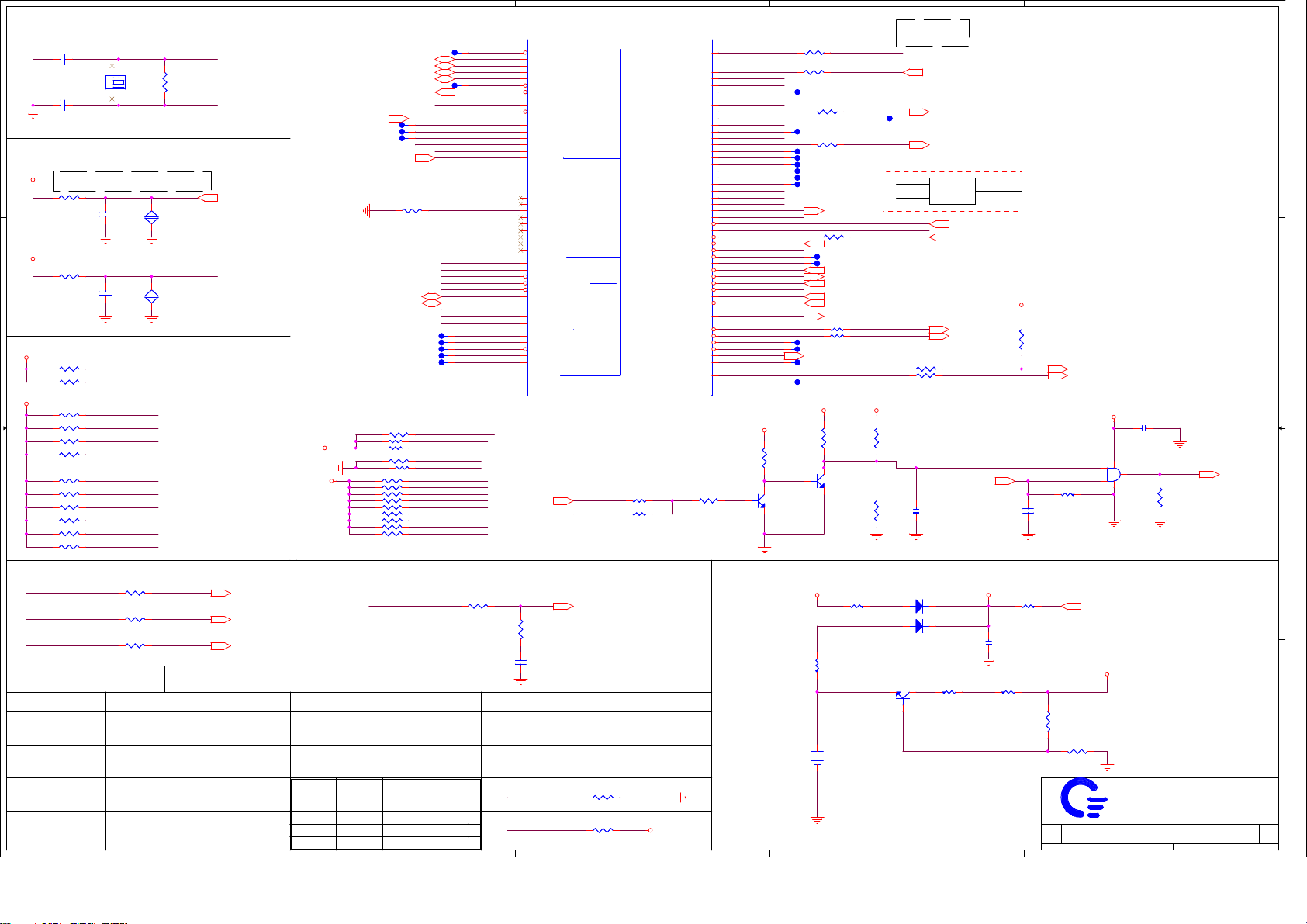

Page 2

5

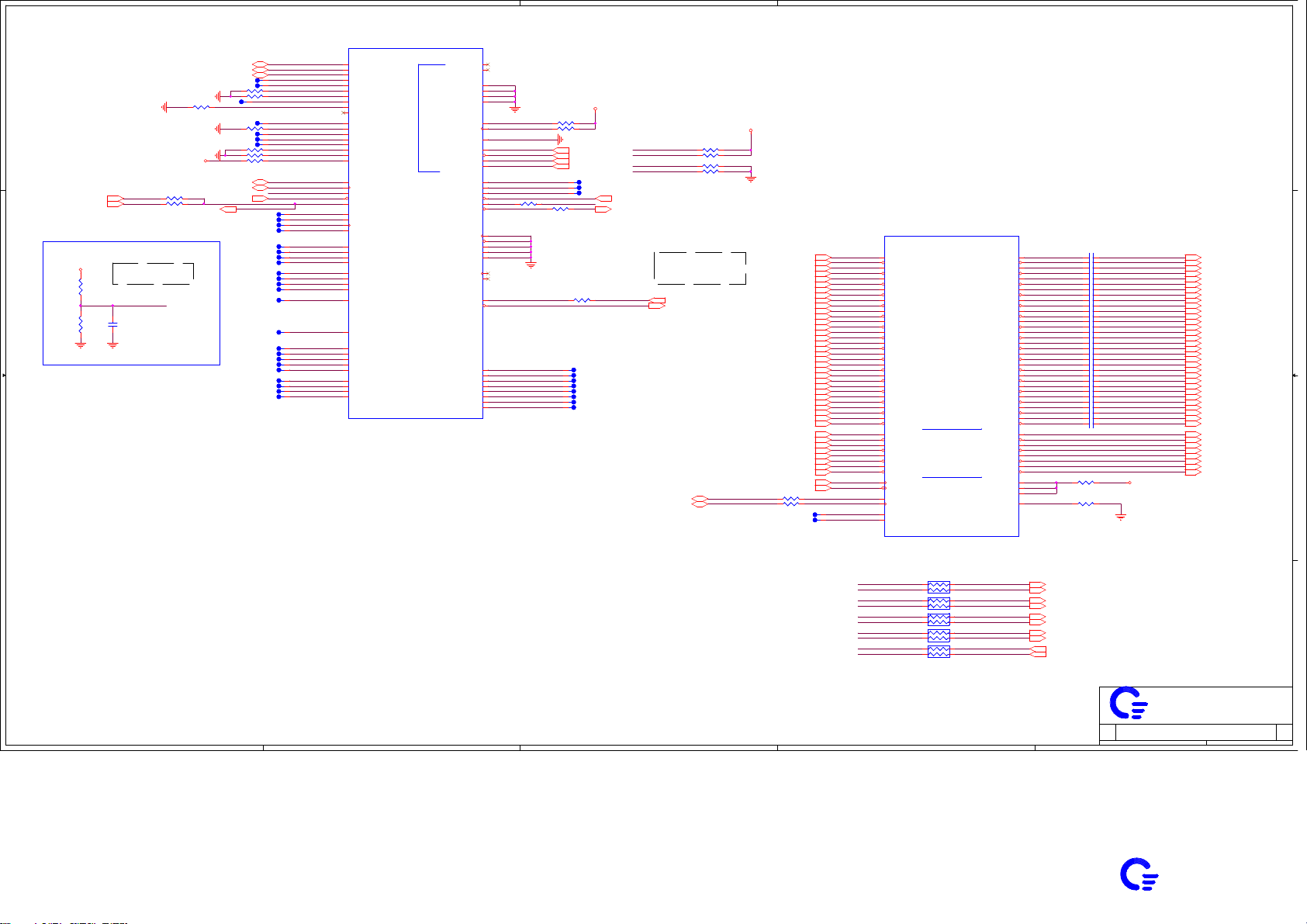

Clock Generator

D D

VCC3

C C

Strap Configuration

VCC3

R7

1K/J_4R71K/J_4

SEL_SRC1

Pin17-18. SRC1 enabled

R8

1K/J_4R81K/J_4

VCC3

PM_STPPCI#

R12.2K/J_4 R12.2K/J_4

PM_STPCPU#

R42.2K/J_4 R42.2K/J_4

L2 PBY16080 8T-301Y-N_6L2 PBY16080 8T-301Y-N_6

C10

C10

10u/10V_6

10u/10V_6

PCLK_DEB UG24

PCLK_EC26

PCLK_ICH11

4

R2 33/J_4R2 33/J_4

R3 33/J_4R3 33/J_4

PCLK_ICH PCLK_ICH_ R

R5 33/J_4R5 33/J_4

PCIF5_ITPEN

R6 33/J_4R6 33/J_4

C9 0.1u/10V _4C9 0.1u/10V _4

C11 0.1u/10V _4C11 0.1u/10V _4

C12 10u/10V_6C12 10u/10V_6

C13 0.1u/10V _4C13 0.1u/10V _4

C14 0.1u/10V _4C14 0.1u/10V _4

C15 0.1u/10V _4C15 0.1u/10V _4

C16 0.1u/10V _4C16 0.1u/10V _4

C17 0.1u/10V _4C17 0.1u/10V _4

PM_STPCPU#10

PM_STPPCI#10

CK_PWRGD10

PCLK_DEB UG_RPCLK_DEB UG

PCLK_EC_ RPCLK_EC

PCIF5_ITPEN_R

SEL_SRC1

PM_STPCPU#

PM_STPPCI#

CK_PWRGD

CGCLK_SMB

CGDAT_SMB

CG_XIN

CG_XOUT

VCC1.2_VDD

VDD_CK_VDD_PLL3

VDD_CK_VDD_PCI

VDD_CK_VDD_48

VDD_CK_VDD_REF

VDD_CK_VDD_CPU

VDD_CK_VDD_SRC

C1

*10u/10V _6C1*10u/10V _6

U1

U1

1

PCI0/CR#_A

3

PCI1/CR#_B

4

*PCI2/SR_ENABLE

5

**PCI3/SATA_SEL

6

PCI4/SRC5_EN

7

PCI_F5/ITP_EN

48

SEL_SRC1_25_24.576**

37

CPU_STOP#/SRCC5

38

PCI_STOP#/SRCT5

56

CKPWRGD/PD#

64

SCL

63

SDA

60

XTAL_IN

59

XTAL_OUT

12

VDDIO

20

VDDPLL3IO

26

VDDSRCIO

36

VDDSRCIO

45

VDDSRCIO

49

VDDCPUIO

16

VDDPLL3

2

VDDPCI

9

VDD48

61

VDDREF

55

VDDCPU

39

VDDSRC

42

GNDSRC

52

GNDCPU

23

GNDSRC

19

GND

15

GND

11

GND48

8

GNDPCI

29

GNDSRC

58

GNDREF

CV193

CV193

3

C2

10u/10V_6C210u/10V_6

C3

0.1u/10V _4C30.1u/10V _4

SRCC1/25MHz1/24.576MHz

CK505

CK505

*Internal 100K Pull High

**Internal 100K Pull Low

C4

0.1u/10V _4C40.1u/10V _4

CPUT0

CPUC0

CPUT1

CPUC1

SRCT8/CPU_ITPT

SRCC8/CPU_ITPC

DOT96T/SRCT0

DOT96C/SRCC0

SRCT1/25MHz0

SRCT2/SATAT

SRCC2/SATAC

SRCT3/CR#_C

SRCC3/CR#_D

SRCT4

SRCC4

SRCT6

SRCC6

SRCT7/CR#_F

SRCC7/CR#_E

SRCT9

SRCC9

SRCT10

SRCC10

SRCT11/CR#_H

SRCC11/CR#_G

USB48/FS_A

FS_B/TESTMODE

REF/FS_C/TESTSEL

C5

0.1u/10V _4C50.1u/10V _4

C6

0.1u/10V _4C60.1u/10V _4

CLK_CPU_BCLK_R

54

CLK_CPU_BCLK#_R

53

CLK_MCH_B CLK_R

51

CLK_MCH_B CLK#_R

50

XDP_DCLKOUT_DP_R

47

XDP_DCLKOUT_DN_R

46

DREFCLK_R

13

DREFCLK#_ R

14

DREFSSCLK _R

17

DREFSSCLK #_R

18

CLK_PCIE_SATA_R

21

CLK_PCIE_SATA#_R

22

MXM_PEGCLK_R

24

MXM_PEGCLK#_R

25

CLK_PCIE_EXP_R

27

CLK_PCIE_EXP#_R

28

CLK_PCIE_ICH_R

41

CLK_PCIE_ICH#_R

40

CLK_PCIE_LAN_R

44

CLK_PCIE_LAN#_R

43

CLK_PCIE_MINI_R

30

CLK_PCIE_MINI#_R

31

CLK_PCIE_MINI2_R

34

CLK_PCIE_MINI2#_R

35

CLK_PCIE_JMB385_ R

33

CLK_PCIE_JMB385# _R

32

10

57

62

2

VCC1.2_VDD

C8

C7

0.1u/10V _4C80.1u/10V _4

0.1u/10V _4C70.1u/10V _4

RP1 0X2RP1 0X2

RP2 0X2RP2 0X2

RP3 0X2RP3 0X2

RP4 IV@0X2RP4 IV@0X2

RP5 IV@0X2RP5 IV@0X2

RP6 0X2RP6 0X2

RP7 EV@0X2RP7 EV@0X2

RP8 0X2RP8 0X2

RP9 0X2RP9 0X2

RP10 0X2RP10 0X2

RP11 0X2RP11 0X2

RP12 0X2RP12 0X2

RP13 0X2RP13 0X2

FSA

FSB CLK_BSEL1

FSC CLK_BSEL2

2

1

4

3

2

1

4

3

2

1

4

3

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

2

1

4

3

2

1

4

3

4

3

2

1

4

3

2

1

2

1

4

3

R933 /J_4 R933/J_4

CLK_BSEL0

R101K /J_4 R101K/J_4

R111K/J_4 R111K/J_4

R121K /J_4 R121K/J_4

R1322 /J_4 R1322/J_4

R151IV@*22/J_4 R151IV@*22/J_4

L1PBY16080 8T-301Y-N_6 L1PBY16080 8T-301Y-N_6

VCC1.2

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

CLK_MCH_B CLK 5

CLK_MCH_B CLK# 5

XDP_DCLKOUT_DP 3

XDP_DCLKOUT_DN 3

DREFCLK 6

DREFCLK# 6

DREFSSCLK 6

DREFSSCLK # 6

CLK_PCIE_SATA 12

CLK_PCIE_SATA# 12

MXM_PEGCLK 18

MXM_PEGCLK# 18

CLK_PCIE_EXP 6

CLK_PCIE_EXP# 6

CLK_PCIE_ICH 11

CLK_PCIE_ICH# 11

CLK_PCIE_LAN 22

CLK_PCIE_LAN# 22

CLK_PCIE_MINI 24

CLK_PCIE_MINI# 24

CLK_PCIE_MINI2 24

CLK_PCIE_MINI2# 24

CLK_PCIE_JMB385 25

CLK_PCIE_JMB385# 25

CLKUSB_4 8 11

14M_ICH 10

14M_CH7308B 19

1

02

To CPU

To NB

To CPU

To NB

To NB

To SB

To MXM

To NB

To SB

To LAN

To WLAN

To TV

To Card Reader

R14 10K/J_4R14 10K/J_4

VCC3

R15 *10K/J_4R15 *10K/J_4

R16 *10K/J_4R16 *10K/J_4

VCC3

R17 10K/J_4R17 10K/J_4

R18 *10K/J_4R18 *10K/J_4

VCC3

B B

VCC3

R19 10K/J_4R19 10K/J_4

R20 10K/J_4R20 10K/J_4

R21 *10K/J_4R21 *10K/J_4

FREQ. SEL TABLE

BSEL Frequency Select Table

FSC FSB FSA Frequency

0

0

0

1

0

1

1

0

A A

1

1

1

1

0

1

101

0

001

1

0

PCLK_DEB UG_R

PCLK_EC_ R

PCLK_ICH_ R

PCIF5_ITPEN

266Mhz0

133Mhz

166Mhz

200Mhz

333Mhz

100Mhz

400Mhz

Reserved

5

Internal 33 ohm resistor enabled

SATA output from PLL2

CPUSTP#/PCISTP enabled

ITPCLK enabled

CPU_BSEL 03

VCC1.2

CPU_BSEL 13

VCC1.2

CPU_BSEL 23

VCC1.2

R22 0/J_4R22 0 /J_4

R24 *0/J_4R24 *0/J_4

R25 470/J_4R25 470/J_4

R27 0/J_4R27 0 /J_4

R29 *0/J_4R29 *0/J_4

R30 470/J_4R30 470/J_4

R32 0/J_4R32 0 /J_4

R34 *0/J_4R34 *0/J_4

R35 470/J_4R35 470/J_4

4

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

R23 0/J_4R23 0/J_4

R28 0/J_4R28 0 /J_4

R33 0/J_4R33 0 /J_4

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

MCH_BSEL0 6

MCH_BSEL1 6

MCH_BSEL2 6

C18 27p/50V_4C18 27p/50V_4

C19 27p/50V_4C19 27p/50V_4

Clock Gen I2C

3

CL=20p

21

CG_XIN

Y1

14.318MHZY114.318MHZ

CG_XOUT

PCIF5_ITPEN

C491 *10pC491 *10p

PCLK_EC

VCC3

Q1

2

RHU002N06Q1RHU002N06

SDATA10,14

SCLK10,14

3

VCC3

Q2

2

RHU002N06Q2RHU002N06

3

R26

R26

10K/J_4

10K/J_4

R31

R31

10K/J_4

10K/J_4

2

CGDAT_SMB

CGCLK_SMB

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CLK. GEN./ CK505

CLK. GEN./ CK505

CLK. GEN./ CK505

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1

C20 *10pC20 *10 p

CLKUSB_4 8

C21 *10pC21 *10 p

14M_ICH

C22 *10pC22 *10 p

PCLK_ICH

C23 *10pC23 *10 p

PCLK_DEB UG

C24 *22pC24 *22 p

14M_CH7308B

C492 *10pC492 *10p

PROJECT : EL8

PROJECT : EL8

Quanta Computer Inc.

Quanta Computer Inc.

1

1A

1A

2 34Monday, March 09 , 2009

2 34Monday, March 09 , 2009

2 34Monday, March 09 , 2009

1A

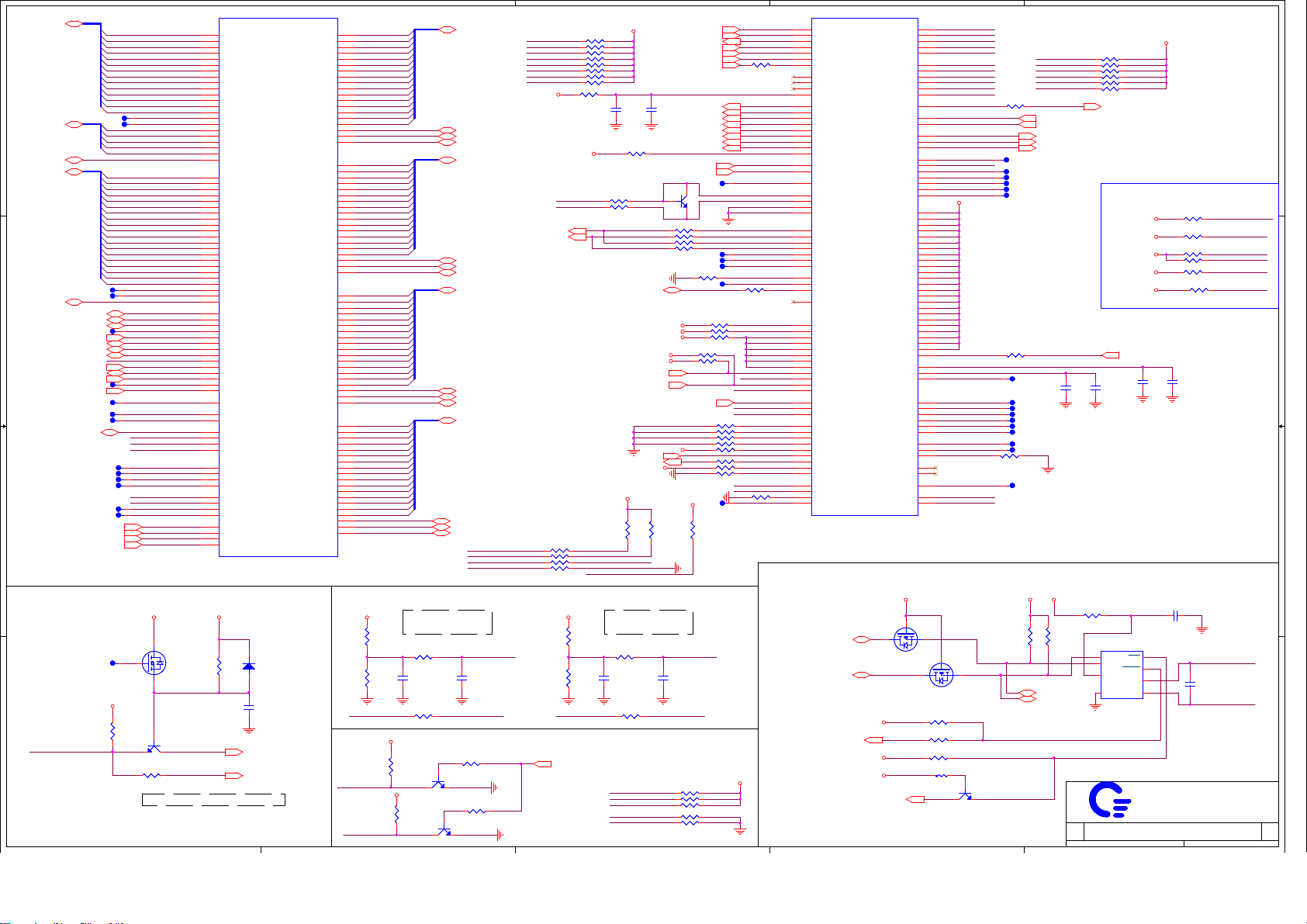

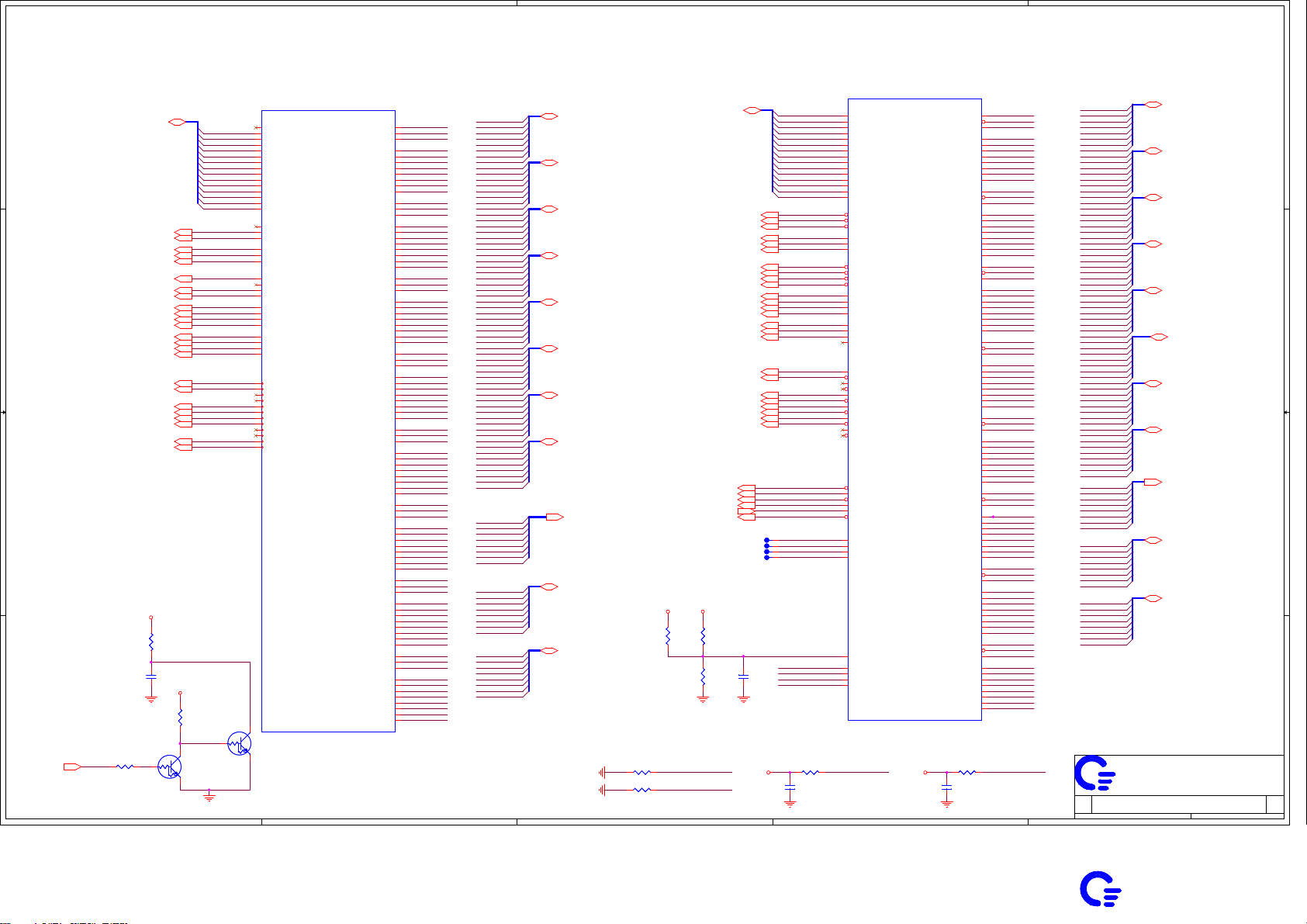

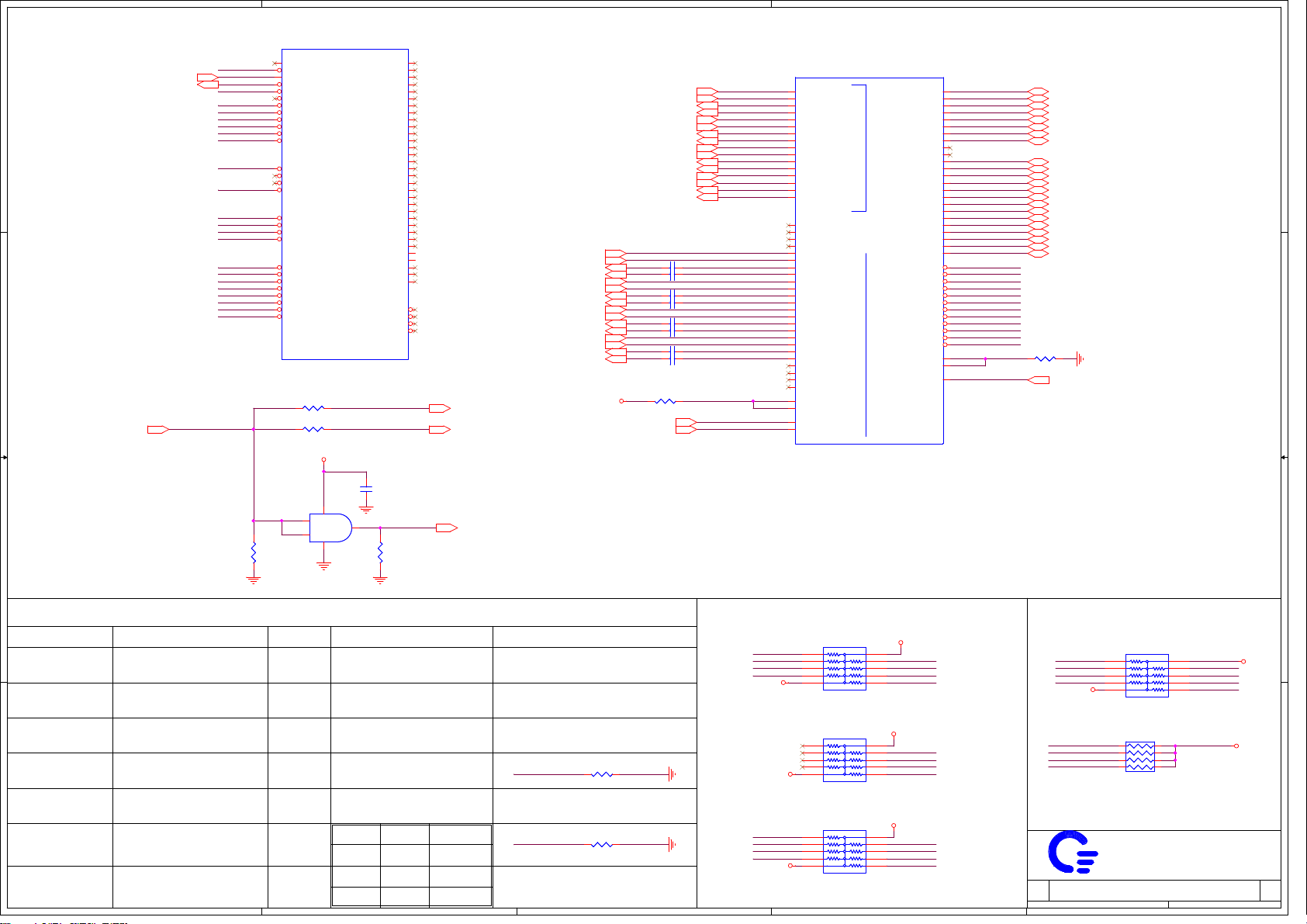

Page 3

5

H_A#[3..1 6]5

D D

H_REQ#[0..4]5

H_ADSTB#05

H_A#[17..35]5

H_ADSTB#15

C C

B B

H_ADS#5

H_BNR#5

H_BPRI#5

H_DBSY#5

H_DRDY#5

H_HITM#5

H_INIT#12

H_LOCK#5

H_TRDY#5

H_DEFER#5

H_BREQ#5

Thermal Trip

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

TP_LGA775_N4

T1T1

TP_LGA775_P5

T2T2

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

TP_LGA775_AC4

T14T14

TP_LGA775_AE5

T15T15

H_ADSTB#1

H_ADS#

H_BNR#

H_HIT#

H_HIT#5

TP_LGA775_H4

T16T16

H_BPRI#

H_DBSY#

H_DRDY#

H_HITM#

H_IERR#

H_INIT#

H_LOCK#

H_TRDY#

TP_LGA775_AD3

T18T18

H_DEFER#

TP_LGA775_AB3

T19T19

TP_LGA775_U2

T22T22

TP_LGA775_U3

T24T24

H_BREQ#

BPMb#3

BPMb#2

CPU_TEST10

TP_LGA775_J16

T30T30

TP_LGA775_H15

T31T31

TP_LGA775_H16

T32T32

TP_LGA775_J17

T33T33

CPU_GTLREF0

CPU_GTLREF1

TP_LGA775_E24

T36T36

TP_LGA775_H29

T37T37

H_CPURST#5

H_RS#05

H_RS#15

H_RS#25

VCC1.2

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

AB6

AA4

AD6

AA5

AB5

AC5

AB4

AF5

AF4

AG6

AG4

AG5

AH4

AH5

AJ5

AJ6

AC4

AE4

AD5

AB2

AD3

AB3

H15

H16

E24

H29

G23

L5

P6

M5

L4

M4

R4

T5

U6

T4

U5

U4

V5

V4

W5

N4

P5

K4

J5

M6

K6

J6

R6

W6

Y6

Y4

D2

C2

D4

H4

G8

B2

C1

E4

P3

C3

E3

G7

U2

U3

F3

G3

G4

H5

J16

J17

H1

H2

B3

F5

A3

VCC1.2

U2A

U2A

H_A3

H_A4

H_A5

H_A6

H_A7

H_A8

H_A9

H_A10

H_A11

H_A12

H_A13

H_A14

H_A15

H_A16

RSVD_0

RSVD_1

REQ_0

REQ_1

REQ_2

REQ_3

REQ_4

H_ADSTB_0

H_A17

H_A18

H_A19

H_A20

H_A21

H_A22

H_A23

H_A24

H_A25

H_A26

H_A27

H_A28

H_A29

H_A30

H_A31

H_A32

H_A33

H_A34

H_A35

RSVD_2

RSVD_3

H_ADSTB_1

ADS#

BNR#

HIT#

FC35

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

FC36

DEFER#

FC37

FC29

FC30

BR0#

BPMb#3

BPMb#2

TESTHI10

FC31

FC32

FC33

FC34

GTLREF0

GTLREF1

FC10

FC15

RESET#

RS0#

RS1#

RS2#

H_D0

H_D1

H_D2

H_D3

H_D4

H_D5

H_D6

H_D7

H_D8

H_D9

H_D10

H_D11

H_D12

H_D13

H_D14

H_D15

H_DSTBP0

H_DSTBN0

H_DINV0

H_D16

H_D17

H_D18

H_D19

H_D20

H_D21

H_D22

H_D23

H_D24

H_D25

H_D26

H_D27

H_D28

H_D29

H_D30

H_D31

H_DSTBP1

H_DSTBN1

H_DINV1

H_D32

H_D33

H_D34

H_D35

H_D36

H_D37

H_D38

H_D39

H_D40

H_D41

H_D42

H_D43

H_D44

H_D45

H_D46

H_D47

H_DSTBP2

H_DSTBN2

H_DINV2

H_D48

H_D49

H_D50

H_D51

H_D52

H_D53

H_D54

H_D55

H_D56

H_D57

H_D58

H_D59

H_D60

H_D61

H_D62

H_D63

H_DSTBP3

H_DSTBN3

H_DINV3

LGA775_ C_EL

LGA775_ C_EL

IC design

3

R94

T180T180

FDV301NQ4FDV301N

Q4

2

R94

*10K/J_4

*10K/J_4

D1

*BAS316D1*BAS316

1

VCC1.2

R100

R100

62/J_4

A A

62/J_4

Q6

2

MMBT3904Q6MMBT3904

SYS_SHDN#CPU_THERMTRIP#

1 3

R103 *0/J_4R103 *0/J_4

PM_THERMTRIP#

No use Thermal trip CPU side still PU 62 ohm.

Use Thermal trip can share PU at SB side

5

C37

C37

*1u/16V_ 6

*1u/16V_ 6

SYS_SHDN#

PM_THERMTRIP# 12

B4

C5

A4

C6

A5

B6

B7

A7

A10

A11

B10

C11

D8

B12

C12

D11

H_DSTBP0

B9

H_DSTBN0

C8

H_DINV#0

A8

G9

F8

F9

E9

D7

E10

D10

F11

F12

D13

E13

G13

F14

G14

F15

G15

H_DSTBP1

E12

H_DSTBN1

G12

H_DINV#1

G11

H_D#32

G16

H_D#33

E15

H_D#34

E16

H_D#35

G18

H_D#36

G17

H_D#37

F17

H_D#38

F18

H_D#39

E18

H_D#40

E19

H_D#41

F20

H_D#42

E21

H_D#43

F21

H_D#44

G21

H_D#45

E22

H_D#46

D22

H_D#47

G22

H_DSTBP2

G19

H_DSTBN2

G20

H_DINV#2

D19

H_D#48

D20

H_D#49

D17

H_D#50

A14

H_D#51

C15

H_D#52

C14

H_D#53

B15

H_D#54

C18

H_D#55

B16

H_D#56

A17

H_D#57

B18

H_D#58

C21

H_D#59

B21

H_D#60

B19

H_D#61

A19

H_D#62

A22

H_D#63

B22

H_DSTBP3

C17

H_DSTBN3

A16

H_DINV#3

C20

VCC1.2

130/J_4

130/J_4

H_PROCHOT#_ D

H_FORCEPH#

4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

R88

R88

57.6/F_4

57.6/F_4

R95

R95

100/F_4

100/F_4

VTT_OUT_RIGHT

R105

R105

VTT_OUT_RIGHT

R110

R110

*130/J_4

*130/J_4

4

H_DSTBP3 5

H_DSTBN3 5

H_DINV#3 5

Layout note:

H_GTLREF: Zo=55 ohm,L<0.5"

0.635*VCC1.2 +/-2%

R92 10/J_4R92 10/J_4

C32

C32

1u/16V_6

1u/16V_6

R970/J_4 R970/J_4

Processor hot

Q31

Q31

2

MMBT3904

MMBT3904

MMBT3904

MMBT3904

13

Q32

Q32

2

3

C25

C25

10u/6.3V _8

10u/6.3V _8

R54 *0/J_4R54 *0/J_4

R55 *0/J_4R55 *0/J_4

BPMb#3

BPMb#2XDP _BPM#2

BPMb#1

BPMb#0

H_TDI_TDO_M

R89

R89

57.6/F_4

57.6/F_4

R96

R96

100/F_4

100/F_4

VCC1.2

C26

C26

.01u/50V _6

.01u/50V _6

R53 680/J_4R53 680/J_4

CLK_CPU_BCLK#2

2

VCC_SENSE

R56 *0/J_4R56 *0/J_4

VSS_SENSE

R57 *0/J_4R57 *0/J_4

R58 0/J_4R5 8 0/J_4

R59 0/J_4R5 9 0/J_4

H_PECI26

VCC1.2

VTT_OUT_LEFT

VCC1.2

VTT_OUT_LEFT

VTT_OUT_LEFT

H_DPSLP#10

H_CPUSLP#6

VTT_OUT_LEFT

ICH_DPRSTP#6,10

VCCP_PSI_N32

VTT_OUT_RIGHT

need check

VCC1.2

R80

R80

*51/F_4

*51/F_4

Layout note:

H_GTLREF: Zo=55 ohm,L<0.5"

0.635*VCC1.2 +/-2%

R93 10/J_4R93 10/J_4

C34

C34

1u/16V_6

1u/16V_6

VTT_OUT_LEFT

12

12

R81

R81

*51/F_4

*51/F_4

CPU_GTLREF1

C35

C35

R980/J_4 R980/J_4

CLK_CPU_BCLK2

R62 51/J_4R62 51/J_4

H_PECI

R68 *51/J_4R68 *51/J_4

R70 *51/J_4R70 *51/J_4

R82

R82

51/F_4

51/F_4

2200p/50V_4

2200p/50V_4

H_D#[0..15] 5

H_DSTBP0 5

H_DSTBN0 5

H_DINV#0 5

H_D#[16..31] 5

H_DSTBP1 5

H_DSTBN1 5

H_DINV#1 5

H_D#[32..47] 5

H_DSTBP2 5

H_DSTBN2 5

H_DINV#2 5

H_D#[48..63] 5

XDP_BPM# 3

XDP_BPM# 1

XDP_BPM# 0

Stuff them for Kentsfield support

CPU_GTLREF0

C33

C33

2200p/50V_4

2200p/50V_4

CPU_GTLREF3CPU_GTLREF0 CPU_GTLREF1 CPU_GTLREF2

H_VID0

R36 680/J_4R36 680/J_4

H_VID1

R48 680/J_4R48 680/J_4

H_VID2

R37 680/J_4R37 680/J_4

H_VID3

R38 680/J_4R38 680/J_4

H_VID4

R49 680/J_4R49 680/J_4

H_VID5

R50 680/J_4R50 680/J_4

H_VID6

R43 680/J_4R43 680/J_4

H_VID7

R45 680/J_4R45 680/J_4

R51 0/J_4R51 0/J_4

VCC1.5

VCC1.2

H_THERMDA

H_THERMDC

VCC_SENSE32

VSS_SENSE32

Connected with VR's PSI#

R83 *0/J_4R83 *0/J_4

R84 *0/J_4R84 *0/J_4

R85 *0/J_4R85 *0/J_4

R86 *0/J_4R86 *0/J_4

VCC1.2

XDP

R150 130/J _4R150 130/J_4

R152 130/J _4R152 130/J_4

13

CPU0_VR_HOT 32

XDP_TDO

XDP_TDI

XDP_TMS

XDP_TCK

XDP_TRST#

R106 *62/F_4R106 *62/F_4

R107 62/J_4R107 62/J_4

R108 62/J_4R108 62/J_4

R109 62/J_4R109 62/J_4

R111 62/J_4R111 62/J_4

3

H_SMI#12

H_A20M#1 2

H_FERR#12

H_INTR12

H_NMI12

H_IGNNE#12

H_STPCLK#12

as design guide page 113

H_VID032

H_VID132

H_VID232

H_VID332

H_VID432

H_VID532

H_VID632

H_VID732

T6T6

Q39

Q39

*MMBT3904

*MMBT3904

1 3

T10T10

T11T11

T12T12

T13T13

R65 51/J_4R65 5 1/J_4

R66 51/J_4R66 5 1/J_4

R67 51/J_4R67 5 1/J_4

H_PWRGD10

R618 0/J_4R618 0/J_4

T35T35

12

U2B

PSI#

U2B

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

C23

VCCIOPLL

D23

VCC_PLL

AM2

VID_0

AL5

VID_1

AM3

VID_2

AL6

VID_3

AK4

VID_4

AL4

VID_5

AM5

VID_6

AM7

VID_7

AN7

VID_SELECT

F28

BCLK_0

G28

BCLK_1

AE8

SKTOCC#

AL1

FC25

AK1

FC24

AJ7

VSS_1

AH7

VSS_2

AN3

VCC_SENSE

AN4

VSS_SENSE

AN5

VCC_MB_REGULATION

AN6

VSS_MB_REGULATION

AL8

VCC_1

AL7

VSS_3

F29

RSVD_4

F6

FC21

G6

RSVD_5

G5

PECI

AL3

VRDSEL

F26

TESTHI_0

W3

TESTHI_1

F25

TESTHI_2

G25

TESTHI_3

G27

TESTHI_4

G26

TESTHI_5

G24

TESTHI_6

F24

TESTHI_7

P1

DPSLP#

W2

TDI_M

L2

SLP#

AK6

FC8

N1

PWRGOOD

AL2

PROCHOT#

M2

THERMTRIP#

A13

COMP_0

T1

COMP_1

G2

COMP_2

R1

COMP_3

J2

FC3

T2

DPRSTP#

Y3

PSI#

AE3

FC18

B13

COMP_8

G1

BPMb#0

U1

TDO_M

A24

FC23

E29

FC26

H_SMI#

H_A20M#

H_FERR#

H_INTR

H_NMI

H_IGNNE#

R40 0/J_4R40 0/J_4

H_VCCPLL

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

H_VID7

H_CPU_VIDSEL

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_SKTOCC#

H_TEMP_SRC_ DP

H_TEMP_RET_DN

VCC_SENSE_R

VSS_SENSE_R

VCC_PKGS ENSE_R

VSS_PKG SENSE_R

TP_LGA775_AL8

TP_LGA775_AL7

TP_LGA775_F29

H_CPU_PD_ F6

TP_LGA775_G6

R657 0/J_4R657 0/J_4

CPU_TEST0

CPU_TEST1

H_DPSLP#

H_TDI_TDO_M

H_CPUSLP#

H_FORCEPH#

H_PWRGD

H_PROCHOT#_ D

CPU_THERMTRIP#

COMP0

R7149.9/F_4 R7149.9/F_4

COMP1

R7249.9/F_4 R7249.9/F_4

COMP2

R7349.9/F_4 R7349.9/F_4

COMP3

R7449.9/F_4 R7449.9/F_4

COMP4

R7549.9/F_4 R7549.9/F_4

ICH_DPRSTP#

COMP7

R7749.9/F_4 R7749.9/F_4

COMP8

R7824.9/F_4 R7824.9/F_4

BPMb#0

H_TDI_TDO_M

R79 *1K/J_4R7 9 *1K/J_4

TP_LGA775_G7 CPU_GTLREF2

2

TRST#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

DBR#

ITPCLK_0

ITPCLK_1

BSEL_0

BSEL_1

BSEL_2

RSVD_8

BPMb#1

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

FC40

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD_14

RSVD_15

RSVD_16

RSVD_17

FC20

FC22

FC39

RSVD_7

FC0/BOOTSELECT

MSID_0

MSID_1

RSVD_6

GTLREF3

GTLREF2

LGA775_ C_EL

LGA775_ C_EL

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

N5

C9

E7

AE6

D16

A20

E23

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

F23

D14

E6

D1

E5

J3

AA2

V2

Y1

W1

V1

AH2

G10

F2

CPU Thermal monitor

VCC3

2

Q3

VCC1.2

MBCLK26

MBDATA26

THERM_ALERT#10

3

RHU002N06Q3RHU002N06

VCC3

VCC3

VCC3

SYS_SHDN#

1

3

Q5 RHU002N06Q5 RHU002N06

NS LM95245 PU this pin

R99 *10K/J_4R99 *10K/J_4

R101 *0/J_4R101 *0/J_4

R102 *10K/J_4R102 *10K/J_4

R104 *330/J_4R1 04 *330/J_4

2

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_BPM# 0

XDP_BPM# 1

XDP_BPM# 2

XDP_BPM# 3

XDP_BPM# 4

XDP_BPM# 5

XDP_DCLKOUT_DP

XDP_DCLKOUT_DN

TP_LGA775_N5

BPMb#1

TP_LGA775_E7

TP_LGA775_AE6

TP_LGA775_D16

TP_LGA775_A20

TP_LAG775_E23

H_VR_READY

VTT_OUT_RIGHT

VTT_OUT_LEFT

TP_VTT_SEL

TP_LAG775_F23

TP_LAG775_D14

TP_LAG775_E6

TP_LAG775_D1

H_DCLKPH

H_ACLKPH

TP_LAG775_AA2

TP_LAG775_V2

CPU_BOOT

as design guide page 113

TP_LGA775_AH2

CPU_GTLREF3

2

CPU_BSEL 0

CPU_BSEL 1

CPU_BSEL 2

VCC1.2

2ND_MBDATA

1

R52 0/J_4R5 2 0/J_4

R69 1K/F_4R69 1K/F_4

R76 51/J_4R76 51/J_4

1 2

2ND_MBCLK

THERM_ALERT#_R

2

THER_SHD#

13

Q7 *MMBT3904Q7 *MMBT3904

T3T3

T4T4

T5T5

T7T7

T8T8

T9T9

1 2

T17T17

T20T20

T21T21

T23T23

T25T25

T26T26

T27T27

T28T28

T29T29

T34T34

R90

R90

10K/J_4

10K/J_4

1

VTT_OUT_RIGHT

XDP_BPM# 0

R39 51/J_4R39 51/J_4

XDP_BPM# 1

XDP_BPM# 2

XDP_BPM# 3

XDP_BPM# 4

XDP_BPM# 5

SYS_RST#XDP_DBRESET#

XDP_DCLKOUT_DP 2

XDP_DCLKOUT_DN 2

CPU_BSEL 0 2

CPU_BSEL 1 2

CPU_BSEL 2 2

2ND_MBCLK 18

2ND_MBDATA 18

1 2

R41 51/J_4R41 51/J_4

1 2

R42 51/J_4R42 51/J_4

1 2

R44 51/J_4R44 51/J_4

1 2

R46 51/J_4R46 51/J_4

1 2

R47 51/J_4R47 51/J_4

1 2

SYS_RST# 10

Termination

or VCC1.2?

VTT_OUT_LEFT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_OUT_RIGHT

VR_READY

C29

C29

.1u/16V_ 6

.1u/16V_ 6

VCC3VCC3

R87 *200/J_6R87 *200/J_6

R91

R91

10K/J_4

10K/J_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

VR_READY 10,32

C30

C30

.1u/16V_ 6

.1u/16V_ 6

LM86VCC

U3

7

OVT

SDAT

8

SCLK

ALERT

1

VCC

DXP

5

DXN

GND

*G780U3*G780

ADDRESS: 98H

CPU(1/2)- Host Bus

CPU(1/2)- Host Bus

CPU(1/2)- Host Bus

Near CPU

C28

C28

C27

C27

.1u/16V_ 6

.1u/16V_ 6

.1u/16V_ 6

.1u/16V_ 6

C31 *0.1u /10V_4C3 1 *0.1u/10V_4

4

6

2

3

PROJECT : EL8

PROJECT : EL8

Quanta Computer Inc.

Quanta Computer Inc.

C36

C36

*2200p/5 0V_4

*2200p/5 0V_4

1

R6062/J_4 R6062/J_4

R6162 /J_4 R6162/J_4

R6362 /J_4 R6362/J_4

R617680 R617680

R6451 /J_4 R6451/J_4

R1531K/J_4 R1531K/J_4

3 34Monday, March 09 , 2009

3 34Monday, March 09 , 2009

3 34Monday, March 09 , 2009

03

H_BREQ#

H_CPURST#

H_IERR#

PSI#

CPU_TEST10

VR_READY

H_THERMDA

H_THERMDC

1A

1A

1A

Page 4

5

U2D

U2D

C10

VSS_4

D12

VSS_5

C24

VSS_6

K2

VSS_7

C22

VSS_8

AN1

VSS_9

B14

VSS_10

K7

VSS_11

AE16

VSS_12

B11

VSS_13

AL10

VSS_14

D D

C C

B B

A A

AK23

AL16

AL24

AK13

AL20

AK16

AK20

AM27

AL13

AL17

AK30

AL23

AE28

AE29

AE30

AN20

AF10

AE24

AM24

AN23

AM16

AE25

AE27

AJ28

AH13

AH16

AK17

AH17

AH20

AH23

AM13

AH24

AJ30

AJ10

AJ16

AK29

AJ17

AK10

AM10

AJ23

AM23

AH10

AJ29

AK27

AK28

AM20

AJ24

AM17

VSS_15

H12

VSS_16

AF7

VSS_17

AK7

VSS_18

H7

VSS_19

E14

VSS_20

L28

VSS_21

Y5

VSS_22

E11

VSS_23

VSS_24

VSS_25

VSS_26

D21

VSS_27

VSS_28

D18

VSS_29

AN2

VSS_30

VSS_31

VSS_32

VSS_33

AM1

VSS_34

VSS_35

VSS_36

C19

VSS_37

E28

VSS_38

VSS_39

D24

VSS_40

VSS_41

A12

VSS_42

L25

VSS_43

J7

VSS_44

VSS_45

VSS_46

K5

VSS_47

J4

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

H9

VSS_55

H8

VSS_56

H13

VSS_57

AC6

VSS_58

AC7

VSS_59

AH6

VSS_60

C16

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

F19

VSS_66

VSS_67

AD7

VSS_68

VSS_69

VSS_70

E17

VSS_71

VSS_72

VSS_73

AE5

VSS_74

VSS_75

AE7

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

AF3

VSS_81

AK5

VSS_82

VSS_83

AF6

VSS_84

VSS_85

VSS_86

F22

VSS_87

AH3

VSS_88

VSS_89

VSS_90

F16

VSS_91

VSS_92

F13

VSS_93

AG7

VSS_94

F10

VSS_95

L26

VSS_96

AD4

VSS_97

H11

VSS_98

L24

VSS_99

L23

VSS_100

VSS_101

A15

VSS_102

VSS_103

B24

VSS_104

L3

VSS_105

H27

VSS_106

A21

VSS_107

AE2

VSS_108

VSS_109

VSS_110

VSS_111

B20

VSS_112

VSS_113

H26

VSS_114

B17

VSS_115

H25

VSS_116

H24

VSS_117

AA3

VSS_118

AA7

VSS_119

H23

VSS_120

AA6

VSS_121

H10

VSS_122

H22

VSS_123

H21

VSS_124

H20

VSS_125

H19

VSS_126

H18

VSS_127

AB7

VSS_128

H17

VSS_129

VSS_130

VSS_131

AC3

VSS_132

H14

VSS_133

P28

VSS_134

V6

VSS_135

AK2

VSS_136

P27

VSS_137

5

VSS_268

VSS_267

VSS_266

VSS_265

VSS_264

VSS_263

VSS_262

VSS_261

VSS_260

VSS_259

VSS_258

VSS_257

VSS_256

VSS_255

VSS_254

VSS_253

VSS_252

VSS_251

VSS_250

VSS_249

VSS_248

VSS_247

VSS_246

VSS_245

VSS_244

VSS_243

VSS_242

VSS_241

VSS_240

VSS_239

VSS_238

VSS_237

VSS_236

VSS_235

VSS_234

VSS_233

VSS_232

VSS_231

VSS_230

VSS_229

VSS_228

VSS_227

VSS_226

VSS_225

VSS_224

VSS_223

VSS_222

VSS_221

VSS_220

VSS_219

VSS_218

VSS_217

VSS_216

VSS_215

VSS_214

VSS_213

VSS_212

VSS_211

VSS_210

VSS_209

VSS_208

VSS_207

VSS_206

VSS_205

VSS_204

VSS_203

VSS_202

VSS_201

VSS_200

VSS_199

VSS_198

VSS_197

VSS_196

VSS_195

VSS_194

VSS_193

VSS_192

VSS_191

VSS_190

VSS_189

VSS_188

VSS_187

VSS_186

VSS_185

VSS_184

VSS_183

VSS_182

VSS_181

VSS_180

VSS_179

VSS_178

VSS_177

VSS_176

VSS_175

VSS_174

VSS_173

VSS_172

VSS_171

VSS_170

VSS_169

VSS_168

VSS_167

VSS_166

VSS_165

VSS_164

VSS_163

VSS_162

VSS_161

VSS_160

VSS_159

VSS_158

VSS_157

VSS_156

VSS_155

VSS_154

VSS_153

VSS_152

VSS_151

VSS_150

VSS_149

VSS_148

VSS_147

VSS_146

VSS_145

VSS_144

VSS_143

VSS_142

VSS_141

VSS_140

VSS_139

VSS_138

LGA775_C_EL

LGA775_C_EL

AG13

AG16

AG17

E8

AG20

AG23

AF20

AL28

AA23

V26

AM4

AB1

AJ27

R30

T7

E27

AE17

AE20

P24

Y2

H3

AN24

AF17

AG24

AF23

AF24

AN27

AN28

AF25

AF26

AF27

AF28

AF29

F7

H28

AF30

AE13

AG10

F4

AA30

N3

AB23

AB24

AB25

M7

AN16

AB26

AB27

AN17

AB28

M1

AB29

L7

L6

AB30

AK24

C13

V7

AH1

AE26

AJ4

B8

B5

B1

D3

A9

D5

D6

A6

C4

D9

E2

A2

A18

H6

AF13

AE10

AF16

P29

V3

P30

R23

R24

U7

R25

R26

R27

R28

R29

E25

T6

V23

V24

T3

V25

AN10

E20

R7

V27

R5

V28

V29

R2

V30

E26

P7

AA24

AA25

P4

AA26

AA27

AN13

AA28

N7

N6

AA29

L27

Y7

AL27

D15

L29

L30

C7

P23

W7

AJ20

P25

W4

AJ13

AM28

P26

4

3

2

1

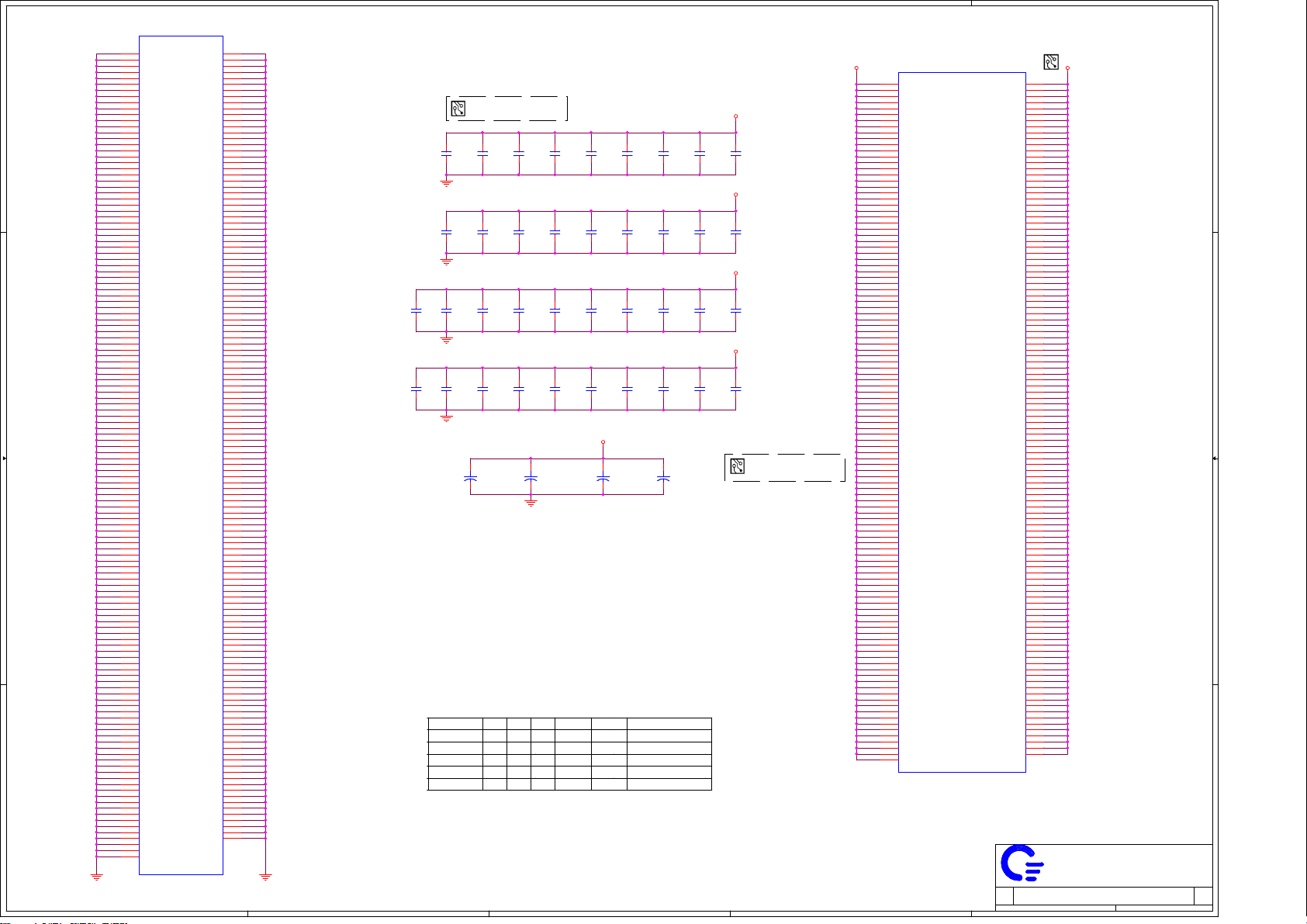

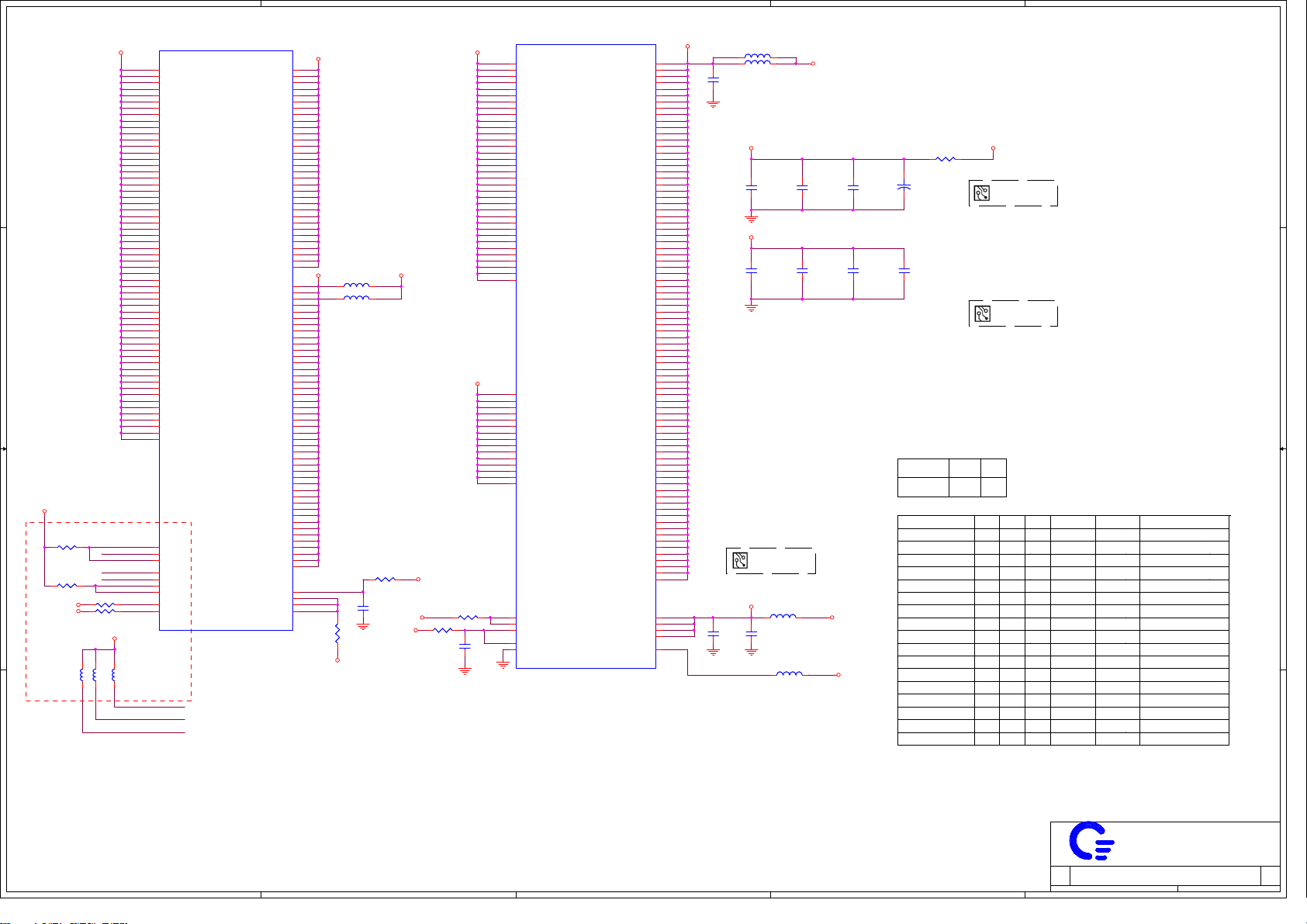

04

VCC_CORE

Place these parts reference

to Intel demo board.

C41

C41

C42

C39

C39

C40

22u/6.3V_12

22u/6.3V_12

C48

C48

22u/6.3V_12

22u/6.3V_12

C58

C58

10u/10V_8

10u/10V_8

C68

C68

10u/10V_8

10u/10V_8

C76

C76

560u/2.5V_7343

560u/2.5V_7343

S0

O

O

O

O

O

S3

X

X

X

X

X

C40

22u/6.3V_12

22u/6.3V_12

C49

C49

22u/6.3V_12

22u/6.3V_12

C59

C59

10u/10V_8

10u/10V_8

C69

C69

10u/10V_8

10u/10V_8

+

+

S4/S5

X

X

X

X

X

C77

C77

560u/2.5V_7343

560u/2.5V_7343

C38

C38

22u/6.3V_12

22u/6.3V_12

C47

C47

22u/6.3V_12

22u/6.3V_12

C57

C57

C56

C56

10u/10V_8

10u/10V_8

0.1u

0.1u

C66

C66

C67

C67

0.1u

0.1u

10u/10V_8

10u/10V_8

+

+

Yorkfield/Wolfdale CPU Power Status and max current table

POWER PLANE

VCC_CORE

VCC_CORE

VTT

VTT

VCC_PLL

4

22u/6.3V_12

22u/6.3V_12

C50

C50

22u/6.3V_12

22u/6.3V_12

C60

C60

10u/10V_8

10u/10V_8

C70

C70

10u/10V_8

10u/10V_8

Voltage

VID

VID

VCC1.2

VCC1.2

VCC1.5

C42

22u/6.3V_12

22u/6.3V_12

C51

C51

22u/6.3V_12

22u/6.3V_12

C61

C61

10u/10V_8

10u/10V_8

C71

C71

10u/10V_8

10u/10V_8

VCC_CORE

+

+

I(max)

100A

75A

8A

7A

260mA

3

C43

C43

22u/6.3V_12

22u/6.3V_12

C52

C52

22u/6.3V_12

22u/6.3V_12

C62

C62

10u/10V_8

10u/10V_8

C72

C72

10u/10V_8

10u/10V_8

C78

C78

560u/2.5V_7343

560u/2.5V_7343

Yorkfield@65W

Wolfdale

After VCC stable

Before VCC stable

Note

C44

C44

22u/6.3V_12

22u/6.3V_12

C53

C53

22u/6.3V_12

22u/6.3V_12

C63

C63

10u/10V_8

10u/10V_8

C73

C73

10u/10V_8

10u/10V_8

C79

C79

+

+

560u/2.5V_7343

560u/2.5V_7343

C45

C45

22u/6.3V_12

22u/6.3V_12

C54

C54

22u/6.3V_12

22u/6.3V_12

C64

C64

10u/10V_8

10u/10V_8

C74

C74

10u/10V_8

10u/10V_8

VCC_CORE

C46

C46

22u/6.3V_12

22u/6.3V_12

VCC_CORE

C55

C55

22u/6.3V_12

22u/6.3V_12

VCC_CORE

C65

C65

10u/10V_8

10u/10V_8

VCC_CORE

C75

C75

10u/10V_8

10u/10V_8

VCC_CORE Bulk CAPs place

to BOT of CPU centeral

2

AG22

AM26

AE12

AE11

W23

W24

W25

AL18

AC25

W30

AN14

AD28

AC29

AC27

AM18

AM19

AC26

AF15

AE14

W29

AC24

AC23

AN26

AN25

AN18

AN11

AD24

AE23

AE22

AN19

AE21

AM30

AE19

AC30

AE15

AN21

AC28

AE18

W26

AD25

AD26

AJ26

AM29

AJ12

AD27

AG29

AM22

AK18

AH28

AH21

AK12

AH22

AM14

AM25

AK25

AK19

AG15

AG21

AM21

AL21

AG25

AJ18

AH30

K29

T25

Y28

Y30

Y26

M29

U24

J23

AB8

J8

J28

T30

AM9

AC8

N23

U29

Y23

Y27

Y25

U27

V8

K8

M30

K27

M24

T8

N25

M8

N30

M25

M26

L8

U25

Y8

U23

M23

N27

U28

K28

U8

AD8

K24

T29

AE9

Y29

J22

T24

J25

U30

J19

U2C

U2C

VCC_CORE_1

VCC_CORE_2

VCC_CORE_3

VCC_CORE_4

VCC_CORE_5

VCC_CORE_6

VCC_CORE_7

VCC_CORE_8

VCC_CORE_9

VCC_CORE_10

VCC_CORE_11

VCC_CORE_12

VCC_CORE_13

VCC_CORE_14

VCC_CORE_15

VCC_CORE_16

VCC_CORE_17

VCC_CORE_18

VCC_CORE_19

VCC_CORE_20

VCC_CORE_21

VCC_CORE_22

VCC_CORE_23

VCC_CORE_24

VCC_CORE_25

VCC_CORE_26

VCC_CORE_27

VCC_CORE_28

VCC_CORE_29

VCC_CORE_30

VCC_CORE_31

VCC_CORE_32

VCC_CORE_33

VCC_CORE_34

VCC_CORE_35

VCC_CORE_36

VCC_CORE_37

VCC_CORE_38

VCC_CORE_39

VCC_CORE_40

VCC_CORE_41

VCC_CORE_42

VCC_CORE_43

VCC_CORE_44

VCC_CORE_45

VCC_CORE_46

VCC_CORE_47

VCC_CORE_48

VCC_CORE_49

VCC_CORE_50

VCC_CORE_51

VCC_CORE_52

VCC_CORE_53

VCC_CORE_54

VCC_CORE_55

VCC_CORE_56

VCC_CORE_57

VCC_CORE_58

VCC_CORE_59

VCC_CORE_60

VCC_CORE_61

VCC_CORE_62

VCC_CORE_63

VCC_CORE_64

VCC_CORE_65

VCC_CORE_66

VCC_CORE_67

VCC_CORE_68

VCC_CORE_69

VCC_CORE_70

VCC_CORE_71

VCC_CORE_72

VCC_CORE_73

VCC_CORE_74

VCC_CORE_75

VCC_CORE_76

VCC_CORE_77

VCC_CORE_78

VCC_CORE_79

VCC_CORE_80

VCC_CORE_81

VCC_CORE_82

VCC_CORE_83

VCC_CORE_84

VCC_CORE_85

VCC_CORE_86

VCC_CORE_87

VCC_CORE_88

VCC_CORE_89

VCC_CORE_90

VCC_CORE_91

VCC_CORE_92

VCC_CORE_93

VCC_CORE_94

VCC_CORE_95

VCC_CORE_96

VCC_CORE_97

VCC_CORE_98

VCC_CORE_99

VCC_CORE_100

VCC_CORE_101

VCC_CORE_102

VCC_CORE_103

VCC_CORE_104

VCC_CORE_105

VCC_CORE_106

VCC_CORE_107

VCC_CORE_108

VCC_CORE_109

VCC_CORE_110

VCC_CORE_111

VCC_CORE_112

VCC_CORE_113

VCC_CORE_225

VCC_CORE_224

VCC_CORE_223

VCC_CORE_222

VCC_CORE_221

VCC_CORE_220

VCC_CORE_219

VCC_CORE_218

VCC_CORE_217

VCC_CORE_216

VCC_CORE_215

VCC_CORE_214

VCC_CORE_213

VCC_CORE_212

VCC_CORE_211

VCC_CORE_210

VCC_CORE_209

VCC_CORE_208

VCC_CORE_207

VCC_CORE_206

VCC_CORE_205

VCC_CORE_204

VCC_CORE_203

VCC_CORE_202

VCC_CORE_201

VCC_CORE_200

VCC_CORE_199

VCC_CORE_198

VCC_CORE_197

VCC_CORE_196

VCC_CORE_195

VCC_CORE_194

VCC_CORE_193

VCC_CORE_192

VCC_CORE_191

VCC_CORE_190

VCC_CORE_189

VCC_CORE_188

VCC_CORE_187

VCC_CORE_186

VCC_CORE_185

VCC_CORE_184

VCC_CORE_183

VCC_CORE_182

VCC_CORE_181

VCC_CORE_180

VCC_CORE_179

VCC_CORE_178

VCC_CORE_177

VCC_CORE_176

VCC_CORE_175

VCC_CORE_174

VCC_CORE_173

VCC_CORE_172

VCC_CORE_171

VCC_CORE_170

VCC_CORE_169

VCC_CORE_168

VCC_CORE_167

VCC_CORE_166

VCC_CORE_165

VCC_CORE_164

VCC_CORE_163

VCC_CORE_162

VCC_CORE_161

VCC_CORE_160

VCC_CORE_159

VCC_CORE_158

VCC_CORE_157

VCC_CORE_156

VCC_CORE_155

VCC_CORE_154

VCC_CORE_153

VCC_CORE_152

VCC_CORE_151

VCC_CORE_150

VCC_CORE_149

VCC_CORE_148

VCC_CORE_147

VCC_CORE_146

VCC_CORE_145

VCC_CORE_144

VCC_CORE_143

VCC_CORE_142

VCC_CORE_141

VCC_CORE_140

VCC_CORE_139

VCC_CORE_138

VCC_CORE_137

VCC_CORE_136

VCC_CORE_135

VCC_CORE_134

VCC_CORE_133

VCC_CORE_132

VCC_CORE_131

VCC_CORE_130

VCC_CORE_129

VCC_CORE_128

VCC_CORE_127

VCC_CORE_126

VCC_CORE_125

VCC_CORE_124

VCC_CORE_123

VCC_CORE_122

VCC_CORE_121

VCC_CORE_120

VCC_CORE_119

VCC_CORE_118

VCC_CORE_117

VCC_CORE_116

VCC_CORE_115

VCC_CORE_114

LGA775_C_EL

LGA775_C_EL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCC_CORE

AK9

M28

AF12

N8

AF19

K26

J14

AN22

N24

AH8

W8

AD29

AL29

AG8

AA8

AG18

J30

AF14

M27

J9

AK14

Y24

AF21

AD30

AL9

AG19

J27

J12

W28

T28

J13

J24

AM12

AL26

AG28

AH27

AH29

AH19

AJ14

AH11

AF22

AF9

N26

AG9

AN12

AK8

T27

AJ19

U26

AJ8

AN15

AL22

AH12

N28

T26

AM8

AL19

K23

P8

K25

J11

J29

AH9

AJ25

AL30

N29

AG14

AK11

AJ9

AL12

AH25

AN30

AL14

K30

AJ11

AL11

AM11

AJ21

AG30

AK21

AF8

AM15

AD23

AF11

AK15

AG27

J21

J18

J26

AL15

AF18

AH15

AN9

AG26

AJ15

J10

AK26

AG11

AN29

AK22

R8

T23

AH14

AN8

AL25

W27

AH26

AH18

J20

AJ22

AG12

J15

PROJECT : EL8

PROJECT : EL8

Quanta Computer Inc.

Quanta Computer Inc.

CPU(2/2)- Power

CPU(2/2)- Power

CPU(2/2)- Power

1A

1A

4 34Monday, March 09, 2009

4 34Monday, March 09, 2009

1

4 34Monday, March 09, 2009

1A

Page 5

5

VCC1.2

R113

R113

301/F_4

VCC1.2

VCC1.2

301/F_4

R112

R112

100/F_4

100/F_4

R115

R115

16.5/F_4

16.5/F_4

R116

R116

57.6/F_4

57.6/F_4

R118

R118

100/F_4

100/F_4

R119

R119

57.6/F_4

57.6/F_4

R121

R121

100/F_4

100/F_4

D D

C C

B B

A A

49.9/F as schematic checklist

R114 51/J_4R114 51/J_4

C80

C80

0.1u/10V_4

0.1u/10V_4

H_RCOMP

49.9/F as schematic checklist

R117 51/J_4R117 51/J_4

C82

C82

1u/10V_6

1u/10V_6

49.9/F as schematic checklist

R120 51/J_4R120 51/J_4

C83

C83

1u/10V_6

1u/10V_6

0.25*VCCP

W:10,S:10 , L<3"

BreakoutL<0.25"

H_SWING

W:10,S:7 , L<0.5"

BreakoutL<0.25"

0.365*VCCP

W:10,S:20 , L<1.5"

C81

C81

220p/10V_4

220p/10V_4

0.365*VCCP

W:10,S:20 , L<1.5"

C84

C84

220p/10V_4

220p/10V_4

MCH_GTLREF0

MCH_GTLREF1

4

H_A#[3..16]3

H_A#[17..35]3

H_REQ#[0..4]3

H_ADSTB#03

H_DSTBP[3..0]3

H_DSTBN[3..0]3

H_DINV#[3..0]3

H_DSTBP0

H_DSTBP1

H_DSTBP2

H_DSTBP3

H_DSTBN0

H_DSTBN1

H_DSTBN2

H_DSTBN3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_ADSTB#13

H_ADS#3

H_TRDY#3

H_DRDY#3

H_DEFER#3

H_HITM#3

H_HIT#3

H_LOCK#3

H_BREQ#3

H_BNR#3

H_BPRI#3

H_DBSY#3

H_RS#[2..0]3

H_CPURST#3

T38T38

3

U4A

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_DSTBP0

H_DSTBN0

H_DINV#0

H_DSTBP1

H_DSTBN1

H_DINV#1

H_DSTBP2

H_DSTBN2

H_DINV#2

H_DSTBP3

H_DSTBN3

H_DINV#3

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BREQ#

H_BNR#

H_BPRI#

H_DBSY#

H_RS#0

H_RS#1

H_RS#2

H_CPURST#

TP_MCH_N25

U4A

L36

FSB_AB_3

L37

FSB_AB_4

J38

FSB_AB_5

F40

FSB_AB_6

H39

FSB_AB_7

L38

FSB_AB_8

L43

FSB_AB_9

N39

FSB_AB_10

N35

FSB_AB_11

N37

FSB_AB_12

J41

FSB_AB_13

N40

FSB_AB_14

M45

FSB_AB_15

R35

FSB_AB_16

T36

FSB_AB_17

R36

FSB_AB_18

R34

FSB_AB_19

R37

FSB_AB_20

R39

FSB_AB_21

U38

FSB_AB_22

T37

FSB_AB_23

U34

FSB_AB_24

U40

FSB_AB_25

T34

FSB_AB_26

Y36

FSB_AB_27

U35

FSB_AB_28

AA35

FSB_AB_29

U37

FSB_AB_30

Y37

FSB_AB_31

Y34

FSB_AB_32

Y38

FSB_AB_33

AA37

FSB_AB_34

AA36

FSB_AB_35

G38

FSB_REQB_0

K35

FSB_REQB_1

J39

FSB_REQB_2

C43

FSB_REQB_3

G39

FSB_REQB_4

J40

FSB_ADSTBB_0

T39

FSB_ADSTBB_1

C39

FSB_DSTBPB_0

B39

FSB_DSTBNB_0

B40

FSB_DINVB_0

K31

FSB_DSTBPB_1

J31

FSB_DSTBNB_1

F33

FSB_DINVB_1

J25

FSB_DSTBPB_2

K25

FSB_DSTBNB_2

F26

FSB_DINVB_2

C32

FSB_DSTBPB_3

D32

FSB_DSTBNB_3

D30

FSB_DINVB_3

J42

FSB_ADSB

L40

FSB_TRDYB

J43

FSB_DRDYB

G44

FSB_DEFERB

K44

FSB_HITMB

H45

FSB_HITB

H40

FSB_LOCKB

L42

FSB_BREQ0B

J44

FSB_BNRB

H37

FSB_BPRIB

H42

FSB_DBSYB

G43

FSB_RSB_0

L44

FSB_RSB_1

G42

FSB_RSB_2

D27

FSB_CPURSTB

N25

RSVD_05

EAGLELAKE_FCBGA1254

EAGLELAKE_FCBGA1254

EAGLELAKE_DDR3

EAGLELAKE_DDR3

SYM_REV = 1.5GC

SYM_REV = 1.5GC

1 OF 9

1 OF 9

FSB

FSB

2

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_DVREF

FSB_ACCVREF

HPL_CLKINP

HPL_CLKINN

F44

C44

D44

C41

E43

B43

D40

B42

B38

F38

A38

B37

D38

C37

D37

B36

E37

J35

H35

F37

G37

J33

L33

G33

L31

M31

M30

J30

G31

K30

M29

G30

J29

F29

H29

L25

K26

L29

J26

M26

H26

F25

F24

G25

H24

L24

J24

N24

C28

B31

F35

C35

B35

D35

D31

A34

B32

F31

D28

A29

C30

B30

E27

B28

B24

A23

C22

B23

P29

P30

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

MCH_GTLREF0

MCH_GTLREF1

CLK_MCH_BCLK

CLK_MCH_BCLK#

1

H_D#[0..15] 3

H_D#[16..31] 3

H_D#[32..47] 3

H_D#[48..63] 3

CLK_MCH_BCLK 2

CLK_MCH_BCLK# 2

05

PROJECT : EL8

PROJECT : EL8

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

NB (1/5) HOST

NB (1/5) HOST

NB (1/5) HOST

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

5 34Monday, March 09, 2009

5 34Monday, March 09, 2009

5 34Monday, March 09, 2009

1

1A

1A

1A

Page 6

5

4

3

2

1

U4E

06

U4E

EAGLELAKE_DDR3

EAGLELAKE_DDR3

SYM_REV = 1.5GC

MCH_BSEL0

MCH_BSEL02

MCH_BSEL12

MCH_BSEL22

T39T39

T40T40

R123 *1K/J_4R123 * 1K/J_4

D D

CLPWROK sequence request

1. asserted after VCC_CL ramp to 1.0V

2. asserted before PWROK

ICH_PWROK10

ECPWROK10,18,26

VCC_CL

C C

B B

R139

R139

1K/F_4

1K/F_4

R141

R141

464/F_4

464/F_4

ICH_PWROK

ECPWROK

Layout note:

H_GTLREF: Zo=55 ohm,L<0.5"

0.316*VCC_CL+-2%

CL_VREF

C98

C98

0.1u/16V_4

0.1u/16V_4

R122

R122

VCC1.2

R135 0/J_4R135 0/J _4

R136 *0/J_4R136 *0/J _4

MCH_CLPWROK12

T41T41

0/J_4

0/J_4

CL_DATA012

CL_CLK012

CL_RST#12

R124 *1K/J_4R124 * 1K/J_4

T42T42

R126 *1K/J_4R126 * 1K/J_4

T43T43

T44T44

T45T45

R128 *1K/J_4R128 * 1K/J_4

R130 *1K/J_4R130 * 1K/J_4

R132 1K/J_4R132 1K/J_4

T49T49

T50T50

T51T51

T52T52

T53T53

T59T59

T54T54

T55T55

T60T60

T61T61

T56T56

T57T57

T58T58

T62T62

T63T63

T64T64

T65T65

T66T66

T67T67

T70T70

T72T72

T74T74

T76T76

MCH_BSEL1

MCH_BSEL2

TP_MCH_M20

TP_MCH_N17

TP_MCH_K16

EXP_SLR

TP_MCH_G15

EXP_SM

TP_MCH_M17

TCEN

TP_MCH_G20

TP_MCH_J16

TP_MCH_M16

TP_MCH_J15

TP_MCH_J20

DUALX8_ENABLE

CL_DATA0

CL_CLK0

CL_VREF

CL_RST#

MCH_CLPWROK

JTAG_TDI

JTAG_TDO

JTAG_TCK

JTAG_TMS

TP_MCH_R31

TP_MCH_R32

TP_MCH_U30

TP_MCH_U31

TP_MCH_R15

TP_MCH_R14

TP_MCH_T15

TP_MCH_T14

TP_MCH_AN17

TP_MCH_AB15

TP_MCH_A44

TP_MCH_BD1

TP_MCH_BD45

TP_MCH_BE2

TP_MCH_BE44

TP_MCH_A45

TP_MCH_B2

TP_MCH_BE1

TP_MCH_BE45

AN13

AN10

AN11

AN17

AB15

BD45

BE44

BE45

F17

G16

P15

M20

N17

K16

F15

G15

H17

L17

M17

J17

G20

J16

M16

J15

J20

F20

AY4

AY2

AW2

AN8

AR7

AN9

R31

R32

U30

U31

R15

R14

T15

T14

A44

BD1

BE2

A45

B2

BE1

SYM_REV = 1.5GC

BSEL0

BSEL1

BSEL2

ALLZTEST

XORTEST

PRIMARY_PEG_PRESENCE

EXP_SLR

RSVD_17

EXP_SM

ITPM_EN#

RSVD_10

CEN

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

DUALX8_ENABLE

CL_DATA

CL_CLK

CL_VREF

CL_RSTB

CL_PWROK

JTAG_TDI

JTAG_TDO

JTAG_TCK

JTAG_TMS

RSVD_31

RSVD_30

RSVD_33

RSVD_32

RSVD_25

RSVD_26

RSVD_27

RSVD_28

NC_01

RSVD_29

NC_13

NC_12

NC_11

NC_10

NC_09

RSVD_18

RSVD_19

RSVD_20

RSVD_21

EAGLELAKE_FCBGA1254

EAGLELAKE_FCBGA1254

5 OF 9

5 OF 9

VGA

VGA

MISC

MISC

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

CRT_DDC_DATA

CRT_DDC_CLK

DAC_IREF

DPL_REFCLKINP

DPL_REFCLKINN

VCC_95

VSS_370

RSVD_35

RSVD_34

NC_19

RSTINB

PWROK

ICH_SYNCB

HDA_BCLK

HDA_RSTB

HDA_SDI

HDA_SDO

HDA_SYNC

DDPC_CTRLCLK

DDPC_CTRLDATA

DPRSTPB

NC_02

NC_18

NC_05

NC_04

NC_06

NC_03

NC_08

NC_07

SLPB

D14

C14

B18

D18

C18

F13

L15

M15

B15

E15

D15

G8

G9

L13

L11

B14

AN6

AR4

K15

AU4

AV4

AU2

AV1

AU3

J11

F11

P43

P42

B45

AK15

AD42

AN16

W30

AW44

R42

U32

CRT_DDC_DATA

CRT_DDC_CLK

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

TP_MCH_L13

TP_MCH_L11

TP_MCH_B14

PLT_RST#_NB

PM_SYNC#_MCH

MCH_DPRSTP#

H_CPUSLP#

TP_MCH_B45

TP_MCH_AK15

TP_MCH_AD42

TP_MCH_AN16

TP_MCH_W30

TP_MCH_AW44

TP_MCH_R42

TP_MCH_U32

R125 1K/J_4R125 1K/J_4

R127 1K/J_4R127 1K/J_4

ICH_PWROK

R1370/ J_4 R1370/J_4

R140 0/J_4R140 0/J _4

VCC3

DREFCLK 2

DREFCLK# 2

DREFSSCLK 2

DREFSSCLK# 2

T46T46

T47T47

T48T48

R1380/J_4 R1380/J_4

T68T68

T69T69

T71T71

T73T73

T75T75

T77T77

T78T78

T79T79

PLT_RST#_NB 11

PM_SYNC# 10

ICH_DPRSTP#

DREFCLK

R129 EV@10K/J_4R129 EV@10K/J_4

DREFSSCLK

R131 EV@10K/J_4R131 EV@10K/J_4

DREFSSCLK#

R133 EV@0/J_4R133 EV@0/J_4

DREFCLK#

R134 EV@0/J_4R134 EV@0/J_4

ICH_DPRSTP#

The Daisy chain topology should

be routed from ICH10 to IMVP ,

then to (G)MCH and CPU, in that

order.

ICH_DPRSTP# 3,10

H_CPUSLP# 3

SDVO_CTRLDATA19

SDVO_CTRLCLK19

Enable Digital Port B

had PU 5.6K to VCC2.5 on CH7308 side

need to check with intel

SDVO_CTRLCLK

VCC1.1

PEG_RXP018

PEG_RXN018

PEG_RXP118

PEG_RXN118

PEG_RXP218

PEG_RXN218

PEG_RXP318

PEG_RXN318

PEG_RXP418

PEG_RXN418

PEG_RXP518

PEG_RXN518

PEG_RXP618

PEG_RXN618

PEG_RXP718

PEG_RXN718

PEG_RXP818

PEG_RXN818

PEG_RXP918

PEG_RXN918

PEG_RXP1018

PEG_RXN1018

PEG_RXP1118

PEG_RXN1118

PEG_RXP1218

PEG_RXN1218

PEG_RXP1318

PEG_RXN1318

PEG_RXP1418

PEG_RXN1418

PEG_RXP1518

PEG_RXN1518

DMI_RXP011

DMI_RXN011

DMI_RXP111

DMI_RXN111

DMI_RXP211

DMI_RXN211

DMI_RXP311

DMI_RXN311

CLK_PCIE_EXP2

CLK_PCIE_EXP#2

R143 IV@0/J_4R143 IV@0/J_4

R144 IV@0/J_4R144 IV@0/J_4

T80T80

T81T81

PEG_RXP0

PEG_RXN0

PEG_RXP1

PEG_RXN1

PEG_RXP2

PEG_RXN2

PEG_RXP3

PEG_RXN3

PEG_RXP4

PEG_RXN4

PEG_RXP5

PEG_RXN5

PEG_RXP6

PEG_RXN6

PEG_RXP7

PEG_RXN7

PEG_RXP8

PEG_RXN8

PEG_RXP9

PEG_RXN9

PEG_RXP10

PEG_RXN10

PEG_RXP11

PEG_RXN11

PEG_RXP12

PEG_RXN12

PEG_RXP13

PEG_RXN13

PEG_RXP14

PEG_RXN14

PEG_RXP15

PEG_RXN15

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

CLK_PCIE_EXP

CLK_PCIE_EXP#

SDVO_CTRLDATA_RSDVO_CTRLDATA

SDVO_CTRLCLK_R

TP_MCH_AB13

TP_MCH_AD13

U4B

U4B

F6

PEG_RXP_0

G7

PEG_RXN_0

H6

PEG_RXP_1

G4

PEG_RXN_1

J6

PEG_RXP_2

J7

PEG_RXN_2

L6

PEG_RXP_3

L7

PEG_RXN_3

N9

PEG_RXP_4

N10

PEG_RXN_4

N7

PEG_RXP_5

N6

PEG_RXN_5

R7

PEG_RXP_6

R6

PEG_RXN_6

R9

PEG_RXP_7

R10

PEG_RXN_7

U10

PEG_RXP_8

U9

PEG_RXN_8

U6

PEG_RXP_9

U7

PEG_RXN_9

AA9

PEG_RXP_10

AA10

PEG_RXN_10

R4

PEG_RXP_11

P4

PEG_RXN_11

AA7

PEG_RXP_12

AA6

PEG_RXN_12

AB10

PEG_RXP_13

AB9

PEG_RXN_13

AB3

PEG_RXP_14

AA2

PEG_RXN_14

AD10

PEG_RXP_15

AD11

PEG_RXN_15

AD7

DMI_RXP_0

AD8

DMI_RXN_0

AE9

DMI_RXP_1

AE10

DMI_RXN_1

AE6

DMI_RXP_2

AE7

DMI_RXN_2

AF9

DMI_RXP_3

AF8

DMI_RXN_3

D9

EXP_CLKP

E9

EXP_CLKN

J13

SDVO_CTRLDATA

G13

SDVO_CTRLCLK

AB13

RSVD_23

AD13

RSVD_22

EAGLELAKE_FCBGA1254

EAGLELAKE_FCBGA1254

EAGLELAKE_DDR3

EAGLELAKE_DDR3

SYM_REV = 1.5GC

SYM_REV = 1.5GC

PCIE

PCIE

DMI

DMI

2 OF 9

2 OF 9

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

EXP_RCOMPO

EXP_COMPI

EXP_ICOMPO

EXP_RBIAS

C_PEG_TXP0 PEG_TXP0

C_PEG_TXN0

C_PEG_TXN1

C_PEG_TXN2

C_PEG_TXP3

C_PEG_TXN3

C_PEG_TXP4

C_PEG_TXN4

C_PEG_TXP5

C_PEG_TXN5

C_PEG_TXP6

C_PEG_TXN6

C_PEG_TXP7

C_PEG_TXN7

C_PEG_TXP8

C_PEG_TXN8

C_PEG_TXP9

C_PEG_TXN9

C_PEG_TXP10

C_PEG_TXN10

C_PEG_TXP11

C_PEG_TXN11

C_PEG_TXP12

C_PEG_TXN12

C_PEG_TXP13

C_PEG_TXN13

C_PEG_TXP14

C_PEG_TXN14

C_PEG_TXP15

C_PEG_TXN15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

GRCOMP

GRBIAS

C85 EV@0.1u/10V_4_X7RC85 EV@0.1u/10V_4_X7R

C86 EV@0.1u/10V_4_X7RC86 EV@0.1u/10V_4_X7R

C87 EV@0.1u/10V_4_X7RC87 EV@0.1u/10V_4_X7R

C88 EV@0.1u/10V_4_X7RC88 EV@0.1u/10V_4_X7R

C89 EV@0.1u/10V_4_X7RC89 EV@0.1u/10V_4_X7R

C90 EV@0.1u/10V_4_X7RC90 EV@0.1u/10V_4_X7R

C91 EV@0.1u/10V_4_X7RC91 EV@0.1u/10V_4_X7R

C92 EV@0.1u/10V_4_X7RC92 EV@0.1u/10V_4_X7R

C93 EV@0.1u/10V_4_X7RC93 EV@0.1u/10V_4_X7R

C94 EV@0.1u/10V_4_X7RC94 EV@0.1u/10V_4_X7R

C95 EV@0.1u/10V_4_X7RC95 EV@0.1u/10V_4_X7R

C96 EV@0.1u/10V_4_X7RC96 EV@0.1u/10V_4_X7R

C97 EV@0.1u/10V_4_X7RC97 EV@0.1u/10V_4_X7R

C99 EV@0.1u/10V_4_X7RC99 EV@0.1u/10V_4_X7R

C100 EV@0.1u/10V_4_ X7RC100 EV@0.1u/10V_4_X7R

C101 EV@0.1u/10V_4_ X7RC101 EV@0.1u/10V_4_X7R

C102 EV@0.1u/10V_4_ X7RC102 EV@0.1u/10V_4_X7R

C103 EV@0.1u/10V_4_ X7RC103 EV@0.1u/10V_4_X7R

C104 EV@0.1u/10V_4_ X7RC104 EV@0.1u/10V_4_X7R

C105 EV@0.1u/10V_4_ X7RC105 EV@0.1u/10V_4_X7R

C106 EV@0.1u/10V_4_ X7RC106 EV@0.1u/10V_4_X7R

C107 EV@0.1u/10V_4_ X7RC107 EV@0.1u/10V_4_X7R

C108 EV@0.1u/10V_4_ X7RC108 EV@0.1u/10V_4_X7R

C109 EV@0.1u/10V_4_ X7RC109 EV@0.1u/10V_4_X7R

C110 EV@0.1u/10V_4_ X7RC110 EV@0.1u/10V_4_X7R

C111 EV@0.1u/10V_4_ X7RC111 EV@0.1u/10V_4_X7R

C112 EV@0.1u/10V_4_ X7RC112 EV@0.1u/10V_4_X7R

C113 EV@0.1u/10V_4_ X7RC113 EV@0.1u/10V_4_X7R

C114 EV@0.1u/10V_4_ X7RC114 EV@0.1u/10V_4_X7R

C115 EV@0.1u/10V_4_ X7RC115 EV@0.1u/10V_4_X7R

C116 EV@0.1u/10V_4_ X7RC116 EV@0.1u/10V_4_X7R

C117 EV@0.1u/10V_4_ X7RC117 EV@0.1u/10V_4_X7R

R142 49.9/F_4R142 49.9/F_4

R145 750/F_4R145 750/F_4

GMCH_CORE

C11

B11

A10

B9

C9

D8

B8

C7

B7

B6

B3

B4

D2

C2

H2

G2

J2

K2

K1

L2

P2

M2

T2

R1

U2

V2

W4

V3

AA4

Y4

AC1

AB2

AC2

AD2

AD4

AE4

AE2

AF2

AF4

AG4

Y7

Y8

Y6

AG1

PEG_TXN0

PEG_TXP1C_PEG_TXP1

PEG_TXN1

PEG_TXP2C_PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_TXP8

PEG_TXN8

PEG_TXP9

PEG_TXN9

PEG_TXP10

PEG_TXN10

PEG_TXP11

PEG_TXN11

PEG_TXP12

PEG_TXN12

PEG_TXP13

PEG_TXN13

PEG_TXP14

PEG_TXN14

PEG_TXP15

PEG_TXN15

PEG_TXP0 18

PEG_TXN0 18

PEG_TXP1 18

PEG_TXN1 18

PEG_TXP2 18

PEG_TXN2 18

PEG_TXP3 18

PEG_TXN3 18

PEG_TXP4 18

PEG_TXN4 18

PEG_TXP5 18

PEG_TXN5 18

PEG_TXP6 18

PEG_TXN6 18

PEG_TXP7 18

PEG_TXN7 18

PEG_TXP8 18

PEG_TXN8 18

PEG_TXP9 18

PEG_TXN9 18

PEG_TXP10 18

PEG_TXN10 18

PEG_TXP11 18

PEG_TXN11 18

PEG_TXP12 18

PEG_TXN12 18

PEG_TXP13 18

PEG_TXN13 18

PEG_TXP14 18

PEG_TXN14 18

PEG_TXP15 18

PEG_TXN15 18

DMI_TXP0 11

DMI_TXN0 11

DMI_TXP1 11

DMI_TXN1 11

DMI_TXP2 11

DMI_TXN2 11

DMI_TXP3 11

DMI_TXN3 11

PEG_TXP0

RP14 IV@0X2RP14 IV@0X2

1

PEG_TXN0

3

PEG_TXP1

RP15 IV@0X2RP15 IV@0X2

1

PEG_TXN1

3

PEG_TXP2

RP16 IV@0X2RP16 IV@0X2

1

PEG_TXN2

3

PEG_TXP3

RP17 IV@0X2RP17 IV@0X2

1

PEG_TXN3

3

PEG_RXP2 SDVO_STALL

RP18 IV@0X2RP18 IV@0X2

1

PEG_RXN2

A A

5

4

3

3

2

SDVO_RED

2

SDVO_RED#

4

SDVO_GREEN

2

SDVO_GREEN#

4

SDVO_BLUE

2

SDVO_BLUE#

4

SDVO_CLK

2

SDVO_CLK#

4

2

SDVO_STALL#

4

SDVO_RED 19

SDVO_RED# 19

SDVO_GREEN 19

SDVO_GREEN# 19

SDVO_BLUE 19

SDVO_BLUE# 19

SDVO_CLK 19

SDVO_CLK# 19

SDVO_STALL 19

SDVO_STALL# 19

PROJECT : EL8

PROJECT : EL8

Quanta Computer Inc.

Size Doc ument Number Rev

Size Doc ument Number Rev

Size Doc ument Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Quanta Computer Inc.

NB (2/5)- VGA, DMI, PCIE

NB (2/5)- VGA, DMI, PCIE

NB (2/5)- VGA, DMI, PCIE

1

PROJECT : EL8

PROJECT : EL8

Quanta Computer Inc.

Quanta Computer Inc.

6 34Monday, March 09, 2009

6 34Monday, March 09, 2009

6 34Monday, March 09, 2009

1A

1A

1A

Page 7

5

U4C

BC41

BC35

BB32

BC32

BD32

BB31

AY31

BA31

BD31

BD30

AW43

BC30

BB30

AM42

BD28

AW42

AU42

AV42

AV45

AY44

BC28

AU43

AR40

AU44

AM43

BB27

BD27

BA27

AY26

AR42

AM44

AR44

AL40

AY37

BA37

AW29

AY29

AU37

AV37

AU33

AT33

AT30

AR30

AW38

AY38

U4C

DDR_A_MA_ 0

DDR_A_MA_ 1

DDR_A_MA_ 2

DDR_A_MA_ 3

DDR_A_MA_ 4

DDR_A_MA_ 5

DDR_A_MA_ 6

DDR_A_MA_ 7

DDR_A_MA_ 8

DDR_A_MA_ 9

DDR_A_MA_ 10

DDR_A_MA_ 11

DDR_A_MA_ 12

DDR_A_MA_ 13

DDR_A_MA_ 14

DDR_A_W EB

DDR_A_CAS B

DDR_A_RAS B

DDR_A_BS_0

DDR_A_BS_1

DDR_A_BS_2

DDR_A_CSB _0

DDR_A_CSB _1

DDR_A_CSB _2

DDR_A_CSB _3

DDR_A_CKE _0

DDR_A_CKE _1

DDR_A_CKE _2

DDR_A_CKE _3

DDR_A_ODT_0

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

DDR_A_CK_ 0

DDR_A_CKB _0

DDR_A_CK_ 1

DDR_A_CKB _1

DDR_A_CK_ 2

DDR_A_CKB _2

DDR_A_CK_ 3

DDR_A_CKB _3

DDR_A_CK_ 4

DDR_A_CKB _4

DDR_A_CK_ 5

DDR_A_CKB _5

DDR_Channel_A

DDR_Channel_A

EAGLELAKE_DDR3

EAGLELAKE_DDR3

SYM_REV = 1 .5GC

SYM_REV = 1 .5GC

D D

C C

B B

M_A_A[0..14]14 ,15

M_A_CAS#14,15

M_A_RAS#14,15

M_A_BS#014,15

M_A_BS#114,15

M_A_BS#214,15

M_SA_CS# 014

M_SA_CS# 215

M_SA_CS# 315

M_SA_CKE 014

M_SA_CKE 114

M_SA_CKE 215

M_SA_CKE 315

M_SA_ODT014

M_SA_ODT114

M_SA_ODT215

M_SA_ODT315

M_SA0_CK 014

M_SA0_CK #014

M_SA0_CK 214

M_SA0_CK #214

M_SA1_CK 315

M_SA1_CK #315

M_SA1_CK 515

M_SA1_CK #515

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_CAS#

M_A_RAS#

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_SA_CS# 0

M_SA_CS# 2

M_SA_CS# 3

M_SA_CKE 0

M_SA_CKE 1

M_SA_CKE 2

M_SA_CKE 3

M_SA_ODT0

M_SA_ODT1

M_SA_ODT2

M_SA_ODT3

M_SA0_CK 0

M_SA0_CK #0

M_SA0_CK 2

M_SA0_CK #2

M_SA1_CK 3

M_SA1_CK #3

M_SA1_CK 5

M_SA1_CK #5

DRAM_PWROK generated circuit

1.5VSUS

R155

R155

10K/J_4

10K/J_4

H_DRAMPW RGD

C118 1u/10V_6C11 8 1u/10V_6

5V_STBY

R158

R158

1K/J_4

2

Q9

DTC144EUQ9DTC144EU

1K/J_4

EAGLELA KE_FCBG A1254

EAGLELA KE_FCBG A1254

2

Q8

1 3

DTC144EUQ8DTC144EU

1 3

3 OF 9

3 OF 9

A A

SUSC#10,26

R159 1K/J_4R159 1K/J_4

5

DDR_A_DQS _0

DDR_A_DQS B_0

DDR_A_DM_0

DDR_A_DQ_ 0

DDR_A_DQ_ 1

DDR_A_DQ_ 2

DDR_A_DQ_ 3

DDR_A_DQ_ 4

DDR_A_DQ_ 5

DDR_A_DQ_ 6

DDR_A_DQ_ 7

DDR_A_DQS _1

DDR_A_DQS B_1

DDR_A_DM_1

DDR_A_DQ_ 8

DDR_A_DQ_ 9

DDR_A_DQ_ 10

DDR_A_DQ_ 11

DDR_A_DQ_ 12

DDR_A_DQ_ 13

DDR_A_DQ_ 14

DDR_A_DQ_ 15

DDR_A_DQS _2

DDR_A_DQS B_2

DDR_A_DM_2

DDR_A_DQ_ 16

DDR_A_DQ_ 17

DDR_A_DQ_ 18

DDR_A_DQ_ 19

DDR_A_DQ_ 20

DDR_A_DQ_ 21

DDR_A_DQ_ 22

DDR_A_DQ_ 23

DDR_A_DQS _3

DDR_A_DQS B_3

DDR_A_DM_3

DDR_A_DQ_ 24

DDR_A_DQ_ 25

DDR_A_DQ_ 26

DDR_A_DQ_ 27

DDR_A_DQ_ 28

DDR_A_DQ_ 29

DDR_A_DQ_ 30

DDR_A_DQ_ 31

DDR_A_DQS _4

DDR_A_DQS B_4

DDR_A_DM_4

DDR_A_DQ_ 32

DDR_A_DQ_ 33

DDR_A_DQ_ 34

DDR_A_DQ_ 35

DDR_A_DQ_ 36

DDR_A_DQ_ 37

DDR_A_DQ_ 38

DDR_A_DQ_ 39

DDR_A_DQS _5

DDR_A_DQS B_5

DDR_A_DM_5

DDR_A_DQ_ 40

DDR_A_DQ_ 41

DDR_A_DQ_ 42

DDR_A_DQ_ 43

DDR_A_DQ_ 44

DDR_A_DQ_ 45

DDR_A_DQ_ 46

DDR_A_DQ_ 47

DDR_A_DQS _6

DDR_A_DQS B_6

DDR_A_DM_6

DDR_A_DQ_ 48

DDR_A_DQ_ 49

DDR_A_DQ_ 50

DDR_A_DQ_ 51

DDR_A_DQ_ 52

DDR_A_DQ_ 53

DDR_A_DQ_ 54

DDR_A_DQ_ 55

DDR_A_DQS _7

DDR_A_DQS B_7

DDR_A_DM_7

DDR_A_DQ_ 56

DDR_A_DQ_ 57

DDR_A_DQ_ 58

DDR_A_DQ_ 59

DDR_A_DQ_ 60

DDR_A_DQ_ 61

DDR_A_DQ_ 62

DDR_A_DQ_ 63

4

M_A_DQ0

M_A_DQS0

BC5

M_A_DQS# 0

BD4

M_A_DM0

BC3

M_A_DQ0

BC2

M_A_DQ1

BD3

M_A_DQ2

BD7

M_A_DQ3

BB7

M_A_DQ4

BB2

M_A_DQ5

BA3

M_A_DQ6

BE6

M_A_DQ7

BD6

M_A_DQS1

BB9

M_A_DQS# 1

BC9

M_A_DM1

BD9

M_A_DQ8

BB8

M_A_DQ9

AY8

M_A_DQ10

BD11

M_A_DQ11

BB11

M_A_DQ12

BC7

M_A_DQ13

BE8

M_A_DQ14

BD10

M_A_DQ15

AY11

M_A_DQS2

BD15

M_A_DQS# 2

BB15

M_A_DM2

BD14

M_A_DQ16

BB14

M_A_DQ17

BC14

M_A_DQ18

BC16

M_A_DQ19

BB16

M_A_DQ20

BC11

M_A_DQ21

BE12

M_A_DQ22

BA15

M_A_DQ23

BD16

M_A_DQS3

AR22

M_A_DQS# 3

AT22

M_A_DM3

AV22

M_A_DQ24

AW21

M_A_DQ25

AY22

M_A_DQ26

AV24

M_A_DQ27

AY24

M_A_DQ28

AU21

M_A_DQ29

AT21

M_A_DQ30

AR24

M_A_DQ31

AU24

M_A_DQS4

AH43

M_A_DQS# 4

AH42

M_A_DM4

AK42

M_A_DQ32

AL41

M_A_DQ33

AK43

M_A_DQ34

AG42

M_A_DQ35

AG44

M_A_DQ36

AL42

M_A_DQ37

AK44

M_A_DQ38

AH44

M_A_DQ39

AG41

M_A_DQS5

AD43

M_A_DQS# 5

AE42

M_A_DM5

AE45

M_A_DQ40

AF43

M_A_DQ41

AF42

M_A_DQ42

AC44

M_A_DQ43

AC42

M_A_DQ44

AF40

M_A_DQ45

AF44

M_A_DQ46

AD44

M_A_DQ47

AC41

M_A_DQS6

Y43

M_A_DQS# 6

Y42

M_A_DM6

AA45

M_A_DQ48

AB43

M_A_DQ49

AA42

M_A_DQ50

W42

M_A_DQ51

W41

M_A_DQ52

AB42

M_A_DQ53

AB44

M_A_DQ54

Y44

M_A_DQ55

Y40

M_A_DQS7

T44