Page 1

5

4

3

2

1

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : IN2

D D

LAYER 5 : VCC

LAYER 6 : BOT

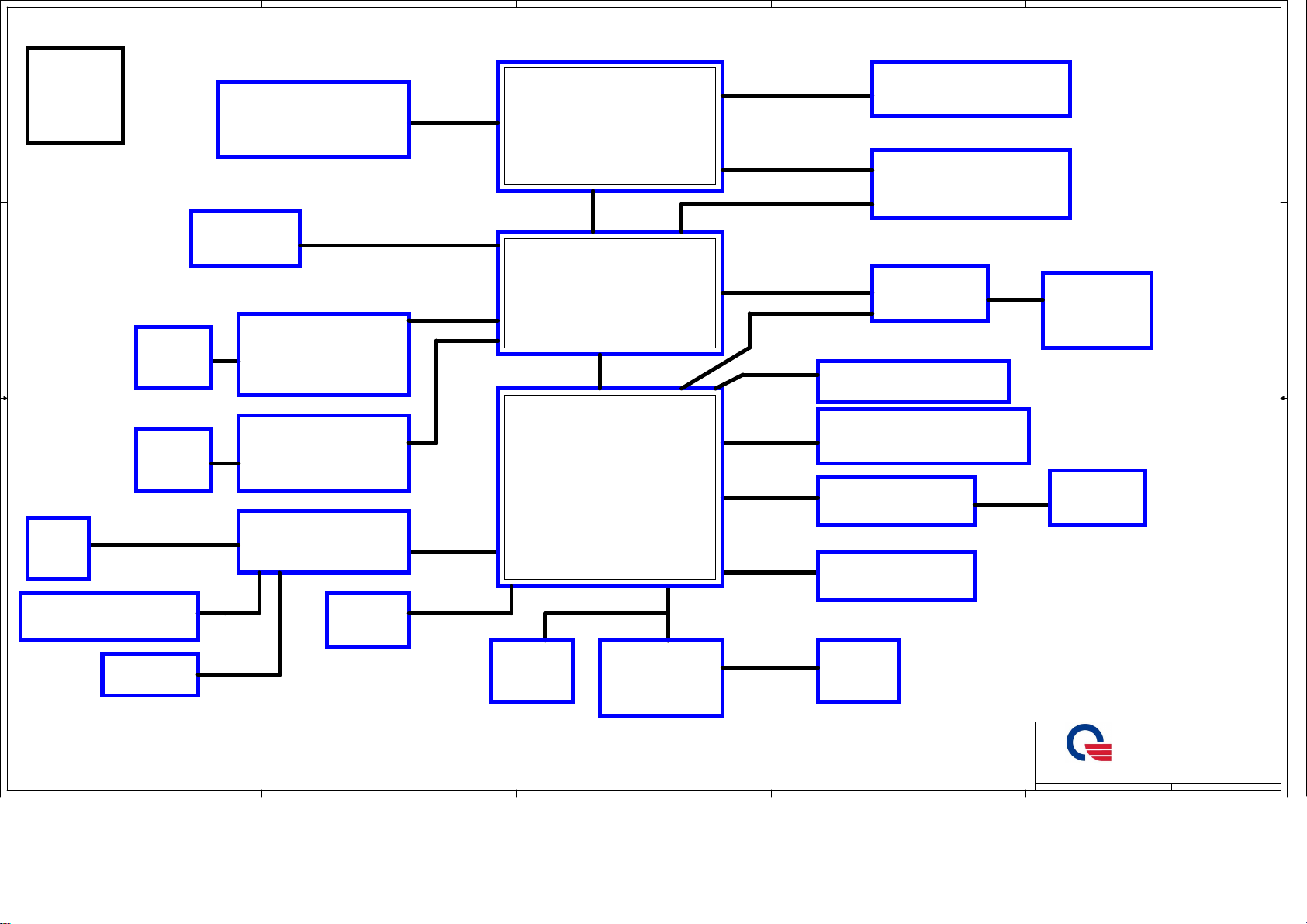

DDRII

512M//1GB/2GB/4GB

18.5" panel

AUO/CMO

C C

10/100 Ethernet

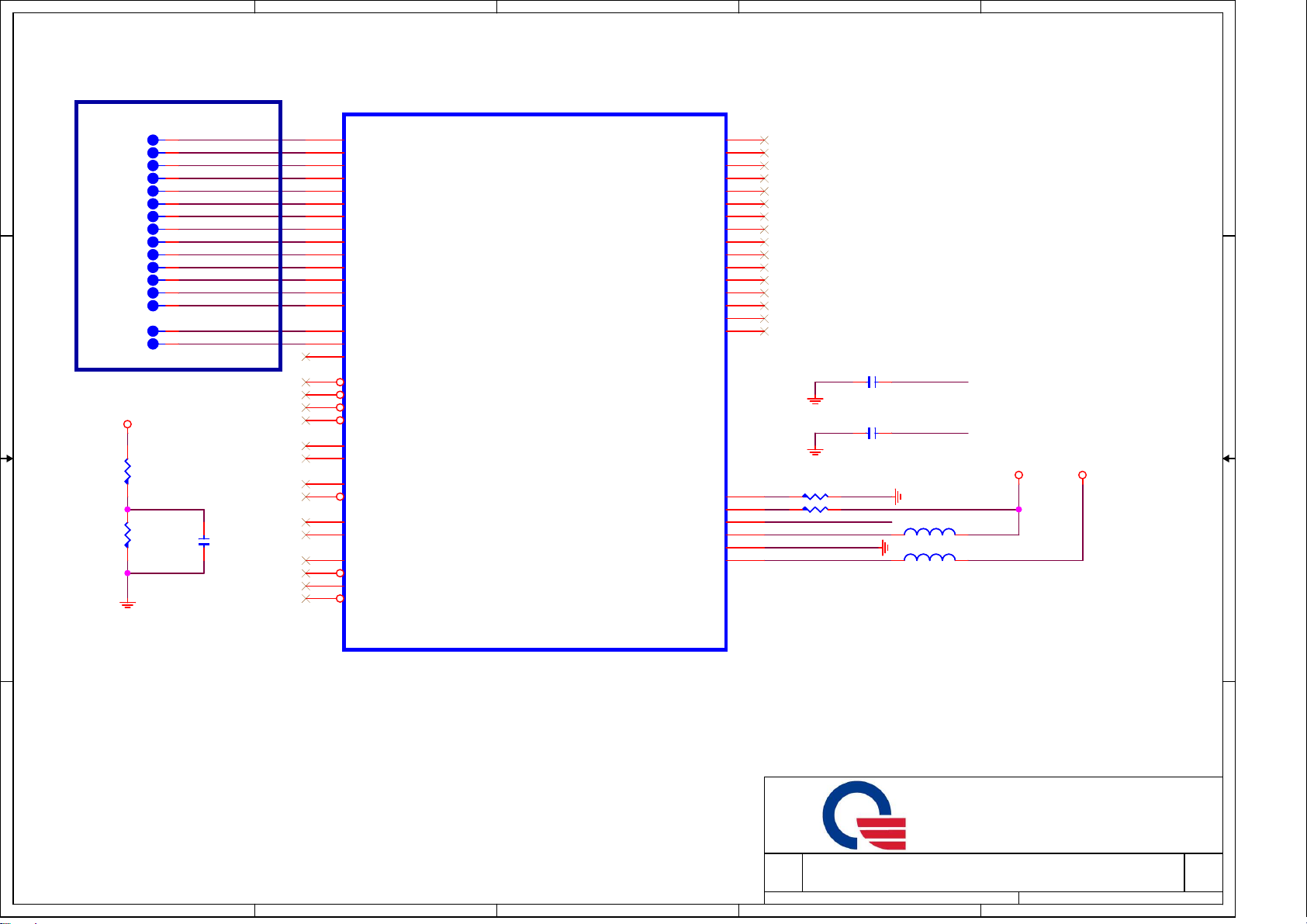

BENQ(EL3) LCDPC Block Diagram

VID[0:5]

+/- CPU_CLK

+/- HCLK

PCI-E

USB

Clock Gengerator

MINI CARD

CHA

LVDS

PCI-E

PCI-E

AMD

VCORE:+0.375V ~ +1.5V 30A

VLDT:+1.2V 1A

VCCA:+2.5V 0.25A

812-PIN BGA

HT-LINK

RS690E

HOST

LVDS, DMI, DDR CLK

POWER

GND

21mmX21mm FCBGA 465PIN

CPU VCORE

MAX8799

ICS951462

WLAN

Module

EM106

RJ-45

RTL8102EL

Card Reader

4 in 1

B B

JMB385E

A_LINK

SB600

RTC, AC97, SATA, IDE, LPC, CPU

PCI-E, USB, DMI, PCI

SMB, GPIO, CLK

SATA

IDE

USB

HDD

SSD module/ZIF

WebCam Conn.

Camera

Module

HDA CODEC

SPK

ALC269 2WX2

HD_AUDIO

23mmX23mm FCBGA 549PIN

USB

USB PORT X4

USB

Headohone Out

Int. Mic

A A

5

USB X2

TPM

ITE8512

4

LPC BUS

EC

3

SPI

Flash

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

BENQ

BENQ

BENQ

1A

1A

1 35Tuesday, January 06, 2009

1 35Tuesday, January 06, 2009

1

1 35Tuesday, January 06, 2009

1A

Page 2

5

4

3

2

1

5VPCU

SW

D D

SUSON

1A

Control By EC

5VSUS

SW

VCC5

MAINON

PU6

VCC1.2SUS

SW

VCC1.2

SUSON

VIN

Always ON

PWM

C C

5VPCU(3A)

3VPCU(3A)

3VPCU

SUSON

RVCC_ON

SW

SW

MAINON

3VSUS

Control By EC

RVCC3

Control By EC

SW

VCC1.5

SW

VCC3

MAINON

LDO

CPU_VDDA(2.5V)

MAINON

VIN

B B

PWM

SUSON

VIN

DCIN S4 OFF

A A

5

ALWAYS ON

1.8VSUS

SW

MAINON

PWM

12A

VRON

S3 OFF

4

3

VCC1.8

VTERM

(0.9V)

+VCORE

2

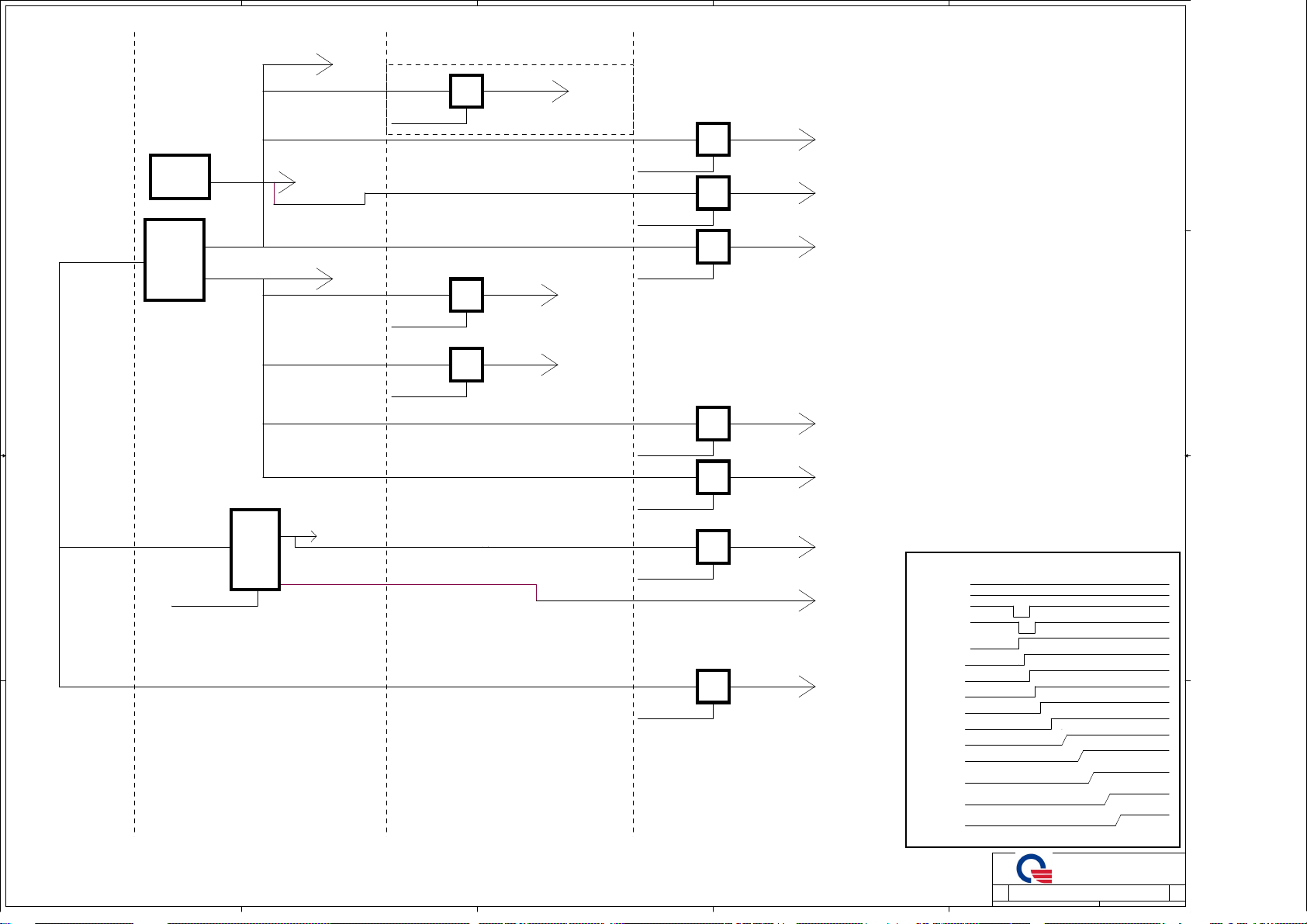

Power On Sequence

ACIN

5VPCU/3VPCU

NBSWON#

PWRBTN#

RVCC_ON

RSMRST#

SUSB#,SUSC#

SUSON

MAINON

VSUS,VCC

VR_ON

VCORE_CPU

NB_PWRGD

PWROK

PCIRST#

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

SB600

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

EL3

EL3

EL3

2 35Tuesday, January 06, 2009

2 35Tuesday, January 06, 2009

2 35Tuesday, January 06, 2009

1A

1A

1A

Page 3

5

4

3

2

1

VCC3

L1 BK1608HS600_6L1 BK1608HS600_6

D D

CLK_VDD

C1

C1

22U/6.3V_8

22U/6.3V_8

C2

0.1U_4C20.1U_4

C3

0.1U_4C30.1U_4

C4

0.1U_4C40.1U_4

C5

*0.1U_4C5*0.1U_4

C6

0.1U_4C60.1U_4

C7

0.1U_4C70.1U_4

C8

0.1U_4C80.1U_4

C9

0.1U_4C90.1U_4

CLK_VDDA

C10

C10

0.1U_4

0.1U_4

L2 BK1608HS600_6L2 BK1608HS600_6

C11

C11

10U_0805

10U_0805

VCC3

Put Decoupling Caps close to Clock Gen. power pin

VCC3

C13

C13

0.1U_4

0.1U_4

C15

C15

0.1U_4

0.1U_4

Y1

Y1

14.318MHZ

14.318MHZ

CLK_VDD_USB

CLK_VDD_REF

21

R4

*1M_4R4*1M_4

L3 BK1608HS600_6L3 BK1608HS600_6

C12

C12

10u/6.3V_6

10u/6.3V_6

VCC3

L4 BK1608HS600_6L4 BK1608HS600_6

C14

C14

10u/6.3V_6

10u/6.3V_6

C C

CLK_VDD

R5

10K_4R510K_4

C16 33P_4C16 33P_4

C17 33P_4C17 33P_4

Parallel Resonance Crystal

SCLK013,15

SDATA013,15

C18

C18

C19

C19

*0.1U_4

*0.1U_4

*0.1U_4

*0.1U_4

B B

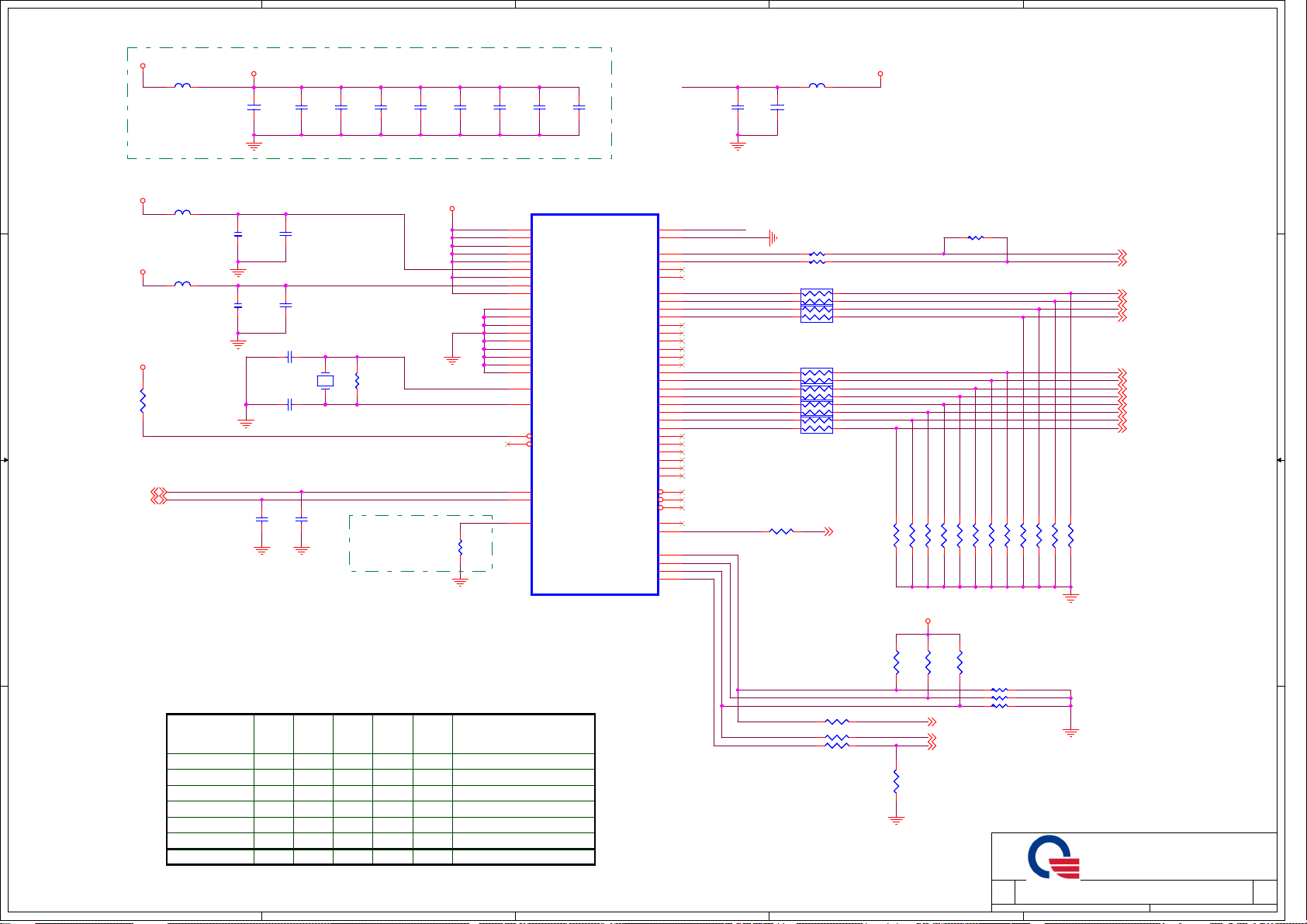

EXT CLK FREQUENCY SELECT TABLE(MHZ)

FS1

FS2

0 0 0

0 0 1

A A

0 1 0

0 1 1

1 0 0

1 0 1

1 1 1

5

CPU

FS0 HTT

SRCCLK

[2:1]

100.00

Hi-Z

100.00

X

100.00

180.00

100.00 48.00

220.00

100.00

100.00

100.00

133.33

200.00

100.00

Ioh = 5 * Iref

(2.32mA)

Voh = 0.71V @ 60 ohm

PCI

Hi-Z

Hi-Z

X/3 X/6

30.00

60.00

73.12

36.56

66.66

33.33

33.33

66.66

66.66

33.33 48.00

4

CLK_VDD

CLK_XIN

CLK_XOUT

R16

R16

475/F_4

475/F_4

CLKREQA# CONTROL SRC5,6,7

CLKREQB# CONTROL SRC2,3,4 ATIG3

CLKREQC# CONTROL SRC0,1 ATIG0,1,2

USB

48.00

48.00

48.00

COMMENT

Reserved

Reserved

Reserved

54

14

23

28

44

5

39

2

60

53

15

22

29

45

8

38

1

58

3

4

11

61

9

10

48

U1

U1

VDDCPU

VDD_SRC1

VDD_SRC2

VDD_SRC3

VDD_SRC4

VDD_48

VDD_ATIG

VDD_REF

VDDHTT

GND_CPU

GND_SRC1

GND_SRC2

GND_SRC3

GND_SRC4

GND_48

GND_ATIG

GND_REF

GNDHTT

XIN

XOUT

RESET_IN#

NC

SMBCLK

SMBDAT

IREF

ICS951462

ICS951462

Reserved

48.00

Reserved

48.00

Reserved

Normal operation

VDDA

GNDA

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

SRCCLKT6

SRCCLKC6

ATIGCLKT0

ATIGCLKC0

ATIGCLKT1

ATIGCLKC1

ATIGCLKT2

ATIGCLKC2

ATIGCLKT3

ATIGCLKC3

SRCCLKT5

SRCCLKC5

SRCCLKT4

SRCCLKC4

SRCCLKT3

SRCCLKC3

SRCCLKT2

SRCCLKC2

SRCCLKT0

SRCCLKC0

SRCCLKT1

SRCCLKC1

SRCCLKT7

SRCCLKC7

CLKREQA#

CLKREQB#

CLKREQC#

48MHz_1

48MHz_0

FS1/REF1

FS0/REF0

FS2/REF2

HTTCLK0

3

50

49

56

55

52

51

16

17

41

40

37

36

35

34

30

31

18

19

20

21

24

25

26

27

47

46

43

42

12

13

57

32

33

7

6

63

64

62

59

CLK_VDDA

CPUCLK_EXT_R

CPUCLK#_EXT_R

SBLINK_CLKP_R

SBLINK_CLKN_R

NBSRC_CLKP_R

NBSRC_CLKN_R

SBSRC_CLKP_R

SBSRC_CLKN_R

GPP_CLK0P_R

GPP_CLK0N_R

GPP_CLK1P_R

GPP_CLK1N_R

GPP_CLK2P_R

GPP_CLK2N_R

CLK_48M_2_R

R2 47.5/F_4R2 47.5/F_4

R3 47.5/F_4R3 47.5/F_4

3

RP1 33X2RP1 33X2

1

1

RP2 33X2RP2 33X2

3

3

RP3

RP3

1

3

RP4

RP4

1

3

RP5

RP5

1

3

RP6

RP6

1

R8 33//F_4R8 33//F_4

48MHZ

SB_OSCIN_R

NB_OSCIN_R

HTREFCLK_R

R28 33_4R28 33_4

R29 33_4R29 33_4

R30 33_4R30 33_4

4

2

2

4

4

33X2

33X2

2

4

33X2

33X2

2

4

33X2

33X2

2

4

33X2

33X2

2

USBCLK 15

R9 49.9/F_4R9 49.9/F_4

2

R22

R22

10K_4

10K_4

R31

R31

49.9/F-4

49.9/F-4

R1 261/F_4R1 261/F_4

R11 49.9/F_4R11 49.9/F_4

R10 49.9/F_4R10 49.9/F_4

R17 49.9/F_4R17 49.9/F_4

CLK_VDD

R23

R23

10K_4

10K_4

SB_OSCIN 15

NB_OSC 10

HTREFCLK 10

66MHZ

CPUCLKP 6

CPUCLKN 6

SBLINK_CLKP 10

SBLINK_CLKN 10

NBSRC_CLKP 10

NBSRC_CLKN 10

CLK_PCIE_WLAN 21

CLK_PCIE_WLAN# 21

CLK_PCIE_LAN 25

CLK_PCIE_LAN# 25

SBSRCCLKP 14

SBSRCCLKN 14

PE0CLK+ 27

PE0CLK- 27

R12 49.9/F_4R12 49.9/F_4

R18 49.9/F_4R18 49.9/F_4

R24

R24

10K_4

10K_4

R25 *0_4R25 *0_4

R26 *0_4R26 *0_4

R27 *0_4R27 *0_4

R14 49.9/F_4R14 49.9/F_4

R20 49.9/F_4R20 49.9/F_4

R19 49.9/F_4R19 49.9/F_4

R13 49.9/F_4R13 49.9/F_4

R15 49.9/F_4R15 49.9/F_4

R21 49.9/F_4R21 49.9/F_4

14MHZ

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Clock Generator

Clock Generator

Clock Generator

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

BenQ

BenQ

BenQ

3 35Tuesday, January 06, 2009

3 35Tuesday, January 06, 2009

3 35Tuesday, January 06, 2009

1

200MHZ

100MHZ

100MHZ

1A

1A

1A

Page 4

5

4

3

2

1

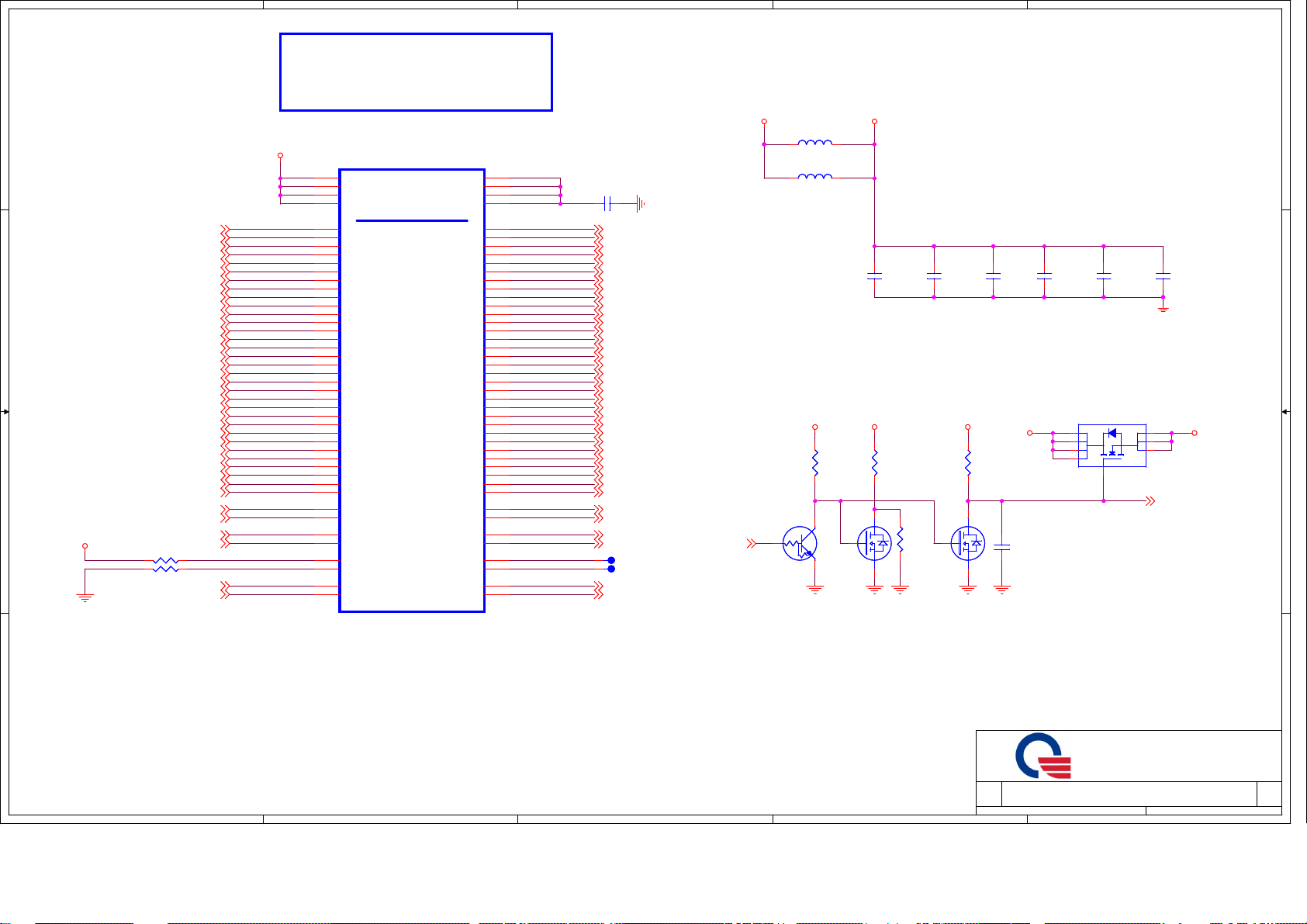

LAYOUT NOTE: VLDT must be routed as

a pour or a trace at least 100 mils wide.

VLDT may be routed from the source to

either ALx balls or Fx balls. Choose

whichever makes routing simpler.

D D

VLDT_RUN

HT_CADIN15_P8

HT_CADIN15_N8

HT_CADIN14_P8

HT_CADIN14_N8

HT_CADIN13_P8

HT_CADIN13_N8

HT_CADIN12_P8

HT_CADIN12_N8

HT_CADIN11_P8

C C

B B

VLDT_RUN

HT_CADIN11_N8

HT_CADIN10_P8

HT_CADIN10_N8

HT_CADIN9_P8

HT_CADIN9_N8

HT_CADIN8_P8

HT_CADIN8_N8

HT_CADIN7_P8

HT_CADIN7_N8

HT_CADIN6_P8

HT_CADIN6_N8

HT_CADIN5_P8

HT_CADIN5_N8

HT_CADIN4_P8

HT_CADIN4_N8

HT_CADIN3_P8

HT_CADIN3_N8

HT_CADIN2_P8

HT_CADIN2_N8

HT_CADIN1_P8

HT_CADIN1_N8

HT_CADIN0_P8

HT_CADIN0_N8

HT_CLKIN1_P8

HT_CLKIN1_N8

HT_CLKIN0_P8

HT_CLKIN0_N8

R32 51_4R32 51_4

R33 51_4R33 51_4

HT_CTLIN0_P8

HT_CTLIN0_N8

HT_CTLIN1_P

HT_CTLIN1_N

U2A

U2A

AL4

VLDT_B4

AL3

VLDT_B3

AL2

VLDT_B2

AL1

VLDT_B1

Y6

L0_CADIN_H15

Y5

L0_CADIN_L15

W7

L0_CADIN_H14

W6

L0_CADIN_L14

U6

L0_CADIN_H13

U5

L0_CADIN_L13

R7

L0_CADIN_H12

R6

L0_CADIN_L12

M8

L0_CADIN_H11

M7

L0_CADIN_L11

L6

L0_CADIN_H10

L5

L0_CADIN_L10

J6

L0_CADIN_H9

J5

L0_CADIN_L9

H4

L0_CADIN_H8

H3

L0_CADIN_L8

T3

L0_CADIN_H7

T4

L0_CADIN_L7

T2

L0_CADIN_H6

T1

L0_CADIN_L6

P3

L0_CADIN_H5

P4

L0_CADIN_L5

P2

L0_CADIN_H4

P1

L0_CADIN_L4

M2

L0_CADIN_H3

M1

L0_CADIN_L3

K3

L0_CADIN_H2

K4

L0_CADIN_L2

K2

L0_CADIN_H1

K1

L0_CADIN_L1

H2

L0_CADIN_H0

H1

L0_CADIN_L0

P6

L0_CLKIN_H1

P5

L0_CLKIN_L1

M3

L0_CLKIN_H0

M4

L0_CLKIN_L0

P8

L0_CTLIN_H1

P9

L0_CTLIN_L1

V2

L0_CTLIN_H0

V1

L0_CTLIN_L0

CPU_EBGA_812_Balls

CPU_EBGA_812_Balls

VLDT_A4

VLDT_A3

VLDT_A2

VLDT_A1

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

HT LINK

HT LINK

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

F4

F3

F2

F1

Y9

Y8

AB6

AB5

AC7

AC6

AE6

AE5

AE9

AE8

AH3

AH4

AK3

AK4

AK1

AK2

Y1

Y2

Y4

Y3

AB1

AB2

AB4

AB3

AD4

AD3

AF1

AF2

AF4

AF3

AH1

AH2

AF6

AF5

AD1

AD2

HT_CPU_CTLOUT1_P

AB8

HT_CPU_CTLOUT1_N

AB9

V4

V3

C20

C20

4.7U_6

4.7U_6

HT_CADOUT15_P 8

HT_CADOUT15_N 8

HT_CADOUT14_P 8

HT_CADOUT14_N 8

HT_CADOUT13_P 8

HT_CADOUT13_N 8

HT_CADOUT12_P 8

HT_CADOUT12_N 8

HT_CADOUT11_P 8

HT_CADOUT11_N 8

HT_CADOUT10_P 8

HT_CADOUT10_N 8

HT_CADOUT9_P 8

HT_CADOUT9_N 8

HT_CADOUT8_P 8

HT_CADOUT8_N 8

HT_CADOUT7_P 8

HT_CADOUT7_N 8

HT_CADOUT6_P 8

HT_CADOUT6_N 8

HT_CADOUT5_P 8

HT_CADOUT5_N 8

HT_CADOUT4_P 8

HT_CADOUT4_N 8

HT_CADOUT3_P 8

HT_CADOUT3_N 8

HT_CADOUT2_P 8

HT_CADOUT2_N 8

HT_CADOUT1_P 8

HT_CADOUT1_N 8

HT_CADOUT0_P 8

HT_CADOUT0_N 8

HT_CLKOUT1_P 8

HT_CLKOUT1_N 8

HT_CLKOUT0_P 8

HT_CLKOUT0_N 8

HT_CTLOUT0_P 8

HT_CTLOUT0_N 8

VLDT_ON26

T3T3

T4T4

VCC1.2

*FBJ3216HS800_1206

*FBJ3216HS800_1206

*FBJ3216HS800_1206

*FBJ3216HS800_1206

2

PQ36

PQ36

DDTC144EUA-7-F

DDTC144EUA-7-F

L5

L5

L6

L6

VLDT_RUN

C21

C21

4.7u/6.3V_6

4.7u/6.3V_6

C22

C22

4.7u/6.3V_6

4.7u/6.3V_6

VLDT_RUN

VLDT_RUN 15VPCU5VPCU

PR123

PR123

100K_6

100K_6

VLDTONG VLDTD

ME2N7002E

ME2N7002E

1 3

1

PQ37

PQ37

32

PR124

PR124

22R

22R

PR126

PR126

*1K

*1K

ME2N7002E

ME2N7002E

1

PQ38

PQ38

C25

C24

C23

C23

.22u/6.3V_4

.22u/6.3V_4

VCC1.2 VLDT_RUN

PR1251MPR125

1M

32

C24

.22u/6.3V_4

.22u/6.3V_4

PC128

PC128

*2200p/50V/X7R

*2200p/50V/X7R

C25

180P_NPO_4

180P_NPO_4

AO4468

AO4468

PQ35

PQ35

8

7

5

4

1

2

36

VLDTD 34

C26

C26

180P_NPO_4

180P_NPO_4

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

HT LINK

HT LINK

HT LINK

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

1

BENQ

BENQ

BENQ

4 35Tuesday, January 06, 2009

4 35Tuesday, January 06, 2009

4 35Tuesday, January 06, 2009

1A

1A

1A

Page 5

5

U2C

U2C

AN13

RSVD1

AL14

RSVD2

AL16

RSVD3

AN17

RSVD4

AN12

RSVD5

AM12

RSVD6

AM16

RSVD7

AN16

RSVD8

AL18

RSVD9

AN19

RSVD10

AM24

RSVD11

D D

C C

B B

A A

AN24

AM18

AN18

AL22

AN23

AM25

AL26

AN28

AL28

AL24

AN25

AN27

AM28

AM29

AL30

AL32

AL33

AK28

AN29

AM31

AM32

E33

D31

B31

A31

F33

F31

C32

B32

C30

A29

B26

A26

B30

A30

A27

C26

A24

B24

C18

A18

A25

C24

C20

A19

C16

A16

B14

A13

B18

A17

C14

A14

K33

K31

G32

F32

L33

K32

H31

G33

H33

AN15

AN20

AK26

AN31

C33

C28

A20

D14

H32

AM14

AN14

AL20

AM20

AN26

AM26

AN30

AM30

D33

D32

B28

A28

A21

B20

B16

A15

J33

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD54

RSVD55

RSVD56

RSVD57

RSVD58

RSVD59

RSVD60

RSVD61

RSVD62

RSVD63

RSVD64

RSVD65

RSVD66

RSVD67

RSVD68

RSVD69

RSVD70

RSVD71

RSVD72

RSVD73

RSVD74

RSVD75

RSVD76

RSVD77

RSVD78

RSVD79

RSVD80

RSVD81

RSVD82

RSVD83

RSVD84

RSVD85

RSVD86

RSVD87

RSVD88

RSVD89

RSVD90

RSVD91

RSVD92

RSVD93

RSVD94

RSVD95

RSVD96

RSVD97

RSVD98

RSVD99

CPU_EBGA_812_Balls

CPU_EBGA_812_Balls

5

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

DDR2: DATA

DDR2: DATA

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_DQS_H8

MA_DQS_L8

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM8

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

AG11

AH11

AJ12

AJ14

AF11

AF12

AG12

AH12

AK14

AF15

AH19

AK20

AF14

AG14

AF17

AG19

AG20

AJ20

AF22

AK24

AF19

AF20

AJ23

AG23

AF23

AF25

AH27

AK30

AJ25

AG25

AJ26

AJ28

D28

G28

D26

E26

F30

E29

F27

H26

H25

D24

H22

E22

F26

G26

D22

G23

G22

G20

G15

F15

D20

F22

D16

E17

H15

H14

G12

H12

E15

E14

E11

F11

K30

J29

G29

F29

L28

L29

H29

H27

H30

AL12

AK16

AK22

AJ27

E27

E23

H19

G14

J27

J26

AJ11

AK12

AG15

AH15

AH22

AG22

AG26

AH26

E28

F28

E25

F25

G17

H17

E12

F12

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

4

MEM_MA_DATA[63..0] 13

MEM_MA_DM[7..0] 13

MEM_MA_DQS7_P 13

MEM_MA_DQS7_N 13

MEM_MA_DQS6_P 13

MEM_MA_DQS6_N 13

MEM_MA_DQS5_P 13

MEM_MA_DQS5_N 13

MEM_MA_DQS4_P 13

MEM_MA_DQS4_N 13

MEM_MA_DQS3_P 13

MEM_MA_DQS3_N 13

MEM_MA_DQS2_P 13

MEM_MA_DQS2_N 13

MEM_MA_DQS1_P 13

MEM_MA_DQS1_N 13

MEM_MA_DQS0_P 13

MEM_MA_DQS0_N 13

4

3

Processor DDR2 Memory Interface

SMDDR_VTERM

U2B

PLACE THEM CLOSE TO

CPU WITHIN 1"

1.8VSUS

to power block

R36

R36

39.2F_4

39.2F_4

1 2

R37

R37

39.2F_4

39.2F_4

1 2

SMDDR_VTERM

MEM_MA_ADD[15..0]13

C37

C37

4.7U_6

4.7U_6

C29

C29

4.7U_6

4.7U_6

CPU_VTT_SUS_SENSE33

CPU_M_VREF

M_ZN

M_ZP

M_A_CS#113

M_A_CS#013

M_CKE013

M_A_BS#213

M_A_BS#113

M_A_BS#013

M_A_RAS#13

M_A_CAS#13

M_A_WE#13

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

LAYOUT NOTE: Decoupling between CPU and DIMM.

Place close to CPU as possible.

C32

C38

C38

4.7U_6

4.7U_6

C30

C30

4.7U_6

4.7U_6

3

C39

C39

0.22U_4

0.22U_4

C31

C31

0.22U_4

0.22U_4

C40

C40

0.22U_4

0.22U_4

C32

0.22U_4

0.22U_4

A12

B12

C12

D12

AK10

AN10

AL10

AM10

B11

A11

B10

AG9

AH9

AH29

AE29

AH30

AF29

AK33

AF33

AJ32

AF31

N33

P32

M30

M28

P30

M29

AG28

P28

T30

AC28

P27

R26

R27

U28

V30

U27

Y30

AB29

W29

AC26

R29

AC29

AE28

AC27

AF30

AE27

C41

C41

0.01U_4

0.01U_4

C33

C33

0.01U_4

0.01U_4

U2B

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA1_CS_L1

MA1_CS_L0

MA0_CS_L1

MA0_CS_L0

RSVD100

RSVD101

RSVD102

RSVD103

RSVD104

RSVD105

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

CPU_EBGA_812_Balls

CPU_EBGA_812_Balls

C42

C42

0.01U_4

0.01U_4

C34

C34

0.01U_4

0.01U_4

DDR2: CMD/CTRL/CLK

DDR2: CMD/CTRL/CLK

C43

C43

180P_4

180P_4

2

MA1_CLK_H2

MA1_CLK_L2

MA1_CLK_H1

MA1_CLK_L1

MA1_CLK_H0

MA1_CLK_L0

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MA0_CLK_H0

MA0_CLK_L0

RSVD106

RSVD107

RSVD108

RSVD109

RSVD110

RSVD111

RSVD112

RSVD113

RSVD114

RSVD115

RSVD116

RSVD117

RSVD118

RSVD119

MA1_ODT0

MA0_ODT0

RSVD120

RSVD121

RSVD122

RSVD123

RSVD124

RSVD125

RSVD126

RSVD127

RSVD128

RSVD130

RSVD131

RSVD132

RSVD133

RSVD134

RSVD135

RSVD136

RSVD137

RSVD138

RSVD139

RSVD140

RSVD141

RSVD142

C35

C35

180P_4

180P_4

2

C44

C44

180P_4

180P_4

1

1.8VSUS

CPU_M_VREF

C27

C27

C28

C28

0.1U_4

0.1U_4

1000P_4

AH17

AG17

E20

E19

AB27

AB26

AK18

AJ17

D18

F19

Y28

Y27

AN21

AM21

A22

A23

AB33

AB32

AN22

AM22

C22

B22

AA32

AA33

AH31

AH33

AF27

AG29

P33

P31

AJ33

T32

T31

AD32

T33

V32

U33

V33

V31

W33

Y31

Y33

Y32

AC33

R33

AD33

AE33

AF32

AH32

AG33

C36

C36

180P_4

180P_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

M_CLKOUT1 13

M_CLKOUT1# 13

M_CLKOUT0 13

M_CLKOUT0# 13

M_ODT1 13M_CKE113

M_ODT0 13

DDR2

DDR2

DDR2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1000P_4

1

BENQ

BENQ

BENQ

5 35Tuesday, January 06, 2009

5 35Tuesday, January 06, 2009

5 35Tuesday, January 06, 2009

R393

R393

300/F_4

300/F_4

R394

R394

300/F_4

300/F_4

1A

1A

1A

Page 6

5

4

3

2

1

HDT Connector

1.8VSUS

R47 300_4R47 300_4

R46 220_4R46 220_4

R45 220_4R45 220_4

R43 220_4R43 220_4

R44 220_4R44 220_4

D D

C C

B B

A A

LDT_RST#

If AMD SI is not used, the SID pin can be left unconnected and SIC

should have a 300-Ω (±5%) pulldown to VSS.

1.8VSUS

CPU_SIC14

CPU_SID14

C50 0.1U_4C50 0.1U_4

C52 2200P_6C52 2200P_6

SYS_SHDN#110,12

VCC3

Vout =1.25(1+R1/R2)

= 1.25 (1+100K/100K)

1.8VSUS

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

1.8VSUS VCC3

R52

R52

10K_4

10K_4

2

1 3

Q2

Q2

*MMBT3904

*MMBT3904

R57 300_4R57 300_4

R61 *300_4R61 *300_4

THERM_VCC

H_THERMDA

H_THERMDC

SYS_SHDN#1

PU1

PU1

1

SHDN

2

GND

3

VIN

12

G923-330T1UF

G923-330T1UF

PC2

PC2

1u/6.3V_4

1u/6.3V_4

CN1

CN1

*ASP-68200-07-25P-LDV

*ASP-68200-07-25P-LDV

1

3

5

7

9

11

13

15

17

19

21

23

KEY

KEY

R53

R53

1K/F_4

1K/F_4

H_HTCPU_RST#

U3

U3

1

VCC

2

DXP

3

DXN

4

-OVT

G781-1

G781-1

MSOP8-4_9-65

MSOP8-4_9-65

4

VO

5

SET

PR4

PR4

100K/F_6

100K/F_6

GND1

RSVD1

RSVD0

DBREQ_L

DBRDY

TCK

TMS

TDI

TRST_L

TDO

VCC_PROC_IO_21

VCC_PROC_IO_23

CPU_SIC_R

CPU_SID_R

R65 0R_6R65 0R_6

SMBUS Add. : 9Ah

SMBUS Add. : 9Ah

SMDATA

PR3

PR3

100K/F_6

100K/F_6

R62300_4 R62300_4

C51

C51

*0.1U

*0.1U

SMCLK

-ALT

GND

GND2

GND4

GND6

GND8

GND10

GND12

GND14

GND16

GND18

GND20

GND22

RESET_L

GND26

C508 100U/10V+C508 100U/10V

+

8

7

6

5

12

CPU_VDDA

2

4

6

8

10

12

14

16

18

20

22

24

25

VCC3

Thermal

Senser

TALERT#

CPU_VDDA

PC1

PC1

1u/6.3V_4

1u/6.3V_4

L7 40ohm_600mA L7 40ohm_600mA

VDDA_RUN

C45

C45

4.7U_0603

4.7U_0603

LDT_RST#14

CPU_PWRGD14

CPU_LDTSTOP#10,14

To power Block

CPU_CORE

COREEFB+V32

COREEFB-32

CPU_VDDIO_SUS_FB_H33

CPUCLKP3

CPUCLKN3

SMBUS SLAVE ADDRESS

G781

G781-1

THMCLK 10

THMDAT 10

TALERT# 10,16

12

C46

C46

0.22U

0.22U

close to CPU

*10/F_6

*10/F_6

C48 3900p_4C48 3900p_4

C49 3900p_4C49 3900p_4

98 (NB)

9A (CPU)

CPU_PROCHOT#_1P8V

C47

C47

3300pF

3300pF

1.8VSUS

R48

R48

300_4

300_4

VLDT_RUN

PR1

PR1

PR2*10/F_6 PR2*10/F_6

T7T7

R54

R54

169_4

169_4

CPU_TEST25_H_BYPASSCLK_P

CPU_TEST25_L_BYPASSCLK_N

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

T8T8

T10T10

T12T12

T14T14

T15T15

VCC3

R414

R414

4.7K

4.7K

1.8VSUS

R268

R268

10K_4

10K_4

2

1 3

MMBT3904

MMBT3904

Q39

Q39

CPU_SIC_R

CPU_SID_R

R49 44.2_4R49 44.2_4

R50 44.2_4R50 44.2_4

VCC3

CPU_HTREF1

CPU_HTREF0

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

H_THERMDC

H_THERMDA

R269

R269

4.7K

4.7K

TALERT_2# 16

U2D

U2D

A8

VDDA2

B8

VDDA1

AK6

RESET_L

AM2

PWROK

AM6

LDTSTOP_L

AN4

SIC

AN5

SID

V10

HT_REF1

V9

HT_REF0

E2

VDD_FB_H

E1

VDD_FB_L

AM9

VDDIO_FB_H

AK9

VDDIO_FB_L

A6

CLKIN_H

A7

CLKIN_L

AH8

DBRDY

AN8

TMS

AK8

TCK

AL8

TRST_L

AM8

TDI

A9

TEST25_H

B9

TEST25_L

A5

TEST19

B6

TEST18

AJ9

TEST13

H8

TEST9

J8

TEST17

C8

TEST16

D9

TEST15

H7

TEST14

AN3

TEST12

C6

TEST7

AH7

TEST6

AL6

THERMDC

AM5

THERMDA

AJ5

TEST3

AJ7

TEST2

M31

RSVD143

L32

RSVD144

M33

RSVD145

CPU_EBGA_812_Balls

CPU_EBGA_812_Balls

M32

RSVD146

W27

RSVD147

W26

RSVD148

AJ29

RSVD149

P26

RSVD150

M26

RSVD151

AJ30

RSVD152

THERMTRIP_L

PROCHOT_L

VID5

VID4

VID3

VID2

VID1

VID0

CPU_PRESENT_L

PSI_L

DBREQ_L

TDO

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD153

RSVD154

RSVD155

RSVD156

RSVD157

RSVD158

RSVD159

RSVD160

RSVD161

RSVD162

RSVD163

RSVD164

RSVD165

RSVD166

MISC

MISC

CPU_THERMTRIP#

AJ6

CPU_PROCHOT#_1P8V

AN6

B2

C2

C1

D2

D1

D3

CPU_PRESENT#

AM3

E4

CPU_DBREQ#

AN9

AN7

CPU_TEST29_H_FBCLKOUT_P

E9

CPU_TEST29_L_FBCLKOUT_N

D10

AH6

AG8

AN11

F9

AM7

G11

H11

AJ8

CPU_TEST26

AM4

D7

B5

L27

B25

G6

A10

B7

E8

G5

G7

AB31

AB30

AK31

AD31

AD30

AK32

R71 *10K_4R71 *10K_4

VCC3

VCC3

R73 *10K_4R73 *10K_4

VCC3

R395 22K_4R395 22K_4

R396 22K_4R396 22K_4

R51 1K_4R51 1K_4

PSI# 32

T6T6

CPU_TDO

CPU_TEST24_SCANCLK1

CPU_TEST23_TSTUPD

CPU_TEST22_SCANSHIFTEN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

To power Block

CPU_TEST25_H_BYPASSCLK_P

CPU_TEST25_L_BYPASSCLK_N

R70 0_4R70 0_4

1

THMCLK MBCLK

1

R75 0_4R75 0_4

R397 22K_4R397 22K_4

R399 22K_4R399 22K_4

R398 22K_4R398 22K_4

R55 80.6/F_4R55 80.6/F_4

= 2.5V

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MISC

MISC

MISC

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1.8VSUS1.8VSUS

VCC3

R400 22K_4R400 22K_4

R40 *300_4R40 *300_4

R39 300_4R39 300_4

R38 300_4R38 300_4

R41

R41

R42

R42

10K_4

10K_4

4.7K

4.7K

2

1 3

MMBT3904

MMBT3904

Q1

Q1

THERMTRIP# 12,15

To power Block

VID5 32

VID4 32

VID3 32

VID2 32

VID1 32

VID0 32

1.8VSUS

CPU_TEST26

CPU_TEST18_PLLTEST1

T9T9

CPU_TEST19_PLLTEST0

T11T11

CPU_TEST21_SCANEN

T13T13

T16T16

Q3

Q3

*2N7002E-LF

*2N7002E-LF

MBDATATHMDAT

3

2

2

3

*2N7002E-LF

*2N7002E-LF

Q4

Q4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

R58

R58

300_4

300_4

R66 510/F_4R66 510/F_4

R67 510/F_4R67 510/F_4

MBDATA 26

MBCLK 26

BENQ

BENQ

BENQ

6 35Tuesday, January 06, 2009

6 35Tuesday, January 06, 2009

6 35Tuesday, January 06, 2009

1

1.8VSUS

1.8VSUS

R59

R59

300_4

300_4

R56

R56

300_4

300_4

R60

R60

300_4

300_4

1A

1A

1A

Page 7

5

CPU_CORE CPU_CORE 1.8VSUS

D D

C C

B B

CPU_CORE

C55

C55

C54

C54

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

U2E

U2E

K10

K12

K14

K18

K20

K21

K23

K25

L11

L13

M10

M12

M25

N11

N24

N25

P15

P18

P20

P24

P25

J10

J12

J14

J18

J20

J21

J23

A3

A4

B3

B4

C3

C4

D4

D5

D6

E5

E6

E7

F5

F6

F7

F8

G8

G9

H9

J9

L7

L9

M5

N9

VDDC#A3

VDDC#A4

VDDC#B3

VDDC#B4

VDDC#C3

VDDC#C4

VDDC#D4

VDDC#D5

VDDC#D6

VDDC#E5

VDDC#E6

VDDC#E7

VDDC#F5

VDDC#F6

VDDC#F7

VDDC#F8

VDDC#G8

VDDC#G9

VDDC#H9

VDDC#J9

VDDC#J10

VDDC#J12

VDDC#J14

VDDC#J18

VDDC#J20

VDDC#J21

VDDC#J23

VDDC#K10

VDDC#K12

VDDC#K14

VDDC#K18

VDDC#K20

VDDC#K21

VDDC#K23

VDDC#K25

VDDC#L7

VDDC#L9

VDDC#L11

VDDC#L13

VDDC#M5

VDDC#M10

VDDC#M12

VDDC#M25

VDDC#N9

VDDC#N11

VDDC#N24

VDDC#N25

VDDC#P15

VDDC#P18

VDDC#P20

VDDC#P24

VDDC#P25

CPU_EBGA_812_Balls

CPU_EBGA_812_Balls

VDDC#AA10

VDDC#AA12

VDDC#AA24

VDDC#AA25

VDDC#AB11

VDDC#AB13

VDDC#AC10

VDDC#AC12

VDDC#AC24

VDDC#AC25

VDDC#AD11

VDDC#AD12

VDDC#AD14

VDDC#AD18

VDDC#AD21

VDDC#AD25

VDDC#AE12

VDDC#AE14

VDDC#AE18

VDDC#AE21

VDDC#AE23

POWER1

POWER1

VDDC#AC5

VDDC#AD9

VDDC#V25

VDDC#V24

VDDC#Y19

VDDC#Y16

VDDC#Y14

VDDC#W20

VDDC#W18

VDDC#W15

VDDC#W5

VDDC#V19

VDDC#V16

VDDC#V14

VDDC#T20

VDDC#T18

VDDC#T15

VDDC#T10

VDDC#R19

VDDC#R16

VDDC#R14

VDDC#R5

AA10

AA12

AA24

AA25

AB11

AB13

AC5

AC10

AC12

AC24

AC25

AD9

AD11

AD12

AD14

AD18

AD21

AD25

AE12

AE14

AE18

AE21

AE23

V25

V24

Y19

Y16

Y14

W20

W18

W15

W5

V19

V16

V14

T20

T18

T15

T10

R19

R16

R14

R5

LAYOUT NOTE: Bottom side decoupling.

C60

C56

C56

22U/6.3V_8

22U/6.3V_8

C57

C57

22U/6.3V_8

22U/6.3V_8

C58

C58

22U/6.3V_8

22U/6.3V_8

C59

C59

22U/6.3V_8

22U/6.3V_8

C60

22U/6.3V_8

22U/6.3V_8

C61

C61

22U/6.3V_8

22U/6.3V_8

4

C62

C62

22U/6.3V_8

22U/6.3V_8

U2F

U2F

Y29

VDDIO#Y29

U29

VDDIO#U29

R28

VDDIO#R28

P29

VDDIO#P29

W32

VDDIO#W32

W30

VDDIO#W30

W28

VDDIO#W28

U30

VDDIO#U30

N30

VDDIO#N30

U32

VDDIO#U32

R32

VDDIO#R32

R30

VDDIO#R30

N32

VDDIO#N32

U26

VDDIO#U26

Y26

VDDIO#Y26

M27

VDDIO#M27

AG32

VDDIO#AG32

AG30

VDDIO#AG30

AF28

VDDIO#AF28

AE30

VDDIO#AE30

AE26

VDDIO#AE26

AC32

VDDIO#AC32

AC30

VDDIO#AC30

AE32

VDDIO#AE32

AB28

VDDIO#AB28

AA30

VDDIO#AA30

CPU_EBGA_812_Balls

CPU_EBGA_812_Balls

3

U2G

U2G

A32

VSS1

AA1

VSS2

AA2

VSS3

AA4

VSS4

AA9

VSS5

AA11

VSS6

AA22

VSS7

AA23

VSS8

AB10

VSS9

AB12

VSS10

AB21

VSS11

AB22

VSS12

AB23

VSS13

AB24

VSS14

AB25

VSS15

AC11

VSS16

AC1

VSS17

AC2

VSS18

AC4

VSS19

AC8

VSS20

AC9

VSS21

AC13

VSS22

AC21

VSS23

AC22

VSS24

AC23

VSS25

AD10

VSS26

AD13

VSS27

AD16

VSS28

AD20

VSS29

AD22

VSS30

AD23

VSS31

AD24

VSS32

AE1

POWER2

POWER2

VSS33

AE2

VSS34

AE4

VSS35

AE7

VSS36

AE10

VSS37

AE11

VSS38

AE13

VSS39

AE16

VSS40

AE20

VSS41

AE22

VSS42

AE24

VSS43

AE25

VSS44

AF7

VSS45

AF8

VSS46

AF9

VSS47

AF26

VSS48

AG1

VSS49

AG2

VSS50

AG4

VSS51

AG6

VSS52

AG7

VSS53

AG27

VSS54

AH5

VSS55

AH14

VSS56

AH20

VSS57

AH23

VSS58

AH25

VSS59

AH28

VSS60

CPU_EBGA_812_Balls

CPU_EBGA_812_Balls

GND1

GND1

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

VSS61

G4

G2

G1

F23

F20

F14

E32

E30

D30

D29

D27

D25

D23

D21

D19

D17

D15

D13

D11

D8

C31

B33

B29

B27

B21

B19

B17

B15

B13

C10

AN32

AN2

AM33

AM27

AM23

AM19

AM17

AM15

AM13

AM11

AM1

AL31

AK29

AK27

AK25

AK23

AK21

AK19

AK17

AK15

AK13

AK11

AK7

AK5

AJ22

AJ19

AJ15

AJ4

AJ2

AJ1

2

U2H

U2H

G19

VSS121

G25

VSS123

G27

VSS124

G30

VSS125

H5

VSS126

H6

VSS127

H20

VSS128

H23

VSS129

H28

VSS130

J1

VSS131

J2

VSS132

J4

VSS133

J7

VSS134

J11

VSS135

J13

VSS136

J16

VSS137

J22

VSS138

J24

VSS139

J25

VSS140

J28

VSS141

J30

VSS142

J32

VSS143

K11

VSS144

K13

VSS145

K16

VSS146

A2

VSS147

K22

VSS148

K24

VSS149

K9

VSS150

L1

VSS151

L2

VSS152

L4

VSS153

L8

VSS154

L10

VSS155

L12

VSS156

L21

VSS157

L22

VSS158

L23

VSS159

L24

VSS160

L25

VSS161

L26

VSS162

L30

VSS163

M6

VSS164

M9

VSS165

M11

VSS166

M13

VSS167

M21

VSS168

M22

VSS169

M23

VSS170

M24

VSS171

N1

VSS172

N2

VSS173

N4

VSS174

N10

VSS175

N12

VSS176

N22

VSS177

N23

VSS178

P7

VSS179

P10

VSS180

P14

VSS181

P16

VSS182

P19

VSS183

CPU_EBGA_812_Balls

CPU_EBGA_812_Balls

GND2

GND2

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

1

R1

R2

R4

R8

R15

R18

R20

T9

T14

T16

T19

T24

T25

V15

V18

V20

U1

U2

U4

U7

U8

W1

W2

W4

W8

W14

W16

W19

Y7

Y10

Y15

Y18

Y20

Y24

Y25

F17

AB7

AG5

B23

B1

CPU_CORE

3

1.8VSUS

C67

C67

4.7U_6

4.7U_6

C68

C68

4.7U_6

4.7U_6

C69

C69

0.22U_4

0.22U_4

C70

C70

0.22U_4

0.22U_4

C509

C509

0.22U_4

0.22U_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CPU Power and GND

CPU Power and GND

CPU Power and GND

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

1

BENQ

BENQ

BENQ

7 35Tuesday, January 06, 2009

7 35Tuesday, January 06, 2009

7 35Tuesday, January 06, 2009

1A

1A

1A

C63

C63

C64

C64

0.22U_4

0.22U_4

0.22U_4

0.22U_4

1.8VSUS

A A

C72

C72

C71

C71

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C65

C65

0.01U_4

0.01U_4

C73

C73

4.7U_6

4.7U_6

5

C66

C66

180P_4

180P_4

C74

C74

4.7U_6

4.7U_6

C75

C75

0.22U_4

0.22U_4

C76

C76

0.22U_4

0.22U_4

C77

C77

0.22U_4

0.22U_4

C78

C78

0.01U_4

0.01U_4

C79

C79

180P_4

180P_4

4

C80

C80

180P_4

180P_4

C81

C81

180P_4

180P_4

C510

C510

0.01U_4

0.01U_4

Page 8

5

D D

C C

B B

RS69012

HT_CADOUT15_P4

HT_CADOUT15_N4

HT_CADOUT14_P4

HT_CADOUT14_N4

HT_CADOUT13_P4

HT_CADOUT13_N4

HT_CADOUT12_P4

HT_CADOUT12_N4

HT_CADOUT11_P4

HT_CADOUT11_N4

HT_CADOUT10_P4

HT_CADOUT10_N4

HT_CADOUT9_P4

HT_CADOUT9_N4

HT_CADOUT8_P4

HT_CADOUT8_N4

HT_CADOUT7_P4

HT_CADOUT7_N4

HT_CADOUT6_P4

HT_CADOUT6_N4

HT_CADOUT5_P4

HT_CADOUT5_N4

HT_CADOUT4_P4

HT_CADOUT4_N4

HT_CADOUT3_P4

HT_CADOUT3_N4

HT_CADOUT2_P4

HT_CADOUT2_N4

HT_CADOUT1_P4

HT_CADOUT1_N4

HT_CADOUT0_P4

HT_CADOUT0_N4

HT_CLKOUT1_P4

HT_CLKOUT1_N4

HT_CLKOUT0_P4

HT_CLKOUT0_N4

HT_CTLOUT0_P4

HT_CTLOUT0_N4

R77 49.9/F_4R77 49.9/F_4 R78 100F_4R78 100F_4

R79 49.9/F_4R79 49.9/F_4

4

HT_RXCALP

HT_RXCALN

R19

R18

R21

R22

U22

U21

U18

U19

W19

W20

AC21

AB22

AB20

AA20

AA19

Y19

T24

R25

U25

U24

V23

U23

V24

V25

AA25

AA24

AB23

AA23

AB24

AB25

AC24

AC25

W21

W22

Y24

W25

P24

P25

A24

C24

U4A

U4A

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALP

HT_RXCALN

3

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

P21

P22

P18

P19

M22

M21

M18

M19

L18

L19

G22

G21

J20

J21

F21

F22

N24

N25

L25

M24

K25

K24

J23

K23

G25

H24

F25

F24

E23

F23

E24

E25

L21

L22

J24

J25

N23

P23

C25

D24

2

1

HT_CADIN15_P 4

HT_CADIN15_N 4

HT_CADIN14_P 4

HT_CADIN14_N 4

HT_CADIN13_P 4

HT_CADIN13_N 4

HT_CADIN12_P 4

HT_CADIN12_N 4

HT_CADIN11_P 4

HT_CADIN11_N 4

HT_CADIN10_P 4

HT_CADIN10_N 4

HT_CADIN9_P 4

HT_CADIN9_N 4

HT_CADIN8_P 4

HT_CADIN8_N 4

HT_CADIN7_P 4

HT_CADIN7_N 4

HT_CADIN6_P 4

HT_CADIN6_N 4

HT_CADIN5_P 4

HT_CADIN5_N 4

HT_CADIN4_P 4

HT_CADIN4_N 4

HT_CADIN3_P 4

HT_CADIN3_N 4

HT_CADIN2_P 4

HT_CADIN2_N 4

HT_CADIN1_P 4

HT_CADIN1_N 4

HT_CADIN0_P 4

HT_CADIN0_N 4

HT_CLKIN1_P 4

HT_CLKIN1_N 4

HT_CLKIN0_P 4

HT_CLKIN0_N 4

HT_CTLIN0_P 4

HT_CTLIN0_N 4

HT_TXCALP

HT_TXCALN

RS690E

RS690E

A A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

RS690E HT

RS690E HT

RS690E HT

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BENQ

BENQ

BENQ

8 35Tuesday, January 06, 2009

8 35Tuesday, January 06, 2009

8 35Tuesday, January 06, 2009

1

1A

1A

1A

Page 9

5

D D

A LINK

G5

G4

J8

J7

J4

J5

L8

L7

L4

L5

M8

M7

M4

M5

P8

P7

4

U4B

U4B

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

PART 2 OF 6

PART 2 OF 6

PCIE I/F GFX

PCIE I/F GFX

3

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

J1

H2

K2

K1

K3

L3

L1

L2

N2

N1

P2

P1

P3

R3

R1

R2

close to connector.

2

PCIE 0 Ethernet

PCIE 1 Card Reader

PCIE 2 MINI Card

1

SOUTH BRIDGE LINK

A_TX2P_C

A_RX2P14

C C

GPP_RX1P_CARD27

GPP_RX1N_CARD27

SOUTH BRIDGE LINK

B B

A_RX2N14

A_RX3P14

A_RX3N14

PE2RX+21

PE2RX-21

GPP_RX3P_LAN25

GPP_RX3N_LAN25

GPP_RX0P_LAN25

GPP_RX0N_LAN25

A_RX0P14

A_RX0N14

A_RX1P14

A_RX1N14

A LINK

Y4

SB_RX2P(GPP_RX0P)

Y5

SB_RX2N(GPP_RX0N)

W4

SB_RX3P(GPP_RX1P)

W5

SB_RX3N(GPP_RX1N)

P4

GPP_RX2P

P5

GPP_RX2N

R4

GPP_RX3P

R5

GPP_RX3N

R7

GPP_RX0P(NC)

R8

GPP_RX0N(NC)

U4

GPP_RX1P(NC)

U5

GPP_RX1N(NC)

AB7

SB_RX0P

AB6

SB_RX0N

V9

SB_RX1P

W9

SB_RX1N

SB_TX2P(GPP_TX0P)

SB_TX2N(GPP_TX0N)

SB_TX3P(GPP_TX1P)

SB_TX3N(GPP_TX1N)

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX0P(NC)

GPP_TX0N(NC)

GPP_TX1P(NC)

GPP_TX1N(NC)

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

AA1

AA2

Y2

Y3

U2

U1

V2

V1

V3

W3

W1

W2

AC1

AC2

AB1

AB2

A_TX2N_C

A_TX3P_C

A_TX3N_C

C_PE2TX+

C_PE2TXGPP_TX3P

GPP_TX3N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

A_TX0P_C

A_TX0N_C

A_TX1P_C

A_TX1N_C

0.1u/10V_4C82 0.1u/10V_4C82

0.1u/10V_4C83 0.1u/10V_4C83

0.1u/10V_4C84 0.1u/10V_4C84

0.1u/10V_4C85 0.1u/10V_4C85

0.1u/10V_4C86 0.1u/10V_4C86

0.1u/10V_4C87 0.1u/10V_4C87

*0.1u/10V_4C511 *0.1u/10V_4C511

*0.1u/10V_4C512 *0.1u/10V_4C512

0.1u/10V_4C88 0.1u/10V_4C88

0.1u/10V_4C89 0.1u/10V_4C89

0.1u/10V_4C90 0.1u/10V_4C90

0.1u/10V_4C91 0.1u/10V_4C91

0.1u/10V_4C92 0.1u/10V_4C92

0.1u/10V_4C93 0.1u/10V_4C93

0.1u/10V_4C94 0.1u/10V_4C94

0.1u/10V_4C95 0.1u/10V_4C95

A_TX2P 14

A_TX2N 14

A_TX3P 14

A_TX3N 14

PE2TX+ 21

PE2TX- 21

GPP_TX0P_LAN 25

GPP_TX0N_LAN 25

GPP_TX1P_CARD 27

GPP_TX1N_CARD 27

A_TX0P 14

A_TX0N 14

A_TX1P 14

A_TX1N 14

A LINK

SOUTH BRIDGE LINK

MINI-Card Wireless lan

Ethernet RTL8102EL

Card Reader JMB385

A LINK

SOUTH BRIDGE LINK

R80 *10K/F_4R80 *10K/F_4

R82 *8.25K/F_4R82 *8.25K/F_4

A A

5

AC4

NC(PCE_ISET)

AD4

NC(PCE_TXISET)

PCE_CALRP(PCE_PCAL)

PCE_CALRN(PCE_NCAL)

RS690E

RS690E

4

3

AE4

AE3

R81 562/F_6R81 562/F_6

R83 2.05K/F_6R83 2.05K/F_6

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

VDDA12_PKG2 12

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

RS690E PCIE

RS690E PCIE

RS690E PCIE

2

BENQ

BENQ

BENQ

9 35Tuesday, January 06, 2009

9 35Tuesday, January 06, 2009

9 35Tuesday, January 06, 2009

1A

1A

1A

1

Page 10

5

VCC1.8

L8 FBMH1608HM221-T_6L8 FBMH1608HM221-T_6

L11 FBMH1608HM221-T_6L11 FBMH1608HM221-T_6

D D

L12 FBMH1608HM221-T_6L12 FBMH1608HM221-T_6

C C

CPU_LDTSTOP#6,14

VCC1.2

L17 FBMH1608HM221-T_6L17 FBMH1608HM221-T_6

B B

VCC3

R96 4.7K_4R96 4.7K_4

R97 4.7K_4R97 4.7K_4

R98 39K_4R98 39K_4

R100 10K_4R100 10K_4

AVDDQ

C96

C96

2.2uF/10V_6

2.2uF/10V_6

PLLVDD

C99

C99

2.2uF/10V_6

2.2uF/10V_6

HTPVDD

C100

C100

1u/10V_4

1u/10V_4

VCC1.8

2

1 3

Q7 MMBT3904Q7 MMBT3904

R89 *0_4R89 *0_4

PLLVDD1P2

C108

C108

2.2uF/10V_6

2.2uF/10V_6

DDC_CLK

DDC_DATA

NB_DDC_DATA

STRP DATA

R87

R87

10K_4

10K_4

VCC3

CRT_VSYNC29

CRT_HSYNC29

R88

R88

10K_4

10K_4

NB LDTSTOP

CRT_RED29

CRT_GRN29

CRT_BLU29

VCC1.2

4

VCC1.8

L10 FBMH1608HM221-T_6L10 FBMH1608HM221-T_6

L15 FBMH1608HM221-TL15 FBMH1608HM221-T

C103

C103

1u/10V_4

1u/10V_4

VCC3

VCC3

L9 FBMH1608HM221-T_6L9 FBMH1608HM221-T_6

2.2uF/10V_6C98 2.2uF/10V_6C98

CRTDCLK29

CRTDDAT29

C104

C104

4.7u/10V_6

4.7u/10V_6

NB_RST#14,20,21,25,27

NB_PWRGD12,26

ALLOW_LDTSTOP14

HTREFCLK3

SUS_STAT#15

NB_OSC3

NBSRC_CLKP3

NBSRC_CLKN3

SBLINK_CLKP3

SBLINK_CLKN3

BMREQ#14

DDC_CLK19

DDC_DATA19

T27T27

T29T29

C97

C97

2.2uF/10V_6

2.2uF/10V_6

AVDDQ

R84 715/F_6R84 715/F_6

R85 33_4R85 33_4

R86 33_4R86 33_4

PLLVDD

HTPVDD

NB LDTSTOP

R90 10K_4R90 10K_4

R91 *4.7K_4R91 *4.7K_4

PLLVDD1P2

NB_THERMDA

NB_THERMDC

TMDS_HPD

NB_DDC_DATA

R99 4.7K_4R99 4.7K_4

STRP DATA

AVDD_NB

DAC-SCLR

DAT_SDAR

TESTMODE

3

U4C

U4C

B22

AVDD1

C22

AVDD2

G17

AVSSN1

H17

AVSSN2

A20

AVDDDI

B20

AVSSDI

A21

AVDDQ

A22

AVSSQ

C21

C_R

C20

Y_G

D19

COMP_B

E19

RED

F19

GREEN

G19

BLUE

C6

DACVSYNC

A5

DACHSYNC

B21

RSET

B6

DACSCL

A6

DACSDA

A10

PLLVDD18

B10

PLLVSS

B24

HTPVDD

B25

HTPVSS

E7

VDDPLL_1(VDDA12)

F7

VDDPLL_2(VDDA12)

F9

VSSPLL_1(VSSA12)

G9

VSSPLL_2(VSSA12)

C10

SYSRESET#

C11

POWERGOOD

C5

LDTSTOP#

B5

ALLOW_LDTSTOP

C23

HTTSTCLK

B23

HTREFCLK

C2

TVCLKIN

B11

OSCIN

A11

PLLVDD12(OSCOUT)

F2

GFX_CLKP

E1

GFX_CLKN

G1

SB_CLKP

G2

SB_CLKN

B2

BMREQb

A2

I2C_CLK

B4

I2C_DATA

AD5

THERMALDIODE_P

AE5

THERMALDIODE_N

C14

TMDS_HPD

B3

DDC_DATA

C3

TESTMODE

A3

STRP_DATA

RS690E

RS690E

PART 3 OF 6

PART 3 OF 6

CRT/TVOUT

CRT/TVOUT

LVDDR33_1(LVDDR18A_1)

LVDDR33_2(LVDDR18A_2)

PLL PWR

PLL PWR

PM

PM

CLOCKs

CLOCKs

MISC

MISC

LVDS

LVDS

TXOUT_L0P

TXOUT_L0N

TXOUT_L1P

TXOUT_L1N

TXOUT_L2P

TXOUT_L2N

TXOUT_L3P

TXOUT_L3N

TXOUT_U0P

TXOUT_U0N

TXOUT_U1P

TXOUT_U1N

TXOUT_U2P

TXOUT_U2N

TXOUT_U3P

TXOUT_U3N

TXCLK_LP

TXCLK_LN

TXCLK_UP

TXCLK_UN

LPVDD

LPVSS

LVDDR18D_1

LVDDR18D_2

LVSSR1

LVSSR3

LVSSR5

LVSSR6

LVSSR7

LVSSR8

LVSSR12

LVSSR13

LVDS_DIGON

LVDS_BLON

LVDS_BLEN

DFT_GPIO0

DFT_GPIO1

DFT_GPIO2

DFT_GPIO3

DFT_GPIO4

DFT_GPIO5

B14

B15

B13

A13

H14

G14

D17

E17

A15

B16

C17

C18

B17

A17

A18

B18

E15

D15

H15

G15

D14

E14

A12

B12

C12

C13

A16

A14

D12

C19

C15

C16

F14

F15

E12

G12

F12

D6

D7

C8

C7

B8

A8

2

LPVDD

LVDDR3P3A

DEF GPIO0

LOAD ROM#

DEF GPIO2

DEF GPIO3

DEF GPIO4

DEF GPIO5

LVDS_TX0+ 19

LVDS_TX0- 19

LVDS_TX1+ 19

LVDS_TX1- 19

LVDS_TX2+ 19

LVDS_TX2- 19

LVDS_TX3+ 19

LVDS_TX3- 19

LVDS_TX4+ 19

LVDS_TX4- 19

LVDS_TX5+ 19

LVDS_TX5- 19

LVDS_TX6+ 19

LVDS_TX6- 19

LVDS_TX7+ 19

LVDS_TX7- 19

LVDS_CLK_L+ 19

LVDS_CLK_L- 19

LVDS_CLK_U+ 19

LVDS_CLK_U- 19

L13 FBMH1608HM221-T_6L13 FBMH1608HM221-T_6

LVDDR1P8D

L14

L14

FBMH1608HM221-T_6

FBMH1608HM221-T_6

L16

L16

FBMH1608HM221-T_6

FBMH1608HM221-T_6

C105

C105

0.1u/10V_4

0.1u/10V_4

VCC1.8

VCC3

C106

C106

2.2uF/10V_6

2.2uF/10V_6

C101

C101

0.1u/10V_4

0.1u/10V_4

DESIGN NOTE:THE FOLLOWING DEBUG

POINTS SHOULD BE PROVIDED.

LVDS DIGON 19

LVDS BLON 19

LVDS BLEN 19

STRP DATA

NB_OSC

NB_PWRGD

DEF GPIO0

LOAD ROM#

DEF GPIO2

DEF GPIO3

DEF GPIO4

DEF GPIO5

LVDDR1P8D

C102

C102

2.2uF/10V_6

2.2uF/10V_6

LPVDD

C107

C107

0.1u/10V_4

0.1u/10V_4

1

T18T18

T19T19

T20T20

T22T22

T23T23

T24T24

T25T25

T26T26

T28T28

Thermal

VCC3

VCC

DXP

DXN

-OVT

R101 0R_6R101 0R_6

C110

C110

SMBUS Add. : 98h

SMBUS Add. : 98h

SMCLK

SMDATA

-ALT

GND

*0.1U

*0.1U

4

8

7

6

5

TALERT# 6,16

THMCLK 6

THMDAT 6

SMBUS SLAVE ADDRESS

G781

G781-1

3

98 (NB)

9A (CPU)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

RS690E MSIC

RS690E MSIC

RS690E MSIC

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

1

BENQ

BENQ

BENQ

10 35Tuesday, January 06, 2009

10 35Tuesday, January 06, 2009

10 35Tuesday, January 06, 2009

1A

1A

1A

Senser

C109 0.1UC109 0.1U

U5

A A

C111 2200P_0603C111 2200P_0603

SYS_SHDN#16,12

5

THERM_NB_VCC

NB_THERMDA

NB_THERMDC

U5

1

2

3

4

G781

G781

MSOP8-4_9-65

MSOP8-4_9-65

Page 11

5

4

3

2

1

DESIGN NOTE:THE FOLLOWING DEBUG

POINTS SHOULD BE PROVIDED.

U4F

U4F

D D

C C

B B

T35T35

T36T36

T37T37

T30T30

T38T38

T39T39

T31T31

T40T40

T32T32

T33T33

T34T34

T41T41

T42T42

T43T43

T44T44

T45T45

VCC1.8

R104

R104

1K/F_4

1K/F_4

MEM_VREF1

R107

R107

1K/F_4

1K/F_4

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_BA0

MEM_BA1

C114

C114

0.1u/10V_4

0.1u/10V_4

W12

MEM_A0(NC)

AD10

MEM_A1(NC)

AB12

MEM_A2(NC)

AB11

MEM_A3(NC)

W14

MEM_A4(NC)

AB15

MEM_A5(NC)

AB14

MEM_A6(NC)

AE9

MEM_A7(NC)

AA12

MEM_A8(NC)

AC9

MEM_A9(NC)

AE10

MEM_A10(NC)

Y14

MEM_A11(NC)

AD9

MEM_A12(NC)

AA11

MEM_A13(NC)

AC11

MEM_BA0(NC)

AE11

MEM_BA1(NC)

AD11

MEM_BA2(NC)

AA15

MEM_RASb(NC)

Y15

MEM_CASb(NC)

AC14

MEM_WEb(NC)

V12

MEM_CSb(NC)

AD12

MEM_CKE(NC)

Y9

MEM_ODT(NC)

W15

MEM_CKP(NC)

V15

MEM_CKN(NC)

AC16

MEM_DM0(NC)

AD19

MEM_DM1/DVO_D8(DVO_D8)

AE17

MEM_DQS0P/DVO_IDCKP(DVO_IDCKP)

AD17

MEM_DQS0N/DVO_IDCKN(DVO_IDCKN)

AD21

MEM_DQS1P(NC)

AC20

MEM_DQS1N(NC)

PAR 6 OF 6

PAR 6 OF 6

MEM_DQ0/DVO_VSYNC(DVO_VSYNC)

MEM_DQ1/DVO_HSYNC(DVO_HSYNC)

SBD_MEM/DVO_I/F

SBD_MEM/DVO_I/F

MEM_DQ2/DVO_DE(DVO_DE)

MEM_DQ3/DVO_D0(DVO_D0)

MEM_DQ4(NC)

MEM_DQ5/DVO_D1(DVO_D1)

MEM_DQ6/DVO_D2(DVO_D2)

MEM_DQ7/DVO_D4(DVO_D4)

MEM_DQ8/DVO_D3(DVO_D3)

MEM_DQ9/DVO_D5(DVO_D5)

MEM_DQ10/DVO_D6(DVO_D6)

MEM_DQ11/DVO_D7(DVO_D7)

MEM_DQ12(NC)

MEM_DQ13/DVO_D9(DVO_D9)

MEM_DQ14/DVO_D10(DVO_D10)

MEM_DQ15/DVO_D11(DVO_D11)

MEM_COMPP(NC)

MEM_COMPN(NC)

MEM_VREF(NC)

IOPLLVDD18(NC)

IOPLLVSS(NC)

IOPLLVDD12(NC)

AD13

AE13

AC13

AD14

AC15

AD15

AE15

AE16

AD16

AC17

AD18

AE19

AC19

AE20

AD20

AE21

R105 40R2/F_4R105 40R2/F_4

Y11

R106 40R2/F_4R106 40R2/F_4

W11

AE12

AA17

Y17

AB17

C112

C112

2.2uF/10V_6

2.2uF/10V_6

C113

C113

2.2uF/10V_6

2.2uF/10V_6

MEM_VREF1

IOPLLVDD18

IOPLLVDD12

IOPLLVDD12

IOPLLVDD18

L18

L18

FBMH1608HM221-T

FBMH1608HM221-T

L19 FBMH1608HM221-TL19 FBMH1608HM221-T

VCC1.8 VCC1.2

RS690E

RS690E

A A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

RS690E PCIE

RS690E PCIE

RS690E PCIE

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BENQ

BENQ

BENQ

11 35Tuesday, January 06, 2009

11 35Tuesday, January 06, 2009

11 35Tuesday, January 06, 2009

1

1A

1A

1A

Page 12

5

4

3

2

1

C129

C129

10u/10V_8

10u/10V_8

C137

C137

0.1u/10V_4

0.1u/10V_4

VCC1.2

C118

C118

10u/10V_8

10u/10V_8

VCC1.2

C138

C138

0.1u/10V_4

0.1u/10V_4

VCC1.2

U4D

U4D

AE24

C120

C120

C121

C121

C122

C122

C123

C123

C115

C115

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

VCC1.8

L20

D D

VCC1.2

L21

L21

FBMH1608HM221-T_6

FBMH1608HM221-T_6

VCC1.8

L22

L22

FBMH1608HM221-T_6

FBMH1608HM221-T_6

C C

B B

A A

L20

FBMH1608HM221-T

FBMH1608HM221-T

C139

C139

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

C147

C147

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

A25

F11

D23

E9

G11

Y23

P11

R24

AC18

M15

J22

G23

J12

L12

L14

L20

L23

M11

M20

M23

M25

N12

N14

B7

L24

P13

P20

P15

R12

R14

R20

W23

Y25

AD25

U20

H25

W24

Y22

AC23

D25

G24

AA14

H12

AC22

R23

C4

Y12

T23

T25

V11

R17

H23

C140

C140

C148

C148

U4E

U4E

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

C119

C119

1u/10V_4

1u/10V_4

C141

C141

1u/10V_4

1u/10V_4

C150

C150

1u/10V_4

1u/10V_4

VDD1.8

C130

C130

1u/10V_4

1u/10V_4

C142

C142

1u/10V_4

1u/10V_4

C151

C151

1u/10V_4

1u/10V_4

PAR 5 OF 6

PAR 5 OF 6

GROUND

GROUND

C143

C143

1u/10V_4

1u/10V_4

VDDDVO

C152

C152

1u/10V_4

1u/10V_4

VSSA1

VSSA2

VSSA3

VSSA4

VSSA5

VSSA6

VSSA7

VSSA8

VSSA9

VSSA10

VSSA11

VSSA12

VSSA13

VSSA14

VSSA15

VSSA16

VSSA17

VSSA18

VSSA19

VSSA20

VSSA21

VSSA22

VSSA23

VSSA24

VSSA25

VSSA26

VSSA27

VSSA28

VSSA29

VSSA30

VSS66

VSS65

VSS64

VSS62

VSS63

VSS61

VSS60

VSS59

VSS58

VSS57

VSS56

VSS55

VSS54

VSS53

RS6908

C116

C116

10u/10V_8

10u/10V_8

VDDA1.2

C149

C149

10u/10V_8

10u/10V_8

C153

C153

10u/10V_8

10u/10V_8

M3

P9

G6

AE1

F3

AD1

A1

H1

G3

J2

H3

AA3

J6

Y7

F1

L6

M2

M6

J3

P6

T1

N3

R9

R6

T2

T3

U3

U6

W6

Y1

AC12

AC10

V14

W17

AB19

AE18

AE14

M13

VSSA

AA7

D4

F17

VSSA

AC6

A23

M17

C124

C124

10u/10V_8

10u/10V_8

VDD1.8

VDD3.3

C144

C144

10u/10V_8

10u/10V_8

C154

C154

10u/10V_8

10u/10V_8

AD24

AE25

AE22

AD22

AE23

AD23

D22

J14

J15

E11

D11

AC5

AB3

U7

W7

AB4

AC3

AD2

AE2

AD6

AC7

AC8

AA9

AD7

AB9

AE6

AE8

AE7

AD8

FAN

SYS_SHDN#16,10

PART 4 OF 6

PART 4 OF 6

VDD_HT1

VDD_HT2

VDD_HT3

VDD_HT4

VDD_HT5

VDD_HT6

VDD_HT7

VDDHT_PKG

VDD18_1

VDD18_2

VDDR3_2

VDDR3_1

VDDA12_13(VDDA18_1)

VDDA12_14(VDDA18_2)

VDDA12_15(VDDA18_3)

VDDA12_16(VDDA18_4)

VDDA12_17(VDDA18_5)

VDDA12_18(VDDA18_6)

VDDA12_19(VDDA18_7)

VDDA12_20(VDDA18_8)

VDD_MEM1(VDD_DVO1)

VDD_MEM2(VDD_DVO2)

VDD_MEM3(VDD_DVO3)

VDD_MEM4(VDD_DVO4)

VDD_MEM5(VDD_DVO5)

VDD_MEM6(VDD_DVO6)

VDD_MEM7(VDD_DVO7)

VDD_MEM8(VDD_DVO8)

VDD_MEM9(VDD_DVO9)

VDD_MEM10(VDD_DVO10)

RS690E

RS690E

VCC5

VFAN126

THERMTRIP#6,15

VDDA12_1

VDDA12_2

VDDA12_3

VDDA12_4

VDDA12_5

VDDA12_6

VDDA12_7

VDDA12_8

VDDA12_9

VDDA12_10

VDDA12_11

VDDA12_12

VDDA12_PKG2

VDDA12_PKG1

POWER

POWER

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDDC_24

VDDC_25

VDDC_26

VDDC_27

VDDC_28

VDDC_29

VDDC_30

VDDC_31

VDDC_32

2.2u/6.3V_6C156 2.2u/6.3V_6C156

U6

VIN2VO

1

FON#

4

VSET

G995U6G995

VCC1.2

D1

G7

E2

C1

E3

D2

M9

F4

B1

D3

L9

E6

AD3

M1

L11

L13

L15

M12

R15

M14

N11

N13

N15

J11

H11

P12

P14

R11

R13

A19

B19

U11

U14

P17

L17

J19

D20

G20

A9

B9

C9

D9

A7

A4

U12

U15

GND

GND

GND

GND

NB_PWRGD10,26

R110

R110

*56_4

*56_4

R111 33_4R111 33_4

10u/10V_8C131 10u/10V_8C131

FANSIG126

30 MIL

TH_FAN_POWER

3

5

6

C157

C157

7

8

2.2u/6.3V_6

2.2u/6.3V_6

R_THERMTRIP_PWR#

C117

C117

1u/10V_4

1u/10V_4

C132

C132

0.1u/10V_4

0.1u/10V_4

C145

C145

10u/10V_8

10u/10V_8

2

C125

C125

1u/10V_4

1u/10V_4

C133

C133

0.1u/10V_4

0.1u/10V_4

VCC1.2

C146

C146

10u/10V_8

10u/10V_8

VCC3

C158

C158

1000p/50V_4

1000p/50V_4

VCC1.2

3

Q8

2N7002EQ82N7002E

1

R109

R109

1K_4

1K_4

2

Q9

Q9

1 3

MMBT3904

MMBT3904

C127

C127

C128

CN2

CN2

1

2

345

C135

C135

FAN

FAN

C128

1u/10V_4

1u/10V_4

C136

C136

0.1u/10V_4

0.1u/10V_4

VDD3.3

C155

C155

2.2uF/10V_6

2.2uF/10V_6

C126

C126

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

VDDA12_PKG2 9

C134

C134

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

L23

L23

FBMH1608HM221-T_6

FBMH1608HM221-T_6

VCC3

R108

R108

10K_6

10K_6

C159

C159

0.01u/16V_4

0.01u/16V_4

125 Degree Protection

SYS_SHDN# 31

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev