Page 1

5

4

3

2

1

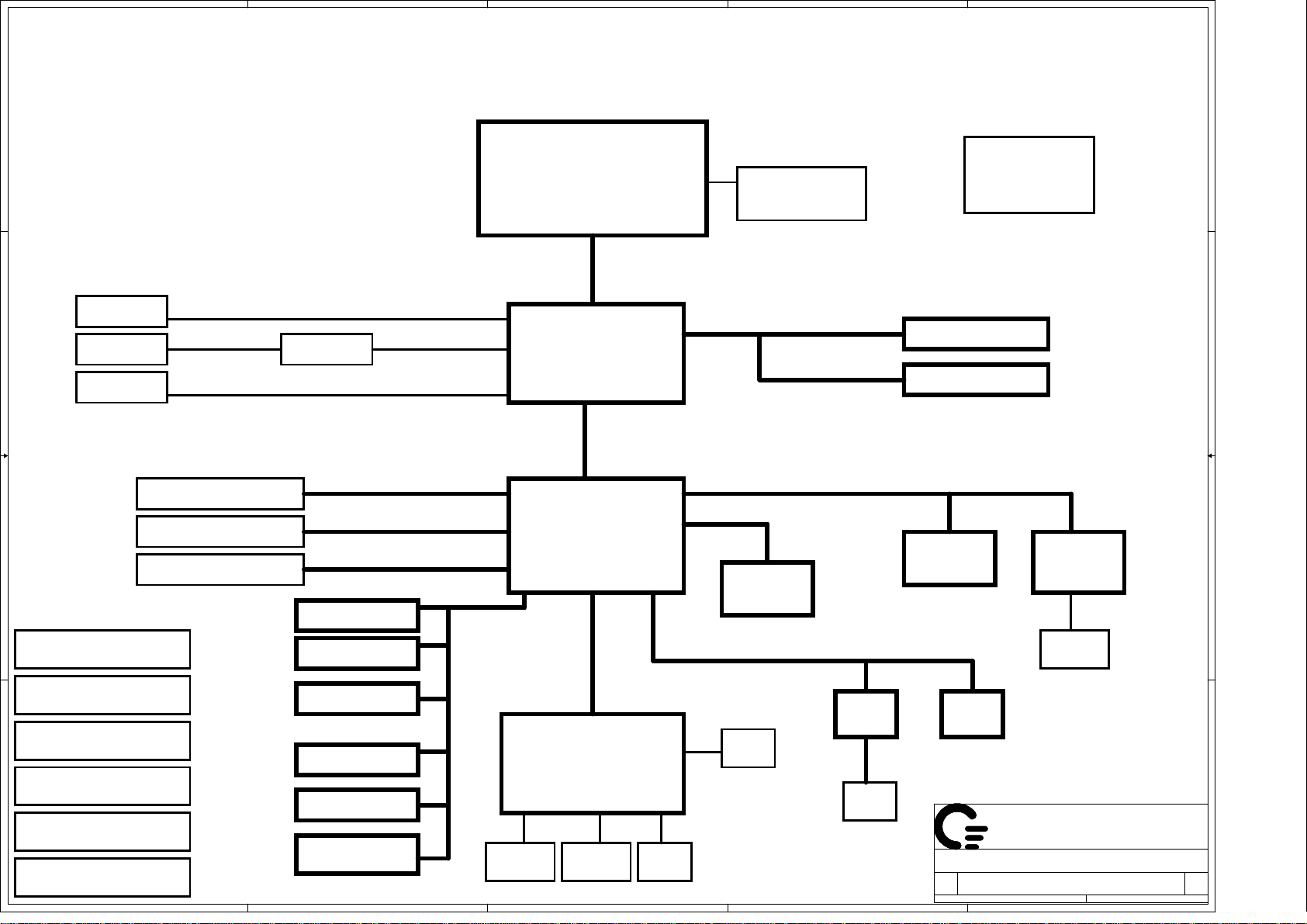

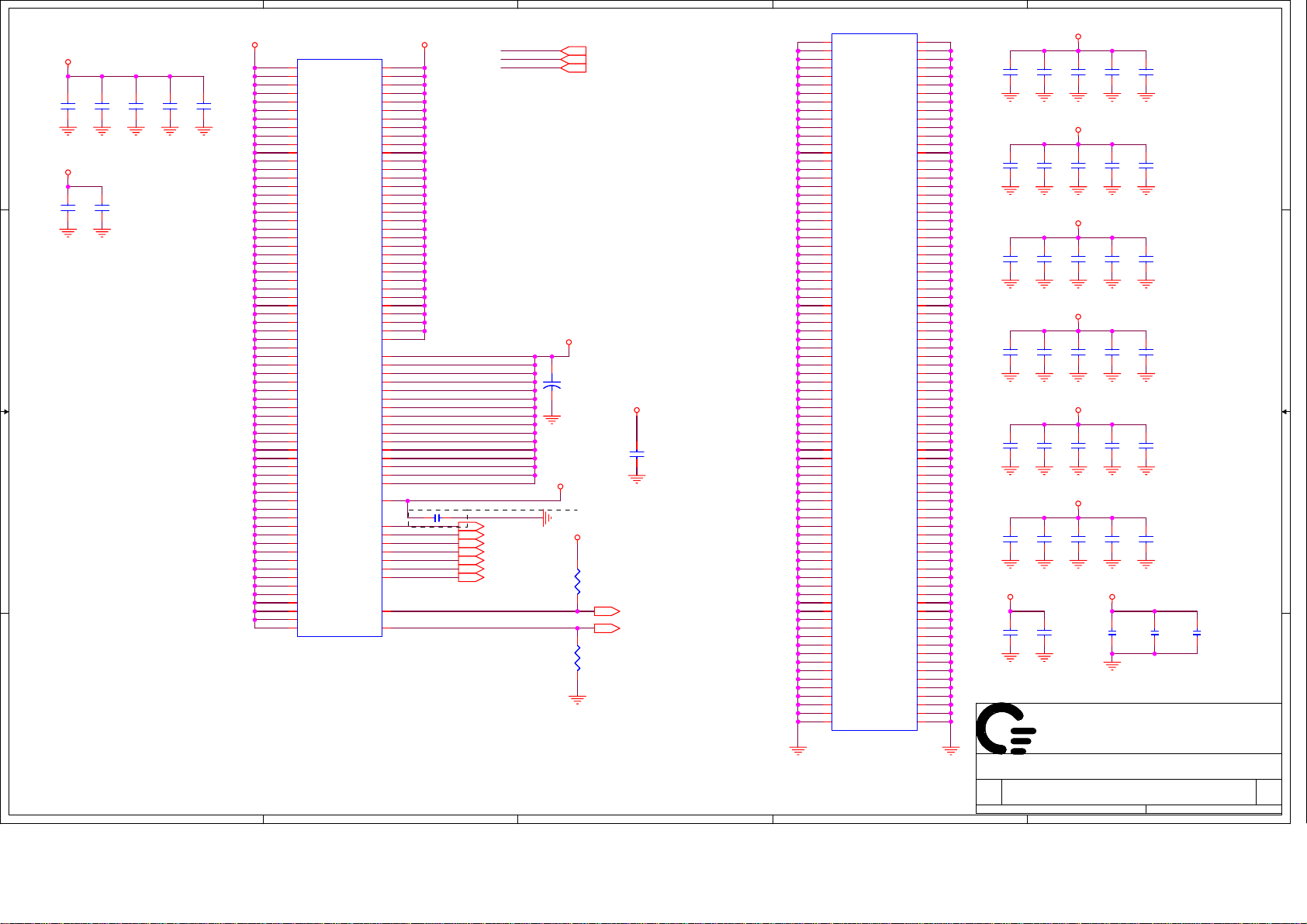

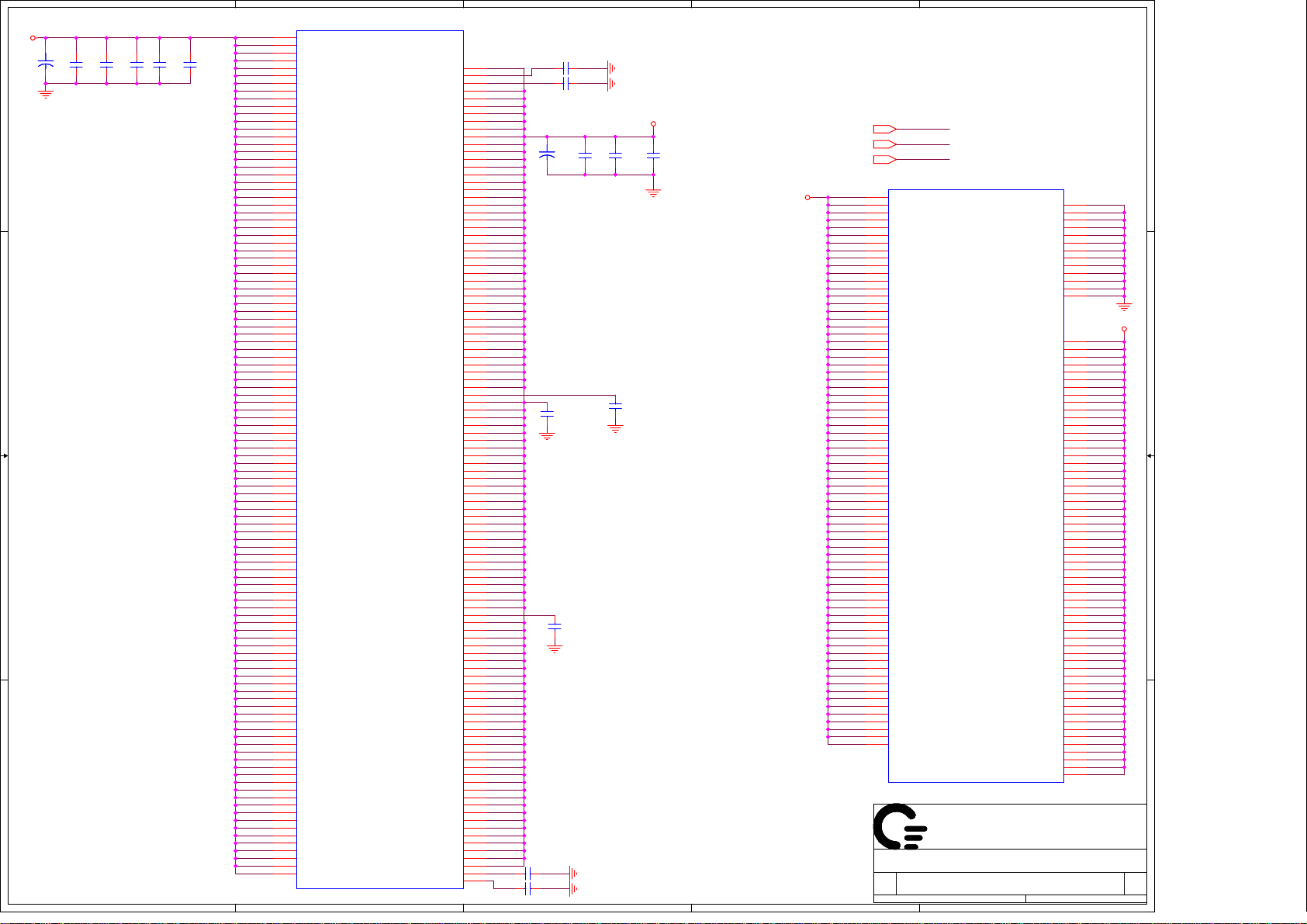

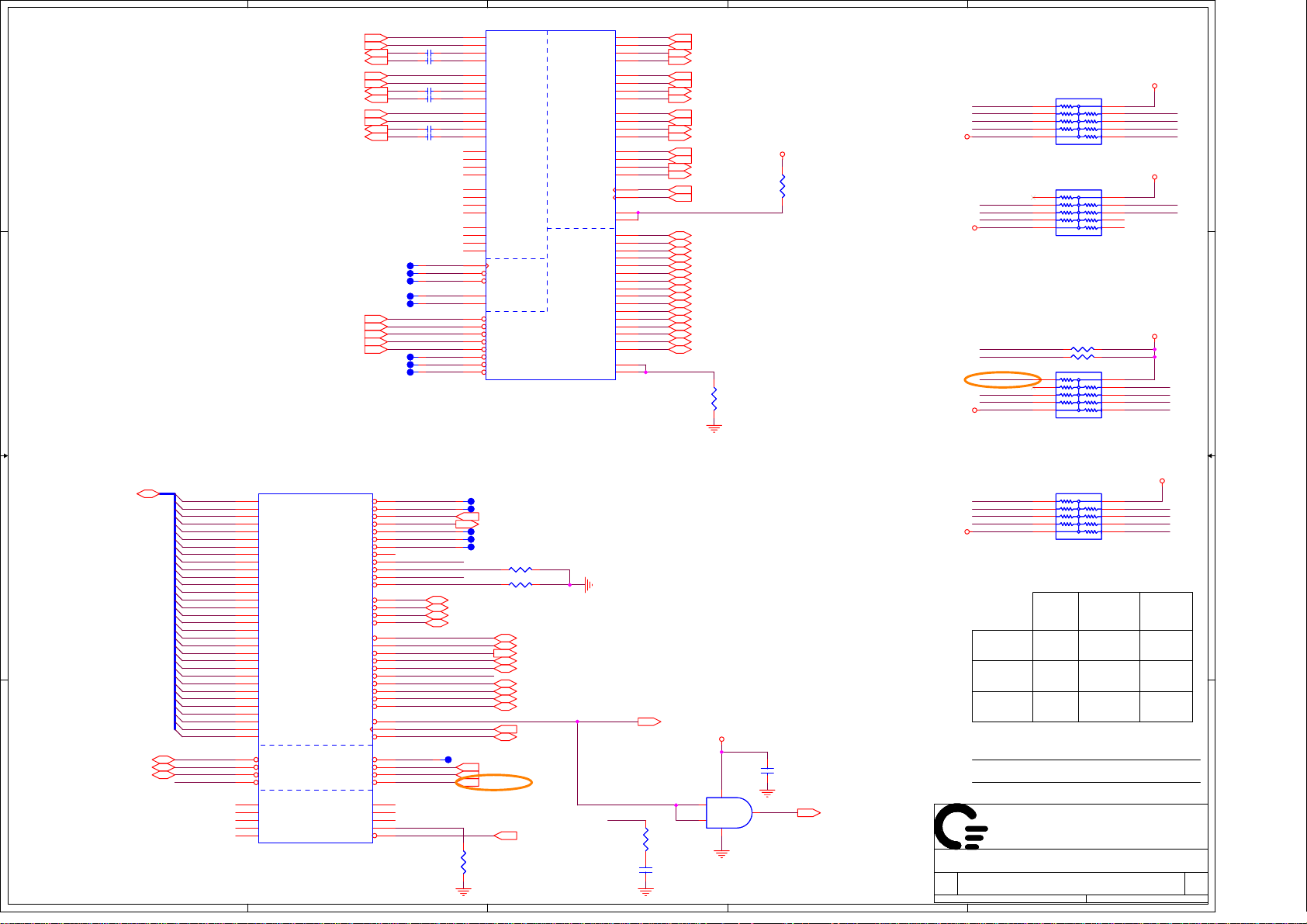

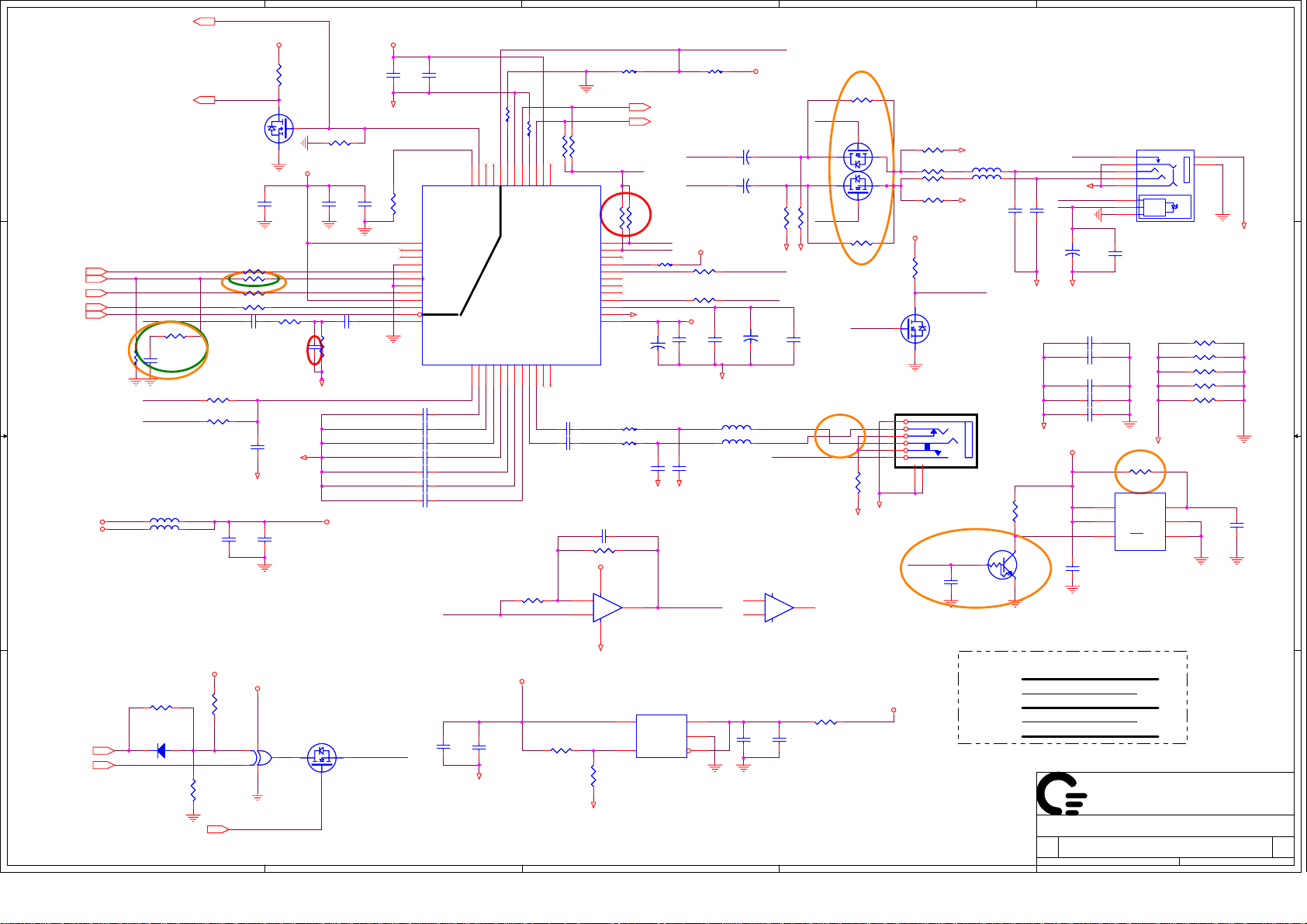

DO1 BLOCK DIAGRAM

01

YONAH+CALISTOGA+ICH_7

D D

Yonah / Merom

479 Pins

(Micro-FCPGA)

PG 4,5

FSB

533/667MHZ

S_VEDIO

PG 18

C C

LCD Panel

PG 19

CRT port

PG 18

L007

PG 28

LVDS

R.G,B

Calistoga

1466 LGA

PG 6~11

DMIx4

SATA HDD

SATA HDD

B B

Primary IDE - ODD

PG 27

PG 27

PG 27

SATA interface

SATA interface

PATA 66/100

USB 2.0

ICH7-M

652 BGA

PG 14,15,16,17

USB PORT 0,1

PG 26

CPU CORE

PG 30

PG 26

3.3V LPC, 33MHz

GMCHVTT & VCC1.5

PG 31

DC/DC 3V & 5V

PG 32

1.8V/0.9V/2.5V

A A

PG 33

USB PORT 4

USB PORT 5

TV MODULE

USB PORT 6

New card

PG 26

PG 25

PG 21

PC87541

176 Pins LQFP

PG 22

BATT CHARGER &

AC CONNECTOR

BATT CONNECTOR

PG 34

PG 35

5

USB PORT 7

Fingerprinter

PG 25

4

TouchPAD

PG 25

Keyboard

PG 26

3

FLASH

PG 22

CPU Thermal

Sensor

GMT781

DDR2 INTERFACE, 533/667 MHz

33MHZ, 3.3V PCI BUS

CARDBUS

R5C841

PG 20,21

Azalia

FAN 1

PG 25

PG 25

MDC

V1.5

RJ11

2

DDR-SODIMM1

DDR-SODIMM2

PCI-Express

MINI-PCI E

PG 29

SOCKET

Clock Generator

ICS954226AG

IDT CV111

PG 12

PG 12

PG 24

Audio

PG 30

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

COMPUTER

System Block Diagram

System Block Diagram

System Block Diagram

PG 13

LAN

BCM5751M

PG 23

RJ45USB PORT 2,3

PG 23

DO1

DO1

DO1

1

139Thursday, February 09, 2006

139Thursday, February 09, 2006

139Thursday, February 09, 2006

of

of

of

3C

3C

3C

Page 2

5

4

3

2

1

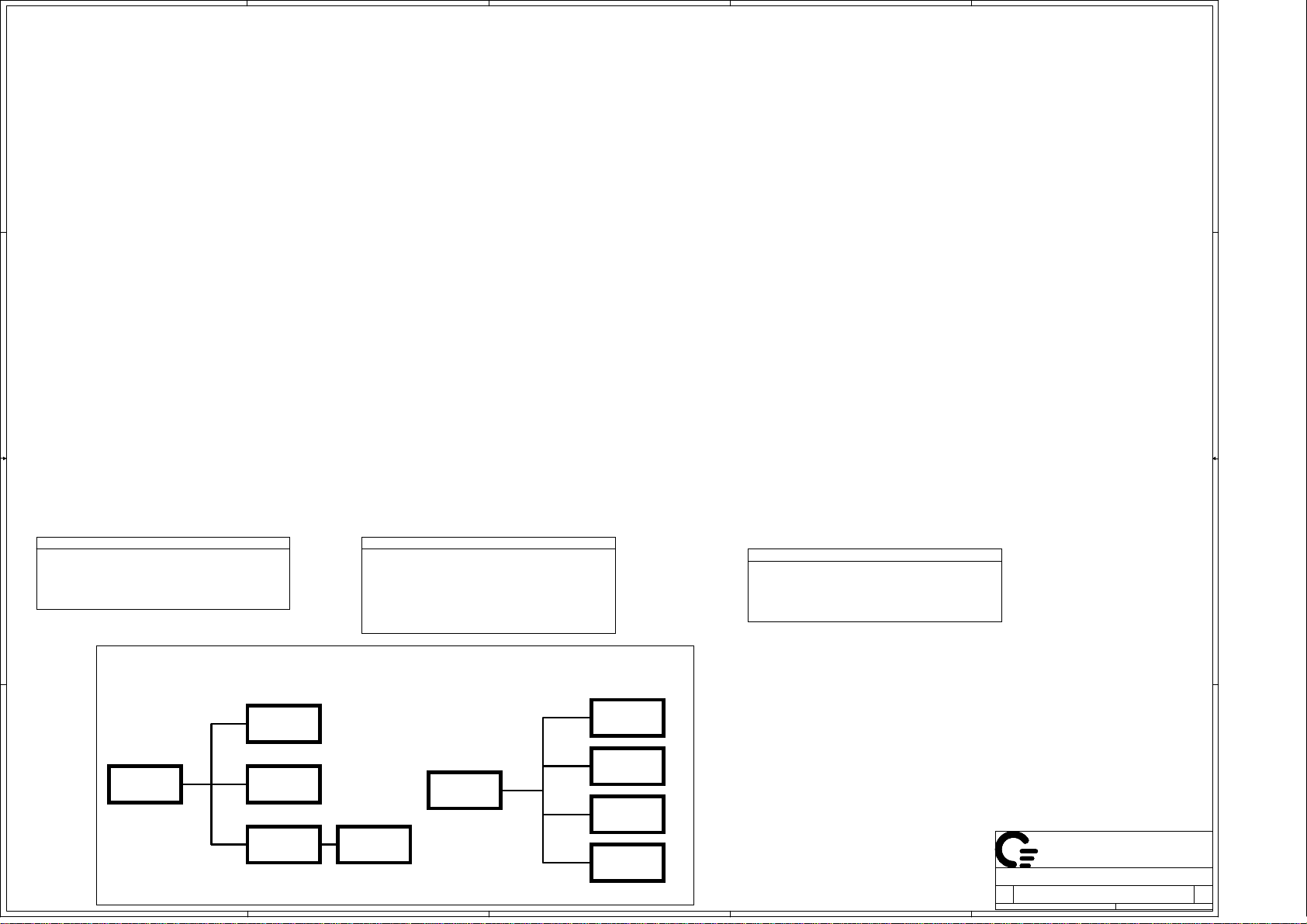

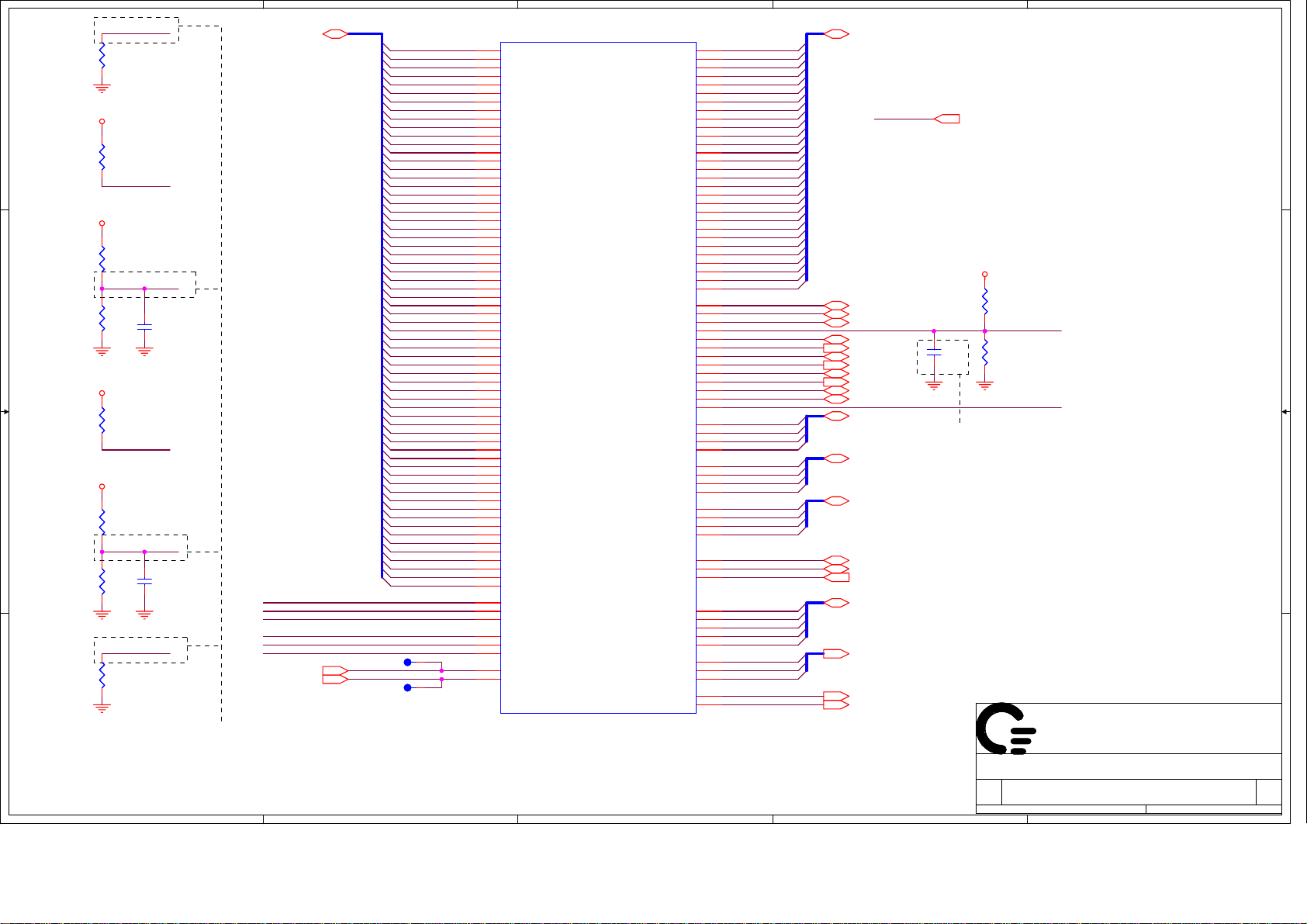

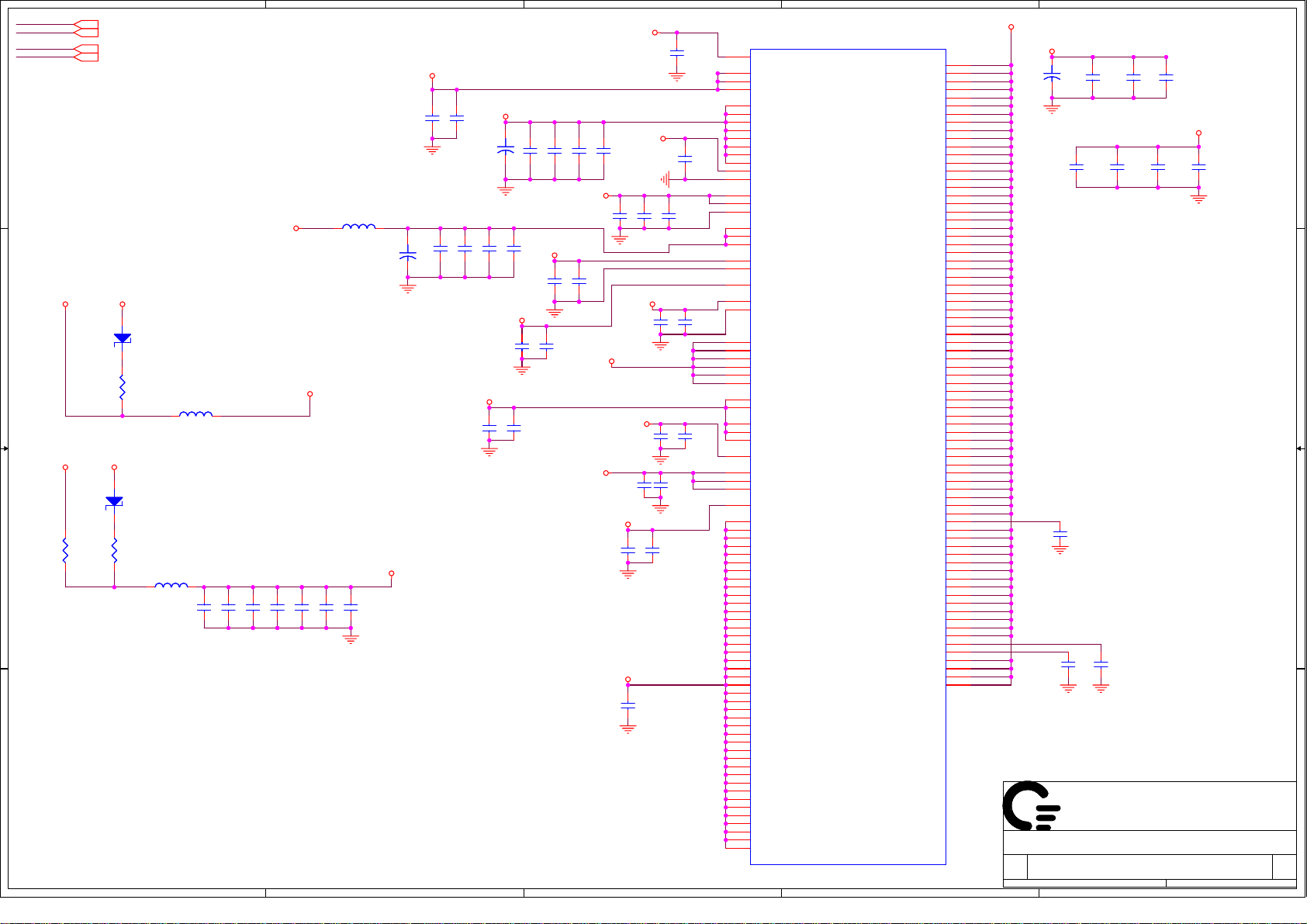

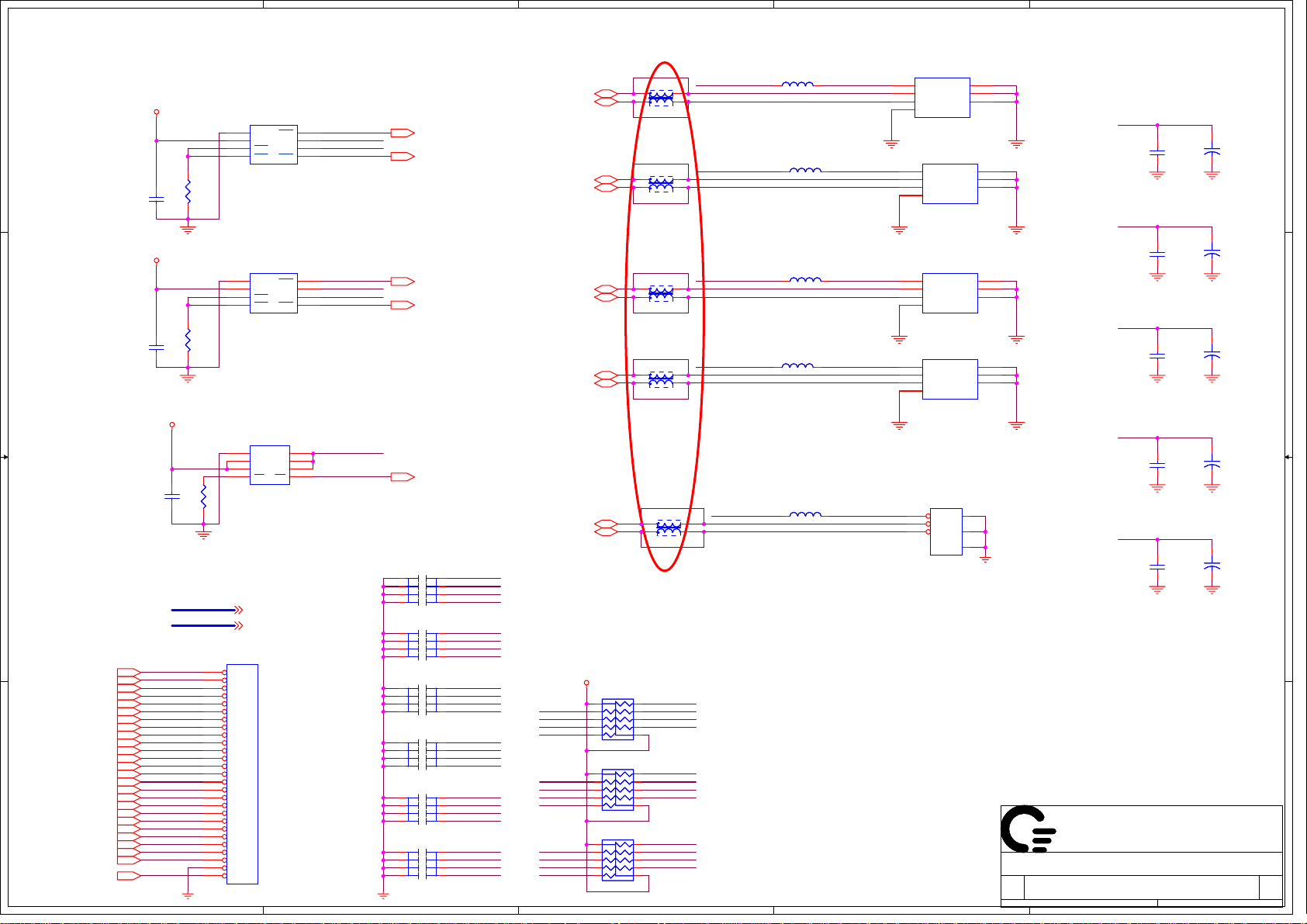

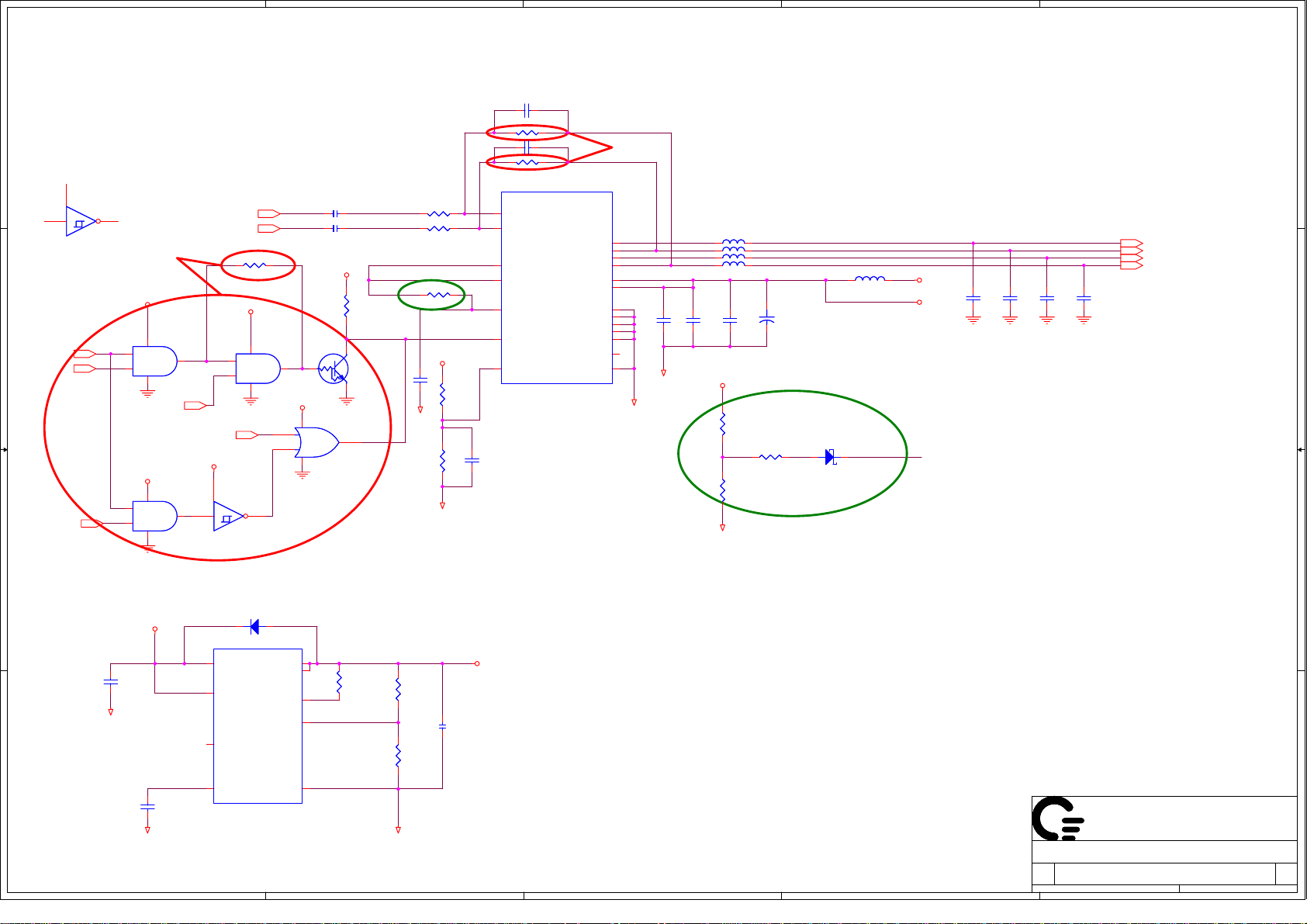

1. Schematic Page Description :

02

DO1 Schematic Ver : 0.2

1. Block Diagram

D D

2. Schematic Page List

3. System Info

4. u-FCPGA Yonah (1/2)

5. u-FCPGA Yonah (2/2)

6. Calistoga HOST

7. Calistoga DDR II

8. Calistoga VGA/DMI/NCTF

9. Calistoga POWER

10. Calistoga POWER

11. Calistoga GND

12. DDR II SODIMM CNN

13. Clock Generator

14. ICH7-M CPU/IDE/SATA/AC97/LPC

C C

15. ICH7-M USB/DMI/LPC/PCI_E/PCI

16. ICH7-M GPIO/SMB

17. ICH7-M POWER/GND

18. CRT Port / S-VIDEO

19. LCD CNN / LID / Audio board CONN

20. R5C841 CONTROLLER

21. R5C841 CNN & 4 IN 1

22. PC87541L / BIOS

23. LAN MARVELL 88E8055/RJ45 CONN

24. Mini PCIE

25. FAN/THERMAL/SWICH CONN/BEEP/TOUCH PAD/ IR RECEIVER

26. USB K/B CNN

27. SATA / PATA HDD

28. L007

29. MDC1.5

30. CODEC ALC262

31. AMP for Speaker

32. CPU CORE

33. VCC1.5V / GMCHVTT

34. DC/DC 3V,5V POWER

35. 1.8V / 0.9V DDR2 / VCC2.5

36. Battery Charge Circuit

37. Battery Select

2. PCI Description :

IDSEL CHIP

AD25

B B

CardBus (R5C841) CardBus

IRQA

IRQB

IRQC

IRQD

IRQE

IRQF

SM BUS Block Diagram

Battery

A A

EC (KBC) EEPROM

5

ThermalSW

4

CHIPPCIINT

CardBus

CardBus

ICH7

DDR2

CLK GEN

Express card

Mini PCIE

3

BUSMASTER

REQ

REQ0 / GNT0

REQ1 / GNT1

REQ2 / GNT2

REQ3 / GNT3

REQ4 / GNT4

CHIP

CardBus (R5C841)

2

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

C

C

C

Description

Description

Description

COMPUTER

DO1

DO1

DO1

1

239Thursday, February 09, 2006

239Thursday, February 09, 2006

239Thursday, February 09, 2006

of

of

of

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

3C

3C

3C

Page 3

5

4

3

2

1

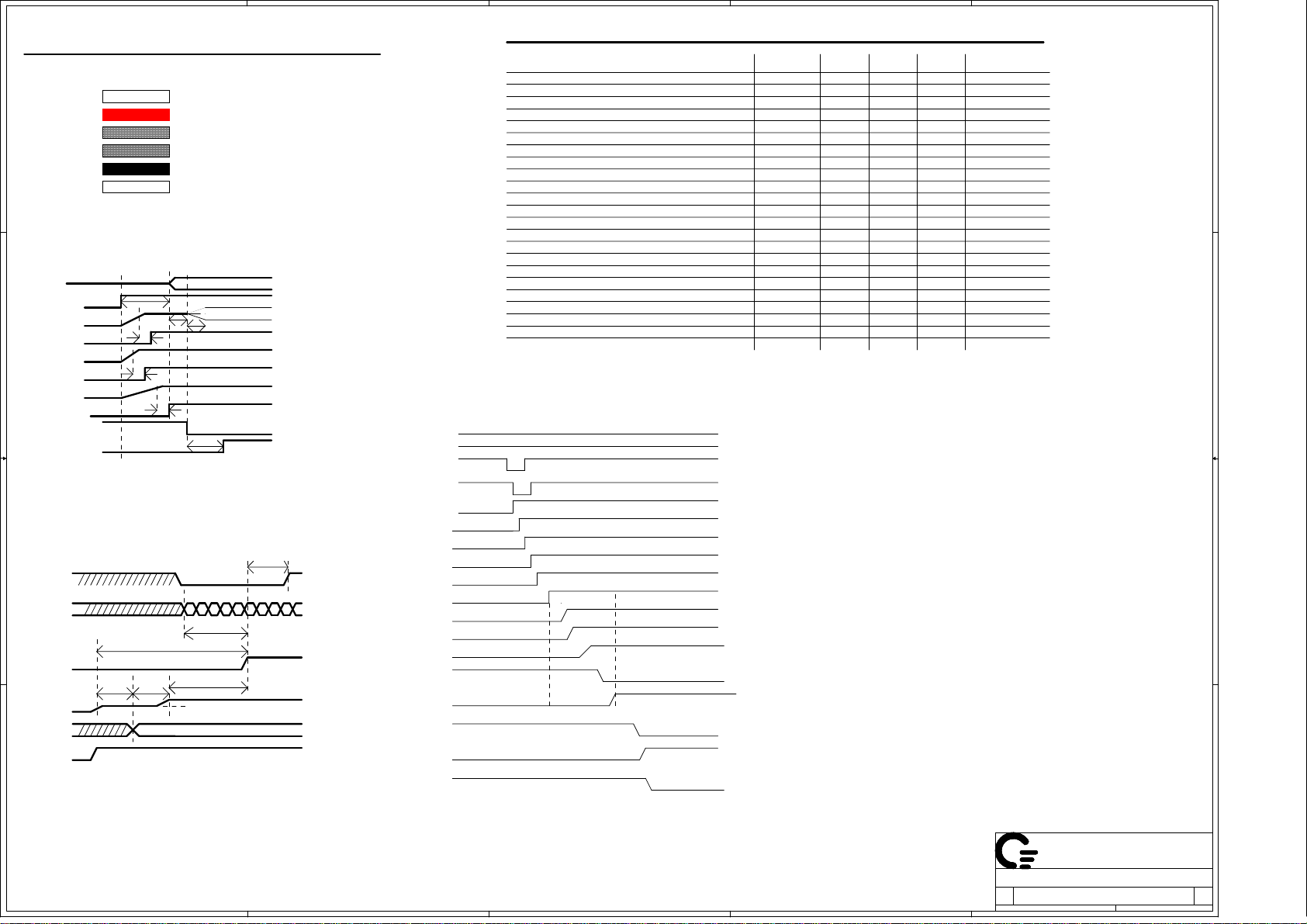

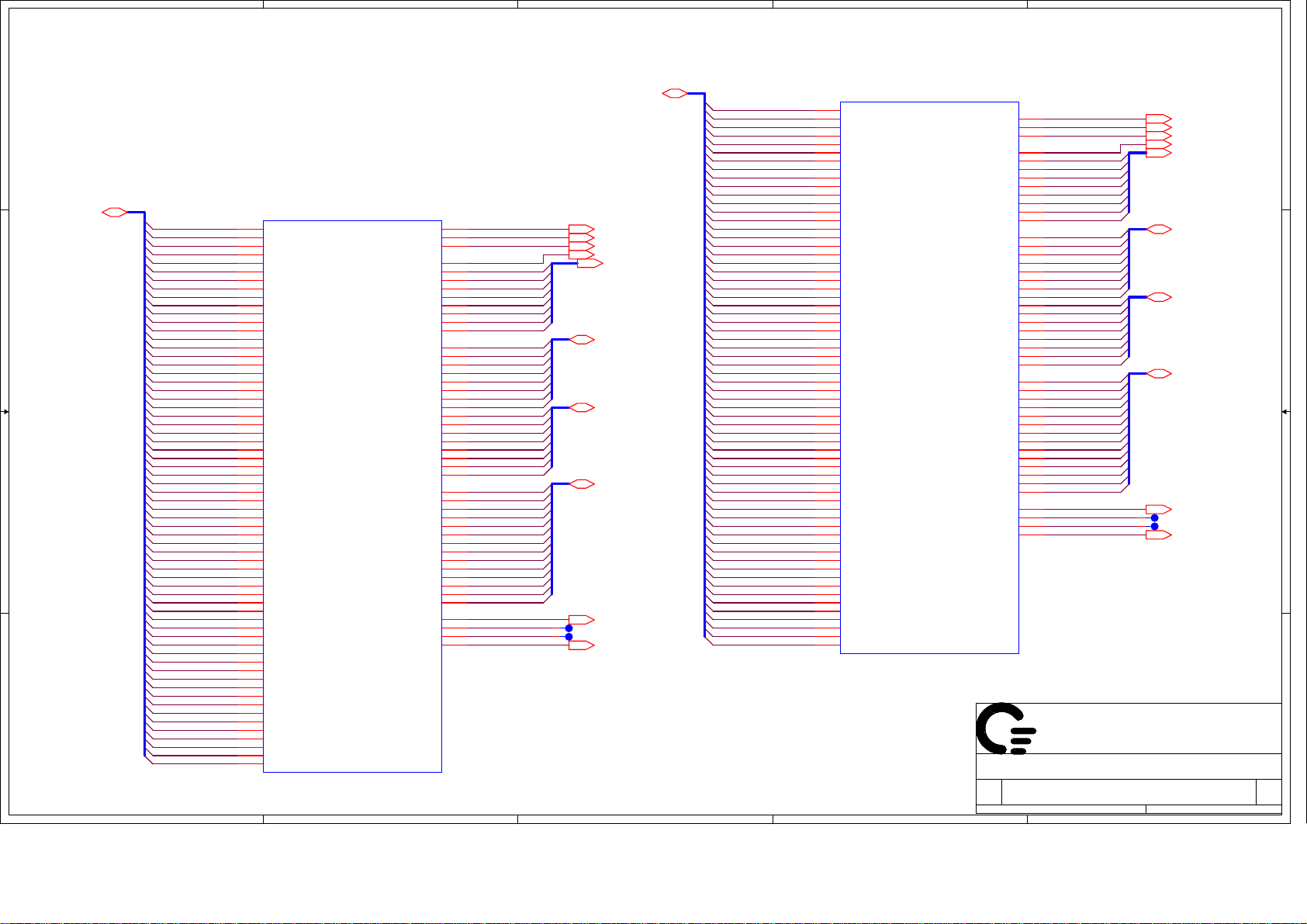

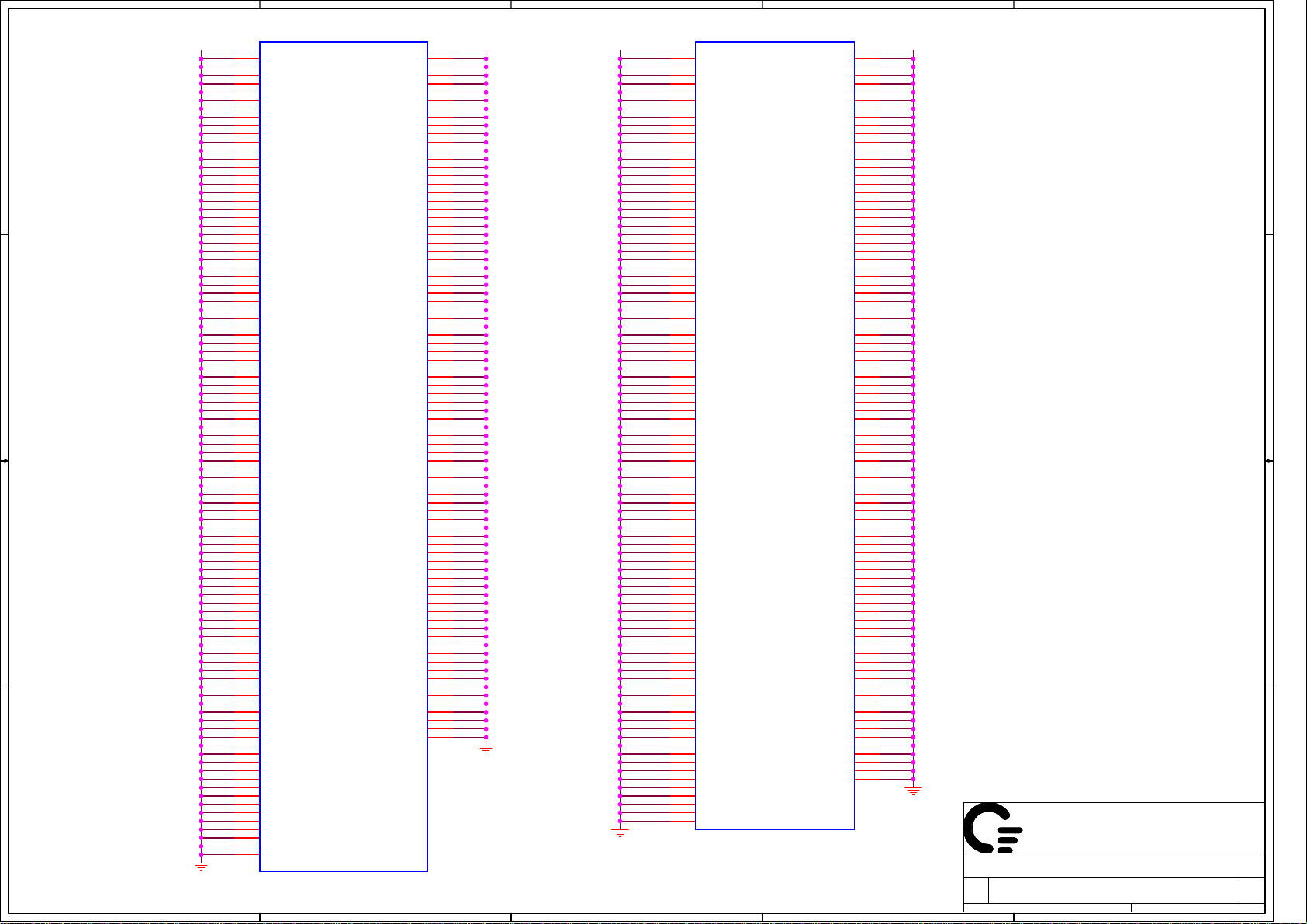

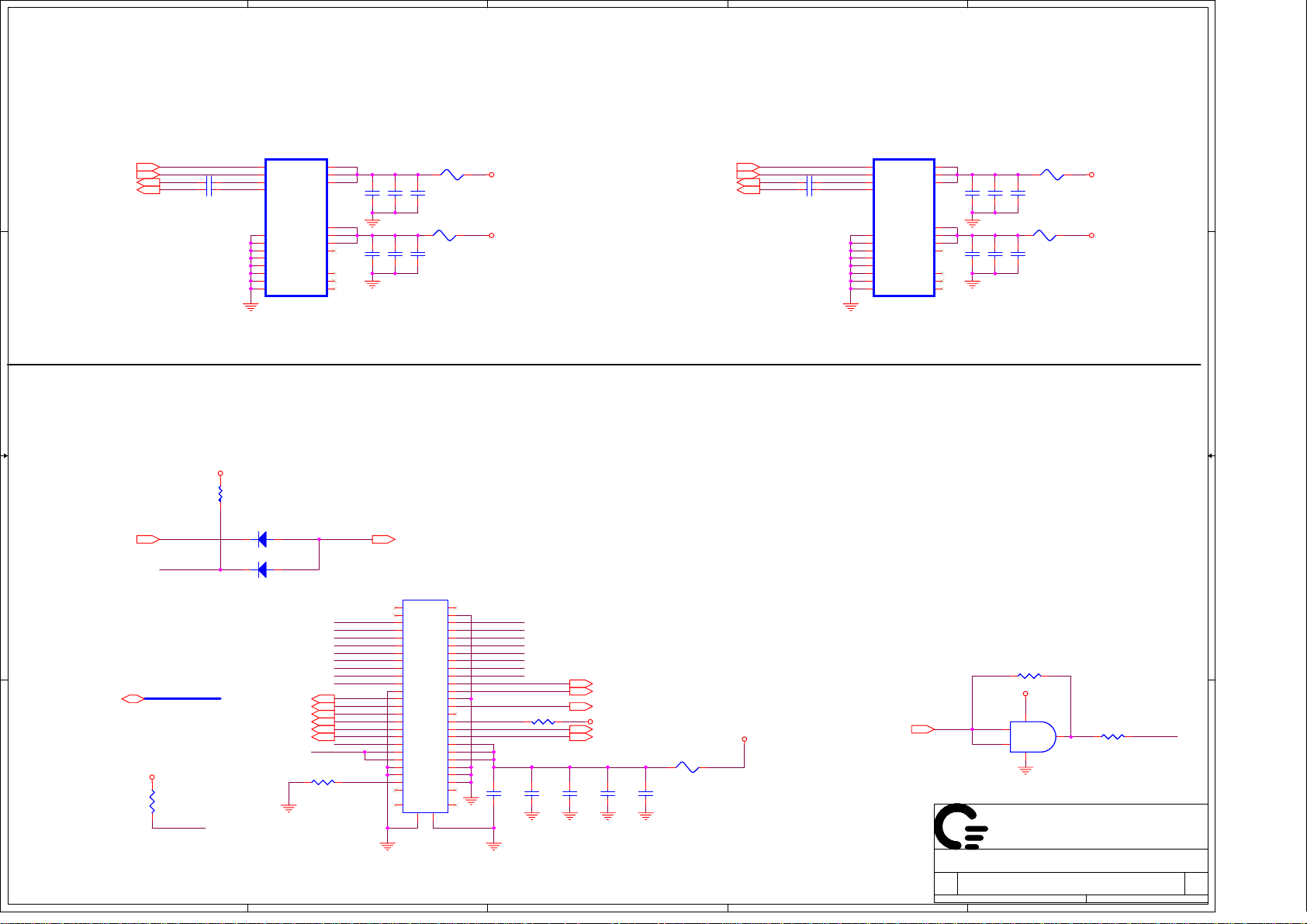

Board Stack up Description

PCB Layers

Layer 1

Layer 2

D D

Layer 3

Layer 4

Layer 5

Layer 6

Power On Sequencing Timing Diagram

VID

VR_ON

Vcc-core

CPU_UP

C C

Vccp

Vccp_UP

TOP(FSB,DDR2,CLK,PEG,Component)

Ground Plane

IN1(FSB,CLOCK,DDR2,PEG,CLK)

IN2(PCI,IDE,LPC)

Power Plane

BOTTOM, (Component,Other)

Tsft_star_vcc

Tboot

Tcpu_up

Tvccp_up

Vboot

Tboot-vid-tr

Vid

Voltage Rails

Voltage Rails ON S0~S2

VCC_CORE

GMCH_VTT

SMDDR_VREF 0.9V for DDR2 Termination voltage

Core voltage for Processor

Core voltage for CPU / NB

RVCC3

VCC1.5

VCC1.8

VCC2.5

VCC3

VCC5

1.8VSUS

3VSUS

5VSUS

3VPCU

5VPCU

9VPCU

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

ON S3 ON S4 ON S5

XX

X

X

X

X

X

X

X

X

X

X

X

X

Control signal

GMCHPG

VR_ON

MAINON

RVCCD

MAINON

MAINON

MAINON

MAIND

MAIND

SUSON

SUSD

SUSD

VL

VL

5VPCU

03

Vccgmch

GMCHPWRGD

CLK_ENABLE#

IMVP4_PWRGD

Tgmch_pwrgd

Tcpu_pwrgd

ACIN POWER ON TIMING

ACIN

5VPCU/3VPCU

NBSWON#

PWRBTN#

To ICH6

RCVV_ON

Dothan Power-up Timing

Specifications

RESET#

B B

BCLK

Tc

Te

PWRGOOD

Tf

Vcc,boot

VCC

Ta

Tb

Td

RSMRST#

SUSB#,SUSC#

SUSON

MAINON

VSUS,VCC

VR_ON

GMCH_VTT/1.05V

VCORE_CPU

CK410_PWRGD

PWROK/IMVP_PWRGD

PLTRST#\PCIRST#

99ms < t 214

VID[5:0]

VTT

Ta=VCC and VCCP asseration to VID[5:0] vaild

Tb=VID[5:0] stable to VCC vaild

Tc=BCLK stable to PWRGOOD assertion

A A

Td=PWRGOOD to RESET# de-assertion time

Te=Vcc,boot vaild to PWRGOOD assertion time

Tf=VCC vaild to PWRGOOD assertion time

5

H_PWRGD

H_CPURST#

4

2ms

3

To ICH6

From ICH6

From 87591

From 87591

From 87591

To clock generator

To GMCH/other PCI device

From ICH6 to CPU

Form GMCH to CPU

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

INFORMATION

INFORMATION

INFORMATION

C

C

C

COMPUTER

DO1

DO1

DO1

1

3C

3C

339Thursday, February 09, 2006

339Thursday, February 09, 2006

339Thursday, February 09, 2006

3C

of

of

of

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

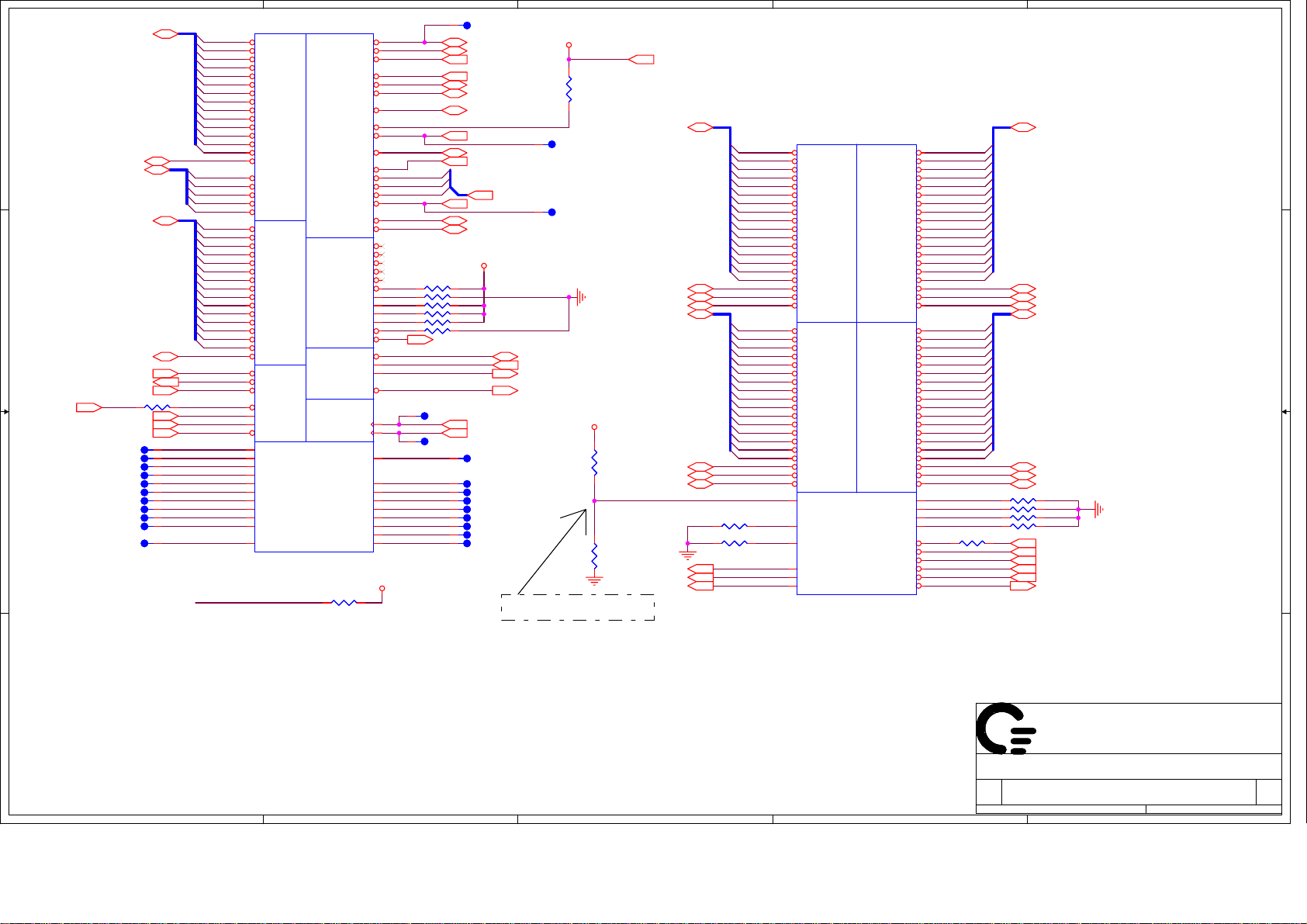

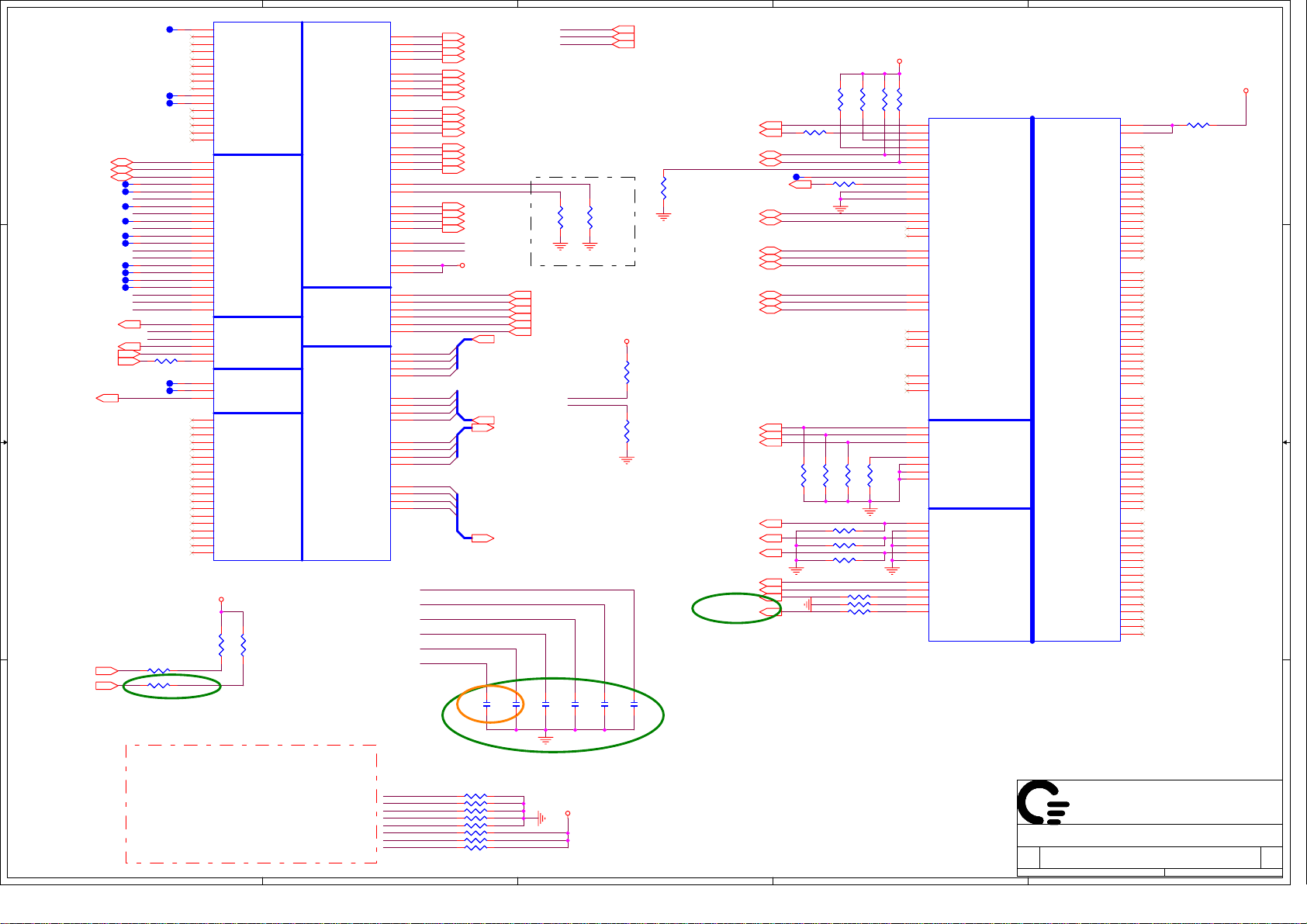

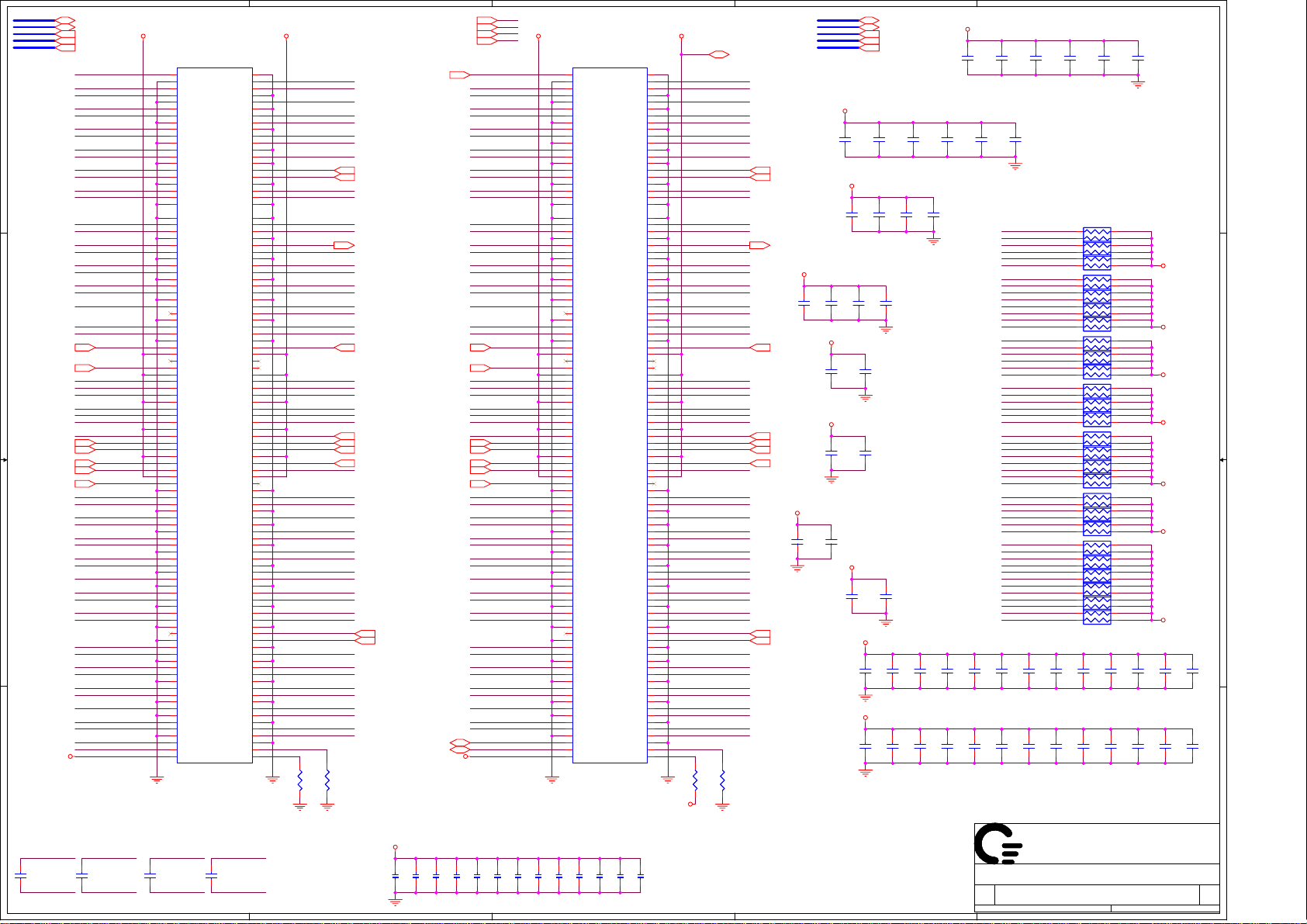

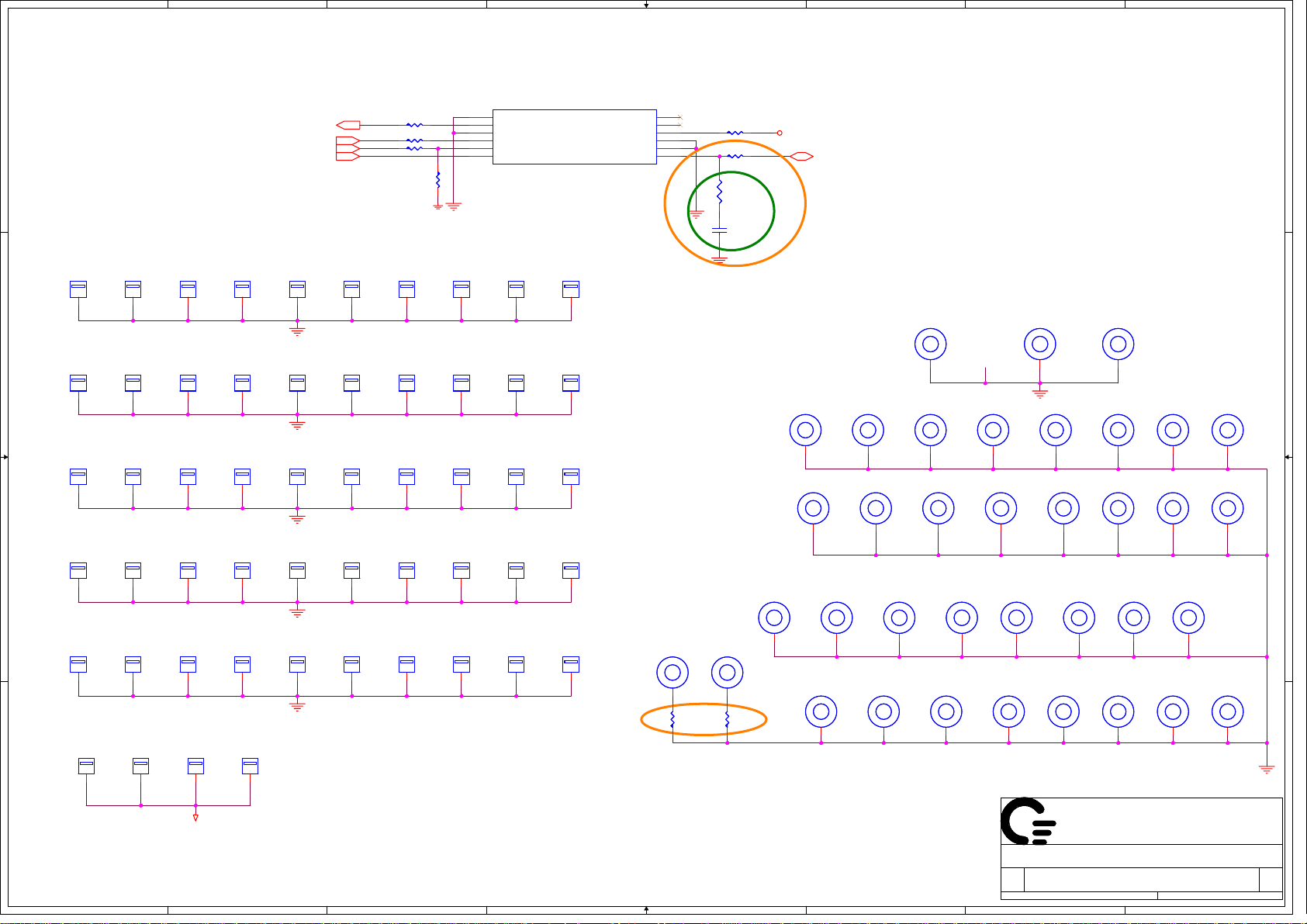

Page 4

5

U4A

H_A#[31:3]6

D D

H_ADSTB#06

H_REQ#[4:0]6

H_A#[31:3]6

C C

H_ADSTB#16

H_A20M#14

H_FERR#14

H_IGNNE#14

H_STPCLK#14

B B

R238 0R238 0

H_INTR14

H_NMI14

H_SMI#14

T4T4

T6T6

T5T5

T3T3

T57T57

T58T58

T2T2

T1T1

T52T52

T54T54

T18T18

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

TP_A32#

TP_A33#

TP_A34#

TP_A35#

TP_A36#

TP_A37#

TP_A38#

TP_A39#

TP_APM0#

TP_APM1#

TP_HFPLL

U4A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

A[6]#

M1

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L1

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

L2

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L5

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U2

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W3

A[27]#

W5

A[28]#

Y4

A[29]#

W2

A[30]#

Y1

A[31]#

V4

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

AA1

RSVD[01]#

AA4

RSVD[02]#

AB2

RSVD[03]#

AA3

RSVD[04]#

M4

RSVD[05]#

N5

RSVD[06]#

T2

RSVD[07]#

V3

RSVD[08]#

B2

RSVD[09]#

C3

RSVD[10]#

B25

RSVD[11]#

PZ47903-2741-01

PZ47903-2741-01

H_PROCHOT#

ADDR GROUP 0

ADDR GROUP 0

DEFER#

DRDY#

DBSY#

CONTROL

CONTROL

LOCK#

RESET#

TRDY#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

PROCHOT

THERMDA

THERMDC

THERMTRIP#

THERMH CLK

THERMH CLK

BCLK[0]

BCLK[1]

RSVD[12]#

RSVD[13]#

RSVD[14]#

RSVD[15]#

RSVD[16]#

RESERVED

RESERVED

RSVD[17]#

RSVD[18]#

RSVD[19]#

RSVD[20]#

R30475R304

ADS#

BNR#

BPRI#

BR0#

IERR#

INIT#

RS[0]#

RS[1]#

RS[2]#

HIT#

HITM#

TCK

TDO

TMS

DBR#

TDI

GMCH_VTT

75

4

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

R231 54.9R231 54.9

AC1

R237 54.9R237 54.9

AC5

R228 54.9R228 54.9

AA6

R230 54.9R230 54.9

AB3

R229 54.9R229 54.9

AB5

R241 54.9R241 54.9

AB6

C20

D21

A24

A25

C7

A22

A21

TP_EXTBREF

T22

TP_SPARE0

D2

TP_SPARE1

F6

TP_SPARE2

D3

TP_SPARE3

C1

TP_SPARE4

AF1

TP_SPARE5

D22

TP_SPARE6

C23

TP_SPARE7

C24

T51T51

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BREQ#0 6

H_INIT# 14

H_LOCK# 6

H_CPURST# 6

H_TRDY# 6

H_HIT# 6

H_HITM# 6

GMCH_VTT

XDP_DBRESET# 16

H_PROCHOT#

T19T19

CLK_CPU_BCLK 13

CLK_CPU_BCLK# 13

T20T20

T68T68

T53T53

T59T59

T56T56

T50T50

T7T7

T71T71

T78T78

T77T77

GMCH_VTT

R27456R274

56

T31T31

H_RS#[2:0] 6

Layout note: 0.5" max for GTLREF

T55T55

H_PROCHOT# 32

H_THERMDA 25

H_THERMDC 25

PM_THRMTRIP# 8,14

GMCH_VTT

R299

R299

1K/F

1K/F

R293

R293

2K/F

2K/F

3

GMCH_VTT 5,6,9,10,13,14,17,33

H_D#[63:0]6

H_DSTBN#06

H_DSTBP#06

H_DINV#06

H_D#[63:0]6

H_DSTBN#16

H_DSTBP#16

H_DINV#16

R285

R285

R29151R291

CPU_BSEL013

CPU_BSEL113

CPU_BSEL213

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

*1K

*1K

51

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

H26

F26

K22

H25

H23

G22

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

AD26

C26

D25

B22

B23

C21

J24

J23

J26

U4B

U4B

D[0]#

D[1]#

D[2]#

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

MISC

MISC

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

PZ47903-2741-01

PZ47903-2741-01

2

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2

DATA GRP 2

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

DATA GRP 3

DATA GRP 3

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

R236 0R236 0

27.4

27.4

H_D#[63:0] 6

H_DSTBN#2 6

H_DSTBP#2 6

H_DINV#2 6

H_D#[63:0] 6

H_DSTBN#3 6

H_DSTBP#3 6

H_DINV#3 6

R302

R302

R30154.9 R30154.9

R23327.4 R23327.4

R23254.9 R23254.9

ICH_DPRSTP# 14

H_DPSLP# 14

H_DPWR# 6

H_PWRGD 14

H_CPUSLP# 6,14

PSI# 32

1

04

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

CPU (Yonah / Merom) -1

CPU (Yonah / Merom) -1

CPU (Yonah / Merom) -1

DO1

DO1

DO1

3C

3C

3C

439Thursday, February 09, 2006

439Thursday, February 09, 2006

439Thursday, February 09, 2006

of

of

1

of

Page 5

5

GMCH_VTT

C260

C260

C256

D D

C C

B B

A A

C256

0.1U

0.1U

GMCH_VTT

C338

C338

0.1U

0.1U

0.1U

0.1U

C329

C329

0.1U

0.1U

C259

C259

0.1U

0.1U

5

C261

C261

0.1U

0.1U

C339

C339

0.1U

0.1U

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A7

A9

B7

B9

C9

D9

E7

E9

F7

F9

U4C

U4C

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[100]

VCC[034]

VCC[035]

VCCP[01]

VCC[036]

VCCP[02]

VCC[037]

VCCP[03]

VCC[038]

VCCP[04]

VCC[039]

VCCP[05]

VCC[040]

VCCP[06]

VCC[041]

VCCP[07]

VCC[042]

VCCP[08]

VCC[043]

VCCP[09]

VCC[044]

VCCP[10]

VCC[045]

VCCP[11]

VCC[046]

VCCP[12]

VCC[047]

VCCP[13]

VCC[048]

VCCP[14]

VCC[049]

VCCP[15]

VCC[050]

VCCP[16]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCCSENSE

VCC[066]

VCC[067]

VSSSENSE

PZ47903-2741-01

PZ47903-2741-01

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

4

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

4

3

U4D

CPU_CORECPU_CORE

C3500.01U C3500.01U

GMCH_VTT

CPU_CORE

VCC1.5

CPU_VID0 32

CPU_VID1 32

CPU_VID2 32

CPU_VID3 32

CPU_VID4 32

CPU_VID5 32

CPU_VID6 32

GMCH_VTT 4,6,9,10,13,14,17,33

CPU_CORE 32

VCC1.5 8,9,10,15,17,21,24,33,34

GMCH_VTT

+

+

C384

C384

330U

330U

VCC1.5

placement near B26

CPU_CORE

R245

R245

100/F

100/F

R244

R244

100/F

100/F

VCC1.5

C359

C359

10U

10U

VCCSENSE 32

VSSSENSE 32

3

U4D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

P3

VSS[081]

PZ47903-2741-01

PZ47903-2741-01

2

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

2

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

1

CPU_CORE

05

C106

C106

C105

C105

C269

C269

C276

C276

C94

C94

10U

10U

10U

10U

10U

10U

10U

10U

10U

10U

CPU_CORE

C300

C300

C263

C263

10U

10U

C333

C333

10U

10U

C97

C97

10U

10U

C92

C92

10U

10U

C275

C275

10U

10U

CPU_CORE

C293

C293

10U

10U

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

CPU (Yonah / Merom) -2

CPU (Yonah / Merom) -2

CPU (Yonah / Merom) -2

C272

C272

10U

10U

10U

10U

CPU_CORE

C102

C102

C249

C249

10U

10U

10U

10U

CPU_CORE

C313

C313

C315

C315

10U

10U

10U

10U

CPU_CORE

C90

C90

C265

C265

10U

10U

10U

10U

CPU_CORE

C268

C268

C292

C292

10U

10U

10U

10U

CPU_CORE

C314

C314

10U

10U

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

DO1

DO1

DO1

C285

C285

10U

10U

C98

C98

10U

10U

C325

C325

10U

10U

C95

C95

10U

10U

C91

C91

10U

10U

C318

C318

1000P

1000P

C101

C101

10U

10U

C93

C93

10U

10U

C299

C299

10U

10U

C324

C324

10U

10U

C286

C286

10U

10U

1

C326

C326

1000P

1000P

C281

C281

1000P

1000P

539Thursday, February 09, 2006

539Thursday, February 09, 2006

539Thursday, February 09, 2006

of

of

of

3C

3C

3C

Page 6

5

H_XRCOMP

R320

R320

24.9/F

24.9/F

D D

C C

B B

A A

GMCH_VTT

R317

R317

54.9/F

54.9/F

GMCH_VTT

R318

R318

221/F

221/F

R319

R319

100/F

100/F

GMCH_VTT

R312

R312

54.9/F

54.9/F

GMCH_VTT

R315

R315

221/F

221/F

R316

R316

100/F

100/F

R311

R311

24.9/F

24.9/F

H_XSCOMP

H_XSWING

C379

C379

0.1U

0.1U

H_YSCOMP

H_YSWING

C409

C409

0.1U

0.1U

H_YRCOMP

Width of trace must meet 10 mil

5

CLK_MCH_BCLK13

CLK_MCH_BCLK#13

H_D#[63:0]4

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

T21T21

T22T22

4

U5A

K11

T10

W11

U11

T11

AB7

AA9

Y10

AB8

AA4

AA7

AA2

AA6

AA10

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

AG2

AG1

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

G4

T3

U7

U9

W9

T1

T8

T4

W7

U5

T9

W6

T5

W4

W3

Y3

Y7

W5

W2

Y8

E1

E2

E4

Y1

U1

W1

U5A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

Calistoga

Calistoga

HOST

HOST

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

4

3

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_VREF_0

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_VREF_1

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

3

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

2

H_A#[31:3] 4

GMCH_VTT

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BREQ#0 4

H_CPURST# 4

H_DBSY# 4

H_DEFER# 4

H_DPWR# 4

H_DRDY# 4

H_DINV#[3:0] 4

H_DSTBN#[3:0] 4

H_DSTBP#[3:0] 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_REQ#[4:0] 4

H_RS#[2:0] 4

H_CPUSLP# 4,14

H_TRDY# 4

2

1

GMCH_VTT 4,5,9,10,13,14,17,33

GMCH_VTT

R286

R286

100/F

100/F

H_VREF

R287

C356

C356

0.1U

0.1U

R287

200/F

200/F

H_VREF

placement near J13 and K13

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

COMPUTER

GMCH HOST (1 of 6)

GMCH HOST (1 of 6)

GMCH HOST (1 of 6)

DO1

DO1

DO1

639Thursday, February 09, 2006

639Thursday, February 09, 2006

639Thursday, February 09, 2006

1

06

3C

3C

3C

of

of

of

Page 7

5

4

3

2

1

07

B_MD[63:0]12

D D

A_MD[63:0]12

C C

B B

A A

A_MD0

A_MD1

A_MD2

A_MD3

A_MD4

A_MD5

A_MD6

A_MD7

A_MD8

A_MD9

A_MD10

A_MD11

A_MD12

A_MD13

A_MD14

A_MD15

A_MD16

A_MD17

A_MD18

A_MD19

A_MD20

A_MD21

A_MD22

A_MD23

A_MD24

A_MD25

A_MD26

A_MD27

A_MD28

A_MD29

A_MD30

A_MD31

A_MD32

A_MD33

A_MD34

A_MD35

A_MD36

A_MD37

A_MD38

A_MD39

A_MD40

A_MD41

A_MD42

A_MD43

A_MD44

A_MD45

A_MD46

A_MD47

A_MD48

A_MD49

A_MD50

A_MD51

A_MD52

A_MD53

A_MD54

A_MD55

A_MD56

A_MD57

A_MD58

A_MD59

A_MD60

A_MD61

A_MD62

A_MD63

5

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

U5D

U5D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

Calistoga

Calistoga

AU12

SA_BS_0

AV14

SA_BS_1

BA20

SA_BS_2

AY13

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_WE#

4

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

A_DM0

A_DM1

A_DM2

A_DM3

A_DM4

A_DM5

A_DM6

A_DM7

A_DQS0

A_DQS1

A_DQS2

A_DQS3

A_DQS4

A_DQS5

A_DQS6

A_DQS7

A_DQS#0

A_DQS#1

A_DQS#2

A_DQS#3

A_DQS#4

A_DQS#5

A_DQS#6

A_DQS#7

A_MA0

A_MA1

A_MA2

A_MA3

A_MA4

A_MA5

A_MA6

A_MA7

A_MA8

A_MA9

A_MA10

A_MA11

A_MA12

A_MA13

TP_MA_RCVENIN#

TP_MA_RCVENOUT#

A_BS0# 12

A_BS1# 12

A_BS2# 12

A_SCASA# 12

A_DQS[7:0] 12

A_DQS#[7:0] 12

A_MA[13:0] 12

A_SRASA# 12

T65T65

T64T64

A_BMWEA# 12

A_DM[0:7] 12

3

B_MD0

B_MD1

B_MD2

B_MD3

B_MD4

B_MD5

B_MD6

B_MD7

B_MD8

B_MD9

B_MD10

B_MD11

B_MD12

B_MD13

B_MD14

B_MD15

B_MD16

B_MD17

B_MD18

B_MD19

B_MD20

B_MD21

B_MD22

B_MD23

B_MD24

B_MD25

B_MD26

B_MD27

B_MD28

B_MD29

B_MD30

B_MD31

B_MD32

B_MD33

B_MD34

B_MD35

B_MD36

B_MD37

B_MD38

B_MD39

B_MD40

B_MD41

B_MD42

B_MD43

B_MD44

B_MD45

B_MD46

B_MD47

B_MD48

B_MD49

B_MD50

B_MD51

B_MD52

B_MD53

B_MD54

B_MD55

B_MD56

B_MD57

B_MD58

B_MD59

B_MD60

B_MD61

B_MD62

B_MD63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

U5E

U5E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

Calistoga

Calistoga

AT24

SB_BS_0

AV23

SB_BS_1

AY28

SB_BS_2

AR24

SB_CAS#

AK36

SB_DM_0

AR38

SB_DM_1

AT36

SB_DM_2

BA31

SB_DM_3

AL17

SB_DM_4

AH8

SB_DM_5

BA5

SB_DM_6

AN4

SB_DM_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_RAS#

SB_WE#

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AU23

AK16

AK18

AR27

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RCVENIN#

SB_RCVENOUT#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

2

Date: Sheet

B_DM0

B_DM1

B_DM2

B_DM3

B_DM4

B_DM5

B_DM6

B_DM7

B_DQS0

B_DQS1

B_DQS2

B_DQS3

B_DQS4

B_DQS5

B_DQS6

B_DQS7

B_DQS#0

B_DQS#1

B_DQS#2

B_DQS#3

B_DQS#4

B_DQS#5

B_DQS#6

B_DQS#7

B_MA0

B_MA1

B_MA2

B_MA3

B_MA4

B_MA5

B_MA6

B_MA7

B_MA8

B_MA9

B_MA10

B_MA11

B_MA12

B_MA13

TP_MB_RCVENIN#

TP_MB_RCVENOUT#

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

GMCH DDRII ( 2 of 6 )

GMCH DDRII ( 2 of 6 )

GMCH DDRII ( 2 of 6 )

DO1

DO1

DO1

B_BS0# 12

B_BS1# 12

B_BS2# 12

B_SCASA# 12

B_DM[7:0] 12

B_DQS[7:0] 12

B_DQS#[7:0] 12

B_MA[13:0] 12

B_SRASA# 12

T73T73

T66T66

B_BMWEA# 12

1

3C

3C

3C

739Thursday, February 09, 2006

739Thursday, February 09, 2006

739Thursday, February 09, 2006

of

of

of

Page 8

5

T61T61

T8T8

T69T69

T74T74

T70T70

T10T10

T11T11

T75T75

T76T76

T80T80

T72T72

T79T79

T9T9

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

EXTTS#0

EXTTS#1

R242 100R242 100

T62T62

T63T63

R261 0R261 0

R255 *0R255 *0

D D

MCH_BSEL013

MCH_BSEL113

MCH_BSEL213

C C

B B

PM_BMBUSY#16

PM_THRMTRIP#4,14

PWROK16,19,22

PLT_RST#15

MCH_ICH_SYNC15

PM_EXTTS#012

DPRSLPVR16,32

H32

T32

R32

F3

F7

AG11

AF11

H7

J19

K30

J29

A41

A35

A34

D28

D27

K16

K18

J18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

J25

K27

J26

G28

F25

H26

G6

AH33

AH34

H28

H27

K28

D1

C41

C1

BA41

BA40

BA39

BA3

BA2

BA1

B41

B2

AY41

AY1

AW41

AW1

A40

A4

A39

A3

EXTTS#0

EXTTS#1

U5B

U5B

RSVD_0

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

SDVO_CTRLCLK

SDVO_CTRLDATA

LT_RESET#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

Calistoga

Calistoga

VCC3

R258

R258

R253

R253

10K

10K

10K

10K

CFGRSVD

CFGRSVD

PM

PM

MISC

MISC

NC

NC

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_RCOMP#

DDR MUXINGCLKDMI

DDR MUXINGCLKDMI

D_REFCLKIN#

D_REFSSCLKIN#

D_REFSSCLKIN

EC1

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_VREF_0

SM_VREF_1

G_CLKIN#

G_CLKIN

D_REFCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

4

AY35

AR1

AW7

AW40

AW35

AT1

AY7

AY40

AU20

AT20

BA29

AY29

AW13

AW12

AY21

AW21

AL20

AF10

BA13

BA12

AY20

AU21

AV9

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

M_RCOMP#

M_RCOMP

CLK_PCIE_3GPLL#

CLK_PCIE_3GPLL

DOT96#

DOT96

DREFSSCLK#

DREFSSCLK

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DREFSSCLK

DREFSSCLK#

DOT96

DOT96#

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

EC34

CLK_SDRAM0 12

CLK_SDRAM1 12

CLK_SDRAM3 12

CLK_SDRAM4 12

CLK_SDRAM0# 12

CLK_SDRAM1# 12

CLK_SDRAM3# 12

CLK_SDRAM4# 12

CKE0 12

CKE1 12

CKE2 12

CKE3 12

SM_CS0# 12

SM_CS1# 12

SM_CS2# 12

SM_CS3# 12

M_ODT0 12

M_ODT1 12

M_ODT2 12

M_ODT3 12

SMDDR_VREF

DMI_TXN[3:0] 15

DMI_TXP[3:0] 15

DMI_RXN[3:0] 15

DMI_RXP[3:0] 15

C273

C273

C267

C267

10P_4

10P_4

10P_4

10P_4

VCC3

SMDDR_VREF

1.8VSUS

R295

R295

*40.2

*40.2

Layout as short as passable

NC from WW45

CLK_PCIE_3GPLL# 13

CLK_PCIE_3GPLL 13

DOT96# 13

DOT96 13

DREFSSCLK# 13

DREFSSCLK 13

M_RCOMP#

M_RCOMP

C96

C96

C99

C99

C254

*1000P_4

*1000P_4

C254

*1000P_4

*1000P_4

*1000P_4

*1000P_4

3

VCC3 10,12,13,14,15,16,17,18,19,21,22,23,24,25,27,28,30,32,34

SMDDR_VREF 12,35

1.8VSUS 9,12,28,34,35

BRIGHTNESS19

LVDS_BLON19,22

EDIDCLK19

EDIDDATA19

R240

R240

1.5K/F_4

1.5K/F_4

R273

R273

*40.2

*40.2

1.8VSUS

R305

R305

80.6/F

80.6/F

R296

R296

80.6/F

80.6/F

TXLCLKOUT-28

TXLCLKOUT+28

TXLOUT0-28

TXLOUT1-28

TXLOUT2-28

TXLOUT0+28

TXLOUT1+28

TXLOUT2+28

TV_COMP18

TV_Y/G18

TV_C/R18

CRT_B18

CRT_G18

CRT_R18

DDCCLK18

DDCDATA18

CRT_HSYNC18

CRT_VSYNC18

EC7

C253

C253

*1000P_4

*1000P_4

EC1

2

VCC3

R251

R251

R249

R249

10K

10K

10K

10K

R250 0R250 0

T60T60

DISP_ON19,28

R247 0R247 0

TXLCLKOUTTXLCLKOUT+

TXLOUT0TXLOUT1TXLOUT2-

TXLOUT0+

TXLOUT1+

TXLOUT2+

R279

R279

150

150

1 2

R265 150/F_4R265 150/F_4

1 2

R268 150/F_4R268 150/F_4

1 2

R272 150/F_4R272 150/F_4

R278

R278

R283

R283

150

150

150

150

R267 39R267 39

R263 255/FR263 255/F

R264 39R264 39

R252

R252

10K

10K

R270

R270

4.99K/F

4.99K/F

R254

R254

10K

10K

D32

H30

H29

G26

G25

B38

C35

F32

C33

C32

A33

A32

E27

E26

C37

B35

A37

B37

B34

A36

G30

D30

F29

F30

D29

F28

A16

C18

A19

B16

B18

B19

E23

D23

C22

B22

A21

B21

C26

C25

G23

H23

U5C

U5C

J30

J20

J22

Calistoga

Calistoga

L_BKLTCTL

L_BKLTEN

L_CLKCTLA

L_CLKCTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

LVDS

LVDS

TV

TV

VGA

VGA

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

1

08

VCC1.5

R246 24.9/FR246 24.9/F

1.MCH_CFG_5 Low = DMI X2, High=DMIX4

A A

3.MCH_CFG_7 CPU Strap Low=RSVD, High=Mobile CPU

4.MCH_CFG_9 PCI Exp Graphics Lane: Low =Reserved,High=Mobility

8.MCH_CFG_18 VCC Select: LOW=1.05V, High=1.5V

9.MCH_CFG_19 DMI LANE Reversal:Low=Normal,High=LANES Reversed.

10.MCH_CFG_20 PCIE Backward interpoerability mode: Low= only SDVO

or PCIE x1 is operational (defaults) ,High=SDVO and PCIE x1 are

operation simultaneously via the PEG port.

5

GMCH Strap pin

MCH_CFG_5

MCH_CFG_7

MCH_CFG_9

MCH_CFG_12

MCH_CFG_13

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

4

R297 *2.2KR297 *2.2K

R276 *2.2KR276 *2.2K

R289 *2.2KR289 *2.2K

R303 *2.2KR303 *2.2K

R280 *2.2KR280 *2.2K

R260 *1KR260 *1K

R248 *1KR248 *1K

R257 *1KR257 *1K

VCC3

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

3

2

Date: Sheet

COMPUTER

GMCH DMI Video ( 3 of 6 )

GMCH DMI Video ( 3 of 6 )

GMCH DMI Video ( 3 of 6 )

DO1

DO1

DO1

1

3C

3C

839Thursday, February 09, 2006

839Thursday, February 09, 2006

839Thursday, February 09, 2006

3C

of

of

of

Page 9

5

U5G

GMCH_VTT

C364

C245

C245

C416

C416

C355

10U

10U

C355

10U

10U

+

+

470U

470U

D D

C C

B B

A A

C364

C347

C425

C425

10U

10U

5

C347

.1U

.1U

.1U

.1U

AA33

W33

P33

N33

L33

AA32

Y32

W32

V32

P32

N32

M32

L32

AA31

W31

V31

T31

R31

P31

N31

M31

AA30

Y30

W30

V30

U30

T30

R30

P30

N30

M30

L30

AA29

Y29

W29

V29

U29

R29

P29

M29

L29

AB28

AA28

Y28

V28

U28

T28

R28

P28

N28

M28

L28

P27

N27

M27

L27

P26

N26

L26

N25

M25

L25

P24

N24

M24

AB23

AA23

Y23

P23

N23

M23

L23

AC22

AB22

Y22

W22

P22

N22

M22

L22

AC21

AA21

W21

N21

M21

L21

AC20

AB20

Y20

W20

P20

N20

M20

L20

AB19

AA19

Y19

N19

M19

L19

N18

M18

L18

P17

N17

M17

N16

M16

L16

U5G

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

J33

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

J32

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

Calistoga

Calistoga

4

VCC

VCC

4

VCC_SM_0

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_SM_37

VCC_SM_38

VCC_SM_39

VCC_SM_40

VCC_SM_41

VCC_SM_42

VCC_SM_43

VCC_SM_44

VCC_SM_45

VCC_SM_46

VCC_SM_47

VCC_SM_48

VCC_SM_49

VCC_SM_50

VCC_SM_51

VCC_SM_52

VCC_SM_53

VCC_SM_54

VCC_SM_55

VCC_SM_56

VCC_SM_57

VCC_SM_58

VCC_SM_59

VCC_SM_60

VCC_SM_61

VCC_SM_62

VCC_SM_63

VCC_SM_64

VCC_SM_65

VCC_SM_66

VCC_SM_67

VCC_SM_68

VCC_SM_69

VCC_SM_70

VCC_SM_71

VCC_SM_72

VCC_SM_73

VCC_SM_74

VCC_SM_75

VCC_SM_76

VCC_SM_77

VCC_SM_78

VCC_SM_79

VCC_SM_80

VCC_SM_81

VCC_SM_82

VCC_SM_83

VCC_SM_84

VCC_SM_85

VCC_SM_86

VCC_SM_87

VCC_SM_88

VCC_SM_89

VCC_SM_90

VCC_SM_91

VCC_SM_92

VCC_SM_93

VCC_SM_94

VCC_SM_95

VCC_SM_96

VCC_SM_97

VCC_SM_98

VCC_SM_99

VCC_SM_100

VCC_SM_101

VCC_SM_102

VCC_SM_103

VCC_SM_104

VCC_SM_105

VCC_SM_106

VCC_SM_107

AU41

AT41

AM41

AU40

BA34

AY34

AW34

AV34

AU34

AT34

AR34

BA30

AY30

AW30

AV30

AU30

AT30

AR30

AP30

AN30

AM30

AM29

AL29

AK29

AJ29

AH29

AJ28

AH28

AJ27

AH27

BA26

AY26

AW26

AV26

AU26

AT26

AR26

AJ26

AH26

AJ25

AH25

AJ24

AH24

BA23

AJ23

BA22

AY22

AW22

AV22

AU22

AT22

AR22

AP22

AK22

AJ22

AK21

AK20

BA19

AY19

AW19

AV19

AU19

AT19

AR19

AP19

AK19

AJ19

AJ18

AJ17

AH17

AJ16

AH16

BA15

AY15

AW15

AV15

AU15

AT15

AR15

AJ15

AJ14

AJ13

AH13

AK12

AJ12

AH12

AG12

AK11

BA8

AY8

AW8

AV8

AT8

AR8

AP8

BA6

AY6

AW6

AV6

AT6

AR6

AP6

AN6

AL6

AK6

AJ6

AV1

AJ1

C250 0.47UC250 0.47U

C251 0.47UC251 0.47U

C405 0.47UC405 0.47U

C395 0.47UC395 0.47U

3

1.8VSUS

+

+

C429

C429

330U

330U

2.5

2.5

C305

C305

0.47U

0.47U

C343

C343

10U

10U

C371

C371

C294

C294

0.047U

0.047U

10U

10U

C301

C301

place C50 on BA23 Ball

0.47U

0.47U

place C49 on AJ23 Ball

place C51 on BA15 Ball

C348

C348

0.47U

0.47U

3

GMCH_VTT

2

1

09

VCC1.55,8,10,15,17,21,24,33,34

GMCH_VTT4,5,6,10,13,14,17,33

1.8VSUS8,12,28,34,35

AD27

AC27

AB27

AA27

AD26

AC26

AB26

AA26

AD25

AC25

AB25

AA25

AD24

AC24

AB24

AA24

AD23

AD22

AD21

AD20

AD19

AD18

AC18

AB18

AA18

2

VCC1.5

GMCH_VTT

1.8VSUS

U5F

U5F

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

Y27

VCC_NCTF4

W27

VCC_NCTF5

V27

VCC_NCTF6

U27

VCC_NCTF7

T27

VCC_NCTF8

R27

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

Y26

VCC_NCTF14

W26

VCC_NCTF15

V26

VCC_NCTF16

U26

VCC_NCTF17

T26

VCC_NCTF18

R26

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

Y25

VCC_NCTF24

W25

VCC_NCTF25

V25

VCC_NCTF26

U25

VCC_NCTF27

T25

VCC_NCTF28

R25

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

Y24

VCC_NCTF34

W24

VCC_NCTF35

V24

VCC_NCTF36

U24

VCC_NCTF37

T24

VCC_NCTF38

R24

VCC_NCTF39

VCC_NCTF40

V23

VCC_NCTF41

U23

VCC_NCTF42

T23

VCC_NCTF43

R23

VCC_NCTF44

VCC_NCTF45

V22

VCC_NCTF46

U22

VCC_NCTF47

T22

VCC_NCTF48

R22

VCC_NCTF49

VCC_NCTF50

V21

VCC_NCTF51

U21

VCC_NCTF52

T21

VCC_NCTF53

R21

VCC_NCTF54

VCC_NCTF55

V20

VCC_NCTF56

U20

VCC_NCTF57

T20

VCC_NCTF58

R20

VCC_NCTF59

VCC_NCTF60

V19

VCC_NCTF61

U19

VCC_NCTF62

T19

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

Y18

VCC_NCTF68

W18

VCC_NCTF69

V18

VCC_NCTF70

U18

VCC_NCTF71

T18

VCC_NCTF72

Calistoga

Calistoga

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

NCTF

NCTF

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

GMCH Power & Strap ( 4 of 6 )

GMCH Power & Strap ( 4 of 6 )

GMCH Power & Strap ( 4 of 6 )

DO1

DO1

Thursday, February 09, 2006

Thursday, February 09, 2006

Thursday, February 09, 2006

DO1

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VCCAUX_NCTF0

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VCCAUX_NCTF39

VCCAUX_NCTF40

VCCAUX_NCTF41

VCCAUX_NCTF42

VCCAUX_NCTF43

VCCAUX_NCTF44

VCCAUX_NCTF45

VCCAUX_NCTF46

VCCAUX_NCTF47

VCCAUX_NCTF48

VCCAUX_NCTF49

VCCAUX_NCTF50

VCCAUX_NCTF51

VCCAUX_NCTF52

VCCAUX_NCTF53

VCCAUX_NCTF54

VCCAUX_NCTF55

VCCAUX_NCTF56

VCCAUX_NCTF57

AE27

AE26

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AC17

Y17

U17

AG27

AF27

AG26

AF26

AG25

AF25

AG24

AF24

AG23

AF23

AG22

AF22

AG21

AF21

AG20

AF20

AG19

AF19

R19

AG18

AF18

R18

AG17

AF17

AE17

AD17

AB17

AA17

W17

V17

T17

R17

AG16

AF16

AE16

AD16

AC16

AB16

AA16

Y16

W16

V16

U16

T16

R16

AG15

AF15

AE15

AD15

AC15

AB15

AA15

Y15

W15

V15

U15

T15

R15

9

9

9

of

of

of

39

39

1

39

VCC1.5

3C

3C

3C

Page 10

5

GMCH_VTT

VCC1.5

VCC2.5

VCC3

D D

C C

B B

A A

GMCH_VTT 4,5,6,9,13,14,17,33

VCC1.5 5,8,9,15,17,21,24,33,34

VCC2.5 23,34,35

VCC3 8,12,13,14,15,16,17,18,19,21,22,23,24,25,27,28,30,32,34

GMCH_VTTVCC2.5

21

D3

PDZ5.6BD3PDZ5.6B

R2710R27

10

L20

L20

FCM2012C-181

FCM2012C-181

VCC1.5VCC3

21

D9

PDZ5.6BD9PDZ5.6B

R280R28

0

R2910R29

10

L21

L21

FCM2012C-181

FCM2012C-181

5

C108

C108

0.1U

0.1U

C104

C104

0.1U

0.1U

C107

C107

0.1U

0.1U

VCC1.5

+V2.5_CRTDAC

C103

C103

0.022U

0.022U

C332

C332

0.022U

0.022U

L31

L31

FCM2012C-181

FCM2012C-181

C337

C337

0.022U

0.022U

+V3.3_TVDAC_FB

C100

C100

10U

10U

4

VCC2.5

C279

C279

0.1U

0.1U

C262

C262

0.1U

0.1U

VCC1.5

C243

C243

220U

220U

C297

C297

0.1U

0.1U

C288

C288

10U

10U

VCC1.5

+

+

VCC1.5

C248

C248

10U

10U

C257

C257

0.1U

0.1U

C291

C291

0.1U

0.1U

C411

C411

22U

22U

C252

C252

C244

C244

10U

10U

10U

10U

+V2.5_CRTDAC

VCC2.5

C247

C247

0.1U

0.1U

C415

C415

0.1U

0.1U

C283

C283

0.1U

0.1U

C258

C258

0.01U

0.01U

+V3.3_TVDAC_FB

VCC3

C277

C277

4.7U

4.7U

C407

C407

+

+

C439

C439

10U

10U

470U

470U

4

VCC2.5

VCC2.5

C255

C255

C320

C320

10U

10U

0.1U

0.1U

+V3.3_TVDAC_FB

VCC1.5

C316

C316

10U

10U

VCC1.5

C345

C345

0.1U

0.1U

VCC1.5

C271

C271

0.1U

0.1U

3

C323

C323

0.1U

0.1U

C335

C335

0.1U

0.1U

C342

C342

0.022U

0.022U

3

C278

C278

0.1U

0.1U

C321

C321

0.022U

0.022U

C312

C312

0.1U

0.1U

C280

C280

0.1U

0.1U

C341

C341

0.022U

0.022U

C349

C349

0.022U

0.022U

H22

C30

B30

A30

AJ41

AB41

Y41

V41

R41

N41

L41

AC33

G41

H41

F21

E21

G21

B26

C39

AF1

A38

B39

AF2

H20

G20

E19

F19

C20

D20

E20

F20

AH1

AH2

A28

B28

C28

D21

A23

B23

B25

H19

AK31

AF31

AE31

AC31

AL30

AK30

AJ30

AH30

AG30

AF30

AE30

AD30

AC30

AG29

AF29

AE29

AD29

AC29

AG28

AF28

AE28

AH22

AJ21

AH21

AJ20

AH20

AH19

P19

P16

AH15

P15

AH14

AG14

AF14

AE14

Y14

AF13

AE13

AF12

AE12

AD12

U5H

U5H

VCCSYNC

VCC_TXLVDS0

VCC_TXLVDS1

VCC_TXLVDS2

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_LVDS

VSSA_LVDS

VCCA_MPLL

VCCA_TVBG

VSSA_TVBG

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCD_HMPLL0

VCCD_HMPLL1

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCD_TVDAC

VCC_HV0

VCC_HV1

VCC_HV2

VCCD_QTVDAC

VCCAUX0

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VCCAUX29

VCCAUX30

VCCAUX31

VCCAUX32

VCCAUX33

VCCAUX34

VCCAUX35

VCCAUX36

VCCAUX37

VCCAUX38

VCCAUX39

VCCAUX40

Calistoga

Calistoga

POWER

POWER

2

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_30

VTT_31

VTT_32

VTT_33

VTT_34

VTT_35

VTT_36

VTT_37

VTT_38

VTT_39

VTT_40

VTT_41

VTT_42

VTT_43

VTT_44

VTT_45

VTT_46

VTT_47

VTT_48

VTT_49

VTT_50

VTT_51

VTT_52

VTT_53

VTT_54

VTT_55

VTT_56

VTT_57

VTT_58

VTT_59

VTT_60

VTT_61

VTT_62

VTT_63

VTT_64

VTT_65

VTT_66

VTT_67

VTT_68

VTT_69

VTT_70

VTT_71

VTT_72

VTT_73

VTT_74

VTT_75

VTT_76

2

VTT_0

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

AC14

AB14

W14

V14

T14

R14

P14

N14

M14

L14

AD13

AC13

AB13

AA13

Y13

W13

V13

U13

T13

R13

N13

M13

L13

AB12

AA12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

L12

R11

P11

N11

M11

R10

P10

N10

M10

P9

N9

M9

R8

P8

N8

M8

P7

N7

M7

R6

P6

M6

A6

R5

P5

N5

M5

P4

N4

M4

R3

P3

N3

M3

R2

P2

M2

D2

AB1

R1

P1

N1

M1

1

GMCH_VTT

GMCH_VTT

+

+

C436

C436

330U

330U

C284

C284

0.22U

0.22U

C381

C381

0.47U

0.47U

C408

C408

0.47U

0.47U

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

COMPUTER

GMCH Power 2 ( 5 of 6 )

GMCH Power 2 ( 5 of 6 )

GMCH Power 2 ( 5 of 6 )

C290

C290

4.7U

4.7U

C412

C412

0.22U

0.22U

DO1

DO1

DO1

C307

C307

0.22U

0.22U

C298

C298

2.2U

2.2U

C354

C354

0.47U

0.47U

1

C390

C390

0.1U

0.1U

GMCH_VTT

C336

C336

0.47U

0.47U

10 39Thursday, February 09, 2006

10 39Thursday, February 09, 2006

10 39Thursday, February 09, 2006

10

of

of

of

3C

3C

3C

Page 11

5

U5I

U5I

AC41

VSS_0

AA41

VSS_1

W41

VSS_2

T41

VSS_3

P41

VSS_4

M41

VSS_5

J41

VSS_6

F41

VSS_7

AV40

VSS_8

D D

C C

B B

A A

5

AP40

AN40

AK40

AJ40

AH40

AG40

AF40

AE40

B40