Page 1

5

www.schematic-x.blogspot.com

4

3

2

1

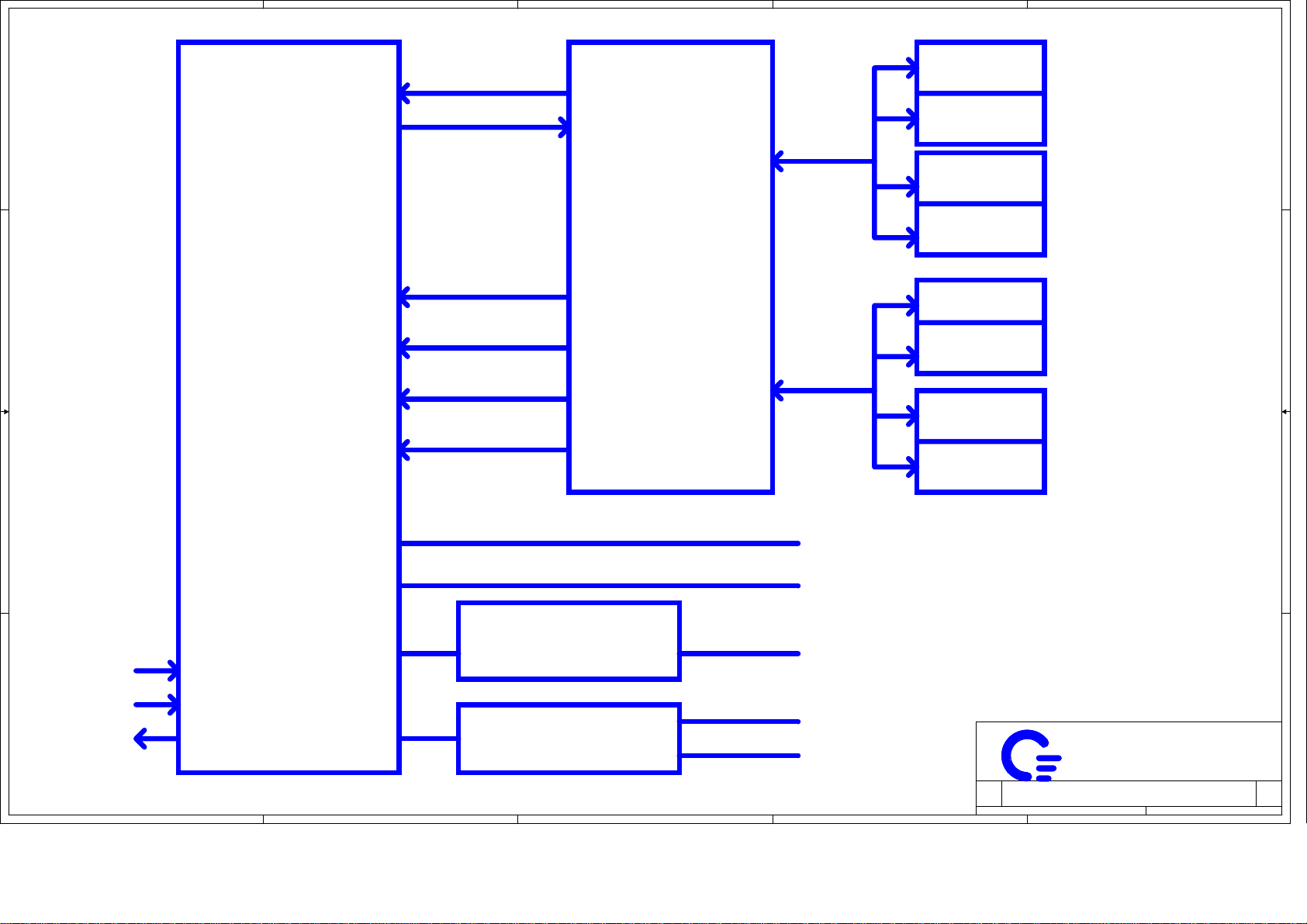

GDDR2

D D

PCI-E x16

ATi

GDDR2

PAGE 8

CH-A

M86-M

FCBGA

GDDR2

GDDR2

PAGE 8

880pin

VGA

C C

CONNECTOR

TV

GDDR2

CRT

GDDR2

PAGE 9

TMDS

CH-B

GDDR2

LVDS

PAGE 3, 4, 5, 6, 7, 10

B B

+5V

GDDR2

PAGE 9

+3.3V

VIN

VGA CORE POWER

OZ8118

PAGE 11

VDD_CORE

GFXON

A A

GFXRST#

GFXPG

1.8V / 1.1V POWERVIN

PAGE 2

5

4

RT8204

PAGE 12

3

+1.8V

+1.1V

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :BD3

PROJECT :BD3

Quanta Computer Inc.

Quanta Computer Inc.

11

11

11

1

1A

1A

1A

3Wednesday, November 07, 2007

3Wednesday, November 07, 2007

3Wednesday, November 07, 2007

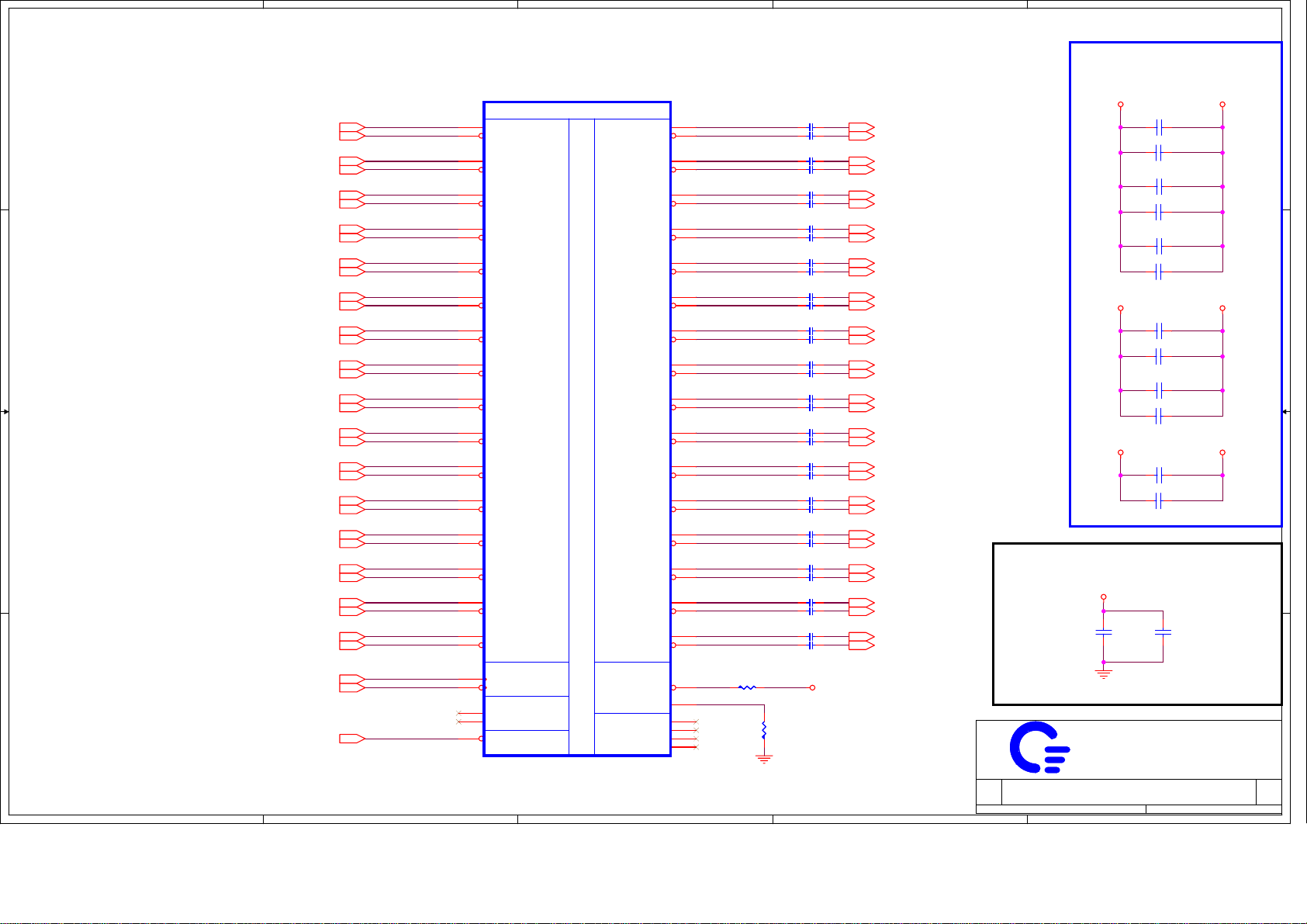

Page 2

5

CN1

C256

C256

10u_6

10u_6

PEG_TXN15

PEG_TXP15

PEG_TXN14

PEG_TXP14

PEG_TXN13

PEG_TXP13

PEG_TXN12

PEG_TXP12

PEG_TXN11

PEG_TXP11

PEG_TXN10

PEG_TXP10

PEG_TXN9

PEG_TXP9

PEG_TXN8

PEG_TXP8

PEG_TXN7

PEG_TXP7

PEG_TXN6

PEG_TXP6

PEG_TXN5

PEG_TXP5

PEG_TXN4

PEG_TXP4

PEG_TXN3

PEG_TXP3

PEG_TXN2

PEG_TXP2

PEG_TXN1

PEG_TXP1

PEG_TXN0

PEG_TXP0

EXT_CRT_DDCCLK

EXT_CRT_DDCDAT

EXT_HDMI_DDCCLK

EXT_HDMI_DDCDAT

EXT_LVDS_PNLCLK

EXT_LVDS_PNLDAT

EXT_VGA_RED

EXT_VGA_GRN

EXT_VGA_BLU

EXT_LVDS_TXL#2

EXT_LVDS_TXL2

EXT_LVDS_TXL#1

EXT_LVDS_TXL1

EXT_LVDS_TXL#0

EXT_LVDS_TXL0

EXT_LVDS_TXLCK#

EXT_LVDS_TXLCK

EXT_TV_C/R

EXT_TV_Y/G

EXT_TV_COMP

EXT_HDMICLK-

EXT_HDMICLK+

EXT_HDMITX2N

EXT_HDMITX2P

EXT_HDMITX1N

EXT_HDMITX1P

EXT_HDMITX0N

EXT_HDMITX0P

VIN VIN

C257

0.1u_4

0.1u_4

C261

C261

*0.1u_4

*0.1u_4

PEG_TXN15(3)

PEG_TXP15(3)

PEG_TXN14(3)

PEG_TXP14(3)

PEG_TXN13(3)

PEG_TXP13(3)

PEG_TXN12(3)

PEG_TXP12(3)

PEG_TXN11(3)

D D

C C

B B

A A

PEG_TXP11(3)

PEG_TXN10(3)

PEG_TXP10(3)

PEG_TXN9(3)

PEG_TXP9(3)

PEG_TXN8(3)

PEG_TXP8(3)

PEG_TXN7(3)

PEG_TXP7(3)

PEG_TXN6(3)

PEG_TXP6(3)

PEG_TXN5(3)

PEG_TXP5(3)

PEG_TXN4(3)

PEG_TXP4(3)

PEG_TXN3(3)

PEG_TXP3(3)

PEG_TXN2(3)

PEG_TXP2(3)

PEG_TXN1(3)

PEG_TXP1(3)

PEG_TXN0(3)

PEG_TXP0(3)

EXT_CRT_DDCCLK(4)

EXT_CRT_DDCDAT(4)

EXT_LVDS_PNLCLK(4)

EXT_LVDS_PNLDAT(4)

EXT_VGA_RED(4)

EXT_VGA_GRN(4)

EXT_VGA_BLU(4)

EXT_LVDS_TXL#2(4)

EXT_LVDS_TXL2(4)

EXT_LVDS_TXL#1(4)

EXT_LVDS_TXL1(4)

EXT_LVDS_TXL#0(4)

EXT_LVDS_TXL0(4)

EXT_LVDS_TXLCK#(4)

EXT_LVDS_TXLCK(4)

EXT_TV_C/R(4)

EXT_TV_Y/G(4)

EXT_TV_COMP(4)

C258

0.1u_4

0.1u_4

SYSFANON# GFXON

5

C254

C254

10u_6

10u_6

CN1

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

34

34

36

36

38

38

40

40

42

42

44

44

46

46

48

48

50

50

52

52

54

54

56

56

58

58

60

60

62

62

64

64

66

66

68

68

70

70

72

72

74

74

76

76

78

78

80

80

82

82

84

84

86

86

88

88

90

90

92

92

94

94

96

96

98

98

100

100

102

102

104

104

106

106

108

108

110

110

112

112

114

114

116

116

118

118

120

120

122

122

124

124

126

126

128

128

130

130

132

132

134

134

136

136

138

138

140

140

142

142

144

144

146

146

148

148

150

150

152

152

154

154

156

156

158

158

160

160

162

162

164

164

166

166

168

168

170

170

172

172

174

174

176

176

178

178

180

180

182

182

184

184

186

186

188

188

190

190

192

192

194

194

196

196

198

198

200

200

FOXCONN-HOUSING

FOXCONN-HOUSING

VIN+3V +5V

C259

C259

*0.1u/50V_6

*0.1u/50V_6

C262

C262

*0.1u_4

*0.1u_4

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

C255

C255

*0.1u/50V_6

*0.1u/50V_6

4

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

4

PEG_RXN15

PEG_RXP15

PEG_RXN14

PEG_RXP14

PEG_RXN13

PEG_RXP13

PEG_RXN12

PEG_RXP12

PEG_RXN11

PEG_RXP11

PEG_RXN10

PEG_RXP10

PEG_RXN9

PEG_RXP9

PEG_RXN8

PEG_RXP8

PEG_RXN7

PEG_RXP7

PEG_RXN6

PEG_RXP6

PEG_RXN5

PEG_RXP5

PEG_RXN4

PEG_RXP4

PEG_RXN3

PEG_RXP3

PEG_RXN2

PEG_RXP2

PEG_RXN1

PEG_RXP1

PEG_RXN0

PEG_RXP0

MXM_REFCLKN

MXM_REFCLKP

GFXRST#

SYSFANON#

GFXON

GFXPG

VGA_MBDATA

VGA_MBCLK

LVDS_BLON

DISP_ON

DVI_HPD

EXT_HSYNC

EXT_VSYNC

EXT_LVDS_TXU#2

EXT_LVDS_TXU2

EXT_LVDS_TXU#1

EXT_LVDS_TXU1

EXT_LVDS_TXU#0

EXT_LVDS_TXU0

EXT_LVDS_TXUCK#

EXT_LVDS_TXUCK

+5V

+3V

PEG_RXN15 (3)

PEG_RXP15 (3)

PEG_RXN14 (3)

PEG_RXP14 (3)

PEG_RXN13

PEG_RXP13 (3)

PEG_RXN12 (3)

PEG_RXP12 (3)

PEG_RXN11

PEG_RXP11 (3)

PEG_RXN10

PEG_RXP10 (3)

PEG_RXN9 (3)

PEG_RXP9 (3)

PEG_RXN8 (3)

PEG_RXP8 (3)

PEG_RXN7 (3)

PEG_RXP7 (3)

PEG_RXN6 (3)

PEG_RXP6 (3)

PEG_RXN5 (3)

PEG_RXP5 (3)

PEG_RXN4 (3)

PEG_RXP4 (3)

PEG_RXN3 (3)

PEG_RXP3 (3)

PEG_RXN2 (3)

PEG_RXP2 (3)

PEG_RXN1 (3)

PEG_RXP1 (3)

PEG_RXN0 (3)

PEG_RXP0 (3)

MXM_REFCLKN (3)

MXM_REFCLKP (3)

GFXRST# (3)

SYSFANON# (10)

GFXON (11)

VGA_MBDATA (10)

VGA_MBCLK (10)

EXT_LVDS_BLON (4)

EXT_DISP_ON (4)

DVI_HPD (4)

EXT_HSYNC (4,10)

EXT_VSYNC (4,10)

EXT_LVDS_TXU#2 (4)

EXT_LVDS_TXU2 (4)

EXT_LVDS_TXU#1 (4)

EXT_LVDS_TXU1 (4)

EXT_LVDS_TXU#0 (4)

EXT_LVDS_TXU0 (4)

EXT_LVDS_TXUCK# (4)

EXT_LVDS_TXUCK (4)

HDMICLK-(4)

HDMICLK+(4)

HDMITX0N(4)

HDMITX0P(4)

HDMITX1N(4)

HDMITX1P(4)

HDMITX2N(4)

HDMITX2P(4)

(3)

(3)

(3)

HDMICLKHDMICLK+

HDMITX0N

HDMITX0P

HDMITX1N

HDMITX1P

HDMITX2N

HDMITX2P

HDMICLKHDMICLK+

HDMITX0N

HDMITX0P

HDMITX1N

HDMITX1P

HDMITX2N

HDMITX2P

R108 *M7X@0_4R108 *M7X@0_4

R109 *M7X@0_4R109 *M7X@0_4

R114 *M7X@0_4R114 *M7X@0_4

R115 *M7X@0_4R115 *M7X@0_4

R112 *M7X@0_4R112 *M7X@0_4

R113 *M7X@0_4R113 *M7X@0_4

R110 *M7X@0_4R110 *M7X@0_4

R111 *M7X@0_4R111 *M7X@0_4

C243 0.1u_4C243 0.1u_4

C244 0.1u_4C244 0.1u_4

C249 0.1u_4C249 0.1u_4

C250 0.1u_4C250 0.1u_4

C247 0.1u_4C247 0.1u_4

C248 0.1u_4C248 0.1u_4

C245 0.1u_4C245 0.1u_4

C246 0.1u_4C246 0.1u_4C257

+5V

R117

R117

100K_4

100K_4

3

COMPARATOR LEVEL SHIFT LOGIC

M8X STUFF MOS TYPE LEVEL SHIFT

+3V_D

R127

R127

R134

R134

*10K_4

*10K_4

*10K_4

R125

R125

499/F_4

499/F_4

*10K_4

1

Q4

Q4

*RHU002N06

*RHU002N06

1

Q7

Q7

*RHU002N06

*RHU002N06

+3V_FIL

R20

R20

*M7X@27.4K/F_4

*M7X@27.4K/F_4

R23

R23

*M7X@4.64K/F_4

*M7X@4.64K/F_4

1

U11A

U11A

*M7X@LM339_ON

*M7X@LM339_ON

R17

R17

*M7X@27.4K/F_4

*M7X@27.4K/F_4

R14

R14

*M7X@4.64K/F_4

*M7X@4.64K/F_4

14

U11C

U11C

*M7X@LM339_ON

*M7X@LM339_ON

R124

R124

499/F_4

499/F_4

+3V_D

+5V

R119

R119

499/F_4

499/F_4

DDC3DAT(4)

DDC3CLK(4)

DDC3DAT

DDC3CLK

M7X STUFF OP-AMP (LM339) TYPE LEVEL SHIFT

+3V_D

L5

L5

*M7X@BLM15BD121SN1

*M7X@BLM15BD121SN1

C22

C22

C23

C23

*M7X@1u_4

*M7X@1u_4

*M7X@0.1u_4

*M7X@0.1u_4

DDC3DAT

DDC3CLK

EXT_HDMICLKEXT_HDMICLK+

EXT_HDMITX0N

EXT_HDMITX0P

EXT_HDMITX1N

EXT_HDMITX1P

EXT_HDMITX2N

EXT_HDMITX2P

R121

R121

R120

R120

499/F_4

499/F_4

499/F_4

499/F_4

3

2

Q3

Q3

RHU002N06

RHU002N06

1

3

OPTION WITH M7X and M8X

R122

R122

R123

R123

499/F_4

499/F_4

499/F_4

499/F_4

2

2

312

+

+

+

+

-

-

-

-

20mil

7

6

9

8

2

3

3

C178

C178

*M7X@0.1u_4

*M7X@0.1u_4

VREF2_1.5V

R78

R78

*M7X@1.1K/F_4

*M7X@1.1K/F_4

VREF2 = 1.5V

EXT_HDMICLK-

EXT_HDMICLK+

EXT_HDMITX0N

EXT_HDMITX0P

EXT_HDMITX1N

EXT_HDMITX1P

EXT_HDMITX2N

EXT_HDMITX2P

R118

R118

499/F_4

499/F_4

2

DDC3DAT

DDC3CLK

+5V

R133

R133

R129

R129

*2K_4

*2K_4

*2K_4

*2K_4

EXT_HDMI_DDCDAT

EXT_HDMI_DDCCLK

used in M7x series

R21

R21

*M7X@4.99K/F_4

*M7X@4.99K/F_4

R79

R79

*M7X@3.01K/F_4

*M7X@3.01K/F_4

VREF1_0.4V

C98

C98

*M7X@0.1u_4

*M7X@0.1u_4

VREF1_0.4V

5

4

11

10

Fine-tune Power-on sequence

GFXPG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

VGA CONNECTOR

VGA CONNECTOR

VGA CONNECTOR

Date: Sheet

Date: Sheet of

Date: Sheet of

R22 0_4R22 0_4

R13 0_4R13 0_4

+

+

-

-

+

+

-

-

EXT_HDMI_DDCDAT

EXT_HDMI_DDCCLK

+5V

R19

R19

*M7X@2K/F_4

*M7X@2K/F_4

EXT_HDMI_DDCDAT

2

U11B

U11B

*M7X@LM339_ON

*M7X@LM339_ON

+5V

R16

R16

*M7X@2K/F_4

*M7X@2K/F_4

EXT_HDMI_DDCCLK

13

U11D

U11D

*M7X@LM339_ON

*M7X@LM339_ON

R136 *0_4R136 *0_4

+3V

R137

R137

0_6

0_6

53

1

4

2

U13

U13

NC7SZ08P5X

NC7SZ08P5XC258

R138 *0_4R138 *0_4

PROJECT :BD3

PROJECT :BD3

Quanta Computer Inc.

Quanta Computer Inc.

C263

C263

0.1u_4

0.1u_4

1

HWPG_1.8V (12)

HWPG_1.1V (12)

1A

1A

1A

of

213Monday, November 12, 2007

213Monday, November 12, 2007

213Monday, November 12, 2007

1

Page 3

5

4

3

2

1

STITCH CAPACITORS

U5A

U5A

D D

C C

B B

A A

5

PEG_TXP0(2)

PEG_TXN0(2)

PEG_TXP1(2)

PEG_TXN1(2)

PEG_TXP2(2)

PEG_TXN2(2)

PEG_TXP3(2)

PEG_TXN3(2)

PEG_TXP4(2)

PEG_TXN4(2)

PEG_TXP5(2)

PEG_TXN5(2)

PEG_TXP6(2)

PEG_TXN6(2)

PEG_TXP7(2)

PEG_TXN7(2)

PEG_TXP8(2)

PEG_TXN8(2)

PEG_TXP9(2)

PEG_TXN9(2)

PEG_TXP10(2)

PEG_TXN10(2)

PEG_TXP11(2)

PEG_TXN11(2)

PEG_TXP12(2)

PEG_TXN12(2)

PEG_TXP13(2)

PEG_TXN13(2)

PEG_TXP14(2)

PEG_TXN14(2)

PEG_TXP15(2)

PEG_TXN15(2)

MXM_REFCLKP(2)

MXM_REFCLKN(2)

GFXRST#(2)

PEG_TXP0

PEG_TXN0

PEG_TXP1

PEG_TXN1

PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_TXP8

PEG_TXN8

PEG_TXP9

PEG_TXN9

PEG_TXP10

PEG_TXN10

PEG_TXP11

PEG_TXN11

PEG_TXP12

PEG_TXN12

PEG_TXP13

PEG_TXN13

PEG_TXP14

PEG_TXN14

PEG_TXP15

PEG_TXN15

MXM_REFCLKP

MXM_REFCLKN

GFXRST#

4

AK33

AJ33

AJ35

AJ34

AH35

AH34

AG35

AG34

AF33

AE33

AE35

AE34

AD35

AD34

AC35

AC34

AB33

AA33

AA35

AA34

Y35

Y34

W35

W34

V33

U33

U35

U34

T35

T34

R35

R34

AJ31

AJ30

AK35

AK34

AM32

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

Clock

Clock

PCIE_REFCLKP

PCIE_REFCLKN

SM Bus

SM Bus

NC_SMB_DATA

NC_SMBCLK

PERSTB

M86-M

M86-M

PART 1 OF 7

PART 1 OF 7

P

P

C

C

I

I

-

E

E

X

X

P

P

R

R

E

E

S

S

S

S

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

Calibration

PCIE_CALRN

PCIE_CALRP

NC_DRAM_0

NC_DRAM_1

NC_AC_BATT

NC_FAN_TACH

3

AG31

AG30

AF31

AF30

AF28

AF27

AD31

AD30

AD28

AD27

AB31

AB30

AB28

AB27

AA31

AA30

AA28

AA27

W31

W30

W28

W27

V31

V30

V28

V27

U31

U30

U28

U27

R31

R30

AG26

AJ27

AF3

AG9

AK29

AK14

C_PEG_RXP0

C_PEG_RXN0

C_PEG_RXP1

C_PEG_RXN1

C_PEG_RXP2

C_PEG_RXN2

C_PEG_RXP3

C_PEG_RXN3

C_PEG_RXP4

C_PEG_RXN4

C_PEG_RXP5

C_PEG_RXN5

C_PEG_RXP6

C_PEG_RXN6

C_PEG_RXP7

C_PEG_RXN7

C_PEG_RXP8

C_PEG_RXN8

C_PEG_RXP9

C_PEG_RXN9

C_PEG_RXP10

C_PEG_RXN10

C_PEG_RXP11

C_PEG_RXN11

C_PEG_RXP12

C_PEG_RXN12

C_PEG_RXP13

C_PEG_RXN13

C_PEG_RXP14

C_PEG_RXN14

C_PEG_RXP15

C_PEG_RXN15

R89 2K/F_4R89 2K/F_4

R90

R90

1.27K/F_4

1.27K/F_4

C2210.1u_4 C2210.1u_4

C2200.1u_4 C2200.1u_4

C2330.1u_4 C2330.1u_4

C2320.1u_4 C2320.1u_4

C2190.1u_4 C2190.1u_4

C2180.1u_4 C2180.1u_4

C2310.1u_4 C2310.1u_4

C2300.1u_4 C2300.1u_4

C2170.1u_4 C2170.1u_4

C2160.1u_4 C2160.1u_4

C2290.1u_4 C2290.1u_4

C2280.1u_4 C2280.1u_4

C2150.1u_4 C2150.1u_4

C2140.1u_4 C2140.1u_4

C2270.1u_4 C2270.1u_4

C2260.1u_4 C2260.1u_4

C2130.1u_4 C2130.1u_4

C2120.1u_4 C2120.1u_4

C2250.1u_4 C2250.1u_4

C2240.1u_4 C2240.1u_4

C2110.1u_4 C2110.1u_4

C2100.1u_4 C2100.1u_4

C2350.1u_4 C2350.1u_4

C2340.1u_4 C2340.1u_4

C2090.1u_4 C2090.1u_4

C2080.1u_4 C2080.1u_4

C2390.1u_4 C2390.1u_4

C2380.1u_4 C2380.1u_4

C2070.1u_4 C2070.1u_4

C2060.1u_4 C2060.1u_4

C2370.1u_4 C2370.1u_4

C2360.1u_4 C2360.1u_4

+1.1V

PCIE_VDDC

PEG_RXP0 (2)

PEG_RXN0 (2)

PEG_RXP1 (2)

PEG_RXN1 (2)

PEG_RXP2 (2)

PEG_RXN2 (2)

PEG_RXP3 (2)

PEG_RXN3 (2)

PEG_RXP4 (2)

PEG_RXN4 (2)

PEG_RXP5 (2)

PEG_RXN5 (2)

PEG_RXP6 (2)

PEG_RXN6 (2)

(2)

PEG_RXP7

PEG_RXN7 (2)

PEG_RXP8 (2)

PEG_RXN8 (2)

PEG_RXP9 (2)

PEG_RXN9 (2)

PEG_RXP10 (2)

PEG_RXN10 (2)

PEG_RXP11 (2)

PEG_RXN11 (2)

PEG_RXP12 (2)

PEG_RXN12 (2)

PEG_RXP13 (2)

PEG_RXN13 (2)

PEG_RXP14 (2)

PEG_RXN14 (2)

PEG_RXP15 (2)

PEG_RXN15 (2)

2

EMI CAP.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GFX(PCIE I/F)

GFX(PCIE I/F)

GFX(PCIE I/F)

Date: Sheet of

Date: Sheet of

Date: Sheet

VIN +1.8V

C260 0.1u/50V_6C260 0.1u/50V_6

C48 1n/50V_6C48 1n/50V_6

1 2

C59 0.1u/50V_6C59 0.1u/50V_6

C205 1n/50V_6C205 1n/50V_6

1 2

C49 0.1u/50V_6C49 0.1u/50V_6

C123 1n/50V_6C123 1n/50V_6

1 2

+1.8V

C80 0.1u/50V_6C80 0.1u/50V_6

C88 1n/50V_6C88 1n/50V_6

1 2

C105 0.1u/50V_6C105 0.1u/50V_6

C106 1n/50V_6C106 1n/50V_6

1 2

VIN

C95 0.1u/50V_6C95 0.1u/50V_6

C91 1n/50V_6C91 1n/50V_6

1 2

+5V

C1

C1

*0.1u/50V_6

*0.1u/50V_6

PROJECT :BD3

PROJECT :BD3

Quanta Computer Inc.

Quanta Computer Inc.

1

VDD_CORE

VDD_CORE

C179

C179

*0.1u_4

*0.1u_4

of

31

31

31

1A

1A

1A

3Thursday, November 08, 2007

3Thursday, November 08, 2007

3Thursday, November 08, 2007

Page 4

5

4

3

2

1

120 ohm/300mA

+3V(250mA)

+3V_D

+1.8V

M86-M=> LVDDR+LVDDC(400mA)

D D

+1.8V(400mA)

FOR M7x

INSTALL LVDDR TO +3.3V(250mA) AND

LVDDC TO 1.8V(100mA)

WITH SEPARATE FILTERS

DO NOT INSTALL STRAP RESISTOR

FOR M8x

INSTALL LVDDR AND LVDDC TO +1.8V(400mA)

WITH THE ONE LVDDC FILTER

DO NOT INSTALL LVDDR FILTER

INSTALL STRAP RESISTOR

C C

B B

A A

+1.8V(40mA)

+1.8V

+1.8V +1.8V

*M7X@BLM15BD121SN1L30 *M7X@BLM15BD121SN1L30

L28 BK1608HS220L28 BK1608HS220

22 ohm/1A

22 ohm/1A

L32 BK1608HS220L32 BK1608HS220

BLM15BD121SN1L26 BLM15BD121SN1L26

120 ohm/300mA

5

LVDDR

C183

C183

C165

C165

10u_6

10u_6

1u_4

1u_4

LVDDC

C193

C193

C199

C199

1u_4

1u_4

10u_6

10u_6

LPVDD

C162

C162

C163

C163

10u_6

10u_6

1u_4

1u_4

+1.8V(52mA)

+1.8V

+1.8V(68mA)

+1.8V

VDD_CORE(345mA)

L25 BK1608HS220L25 BK1608HS220

VDD_CORE

+1.1V(80mA)

+1.1V

C182

C182

0.1u_4

0.1u_4

C181

C181

0.1u_4

0.1u_4

C160

C160

0.1u_4

0.1u_4

U5F

U5F

PART 7 OF 7

PART 7 OF 7

AJ26

LVDDR_1

AH26

LVDDR_2

AK27

LVDDC_1

AL27

LVDDC_2

AM24

LVSSR_1

AN28

LVSSR_2

AN21

LVSSR_3

AN24

LVSSR_4

AN25

LVSSR_5

AM22

LVSSR_6

AP21

LVSSR_7

AP26

LVSSR_8

AM27

LVSSR_9

AR21

LVSSR_10

AR26

LVSSR_11

AM26

LVSSR_12

AJ22

LVSSR_13

AJ24

LVSSR_14

AL22

LPVDD

AK22

LPVSS

M86-M

M86-M

BLM15BD121SN1L7 BLM15BD121SN1L7

C24

C24

C30

C30

1u_4

1u_4

10u_6

10u_6

BLM15BD121SN1L35 BLM15BD121SN1L35

C251

C251

C240

C240

10u_6

10u_6

1u_4

1u_4

C150

C150

C131

C131

10u_6

10u_6

1u_4

1u_4

BLM15BD121SN1L20 BLM15BD121SN1L20

C130

C130

C117

C117

10u_6

10u_6

1u_4

1u_4

DPLL_PVDD

C25

C25

0.1u_4

0.1u_4

PCIE_PVDD

C242

C242

0.1u_4

0.1u_4

MPVDD

C139

C139

0.1u_4

0.1u_4

DPLL_VDDC

C148

C148

0.1u_4

0.1u_4

4

Control

Control

TXCLK_UN

TXOUT_U0P

TXOUT_U0N

TXOUT_U1P

TXOUT_U1N

TXOUT_U2P

TXOUT_U2N

TXOUT_U3P

TXOUT_U3N

LVDS channel

LVDS channel

TXOUT_L0P

TXOUT_L0N

TXOUT_L1P

TXOUT_L1N

TXOUT_L2P

TXOUT_L2N

TXOUT_L3P

TXOUT_L3N

VARY_BL

TXCLK_UP

TXCLK_LP

TXCLK_LN

DIGON

EXT_LVDS_BLON(2)

AG7

AJ6

AK24

AL24

AN27

AN26

AP27

AR27

AG24

AH24

AK26

AL26

AR22

AP22

AN23

AN22

AP23

AR23

AP24

AR24

AP25

AR25

+3V_D

R63 *10K_4R63 *10K_4

EXT_DISP_ON (2)

EXT_LVDS_TXUCK (2)

EXT_LVDS_TXUCK# (2)

EXT_LVDS_TXU0 (2)

EXT_LVDS_TXU#0 (2)

EXT_LVDS_TXU1 (2)

EXT_LVDS_TXU#1 (2)

EXT_LVDS_TXU2 (2)

EXT_LVDS_TXU#2 (2)

EXT_LVDS_TXLCK (2)

EXT_LVDS_TXLCK# (2)

EXT_LVDS_TXL0 (2)

EXT_LVDS_TXL#0

EXT_LVDS_TXL1 (2)

EXT_LVDS_TXL#1 (2)

EXT_LVDS_TXL2 (2)

EXT_LVDS_TXL#2 (2)

R55 10K_4R55 10K_4

R66 10K_4R66 10K_4

R61 *10K_4R61 *10K_4

+1.8V

C39 6.8p_4C39 6.8p_4

C43 6.8p_4C43 6.8p_4

R54 *10K_4R54 *10K_4

R73

R73

499/F_4

499/F_4

R75

R75

249/F_4

249/F_4

24

Y1

27MHZY127MHZ

3 1

VCORE1.2ID0(11)

VCORE1.2ID1(11)

SCS#_GPIO22(10)

VIP3(10)

VHAD0(10)

PSYNC(10)

DVALID(10)

(2)

Reserved for I2C Debug

RAM_STRAP0(10)

RAM_STRAP1(10)

RAM_STRAP2(10)

RAM_STRAP3(10)

GPIO0(10)

GPIO1(10)

GPIO2(10)

GPIO3(10)

GPIO4(10)

GPIO5(10)

GPIO6(10)

SOUT_GPIO8(10)

SIN_GPIO9(10)

SCLK(10)

GPIO11(10)

GPIO12(10)

GPIO13(10)

ALT#_GPIO17(10)

R57 1K_4R57 1K_4

T24T24

Reserved for ICT

VREFG

DPLL_PVDD

C96

C96

0.1u_4

0.1u_4

PCIE_PVDD

MPVDD

XTALI

XTALO

R25

R25

1M_4

1M_4

DPLL_VDDC

D-(10)

D+(10)

T23T23

T22T22

GFX_CTF

CLKREQ#

JMODE

T25T25

T26T26

T27T27

T28T28

3

U5B

U5B

AM12

VIP_0

AL12

VIP_1

AJ12

VIP_2

AH12

VIP_3

AM10

VIP_4

AL10

VIP_5

AJ10

VIP_6

AH10

VIP_7

AM9

VHAD_0

AL9

VHAD_1

AJ9

VPHCTL

AL7

VPCLK0

AK7

VIPCLK

AM7

PSYNC

AJ7

DVALID

AK6

SDA

AM6

SCL

AN8

DVPCNTL__MVP_0

AP8

DVPCNTL__MVP_1

AG1

DVPCNTL_0

AH3

DVPCNTL_1

AH2

DVPCNTL_2

AH1

DVPCLK

AJ3

DVPDATA_0

AJ2

DVPDATA_1

AJ1

DVPDATA_2

AK2

DVPDATA_3

AK1

DVPDATA_4

AL3

DVPDATA_5

AL2

DVPDATA_6

AL1

DVPDATA_7

AM3

DVPDATA_8

AM2

DVPDATA_9

AN2

DVPDATA_10

AP3

DVPDATA_11

AR3

DVPDATA_12

AN4

DVPDATA_13

AR4

DVPDATA_14

AP4

DVPDATA_15

AN5

DVPDATA_16

AR5

DVPDATA_17

AP5

DVPDATA_18

AP6

DVPDATA_19

AR6

DVPDATA_20

AN7

DVPDATA_21

AP7

DVPDATA_22

AR7

DVPDATA_23

AG2

GPIO_0

AF2

GPIO_1

AF1

GPIO_2

AE3

GPIO_3

AE2

GPIO_4

AE1

GPIO_5

AD3

GPIO_6

AD2

GPIO_7_BLON

AD1

GPIO_8_ROMSO

AD5

GPIO_9_ROMSI

AD4

GPIO_10_ROMSCK

AC3

GPIO_11

AC2

GPIO_12

AC1

GPIO_13

AB3

GPIO_14_HPD2

AB2

GPIO_15_PWRCNTL_0

AB1

GPIO_16_SSIN

AF5

GPIO_17_THERMAL_INT

AF4

GPIO_18_HPD3

AG4

GPIO_19_CTF

AG3

GPIO_20_PWRCNTL_1

AD9

GPIO_21_BBEN

AD8

GPIO_22_ROMCSB

AD7

GPIO_23_CLKREQB

AB4

GPIO_24_JMODE

AB6

GPIO_25_TDI

AB7

GPIO_26_TCK

AB9

GPIO_27_TMS

AA9

GPIO_28_TDO

AF8

GEN_A

AF7

GEN_B

AG5

GEN_C

AP9

GEN_D_HPD4

AR9

GEN_E

AP13

GEN_F

AR13

GEN_G

AD12

VREFG

AR20

DPLL_PVDD

AP20

DPLL_PVSS

AM35

PCIE_PVDD

A14

MPVDD

B15

MPVSS

AR33

XTALIN

AP33

XTALOUT

AG19

DPLL_VDDC

AG21

TS_FDO

AK4

DMINUS

AM4

DPLUS

M86-M

M86-M

VIP / I2C

VIP / I2C

MULTI_GFX

MULTI_GFX

EXTERNAL

EXTERNAL

TMDS

TMDS

GENERAL

GENERAL

PURPOSE

PURPOSE

I/O

I/O

PLL

PLL

CLOCKS

CLOCKS

THERMAL

THERMAL

PART 2 OF 7

PART 2 OF 7

INTEGRATED

INTEGRATED

TMDS/DP

TMDS/DP

DAC1

DAC1

DAC2

DAC2

DDC

DDC

DP AUX

DP AUX

DDC3DATA_DP3_AUXN

DDC3CLK_DP3_AUXP

DDC4DATA_DP4_AUXN

DDC4CLK_DP4_AUXP

TXCAM_DPA0P

TXCAP_DPA0N

TX0M_DPA1P

TX0P_DPA1N

TX1M_DPA2P

TX1P_DPA2N

TX2M_DPA3P

TX2P_DPA3N

TXCBM_DPB0P

TXCBP_DPB0N

TX3M_DPB1P

TX3P_DPB1N

TX4M_DPB2P

TX4P_DPB2N

TX5M_DPB3P

TX5P_DPB3N

DPA_PVDD

DPA_PVSS

DPB_PVDD

DPB_PVSS

DPB_VDDR_1

DPB_VDDR_2

DPA_VDDR_3

DPA_VDDR_4

DPB_VSSR_1

DPB_VSSR_2

DPB_VSSR_3

DPB_VSSR_4

DPB_VSSR_6

DPA_VSSR_5

DPA_VSSR_7

DPA_VSSR_8

DPA_VSSR_9

DPA_VSSR_10

DP_CALR

NC_TPVDDC

NC_TPVSSC

HPD1

HSYNC

VSYNC

RSET

AVDD

AVSSQ

VDD1DI

VSS1DI

COMP

V2SYNC

H2SYNC

A2VDD

A2VDDQ

A2VSSQ

VDD2DI

VSS2DI

R2SET

DDC1DATA

DDC1CLK

DDC2DATA

DDC2CLK

M7X

R70 *M7X@180_4R70 *M7X@180_4

AN9

AN10

R65 *M7X@180_4R65 *M7X@180_4

AR10

AP10

R67 *M7X@180_4R67 *M7X@180_4

AR11

AP11

R71 *M7X@180_4R71 *M7X@180_4

AR12

AP12

AR14

AP14

AR15

AP15

AR16

AP16

AR17

AP17

TPVDD

AM14

AL14

AH17

AG17

AN19

AN20

AP19

AR19

AN18

AP18

AR18

AN16

AN17

AN15

AN11

AN12

AN13

AN14

R80 150/F_4R80 150/F_4

AG15

AH18

AG18

R59 0_4R59 0_4

AG6

AR31

R

AP31

RB

AR30

G

AP30

GB

AR29

B

AP29

BB

R99 0_4R99 0_4

AN29

R102 0_4R102 0_4

AN30

R94 499/F_4R94 499/F_4

AN31

AVDD

AR32

AP32

VDD1DI

AR28

AP28

AM19

R2

AL19

R2B

AM18

G2

AL18

G2B

AM17

B2

AL17

B2B

EXT_TV_C/R

AK19

C

EXT_TV_Y/G

AK18

Y

EXT_TV_COMP

AK17

V2SYNC

AL15

H2SYNC

AM15

A2VDD

AM21

A2VDDQ

AL21

AK21

VDD1DI

AH22

AG22

R88 715/F_4R88 715/F_4

AJ21

DDC1DAT

AM29

DDC1CLK

AL29

AJ15

AH15

AJ5

AJ4

DDC4DAT

AH14

DDC4CLK

AG14

3.3V TO 5V LEVEL SHIFT LOGIC REQUIRED

DDC1,DDC2 DDC3 USED ON M8x

DDC1,DDC2,DDC3 USED ON M7x (Level shift)

DPB_VDDR

DPA_VDDR

EXT_VGA_RED

EXT_VGA_GRN

EXT_VGA_BLU

EXT_LVDS_PNLDAT (2)

EXT_LVDS_PNLCLK (2)

DDC3DAT (2)

DDC3CLK (2)

C116

C116

1u_4

1u_4

C143

C143

1u_4

1u_4

C129

C129

1u_4

1u_4

C186

C186

1u_4

1u_4

V2SYNC (10)

H2SYNC (10)

T17T17

T16T16

DDC3,DDC4 ARE 5V TOLERANT ON M8x

2

C107

C107

0.1u_4

0.1u_4

C140

C140

0.1u_4

0.1u_4

C133

C133

0.1u_4

0.1u_4

DVI_HPD (2)

EXT_VGA_RED (2)

EXT_VGA_GRN (2)

EXT_VGA_BLU

EXT_HSYNC (2,10)

EXT_VSYNC (2,10)

C156

C156

0.1u_4

0.1u_4

EXT_TV_C/R (2)

EXT_TV_Y/G (2)

EXT_TV_COMP (2)

C161

C161

C28

C28

1u_4

1u_4

0.1u_4

0.1u_4

HDMICLK- (2)

HDMICLK+ (2)

HDMITX0N (2)

HDMITX0P (2)

HDMITX1N (2)

HDMITX1P (2)

HDMITX2N (2)

HDMITX2P (2)

C101

C101

10u_6

10u_6

C142

C142

10u_6

10u_6

C21

C21

10u_6

10u_6

+1.8V(104mA)

C34

C34

10u_6

10u_6

10u_6

10u_6

120 ohm/300mA

BLM15BD121SN1L17 BLM15BD121SN1L17

*M7X@BLM15BD121SN1L23 *M7X@BLM15BD121SN1L23

BLM15BD121SN1L22 BLM15BD121SN1L22

INSTALL DPA/B_VDDR TO +1.8V(100mA) FOR M7x

INSTALL DPA/B_VDDR TO +1.1V(200mA) FOR M8x

BLM15BD121SN1L21 BLM15BD121SN1L21

*M7X@BLM15BD121SN1L3 *M7X@BLM15BD121SN1L3

EXT_VGA_RED

EXT_VGA_GRN

EXT_VGA_BLU

EXT_TV_C/R

(2)

BLM15BD121SN1L9 BLM15BD121SN1L9

+1.8V(48mA)

BLM15BD121SN1L6 BLM15BD121SN1L6

C29

C29

DDC1DAT

DDC1CLK

EXT_TV_Y/G

EXT_TV_COMP

AVDD

C41

C41

+1.8V

10u_6

10u_6

A2VDD

+1.8V

DDC1DAT

R126 0_4R126 0_4

DDC1CLK

R135 0_4R135 0_4

+3V_D

R128

R128

R132

R132

*10K_4

*10K_4

2

*10K_4

*10K_4

1

Q5

Q5

*RHU002N06

*RHU002N06

+3V_D

2

1

Q6

Q6

*RHU002N06

*RHU002N06

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GFX(LVDS, DVI, CRT, TV)

GFX(LVDS, DVI, CRT, TV)

GFX(LVDS, DVI, CRT, TV)

Date: Sheet of

Date: Sheet of

Date: Sheet of

+1.8V(40mA)

+1.8V

+1.1V(200mA)

+1.1V

+1.1V(200mA)

+1.1V

+1.8V

R97 150/F_4R97 150/F_4

150/F_4

150/F_4

R96

R96

R92 150/F_4R92 150/F_4

R87 150/F_4R87 150/F_4

R84 150/F_4R84 150/F_4

R83 150/F_4R83 150/F_4

R131

R131

*2K_4

*2K_4

10u_6

10u_6

C37

C37

*47u/6.3V_1210

*47u/6.3V_1210

C31

C31

BLM15BD121SN1L10 BLM15BD121SN1L10

+3.3V(100mA)

BLM15BD121SN1L8 BLM15BD121SN1L8

EXT_CRT_DDCDAT (2)

EXT_CRT_DDCCLK (2)

C38

C38

C42

C42

0.1u_4

0.1u_4

1u_4

1u_4

C33

C33

C32

C32

0.1u_4

0.1u_4

1u_4

1u_4

EXT_CRT_DDCDAT

EXT_CRT_DDCCLK

+5V

R130

R130

*2K_4

*2K_4

3

3

PROJECT :BD3

PROJECT :BD3

Quanta Computer Inc.

Quanta Computer Inc.

1

+1.8V(96mA)

+1.8V

+3V_D

1A

1A

1A

3Thursday, November 15, 2007

3Thursday, November 15, 2007

3Thursday, November 15, 2007

41

41

41

Page 5

5

VMA_DQ[63..0](8)

D D

C C

B B

VMA_DM[7..0](8)

VMA_RDQS[7..0](8)

VMA_WDQS[7..0](8)

VMA_MA[12..0](8)

VMA_BA0(8)

VMA_BA1(8)

VMA_DQ[63..0]

VMA_DM[7..0]

VMA_RDQS[7..0]

VMA_WDQS[7..0]

VMA_MA[12..0]

VMA_BA0

VMA_BA1

+1.8V

R101

R101

100/F_4

100/F_4

R104

R104

100/F_4

100/F_4

4

MVREFDA

C223

C223

0.1u_4

0.1u_4

VMA_DQ0

VMA_DQ1

VMA_DQ2

VMA_DQ3

VMA_DQ4

VMA_DQ5

VMA_DQ6

VMA_DQ7

VMA_DQ8

VMA_DQ9

VMA_DQ10

VMA_DQ11

VMA_DQ12

VMA_DQ13

VMA_DQ14

VMA_DQ15

VMA_DQ16

VMA_DQ17

VMA_DQ18

VMA_DQ19

VMA_DQ20

VMA_DQ21

VMA_DQ22

VMA_DQ23

VMA_DQ24

VMA_DQ25

VMA_DQ26

VMA_DQ27

VMA_DQ28

VMA_DQ29

VMA_DQ30

VMA_DQ31

VMA_DQ32

VMA_DQ33

VMA_DQ34

VMA_DQ35

VMA_DQ36

VMA_DQ37

VMA_DQ38

VMA_DQ39

VMA_DQ40

VMA_DQ41

VMA_DQ42

VMA_DQ43

VMA_DQ44

VMA_DQ45

VMA_DQ46

VMA_DQ47

VMA_DQ48

VMA_DQ49

VMA_DQ50

VMA_DQ51

VMA_DQ52

VMA_DQ53

VMA_DQ54

VMA_DQ55

VMA_DQ56

VMA_DQ57

VMA_DQ58

VMA_DQ59

VMA_DQ60

VMA_DQ61

VMA_DQ62

VMA_DQ63

P27

P28

P31

P32

M27

K29

K31

K32

M33

M34

L34

L35

J33

J34

H33

H34

K27

J29

J30

J31

F29

F32

D30

D32

G33

G34

G35

F34

D34

C34

C35

B34

C24

B24

B23

A23

C21

B21

C20

B20

J22

H22

F22

D21

J19

G19

F19

D19

C19

B19

A19

B18

C16

B16

C15

A15

H18

F18

E18

D18

J17

G15

E15

D15

N35

N34

AM34

U5C

U5C

DQA_0

DQA_1

DQA_2

DQA_3

DQA_4

DQA_5

DQA_6

DQA_7

DQA_8

DQA_9

DQA_10

DQA_11

DQA_12

DQA_13

DQA_14

DQA_15

DQA_16

DQA_17

DQA_18

DQA_19

DQA_20

DQA_21

DQA_22

DQA_23

DQA_24

DQA_25

DQA_26

DQA_27

DQA_28

DQA_29

DQA_30

DQA_31

DQA_32

DQA_33

DQA_34

DQA_35

DQA_36

DQA_37

DQA_38

DQA_39

DQA_40

DQA_41

DQA_42

DQA_43

DQA_44

DQA_45

DQA_46

DQA_47

DQA_48

DQA_49

DQA_50

DQA_51

DQA_52

DQA_53

DQA_54

DQA_55

DQA_56

DQA_57

DQA_58

DQA_59

DQA_60

DQA_61

DQA_62

DQA_63

MVREFDA

MVREFSA

NC_1

3

Part 3 of 7

Part 3 of 7

C27

MAA_0

B28

MAA_1

B27

MAA_2

G26

MAA_3

F27

MAA_4

E27

MAA_5

D27

MAA_6

J27

MAA_7

E29

MAA_8

C30

MAA_9

E26

MAA_10

A27

MAA_11

G27

MAA_A12

D26

MAA_BA2

C28

MAA_BA0

B29

MAA_BA1

M29

DQMAb_0

K33

DQMAb_1

G30

DQMAb_2

E33

DQMAb_3

C22

DQMAb_4

H21

DQMAb_5

C17

DQMAb_6

G17

DQMAb_7

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

QSA_0B

QSA_1B

QSA_2B

QSA_3B

QSA_4B

QSA_5B

QSA_6B

QSA_7B

ODTA0

ODTA1

CLKA0

CLKA1

CLKA0b

CLKA1b

RASA0b

RASA1b

CASA0b

CASA1b

CSA0b_0

CSA0b_1

CSA1b_0

CSA1b_1

CKEA0

CKEA1

WEA0b

WEA1b

M30

K34

G31

E34

B22

F21

B17

D17

M31

K35

G32

E35

A22

E21

A17

E17

C31

C25

A33

A26

B33

B26

A31

D24

C32

H26

A30

B30

G24

H24

B31

F24

C29

D22

MEMORY INTERFACE A

MEMORY INTERFACE A

write strobe read strobe

write strobe read strobe

VMA_MA0

VMA_MA1

VMA_MA2

VMA_MA3

VMA_MA4

VMA_MA5

VMA_MA6

VMA_MA7

VMA_MA8

VMA_MA9

VMA_MA10

VMA_MA11

VMA_MA12

VMA_BA2

VMA_BA0

VMA_BA1

VMA_DM0

VMA_DM1

VMA_DM2

VMA_DM3

VMA_DM4

VMA_DM5

VMA_DM6

VMA_DM7

VMA_RDQS0

VMA_RDQS1

VMA_RDQS2

VMA_RDQS3

VMA_RDQS4

VMA_RDQS5

VMA_RDQS6

VMA_RDQS7

VMA_WDQS0

VMA_WDQS1

VMA_WDQS2

VMA_WDQS3

VMA_WDQS4

VMA_WDQS5

VMA_WDQS6

VMA_WDQS7

VMA_ODT0

VMA_ODT1

VMA_CLK0

VMA_CLK1

VMA_CLK0#

VMA_CLK1#

RASA0#

RASA1#

CASA0#

CASA1#

CSA0_0#

CSA0_1#

CSA1_0#

CSA1_1#

CKEA0

CKEA1

WEA0#

WEA1#

T20T20

QSA[7..0]

QSA#[7..0]

VMA_ODT0

VMA_ODT1 (8)

VMA_CLK0 (8)

VMA_CLK1 (8)

VMA_CLK0# (8)

VMA_CLK1# (8)

RASA0#

RASA1# (8)

CASA0# (8)

CASA1# (8)

CSA0_0# (8)

T21T21

CSA1_0#

T19T19

CKEA0 (8)

CKEA1 (8)

WEA0# (8)

WEA1# (8)

2

(8)

(8)

(8)

1

+1.8V

R116

R116

100/F_4

A A

5

100/F_4

R105

R105

100/F_4

100/F_4

MVREFSA

C241

C241

0.1u_4

0.1u_4

4

M86-M

M86-M

DIVIDER RESISTORS DDR2 DDR3

MVREF TO 1.8V

MVREF TO GND

100R

100R

MVREF Voltage 0.9V

0.5*VDDQ

3

40.2R

100R

1.28V

0.713*VDDQ

PROJECT :BD3

Document Number Rev

Size

Size Document Number Rev

Size Document Number Rev

GFX(MEM I/F 1/2)

GFX(MEM I/F 1/2)

GFX(MEM I/F 1/2)

Date: Sheet

Date: Sheet of

2

Date: Sheet of

PROJECT :BD3

Quanta Computer Inc.

Quanta Computer Inc.

of

513Monday, November 12, 2007

513Monday, November 12, 2007

513Monday, November 12, 2007

1

1A

1A

1A

Page 6

5

D D

VMB_DQ[63..0](9)

VMB_DM[7..0](9)

VMB_RDQS[7..0](9)

VMB_WDQS[7..0](9)

VMB_MA[12..0](9)

VMB_BA0(9)

VMB_BA1(9)

C C

B B

VMB_DQ[63..0]

VMB_DM[7..0]

VMB_RDQS[7..0]

VMB_WDQS[7..0]

VMB_MA[12..0]

VMB_BA0

VMB_BA1

+1.8V

+1.8V

R76

R76

100/F_4

100/F_4

R82

R82

100/F_4

100/F_4

MVREFDB

C113

C113

0.1u_4

0.1u_4

4

VMB_DQ0

VMB_DQ1

VMB_DQ2

VMB_DQ3

VMB_DQ4

VMB_DQ5

VMB_DQ6

VMB_DQ7

VMB_DQ8

VMB_DQ9

VMB_DQ10

VMB_DQ11

VMB_DQ12

VMB_DQ13

VMB_DQ14

VMB_DQ15

VMB_DQ16

VMB_DQ17

VMB_DQ18

VMB_DQ19

VMB_DQ20

VMB_DQ21

VMB_DQ22

VMB_DQ23

VMB_DQ24

VMB_DQ25

VMB_DQ26

VMB_DQ27

VMB_DQ28

VMB_DQ29

VMB_DQ30

VMB_DQ31

VMB_DQ32

VMB_DQ33

VMB_DQ34

VMB_DQ35

VMB_DQ36

VMB_DQ37

VMB_DQ38

VMB_DQ39

VMB_DQ40

VMB_DQ41

VMB_DQ42

VMB_DQ43

VMB_DQ44

VMB_DQ45

VMB_DQ46

VMB_DQ47

VMB_DQ48

VMB_DQ49

VMB_DQ50

VMB_DQ51

VMB_DQ52

VMB_DQ53

VMB_DQ54

VMB_DQ55

VMB_DQ56

VMB_DQ57

VMB_DQ58

VMB_DQ59

VMB_DQ60

VMB_DQ61

VMB_DQ62

VMB_DQ63

R91 1K_4R91 1K_4

R69 4.7K_4R69 4.7K_4

R62 4.7K_4R62 4.7K_4

R58 240/F_4R58 240/F_4

T18T18

H15

G14

E14

D14

H12

G12

F12

D10

B13

C12

B12

B11

H10

F10

AA2

AA1

B14

A13

AM30

AA8

AA7

AA5

AH19

C9

B9

A9

B8

J10

D9

G7

G6

F6

D6

C8

C7

B7

A7

B5

A5

C4

B4

M3

M2

N2

N1

R3

R2

T3

T2

M8

M7

P5

P4

R9

R8

R6

U4

U3

U2

U1

V2

Y3

Y2

U9

U7

U6

V4

W9

W7

W6

W4

U5G

U5G

DQB_0

DQB_1

DQB_2

DQB_3

DQB_4

DQB_5

DQB_6

DQB_7

DQB_8

DQB_9

DQB_10

DQB_11

DQB_12

DQB_13

DQB_14

DQB_15

DQB_16

DQB_17

DQB_18

DQB_19

DQB_20

DQB_21

DQB_22

DQB_23

DQB_24

DQB_25

DQB_26

DQB_27

DQB_28

DQB_29

DQB_30

DQB_31

DQB_32

DQB_33

DQB_34

DQB_35

DQB_36

DQB_37

DQB_38

DQB_39

DQB_40

DQB_41

DQB_42

DQB_43

DQB_44

DQB_45

DQB_46

DQB_47

DQB_48

DQB_49

DQB_50

DQB_51

DQB_52

DQB_53

DQB_54

DQB_55

DQB_56

DQB_57

DQB_58

DQB_59

DQB_60

DQB_61

DQB_62

DQB_63

MVREFDB

MVREFSB

TESTEN

TEST_MCLK

TEST_YCLK

MEMTEST

PLLTEST

M86-M

M86-M

3

Part 4 of 7

Part 4 of 7

H2

MAB_0

H3

MAB_1

J3

MAB_2

J5

MAB_3

J4

MAB_4

J6

MAB_5

G5

MAB_6

J9

MAB_7

F3

MAB_8

F4

MAB_9

J1

MAB_10

J2

MAB_11

J7

MAB_A12

F1

MAB_BA2

G2

MAB_BA0

G3

MAB_BA1

D12

DQMBb_0

C10

DQMBb_1

E7

DQMBb_2

C6

DQMBb_3

P3

DQMBb_4

R4

DQMBb_5

W3

DQMBb_6

V8

DQMBb_7

MEMORY INTERFACE B

MEMORY INTERFACE B

write strobe read strobe

write strobe read strobe

DRAM_RST

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

QSB_0B

QSB_1B

QSB_2B

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

ODTB0

ODTB1

CLKB0

CLKB1

CLKB0b

CLKB1b

RASB0b

RASB1b

CASB0b

CASB1b

CSB0b_0

CSB0b_1

CSB1b_0

CSB1b_1

CKEB0

CKEB1

WEB0b

WEB1b

J14

B10

F9

B6

P2

P8

W2

V6

H14

A10

E9

A6

P1

P7

W1

V5

D2

K5

A3

K1

B3

K2

D3

K7

C1

K4

E1

E2

L3

M4

E3

K8

F2

M6

AA4

VMB_MA0

VMB_MA1

VMB_MA2

VMB_MA3

VMB_MA4

VMB_MA5

VMB_MA6

VMB_MA7

VMB_MA8

VMB_MA9

VMB_MA10

VMB_MA11

VMB_MA12

VMB_BA2

VMB_BA0

VMB_BA1

VMB_DM0

VMB_DM1

VMB_DM2

VMB_DM3

VMB_DM4

VMB_DM5

VMB_DM6

VMB_DM7

VMB_RDQS0

VMB_RDQS1

VMB_RDQS2

VMB_RDQS3

VMB_RDQS4

VMB_RDQS5

VMB_RDQS6

VMB_RDQS7

VMB_WDQS0

VMB_WDQS1

VMB_WDQS2

VMB_WDQS3

VMB_WDQS4

VMB_WDQS5

VMB_WDQS6

VMB_WDQS7

VMB_ODT0

VMB_ODT1

VMB_CLK0

VMB_CLK1

VMB_CLK0#

VMB_CLK1#

RASB0#

RASB1#

CASB0#

CASB1#

CSB0_0#

CSB0_1#

CSB1_0#

CSB1_1#

CKEB0

CKEB1

WEB0#

WEB1#

MEM_RST#

T12T12

QSB[7..0]

QSB#[7..0]

VMB_ODT0 (9)

VMB_ODT1 (9)

VMB_CLK0 (9)

VMB_CLK1 (9)

VMB_CLK0#

VMB_CLK1# (9)

RASB0# (9)

RASB1# (9)

CASB0# (9)

CASB1# (9)

CSB0_0# (9)

T15T15

CSB1_0# (9)

T14T14

CKEB0 (9)

CKEB1 (9)

WEB0# (9)

WEB1# (9)

R45 4.7K_4R45 4.7K_4

+1.8V

2

(9)

1

R74

R74

100/F_4

A A

5

100/F_4

R77

R77

100/F_4

100/F_4

MVREFSB

C99

C99

0.1u_4

0.1u_4

DIVIDER RESISTORS DDR2 DDR3

MVREF TO 1.8V

MVREF TO GND

MVREF Voltage 0.9V

0.5*VDDQ

4

100R

100R

40.2R

100R

1.28V

0.713*VDDQ

3

PROJECT :BD3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GFX(MEM I/F 2/2)

GFX(MEM I/F 2/2)

GFX(MEM I/F 2/2)

Date: Sheet

Date: Sheet of

2

Date: Sheet of

PROJECT :BD3

Quanta Computer Inc.

Quanta Computer Inc.

of

61

61

61

1

1A

1A

1A

3Thursday, November 08, 2007

3Thursday, November 08, 2007

3Thursday, November 08, 2007

Page 7

5

+1.8V

D D

120ohm/300mA

+1.8V

C C

+3V_D

Modify for AMD request 11/5

+1.8V

+1.8V

120ohm/300mA

120ohm/300mA

120ohm/300mA

BLM15BD121SN1L29 BLM15BD121SN1L29

BLM15BD121SN1L31 BLM15BD121SN1L31

BLM15BD121SN1L15 BLM15BD121SN1L15

+1.8V

+1.8V

B B

+1.8V

C122

C122

10u_6

10u_6

C84

C84

C112

C112

C188

C114

C114

0.1u_4

0.1u_4

C83

C83

10u_6

10u_6

C264

C264

*10u_6

*10u_6

C108

C108

1u_4

1u_4

10u_6

10u_6

10u_6

10u_6

VDD_CT

C166

C166

VDDR3

VDDR4

VDDR5

VDDRHA1

C180

C180

0.1u_4

0.1u_4

VDDRHA2

C189

C189

0.1u_4

0.1u_4

VDDRHB1

C79

C79

0.1u_4

0.1u_4

C188

1u_4

1u_4

C155

C155

1u_4

1u_4

C124

C124

0.1u_4

0.1u_4

+1.8V(76mA)

+3.3V(100mA)

C90

C90

1u_4

1u_4

C82

C82

1u_4

1u_4

VDD_CORE

C81

C81

0.1u_4

0.1u_4

C89

C89

0.1u_4

0.1u_4

C265

C265

0.1u_4

0.1u_4

10u_6

10u_6

C92

C92

0.1u_4

0.1u_4

BLM15BD121SN1L18 BLM15BD121SN1L18

BLM15BD121SN1L24 BLM15BD121SN1L24

BLM15BD121SN1L36 BLM15BD121SN1L36

BLM15BD121SN1L37 BLM15BD121SN1L37

C173

C173

1u_4

1u_4

C191

C191

1u_4

1u_4

C14

C14

1u_4

1u_4

C174

C174

1u_4

1u_4

C149

C149

1u_4

1u_4

C97

C97

1u_4

1u_4

C125

C125

1u_4

1u_4

C184

C184

0.1u_4

0.1u_4

C94

C94

0.1u_4

0.1u_4

C115

C115

0.1u_4

0.1u_4

C135

C135

1u_4

1u_4

C86

C86

1u_4

1u_4

C87

C87

0.1u_4

0.1u_4

C120

C120

1u_4

1u_4

VDDRHA1

VDDRHA2

VDDRHB1

VDDRHB2

C126

C126

0.1u_4

0.1u_4

Fine-tune Power-on sequence

120ohm/300mA

BLM15BD121SN1L16 BLM15BD121SN1L16

+1.8V

A A

C77

C77

1u_4

1u_4

VDDRHB2

C78

C78

0.1u_4

0.1u_4

R98 2K_4R98 2K_4

AA11

AB11

AD10

AF10

AE14

AE15

AF12

AE17

AA13

4

U5D

U5D

D1

VDDR1_1

A8

VDDR1_2

A12

VDDR1_3

A16

VDDR1_4

A20

VDDR1_5

A24

VDDR1_6

A28

VDDR1_7

B1

VDDR1_8

H1

VDDR1_9

H35

VDDR1_10

L18

VDDR1_11

L19

VDDR1_12

L21

VDDR1_13

L22

VDDR1_14

M10

VDDR1_15

M35

VDDR1_16

P10

VDDR1_17

T1

VDDR1_18

Y1

VDDR1_19

B35

VDDR1_20

M1

VDDR1_21

D35

VDDR1_22

K10

VDDR1_23

K12

VDDR1_24

K24

VDDR1_25

K26

VDDR1_26

L14

VDDR1_27

L15

VDDR1_28

L17

VDDR1_29

VDD_CT_1

VDD_CT_2

VDD_CT_3

VDD_CT_4

R11

VDD_CT_5

R25

VDD_CT_6

U11

VDD_CT_7

U25

VDD_CT_8

VDDR3_1

VDDR3_2

VDDR3_3

VDDR3_4

AP2

VDDR4_1

AR2

VDDR4_2

AN1

VDDR5_1

AP1

VDDR5_2

A25

VDDRHA_1

A32

VDDRHA_2

B25

VSSRHA_1

B32

VSSRHA_2

B2

VDDRHB_1

L1

VDDRHB_2

C2

VSSRHB_1

L2

VSSRHB_2

W13

BBN_1

BBN_2

U13

BBP_1

V13

BBP_2

M86-M

M86-M

C195

C195

1u_4

1u_4

+3V +3V

2

PART 5 OF 7

PART 5 OF 7

Memory I/O

Memory I/O

P

P

O

O

I/O Internal

I/O Internal

W

W

E

E

R

R

Memory I/O

Clock

Memory I/O

Clock

Back

Bias

Back

Bias

R24

R24

4.7K_4

4.7K_4

Q2

Q2

PDTC143TT

PDTC143TT

1 3

PCIE_VDDC_10

PCIE_VDDC_11

PCI-Express

PCI-Express

PCIE_VDDC_12

2

PCIE_VDDR_1

PCIE_VDDR_2

PCIE_VDDR_3

PCIE_VDDR_4

PCIE_VDDR_5

PCIE_VDDR_6

PCIE_VDDR_7

PCIE_VDDR_8

PCIE_VDDC_1

PCIE_VDDC_2

PCIE_VDDC_3

PCIE_VDDC_4

PCIE_VDDC_5

PCIE_VDDC_6

PCIE_VDDC_7

PCIE_VDDC_8

PCIE_VDDC_9

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

Core

Core

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDDC_24

VDDC_25

VDDC_26

VDDC_27

VDDC_28

VDDC_29

VDDC_30

VDDC_31

VDDC_32

VDDC_33

VDDC_34

VDDC_35

VDDC_36

VDDC_37

VDDC_38

VDDC_39

VDDC_40

VDDC_41

VDDC_42

VDDC_43

VDDC_44

VDDCI_1

VDDCI_2

VDDCI_3

VDDCI_4

1

AO3413Q1AO3413

Q1

3

C194

C194

10u_6

10u_6

C187

C187

1u_4

1u_4

AR34

AL33

AM33

AN33

AN34

AN35

AP34

AP35

R26

U26

V25

V26

W25

W26

AA25

AD26

AF26

AA26

AB25

AB26

N13

N15

N18

N21

N23

P14

P17

P19

P22

V18

V21

V23

W14

W17

W19

W22

AA15

AA18

AA21

AA23

AB14

AB17

AB19

AB22

AC13

AC15

AC18

AC21

AC23

AE18

AE22

AE19

AE21

R13

R15

R18

R21

R23

U14

U17

U19

U22

V15

W11

M12

M24

P11

P25

10u_6

10u_6

+3.3V(0.5A)

+3V_D+1.8V

C190

C190

0.1u_4

0.1u_4

C196

C196

0.1u_4

0.1u_4

C171

C171

0.1u_4

0.1u_4

C144

C144

C152

C152

1u_4

1u_4

C147

C147

1u_4

1u_4

C127

C127

1u_4

1u_4

C154

C154

0.1u_4

0.1u_4

C93

C93

0.1u_4

0.1u_4

3

PCIE_VDDR

C204

C204

1u_4

1u_4

C170

C170

0.1u_4

0.1u_4

C121

C121

10u_6

10u_6

C110

C110

1u_4

1u_4

C146

C146

1u_4

1u_4

C128

C128

1u_4

1u_4

C109

C109

0.1u_4

0.1u_4

VDDCI

C177

C177

1u_4

1u_4

+1.8V(472mA)

C201

C201

10u_6

10u_6

C169

C169

1u_4

1u_4

C103

C103

10u_6

10u_6

C157

C157

1u_4

1u_4

C136

C136

1u_4

1u_4

C111

C111

1u_4

1u_4

C159

C159

0.1u_4

0.1u_4

C176

C176

1u_4

1u_4

PCIE_VDDC

C172

C172

C168

C168

1u_4

1u_4

1u_4

1u_4

C102

C102

10u_6

10u_6

C118

C118

1u_4

1u_4

C137

C137

1u_4

1u_4

C153

C153

C138

C138

0.1u_4

0.1u_4

0.1u_4

0.1u_4

33ohm/3000mA

L27 BLM18PG330SN1DL27 BLM18PG330SN1D

C104

C104

10u_6

10u_6

33ohm/3000mA

L34 BLM18PG330SN1DL34 BLM18PG330SN1D

+1.1V(1.36A)

33ohm/3000mA

L19 BLM18PG330SN1DL19 BLM18PG330SN1D

C167

C167

10u_6

10u_6

VDDC+VDDCI

0.95~1.1V(24A)

C119

C119

1u_4

1u_4

C145

C145

1u_4

1u_4

C158

C158

0.1u_4

0.1u_4

VDD_CORE

VDD_CORE

+1.8V

+1.1V

2

U5E

AA29

AA32

AB29

AB32

AB34

AB35

AC33

AD29

AD32

AF29

AF32

AD33

AF34

AF35

AG27

AG29

AG32

AG33

AJ29

AJ32

AH33

AL34

AL35

AK32

U5E

P33

P34

P35

R27

R28

R29

R32

R33

U29

U32

V29

V32

T33

V34

V35

W29

W32

W33

Y33

A2

A34

C3

C5

A4

C18

A21

C23

C11

C13

C14

A18

A11

C26

C33

F35

R7

G10

F15

H17

G21

D29

A29

G1

F14

J15

E19

E22

E24

D7

G9

F26

G29

D33

M5

G4

E10

E12

F17

G18

G22

F30

J35

J18

H19

J21

F7

J12

J24

J26

K30

J32

F33

K6

K9

K14

K15

K17

K18

K19

K21

K22

M28

K3

L33

M86-M

M86-M

PCIE_VSS_1

PCIE_VSS_2

PCIE_VSS_3

PCIE_VSS_4

PCIE_VSS_5

PCIE_VSS_6

PCIE_VSS_7

PCIE_VSS_8

PCIE_VSS_9

PCIE_VSS_10

PCIE_VSS_11

PCIE_VSS_12

PCIE_VSS_13

PCIE_VSS_14

PCIE_VSS_15

PCIE_VSS_16

PCIE_VSS_17

PCIE_VSS_18

PCIE_VSS_19

PCIE_VSS_20

PCIE_VSS_21

PCIE_VSS_22

PCIE_VSS_23

PCIE_VSS_24

PCIE_VSS_25

PCIE_VSS_26

PCIE_VSS_27

PCIE_VSS_28

PCIE_VSS_29

PCIE_VSS_30

PCIE_VSS_31

PCIE_VSS_32

PCIE_VSS_33

PCIE_VSS_34

PCIE_VSS_35

PCIE_VSS_36

PCIE_VSS_37

PCIE_VSS_38

PCIE_VSS_39

PCIE_VSS_40

PCIE_VSS_41

PCIE_VSS_42

PCIE_VSS_43

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

Part 6 of 7

Part 6 of 7

CORE GND

CORE GND

1

P6

VSS_66

M9

VSS_67

M26

VSS_68

K28

VSS_69

M32

VSS_70

N14

VSS_71

N17

VSS_72

N19

VSS_73

N22

VSS_74

N33

VSS_75

N3

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

MECH_1

MECH_2

MECH_3

R5

U8

P13

P15

P18

P21

P23

P26

P29

P30

R1

U5

P9

R10

R14

R17

R19

R22

V3

AK9

U10

U15

U18

U21

U23

V7

W8

V10

V14

V17

V19

V22

V1

AK12

V9

W10

W15

W18

W21

W23

AA6

AA10

AA14

AA17

AA19

AA22

AB8

AB10

AB13

AB15

AB18

AB21

AB23

AC14

AC17

AC19

AC22

AF9

AD6

AB5

AD24

W5

AF6

AF14

AF21

AF22

AK10

AF17

AF18

AF19

AA3

AG12

AJ14

AH21

D4

AF15

AG10

AN6

AK15

AJ17

AJ18

AJ19

AF24

AN32

AK3

AN3

AR8

AM1

AK30

V11

A35

AR1

AR35

PCI-Express GND

PCI-Express GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GFX(GPIO, STRAP)

GFX(GPIO, STRAP)

GFX(GPIO, STRAP)

Date: Sheet of

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :BD3

PROJECT :BD3

Quanta Computer Inc.

Quanta Computer Inc.

of

of

71

71

71

1

1A

1A

1A

3Thursday, November 15, 2007

3Thursday, November 15, 2007

3Thursday, November 15, 2007

Page 8

5

Channel A-1

VMA_DQ[63..0](5)

VMA_DM[7..0](5)

VMA_RDQS[7..0](5)

VMA_WDQS[7..0](5)

VMA_MA[12..0](5)

D D

C C

VMA_BA0(5)

VMA_BA1(5)

VMA_ODT0(5)

CKEA0(5)

CSA0_0#(5)

WEA0#(5)

RASA0#(5)

CASA0#(5)

VMA_CLK0(5)

VMA_CLK0#(5)

VMA_DQ[63..0]

VMA_DM[7..0]

VMA_RDQS[7..0]

VMA_WDQS[7..0]

VMA_MA[12..0]

VMA_BA0

VMA_BA1

VMA_ODT0

CKEA0

CSA0_0#

WEA0#

RASA0#

CASA0#

VMA_CLK0

VMA_CLK0#

R107

R107

56_4

56_4

C252

C252

470p_4

470p_4

R106

R106

56_4

56_4

VMA_DQ7

VMA_DQ0

VMA_DQ6

VMA_DQ2

VMA_DQ3

VMA_DQ4

VMA_DQ1

VMA_DQ5

VMA_DQ29

VMA_DQ26

VMA_DQ24

VMA_DQ27

VMA_DQ30

VMA_DQ28

VMA_DQ25

VMA_DQ31

VMA_DM0

D0-D7 D8-D15

VMA_DM3

VMA_RDQS0

VMA_WDQS0

VMA_RDQS3

VMA_WDQS3

VMA_CLK0

VMA_CLK0#

VMA_BA1

VMA_BA0

VMA_MA12

VMA_MA11

VMA_MA10

VMA_MA9

VMA_MA8

VMA_MA7

VMA_MA6

VMA_MA5

VMA_MA4

VMA_MA3

VMA_MA2

VMA_MA1

VMA_MA0

VMA_ODT0

CKEA0

CSA0_0#

WEA0#

RASA0#

CASA0#

U6

U6

B9

UDQ7

B1

UDQ6

D9

UDQ5

D1

UDQ4

D3

UDQ3

D7

UDQ2

C2

UDQ1

C8

UDQ0

F9

LDQ7

F1

LDQ6

H9

LDQ5

H1

LDQ4

H3

LDQ3

H7

LDQ2

G2

LDQ1

G8

LDQ0

B3

UDM

F3

LDM

B7

UDQS

A8

UDQS

F7

LDQS

E8

LDQS

J8

CK

K8

CK

L3

BA1

L2

BA0

R2

A12

P7

A11

M2

A10

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K9

ODT

K2

CKE

L8

CS

K3

WE

K7

RAS

L7

CAS

GDDR2-BGA84

GDDR2-BGA84

4

15mil

VMREFA1

R26 4.99K/F_4R26 4.99K/F_4

J2

VREF

VDD1

VDD2

VDD3

VDD4

VDD5

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDL

NC1

NC2

NC3

NC4

NC5

NC6

VSS1

VSS2

VSS3

VSS4

VSS5

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSSDL

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

J1

A2

E2

L1

R3

R7

R8

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

R27 4.99K/F_4R27 4.99K/F_4

C45 0.1u_4C45 0.1u_4

C40

C40

1000p_4

1000p_4

L11 0_6L11 0_6

VDDLA1

C44

C44

0.1u_4

0.1u_4

C35

C35

C47

C47

0.1u_4

0.1u_4

0.01u_4

0.01u_4

15mil 15mil

C46

C46

1u_6

1u_6

+1.8V

C175

C175

10u_6

10u_6

3

U12

U12

B9

UDQ7

B1

UDQ6

D9

UDQ5

D1

UDQ4

D3

UDQ3

D7

UDQ2

C2

UDQ1

C8

UDQ0

F9

LDQ7

F1

LDQ6

H9

LDQ5

H1

LDQ4

H3

LDQ3

H7

LDQ2

G2

LDQ1

G8

LDQ0

B3

UDM

F3

LDM

B7

UDQS

A8

UDQS

F7

LDQS

E8

LDQS

J8

CK

K8

CK

L3

BA1

L2

BA0

R2

A12

P7

A11

M2

A10

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K9

ODT

K2

CKE

L8

CS

K3

WE

K7

RAS

L7

CAS

GDDR2-BGA84

GDDR2-BGA84

C36

C36

10u_6

10u_6

+1.8V

VMA_DQ11

VMA_DQ12

VMA_DQ8

VMA_DQ14

VMA_DQ15

VMA_DQ9

VMA_DQ13

VMA_DQ10

VMA_DQ19

VMA_DQ20

VMA_DQ23

VMA_DQ16

VMA_DQ18

VMA_DQ22

VMA_DQ17

VMA_DQ21

VMA_DM1

D16-D23D24-D31

VMA_DM2

VMA_RDQS1

VMA_WDQS1

VMA_RDQS2

VMA_WDQS2

VMA_CLK0

VMA_CLK0#

VMA_BA1

VMA_BA0

VMA_MA12

VMA_MA11

VMA_MA10

VMA_MA9

VMA_MA8

VMA_MA7

VMA_MA6

VMA_MA5

VMA_MA4

VMA_MA3

VMA_MA2

VMA_MA1

VMA_MA0

VMA_ODT0

CKEA0

CSA0_0#

WEA0#

RASA0#

CASA0#

VREF

VDD1

VDD2

VDD3

VDD4

VDD5

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDL

NC1

NC2

NC3

NC4

NC5

NC6

VSS1

VSS2

VSS3

VSS4

VSS5

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSSDL

2

VMREFA2

J2

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

J1

A2

E2

L1

R3

R7

R8

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

R95 4.99K/F_4R95 4.99K/F_4

R93 4.99K/F_4R93 4.99K/F_4

C192 0.1u_4C192 0.1u_4

C185

C185

1000p_4

1000p_4

L33 0_6L33 0_6

VDDLA2

C200

C200

0.1u_4

0.1u_4

C202

C202

1u_6

1u_6

C253

C253

0.01u_4

0.01u_4

C222

C222

0.1u_4

0.1u_4

+1.8V

C151

C151

10u_6

10u_6

C164

C164

10u_6

10u_6

1

+1.8V

U4

Channel A-1

VMA_ODT1(5)

B B

A A

CKEA1(5)

CSA1_0#(5)

WEA1#(5)

RASA1#(5)

CASA1#(5)

VMA_CLK1(5)

VMA_CLK1#(5)

VMA_ODT1

CKEA1

CSA1_0#

WEA1#

RASA1#

CASA1#

VMA_CLK1

VMA_CLK1#

R42

R42

R43

R43

56_4

56_4 C16

56_4

56_4 C17

C74

C74

470p_4

470p_4

5

VMA_DQ44

VMA_DQ47

VMA_DQ42

VMA_DQ40

VMA_DQ41

VMA_DQ43

VMA_DQ46

VMA_DQ45

VMA_DQ34

VMA_DQ38

VMA_DQ32

VMA_DQ37

VMA_DQ36

VMA_DQ35

VMA_DQ39

VMA_DQ33

VMA_DM5

D40-D47

VMA_DM4

D32-D39 D48-D55

VMA_RDQS5

VMA_WDQS5

VMA_RDQS4

VMA_WDQS4

VMA_CLK1

VMA_CLK1#

VMA_BA1

VMA_BA0

VMA_MA12

VMA_MA11

VMA_MA10

VMA_MA9

VMA_MA8

VMA_MA7

VMA_MA6

VMA_MA5

VMA_MA4

VMA_MA3

VMA_MA2

VMA_MA1

VMA_MA0

VMA_ODT1

CKEA1

CSA1_0#

WEA1#

RASA1#

CASA1# CASA1#

U4

B9

UDQ7

B1

UDQ6

D9

UDQ5

D1

UDQ4

D3

UDQ3

D7

UDQ2

C2

UDQ1

C8

UDQ0

F9

LDQ7

F1

LDQ6

H9

LDQ5

H1

LDQ4

H3

LDQ3

H7

LDQ2

G2

LDQ1

G8

LDQ0

B3

UDM

F3

LDM

B7

UDQS

A8

UDQS

F7

LDQS

E8

LDQS

J8

CK

K8

CK

L3

BA1

L2

BA0

R2

A12

P7

A11

M2

A10

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K9

ODT

K2

CKE

L8

CS

K3

WE

K7

RAS

L7

CAS

GDDR2-BGA84

GDDR2-BGA84

VDDQ10

VSSQ10

4

VREF

VDD1

VDD2

VDD3

VDD4

VDD5

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDL

NC1

NC2

NC3

NC4

NC5

NC6

VSS1

VSS2

VSS3

VSS4

VSS5

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSDL

J2

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

J1

A2

E2

L1

R3

R7

R8

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

15mil

VMREFA3

R18 4.99K/F_4R18 4.99K/F_4

R15 4.99K/F_4R15 4.99K/F_4

C26 0.1u_4C26 0.1u_4

C63

C63

1000p_4

1000p_4

L4 0_6L4 0_6

C19

C19

0.1u_4

0.1u_4

D56-D63

VMA_DQ58

VMA_DQ60

VMA_DQ59

VMA_DQ61

VMA_DQ63

VMA_DQ56

VMA_DQ62

VMA_DQ57

VMA_DQ49

VMA_DQ53

VMA_DQ50

VMA_DQ55

VMA_DQ52

VMA_DQ48

VMA_DQ54

VMA_DQ51

VMA_DM7

VMA_DM6

VMA_RDQS7

VMA_WDQS7

VMA_RDQS6

VMA_WDQS6

VMA_CLK1

VMA_CLK1#

VMA_BA1

VMA_BA0

VMA_MA12

VMA_MA11

VMA_MA10

VMA_MA9

VMA_MA8

VMA_MA7

VMA_MA6

VMA_MA5

VMA_MA4

VMA_MA3

VMA_MA2

VMA_MA1

VMA_MA0

VMA_ODT1

CKEA1

CSA1_0#

WEA1#

RASA1#

+1.8V

C27

C27

0.01u_4

0.01u_4

C12

C12

0.1u_4

0.1u_4

C5

10u_6C510u_6

+1.8V +1.8V

C6

10u_6C610u_6

15mil 15mil

C20

C20

1u_6

1u_6

3

U10

U10

B9

UDQ7

B1

UDQ6

D9

UDQ5

D1

UDQ4

D3

UDQ3

D7

UDQ2

C2

UDQ1

C8

UDQ0

F9

LDQ7

F1

LDQ6

H9

LDQ5

H1

LDQ4

H3

LDQ3

H7

LDQ2

G2

LDQ1

G8

LDQ0

B3

UDM

F3

LDM

B7

UDQS

A8

UDQS

F7

LDQS

E8

LDQS

J8

CK

K8

CK

L3

BA1

L2

BA0

R2

A12

P7

A11

M2

A10

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K9

ODT

K2

CKE

L8

CS

K3

WE

K7

RAS

L7

CAS

GDDR2-BGA84

GDDR2-BGA84

VREF

VDD1

VDD2

VDD3

VDD4

VDD5

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDL

NC1

NC2

NC3

NC4

NC5

NC6

VSS1

VSS2

VSS3

VSS4

VSS5

VSSQ1

VSSQ2

VSSQ3

VSSQ4