1

2

3

4

5

6

7

8

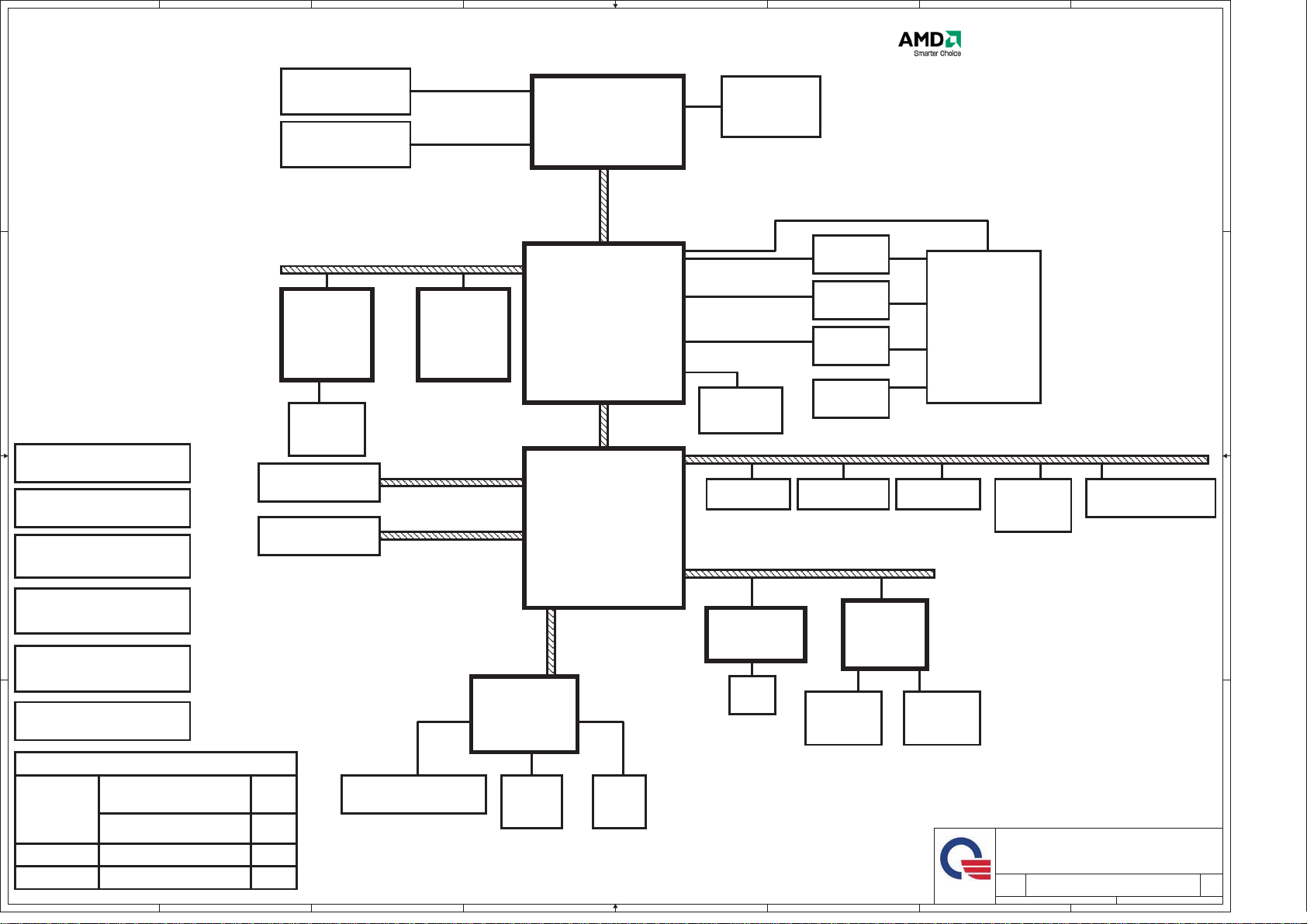

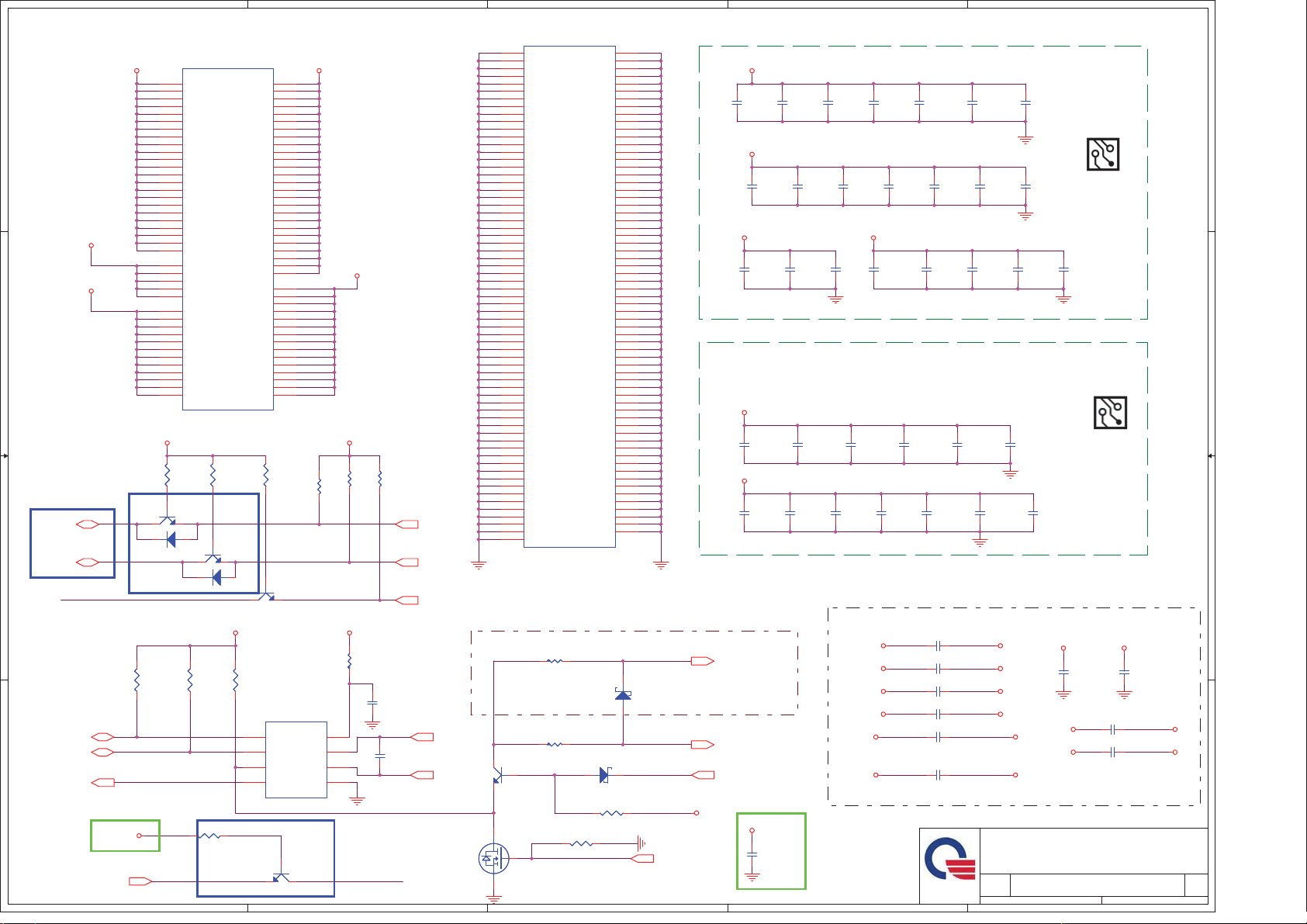

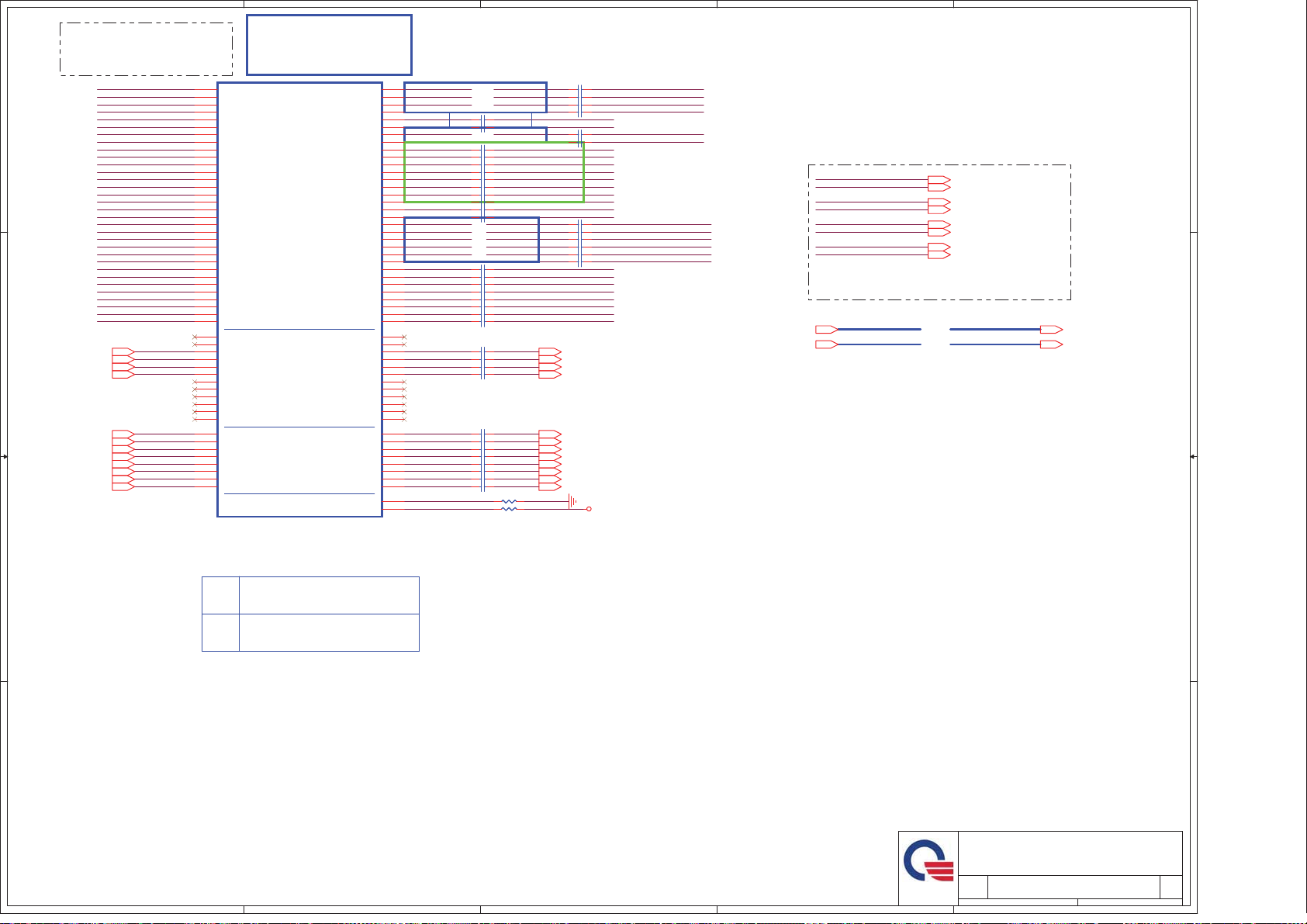

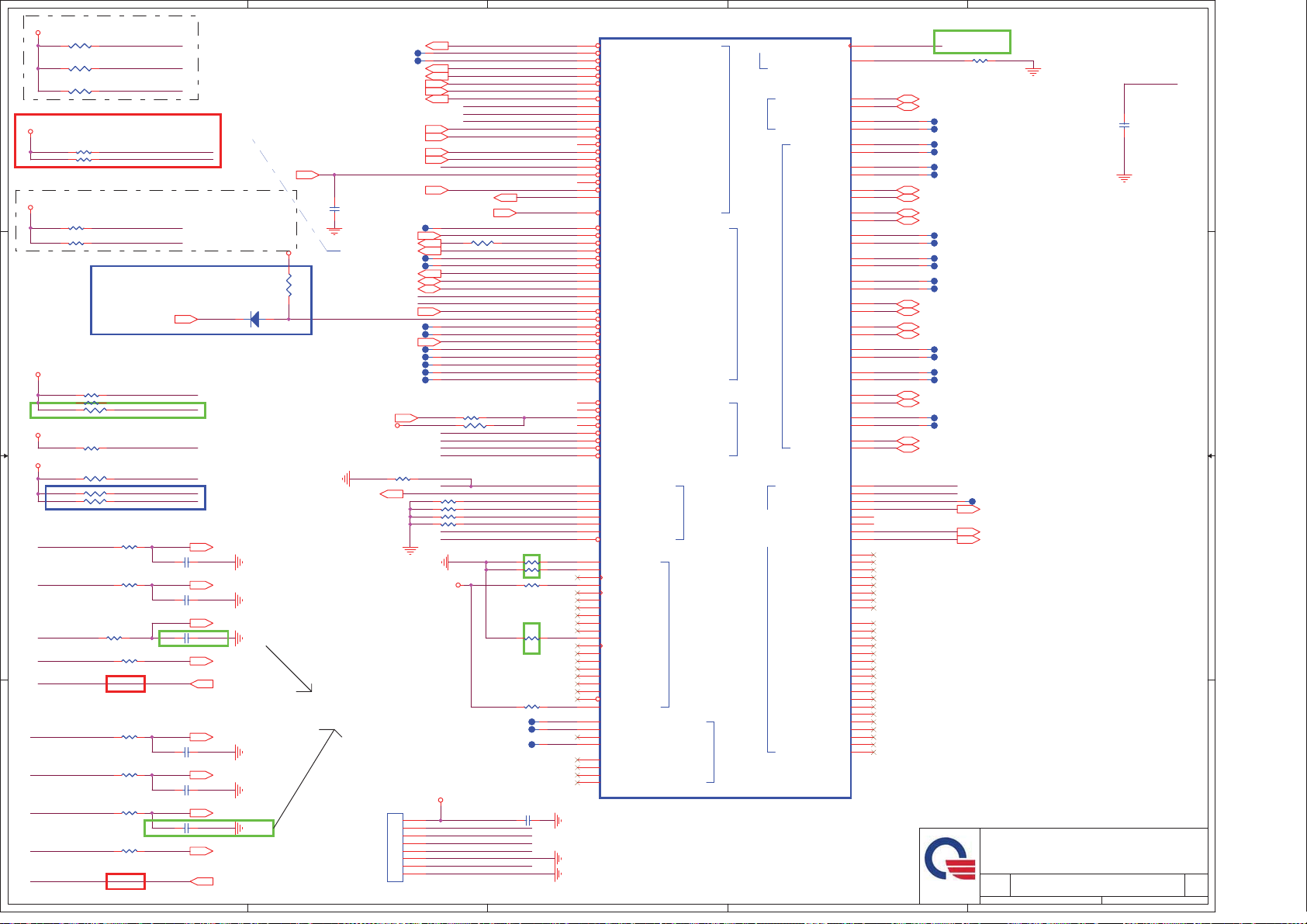

AX2/7 SYSTEM DIAGRAM

DDR3-SODIMM1

PAGE 6

A A

DDR3-SODIMM2

PAGE 7

DDR3 channel A

DDR3 channel B

AMD Champlain

35mm X 35mm

S1G4 Processor

638P (PGA)35W/25W

PAGE 3,4,5

CPU THERMAL

SENSOR

PAGE 5

01

HT3

PCI-E

3&,([SUHVV;

+'0,

PAGE 25

;

/$1

5HDOWHN

3&,(/$1

B B

RTL8103E

(10/100)

PAGE 30

;

0LQL3&,(

&DUG

:LUHOHVV/$1

PAGE 33

5-

PAGE 30

SYSTEM CHARGER(ISL6251)

PAGE 40

SYSTEM POWER ISL6237

6$7$+''

PAGE 29

PAGE 34

DDR II SMDDR_VTERM

1.8V/1.8VSUS(RT8207)

C C

VCCP +1.1V AND +1.2V(RT8204)

PAGE 37

6$7$&'520

PAGE 29

6$7$0%

6$7$0%

PAGE 35

VGACORE(1.1V~1.2V)Oz8118

NORTH BRIDGE

RS880M

PP;PPSLQ%*$

PAGE 8,9,10,11

ALINK X4

SOUTH BRIDGE

SB820 A12

PP;PPSLQ)&%*$

PAGE 12,13,14,15,16

/3&

A12

4.5W(Ext)

4.3W(Int)

6LGHSRUW

''55$0

IRU80$RQO\

PAGE 8

86%

0,5,8

;

$]DOLD

0'&&211

&57

PAGE 24

/9'6

PAGE 23

95$0

PAGE 22

15

PAGE 29 PAGE 29

%7VRIWEUHH]H86%3RUWV

5HDOWHN

$/&*5

PAGE 28

''5

:HEFDP

;

PAGE 27

$7,

3$5./3

23mm X 23mm

PAGE 17,18,19

20,21

2

PAGE 23

3

)ODVK0HGLD

576

PAGE 26

10

3&,(:/$1&DUG[

PAGE 33

PAGE 38

CPU CORE ISL6265HRTZ-T

PAGE 36

(1(.%&

.%'[

PAGE 32

5-

$QJ0,&

$8',2&211

3KRQH0,&

PAGE 28PAGE 27

SMBUS TABLE

Clock gen/Robson/TV tuner

SB--SCL0/SD0

D D

EC --SCL/SD

EC--SCL2/SD2

/DDR2/DDR2 thermal/Accelerometer

epress card

Wlan Card

Battery charge/discharge

VGA thermal/system thermal

1

+3V

.H\ERDUG

7RXFK3DG

+3VS5

+3VPCU

+3V

2

3

PAGE 31

PAGE 31

)$1

PAGE 28

4

63,

PAGE 31

352-(&7$;

352-(&7$;

352-(&7$;

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Block Diagram

Block Diagram

1%5'

1%5'

5

6

1%5'

Block Diagram

Date: Sheet

Date: Sheet

Date: Sheet

7

142Thursday, December 24, 2009

142Thursday, December 24, 2009

142Thursday, December 24, 2009

8

1A

1A

1A

of

of

of

5

4

3

2

1

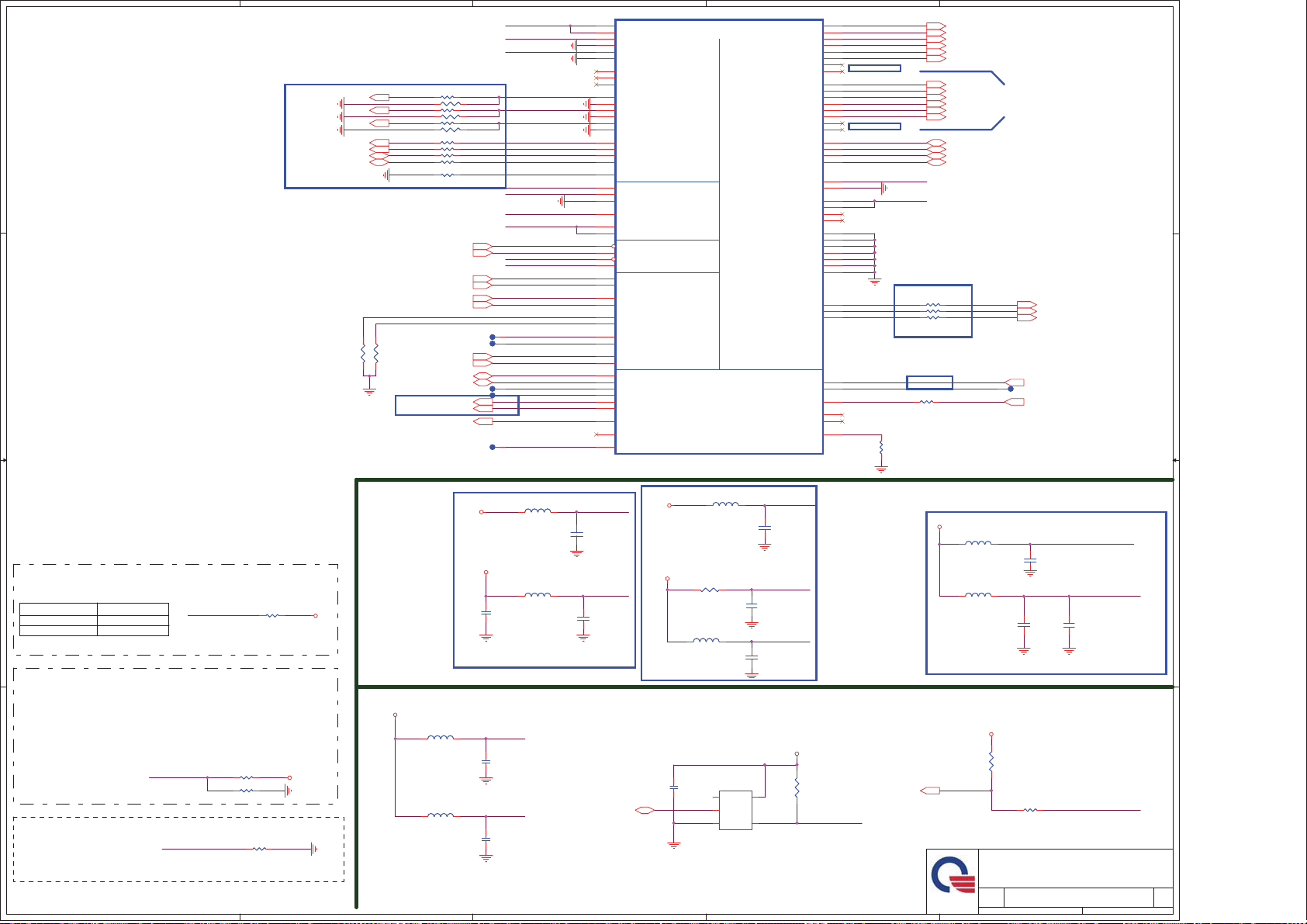

02

D D

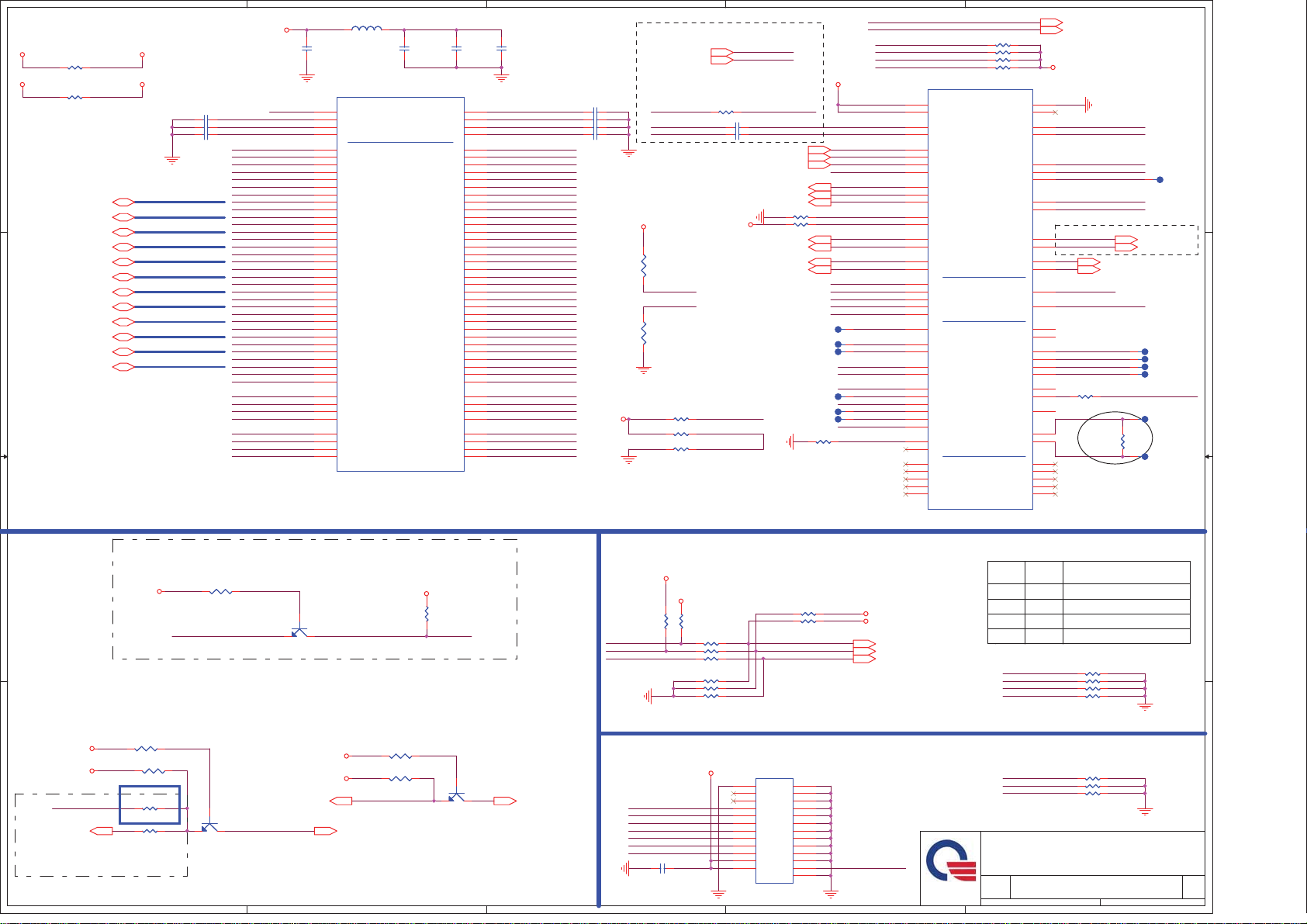

PV,delete all external clock GEN reserve material

C C

B B

A A

352-(&7$;

352-(&7$;

352-(&7$;

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

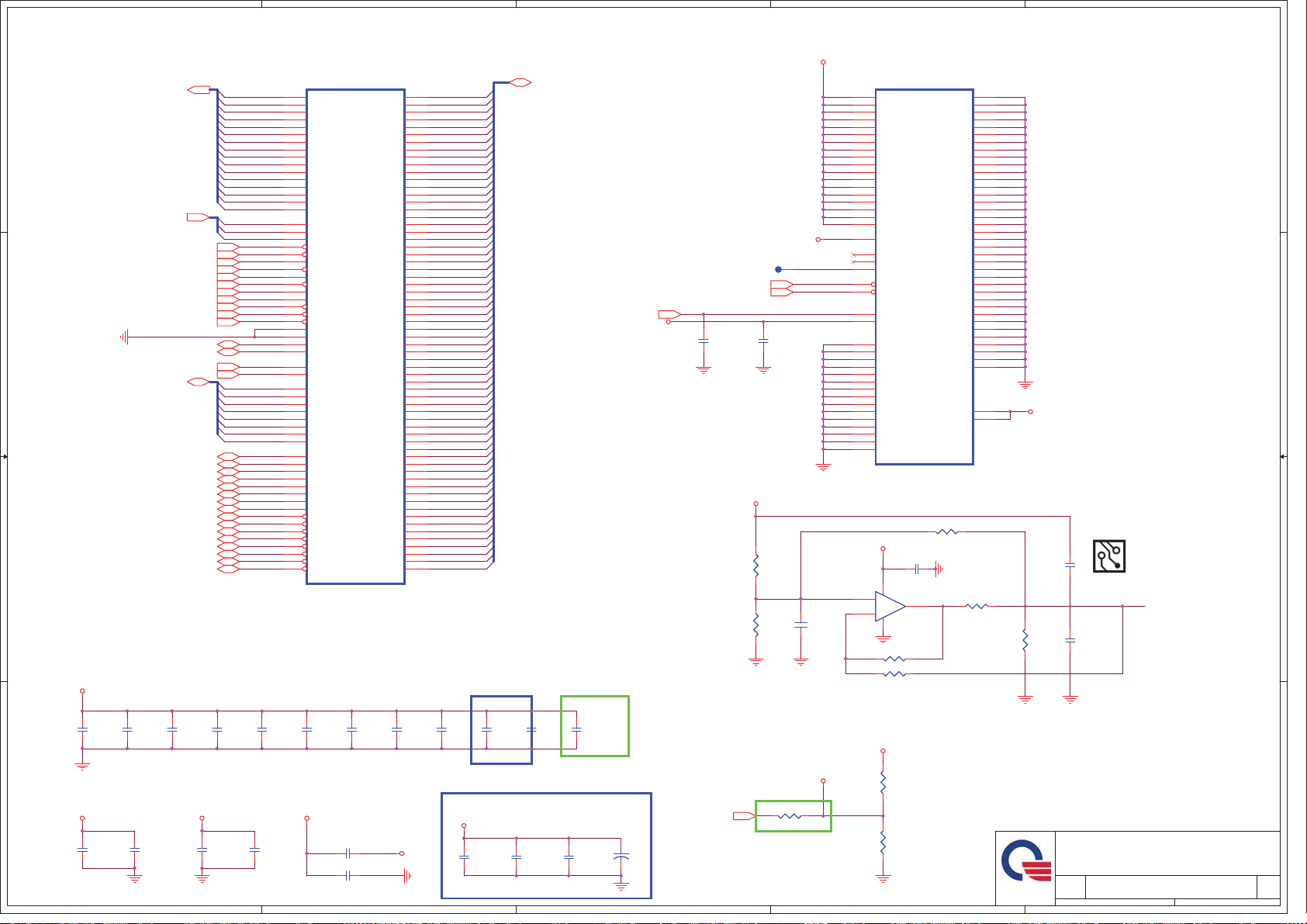

Clock Generator

Clock Generator

1%5'

1%5'

5

4

3

2

1%5'

Clock Generator

Date: Sheet

Date: Sheet

Date: Sheet

1

242Wednesday, December 23, 2009

242Wednesday, December 23, 2009

242Wednesday, December 23, 2009

1A

1A

1A

of

of

of

5

VLDT use 1.5A Max current

+1.1V +1.1V_VLDT

R164 *0_6/SR164 *0_6/S

R83 *0_6/SR83 *0_6/S

D D

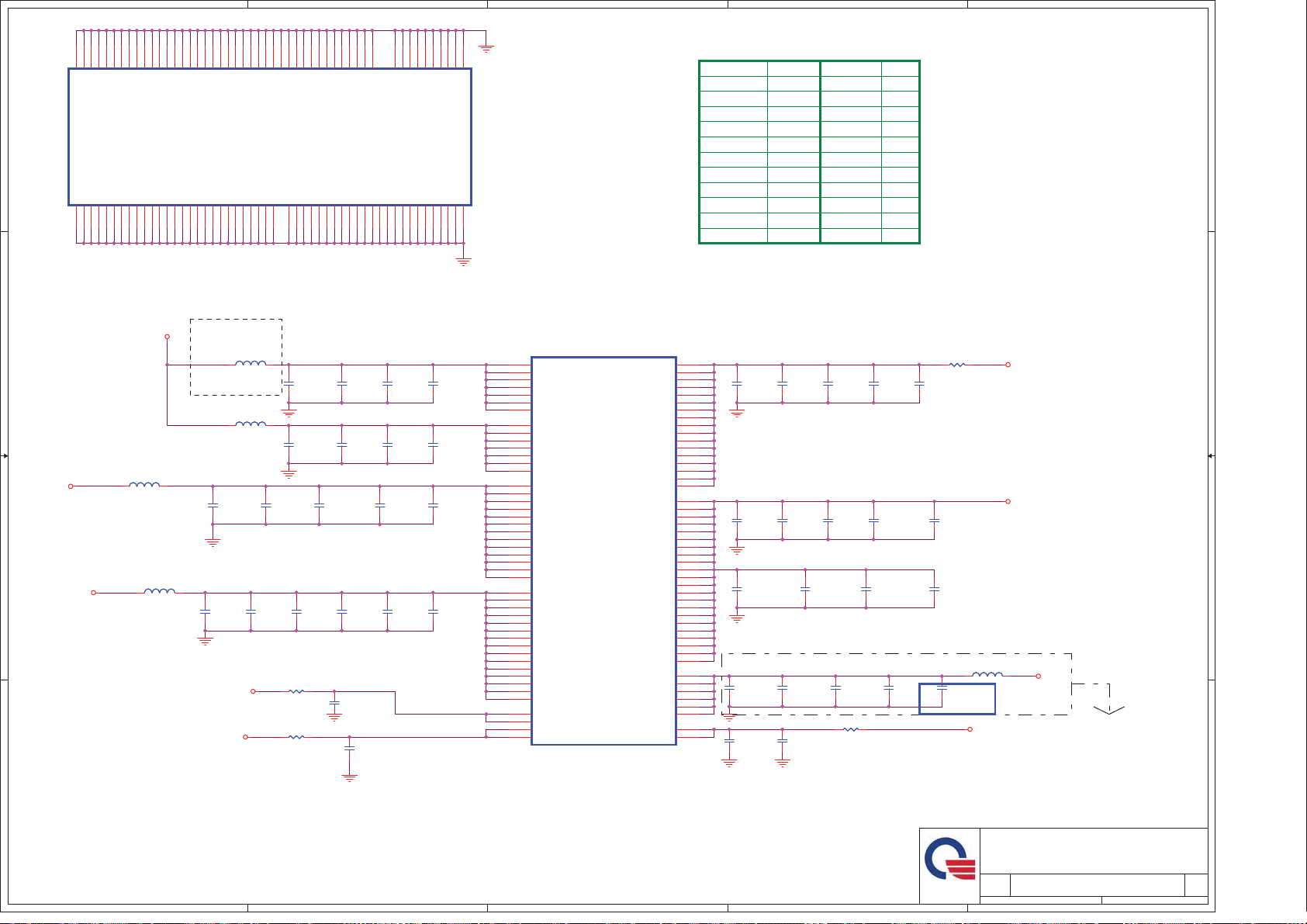

HT_NB_CPU_CAD_H[15..0]8

HT_NB_CPU_CAD_L[15..0]8

HT_NB_CPU_CLK_H[1..0]8

HT_NB_CPU_CLK_L[1..0]8

HT_NB_CPU_CTL_H[1..0]8

HT_NB_CPU_CTL_L[1..0]8

HT_CPU_NB_CAD_H[15..0]8

HT_CPU_NB_CAD_L[15..0]8

HT_CPU_NB_CLK_H[1..0]8

HT_CPU_NB_CLK_L[1..0]8

C C

HT_CPU_NB_CTL_H[1..0]8

HT_CPU_NB_CTL_L[1..0]8

FOX PZ63826-284R-41F

DG0^8000004 IC SOCKET SMD 638P S1(P1.27,H3.2)

MLX 47296-4131

DG0^8000003 IC SOCKET SMD 638P S1(P1.27,H3.2)

TYC 4-1903401-2

DG0^8000005 IC SOCKET SMD 638P S1(P1.27,H3.2)

+1.1V_VLDT_R+1.1V

C396 10U/6.3V_8C396 10U/6.3V_8

C390 0.22U/6.3V_4C390 0.22U/6.3V_4

C389 180P/50V_4C389 180P/50V_4

HT_NB_CPU_CAD_H[15..0]

HT_NB_CPU_CAD_L[15..0]

HT_NB_CPU_CLK_H[1..0]

HT_NB_CPU_CLK_L[1..0]

HT_NB_CPU_CTL_H[1..0]

HT_NB_CPU_CTL_L[1..0]

HT_CPU_NB_CAD_H[15..0]

HT_CPU_NB_CAD_L[15..0]

HT_CPU_NB_CLK_H[1..0]

HT_CPU_NB_CLK_L[1..0]

HT_CPU_NB_CTL_H[1..0]

HT_CPU_NB_CTL_L[1..0]

HT_NB_CPU_CAD_H0

HT_NB_CPU_CAD_L0

HT_NB_CPU_CAD_H1

HT_NB_CPU_CAD_L1

HT_NB_CPU_CAD_H2

HT_NB_CPU_CAD_L2

HT_NB_CPU_CAD_H3

HT_NB_CPU_CAD_L3

HT_NB_CPU_CAD_H4

HT_NB_CPU_CAD_L4

HT_NB_CPU_CAD_H5

HT_NB_CPU_CAD_L5

HT_NB_CPU_CAD_H6

HT_NB_CPU_CAD_L6

HT_NB_CPU_CAD_H7

HT_NB_CPU_CAD_L7

HT_NB_CPU_CAD_H8

HT_NB_CPU_CAD_L8

HT_NB_CPU_CAD_H9

HT_NB_CPU_CAD_L9

HT_NB_CPU_CAD_H10

HT_NB_CPU_CAD_L10

HT_NB_CPU_CAD_H11

HT_NB_CPU_CAD_L11

HT_NB_CPU_CAD_H12

HT_NB_CPU_CAD_L12

HT_NB_CPU_CAD_H13

HT_NB_CPU_CAD_L13

HT_NB_CPU_CAD_H14

HT_NB_CPU_CAD_L14

HT_NB_CPU_CAD_H15

HT_NB_CPU_CAD_L15

HT_NB_CPU_CLK_H0

HT_NB_CPU_CLK_L0

HT_NB_CPU_CLK_H1

HT_NB_CPU_CLK_L1

HT_NB_CPU_CTL_H0

HT_NB_CPU_CTL_H1

HT_NB_CPU_CTL_L1

BLM21PG221SN1D(220,100M,2A)_8

BLM21PG221SN1D(220,100M,2A)_8

+2.5V

C418

C418

4.7U/6.3V_6

4.7U/6.3V_6

+1.1V_VLDT

+1.1V_VLDT

+1.1V_VLDT

+1.1V_VLDT

L34

L34

LS0805-100M-N

U21A

U21A

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

SOCKET_638_PIN

SOCKET_638_PIN

4

HT LINK

HT LINK

+CPUVDDA

C392

C392

4.7U/6.3V_6

4.7U/6.3V_6

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

W/S= 15 mil/20mil

C304

C304

C302

C302

3300P/50V_4

3300P/50V_4

0.22U/25V_6

0.22U/25V_6

+1.1V_VLDT_R

AE2

+1.1V_VLDT_R

AE3

+1.1V_VLDT_R

AE4

+1.1V_VLDT_R

AE5

HT_CPU_NB_CAD_H0

AD1

HT_CPU_NB_CAD_L0

AC1

HT_CPU_NB_CAD_H1

AC2

HT_CPU_NB_CAD_L1

AC3

HT_CPU_NB_CAD_H2

AB1

HT_CPU_NB_CAD_L2

AA1

HT_CPU_NB_CAD_H3

AA2

HT_CPU_NB_CAD_L3

AA3

HT_CPU_NB_CAD_H4

W2

HT_CPU_NB_CAD_L4

W3

HT_CPU_NB_CAD_H5

V1

HT_CPU_NB_CAD_L5

U1

HT_CPU_NB_CAD_H6

U2

HT_CPU_NB_CAD_L6

U3

HT_CPU_NB_CAD_H7

T1

HT_CPU_NB_CAD_L7

R1

HT_CPU_NB_CAD_H8

AD4

HT_CPU_NB_CAD_L8

AD3

HT_CPU_NB_CAD_H9

AD5

HT_CPU_NB_CAD_L9

AC5

HT_CPU_NB_CAD_H10

AB4

HT_CPU_NB_CAD_L10

AB3

HT_CPU_NB_CAD_H11

AB5

HT_CPU_NB_CAD_L11

AA5

HT_CPU_NB_CAD_H12

Y5

HT_CPU_NB_CAD_L12

W5

HT_CPU_NB_CAD_H13

V4

HT_CPU_NB_CAD_L13

V3

HT_CPU_NB_CAD_H14

V5

HT_CPU_NB_CAD_L14

U5

HT_CPU_NB_CAD_H15

T4

HT_CPU_NB_CAD_L15

T3

HT_CPU_NB_CLK_H0

Y1

HT_CPU_NB_CLK_L0

W1

HT_CPU_NB_CLK_H1

Y4

HT_CPU_NB_CLK_L1

Y3

HT_CPU_NB_CTL_H0

R2

HT_CPU_NB_CTL_L0HT_NB_CPU_CTL_L0

R3

HT_CPU_NB_CTL_H1

T5

HT_CPU_NB_CTL_L1

R5

3

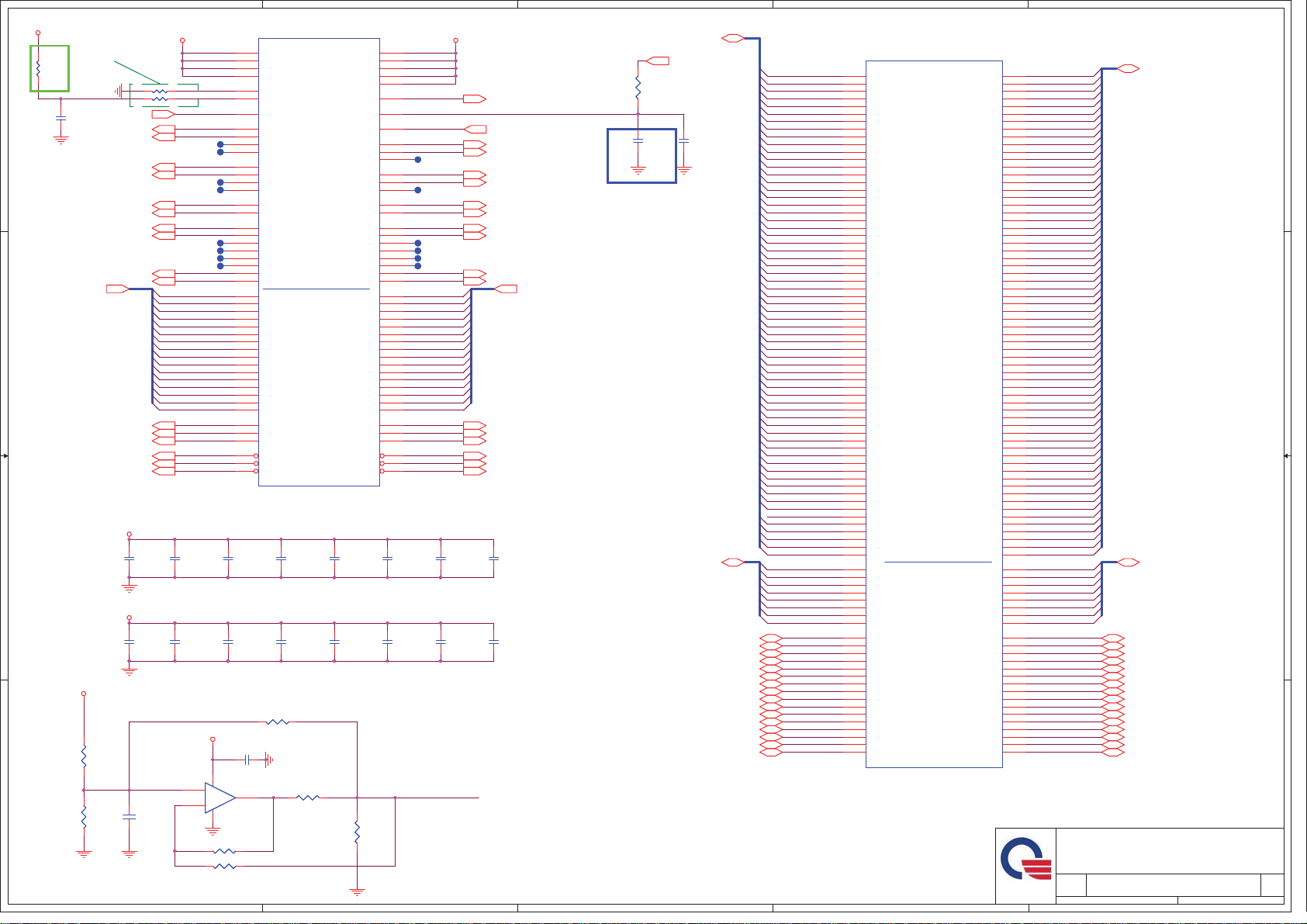

CPU CLK

CPUCLKP12

CPUCLKN12

Keep trace from resisor to CPU within 0.6"

keep trace from caps to CPU within 1.2"

CPUCLKIN

C9910U/6.3V_8 C9910U/6.3V_8

C1130.22U/6.3V_4 C1130.22U/6.3V_4

C120180P/50V_4 C120180P/50V_4

C59410U/6.3V_8 C59410U/6.3V_8

+1.5VSUS

+1.5VSUS

SideBand Temp sense I2C

R163

R163

510/F_4

510/F_4

CPUTEST25H

CPUTEST25L

R162

R162

510/F_4

510/F_4

R172 300/F_4R172 300/F_4

R338 1K/F_4R338 1K/F_4

R339 *300/F_4R339 *300/F_4

CPUCLKP

CPUCLKN

R149 169/F_4R149 169/F_4

C402 3900P/25V_4C402 3900P/25V_4

C401 3900P/25V_4C401 3900P/25V_4

+1.1V_VLDT

CPU_DBREQ#

CPUTEST27

CPU_VDD0_RUN_FB_H36

CPU_VDD0_RUN_FB_L36

CPU_VDD1_RUN_FB_H36

CPU_VDD1_RUN_FB_L36

CPUCLKP

CPUCLKN

CPU_LDT_RST#12

CPU_PWRGD12

CPU_LDT_STOP#10,12

CPU_SIC5

CPU_SID5

CPU_ALERT5

R114 44.2/F_4R114 44.2/F_4

R115 44.2/F_4R115 44.2/F_4

CPUCLKIN#

R157 *0_4/SR157 *0_4/S

2

H_THRMDC

H_THRMDA

CPU_PWRGD

CPU_LDT_RST#

CPU_LDT_STOP#

+CPUVDDA

place them to CPU within 1.5"

T7T7

T26T26

T30T30

place them to CPU within 1.5"

T127T127

T8T8

T6T6

CPU_LDT_REQ#_CPU

250mA

W/S= 15 mil/20mil

+CPUVDDA

+CPUVDDA

CPUCLKIN

CPUCLKIN#

CPU_LDT_RST#

CPU_PWRGD

CPU_LDT_STOP#

CPU_LDT_REQ#_CPU

CPU_SIC

CPU_SID

CPU_ALERT

CPU_HTREF0

CPU_HTREF1

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPUTEST23

CPUTEST18

CPUTEST19

CPUTEST25H

CPUTEST25L

CPUTEST21

CPUTEST20

CPUTEST24

CPUTEST22

CPUTEST12

CPUTEST27

U21D

U21D

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

C6

LDTREQ_L

AF4

SIC

AF5

SID

AE6

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_H

E6

VDD0_FB_L

Y6

VDD1_FB_H

AB6

VDD1_FB_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

AD7

TEST23

H10

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

AB8

TEST21

AF7

TEST20

AE7

TEST24

AE8

TEST22

AC8

TEST12

AF8

TEST27

C2

TEST9

AA6

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

SOCKET_638_PIN

SOCKET_638_PIN

VSS

RSVD11

SVC

SVD

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

R146300_4 R146300_4

R148300_4 R148300_4

R166300_4 R166300_4

R144*300/F_4 R144*300/F_4

1

H_THRMDC 5

H_THRMDA 5

+1.5V

M11

W18

CPU_SVC_R

A6

CPU_SVD_R

A4

CPU_THERMTRIP_L#

AF6

CPU_PROCHOT_L#

AC7

CPU_MEMHOT_L#

AA8

H_THRMDC

W7

H_THRMDA

W8

VDDIO_FB_H

W9

VDDIO_FB_L

Y9

H6

G6

E10

AE9

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

CPU_VDDNB_RUN_FB_H 36

CPU_VDDNB_RUN_FB_L 36

CPU_DBREQ#

CPU_TDO

CPUTEST17

CPUTEST16

CPUTEST15

CPUTEST14

R156 *300/F_4R156 *300/F_4

CPUTEST29H

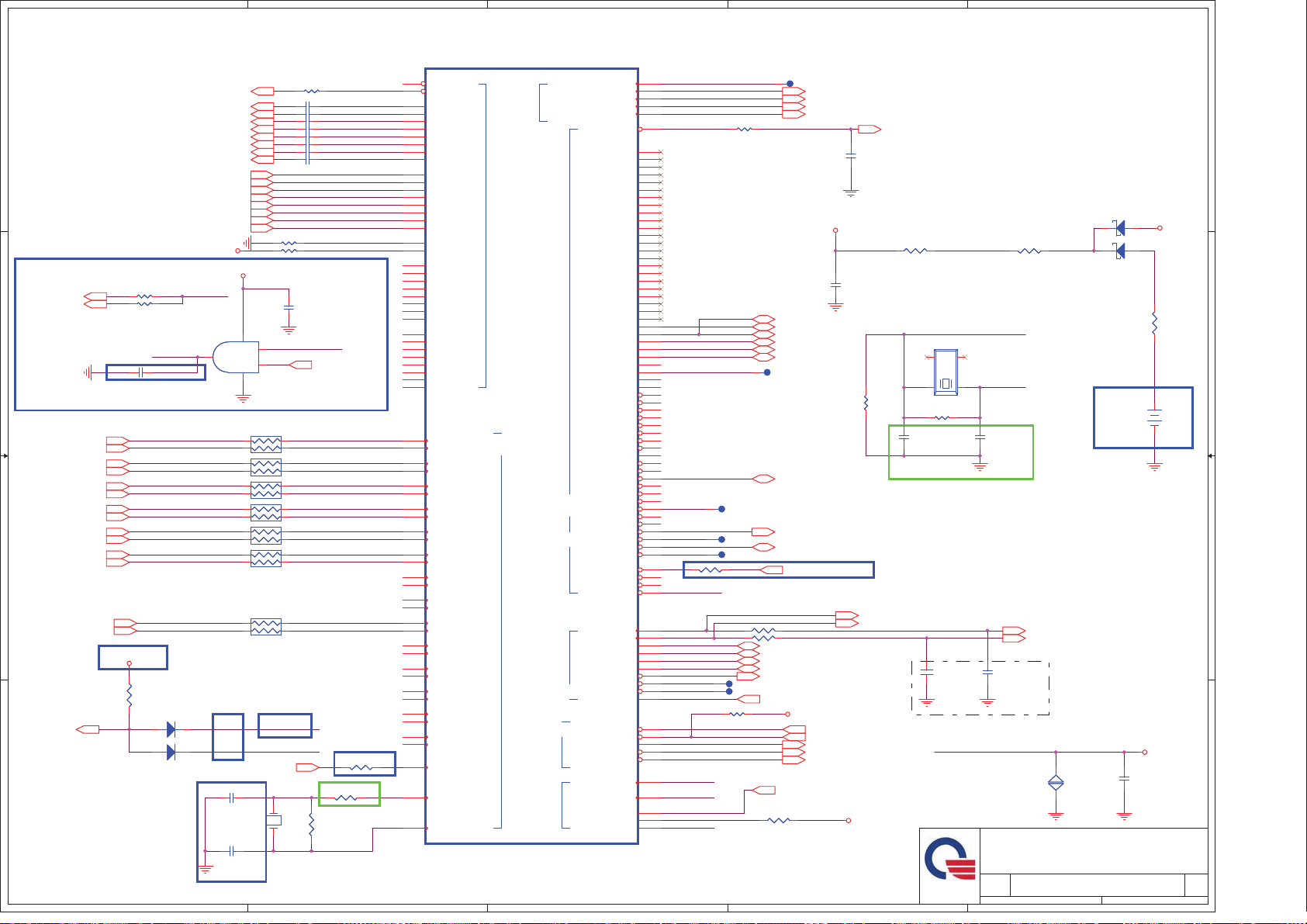

CPUTEST29L

Route as 80ohm, diff

03

T15T15

VDDIO_FB_H 37

VDDIO_FB_L 37

T37T37

T38T38

T29T29

T49T49

+1.1V_VLDT

T46T46

R130

R130

80.6/F_4

80.6/F_4

T45T45

MV can remove reserve for debug

B B

+1.5VSUS

+1.5VSUS

+1.5VSUS

A A

CPU_PROCHOT_L#

R224 10K/F_4R224 10K/F_4

R225 300_4R225 300_4

R205 0_4R205 0_4

R219 0_4R219 0_4

EC new option

5

R207 10K/F_4R207 10K/F_4

CPU_LDT_RST#

2

Q22

Q22

1 3

MMBT3904

MMBT3904

SI , add R205 for P-state implement

CNTR_VREF

1 3

CPU_PROCHOT_R#

2

Q19

Q19

MMBT3904

MMBT3904

+1.5VSUS

+1.5VSUS

CPU_LDT_RST_HTPA#

CPU_THERMTRIP_L#

CPU_PROCHOT_R# 12CPU_PROCHOT#32

4

+3V

R181 10K/F_4R181 10K/F_4

R180 1K/F_4R180 1K/F_4

R186

R186

1K/F_4

1K/F_4

2

1 3

Q18

Q18

MMBT3904

MMBT3904

CPU_THERMTRIP# 13CPU_THERMTRIP_L#5

Serial VID

+1.5VSUS

+1.5V

R170

R170

*1K/F_4

*1K/F_4

CPU_SVC_R

CPU_SVD_R

CPU_PWRGD

R171

R171

*1K/F_4

*1K/F_4

R176 0_4R176 0_4

R175 0_4R175 0_4

R177 0_4R177 0_4

R184 *220_4R184 *220_4

R183 *220_4R183 *220_4

R185 *220_4R185 *220_4

HDT Connector

+1.5VSUS

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

C74 *0.1U/10V_4C74 *0.1U/10V_4

3

R189 1K/F_4R189 1K/F_4

R190 1K/F_4R190 1K/F_4

CPU_SVC

CPU_SVD

CPU_PWRGD_SVID_REG

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

KEY

KEY

CN6 *HDT CONN

CN6 *HDT CONN

25

+1.5VSUS

+1.5V

CPU_SVC 36

CPU_SVD 36

CPU_PWRGD_SVID_REG 36

CPU_LDT_RST_HTPA#

2

1%5'

1%5'

1%5'

VFIX MODE

SVC SVD Output Voltage

00

001

1

11

CPUTEST20

CPUTEST21

CPUTEST22

CPUTEST24

CPUTEST12

CPUTEST19

CPUTEST18

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

Date: Sheet of

VID Override table (VDD)

1.1V

1.0V

0.9V

0.8V

R340 1K/F_4R340 1K/F_4

R81 1K/F_4R81 1K/F_4

R80 1K/F_4R80 1K/F_4

R69 1K/F_4R69 1K/F_4

R70 1K/F_4R70 1K/F_4

R124 1K/F_4R124 1K/F_4

R125 1K/F_4R125 1K/F_4

352-(&7$;

352-(&7$;

352-(&7$;

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

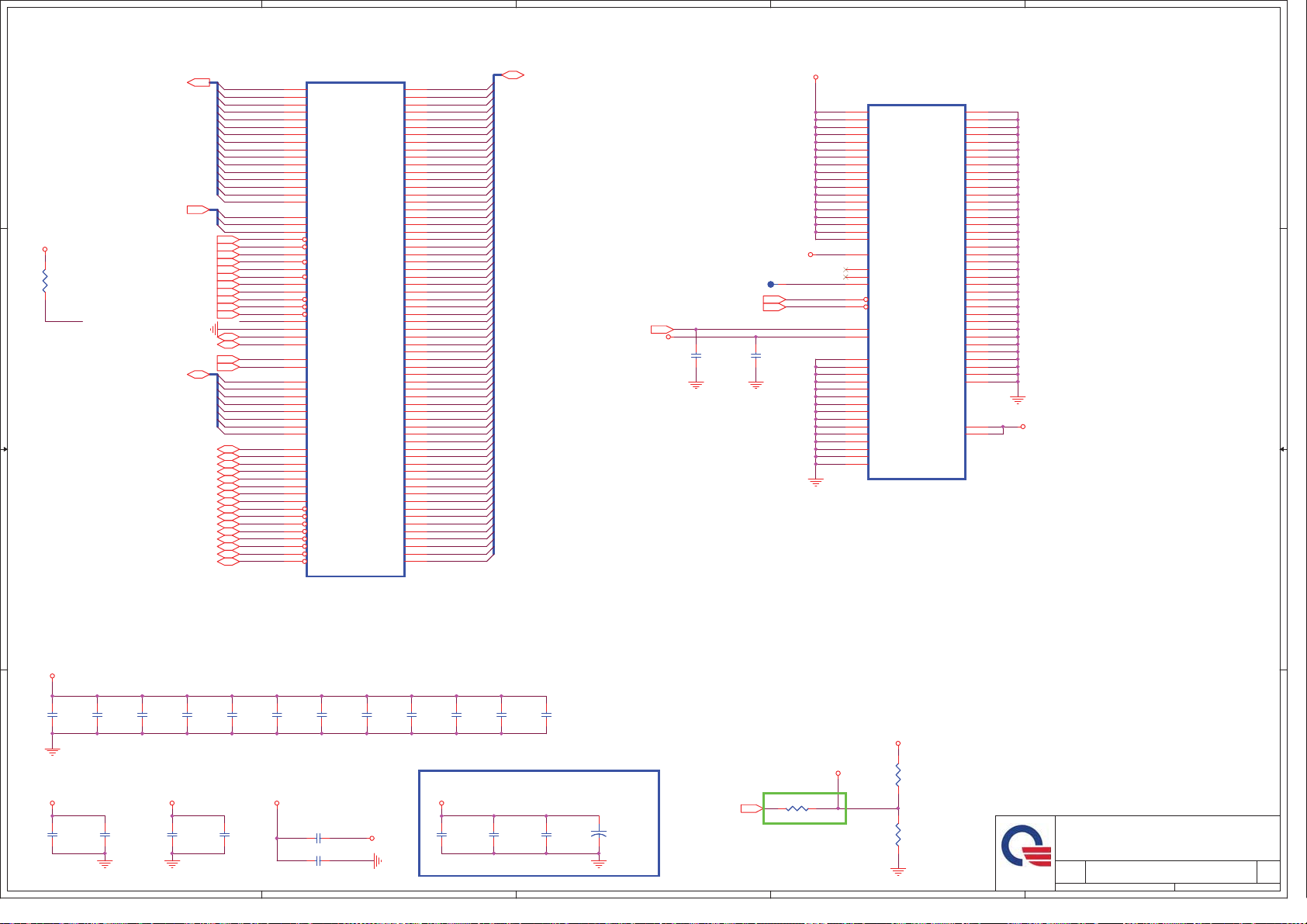

S1G4 HT,CTL I/F 1/3

S1G4 HT,CTL I/F 1/3

S1G4 HT,CTL I/F 1/3

1

of

342Thursday, December 24, 2009

342Thursday, December 24, 2009

342Thursday, December 24, 2009

1A

1A

1A

A

+1.5VSUS

PLACE THEM CLOSE TO

CPU WITHIN 1"

R337

R337

*0_4/S

*0_4/S

C593

C593

4 4

10U/6.3V_8

10U/6.3V_8

PV,change

to short pad

MEM_MA_ADD[0..15]6

3 3

2 2

1 1

MEM_MA_RESET#6

+1.5VSUS

MEM_MA0_ODT06

MEM_MA0_ODT16

MEM_MA0_CS#06

MEM_MA0_CS#16

MEM_MA_CLK5_P6

MEM_MA_CLK5_N6

MEM_MA_CLK4_P6

MEM_MA_CLK4_N6

MEM_MA_BANK06

MEM_MA_BANK16

MEM_MA_BANK26

MEM_MA_RAS#6

MEM_MA_CAS#6

MEM_MA_WE#6

R229

R229

1K/F_4

1K/F_4

R222

R222

1K/F_4

1K/F_4

MEM_MA_CKE06

MEM_MA_CKE16

+0.9V

4.7U/6.3V_6

4.7U/6.3V_6

+0.9V

1000P/50V_4

1000P/50V_4

+0.9V +0.9V

R344 39.2/F_4R344 39.2/F_4

R342 39.2/F_4R342 39.2/F_4

M_ZP

M_ZN

MEM_MA_RESET# MEMVREF_CPU

T19T19

T17T17

T18T18

T16T16

T39T39

T34T34

T13T13

T14T14

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

D10

C10

B10

AD10

AF10

AE10

H16

T19

V22

U21

V19

T20

U19

U20

V20

J22

J20

N19

N20

E16

F16

Y16

AA16

P19

P20

N21

M20

N22

M19

M22

L20

M24

L21

L19

K22

R21

L22

K20

V24

K24

K19

R20

R23

J21

R19

T22

T24

U21B

U21B

VDDR1

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

VDDR2

VDDR3

VDDR4

MEMZP

MEMZN

MA_RESET_L

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_CKE0

MA_CKE1

MA_CLK_H5

MA_CLK_L5

MA_CLK_H1

MA_CLK_L1

MA_CLK_H7

MA_CLK_L7

MA_CLK_H4

MA_CLK_L4

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_RAS_L

MA_CAS_L

MA_WE_L

SOCKET_638_PIN

SOCKET_638_PIN

VDDR_SENSE

MEMVREF

MB_RESET_L

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

Place close to socket

C94

C95

C95

C98

C98

C439

C439

*0.47u/6.3V_4

*0.47u/6.3V_4

A

C94

4.7U/6.3V_6

4.7U/6.3V_6

C96

C96

1000P/50V_4

1000P/50V_4

4.7U/6.3V_6

4.7U/6.3V_6

1000P/50V_4

1000P/50V_4

+3VPCU

52

U14

U14

3

+

+

4

-

-

*OPA343NA/3K

*OPA343NA/3K

R193 *0_4R193 *0_4

R204 *0_4R204 *0_4

C420

C420

C400

C400

R211 0_4R211 0_4

C435

C435

*.1U/10V_4

*.1U/10V_4

1

C419

C419

4.7U/6.3V_6

4.7U/6.3V_6

C397

C397

1000P/50V_4

1000P/50V_4

R200 *10_4R200 *10_4

1 2

0.22U/6.3V_4

0.22U/6.3V_4

180P/50V_4

180P/50V_4

R220

R220

*10K/F_4

*10K/F_4

VDDR5

VDDR6

VDDR7

VDDR8

VDDR9

MB_CKE0

MB_CKE1

C91

C91

C105

C105

B

VDDR = 0.9V for 25W & 35W CPU

W10

AC10

AB10

AA10

A10

CPU_VTT_SENSE

Y10

W17

MEM_MB_RESET#

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

C90

C90

0.22U/6.3V_4

0.22U/6.3V_4

C104

C104

180P/50V_4

180P/50V_4

T132T132

T20T20

T142T142

T141T141

T128T128

T129T129

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

VDDR = 1.05V for 35V & 45W CPU

C411

C411

0.22U/6.3V_4

0.22U/6.3V_4

C393

C393

180P/50V_4

180P/50V_4

Reserved for AMD suggest

MEMVREF_CPU

B

CPU_VTT_SENSE 37

MEM_MB_RESET# 7

MEM_MB0_ODT0 7

MEM_MB0_ODT1 7

MEM_MB0_CS#0 7

MEM_MB0_CS#1 7

MEM_MB_CKE0 7

MEM_MB_CKE1 7

MEM_MB_CLK5_P 7

MEM_MB_CLK5_N 7

MEM_MB_CLK4_P 7

MEM_MB_CLK4_N 7

MEM_MB_ADD[0..15] 7

MEM_MB_BANK0 7

MEM_MB_BANK1 7

MEM_MB_BANK2 7

MEM_MB_RAS# 7

MEM_MB_CAS# 7

MEM_MB_WE# 7

C407

C407

0.22U/6.3V_4

0.22U/6.3V_4

C93

C93

180P/50V_4

180P/50V_4

C

MEM_MB_DATA[0..63]7

DDR_VTTREF 6,7,37

R113

R113

*0_4

*0_4

Reserved

C181

C181

0.1U/10V_4

0.1U/10V_4

SI , change from 0.01u to 0.1u

from AMD recommand

C

C175

C175

1000P/50V_4

1000P/50V_4

MEM_MB_DM[0..7]7

MEM_MB_DQS0_P7

MEM_MB_DQS0_N7

MEM_MB_DQS1_P7

MEM_MB_DQS1_N7

MEM_MB_DQS2_P7

MEM_MB_DQS2_N7

MEM_MB_DQS3_P7

MEM_MB_DQS3_N7

MEM_MB_DQS4_P7

MEM_MB_DQS4_N7

MEM_MB_DQS5_P7

MEM_MB_DQS5_N7

MEM_MB_DQS6_P7

MEM_MB_DQS6_N7

MEM_MB_DQS7_P7

MEM_MB_DQS7_N7

D

Processor Memory Interface

U21C

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

Y11

AE14

AF14

AF11

AD11

A12

B16

A22

E25

AB26

AE22

AC16

AD12

C12

B12

D16

C16

A24

A23

F26

E26

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

U21C

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

SOCKET_638_PIN

SOCKET_638_PIN

D

MEM:DATA

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

1%5'

1%5'

1%5'

E

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

352-(&7$;

352-(&7$;

352-(&7$;

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

S1G4 DDRII MEMORY I/F 2/3

S1G4 DDRII MEMORY I/F 2/3

S1G4 DDRII MEMORY I/F 2/3

Date: Sheet

Date: Sheet

Date: Sheet

MEM_MA_DATA[0..63] 6

MEM_MA_DM[0..7] 6

MEM_MA_DQS0_P 6

MEM_MA_DQS0_N 6

MEM_MA_DQS1_P 6

MEM_MA_DQS1_N 6

MEM_MA_DQS2_P 6

MEM_MA_DQS2_N 6

MEM_MA_DQS3_P 6

MEM_MA_DQS3_N 6

MEM_MA_DQS4_P 6

MEM_MA_DQS4_N 6

MEM_MA_DQS5_P 6

MEM_MA_DQS5_N 6

MEM_MA_DQS6_P 6

MEM_MA_DQS6_N 6

MEM_MA_DQS7_P 6

MEM_MA_DQS7_N 6

E

442Thursday, December 24, 2009

442Thursday, December 24, 2009

442Thursday, December 24, 2009

04

of

of

of

1A

1A

1A

5

U21E

U21E

G4

VDD0_1

H2

VDD0_2

J9

VDD0_3

J11

VDD0_4

J13

VDD0_5

MMBT3904

MMBT3904

Q23

Q23

J15

VDD0_6

K6

VDD0_7

K10

VDD0_8

K12

VDD0_9

K14

VDD0_10

L4

VDD0_11

L7

VDD0_12

L9

VDD0_13

L11

VDD0_14

L13

VDD0_15

L15

VDD0_16

M2

VDD0_17

M6

VDD0_18

M8

VDD0_19

M10

VDD0_20

N7

VDD0_21

N9

VDD0_22

N11

VDD0_23

K16

VDDNB_1

M16

VDDNB_2

P16

VDDNB_3

T16

VDDNB_4

V16

VDDNB_5

H25

VDDIO1

J17

VDDIO2

K18

VDDIO3

K21

VDDIO4

K23

VDDIO5

K25

VDDIO6

L17

VDDIO7

M18

VDDIO8

M21

VDDIO9

M23

VDDIO10

M25

VDDIO11

N17

VDDIO12

SOCKET_638_PIN

SOCKET_638_PIN

R228

R228

2K/F_4

2K/F_4

2

13

21

D19RB501V-40 D19RB501V-40

D D

+CPUVDDNB

4A

+1.5VSUS

2A

C C

SI , change SMB

connection

MBCLK32,40

MBDATA32,40

B B

MBCLK

MBDATA

SMBALERT#

R198

R198

2K/F_4

2K/F_4

2

Q21

Q21

MMBT3904

MMBT3904

13

21

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

D16RB501V-40 D16RB501V-40

+VCORE+VCORE +VCORE

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

R173

R173

2K/F_4

2K/F_4

CPU_SIC

CPU_SID

2

Q17 *MMBT3904Q17 *MMBT3904

13

SI , add Q21,Q23,D16,D19

200/F_6

G786P8

G786P8

2

VCC

DXP

DXN

GND

MSOP

Q33

Q33

MMBT3904

MMBT3904

200/F_6

R424

R424

10K/F_4

10K/F_4

MBCLK218,32

MBDATA218,32

PM_THERM#13

A A

PV ,Change from +1.5VSUS to +1.5V

for leakage current issue

+1.5V

CPU_THERMTRIP_L#3

5

R423

R423

R416

R416

10K/F_4

10K/F_4

10K/F_4

10K/F_4

U25

U25

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

R428 10K/F_4R428 10K/F_4

CPU_THERMTRIP_L# SMBALERT#

1 3

4

+1.5VSUS

+1.5VSUS+1.5VSUS

R214

R214

R187

R187

1K/F_4

1K/F_4

1K/F_4

1K/F_4

CPU_ALERT

+3V+3V

R405

R405

1

2

3

5

SMBALERT#

SI , add Q33,R428

4

R178

R178

1K/F_4

1K/F_4

C693

C693

0.1U/10V_4

0.1U/10V_4

C695

C695

1000P/50V_4

1000P/50V_4

3

U21F

U21F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

CPU_SIC 3

CPU_SID 3

CPU_ALERT 3

H_THRMDA 3

H_THRMDC 3 ECPWROK 16,32

PQ18

PQ18

*2N7002E-G

*2N7002E-G

H21

VSS63

H23

VSS64

J4

VSS65

SOCKET_638_PIN

SOCKET_638_PIN

PROCESSOR POWER AND GROUND

R212 *0_4R212 *0_4

reserve for

power shutdown

( if can )

R203 *0_4/SR203 *0_4/S

Q20

Q20

MMBT3904

MMBT3904

2

1 3

3

1

R174 *10K/F_4R174 *10K/F_4

2

ADD VGA TEMP_ FAIL function

M92 is active Hi

J6

VSS66

J8

VSS67

J10

VSS68

J12

VSS69

J14

VSS70

J16

VSS71

J18

VSS72

K2

VSS73

K7

VSS74

K9

VSS75

K11

VSS76

K13

VSS77

K15

VSS78

K17

VSS79

L6

VSS80

L8

VSS81

L10

VSS82

L12

VSS83

L14

VSS84

L16

VSS85

L18

VSS86

M7

VSS87

M9

VSS88

AC6

VSS89

M17

VSS90

N4

VSS91

N8

VSS92

N10

VSS93

N16

VSS94

N18

VSS95

P2

VSS96

P7

VSS97

P9

VSS98

P11

VSS99

P17

VSS100

R8

VSS101

R10

VSS102

R16

VSS103

R18

VSS104

T7

VSS105

T9

VSS106

T11

VSS107

T13

VSS108

T15

VSS109

T17

VSS110

U4

VSS111

U6

VSS112

U8

VSS113

U10

VSS114

U12

VSS115

U14

VSS116

U16

VSS117

U18

VSS118

V2

VSS119

V7

VSS120

V9

VSS121

V11

VSS122

V13

VSS123

V15

VSS124

V17

VSS125

W6

VSS126

Y21

VSS127

Y23

VSS128

N6

VSS129

SYS_SHDN#

D17

D17

*CH500H

*CH500H

2 1

3920_RST#

D18

D18

2 1

CH501H-40PT

CH501H-40PT

R218 10K/F_4R218 10K/F_4

ECPWROK

3

+VCORE

+CPUVDDNB

+1.5VSUS

+1.5VSUS

SYS_SHDN# 34

3920_RST# 32

+3V

TEMP_FAIL 18

2

1

BOTTOM SIDE DECOUPLI NG

C216

C180

C180

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C223

C223

22U/6.3V_8

22U/6.3V_8

C242

C242

C216

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C212

C212

22U/6.3V_8

22U/6.3V_8

C250

C250

C230

C230

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C235

C235

22U/6.3V_8

22U/6.3V_8

C228

C228

+1.5VSUS

C247

C247

22U/6.3V_8

22U/6.3V_8

C214

C214

22U/6.3V_8

22U/6.3V_8

C215

C215

22U/6.3V_8

22U/6.3V_8

C256

C256

0.22U/6.3V_4

0.22U/6.3V_4

C177

C177

0.22U/6.3V_4

0.22U/6.3V_4

C227

C227

22U/6.3V_8

22U/6.3V_8

C255

C255

0.01U/16V_4

0.01U/16V_4

C178

C178

0.01U/16V_4

0.01U/16V_4

C238

C238

0.22U/6.3V_4

0.22U/6.3V_4

C254

C254

180P/50V_4

180P/50V_4

C176

C176

180P/50V_4

180P/50V_4

C257

C257

0.22U/6.3V_4

0.22U/6.3V_4

C258

C258

180P/50V_4

180P/50V_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

C123

C115

C115

4.7U/6.3V_6

4.7U/6.3V_6

C135

C135

0.22U/6.3V_4

0.22U/6.3V_4

+VIN

EC13

EC13

0.1U/10V_4

0.1U/10V_4

C291

C126

C126

4.7U/6.3V_6

4.7U/6.3V_6

C133

C133

0.22U/6.3V_4

0.22U/6.3V_4

C291

4.7U/6.3V_6

4.7U/6.3V_6

C188

C188

0.01U/16V_4

0.01U/16V_4

+1.5V_VGA +3V

+VGA_CORE

+VIN

+5V

+VGA_CORE +1.8V_VGA

PV,add for

EMI suggest

2

C172

C172

0.1U/10V_4

0.1U/10V_4

4.7U/6.3V_6

4.7U/6.3V_6

C288

C288

0.22U/6.3V_4

0.22U/6.3V_4

C287

C287

180P/50V_4

180P/50V_4

EC10 0.01U/16V_4EC10 0.01U/16V_4

EC12 0.01U/16V_4EC12 0.01U/16V_4

EC8 0.01U/16V_4EC8 0.01U/16V_4

EC7 0.01U/16V_4EC7 0.01U/16V_4

EC1 *0.01U/16V_4EC1 *0.01U/16V_4

EC2 *0.01U/16V_4EC2 *0.01U/16V_4

1%5'

1%5'

1%5'

C119

C119

C123

0.22U/6.3V_4

0.22U/6.3V_4

C189

C284

C284

180P/50V_4

180P/50V_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

C189

0.1U/10V_4

0.1U/10V_4

+VGA_CORE

EC15

+3V+1.8V_VGA

+3V

+3V

+3V

For fix HyperTransport nets

across plane splits

352-(&7$;

352-(&7$;

352-(&7$;

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

S1G4 PWR & GND 3/3

S1G4 PWR & GND 3/3

S1G4 PWR & GND 3/3

EC15

0.1U/10V_4

0.1U/10V_4

+1.5V_VGA +3V

EC9 0.01U/16V_4EC9 0.01U/16V_4

EC11 0.01U/16V_4EC11 0.01U/16V_4

1

+3V

05

EC6

EC6

*0.1U/10V_4

*0.1U/10V_4

of

of

of

542Thursday, December 24, 2009

542Thursday, December 24, 2009

542Thursday, December 24, 2009

+1.1V+1.5VSUS

1A

1A

1A

5

4

3

2

1

+1.5VSUS

CN23A

MEM_MA_ADD[0..15]4

D D

MEM_MA_BANK[0..2]4

MEM_MA0_CS#04

MEM_MA0_CS#14

MEM_MA_CLK5_P4

MEM_MA_CLK5_N4

MEM_MA_CLK4_P4

MEM_MA_CLK4_N4

MEM_MA_CKE04

MEM_MA_CKE14

MEM_MA_CAS#4

MEM_MA_RAS#4

MEM_MA_WE#4

C C

MEM_MA_DM[0..7]4

B B

PCLK_SMB7,13,33

PDAT_SMB7,13,33

MEM_MA0_ODT04

MEM_MA0_ODT14

MEM_MA_DQS0_P4

MEM_MA_DQS1_P4

MEM_MA_DQS2_P4

MEM_MA_DQS3_P4

MEM_MA_DQS4_P4

MEM_MA_DQS5_P4

MEM_MA_DQS6_P4

MEM_MA_DQS7_P4

MEM_MA_DQS0_N4

MEM_MA_DQS1_N4

MEM_MA_DQS2_N4

MEM_MA_DQS3_N4

MEM_MA_DQS4_N4

MEM_MA_DQS5_N4

MEM_MA_DQS6_N4

MEM_MA_DQS7_N4

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

PCLK_SMB

PDAT_SMB

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

CN23A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3-DIMM1

DDR3-DIMM1

H=5.2 footprint: "ddr-c-2013289-204p"

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

(204P)

(204P)

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

MEM_MA_DATA0

5

MEM_MA_DATA1

7

MEM_MA_DATA2

15

MEM_MA_DATA3

17

MEM_MA_DATA4

4

MEM_MA_DATA5

6

MEM_MA_DATA6

16

MEM_MA_DATA7

18

MEM_MA_DATA8

21

MEM_MA_DATA9

23

MEM_MA_DATA10

33

MEM_MA_DATA11

35

MEM_MA_DATA12

22

MEM_MA_DATA13

24

MEM_MA_DATA14

34

MEM_MA_DATA15

36

MEM_MA_DATA16

39

MEM_MA_DATA17

41

MEM_MA_DATA18

51

MEM_MA_DATA19

53

MEM_MA_DATA20

40

MEM_MA_DATA21

42

MEM_MA_DATA22

50

MEM_MA_DATA23

52

MEM_MA_DATA24

57

MEM_MA_DATA25

59

MEM_MA_DATA26

67

MEM_MA_DATA27

69

MEM_MA_DATA28

56

MEM_MA_DATA29

58

MEM_MA_DATA30

68

MEM_MA_DATA31

70

MEM_MA_DATA32

129

MEM_MA_DATA33

131

MEM_MA_DATA34

141

MEM_MA_DATA35

143

MEM_MA_DATA36

130

MEM_MA_DATA37

132

MEM_MA_DATA38

140

MEM_MA_DATA39

142

MEM_MA_DATA40

147

MEM_MA_DATA41

149

MEM_MA_DATA42

157

MEM_MA_DATA43

159

MEM_MA_DATA44

146

MEM_MA_DATA45

148

MEM_MA_DATA46

158

MEM_MA_DATA47

160

MEM_MA_DATA48

163

MEM_MA_DATA49

165

MEM_MA_DATA50

175

MEM_MA_DATA51

177

MEM_MA_DATA52

164

MEM_MA_DATA53

166

MEM_MA_DATA54

174

MEM_MA_DATA55

176

MEM_MA_DATA56

181

MEM_MA_DATA57

183

MEM_MA_DATA58

191

MEM_MA_DATA59

193

MEM_MA_DATA60

180

MEM_MA_DATA61

182

MEM_MA_DATA62

192

MEM_MA_DATA63

194

SO-DIMM BYPASS PLACEMENT :

3ODFHWKHVH&DSVQHDU6R'LPP

1R9LDV%HWZHHQWKH7UDFHRI3,1WR&$3

+1.5VSUS

DE-COUPLING FOR DIMM1(ONE CAP PER POWER PIN)

SI , add C226 from EMI suggest

MEM_MA_DATA[0..63] 4

+VREF_DQ7

+VREF_CA_A

MEM_MA_EVENT#14

MEM_MA_RESET#4

C413

C413

1000P/50V_4

1000P/50V_4

T12T12

+1.5VSUS

C603

C603

1000P/50V_4

1000P/50V_4

R169

R169

1K/F_4

1K/F_4

R158

R158

1K/F_4

1K/F_4

+3V

MEM_MA_TEST

MEM_MA_RESET#

+VREF_DQ

C412

C412

1n/50V_4

1n/50V_4

CN23B

CN23B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

DDR3-DIMM1

DDR3-DIMM1

+3VPCU

52

3

+

+

4

-

-

R179 0_4R179 0_4

R182 *0_4R182 *0_4

R159 *0_4R159 *0_4

C421

C421

.1U/10V_4

.1U/10V_4

U11

U11

1

OPA343NA/3K

OPA343NA/3K

(204P)

(204P)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

R160 10_4R160 10_4

1 2

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

+0.75V_DDR_VTT

Place close to DIMMs

C415

C415

.1U/10V_4

.1U/10V_4

R161

R161

C414

10K/F_4

10K/F_4

C414

0.01U/16V_4

0.01U/16V_4

+VREF_DQ

06

C142

C226

C153

C635

C635

C606

C606

C129

C651

C651

.1U/10V_4

.1U/10V_4

.1U/10V_4

.1U/10V_4

A A

+3V

C39

C39

1U/6.3V_4

1U/6.3V_4

C40

C40

*.1U/10V_4

*.1U/10V_4

5

.1U/10V_4

.1U/10V_4

+0.75V_DDR_VTT

C31

C31

4.7U/6.3V_6

4.7U/6.3V_6

C129

.1U/10V_4

.1U/10V_4

C34

C34

*22U/6.3V_8

*22U/6.3V_8

C199

C199

.1U/10V_4

.1U/10V_4

C153

.1U/10V_4

.1U/10V_4

C609

C609

*.1U/10V_4

*.1U/10V_4

C642

C642

*.1U/10V_4

*.1U/10V_4

DE-COUPLING FOR DIMM1

+0.75V_DDR_VTT

C35 *.1U/10V_4C35 *.1U/10V_4

C33 .1U/10V_4C33 .1U/10V_4

+1.5VSUS

4

C615

C615

*.1U/10V_4

*.1U/10V_4

+1.5VSUS

C226

.1U/10V_4

.1U/10V_4

C100

C100

10U/6.3V_8

10U/6.3V_8

C136

C136

10U/6.3V_8

10U/6.3V_8

C142

C168

C168

.1U/10V_4

.1U/10V_4

*.1U/10V_4

*.1U/10V_4

SI , remove C100 , C136

. add C100 , C136 C843

Reserve C901

C843

C843

10U/6.3V_8

10U/6.3V_8

PV,add from EMI suggestion

DDR_VTTREF4,7,37

12

+

C901

+

C901

*150u_6.3V_3528

*150u_6.3V_3528

3

+VREF_CA_A

R347 *0_4/SR347 *0_4/S

PV,change

to short pad

VREF_CA_A

+1.5VSUS

R348

R348

*2K/F_4

*2K/F_4

R349

R349

*2K/F_4

*2K/F_4

2

352-(&7$;

352-(&7$;

352-(&7$;

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

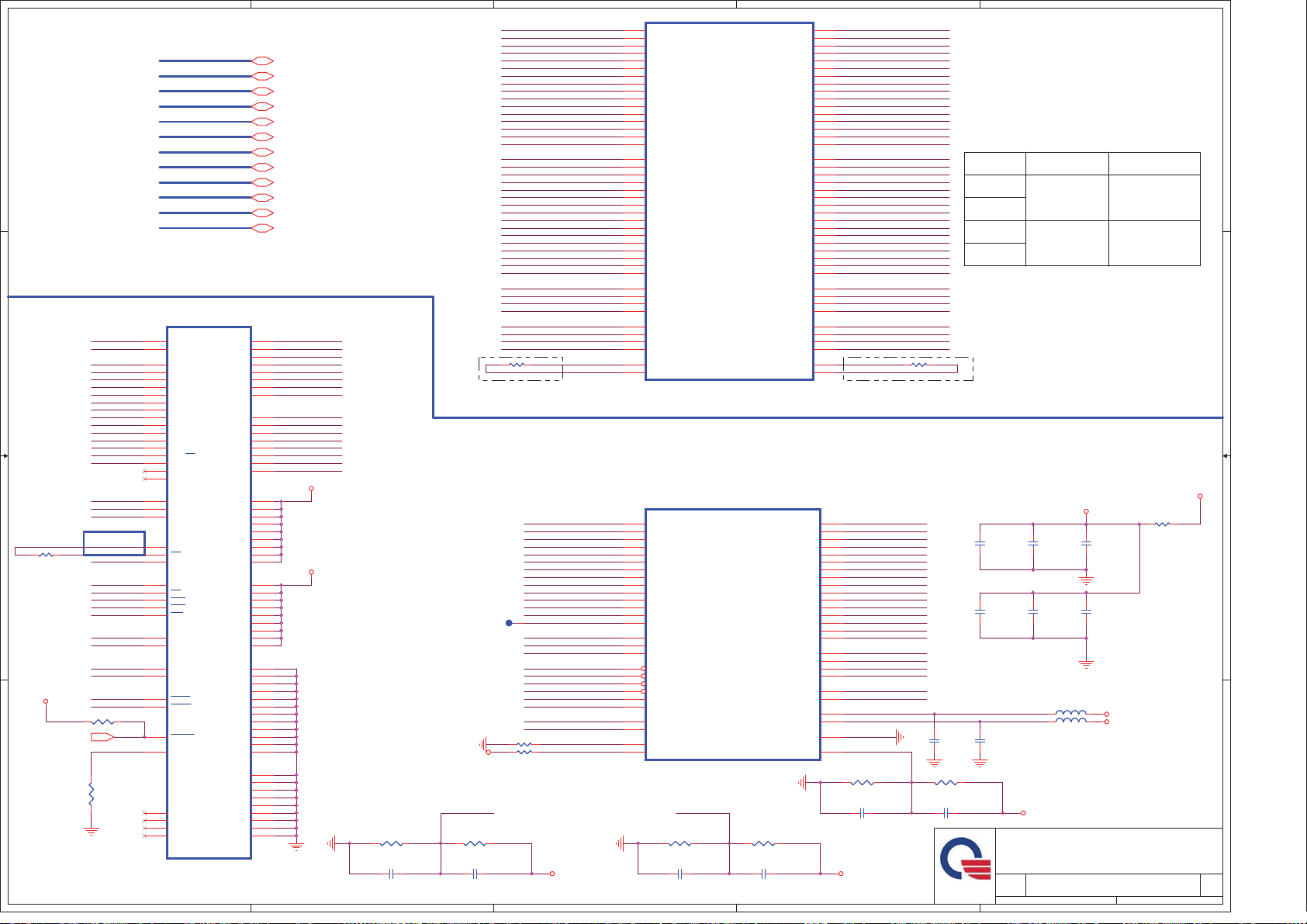

DDR3 SODIMMS: A/B CHANNEL

DDR3 SODIMMS: A/B CHANNEL

1%5'

1%5'

1%5'

DDR3 SODIMMS: A/B CHANNEL

Date: Sheet

Date: Sheet

Date: Sheet

1

1A

1A

642Thursday, December 24, 2009

642Thursday, December 24, 2009

642Thursday, December 24, 2009

1A

of

of

of

5

4

3

2

1

07

MEM_MB_TEST

MEM_MB_RESET#

C112

C112

1000P/50V_4

1000P/50V_4

+1.5VSUS

+3V

+VREF_DQ

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

199

77

122

125

198

30

1

126

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

CN24B

CN24B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDDSPD

NC1

NC2

NCTEST

EVENT#

RESET#

VREF_DQ

VREF_CA

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

DDR3-DIMM2

DDR3-DIMM2

(204P)

(204P)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

+0.75V_DDR_VTT

CN24A

MEM_MB_ADD[0..15]4

D D

MEM_MB_BANK[0..2]4

+3V

R335

R335

4.7K_4

4.7K_4

DIM2_SA0 DIM2_SA0

C C

B B

MEM_MB0_CS#04

MEM_MB0_CS#14

MEM_MB_CLK5_P4

MEM_MB_CLK5_N4

MEM_MB_CLK4_P4

MEM_MB_CLK4_N4

MEM_MB_CKE04

MEM_MB_CKE14

MEM_MB_CAS#4

MEM_MB_RAS#4

MEM_MB_WE#4

PCLK_SMB6,13,33

PDAT_SMB6,13,33

MEM_MB0_ODT04

MEM_MB0_ODT14

MEM_MB_DM[0..7]4

MEM_MB_DQS0_P4

MEM_MB_DQS1_P4

MEM_MB_DQS2_P4

MEM_MB_DQS3_P4

MEM_MB_DQS4_P4

MEM_MB_DQS5_P4

MEM_MB_DQS6_P4

MEM_MB_DQS7_P4

MEM_MB_DQS0_N4

MEM_MB_DQS1_N4

MEM_MB_DQS2_N4

MEM_MB_DQS3_N4

MEM_MB_DQS4_N4

MEM_MB_DQS5_N4

MEM_MB_DQS6_N4

MEM_MB_DQS7_N4

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

PCLK_SMB

PDAT_SMB

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

CN24A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3-DIMM2

DDR3-DIMM2

H=9.2 footprint: "ddr-c-2013310-204p-1"

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

(204P)

(204P)

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

MEM_MB_DATA0

5

MEM_MB_DATA1

7

MEM_MB_DATA2

15

MEM_MB_DATA3

17

MEM_MB_DATA4

4

MEM_MB_DATA5

6

MEM_MB_DATA6

16

MEM_MB_DATA7

18

MEM_MB_DATA8

21

MEM_MB_DATA9

23

MEM_MB_DATA10

33

MEM_MB_DATA11

35

MEM_MB_DATA12

22

MEM_MB_DATA13

24

MEM_MB_DATA14

34

MEM_MB_DATA15

36

MEM_MB_DATA16

39

MEM_MB_DATA17

41

MEM_MB_DATA18

51

MEM_MB_DATA19

53

MEM_MB_DATA20

40

MEM_MB_DATA21

42

MEM_MB_DATA22

50

MEM_MB_DATA23

52

MEM_MB_DATA24

57

MEM_MB_DATA25

59

MEM_MB_DATA26

67

MEM_MB_DATA27

69

MEM_MB_DATA28

56

MEM_MB_DATA29

58

MEM_MB_DATA30

68

MEM_MB_DATA31

70

MEM_MB_DATA32

129

MEM_MB_DATA33

131

MEM_MB_DATA34

141

MEM_MB_DATA35

143

MEM_MB_DATA36

130

MEM_MB_DATA37

132

MEM_MB_DATA38

140

MEM_MB_DATA39

142

MEM_MB_DATA40

147

MEM_MB_DATA41

149

MEM_MB_DATA42

157

MEM_MB_DATA43

159

MEM_MB_DATA44

146

MEM_MB_DATA45

148

MEM_MB_DATA46

158

MEM_MB_DATA47

160

MEM_MB_DATA48

163

MEM_MB_DATA49

165

MEM_MB_DATA50

175

MEM_MB_DATA51

177

MEM_MB_DATA52

164

MEM_MB_DATA53

166

MEM_MB_DATA54

174

MEM_MB_DATA55

176

MEM_MB_DATA56

181

MEM_MB_DATA57

183

MEM_MB_DATA58

191

MEM_MB_DATA59

193

MEM_MB_DATA60

180

MEM_MB_DATA61

182

MEM_MB_DATA62

192

MEM_MB_DATA63

194

MEM_MB_DATA[0..63] 4

+VREF_DQ6

+VREF_CA_B

MEM_MB_EVENT#14

MEM_MB_RESET#4

C395

C395

1000P/50V_4

1000P/50V_4

T11T11

SO-DIMM BYPASS PLACEMENT :

3ODFHWKHVH&DSVQHDU6R'LPP

1R9LDV%HWZHHQWKH7UDFHRI3,1WR&$3

+1.5VSUS

A A

+3V +0.75V_DDR_VTT +0.75V_DDR_VTT

1U/6.3V_4

1U/6.3V_4

DE-COUPLING FOR DIMM2(ONE CAP PER POWER PIN)

C128

C197

C197

.1U/10V_4

.1U/10V_4

C151

C151

.1U/10V_4

.1U/10V_4

C127

C127

.1U/10V_4

.1U/10V_4

C198

C198

.1U/10V_4

.1U/10V_4

C152

C152

.1U/10V_4

.1U/10V_4

C128

.1U/10V_4

.1U/10V_4

C229

C229

*.1U/10V_4

*.1U/10V_4

DE-COUPLING FOR DIMM2

C32

C37

C36

C36

C37

*.1U/10V_4

*.1U/10V_4

C32

4.7U/6.3V_6

4.7U/6.3V_6

5

C43

C43

*22U/6.3V_8

*22U/6.3V_8

C30 *.1U/10V_4C30 *.1U/10V_4

C38 .1U/10V_4C38 .1U/10V_4

C166

C166

*.1U/10V_4

*.1U/10V_4

+1.5VSUS

4

C140

C140

*.1U/10V_4

*.1U/10V_4

+1.5VSUS

C225

C225

*.1U/10V_4

*.1U/10V_4

C845

C845

10U/6.3V_8

10U/6.3V_8

C167

C167

*.1U/10V_4

*.1U/10V_4

C846

C846

10U/6.3V_8

10U/6.3V_8

C141

C141

*.1U/10V_4

*.1U/10V_4

SI , remove C165 , C236

add C845 , C846 ,C844

Reserve C902

12

+

C902

+

C844

C844

10U/6.3V_8

10U/6.3V_8

C902

*150u_6.3V_3528

*150u_6.3V_3528

+1.5VSUS

+VREF_CA_B

DDR_VTTREF4,6,37

3

R88 *0_4/SR88 *0_4/S

PV,change

to short pad

+VREF_CA_B

R99

R99

*2K/F_4

*2K/F_4

R96

R96

*2K/F_4

*2K/F_4

1%5'

1%5'

2

1%5'

352-(&7$;

352-(&7$;

352-(&7$;

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

4XDQWD&RPSXWHU,QF

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

DDR3 SODIMMS TERMINATIONS

DDR3 SODIMMS TERMINATIONS

DDR3 SODIMMS TERMINATIONS

Date: Sheet

Date: Sheet

Date: Sheet

1

742Thursday, December 24, 2009

742Thursday, December 24, 2009

742Thursday, December 24, 2009

of

of

of

1A

1A

1A

5

HT_CPU_NB_CAD_H[15..0]

HT_CPU_NB_CAD_L[15..0]

HT_CPU_NB_CLK_H[1..0]

HT_CPU_NB_CLK_L[1..0]

D D

SPM_VREF1

C C

SI,exchange

net name

R95 *100_4R95 *100_4

B B

+1.5V_MEM_VDDQ

SP_DDR3_RST#13

A A

SPM_VREF2

SPM_A0

SPM_A1

SPM_A2

SPM_A3

SPM_A4

SPM_A5

SPM_A6

SPM_A7

SPM_A8

SPM_A9

SPM_A10

SPM_A11

SPM_A12

SPM_A13

SPM_BA0

SPM_BA1

SPM_BA2

SPM_CLKP

SPM_CLKN

SPM_CKE

SPM_ODT

SPM_CS#

SPM_RAS#

SPM_CAS#

SPM_WE#

SPM_DQS0P

SPM_DQS1P

SPM_DM0

SPM_DM1

SPM_DQS0N

SPM_DQS1N

R343 *10K/F_4R343 *10K/F_4

VMA_ZQ2

R91

R91

*243/F_4

*243/F_4

HT_CPU_NB_CTL_H[1..0]

HT_CPU_NB_CTL_L[1..0]

HT_NB_CPU_CAD_H[15..0]

HT_NB_CPU_CAD_L[15..0]

HT_NB_CPU_CLK_H[1..0]

HT_NB_CPU_CLK_L[1..0]

HT_NB_CPU_CTL_H[1..0]

HT_NB_CPU_CTL_L[1..0]

U18

U18

M9

H2

N4

P8

P4

N3

P9

P3

R9

R3

T9

R4

L8

R8

N8

T4

T8

M8

M3

N9

M4

J8

K8

K10

K2

L3

J4

K4

L4

F4

C8

E8

D4

G4

B8

T3

L9

J2

L2

J10

L10

*H5TQ1G63AFR-14C

*H5TQ1G63AFR-14C

5

VREFCA

VREFDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC

A13

A14

A15

BA0

BA1

BA2

CK

CK

CKE

ODT

CS

RAS

CAS

WE

DQSL

DQSU

DML

DMU

DQSL

DQSU

RESET

ZQ

NC#J2

NC#L2

NC#J10

NC#L10

100-BALL

100-BALL

SDRAM DDR3

SDRAM DDR3

VDD#B3

VDD#D10

VDD#G8

VDD#K3

VDD#K9

VDD#N2

VDD#N10

VDD#R2

VDD#R10

VDDQ#A2

VDDQ#A9

VDDQ#C2

VDDQ#C10

VDDQ#D3

VDDQ#E10

VDDQ#F2

VDDQ#H3

VDDQ#H10

VSS#A10

VSS#B4

VSS#E2

VSS#G9

VSS#J3

VSS#J9

VSS#M2

VSS#M10

VSS#P2

VSS#P10

VSS#T2

VSS#T10

VSSQ#B2

VSSQ#B10

VSSQ#D2

VSSQ#D9

VSSQ#E3

VSSQ#E9

VSSQ#F10

VSSQ#G2

VSSQ#G10

DQL0

DQL1

DQL2

DQL3

DQL4

DQL5

DQL6

DQL7

DQU0

DQU1

DQU2

DQU3

DQU4

DQU5

DQU6

DQU7

E4

F8

F3

F9

H4

H9

G3

H8

D8

C4

C9

C3

A8

A3

B9

A4

B3

D10

G8

K3

K9

N2

N10

R2

R10

A2

A9

C2

C10

D3

E10

F2

H3

H10

A10

B4

E2

G9

J3

J9

M2

M10

P2

P10

T2

T10

B2

B10

D2

D9

E3

E9

F10

G2

G10

HT_CPU_NB_CAD_H[15..0] 3

HT_CPU_NB_CAD_L[15..0] 3

HT_CPU_NB_CLK_H[1..0] 3

HT_CPU_NB_CLK_L[1..0] 3

HT_CPU_NB_CTL_H[1..0] 3

HT_CPU_NB_CTL_L[1..0] 3

HT_NB_CPU_CAD_H[15..0] 3

HT_NB_CPU_CAD_L[15..0] 3

HT_NB_CPU_CLK_H[1..0] 3

HT_NB_CPU_CLK_L[1..0] 3

HT_NB_CPU_CTL_H[1..0] 3

HT_NB_CPU_CTL_L[1..0] 3

SPM_DQ2

SPM_DQ1

SPM_DQ5

SPM_DQ3

SPM_DQ7

SPM_DQ0

SPM_DQ4

SPM_DQ6

SPM_DQ13

SPM_DQ8

SPM_DQ10

SPM_DQ12

SPM_DQ15

SPM_DQ11

SPM_DQ14

SPM_DQ9

+1.5V_MEM_VDDQ

+1.5V_MEM_VDDQ

4

C85 *0.1U/10V_4C85 *0.1U/10V_4

4

3

U22A

HT_CPU_NB_CAD_H0

HT_CPU_NB_CAD_L0

HT_CPU_NB_CAD_H1

HT_CPU_NB_CAD_L1

HT_CPU_NB_CAD_H2

HT_CPU_NB_CAD_L2

HT_CPU_NB_CAD_H3

HT_CPU_NB_CAD_L3

HT_CPU_NB_CAD_H4

HT_CPU_NB_CAD_L4

HT_CPU_NB_CAD_H5

HT_CPU_NB_CAD_L5

HT_CPU_NB_CAD_H6

HT_CPU_NB_CAD_L6

HT_CPU_NB_CAD_H7

HT_CPU_NB_CAD_L7

HT_CPU_NB_CAD_H8

HT_CPU_NB_CAD_L8

HT_CPU_NB_CAD_H9

HT_CPU_NB_CAD_L9

HT_CPU_NB_CAD_H10

HT_CPU_NB_CAD_L10

HT_CPU_NB_CAD_H11

HT_CPU_NB_CAD_L11

HT_CPU_NB_CAD_H12

HT_CPU_NB_CAD_L12

HT_CPU_NB_CAD_H13

HT_CPU_NB_CAD_L13

HT_CPU_NB_CAD_H14

HT_CPU_NB_CAD_L14

HT_CPU_NB_CAD_H15

HT_CPU_NB_CAD_L15

HT_CPU_NB_CLK_H0

HT_CPU_NB_CLK_L0

HT_CPU_NB_CLK_H1

HT_CPU_NB_CLK_L1

HT_CPU_NB_CTL_H0

HT_CPU_NB_CTL_L0

HT_CPU_NB_CTL_H1

HT_CPU_NB_CTL_L1

R412 301/F_4R412 301/F_4

HT_RXCALP

HT_RXCALN

Y25

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

AC24

AC25

AB25

AB24

AA24

AA25

Y22

Y23

W21

W20

V21

V20

U20

U21

U19

U18

T22

T23

AB23

AA22

M22

M23

R21

R20

C23

A24

U22A

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS880

RS880

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

This block is for UMA only , DIS can remove all component

U22D

U22D

SPM_A0

SPM_A1 SPM_DQ1

SPM_A2

SPM_A3

SPM_A4

SPM_A5

SPM_A6

SPM_A7

SPM_A8

SPM_A9

SPM_A10

SPM_A11

SPM_A12

SPM_A13

T21T21

SPM_BA0

SPM_BA1

SPM_BA2

SPM_RAS#

SPM_CAS#

SPM_WE#

SPM_CS#

SPM_CKE

SPM_ODT

SPM_CLKP

SPM_CLKN

R357 *40.2/F_4R357 *40.2/F_4

R352 *40.2/F_4R352 *40.2/F_4

+1.5V_MEM_VDDQ

SPM_VREF1 SPM_VREF2

R75 *1K/F_4R75 *1K/F_4 R100 *1K/F_4R100 *1K/F_4R73 *1K/F_4R73 *1K/F_4

C77 *0.1U/10V_4C77 *0.1U/10V_4

SPM_COMPP

SPM_COMPN

+1.5V_MEM_VDDQ +1.5V_MEM_VDDQ

AB12

AE16

V11

AE15

AA12

AB16

AB14

AD14

AD13

AD15

AC16

AE13

AC14

Y14

AD16

AE17

AD17

W12

Y12

AD18

AB13

AB18

V14

V15

W14

AE12

AD12

3

MEM_A0(NC)

MEM_A1(NC)

MEM_A2(NC)

MEM_A3(NC)

MEM_A4(NC)

MEM_A5(NC)

MEM_A6(NC)

MEM_A7(NC)

MEM_A8(NC)

MEM_A9(NC)

MEM_A10(NC)

MEM_A11(NC)

MEM_A12(NC)

MEM_A13(NC)

MEM_BA0(NC)

MEM_BA1(NC)

MEM_BA2(NC)

MEM_RASb(NC)

MEM_CASb(NC)

MEM_WEb(NC)

MEM_CSb(NC)

MEM_CKE(NC)

MEM_ODT(NC)

MEM_CKP(NC)

MEM_CKN(NC)

MEM_COMPP(NC)

MEM_COMPN(NC)

RS880

RS880

PAR 4 OF 6

PAR 4 OF 6

C121 *0.1U/10V_4C121 *0.1U/10V_4

MEM_DQ0/DVO_VSYNC(NC)

MEM_DQ1/DVO_HSYNC(NC)

MEM_DQ2/DVO_DE(NC)

MEM_DQ3/DVO_D0(NC)

MEM_DQ4(NC)

MEM_DQ5/DVO_D1(NC)

MEM_DQ6/DVO_D2(NC)

MEM_DQ7/DVO_D4(NC)

MEM_DQ8/DVO_D3(NC)

MEM_DQ9/DVO_D5(NC)

MEM_DQ10/DVO_D6(NC)

MEM_DQ11/DVO_D7(NC)

MEM_DQ12(NC)

MEM_DQ13/DVO_D9(NC)

MEM_DQ14/DVO_D10(NC)

MEM_DQ15/DVO_D11(NC)

MEM_DQS0P/DVO_IDCKP(NC)

MEM_DQS0N/DVO_IDCKN(NC)

MEM_DQS1P(NC)

MEM_DQS1N(NC)

MEM_DM0(NC)

MEM_DM1/DVO_D8(NC)

SBD_MEM/DVO_I/F

SBD_MEM/DVO_I/F

IOPLLVDD18(NC)

IOPLLVDD(NC)

IOPLLVSS(NC)

MEM_VREF(NC)

R101 *1K/F_4R101 *1K/F_4

C138 *0.1U/10V_4C138 *0.1U/10V_4

HT_NB_CPU_CAD_H0

D24

HT_NB_CPU_CAD_L0

D25

HT_NB_CPU_CAD_H1

E24

HT_NB_CPU_CAD_L1

E25

HT_NB_CPU_CAD_H2

F24

HT_NB_CPU_CAD_L2

F25

HT_NB_CPU_CAD_H3

F23

HT_NB_CPU_CAD_L3

F22

HT_NB_CPU_CAD_H4

H23

HT_NB_CPU_CAD_L4

H22

HT_NB_CPU_CAD_H5

J25

HT_NB_CPU_CAD_L5

J24

HT_NB_CPU_CAD_H6

K24

HT_NB_CPU_CAD_L6

K25

HT_NB_CPU_CAD_H7

K23

HT_NB_CPU_CAD_L7

K22

HT_NB_CPU_CAD_H8

F21

HT_NB_CPU_CAD_L8

G21

HT_NB_CPU_CAD_H9

G20

HT_NB_CPU_CAD_L9

H21

HT_NB_CPU_CAD_H10

J20

HT_NB_CPU_CAD_L10

J21

HT_NB_CPU_CAD_H11

J18

HT_NB_CPU_CAD_L11

K17

HT_NB_CPU_CAD_H12

L19

HT_NB_CPU_CAD_L12

J19

HT_NB_CPU_CAD_H13

M19

HT_NB_CPU_CAD_L13

L18

HT_NB_CPU_CAD_H14

M21

HT_NB_CPU_CAD_L14

P21

HT_NB_CPU_CAD_H15

P18

HT_NB_CPU_CAD_L15

M18

HT_NB_CPU_CLK_H0

H24

HT_NB_CPU_CLK_L0

H25

HT_NB_CPU_CLK_H1

L21

HT_NB_CPU_CLK_L1

L20

HT_NB_CPU_CTL_H0

M24

HT_NB_CPU_CTL_L0

M25

HT_NB_CPU_CTL_H1

P19

HT_NB_CPU_CTL_L1

R18

HT_TXCALP

B24

HT_TXCALN

B25

AA18

AA20

AA19

Y19

V17

AA17

AA15

Y15

AC20

AD19

AE22

AC18

AB20

AD22

AC22

AD21

Y17

W18

AD20

AE21

W17

AE19

+1.8V_IOPLLVDD18

AE23

+1.1V_IOPLLVDD

AE24

AD23

SPM_VREF

AE18

R356 *1K/F_4R356 *1K/F_4

C619 *0.1U/10V_4C619 *0.1U/10V_4

2

SPM_DQ0

SPM_DQ2

SPM_DQ3

SPM_DQ4

SPM_DQ5

SPM_DQ6

SPM_DQ7

SPM_DQ8

SPM_DQ9

SPM_DQ10

SPM_DQ11

SPM_DQ12

SPM_DQ13

SPM_DQ14

SPM_DQ15

SPM_DQS0P

SPM_DQS0N

SPM_DQS1P

SPM_DQS1N

SPM_DM0

SPM_DM1

2

R411 301/F_4R411 301/F_4

*2.2U/6.3V_6

*2.2U/6.3V_6

R355 *1K/F_4R355 *1K/F_4

C620 *0.1U/10V_4C620 *0.1U/10V_4

signals

HT_TXCALP

HT_TXCALN

HT_RXCALP

HT_RXCALN

40mils wdith or more

C86

C86

*1U/10V_4

*1U/10V_4

C84

C84

*0.1U/10V_4

*0.1U/10V_4

C630

C630

C146

C146

*2.2U/6.3V_6

*2.2U/6.3V_6

1%5'

1%5'

1%5'

1

08

RS880 RX880

R430

301 ohm 1%

R434

301 ohm 1%

+1.5V_MEM_VDDQ

C71

C71

*10U/6.3V_8

*10U/6.3V_8

C92

C92

*0.1U/10V_4

*0.1U/10V_4