Page 1

No part of this manual may be copied, transcribed, translated or reproduced in any manner or form

whatsoever, for commercial purposes, without obtaining prior written permission from Q-MAC

Electronics Pty Ltd. However, limited copying is permitted for private use providing authorship is

acknowledged.

© Copyright Q-MAC Electronics Pty Ltd, 2003.

142 Hasler Road

Osborne Park, WA 6017

PO Box 1334

Osborne Park Business Centre, WA 6916

AUSTRALIA

Australia: Phone 08 - 9242 2900, Fax 08 - 9242 3900

International: Phone +618 - 92242 2900, Fax +618 - 9242 3900

Print date: August 1996

Print date: February 1997

Print date: October 2000

Author: Rod Macduff

Literature Reference Number: TECH02C.PUB

Part Number: QM1021

First Edition

Second Edition

Third Edition

Additional Technical Support:

Note that additional technical support is available to Q-MAC Dealers under the “Dealer Support”

section of the Q-MAC website: www.qmac.com

. This site incorporates Technical Bulletins issued by

Q-MAC, plus Technical Notes and Instructions in relation to specif ic produ ct s.

- 1 -

Page 2

TABLE OF CONTENTS

Section 1 Warnings & advice

..............................................................................................4

Section 2 Introduction

........................................................................................................... 5

Section 3 Product specification

........................................................................................ 6

Section 4 Mechanical assembly

.........................................................................................7

Section 5 Functional overview

...........................................................................................8

Section 6 Block diagrams

Microprocessor..........................................................................................................11

Receiver/exciter.........................................................................................................12

Synthesizers...............................................................................................................13

Power amp & switching P.S.U..................................................................................14

Front panel.................................................................................................................10

Section 7 Circuit description

7.1 Front panel PCB...............................................................................................15

7.2 RXMP PCB ....................................................................................................16

7.3 PASW PCB ....................................................................................................21

Section 8 Tables & diagrams

Diagram 1. Serial link chain ....................................................................................25

Table 2.

Diagram 2. Superhet. mixing scheme......................................................................26

Diagram 3. HF-90 Rx gain distribution...................................................................26

Table 3. HF-90 Tx low pass filters......................................................................27

Table 4. HF-90 connector pinouts.......................................................................28

Diagram 4. Connector positions...............................................................................30

Table 1. HF-90 micro port allocations................................................................24

Section 9 Maintenance

9.2 Replacement of Microprocessor.......................................................................32

9.3 Radio alignment................................................................................................33

9.1 Disassembly & assembly..................................................................................31

Section 10 Fault finding

10.1 No tools fault finding......................................................................................36

Section 11 Diagnostic test sequence

11.2 Transmitter test sequence ...............................................................................43

11.1 Receiver test sequence....................................................................................39

- 2 -

Page 3

Section 12 Test point overlays

12.1 RXMP test point voltages...............................................................................45

HF-90 P.A. board alignment - position reference......................................................46

Section 13 Software overview

13.2 Routine description (not frequency hopping).................................................48

13.3 Software releases............................................................................................50

13.1 Program description........................................................................................47

Section 14 Hints & tips

14.2 Servicing warnings.........................................................................................52

14.1 Device removal...............................................................................................51

14.3 Servicing case histories...................................................................................53

Section 15 Parts List

15.1 Front panel PCB parts list (ISSUE N)............................................................60

15.2 RXMP PCB parts list (ISSUE V)...................................................................61

15.3 PASW PCB parts list (ISSUE Q)...................................................................67

Section 16 PCB overlays

Front panel top overlay - issue N (designators).........................................................72

Front panel top overlay - issue N (component values)..............................................73

RXMP top overlay - issue V (designators)................................................................74

RXMP top overlay - issue V (component values).....................................................75

PASW top overlay - issue Q (designators)................................................................76

PASW top overlay - issue Q (component values).....................................................77

Section 17 Schematic diagrams

HF-90 I.F. strip, micro section & synth (90003).......................................................80

HF-90 P.A. & power supply (90002)........................................................................81

HF-90 display (90000)...............................................................................................79

Section 18 External connectors

.........................................................................................82

Section 19 Device pinouts & codes

Device pinouts...........................................................................................................84

19.1 SMD capacitor codes......................................................................................85

- 3 -

Page 4

1. WARNINGS & ADVICE

1. On no account should the unit be connected directly to 110volt or 240volt AC mains

power. Serious damage or personal injury may result.

2. An approved 12volt or 24volt power supply or battery should be used. The supply

should be capable of sourcing peak currents up to 10ampere. Failure to comply with

this rating will result in severe distortion on transmissions. Please note that some

power supplies labeled as 10ampere peak are not adequate as the voltage collapses

towards the peaks.

3. Use only the approved power cable for installation. Use of thinner conductors or

extensions will result in severe distortion on transmissions.

!

!

4. The system performance is generally only as good as the antenna and ground system

will allow. If unbalanced antennas are being used eg. whips, end-fed broadbands etc,

then it is vital to obtain a good low impedance ground connection either to a vehicle

body, a moist patch of ground or a metal fence with rust removed at the point of

connection.

5. The HF-90 is extremely small. When transmitting, the heatsink and extrusion may get

very hot. Under some circumstances it may be possible to get burned by touching the

heatsink. The radio has been designed and tested to cope with elevated temperatures.

However the user should endeavour to allow free circulation of air around the radio.

6. In order to achieve the high output power, an internal power convertor is used to

supply +55volt to the final amplifier on transmit. The energy stored by this supply is

quite high (2.2joules) and it is wise to WAIT FOR A FULL MINUTE after

transmitting prior to doing any service work on the PASW printed circuit board.

7. Radio Frequency Field Exposure: The HF-90 Packages generate high radio frequency

fields. Their antennas are marked with a safe working distance in accordance with

required Standards. This should be observed.

8. This device complies with Part 90 of the FCC Rules. Operation is subject to the

condition that this device does not cause harmful interference.

- 4 -

Page 5

2. INTRODUCTION

The HF-90 Compact Transceiver breaks new ground in the following areas:

Size: The volume of the transceiver is approximately one litre. This is less than a tenth of

comparable products. On initial inspection it is often mistaken for a VHF/UHF set.

Weight: At 1 kilogram, the HF-90 is a quarter of the weight of products with a similar

specification.

Ease of use: The HF-90 has quite deliberately been kept simple so that persons unfamiliar

with HF communications may immediately pick it up and use it.

Low cost: The transceiver has been designed using state of the art SMD technology.

Components from cellular telephony, satellite television, and personal computers have been

used wherever possible to keep the cost at a minimum. Also, wherever possible,

functionality has been implemented in software rather than hardware.

Ruggedness: Use of a heavily ribbed aluminium extrusion confers great strength to the

HF-90. Stainless steel handles protect all front panel controls. A ribbed rear heatsink

protects the rear connectors.

Reliability: Use of SMD technology and the delegation of functionality to software has led

to simplicity of design which translates to high reliability. Unreliable parts such as

potentiometers and wiring looms are avoided. All internal connectors have gold to gold

mating surfaces.

Serviceability: The HF-90 was designed with serviceability as a top priority. The radio

consists of three PCBs, all of which plug together. Only four screws need be removed to

access the main PCBs. These PCBs plug together as a ‘sandwich’ with all the essential

components and nodes easily probeable while the radio is operating, without the use of

extenders. All power transistors are easily accessed and use single screw fixing.

Minimised inventory: The design of the HF-90 was implemented with the minimum

number of different types of components. Thus spares inventory is reduced.

Versatility: The high performance and small size allows the HF-90 to be used in portable,

mobile or fixed configurations. The wide power supply range (12 to 24volt) makes it

particularly attractive in multi-role applications.

Receiver performance: Excellent receive sensitivity is combined with a large dynamic

range through the use of four GaAs FETs in the front end mixer.

Transmit ter performance: A very high power to weight ratio and extreme RF ruggedness

is obtained through the use of 500volt MOS FETs in the power amplifier.

Selcall performance: A sophisticated digital signal processing algorithm is capable of

extracting very weak calls in the presence of noise. Successful decodes at down to -132dBm

have been observed.

- 5 -

Page 6

3. PRODUCT SPECIFICATION

General

Frequency range: 2 ! 30MHz

Modes of operation: USB, LSB (J3E)

Number of channels: 255

Channel resolution: 100Hz

Supply voltage: 12 ! 24V DC nominal

Power consumption:

- Transmit: 2A! 10A

- Receive: 310mA

Frequency stability: ± 1.5ppm

Antenna impedance:

Antenna connector: BNC

Handsets: Speaker microphone

Selcall system: Based on CCIR 493-4

Programming: IBM PC 4800,8,1,N

BITE: Micro, Rx, Tx tests

Environmental

Operating temperature: -30ºC ! 60ºC

Storage temperature: -30ºC ! 80ºC

Humidity: 95% non-condensing

Environmental rating: IP54

Physical characteri st ics

Dimensions (mm): 112(W) x 47(H) x 220(D)

Weight: 1kg (HF-90 only)

Construction: All metal extruded sleeve

Finish: Black anodized aluminium

CW (optional)

Hopping (optional)

AM (Rx only), FSK

(subject to pre-set power

output)

50Ω

DTMF microphone

& telephone handset

(Australian Standard)

with front panel and

heatsink

Transmitter

Power output: 50Wat t PEP

Duty cycle: Normal speech or data

Unwanted sideband: Better than -45dB

Carrier suppression: Better than -50dB

Harmonic suppression: Better than –60dB

Spurious emissions: Better than –60dB

Noise suppression: Better than -35dB

Distortion: Less than 5% @ 70% PEP

Audio response: 270Hz ! 2800Hz

Microphone: Electret insert

Tune: >20W radiated @ +1000Hz

Load protection: ALC

Receiver

Sensitivity: 0.25µV for 10dB S+N/N

Selectivity: 2.3 kHz @ -6dB

Image rejection: Better than -50dB

Intermodulation: Better than -70dB

3rd order intercept: +20dBm (GaAs FET

Blocking: Better than -70dB

Spurious response: Better than -60dB

IF rejection: Better than -60dB

Intermediate freq’s: 83.16MHz, 455kHz

AGC: Less than 3dB

Clarifier range: ± 250Hz

Audio response: 270Hz ! 2800Hz

Audio output: 2Watt

Audio load impedance:

Audio distortion: Less than 5% @ 1W

(with fan option)

6kHz @ -60dB

mixer)

from 3µV ! 1V

8Ω

Specifications are subject to change without notice

- 6 -

Page 7

4. MECHANICAL ASSEMBLY

Radio construction

The radio shell comprises a 2.5mm aluminium front plate complete with black stainless steel

handles, a 160mm long key-ribbed sleeve extrusion and a 10-fin extruded rear heatsink. This

provides a simple and strong housing for the radio. Four M3x12 screws are used to secure

both front and rear panels. The display PCB is secured to the metal front-plate by the fixing

nuts of three front panel parts. This allows for simple removal. The two main PCBs pug into

each other as a ‘sandwich’, and the whole assembly slides into the extruded sleeve on

keyways. The rear heatsink is part of the PASW board assembly. Rubber gaskets on the

front and rear mating surfaces give some water resistance.

Front panel

The front panel allows manual control of all the radio functions. This is achieved by six

elastomer keys, an incremental shaft encoder (volume) and a toggle switch for power

activation. A high efficiency 6-digit 7-segment LED display indicates the channel number

on receive and frequency on transmit. An 8-pole microphone socket provides all the external

interface requirements for m icrophones , headphon es, D TMF keyp ad, and comput er inte rf ace.

The front panel can be removed by undoing the four screws on the front of the radio and

pulling gently on the handles. It can be further disassembled by simply undoing the two hex

grub screws on the volume knob and unscrewing the volume, on/off switch and microphone

socket n uts. The elastomer ke ys and f ibregl ass key se parat or shoul d be left i n the keyho les.

The gold keyp ad s ar e pl ac ed on a sma ll su b-bo ar d a bove th e di s pla y PCB . S ix p ins hol d t his

small keypad in place.

RXMP board

This board has no direct connections to the outside world. It mates both mechanically and

electrically with the PASW board via four 10-way connectors. It also mates via two of the

10-way connectors with the display PCB. There is one unused 10-way pin field for test use.

When mated with the PASW board it slides into the extruded sleeve on keyways.

PASW board

The PASW board incorporates the rear heatsink extrusion as part of its assembly. The

heatsink contains the BNC antenna connector and the 4-pole power receptacle. The heatsink

is attached to the PCB by virtue of the heavy connections to the power receptacle and the 18

power transistor leads. The PASW board mates with the RXMP board via four 10-way

connectors but has no connection to the display PCB.

- 7 -

Page 8

Front panel

Refer to the block diagram (FRONT PANEL) in Section 6 of this manual.

The only electronic parts of significance on the display PCB belong to the display register

and multiplexor. All other parts merely route signals from the keys, microphone socket,

volume encoder etc to the main two PCBs via a pair of 10-way connectors.

RXMP PCB

This board incorporates three distinct functional blocks, the Microprocessor, Receiver/

Exciter and Synthesizer.

Microprocessor

Refer to the block diagram (MICROPROCESSOR) in Section 6 of this manual.

This section contains the 8-bit microcontroller along with its address latch, battery backed

RAM, data memory and glue logic. For simpl icity, communi cation wit h peripheral devices

is via a serial 3-wire bus. This bus sends data to the display, volume DAC, transmit low pass

filters and power control. A separate data line feeds the synthesizer. Computer I/O and

Selcall data in, also share the same serial ports. The keypad is read via a 5-wire matrix and

the volume encoder has a 2-line quadrature input plus interrupt. A DTMF decoder handles

tones from the microphone and utilises a memory mapped interface.

Receiver/Exciter

Refer to the block diagram (RECEIVER/EXCITER) in Section 6 of this manual.

The receiver/exciter section is configured as a double superhet with first IF at 83.160MHz

and second IF at 455kHz. The same circuit is used on receive and transmit apart from the

second IF processor. Relays re-route the signal on transmit through the first IF. The other

circuit elements are bi-directional. LO1 and LO2 are synthesizer derived. The carrier

insertion oscillator at 453.6kHz or 456.4kHz is counted down from the LSB or USB crystal.

Synthesizer

Refer to the block diagram (SYNTHESIZER) in Section 6 of this manual.

The first local oscillator uses a high level push-pull circuit. It covers a 30MHz span and is

controlled by one half of the frequency synthesizer running at a high comparison frequency

to obtain low phase noise. The second local oscillator is a simple single ended unit covering

a 20kHz span, controlled by the other half of the frequency synthesizer. The Selcall decoder

uses a PLL and data slicer to demodulate the FSK signal.

PASW PCB

Refer to the block diagram (POWER AMP & SWITCHING PSU) in Section 6 of this manual.

The PASW board contains the main power supplies and the transmitter power train. A

shielded +5volt switching power supply provides power for most of the RX and logic and a

+10volt linear supply is also provided. On transmit a +50volt switching power supply is

active. The transmit power train comprises two RF Op-Amps, the first of which is ALC

controlled, then a driver stage and final amplifier, both of which use MOS FETs. One out of

six harmonic filters is selected by a darlington driver.

5. FUNCTIONAL OVERVIEW

- 8 -

Page 9

6. BLOCK DIAGRAMS

Please refer to the following pages for block diagrams .....

- 9 -

Page 10

REFER BLOCK DIAGRAM

“HF-90 RADIO BLOCK DIAGRAM - FRONT PANEL”

IN FILE NAMED “HF90BFP.xxx”

- 10 -

Page 11

REFER BLOCK DIAGRAM

“HF-90 RADIO BLOCK DIAGRAM - MICROPROCESSOR”

IN FILE NAMED “HF90BMCP.xxx”

- 11 -

Page 12

REFER BLOCK DIAGRAM

“HF-90 RADIO BLOCK DIAGRAM RECEIVER / EXCITER”

IN FILE NAMED “HF90BRXE.xxx”

- 12 -

Page 13

REFER BLOCK DIAGRAM

“HF-90 RADIO BLOCK DIAGRAM - SYNTHESIZERS”

IN FILE NAMED “QMAPAPS.xxx”

- 13 -

Page 14

REFER BLOCK DIAGRAM

“HF-90 RADIO BLOCK DIAGRAM POWER

AMP & SWITCHING P.S.U.”

IN FILE NAMED “HF90BPAP.xxx”

- 14 -

Page 15

7. CIRCUIT DESCRIPTION

7.1 Front panel PCB

Refer to the schematic diagram (HF-90 DISPLAY 90000) in Section 17 of this manual.

The front panel PCB contains a 6-digit 7-segment LED display, 6-button keypad matrix, on/

off switch, volume control and microphone socket. It measures 35mm x 95mm and contains

eight integrated circuits.

Display data is contained within a 6-byte serial shift register (U1 - U6) and the display is

refreshed at one sixth of the 7kHz clock rate by the multiplex counter (U8 & U25).

The displ ay is updated from t he microproc essor via a 3-wire serial interfa ce (TOC, SCK &

DIS). A fourth line DSIRO allows the microprocessor to check for serial link integrity.

The 7-segment display sections (U18 - U23) are extremely compact and efficient resulting in

excellent readability and endurance.

An incremental shaft encoder (VR1) controls the volume level on the Standard and

Advanced Model HF-90 and allows a flexible user interface for possible future options. It

gives 24 detents (clicks) per revolution.

The computer programming interface utilises D1 and Q2 to achieve compatibility with IBM

PC Clone RS232C ports, operating at 4800N81 (4800 baud, no parity, eight data, one stop).

A simple auxiliary PCB contains the 5-line, 6-button keypad matrix. TR and BR (top and

bottom row) carry negative going key scan pulses at 250Hz repetition rate. RCL, MCL and

LCL (right, middle and bottom column) are inputs allowing the key presses to be read by the

microprocessor.

The microphone socket allows use of an unbalanced electret microphone, telephone style

handset with PTT, a DTMF keypad and an RS232C programming link.

A single pole on/off switch activates the power relay on the PASW PCB (power amplifier

and switch mode power supply PCB), by switch closure to ground.

- 15 -

Page 16

7.2 RXMP PCB

Refer to the schematic diagram (HF-90 I.F. STRIP , MICRO SECTION & SYNTH. 90003) in Section

17 of this manual. Applies to RXMP boards of issue U and beyond.

The RXMP PCB is the heart of the radio and condenses a high degree of functionality into a

small board area.

The two main functional blocks on this board are the microprocessor and the receiver. Large

sections of the receiver are re-used on transmit to generate the drive for the PASW PCB. This

minimises unnecessary replication of circuitry. The RXMP PCB measures 100mm x 147mm

and contains 30 integrated circuits.

Microprocessor architecture

A minimal number of components are used as a result of the following:

" Delegation of functionality to software, wherever possible.

" Extensive re-use of ports.

" Utilisation of a simple serial interface.

" Use of a microprocessor with embedded code and separate data memory.

The microprocessor core consists of the microprocessor (U1), the non-volatile data memory

(U2), and the low address latch (U3). D24 gates the battery backed RAM enabling it during

RAM reads and writes.

DTMF detector

The DTMF chip (U9) flags data valid on pin 14 when keys on the DTMF microphone are

pushed. The microprocessor activates the DTMFE line when it is ready to read the DTMF

code. The DTMF chip is memory mapped at address #8000H and diode D1 disables the

battery backed RAM when a DTMF read occurs.

A full table of microprocessor port allocations is shown in Table 1 (Section 8 of this manual).

Serial links

There are two separate serial data paths which share a common data and clock signal (TOC

and SCK) but have different enable lines (SYN and DIS).

One of these serial links has been described in Section 7.1 (Front panel PCB), however it

services other registers besides the display. It loops back onto the RXMP PCB and controls

the miscellaneous register and volume control. It then loops through the PASW PCB where

it controls the PA low pass filter selection and power selection. Finally, it loops back to the

microprocessor where it can be sampled to check the link.

The second serial data signal is the synthesizer loader. This is fed to U16 setting the

frequency of LO1 and LO2.

The display enable and clock are also used to increment the signal strength meter ramp

counter, which is active on every display write.

A hardware and software summary of these two serial links is contained in Diagram 1 and

Table 2, respectively (Section 8 of this manual).

- 16 -

Page 17

Interrupts

The microprocessor runs three interrupts:-

1. The incremental shaft encoder interrupt on INT1 (volume set).

2. An internal software interrupt on Timer 0, TICKINT which wakes up the

microprocessor from an idle state every 2ms (or 666µs in hop mode). This is the

‘heartbeat’ of the radio and it ticks at all times except during computer

communication.

3. An internal software interrupt on Timer 1, TIMER1INT which provides timing for all

tones generated by the radio on receive and transmit.

The RS232 serial I/O programming link is not run as an interrupt driven service. It is

operated as a scheduled polled service.

Although PTT input to the microprocessor is fed into pin INT0, the interrupt on this pin is

disabled and instead the pin is polled. It is also a PTT output.

Shaft encoder

Quadrature drives to the shaft encoder from QUAD1 and QUAD2 allow the detection of

turning direction and velocity, by line INT1. The change in volume is output via the serial

link to the shift register (U11) setting the gain DAC (U13).

Clarifier

The clarifier on receive is implemented entirely in software adjusting the synthesizer in 25Hz

increments over ±250Hz.

Receiver and synthesizers

The receiver architecture comprises a double conversion superheterodyne with intermediate

frequencies of 83.16MHz and 455kHz. Two high-side local oscillators (LO1 and LO2) mix

down to 83.16MHz and 455kHz respectively.

The local oscillators are controlled by a dual frequency synthesizer which allow coverage of

2 - 30MHz in 100Hz steps.

Mixing scheme

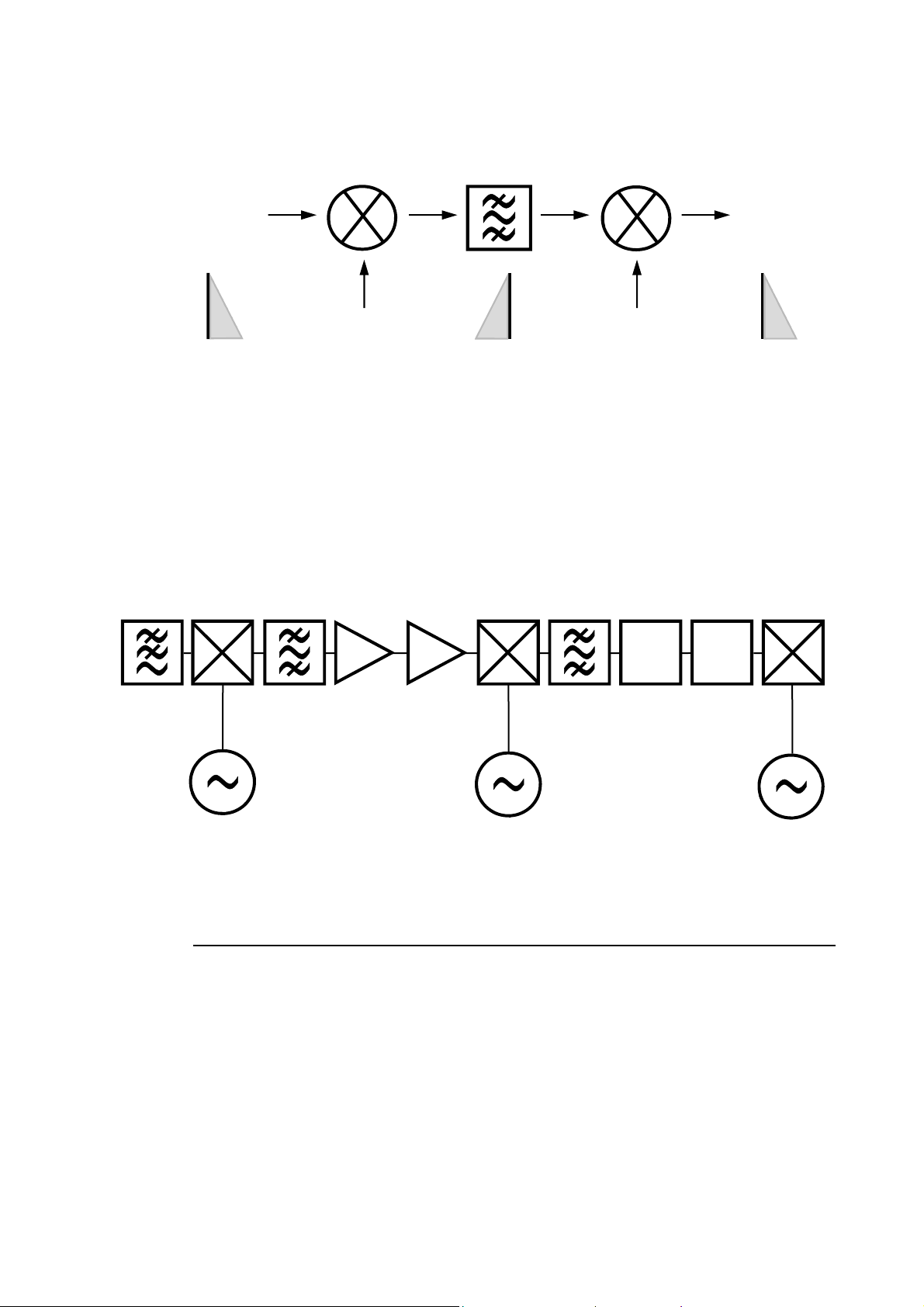

Diagram 2 (Section 8 of this manual) shows the HF-90 superheterodyne mixing scheme.

Synthesizer Part 1

Synthesizer Part 1 controls LO1. The synthesizer chip (U16) utilises an internal dual

modulus prescaler to obtain a high operating frequency (85 - 113MHz), along with a high

phase comparison frequency (47 - 202kHz). The synthesizer is designed for low phase noise

and the loop filter (R25, C96, C99) is optimized for low phase comparison sideband level.

The high comparison rate gives the synthesizer a very rapid lock time of 3ms. The nonlinear amplifier (Q10, Q14, Q15, Q16, Q22) linearises the overall system gain to maintain

consistent noise performance across the VCO span.

- 17 -

Page 18

LO1

LO1 is a high level (+13dBm) low phase noise VCO providing the injection source for Mixer

1. It employs push-pull JFETS (Q6, Q7) and an amplitude stabilisation circuit (D7, D8, Y1,

Y2, Y7, Y8). Fast inverters (U29 E and F) provide hard switching and load isolation.

Synthesizer Part 2

Synthesizer Part 2 (U16) employs a single chip synthesizer to stabilize the injection

frequency of LO2. It has an on-board prescaler and requires only the external loop filter

(C85, C77, R83, R4, C46). The frequency of LO2 is controlled in 200 100Hz steps over a

20kHz span.

LO2

LO2 employs a Vackar circuit with a very narrow span. It provides a +7dBm injection level

for Mixer 2 using a single JFET (Q8). A fast inverter (U30C) and a 3dB pad provide hard

switching and load isolation. Capacitor C212 is a 33p N470 type, to achieve temperature

compensation from -30ºC to +60ºC.

Front end

A 5-element elliptic low pass filter band limits the receiver input signal and suppresses

leakage from LO1 on transmit and receive.

A high-level GaAs FET mixer (Q1, Q2, Q3, Q4) provides a low loss, high 3IP performance

to obtain excellent sensitivity and dynamic range. This mixer incorporates proprietary

architecture. Being essentially a passive element, the mixer is reciprocal and operates in the

reverse direction in transmit mode. Diodes D14 and D27 provide front end protection.

First IF

The first IF chain comprises F1, Q5 & U21, with associated components. The active

components are switched in direction between receive and transmit by a relay pair (RL1 &

RL2). This ensures optimum IMD performance on both receive and transmit.

Saw filter

Selectivity with a bandwidth of 30kHz is provided by the first IF filter (F1). Use of a SAW

device allows very smooth passband performance with deep transmission zeros on the image

frequency of the second IF. The tank circuits associated with L5 and L6 provide impedance

matching for the filter which has a Zo of 800Ω.

Active devices (Q5 and U21) provide the AGC controlled gain in the first IF. The Op-Amp

(U20) stabilises the bias current in the GaAs FET. The GaAs FET is characterised by

excellent linearity and ultra low noise.

Mixer 2

The second mixer uses a diode ring module (M1) to mix to 455 kHz. Because it is passive, it

functions as a reciprocal device, operating in the reverse direction on transmit.

- 18 -

Page 19

Filter 2

The ultimate selectivity of 2.4kHz @ 3dB points is provided by ceramic filter (F2). This

device has a Zo of 2kΩ. Matching on transmit and receive is performed by 5mm transformer

(T8).

Tx/Rx switch

Bilateral switch (U22) routes the signal through the final IF processor chip (U23) on receive

and direct from the double balanced mixer on transmit. It also handles the transmit and

receive audio paths ensuring correct audio switching to/from the double balanced mixer

(U24).

455 kHz IF processor

The IF processor chip (U23) provides up to 100dB gain at 455kHz and provides 100dB of

AGC range. U19C and Q11 along with C131, C22 and C174, implement hang AGC

appropriate to SSB signals. Two different decay times, fast and slow, are available by

switching MOS FET Q25.

Double balanced mixer

The double balanced mixer (U24) provides greater than 50dB of carrier suppression on

transmit and highly linear demodulation on receive. As previously described, bilateral switch

(U22) performs the signal routing to enable th is to happen.

Carrier insertion oscillator

To generate and receive a single sideband signal a carrier insertion oscillator is required. On

USB this operates at 453.6kHz and on LSB the frequency is 456.4kHz. It is derived from

oscillator (U6), which has selectable crystals (X3 & X4). The oscillator operates on

7257.6kHz or 7302.4kHz for USB and LSB respectively. The CIO frequency emerges from

output Q4 of counter U7, after division by 16. Counter U7 also provides a 7kHz clock to run

the charge pump, 25volt & -5volt supplies and the display multiplex clock.

Gain distribution

Diagram 3 (Section 8 of this manual) shows the HF-90 system gain distribution.

Receive audio chain

The recovered audio of pin 6 of the double balanced modulator (U24) is routed through a

switch (U22) to the gain stage (U25B). This provides 30dB gain, taking AGC level signals

up to 2volt p-p.

The audi o pat h fe eds thr ough th e vo lu me co nt rol DAC o nwa rd t o t he o utp ut amp l ifie r (U 28 ).

The DIL audio amplifier yields 2watt, or more if the radio is operating from higher than

12volt.

The amplifier (U27:B) provides a limiting signal to the Selcall decoder (U18).

- 19 -

Page 20

Selcall decoder

The Selcall decoder uses an on-frequency PLL with a VCO centre frequency of 1700 Hz. An

XOR phase comparator (PCI) is used for noise rejection. The recovered data signal appears

on the loop filter (R32, R128, C127, C129). It is then fed to a data slicer which has an

adaptive reference level (pin 6 U19:A). This ensures that off-frequency signals will be

satisfactorily recovered since the reference is the mean signal deviation. The data is sent on

its way to the microprocessor as SELD.

The switching transistor (Q12) disables the Selcall output (SELD) when SELE is taken high

by output PL3/Pin 7 on the PASW PCB. This allows the computer the use of the FROMC

line during programming.

Microphone amplifier

The microphone amplifier (U25:A) provides a differential balanced input allowing common

mode rejection. Inputs from TR and BR allow tone modulation for the emergency alarm,

being added at the virtual earth. Input from the microphone is via a 600Ω transformer (T7)

which provides isolation. The microphone amplifier has a feed to DTMF chip U9.

Automatic audio level control

The ALC chip (U26) works on transmit to maintain a near constant output level of 2volt p-p

when the audio output is beyond a certain threshold set by R73. In this way the best radiated

signal to noise ratio is maintained. The transmit audio signal (TXA) is routed through U22 to

pin 4 of the double balanced mixed (U24). A diode clipper (D18,C173) prevents any

transient overshoot.

Receiver voltage supplies

The main +5volt supply is switch mode derived on the PASW PCB. The main +10volt

supply is from a linear regulator on the PASW PCB.

Low current supplies at +25volt and -5volt are derived from a charge pump circuit

(comprising U8, D2, D6, D16, D17 and D19). The charge pump is clocked at 7kHz by the

CIO counter (U7).

Low battery detector

The comparator (U4B and A) detects when the 10volt regulator loses regulation and pulls the

LOBAT line low, signaling low battery level. At present this signal is not used by the radio.

Signal strength meter

The signal strength meter comprises counter U14, DAC U15 and comparator U4:C. The

counter is clocked and enabled by the display serial line. During display write the counter is

clocked and when the DAC ramp crosses the AGC level comparator U4:C, output feeding

RCL is pulled low. In this way the microprocessor can measure signal level.

- 20 -

Page 21

7.3 PASW PCB

Refer to the schematic diagram (HF-90 P.A. & POWER SUPPLY 90002) in Section 17 of this

manual.

This printed circuit board contains the power stages of the transmitter and all the radio power

supplies. It measures 100mm x 147mm and contains nine integrated circuits. Four MOS

FETS and two power transistors are mounted on the mechanically connec ted rea r heat sink .

The HF-90 breaks new ground in obtaining excellent transmitter intermodulation distortion,

low broadband noise and PA economy, through the use of high voltage MOS FETs in the PA

and driver stages. The necessary supply rails are provided by low EMI switch mode power

supplies.

Power supplies

Tx supply switches

The darlington driver (U8) inverts the PTT / line to switch series pass transistor (Q11) which

keys up the +5 Tx supply.

+5volt supply

A simple switcher chip (U9) along with D10, L2 and C80, provide a high efficiency +5volt

output from a wide range of input voltages (10 - 28volt). Chokes (L1 and L3) with

associated decoupling capacitors minimise electromagnetic emission. The unit is enclosed

by a shield to further reduce interference.

+10volt supply

This relatively low current +10volt supply is obtained by sitting a 5volt regulator (U10) on

the +5volt rail. The regulator is a low dropout type requiring only 0.2volt of headroom.

+15volt supply

This supply should be more correctly designated the +11.4volt limiter since its function is to

maintain an output voltage in the range 10 - 11.4volt, irrespective of input voltage.

The series pass transistor (Q13) is hard on until U3:A detects that its output has risen to

+11.4volt. Thereafter it is held in regulation. It is keyed on only in transmit by using the

+5volt supply as a reference. Its function is to limit supply voltage to U4 and MOSFET

drivers (Q1 & Q2).

+50volt Tx supply

The +50volt Tx supply is a classic boost convertor utilising energy storage choke (L5),

switches (Q5 and Q6), and a rectifier (D5). The switch mode controller chip (U4) monitors

the output voltage via voltage divider (R7 & R8) comparing it against a 5volt reference to

obtain an error duty cycle on the gates of Q5 and Q6. The chokes (L4 & L6) with their

associated decoupling capacitors yield a low EMI design. Some supply droop will occur on

speech peaks.

Tx amplifier (pre-driver)

The current mode Op-Amps (U1 & U11) each provide +16dB of gain with low output

impedance, wide bandwidth and excellent linearity. They drive the driver MOS FET gates

through a balanced transformer (T4). the MOS FET (Q9) in the feedback circuit of U11

controls the stage gain. This permits ALC of the PASW unit.

- 21 -

Page 22

Bias circuit

Bias for both the driver and PA MOS FETs is derived from a source which is effectively an

amplified thermal junction pedestal (Q8 and Q12). VR1 is the driver bias pot and VR2 is the

PA bias pot. These references are buffered by Op-Amps (U2:A and U3:B) which have gains

of three and five respectively. Device Q12 is in direct thermal contact with PA MOS FET

Q3, and device Q8 is in direct thermal contact with Q4 in order to obtain a thermal

coefficient of bias which is slightly negative, thus ensuring thermal stability.

PA drivers

The PA driver circuit uses MOS FETs (Q1 and Q2) running from the +15volt limited supply

(+11.4volt). Negative feedback networks (C57, R43, R90, C56, R88 & R44) fix the gain of

the stage at 20dB. The 10R input resistors (R37 & R55) suppress parasitics. The bifilar feed

transformer (T1) provides a DC cancelled supply isolation.

The transmission line transformer (T5) yields a 4:1 impedance step-down to provide final

output MOS FETs (Q3 & Q4) with a high current source for gate drive.

PA final output

The final output architecture is similar to that of the drivers, with negative feedback and

parasitic stoppers. The difference lies in the supply voltage and output matching. The PA

transistors operate from a +50volt rail, achieving isolation from supply by a DC cancelled

bifilar choke (T2). An output transmission line transformer (T3) combines the output signals

and provides balance-to-unbalance conversion. Impedance conversion is unnecessary since

the PA matches directly to 50Ω. Polyswitches (Negative TC Thermistors) in series with the

source leads of the output MOS FETs Q3 and Q4, wind back the output power when the

temperature on the heatsink exceeds 80°C.

PA low pass filters

Harmonic attenuation of the transmitter output signal is implemented through the six 5element elliptic low pass filters. Latching relays (RL3 - RL8) select the sub-octave filters

according to Table 3 (Section 7 of this manual).

Relay drive circuit

Selection of the set or reset coil for activation is implemented via seven darlington drivers

(U6). The address information is loaded down the DIS serial data line into a shift register

(U5) and this drives the darlington driver (U6). When a frequency change occurs the

common reset line is pulsed, then the specific set line is pulsed. In the static condition no

current is consumed by the relays. Latching takes place through application of a 5ms pulse.

Tx RF ALC

The forward and reverse current are sampled by a 16:1 current transformer (L19) and

detector diodes (D1 and D2). These provide references for the ALC circuit. Potentiometer

VR3 sets the power level by manipulating the fraction of signal fed to U3:B.

Low power select deactivates the +50V supply by grounding pin 2 on U4.

ALC time constants are determined by C34, R95 and R96. A diode (D3) combines the

- 22 -

Page 23

forward and reverse signals and the Op-Amp (U2:B) provides system gain in the ALC

feedback loop. The gain controlled RF amplifier (U11) in the first stage of the PASW PCB

is fed with the ALC output signal via Q7.

ATU PSU switch

A software keyed +12 - 28volt supply is provided on the rear 4-pin connector to allow the

interfacing of a TA-90 automatic antenna tun er, a horn ala rm or flashing beacon.

Reverse / over-voltage / under-voltage protection

A tranzorb diode (D7) provides reverse and 33volt clamp protection. An external fuse must

be fitted. Diodes D4 and D6, in series with the power on relay activation coil, ensure that the

radio will not power up if the supply is accidentally reverse polarised. The relay also

guarantees that the radio will switch off completely below 9.5volt, thus protecting the

connected battery against over discharge.

- 23 -

Page 24

8. TABLES & DIAGRAMS

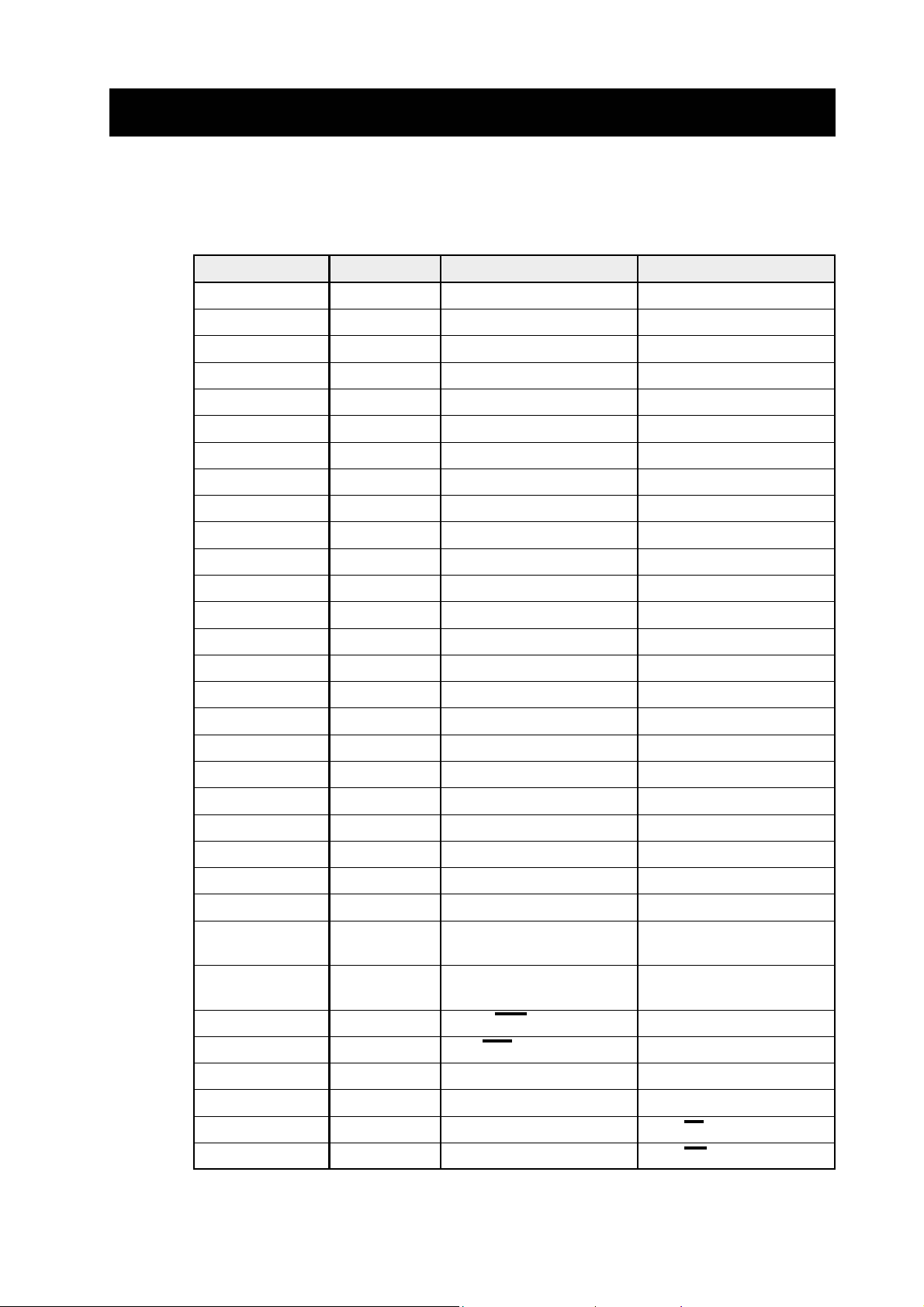

Table 1. HF-90 micro port allocations

Port Number Micro Pin Input Function Output Function

P0.0 43 D0 / DTMF Q0 A/D0

P0.1 42 D1 / DTMF Q1 A/D1

P0.2 41 D2 / DTMF Q2 A/D2

P0.3 40 D3 / DTMF Q3 A/D3

P0.4 39 D4 A/D4

P0.5 38 D5 A/D5

P0.6 37 D6 A/D6

P0.7 36 D7 A/D7

P1.0 2 TOP ROW TONE 1 OUTPUT

P1.1 3 SIG METER INPUT RIGHT COLUMN

P1.2 4 DTMF NOT VALID MIDDLE COLUMN

P1.3 5 LEFT COLUMN

P1.4 6 BOTTOM ROW TONE 2 OUTPUT

P1.5 7 SYNTH. CLOCK

P1.6 8 SYNTH. ENABLE

P1.7 9 DISPLAY ENABLE

P2.0 24 A8

P2.1 25 A9

P2.2 26 A10

P2.3 27 A11

P2.4 28 A12

P2.5 29 DTMF ENABLE

P2.6 30 (A14)

P2.7 31 (A15)

P3.0 11 RXD SE RIAL DATA/

SELCALL IN

P3.1 13 TXD ALL SERIAL DATA

P3.2 14 INT0/PTT IN PTT OUT

OUT

P3.3 15 INT1/ENCODER

P3.4 16 T0 QUAD IN

P3.5 17 T1 QUAD IN

P3.6 18 WR EXT DATA

P3.7 19 RD EXT DATA

Note:- ALE latches Port 0 address

- 24 -

Page 25

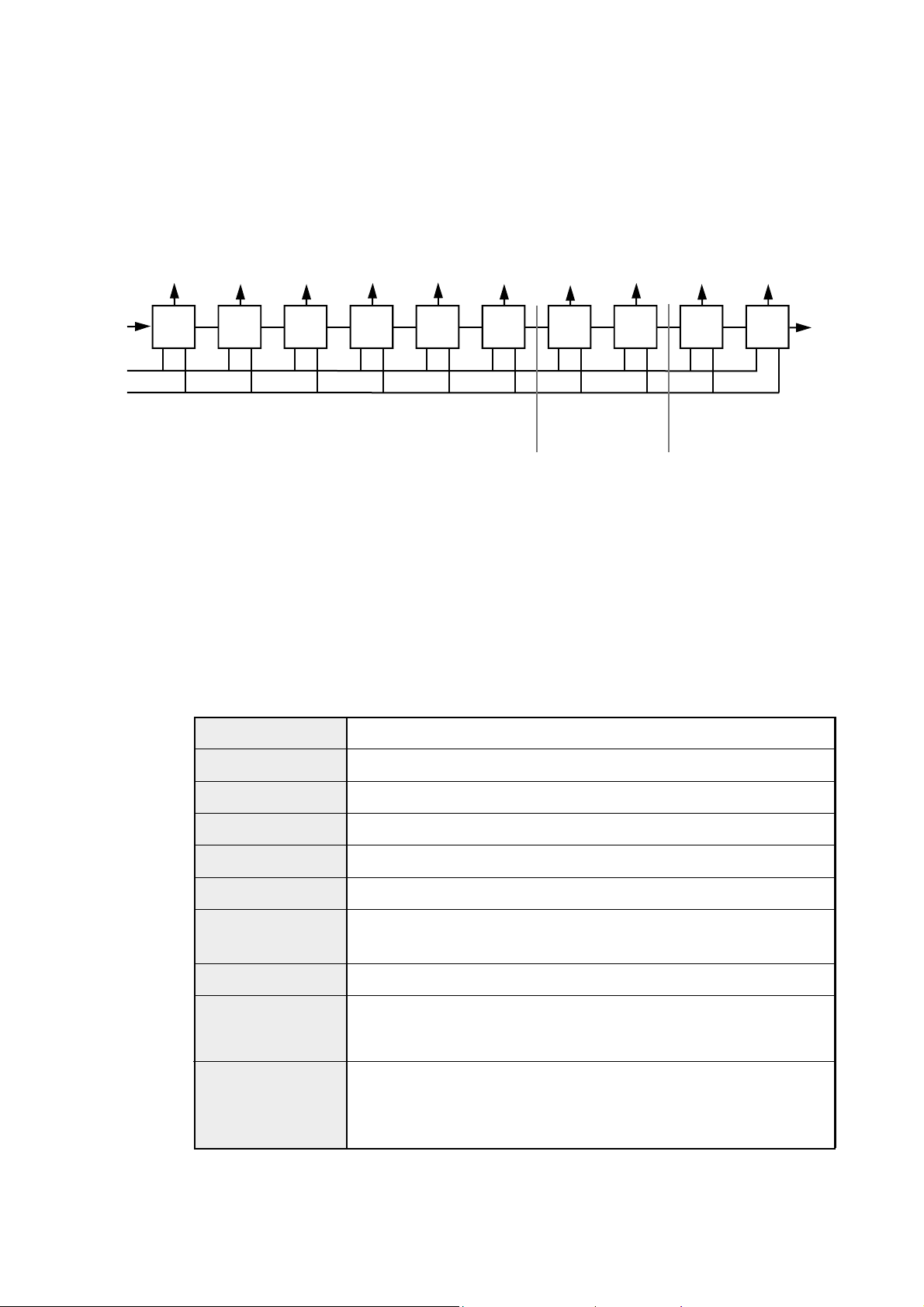

Diagram 1./Table 2. Serial link chain

Diagram 1. Physical hardware

LED

100Hz

(TOC)

SDIN

LED

1kHz

LED

10kHz

SCK

DIS

Front Panel PCB RXMP

The serial link chain comprises 10, 8-bit serial shift registers with common serial clock

(SCK), select display (DIS) lines and cascade data (TOC).

Serial data is clocked through the shift registers by SCK and when 80 bits of data have gone

through, the enable DIS is pulsed high and the data is parallel loaded to internal latches.

Table 2. Software byte allocation

Byte 0

LED

100kHz

LED

1MHz

LED

10MHz

Miscellaneous

DAC

100 Hz display

Volume

DAC

PA Filter

Switch

Power

Setting etc.

Loop

Back

PASRO

PASW

(last byte)

Byte 1

Byte 2

Byte 3

Byte 4

Byte 5

Byte 6

Byte 7

Byte 8

1 kHz display

10 kHz display

100 kHz display

1 MHz display

10 MHz display

BIT 6 BIT 1

1 = MIC INHIBIT 1 = AGC SLOW

BIT 0

1 = USB, 0 = LSB

Bits 0 to 7 volume in range 00H - FFH (LOW = LOW VOL)

BIT7

NIL

BIT6

BAND1

BIT5

BAND6

BIT4

BAND2

BIT3

BAND5

BIT2

BAND3

BIT1

BAND4

BIT0

RESET

PA Filter

Band

Select

Disable

Byte 9

loopback

Disable

Selcall

NIL NIL +50V

OFF

Low

power

ATU

ON

NIL

(1st byte)

- 25 -

Page 26

Diagram 2. Superhet. mixing scheme

3740 USB 453.6 CIO

86900 kHz

LO1

83613.6

LO2

Diagram 3. HF-90 Rx gain distribution

-0.5dB -5dB -4dB +20dB +20dB -8dB -6dB +16dB +80dB

LPF 4 x GaAS SAW

83.160 MHz

LO1

85.113 MHz

ATF

13736

ERA3

LO2

83.615 MHz

+/-10 kHz

TDA

1572

STAGE 1

CERAMIC

455 kHz

USB 453.6 kHz

LSB 456.4 kHz

TDA

1572

STAGE 2

CIO

Sensitivity = 0.25uV @ 10dB S+N/N

3I/P = +20dBm

3dB AGC knee = 1uV

- 26 -

Page 27

Table 3. HF-90 Tx low pass filters

Truth table

Band HEX Code Causes 1 Causes 0

RESET 01H 15 10

NULL 00H -

1 40H 6 16

2 10H 4 14

3 04H 2 12

4 02H 1 11

5 08H 3 13

U5 Pin U6 Pin

Note:-

6 20H 5 15

When the PA filter is selected, the high level (+5V) on U5 pin persists for only

three seconds. After this time the voltage on all U5 output pins reverts to zero.

The latching relays preserve their current state.

Relays may be selected manually by first resetting (ie. shorting pin 10 of U6 to

ground momentarily) then shorting the relevant pin (11-16) on U6 momentarily

to ground, to select the desired filter.

- 27 -

Page 28

Table 4. HF-90 connector pinouts

Pin Code Function Used on

(source underlined)

Con: PL1

SERIAL

QUAD

Con: PL2

KEYS

MIC

LS

1 QUAD 1 QUAD ENCODER IN 1 FP / RXMP / PASW

2 QUAD 2 QUAD ENCODER IN 2 FP / RXMP / PASW

3 DISRO DISPLAY SHIFT REG OUT FP / RXMP / PASW

4 FROMC SERIAL DATA IN

FP / RXMP / PASW

(FROM COMPUTER)

5 SCK SERIAL CLOCK FP / RXMP / PASW

6 GND GROUND FP / RXMP / PASW

7 DIS DISPLAY ENABLE FP / RXMP / PASW

8 +5 +5 SUPPLY FP / RXMP / PASW

9 TOC GENERAL SERIAL DATA OUT

FP / RXMP / PASW

(TO COMPUTER)

10 7 kHz DISPLAY MPX CLOCK FP / RXMP / PASW

1 MCL MIDDLE COLUMN FP / RXMP / PASW

2 LCL LEFT COLUMN FP / RXMP / PASW

3 RCL RIGHT COLUMN FP / RXMP / PASW

4 TR TOP ROW FP / RXMP / PASW

5 BR BOTTOM ROW FP / RXMP / PASW

6 MIC1 MICROPHONE 1 FP / RXMP / PASW

Con: PL3

POWER

SIGNALS

7 MIC2 MICROPHONE 2 FP / RXMP / PASW

8 ON/OFF ON/OFF FP / RXMP / PASW

9 PTTU PTT UNBUFFERED FP / RXMP / PASW

10 LS LOUD SPEAKER FP / RXMP / PASW

1 PASRI PA SHIFT REG IN RXMP / PASW

2 PASR0 PA SHIFT REG OUT (SELD) RXMP / PASW

3 SCK SERIAL CLOCK RXMP / PASW

4 DIS DISPLAY ENABLE RXMP / PASW

5 +5 +5 SUPPLY RXMP / PASW

6 +10 +10 SUPPLY RXMP / PASW

7 SELNE SELCALL DISABLE RXMP / PASW

8 GND GROUND FP / RXMP / PASW

9 GND GROUND FP / RXMP / PASW

10 GND GROUND FP / RXMP / PASW

- 28 -

Page 29

Pin Code Function Used on

(source underlined)

Con: PL4

PA

MONITOR

Con: PL5

RXMP

SIGNAL

TEST

SOCKET

1 GND GROUND FP / RXMP / PASW

2 +24 +24 RELAY SWITCHED RXMP / PASW

3 GND GROUND FP / RXMP / PASW

4 +50 +50 TX SUPPLY RXMP / PASW

5 +15 +11.4 LIMITED TX SUPPLY RXMP / PASW

6 PA BIAS PA BIAS (3.9V) RXMP / PASW

7 RFI0 RF INPUT/OUTPUT RXMP / PASW

8 DR BIAS DR BIAS (2.2V) RXMP / PASW

9 GND GROUND FP / RXMP / PASW

10 ALC ALC MONITOR RXMP / PASW

1 NOT USED

2 GND GROUND FP / RXMP / PASW

3 NOT USED

4 AGC RX AGC OUT RXMP

5 SELD (PASRO) SELCALL DATA RXMP

6 GND GROUND FP / RXMP / PASW

7 GND GROUND FP / RXMP / PASW

Con: PL6

RXMP

MICRO

TEST

SOCKET

See below

8 RXA RX AUDIO RXMP

9 SELA SELCALL AUDIO RXMP

10 TXA TX AUDIO RXMP

1 ROMOE ROM OUTPUT ENABLE RXMP

2 WR ROM WRITE RXMP

3 ROMCE ROM CHIP ENABLE RXMP

*

4 12 MHz 12 MHz CLOCK RXMP

5 ALE ADDRESS LATCH RXMP

6 DTMFE DTMF ENABLE RXMP

7 A0 ADDRESS 0 RXMP

8 A3 ADDRESS 3 RXMP

9 A1 ADDRESS 1 RXMP

10 A2 AD DRESS 2 RXMP

* PL6 not present on RXMP issue M and beyond (S/No 1400→→→→).

- 29 -

Page 30

Diagram 4. Connector positions

PL1

PL2

PL6 *

PL3

PL5

PL4

COMPONENT SIDE OF RXMP PCB

* PL6 not present on RXMP issue M and beyond (S/No 1400→→→→).

- 30 -

Page 31

9. MAINTENANCE

9.1 Disassembly and assem bl y

A. Removal of PCBs

First undo the four M3 screws on the rear heatsink. Take care not to lose the insulating

bushes. Slide the heatsink assembly complete with PASW and RXMP boards out of the

extruded sleeve.

B. Separation of PCBs

The PASW and RXMP PCBs mate via four 10-way connectors. These hold the boards

firmly together. It is best to separate the boards by taking one board in the left hand and the

other board in the right and using the fingers as levers to gently prize the boards apart in a

controlled manner.

C. Removal of the front panel

Undo the four M3 screws on the front panel. Take care not to lose the three plastic bushes.

The display PCB is held on to the front panel by the nuts of the on/off switch, microphone

socket and volume encoder.

D. Reassembly of radio

It is advisable to commence reassembly with the RXMP and PASW boards first. Make sure

that the boards are firmly together and that the rear rubber gasket is in place. Slide the 2board ‘sandwich’ into the sleeve making sure that the correct orientation has been selected.

The small aluminium heatsink on the PASW board has a keyway which engages in the

extruded sleeve. Tighten the screws on the rear heatsink evenly, making sure that the gasket

is correctly placed. Finally, replace the front panel making sure that the two 10-way

connectors engage properly on the RXMP board. Tighten the four M3 screws taking care to

position the gasket correctly.

- 31 -

Page 32

9.2 Replacement of Microprocessor

In the event of firmware upgrade or in the extremely unlikely event of corruption (leading

character of software version display is “E”), the microprocessor chip U1 will require

replacement.

A number of precautions should be observed during this procedure.

" The correct PLCC 44 “scissor squeeze” type of extraction tool MUST be used.

" Removal and insertion must take place at an antistatic workstation.

" Orientation of U1 is critical with PIN 1 dot nearest to edge of RXMP board.

" This chip determines whether or not radio has a hopping option fitted.

- 32 -

Page 33

9.3 Radio alignment

RXMP board

Refer to the test point overlay (HF-90 RECEIVER BOARD ALIGNMENT - POSITION REFERENCE)

in Section 12 of this manual, as well as the schematic diagram (HF-90 I.F. STRIP , MICRO

SECTION & SYNTH. 90003) in Section 17 of this manual.

1. Set the radio to any channel where its frequency is exactly divisible by 20kHz, ie

frequency ending in 00, 20, 40, 60, 80.

2. Using a digital multimeter measure the voltage at TPLO2. Adjust VC5 until this

voltage is 2.3volt +/-0.1

3. Set the radio to 30,000kHz

4. Using a digital multimeter measure the voltage at TPLO1. Adjust VC6 until this

voltage is 20volt +/-0.5

5. Using a frequency counter with high impedance probe measure the frequency at

TP24MHz. Check that the radio has been running for two minutes. Set the frequency

to 24MHz +/-7Hz by adjusting the TCXO.

6. Check that a USB channel has been selected. (no indicator point lit next to highest

digit).

7. Using a frequency counter with high impedance probe measure the frequency at USB/

LSB TP. Adjust VC3 to obtain 453.6kHz +/-3Hz.

8. If the radio has software for the export market ie HF-90E then select an LSB channel.

9. At the same USB/LSB test point measure the frequency and adjust VC2.

" On radios with Serial Number below 1200 measure 456.6kHz.

" On radios with Serial Number of 1200 and above measure 456.4kHz.

10. On PL5 fit a 10-way receptacle which has pin 7 connected to pin 9 via a 100nF

capacitor. Using a frequency counter with high impedance probe, measure the

frequency at TP1700Hz (U18 pin 3 & 4). Adjust VR1 until the frequency is 1700Hz

+/-8Hz.

11. Using an oscilloscope with 10:1 probe, measure the voltage on USB/LSB TP. Adjust

core T10 for maximum. This corresponds to approximately 1.7volt p-p.

12. Select a channel somewhere in the 5 - 8MHz region. Turn up the volume and with no

antenna or signal generator connected, adjust the AGC threshold control (VR2)

clockwise just beyond the point where there is no increase in noise. RXMP boards

beyond issue S do not require this adjustment.

13. Inductors L1 and L2 should be left at the factory setting. The core position will be

approximately 2mm below the coil top.

14. Apply a signal at 1kHz above the channel frequency to obtain a 1kHz tone. Set the

level to 0.25µv and monitor the loudspeaker recovered audio on an oscilloscope.

15. Adjust L5 and L6 to obtain a peak in the tone. L6 will probably be screwed further in

than L5. Neither adjustment is very critical.

- 33 -

Page 34

16. Adjust L11 to obtain a peak in the tone. This will probably be quite sharp.

17. Adjust L7 to peak the recovered tone. The core may be screwed up until it is starting

to emerge from the coil. Do not allow it to protrude more than 1mm above the coil.

18. Adjust T9 to obtain a peak in the tone. The signal to noise may be slightly improved

by turning the core slightly clockwise beyond the peak.

It should now be possible to measure 10dB S+N/N on the 0.25µv signal.

The receiver alignment is now concluded.

PASW board

Refer to the test point overlay (HF-90 P.A. BOARD ALIGNMENT - POSITION REFERENCE) in

Section 12 of this manual, as well as the schematic diagram (HF-90 P.A. & POWER SUPPLY

90002) in Section 17 of this manual.

1. There are only three adjustable potentiometers on the PASW board and with two of

them (VR1 and VR2) the bias settings SHOULD NOT BE TOUCHED unless a driver

or final amplifier transistor has been changed.

2. Connect the HF-90 to a power meter and dummy load. The wave form can be

monitored by ‘eavesdropping’ on the coaxial line using an asymmetric Tee pad. This

consists of a 1K 1watt resistor connected to the 50Ω line. The other end of the resistor

is connected to the oscilloscope input and a 47Ω resistor must be connected across the

oscilloscope input. The above network yields approximately 30dB attenuation.

3. Inductor L20 should not be adjusted. It should remain as factory set with core 1mm

below the coil top.

4. Potentiometer VR3 is the ALC power level setting pot. It should be set on a channel

in the 4 to 6MHz range to give a clean 2-tone signal of the required power level (5060watt). On Australian models (HF-90A) a 2-tone signal can be obtained by holding

down the ALARM key for two seconds. The control VR3 is typically adjusted near to

the anti-clockwise end-point. Note that if the power level is backed off, a ‘bubbling’

effect can occur. This can be alleviated by screwing in core L7 slightly or adjusting

VR3 on the RXMP board. It may also be necessary to do this when swapping PCBs.

5. In the event of either driver or final amplifier MOS FETs having been changed, the

bias can be set up as follows:

" First remove the two jumper links on the back of the PASW board.

" Using a multimeter on the 10volt range, measure the voltage on the positive end

of C49 (10µF tant).

" Push the PTT switch and adjust VR1 to obtain 2.6volt.

" Measure the voltage on the positive end of C63 (10µF tant).

" Push the PTT switch and adjust VR2 to obtain 3.7volt.

" Now replace the jumpers under the PASW board.

Changing a final amplifier transistor

Should either of the final amplifier MOS FETs Q3 or Q4 require changing, the following

procedure should be followed:

1. First check the manufacturer of the replacement. IRF830 devices from Motorola (M),

Harris (H), International Rectifier (IR) and SGS-Thomson (S or ST) have been used.

If the replacement is not the same manufacturer as the original parts, then both devices

MUST be replaced.

- 34 -

Page 35

2. Loosen off the M3 screw securing the power device. Carefully remove the screw and

swing away the thermal protection transistor Q8 or Q12 on its flying lead. The

SILPAD between the thermal sensor and the output device must be kept. Next

desolder all three legs of the defective device. Remove the device taking care to

preserve both the SILPAD under the device flange AND THE TINY PLASTIC

SLEEVE WHICH SPACES THE FLANGE FROM THE SCREW. Note that a

polyswitch disc thermistor may be fitted in series with the source lead of each output

transistor Q3 and Q4. These should not be removed. If they are not fitted (two yellow

discs) contact Q-MAC Electronics for advice on fitting as per ECN 79 and 80.

3. Having removed the device, simply reverse the process with the new device taking

care to fit all the parts correctly (two SILPADs plus plastic sleeve). The M3 screw

should be firmly tightened.

IMPORTANT NOTE:

THIS PROCEDURE SHOULD ONLY BE ATTEMPTED BY QUALIFIED SERVICE

PERSONNEL. Q-MAC ELECTRONICS WILL CHARGE FOR ANY DAMAGE CAUSED BY

INCORRECTLY IMPLEMENTING THIS PROCEDURE.

- 35 -

Page 36

10. FAULT FINDING

10.1 No tools fault finding

Fault diagnosis

1. Check that the 4-pole power connector on the rear of the radio is correctly connected

to a 12 - 24volt power source (battery or power supply) capable of providing 10ampere

peak current. Screw up the locking ring. Ensure correct polarity. Refer to the table

below if in doubt.

2. Check that an approved antenna or 50Ω dummy load is connected to the rear BNC

coaxial socket.

3. Connect the microphone to the front 8-pole receptacle. Screw up the locking ring.

4. Connect the loudspeaker to the 4-pole spur connector on the rear cable if required.

ENSURE THAT THE CORRECT POLARITY IS OBSERVED

5. Switch ON/OFF switch to the ON position and check that the following power on

sequence occurs.

Power-on Sequence

Elapsed Time Display Contents Loud Speaker Internal Sounds

Start Blank Click Relay Click

1 second HF-90A or HF-90E

or HF-90H

2 seconds Software Revision

eg. 2-407

or if error E2-407

3 seconds Selcall Number if

Advanced Model eg.

1234

4 seconds Channel Number eg.

CH 2

5 seconds onward Frequency display

if HF-90E or HF-90H

1kHz Tone Relay Click

Silence or if error

900Hz Tone

Radio Noise Relay Click

Radio Noise Relay Click

Radio Noise Silence

Relay Click

6. If the radio is completely dead, ie. no tones, clicks, loudspeaker noise or display, then

suspect that no power is getting through to the rear connector. If this is not the case

then possibly the wiring at the rear of the front panel ON/OFF switch is faulty, or the

two front panel 10-way connectors may have been mis-engaged during the last reassembly.

- 36 -

Page 37

7. If a display is present on turn-on, but the software revision comes up with a program

memory checksum error (eg. E2-407), accompanied by a 900Hz tone from the

loudspeaker, then some degree of memory corruption has occurred. The radio should

be fitted with a new microprocessor available from an authorised dealer or Q-MAC

Electronics Pty Ltd. The microprocessor is the only pluggable component on the

RXMP PCB. Some radio functionality may be unaffected by the corruption.

Corruption is highly unlikely to occur.

8. If the display is normal on turn-on and the sequence of five relay clicks can be heard

from inside the radio, but no loudspeaker tones or noise of any sort is heard, then

suspect a problem with the external loudspeaker connection. If the loudspeaker and

wiring are in good condition then the internal loudspeaker feed wire or tracks on the

RXMP or PASW PCBs may be broken or short-circuited. If a speaker microphone

produces audio but a loudspeaker does not, then the loudspeaker track on the PASW

PCB has been broken. Check that the loud speaker plug has been correctly inserted.

9. If the display is blank or has unintelligible characters, but the turn-on sequence of

tones and relay clicks is correct, then the microprocessor is probably operating

correct ly but the di splay mul tiplexor c lock (7kHz) is abse nt. This s ignal is generated

on the RXMP PCB.

10. If no clicks other than the first power relay click are heard, and no tones are audible

and either no display or incorrect characters are shown, then the microprocessor is

probably not running correctly. Some faint noise from the loudspeaker may be audible

in this condition. Replacing the RXMP PCB should fix the problem.

11. If the display comes up normally and tones are heard, but the sequence of relay clicks

is absent, then the serial data chain is broken somewhere. Turn the volume control up

and down and if this works then the break is between the RXMP and PASW PCBs. If

the volume is not working then the break is between the DISPLAY and RXMP boards.

Board substitution will confirm this.

12. If switch-on tones and clicks are normal but no radio noise is audible then there may

be a receiver fault. With the volume control at maximum a reasonable amount of noise

should be heard. The volume control gives clicks when it is being turned up or down.

At maximum or minimum, no more clicks will be heard. A high pitched whine may

indicate a fault in the -5v supply. If the problem has not been located substitute the

RXMP PCB.

13. Pressing the CHAN∧ or CHAN∨ keys should produce an internal click and the display

should show the next channel number. Some change in the character of the noise from

the loudspeaker may occur. If only UP or DOWN works then suspect a key or matrix

fault on the DISPLAY board. If it is a matrix fault then it will affect a whole row or

column of keys.

14. Press the PTT switch on the microphone. Listen for an internal relay click. Check that

the display changes to exhibit the frequency in kHz with decimal point illuminated. If

neither occurs then a fault in the microphone PTT switch should be suspected. If this

is not the case then the internal PTT circuit is faulty. If the frequency display is not

accompanied by a click, then the microprocessor is responding correctly but the PTT

feed to the changeover relays is faulty. If there is no display change but a relay click is

audible then the PTT input of the microprocessor has been damaged and a new micro

will be required. Replace the RXMP board.

- 37 -

Page 38

15. Press the TUNE key briefly. The PTT relay clicks should again be heard. This time

the microprocessor is activating the PTT.

16. Program the radio with CH9999 (23999kHz USB). A strong 1kHz tone should be

audible on this channel. This is the 24MHz microprocessor clock. If it can be heard

then:

" The microprocessor clock is running.

" The receiver is functioning.

17. If the receiver is working but the transmitter is giving no power, then the internal HV

fuse on the rear surface of the PASW board may have ruptured. The fuse is

implemented as a meander track on the PCB. It should be replaced with 20mm of

0.16mm enameled copper wire.

18. Hold down the TUNE key for 20 seconds. The rear heatsink should start to get

significantly warm compared to the receive condition. If this is not the case then the

TX current is abnormally low. Again the HV fuse should be checked.

- 38 -

Page 39

11. DIAGNOSTIC TEST SEQUENCE

11.1 Receiver test sequence

Refer to the test point overlay (HF-90 RECEIVER BOARD ALIGNMENT - POSITION REFERENCE)

in Section 12 of this manual, as well as the schematic diagram (HF-90 I.F. STRIP , MICRO

SECTION & SYNTH. 90003) in Section 17 of this manual.

The checks below should be made with the radio on receive with a USB channel in the range

3 - 6MHz selected.

1. Check the rails on RXMP

+5volt

" If dead, then check inverter on PASW.

" If high, then check for short between middle pin and output on U10 PASW.

+10volt

" If dead, then check that U10 PASW is properly connected.

+5volt output U31 RXMP

" If low, then open R80, R108 and R111 to see which is loading supply.

+5volt output U32 RXMP

" If low, then open R87 to see if it is loading supply.

+3v6 supply R133

" If high, then check for open circuit LED Y3, Y4.

-5volt supply

" If low, then check for loading by opening R150 RXMP. If this makes little difference,

then suspect charge pump or CIO.

+25volt supply

" If low, then check for loading by opening R137 RXMP. If this makes little difference,

then suspect charge pump or CIO.

2. Check clocks on RXMP

TP24MHz

" If clock is absent or low, then open R101 then R187 to check for loading.

" If the clock is absent after opening R101 and R187 then replace TCXO.

USB/LSBTP

" Using an oscilloscope check that the wave form at this point is approximately 1.7volt

p-p at 453.6kHz. It should be approximately sinusoidal.

" If no signal is present, check for a 7257,6kHz square wave at U6 pin8 (74HC00D). If

nothing is present then the CIO has stopped. If the wave form is there, then U7 (the

74HC4040) is at fault.

7kHz clock

" Using an oscilloscope, check the wave form at U7 pin14 (74HC4040). This should be

a 7kHz square wave and without it the display multiplexor and charge pumps will not

run.

- 39 -

Page 40

U18 pins 3 and 4

" Using an oscilloscope check for the presence of a noisy square wave at an average

frequency of 1700Hz.

" In the absence of this, check the supply to the chip and the timing components C28,

R30, R127, VR1.

ALE on U4 pin 1

" This wave form is the ‘heart beat’ of the radio. If it consists of bursts of logic high

going pulses every 2ms during normal operation or every 666µs whilst hopping, then

the microprocessor is basically healthy. It is executing instructions correctly and

responding to the Timer 0 interrupt. It is also idling correctly. This wave form shows

how ‘busy’ the microprocessor is at any point in time.

" If the wave form is incorrect maybe an interrupt is stuck or the one of the buses has a

fault.

3. Check the synthesizer control voltages

LO2 TP

" Using a multimeter or oscilloscope, check that the voltage on this point is in the range

2 - 3volt. It should also be clean.

" If it is out of range then check that VC5 has not been damaged. Reset VC5 if

necessary as per Section 9.3 (Radio alignment).

LO1 TP

" This control voltage should start off low at 2MHz (2 - 3volt approx) and increase

towards 20volt at 13MHz. By 14MHz it should be back low again and increase back

up to 20volt at 30MHz.

" If there is noise or a sawtooth on the wave form inspect C96 and C99 for damage. Bad

connections to T12, T13 and T5 will also cause problems.

" Above 5MHz check that at least two of the four LO1 LEDs are lit. If not then LO1 is

dead or LO1 TP is at a very low value with the loop out of lock.

4. Check for correct DC voltages around the RXMP

GaAs FET gates Q1 and Q2, Q3 and Q4

" Check for approximately -1.8volt at both these points. This voltage is present only if

LO1 is running correctly (although not necessarily in lock) AND if all the GaAs FETs

are intact.

" If both points are slightly positive and all four LEDs in LO1 are extinguished, then

there is a problem with LO1 activity. Check T12, T13 and T5.

" If one point is normal and the other slightly positive, then it may be due to asymmetry

in LO1 or one or two defective GaAs FETs. Check also one end of R91 and R104 for

2.5volt bias and check U29 gate E and F levels (approximately 2volt average). U29

runs warm.

Q5 (ATF13736) gate

" This should measure -0.7volt approximately and the drain +2.8volt.

" If this is not so, then either the -5volt charge pump derived rail is not correct, or

feedback stabilising amplifier U20:B (LM358D) is faulty. U20 should have +2.8volt

on both pins 5 and 6.

Q21 (SST309) source

" This should measure +8.7volt approximately. If this is not the case then Op-Amp

U20:A is faulty.

- 40 -

Page 41

Pin4 of F2 (the 455Khz filter at the end furthest from T8)

" This should have 2.5volt present. If not then R48 or R49 are faulty.

U23 pin 12 (TDA1572T)

" This should have 5.9volt with 0.5volt p-p of noisy 455kHz signal present.

" If not check for 2.2volt on pin 1 of U23 and 2.2volt on pins 3 and 4.

AGC monitoring point (on plus terminal of C22)

" This should be 2volt with no signal and rise to a maximum of 3.8volt with a huge

signal.

" If it is stuck high then check that AGC transistor Q11 is functioning.

Bias voltages on U24 (MC1496D)

" Pins 6 and 12, the outputs should be at 7volt.

" Pins 8 and 10, the CIO ports should be at 3.8volt.

" Pins 1 and 4, the signal input ports should be at 1.7volt.

" Significant discrepancies will likely be due to faulty resistors in the biasing chain.

" Injection at 453.6kHz should be visible at pin 8 of U24 (MC1496D) at a level of

approximately 0.3volt p-p.

RXA PL5 pin 8

" This should have a DC level of 3.6volt and a very low level recovered audio signal.

" If the DC level is incorrect then the bias pedestal set by R133, Y3 and Y4 is probably

faulty.

" If no audio is making it through the TX/RX switch ,U22 (4053D), then possibly it has

been damaged or the PTT level reaching pins 9,10 and 11 may be incorrect.

" Finally, damage to R178 or C200 may disable the switch path.

VOLI on pin 7 of U25 (LM358M)

" This should again be at a DC level of 3.6volt with a maximum recovered signal of

1.2volt p-p when a signal at full AGC level is applied.

U13 pin 8 (DAC0800M)

" This should have a DC level varying between 5volt at minimum volume and 3.3volt at

maximum.

" Failure of the DC level to correctly follow the encoder may be due to loss of the -5volt

bias on pin 7 or a failure of the serial data to correctly reach U11 (74HC595D).

U27

" This Selcall audio amplifier has a gain of 100 and should have clipped noise present on

pin 7 of U27 (LM358M).

U28 pin 14 (LM384N)

" This should have full supply voltage typically 14volt, otherwise resistor R172 has

failed.

U28 pin 8 (LM384N)

" This should have half supply voltage typically 7volt, with the full audio output present

under received signal conditions.

SELA pin 9 PL5

" This should exhibit almost rail to rail noise on an unoccupied channel. The average

voltage should be 2.5volt.

- 41 -

Page 42

5. Serial digital wave forms can be checked

Channel change

" This should provoke activity on SYDA (DOP), SYCK (SCK) and SYEN (SEN) on

resistors R17, R13 and R12 respectively. Refer to schematic for wave forms.

Volume control change

" This should provoke activity on DIS (DEN) R14 and on SYCK (SCK) and SYEN

(SEN) as the serial data is sent down the chain to the volume control shift register U11

(74HC595D). However after the control reaches the ‘software endstop’ no further data

will be seen.

" Note that SYEN (SEN) pulses are very few and narrow.

" The volume encoder wave forms to the microprocessor can be checked on pins 1 and 2

of PL1. These are normally high but pulse low with shaft rotation.

SELD pin 5 PL5

" On a Selcall channel check for multiple data transitions on incoming noise.

" When receiving a Selcall the data on SELD should display a periodicity of 10ms.

Pin 13 of the micro U1 (89C738)

" All serial data from the microprocessor, for the synthesizer or the serial data chain or

for the computer during frequency programming emerges from pin 13 of the micro U1

(89C738).

U1 at pin 11

" All serial data to the micro from the Selcall decoder or from the computer during

frequency programming or from the serial chain loopback when enabled enters the

micro U1 at pin 11.

Keypad

" Keypad reading strobes emerge on pins 1, 2 and 3 of PL2 MCL, LCL and RCL.

These are short negative going pulses at 250Hz repetition rate.

" When keys are pressed in the matrix, either TR or BR pins 4 or 5 PL2 will be strobed

low.

" If all seems to be well yet keys are not being read check for shorts between the column

lines MCL, LCL and RCL.

DTMF keys

" Pressing keys on the DTMF microphone on an advanced model should produce a high

level on DV pin 14 of U9, (MC145436D).

" If this does not happen check that the DTMF tones at level 0.5volt p-p are reaching U9

pin 8.

- 42 -

Page 43

11.2 Transmitter test sequence

Refer to the test point overlay (HF-90 P.A. BOARD ALIGNMENT - POSITION REFERENCE) in

Section 12 of this manual, as well as the schematic diagram (HF-90 P.A. & POWER SUPPLY

90002) in Section 17 of this manual.

For these tests the radio should be connected to a power meter and dummy load via a 30dB

asymmetric Tee off to an oscilloscope. A channel in the range 3 - 6MHz should be chosen

for measurements.

6. Transmitter Power Supplies

" Press PTT and check that +5voltTX is present on pin 5 of U3 (LM358M). If not check

Q11 and D10.

" Press PTT and check that +15voltTX is present in the range 10 - 11.4volt on collector

of Q13 (BD136 on heatsink). If not check Q13 and U3:A bias voltages.

" Press PTT and check that +50volt rail comes up to approximately +55volt. Some sag

of this rail is normal on speech peaks and Selcalls. If +50volt rail remains at 14volt on

transmit, check first that the channel program does not specify low power and then

check for 25kHz switching wave forms on R2 and R3.

" A 3-step w ave form which vari es with duty cycle should be visible on the anode of

diode D5 in the centre of large toroid L5.

7. Lowpass filter selection

" The low-going lowpass filter selection pulses to the latching relays are emitted on pins

10 to 16 of U6 (ULN2003L). On a channel change, the common RST line is pulsed

and then the band of choice is pulsed. As the driving device is open collector, the lines

may be manually pulled low to test for switching by momentarily shorting the relevant

pin to ground. Refer to Table 3 (Section 8 of this manual) which details the expected

state on pins of U6.

" For the filters to operate correctly the serial data chain must be intact all the way to U7

pin 9 (74HC595D), and serial data should be visible on this pin during a channel

change.

8. Bias check

" Check that the bias settings for driver and PA are approximately 2.6volt on C49

positive and 3.7volt on C63 positive with PTT active.

" Check that Op-Amp outputs U11 pin 6 and U1 pin 6 are approximately half rail (6volt)

with PTT active and no modulation.

9. Signal check

" Apply a fully modulating 2-tone by external means.

" The 2-tone envelope should reach 0.8volt p-p on U11 pin 6, 6volt p-p on U1 pin 6,

3volt p-p on the gates of Q1 and Q2 (VN88AFDs), 7volt p-p on the gates of Q3 and

Q4, 70volt p-p on the drains of Q3 and Q4 (IRF830s) and finally 140volt p-p at the

output of T3. Note that these values are approximate and are most accurate in the rage

3 - 6MHz.

" For the above levels, the rectified ALC wave form at U3 pin 7 should be

approximately 9volt peak. A similar voltage should be present on the gate of Q9

(BSD22).

" If signals are larger than above up to a stage and then very small thereafter, then the

first stage with the small sig n als is the one to suspect.