Profichip VPC3+C User Manual

VPC3+C

User Manual

Revision 1.03

The C lever Alternative

Liability Exclusion

We have tested the contents of this document regarding

agreement with the hardware and software described.

Nevertheless, there may be deviations and we do not

guarantee complete agreement. The data in the

document is tested periodically, however. Required

corrections are included in subsequent versions. We

gratefully accept suggestions for improvements.

Copyright

Copyright © profichip GmbH 2004-2006.

All Rights Reserved.

Unless permission has been expressly granted, passing

on this document or copying it, or using and sharing its

content are not allowed. Offenders will be held liable. All

rights reserved, in the event a patent is granted or a

utility model or design is registered.

This document is subject to technical changes.

2 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Table of Contents

1 Introduction.................................................................5

2 Functional Description...............................................7

2.1 Overview ......................................................................................7

3 Pin Description............................................................9

3.1 Pin Assignment ............................................................................9

3.2 Pinout .........................................................................................11

4 Memory Organization ...............................................13

4.1 Overview ....................................................................................13

4.2 Control Parameters (Latches/Registers)....................................15

4.3 Organizational Parameters (RAM) .............................................17

5 ASIC Interface............................................................19

5.1 Mode Registers ..........................................................................19

5.1.1 Mode Register 0 .............................................................19

5.1.2 Mode Register 1 .............................................................21

5.1.3 Mode Register 2 .............................................................23

5.2 Status Register...........................................................................25

5.3 Interrupt Controller .....................................................................27

5.3.1 Interrupt Request Register.............................................. 28

5.3.2 Interrupt Acknowledge / Mask Register .......................... 31

5.4 Watchdog Timer.........................................................................31

5.4.1 Automatic Baud Rate Identification................................. 32

5.4.2 Baud Rate Monitoring ..................................................... 32

5.4.3 Response Time Monitoring.............................................32

6 PROFIBUS DP Interface............................................35

6.1 DP Buffer Structure ....................................................................35

6.2 Description of the DP Services...................................................38

6.2.1 Set_Slave_Add (SAP 55) ...............................................38

6.2.2 Set _Prm (SAP 61) .........................................................39

6.2.3 Chk_Cfg (SAP 62) ..........................................................43

6.2.4 Slave_Diag (SAP 60)......................................................44

6.2.5 Write_Read_Data / Data_Exchange (Default_SAP)....... 46

6.2.6 Global_Control (SAP 58) ................................................50

6.2.7 RD_Input (SAP 56) ......................................................... 51

6.2.8 RD_Output (SAP 57) ......................................................51

6.2.9 Get_Cfg (SAP 59)...........................................................52

VPC3+C User Manual

Revision 1.03 3

Copyright © profichip GmbH 2004-2006

Table of Contents

7 PROFIBUS DP Extensions .......................................53

7.1 Set_(Ext_)Prm (SAP 53 / SAP 61).............................................53

7.2 PROFIBUS DP-V1 .....................................................................54

7.2.1 Acyclic Communication Relationships ............................ 54

7.2.2 Diagnosis Model .............................................................57

7.3 PROFIBUS DP-V2 .....................................................................58

7.3.1 DXB (Data eXchange Broadcast) ................................... 58

7.3.2 IsoM (Isochron Mode).....................................................64

8 Hardware Interface....................................................69

8.1 Universal Processor Bus Interface.............................................69

8.1.1 Overview.........................................................................69

8.1.2 Bus Interface Unit ...........................................................69

8.1.3 Application Examples (Principles) ..................................73

8.1.4 Application with 80C32 (2K Byte RAM Mode) ................75

8.1.5 Application with 80C32 (4K Byte RAM Mode) ................76

8.1.6 Application with 80C165 .................................................77

8.2 Dual Port RAM Controller...........................................................77

8.3 UART..........................................................................................78

8.4 ASIC Test...................................................................................78

9 PROFIBUS Interface..................................................79

9.1 Pin Assignment ..........................................................................79

9.2 Example for the RS485 Interface ...............................................80

10 Operational Specifications.......................................81

10.1 Absolute Maximum Ratings........................................................81

10.2 Recommended Operating Conditions ........................................81

10.3 General DC Characteristics........................................................81

10.4 Ratings for the Output Drivers ....................................................82

10.5 DC Electrical Characteristics Specification for 5V Operation .....82

10.6 DC Electrical Characteristics Specification for 3.3V Operation ..83

10.7 Timing Characteristics ................................................................84

10.7.1 System Bus Interface......................................................84

10.7.2 Timing in the Synchronous Intel Mode ...........................85

10.7.3 Timing in the Asynchronous Intel Mode..........................87

10.7.4 Timing in the Synchronous Motorola Mode .................... 89

10.7.5 Timing in the Asynchronous Motorola Mode ..................91

10.8 Package .....................................................................................94

10.9 Processing Instructions ..............................................................96

4 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Introduction 1

1 Introduction

Profichip’s VPC3+C is a communication chip with processor interface for

intelligent PROFIBUS DP-Slave applications. It’s an enhancement of the

VPC3+B in terms of protocol functions and power consumption.

The VPC3+C handles the message and address identification, the data

security sequences and the protocol processing for PROFIBUS DP. In

addition the acyclic communication and alarm messages, described in

DPV1 extension, are supported. Furthermore the slave-to-slave

communication Data eXchange Broadcast (DXB) and the Isochronous Bus

Mode (IsoM), described in DPV2 extension, are also provided.

Automatic recognition and support of data transmissions rates up to 12

Mbit/s, the integration of the complete PROFIBUS DP protocol, 4K Byte

communication RAM and the configurable processor interface are features

to create high-performance PROFIBUS DP-Slave applications. The device

can be operated with either 3.3V or 5V single supply voltage. For 3.3V

operation the inputs are 5V tolerant.

Profichip’s VPC3+ is the predecessor of VPC3+C and VPC3+B. The chip

offers 2 kByte communication RAM and PROFIBUS DP functionality only

and is therefore suited for DP-Slave applications which do not require

DP-V1 or DP-V2 functions. The device can be operated with 5V single

supply only.

VPC3+ and VPC3+C are pin-compatible. Therefore VPC3+ can be

replaced by VPC3+C in existing applications without any restrictions or SWmodifications. However, downgrading from VPC3+C to VPC3+ is only

possible, if the additional features of VPC3+C (4K Byte RAM, DP-V1- or

DP-V2-functionality, 3.3V supply) are not used.

As there are also simple devices in the automation engineering area, such

as switches or thermoelements, that do not require a microcontroller for

data preprocessing, profichip offers a DP-Slave ASIC with 32 direct

input/output bits. The VPCLS2 handles the entire data traffic independently.

No additional microprocessor or firmware is necessary. The VPCLS2 is

compatible to existing chips.

Further information about our products or current and future projects is

available on our web page:

http://www.profichip.com.

VPC3+C User Manual

Revision 1.03 5

Copyright © profichip GmbH 2004-2006

1 Introduction

Notes:

6 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Functional Description 2

2 Functional Description

2.1 Overview

The VPC3+C makes a cost optimized design of intelligent PROFIBUS DPSlave applications possible.

The processor interface supports the following processor series:

Intel: 80C31, 80X86

Siemens: 80C166/165/167

Motorola: HC11-, HC16-, and HC916 types

The VPC3+C handles the physical layer 1 and the data link layer 2 of the

ISO/OSI-reference-model excluding the analog RS485 drivers.

The integrated 4K Byte Dual-Port-RAM serves as an interface between

the VPC3+C and the software/application. In case of using 2K Byte the

entire memory is divided into 256 segments, with 8 bytes each. Otherwise

in the 4K Byte mode the segment base addresses starts at multiple of 16.

Addressing by the user is done directly, however, the internal Micro

Sequencer (MS) addresses the RAM by means of the so-called basepointer. The base-pointer can be positioned at the beginning of a segment

in the memory. Therefore, all buffers must be located at the beginning of a

segment.

If the VPC3+C carries out a DP communication it automatically sets up all

DP-SAPs. The various telegram information are made available to the user

in separate data buffers (for example, parameter and configuration data).

Three buffers are provided for data communication (three for output data

and three for input data). As one buffer is always available for communication no resource problems can occur. For optimal diagnosis support, the

VPC3+C offers two Diagnosis-Buffers. The user enters the updated

diagnosis data into these buffers. One Diagnosis-Buffer is always assigned

to the VPC3+C.

The Bus Interface Unit is a parameterizable synchronous/asynchronous 8-

bit interface for various Intel and Motorola microcontrollers/processors. The

user can directly access the internal 2K/4K Byte RAM or the parameter

latches and control registers via the 11/12-bit address bus.

Procedure-specific parameters (Station_Address, control bits, etc.) must be

transferred to the Parameter Registers and to the Mode Registers after

power-on.

The MAC status can be observed at any time in the Status Register.

Various events (e.g. various indications, error events, etc.) are entered in

the Interrupt Controller. These events can be individually enabled via a

mask register. Acknowledgement takes place by means of the acknowledge register. The VPC3+C has a common interrupt output.

VPC3+C User Manual

Revision 1.03 7

Copyright © profichip GmbH 2004-2006

2 Functional Description

The integrated Watchdog Timer is operated in three different states:

BAUD_SEARCH, BAUD_CONTROL and DP_CONTROL.

The Micro Sequencer (MS) controls the entire process. It contains the DP-

Slave state machine (DP_SM).

The integrated 4K Byte RAM that operates as a Dual-Port-RAM contains

procedure-specific parameters (buffer pointer, buffer lengths,

Station_Address, etc.) and the data buffers.

In the UART, the parallel data flow is converted into the serial data flow and

vice-versa. The VPC3+C is capable of automatically identifying the baud

rates (9.6 Kbit/s - 12 Mbit/s).

The Idle Timer directly controls the bus times on the serial bus line.

8 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Pin Description 3

3 Pin Description

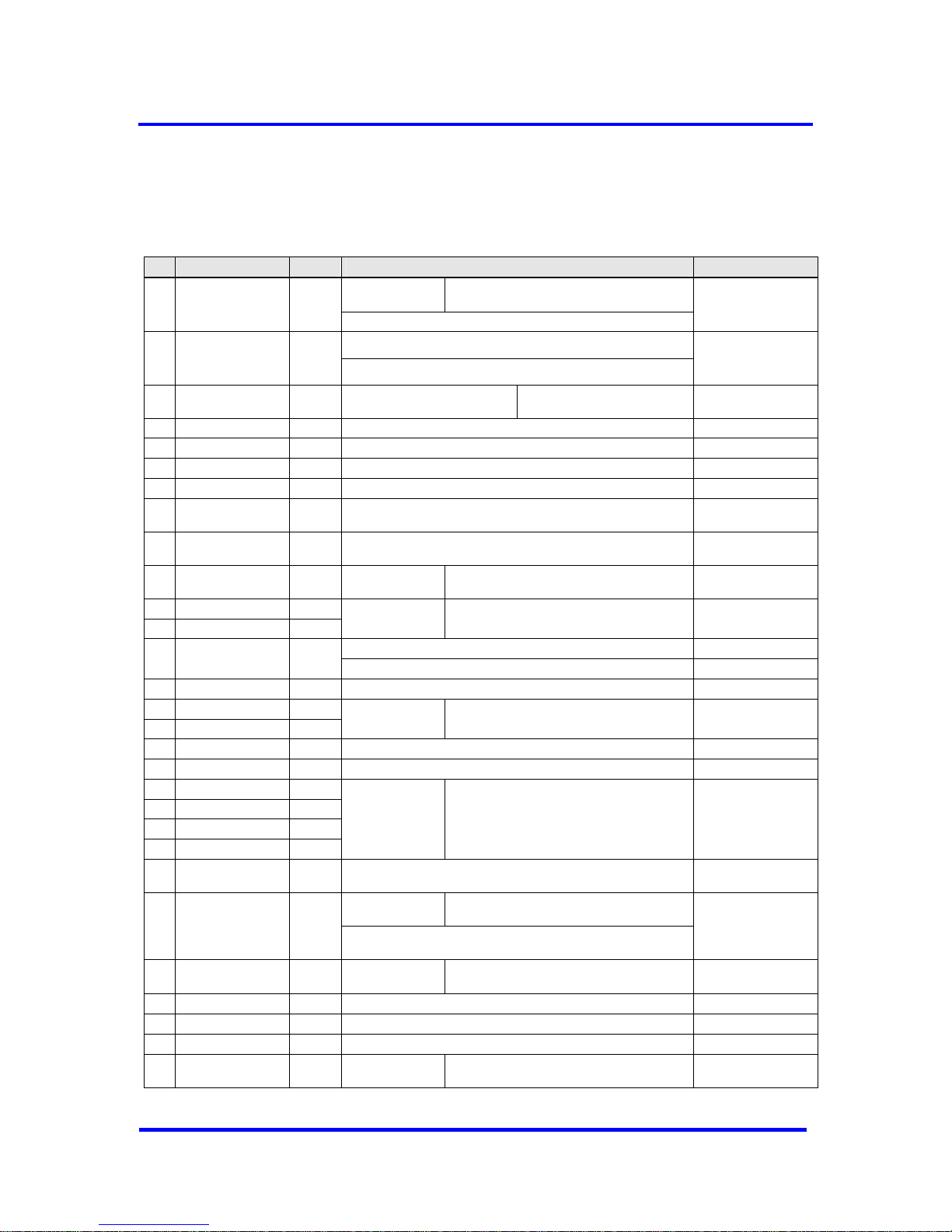

3.1 Pin Assignment

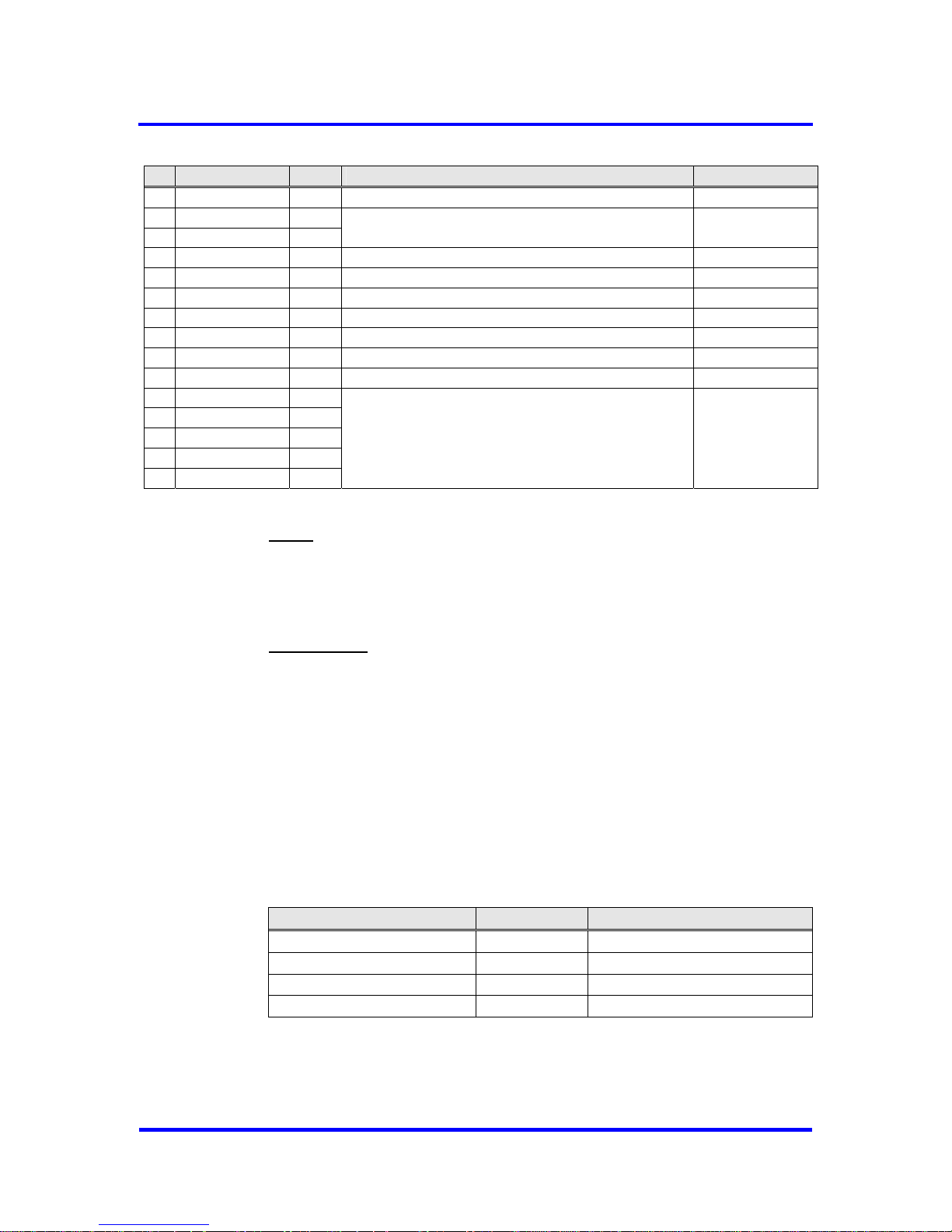

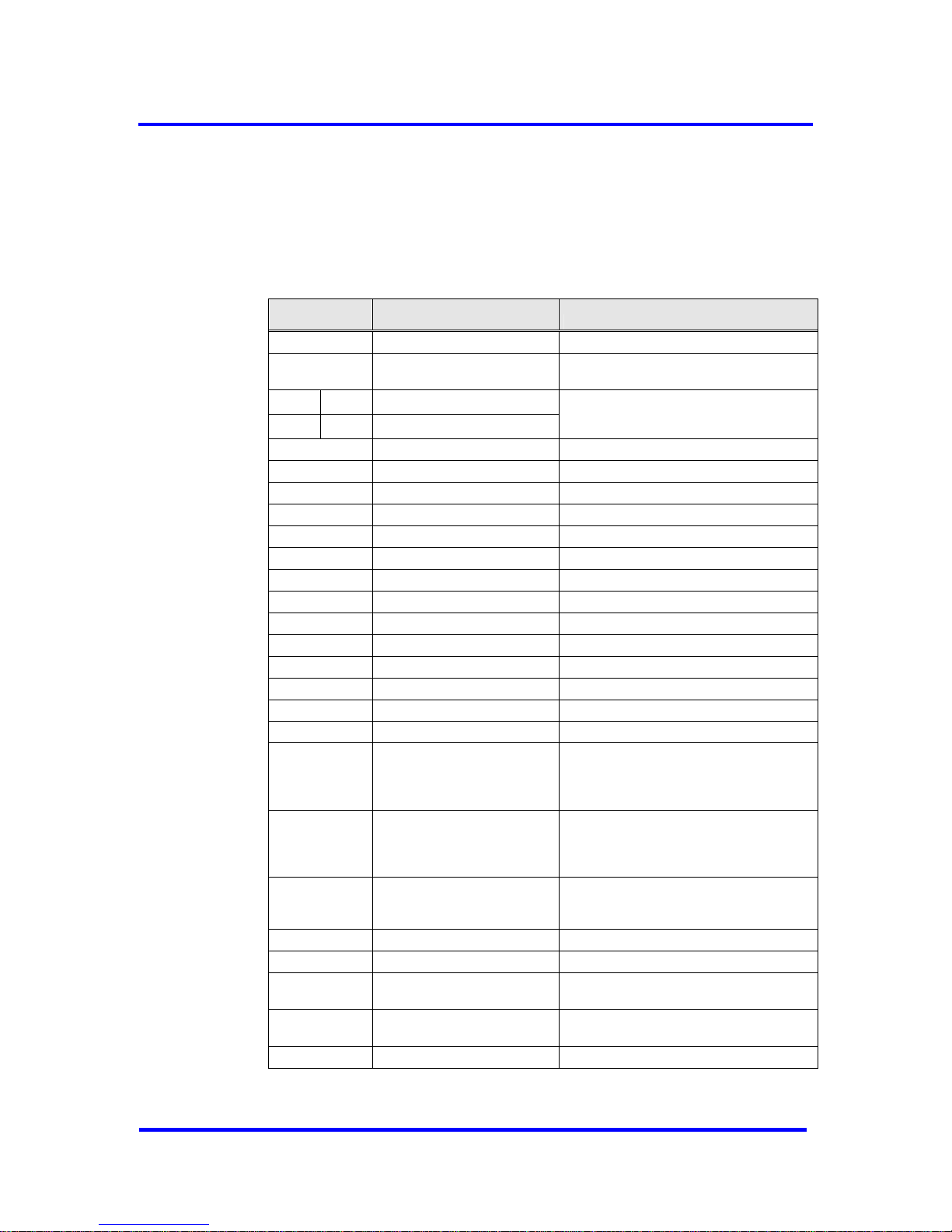

Pin Signal Name In/Out Description Source / Destination

XCS Chip-Select

C32 Mode (2K Byte RAM): connect to VDD

C165 Mode: CS-Signal

1

AB11

I(C)

Address Bus 11 (C32-Mode; 4K Byte RAM)

CPU (80C165)

XWR / E_CLOCK Write Signal / E_Clock for Motorola

2

AB11

I(C)

Address Bus 11 (Asynchronous Motorola Mode; 4K Byte RAM)

CPU

3 DIVIDER I(C)

Setting the scaling

factor for CLKOUT2/4

‘0’ = CLK divided by 4

’1’ = CLK divided by 2

Configuration Pin

4 XRD / R_W I(C) Read Signal / Read _Write for Motorola CPU

5 CLK I(TS) System Clock Input, 48 MHz System

6 VSS

7 CLKOUT2/4 O Clock Output (System Clock divided by 2 or 4) System, CPU

8 XINT/MOT I(C)

‘0’ = Intel Interface

’1’ = Motorola Interface

Configuration Pin

9 X/INT O Interrupt

CPU; InterruptController

10 AB10 I(CPD) Address Bus

C32 Mode: ‘0’

C165 Mode: Address Bus

System, CPU

11 DB0 I(C)/O

12 DB1 I(C)/O

Data Bus

C32 Mode: Data/Address Bus multiplexed

C165 Mode: Data/Address Bus separated

CPU, Memory

XDATAEXCH Indicates DATA-EXCH state for PROFIBUS DP LED

13

SYNC

O

Synchronization Signal for Isochron Mode (see section 8.3.2) CPU

14 XREADY/XDTACK O Ready for external CPU System, CPU

15 DB2 I(C)/O

16 DB3 I(C)/O

Data Bus

C32 mode: Data /Address Bus multiplexed

C165 mode: Data/Address Bus separate

CPU, Memory

17 VSS

18 VDD

19 DB4 I(C)/O

20 DB5 I(C)/O

21 DB6 I(C)/O

22 DB7 I(C)/O

Data Bus

C32 mode: Data/Address Bus multiplexed

C165 mode: Data/Address Bus separate

CPU, Memory

23 MODE I

‘0’ = 80C166 Data/Address Bus separated; Ready Signal

’1’ = 80C32 Data/Address Bus multiplexed, fixed Timing

Configuration Pin

ALE / AS

Address Latch

Enable

C32 mode: ALE

C165 mode: ‘0’ (2K Byte RAM)

24

AB11

I(C)

Address Bus 11 (Asynchronous Intel and

Synchronous Motorola Mode; 4K Byte RAM)

CPU

25 AB9 I Address Bus

C32 Mode: <log>0

C165 Mode: Address Bus

CPU, Memory

26 TXD O Serial Transmit Port PROFIBUS Interface

27 RTS O Request to Send PROFIBUS Interface

28 VSS

29 AB8 I(C) Address Bus

C32 mode: ‘0’

C165 mode: Address Bus

CPU, Memory

VPC3+C User Manual

Revision 1.03 9

Copyright © profichip GmbH 2004-2006

3 Pin Description

Pin Signal Name In/Out Description Source / Destination

30 RXD I(C) Serial Receive Port PROFIBUS Interface

31 AB7 I(C)

32 AB6 I(C)

Address Bus CPU, Memory

33 XCTS I(C) Clear to Send: ‘0’ = send enable FSK Modem

34 XTEST0 I(C) Pin must be connected to VDD.

35 XTEST1 I(C) Pin must be connected to VDD.

36 RESET I(CS) Connect Reset Input with CPU’s port pin.

37 AB4 I(C) Address Bus CPU, Memory

38 VSS

39 VDD

40 AB3 I(C)

41 AB2 I(C)

42 AB5 I(C)

43 AB1 I(C)

44 AB0 I(C)

Address Bus CPU, Memory

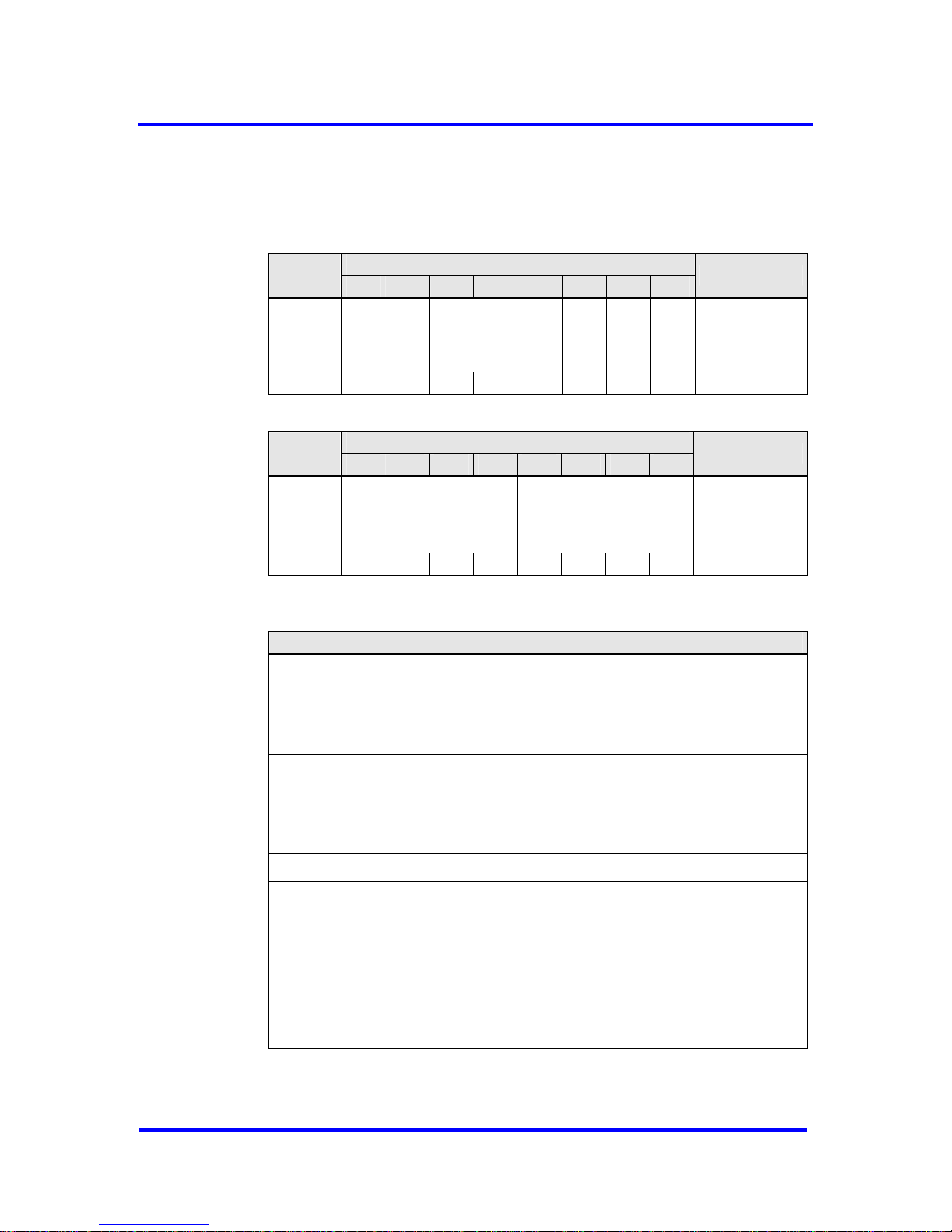

Figure 3-1: Pin Assignment

Notes: All signals that begin with X.. are LOW active.

C32-Mode means ‘Synchronous Intel Mode’ and

C165-Mode means ‘Asynchronous Intel Mode’.

VDD = +5 V

VSS = 0 V

Input Levels:

I ( C ) : CMOS

I ( CS ) : CMOS, Schmitt-Trigger

I (CPD ) : CMOS, pulldown

I (TS ) : TTL, Schmitt-Trigger

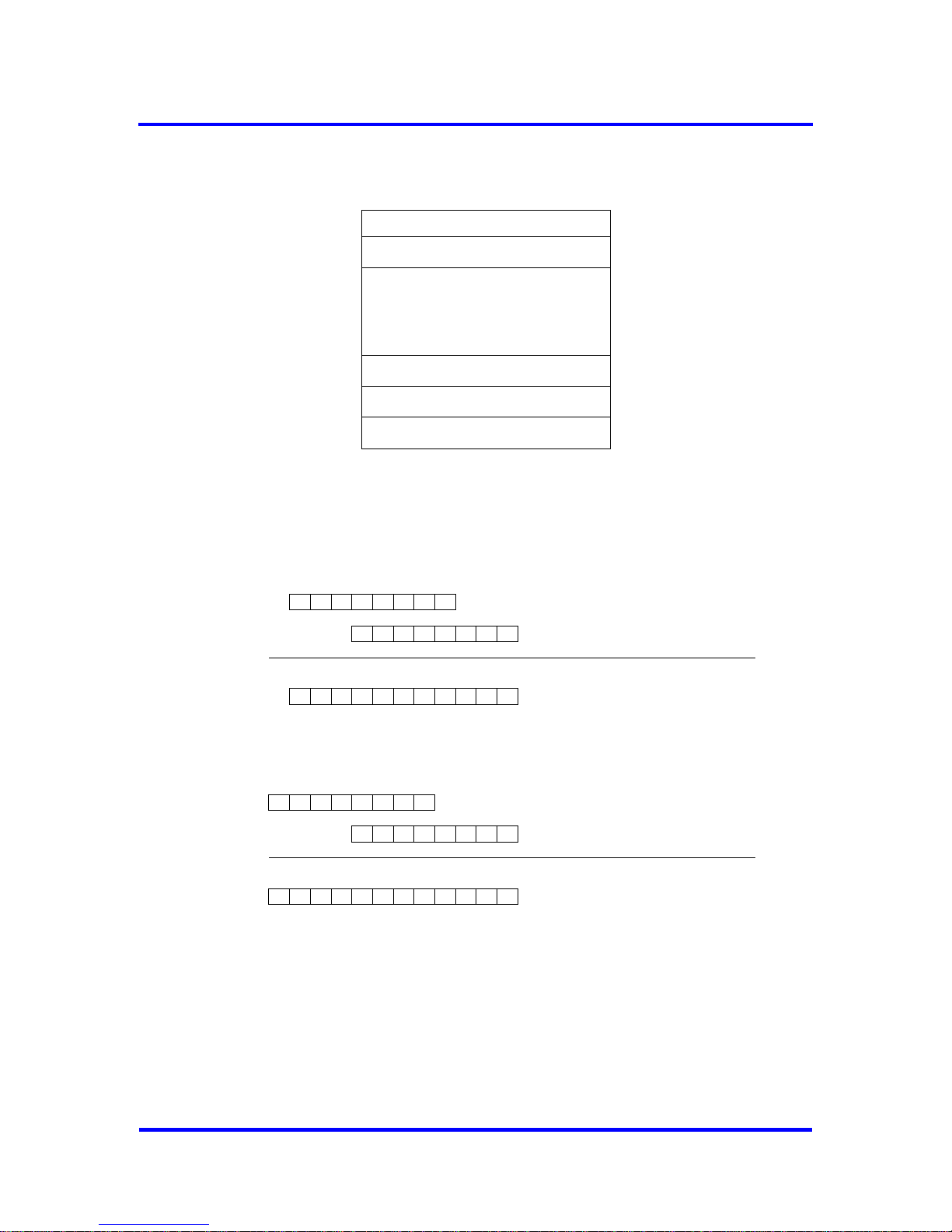

4K Byte RAM extension

Beginning with Step B of the VPC3+ the communication RAM has been

extended to 4K Byte, whereas Step A only has 2K Byte. To access the

entire 4K Byte RAM in VPC3+C an additional address signal AB11 is

required. Which pin is assigned to A11 depends on the Processor Interface

Mode used (see Figure 3-2). Due to compatibility reasons the pin which is

now assigned to A11 was unused in Step A for the certain Interface Mode.

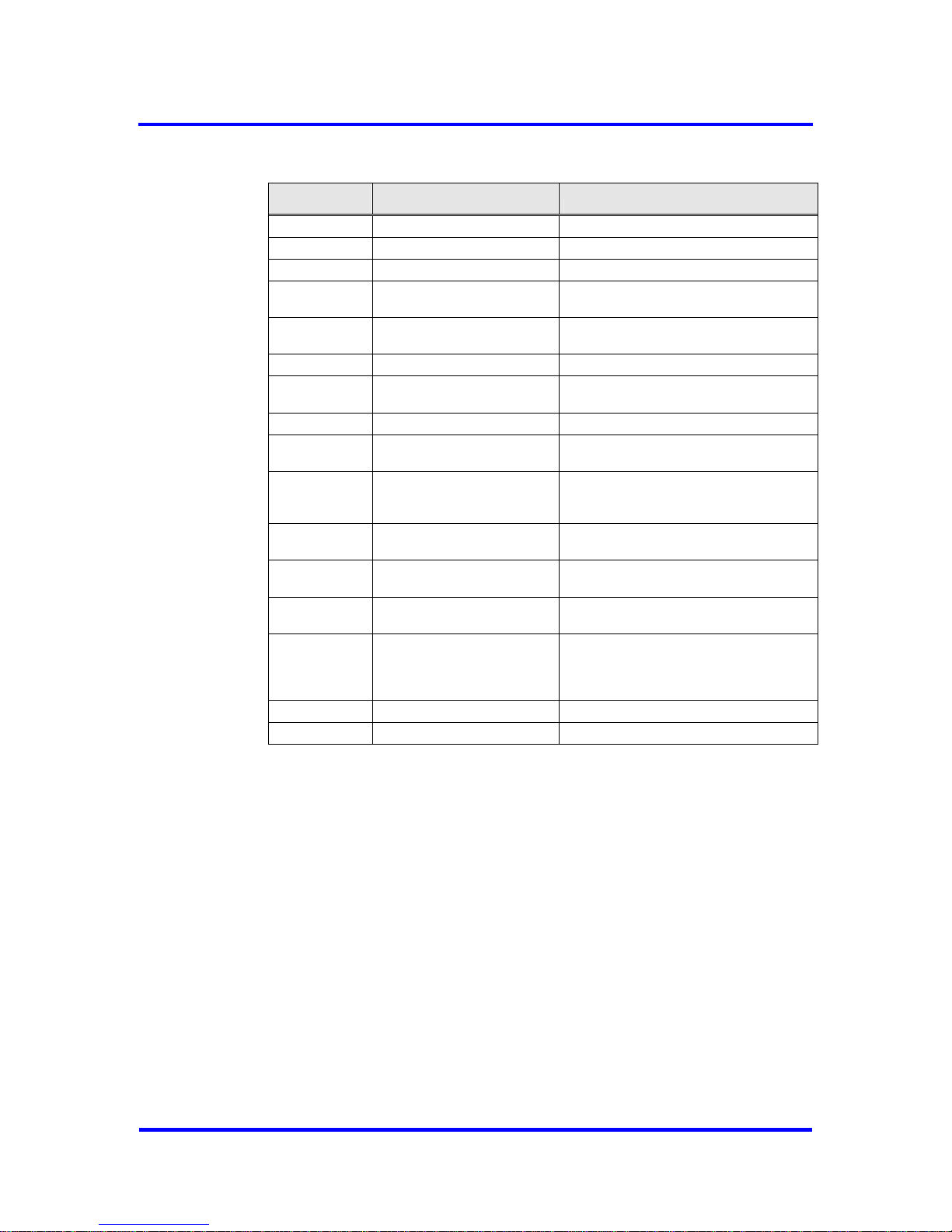

Processor Interface Mode Pin Signal Name

Synchronous Intel Mode 1 XCS

Asynchronous Intel Mode 24 ALE/AS

Asynchronous Motorola Mode 2 XWR/E_CLOCK

Synchronous Motorola Mode 24 ALE/AS

Figure 3-2 : Pin assignment for AB11

The 4K Byte RAM extension must be enabled in Mode Register 2 (see

section 5.1.3). By default the 4K Byte mode is disabled.

10 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Pin Description 3

3.2 Pinout

VPC3+C has a 44-pin PQFP housing with the following pinout:

DB7

DB6

DB5

DB4

VDD

VSS

DB3

DB2

XREADY/XDTACK

XDATAEXCH/SYNC

DB1

XCS/AB11

WR/E_CLOCK/AB11

DIVIDER

XRD/R_W

CLK

VSS

CLCKOUT2/4

XINT/MOT

X/INT

AB10

DB0

XCTS

AB6

AB7

RXD

AB8

VSS

RTS

TXD

AB9

ALE/AS/AB11

MODE

XTEST0

XTEST1

RESET

AB4

VSS

VDD

AB3

AB2

AB5

AB1

AB0

111

12

22

2333

34

44

Figure 3-3: VPC3+C Pinout

For details about package outline and dimensions see section 10.8.

VPC3+C User Manual

Revision 1.03 11

Copyright © profichip GmbH 2004-2006

3 Pin Description

Notes:

12 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Memory Organization 4

4 Memory Organization

4.1 Overview

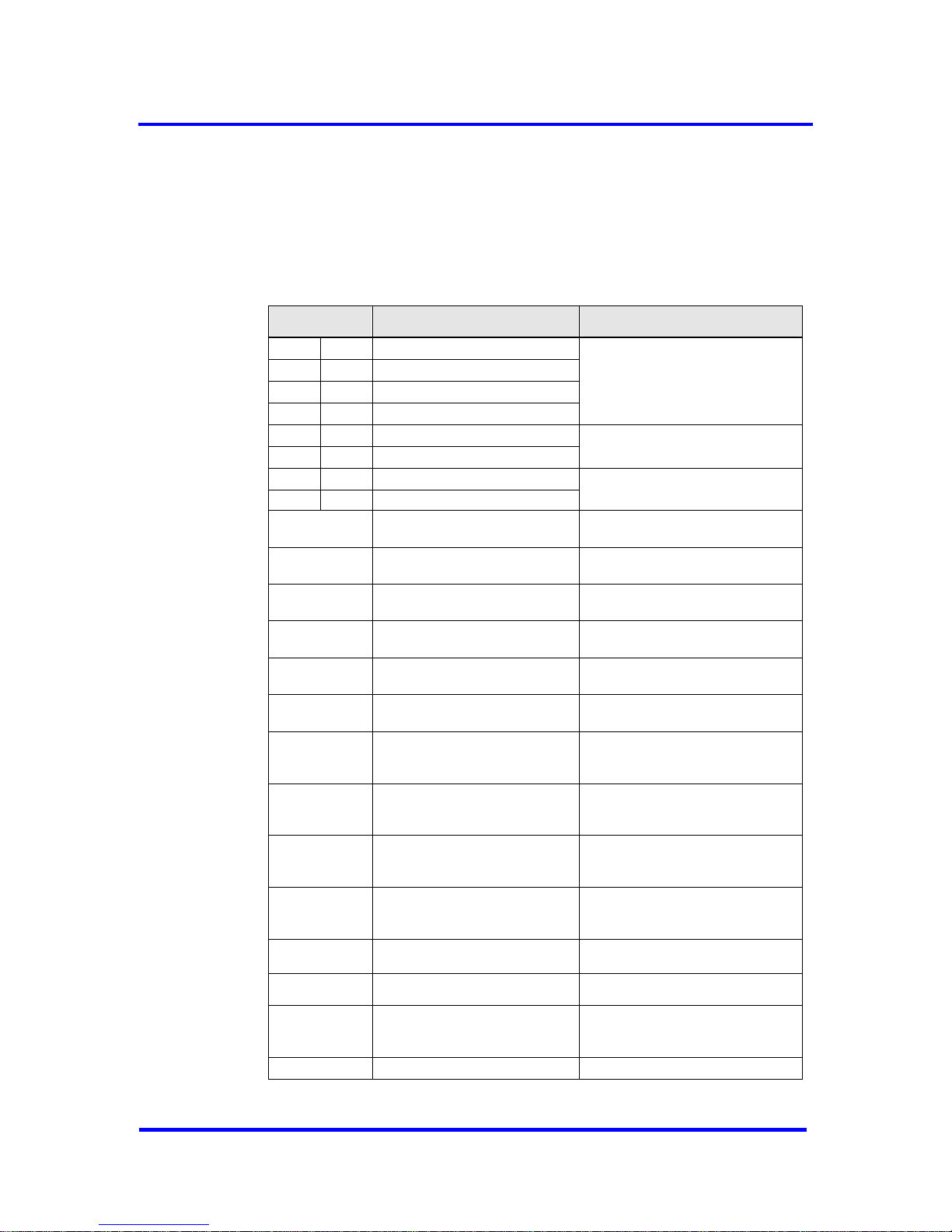

The internal Control Parameters are located in the first 21 addresses. The

latches/registers either come from the internal controller or influence the

controller. Certain cells are read- or write-only. The internal working cells,

which are not accessible by the user, are located in RAM at the same

address locations.

The Organizational Parameters are located in RAM beginning with address

16H. The entire buffer structure (for the DP-SAPs) is based on these parameters. In addition, general parameter data (Station_Address,

Ident_Number, etc.) and status information (Global_Control command, etc.)

are also stored in these cells.

Corresponding to the parameter setting of the Organizational Parameters,

the user-generated buffers are located beginning with address 40H. All

buffers or lists must begin at segment addresses (8 bytes segmentation for

2K Byte mode, 16 bytes segmentation for 4K Byte mode).

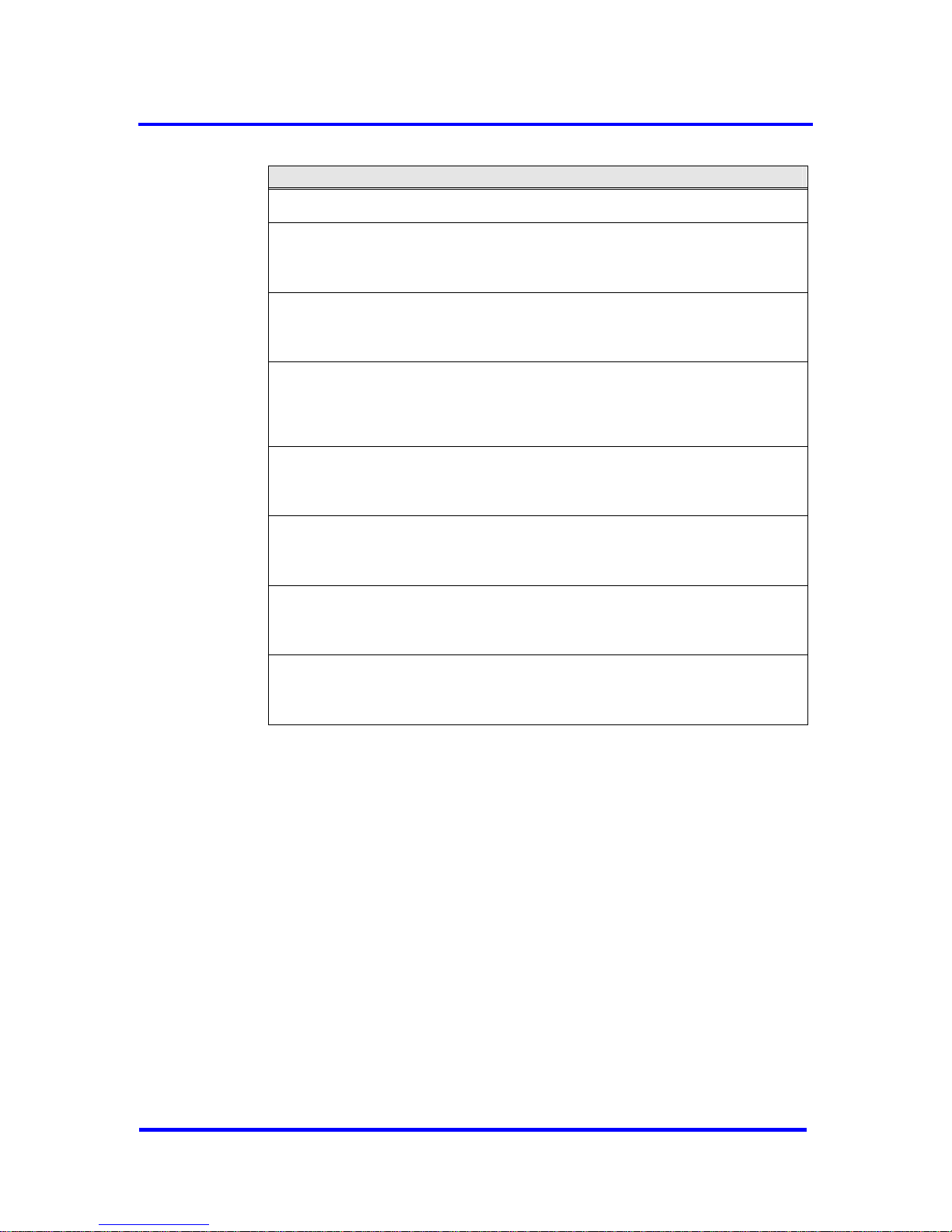

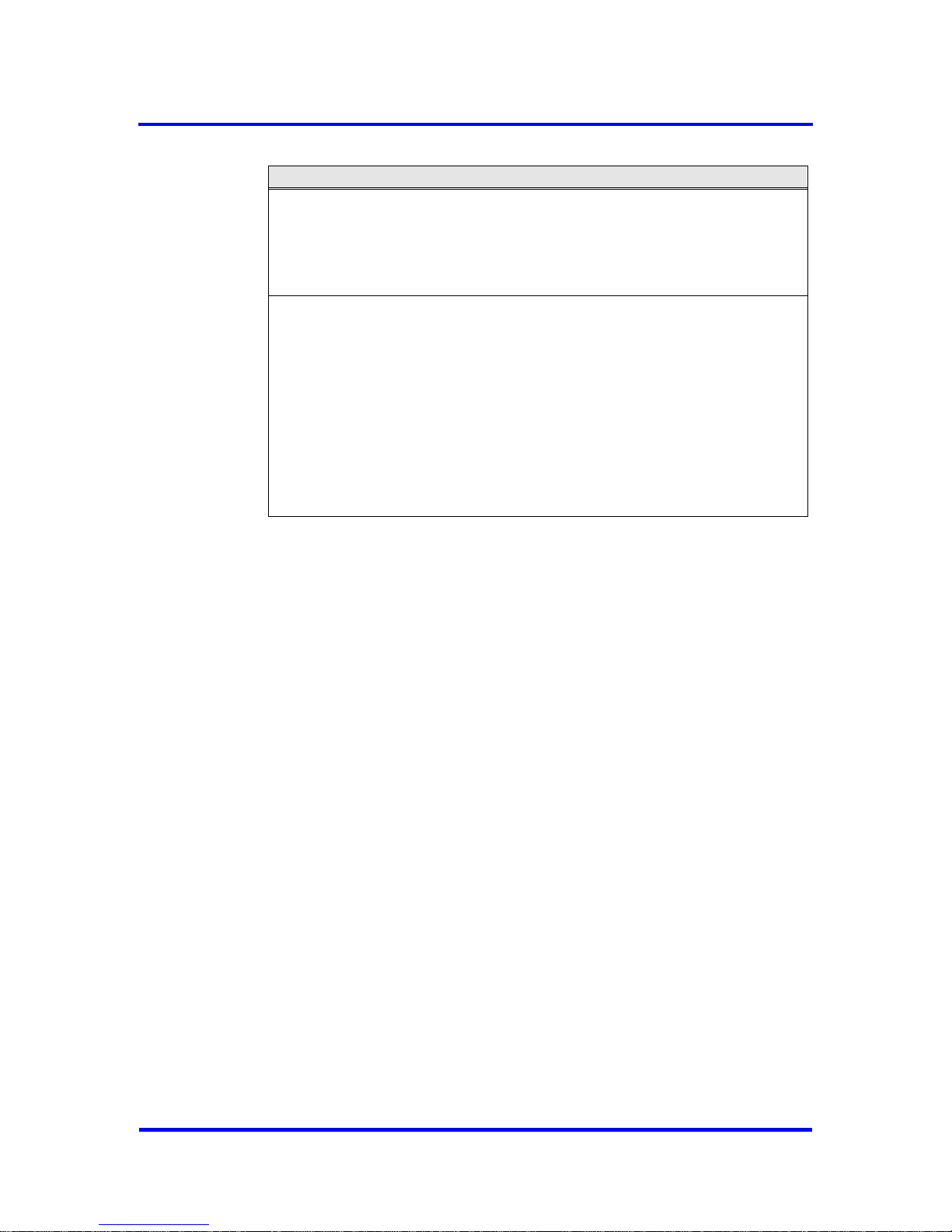

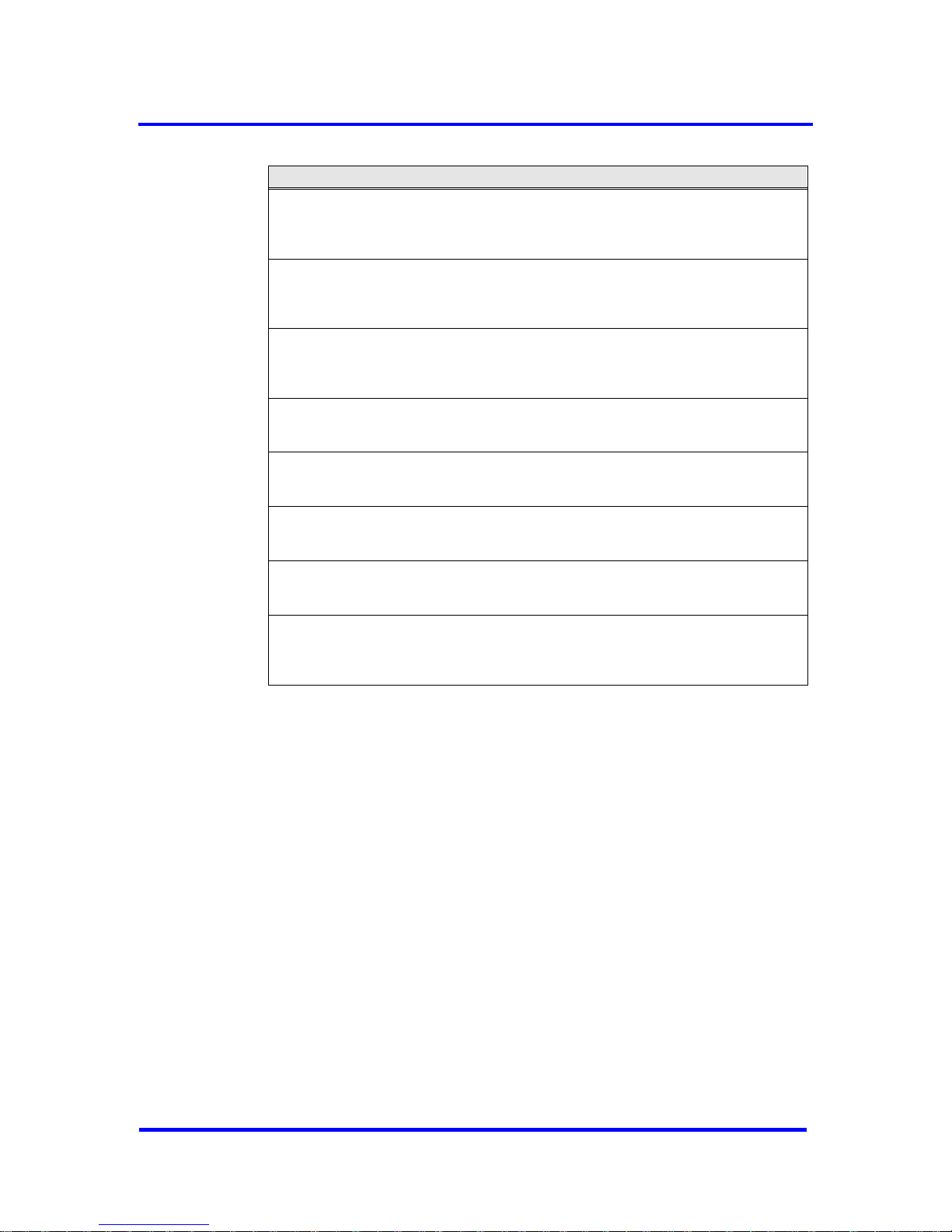

Address Function

000H

:

015H

Control Parameters

(latches/registers) (21 bytes)

Internal working cells

016H

:

03FH

Organizational Parameters (42 bytes)

040H

:

7FFH (FFFH)

DP-buffers: Data in (3)*

Data out (3)**

Diagnosis data(2)

Parameter data (1)

Configuration data (2)

Auxiliary buffers (2)

SSA-buffer (1)

DP-V1-buffer: SAP-List (1)

Indication / Response buffers ***

DP-V2-buffer: DXB out (3)****

DXB-buffers (2)

CS-buffers (1)

Figure 4-1: Memory Table

* Data in means input data from DP-Slave to DP-Master

** Data out means output data from DP-Master to DP-Slave

*** number of buffers depends on the entries in the SAP-List

**** DXB out means input data from another DP-Slave (slave-to-slave communication)

VPC3+C User Manual

Revision 1.03 13

Copyright © profichip GmbH 2004-2006

4 Memory Organization

Internal VPC3+C RAM (2K/4K Byte)

Segment 0

Segment 1

Segment 2

8/16 bit segment addresses

(pointer to the buffers)

Segment 254

Segment 255

Building of the physical buffer address:

2K Byte Mode:

7 0

Segment base address (8 bit)

0 0 0 0 0 Offset (3 bit)

+

10 0

Physical address (11 bit)

4K Byte Mode:

7 0

Segment base address (8 bit)

0 0 0 0 Offset (4 bit)

+

11 0

Physical address (12 bit)

14 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Memory Organization 4

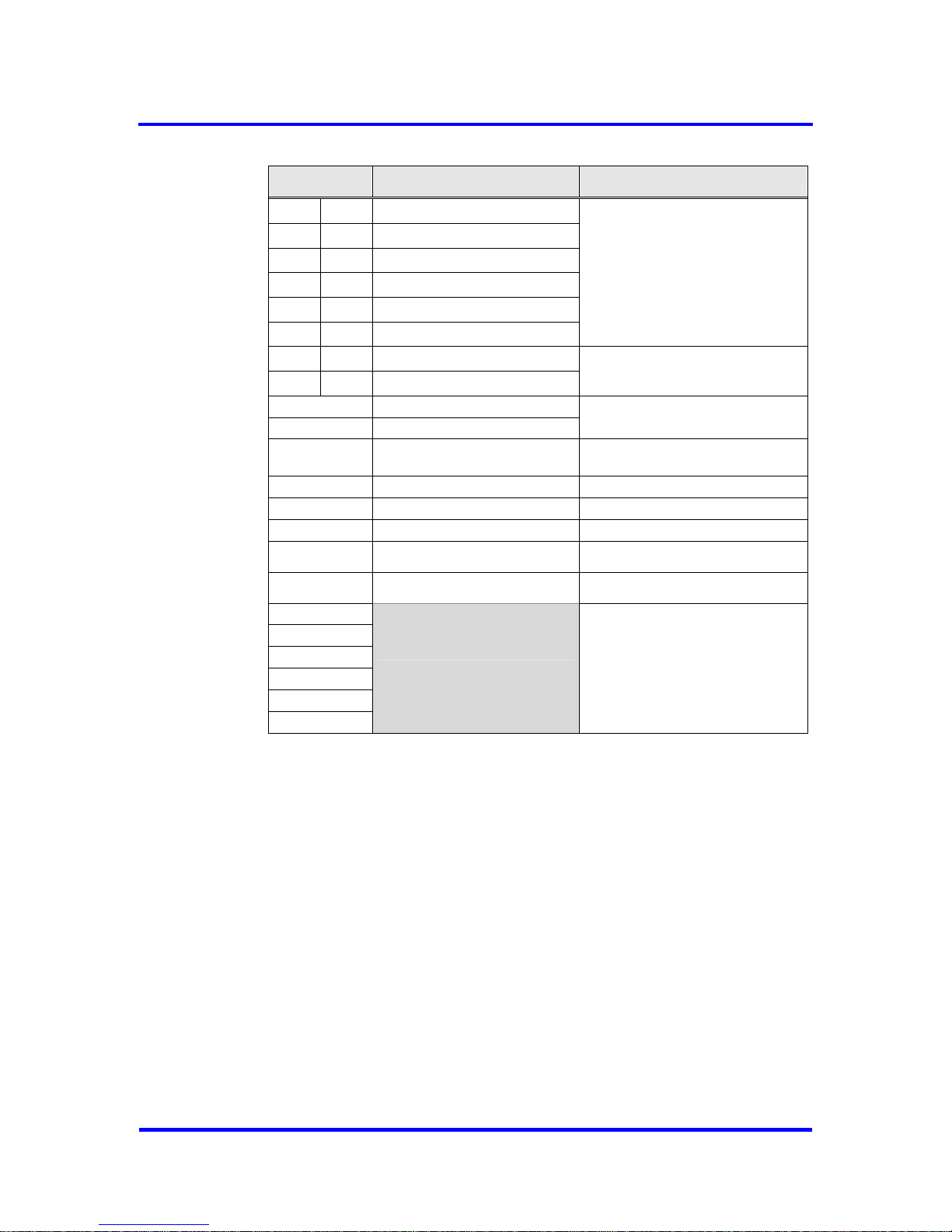

4.2 Control Parameters (Latches/Registers)

These cells can be either read-only or write-only. In the Motorola Mode the

VPC3+C carries out ‘address swapping’ for an access to the address

locations 00H - 07H (word registers). That is, the VPC3+C internally

generates an even address from an odd address and vice-versa.

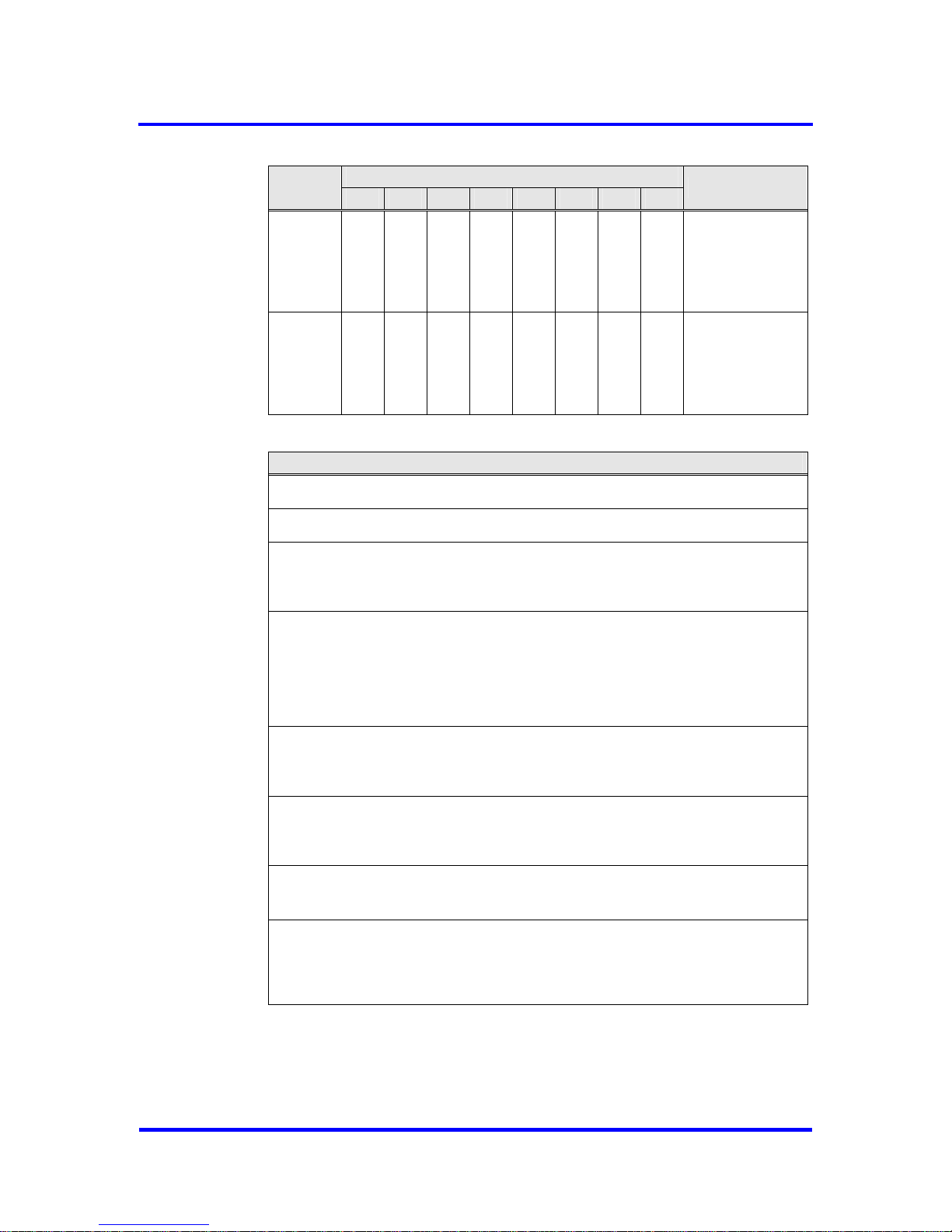

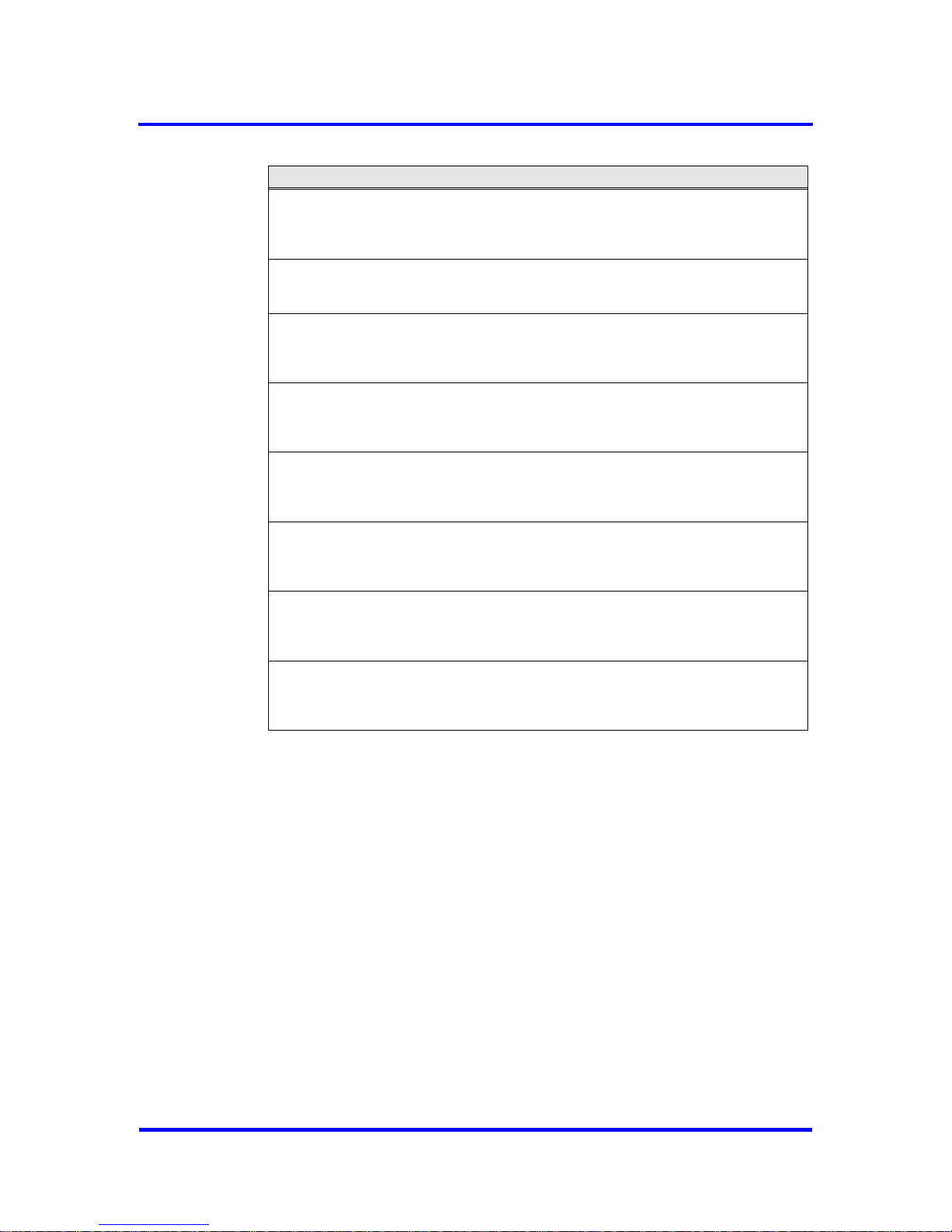

Address

Intel Mot. Name Bit No. Significance (Read Access!)

00H 01H

Int-Req-Reg 7..0

01H 00H

Int-Req-Reg 15..8

02H 03H

Int−Reg 7..0

03H 02H

Int−Reg 15..8

Interrupt Controller Register

04H 05H

Status-Reg 7..0

05H 04H

Status-Reg 15..8

Status Register

06H 07H

Mode-Reg 0 7..0

07H 06H

Mode-Reg 0 15..8

Mode Register 0

08H Din_Buffer_SM 7..0

Buffer assignment of the

DP_Din_Buffer_State_Machine

09H New_Din_Buffer_Cmd 1..0

The user makes a new DP Din_Buf

available in the N state.

0AH Dout_Buffer_SM 7..0

Buffer assignment of the

DP_Dout_Buffer_State_Machine

0BH Next_Dout_Buffer_Cmd 3..0

The user fetches the last DP

Dout_Buf from the N state

0CH Diag_Buffer_SM 3..0

Buffer assignment for the

DP_Diag_Buffer_State_Machine

0DH New_Diag_Buffer_Cmd 1..0

The user makes a new DP

Diag_Buf available to the VPC3+C.

0EH User_Prm_Data_Okay 1..0

The user positively acknowledges

the user parameter setting data of a

Set_(Ext_)Prm telegram.

0FH User_Prm_Data_Not_Okay 1..0

The user negatively acknowledges

the user parameter setting data of a

Set_(Ext_)Prm telegram.

10H User_Cfg_Data_Okay 1..0

The user positively acknowledges

the configuration data of a Chk_Cfg

telegram.

11H User_Cfg_Data_Not_Okay 1..0

The user negatively acknowledges

the configuration data of a Chk_Cfg

telegram.

12H

DXBout_Buffer_SM 7..0

Buffer assignment of the

DXBout_Buffer_State_Machine

13H

Next_DXBout_Buffer_Cmd 2..0

The user fetches the last

DXBout Buf from the N state

14H SSA_Buffer_Free_Cmd

The user has fetched the data from

the SSA_Buf and enables the buffer

again.

15H

Mode-Reg 1 7..0

Figure 4-2: Assignment of the Internal Parameter-Latches for READ

VPC3+C User Manual

Revision 1.03 15

Copyright © profichip GmbH 2004-2006

4 Memory Organization

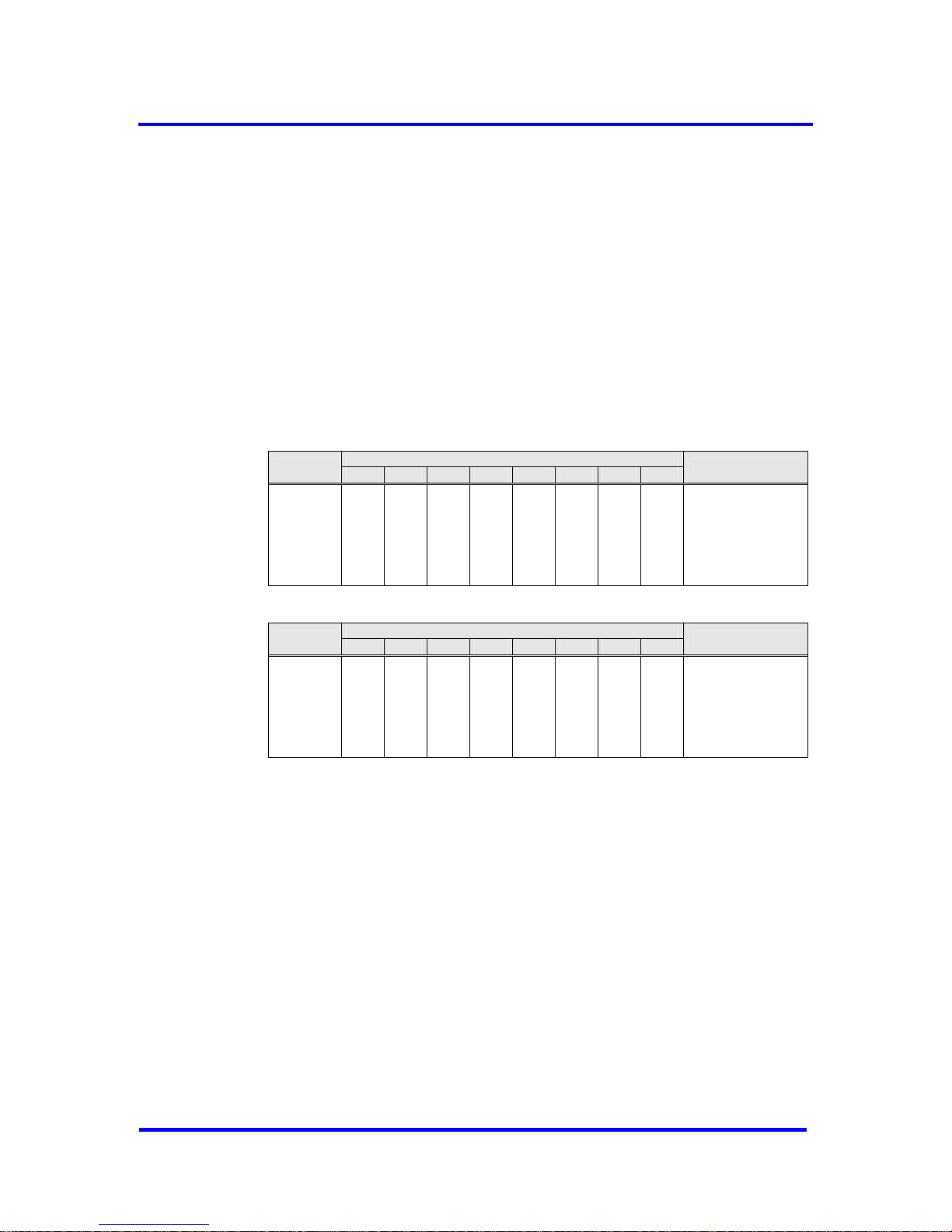

Address

Intel Mot.

Name Bit No. Significance (Write Access!)

00H 01H Int-Req-Reg 7..0

01H

00H Int-Req_Reg 15..8

02H

03H Int-Ack-Reg 7..0

03H

02H Int-Ack-Reg 15..8

04H

05H

Int−Mask-Reg 7..0

05H

04H

Int−Mask-Reg 15..8

Interrupt-Controller-Register

06H

07H Mode-Reg0 7..0

07H

06H Mode-Reg0 15..8

Setting parameters for individual bits

08H

Mode-Reg1-S 7..0

09H

Mode-Reg1-R 7..0

0AH WD_BAUD_CONTROL_Val 7..0

Square-root value for

baud rate monitoring

0BH

minT

SDR

_Val 7..0

minT

SDR

time

0CH

Mode-Reg2 7..0

Mode Register 2

0DH

Sync_PW_Reg 7..0 Sync Pulse Width Register

0EH

Control_Command_Reg 7..0

Control_Command value for

comparison with SYNCH telegram

0FH

Group_Select_Reg 7..0

Group_Select value for comparison

with SYNCH telegram

10H

11H

12H

13H

14H

15H

Reserved

Figure 4-3: Assignment of the Internal Parameter-Latches for WRITE

16 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Memory Organization 4

4.3 Organizational Parameters (RAM)

The user stores the organizational parameters in the RAM under the

specified addresses. These parameters can be written and read.

Address

Intel Mot.

Name Bit No. Significance

16H R_TS_Adr Setup Station_Address of the VPC3+C

17H SAP_List_Ptr

Pointer to a RAM address which is preset

with FFh or to SAP-List

18H

19H

R_User_WD_Value 7..0

19H

18H

R_User_WD_Value 15..8

In DP_Mode an internal 16-bit watchdog

timer monitors the user.

1AH R_Len_Dout_Buf Length of the 3 Dout_Buf

1BH R_Dout_Buf_Ptr1 Segment base address of Dout_Buf 1

1CH R_Dout_Buf_Ptr2 Segment base address of Dout_Buf 2

1DH R_Dout_Buf_Ptr3 Segment base address of Dout_Buf 3

1EH R_Len_Din_Buf Length of the 3 Din_Buf

1FH R_Din_Buf_Ptr1 Segment base address of Din_Buf 1

20H R_Din_Buf_Ptr2 Segment base address of Din_Buf 2

21H R_Din_Buf_Ptr3 Segment base address of Din_Buf 3

22H R_Len_DXBout_Buf Length of the 3 DXBout_Buf

23H R_DXBout_Buf_Ptr1 Segment base address of DXBout_Buf 1

24H R_Len Diag_Buf1 Length of Diag_Buf 1

25H R_Len Diag_Buf2 Length of Diag_Buf 2

26H R_Diag_Buf_Ptr1 Segment base address of Diag_Buf 1

27H R_Diag_Buf_Ptr2 Segment base address of Diag_Buf 2

28H R_Len_Cntrl_Buf1

Length of Aux_Buf 1 and the

corresponding control buffer, for example

SSA_Buf, Prm_Buf, Cfg_Buf,

Read_Cfg_Buf

29H R_Len_Cntrl_Buf2

Length of Aux_Buf 2 and the

corresponding control buffer, for example

SSA_Buf, Prm_Buf, Cfg_Buf,

Read_Cfg_Buf

2AH R_Aux_Buf_Sel

Bit array; defines the assignment of the

Aux_Buf 1 and 2 to the control buffers

SSA_Buf, Prm_Buf, Cfg_Buf

2BH R_Aux_Buf_Ptr1 Segment base address of Aux_Buf 1

2CH R_Aux_Buf_Ptr2 Segment base address of Aux_Buf 2

2DH R_Len_SSA_Data

Length of the input data in the

Set_Slave_Address_Buf

2EH R_SSA_Buf_Ptr

Segment base address of the

Set_Slave_Address_Buf

2FH R_Len_Prm_Data Length of the input data in the Prm_Buf

VPC3+C User Manual

Revision 1.03 17

Copyright © profichip GmbH 2004-2006

4 Memory Organization

Address

Intel Mot.

Name Bit No. Significance

30H R_Prm_Buf_Ptr Segment base address of the Prm_Buf

31H R_Len_Cfg_Data Length of the input data in the Cfg_Buf

32H R_Cfg_Buf_Ptr Segment base address of the Cfg_Buf

33H

R_Len_Read_Cfg_Data

Length of the input data in the

Read_Cfg_Buf

34H R_Read_Cfg_Buf_Ptr

Segment base address of the

Read_Cfg_Buf

35H R_Len_DXB_Link_Buf Length of the DXB_Linktable

36H R_DXB_Link_Buf_Ptr

Segment base address of the

DXB_Link_Buf

37H R_Len_DXB_Status_Buf Length of the DXB_Status

38H R_DXB_Status_Buf_Ptr

Segment base address of the

DXB_Status_Buf

39H R_Real_No_Add_Change

This parameter specifies whether the

Station_Address may be changed again

later.

3AH R_Ident_Low

The user sets the parameters for the

Ident_Number_Low value.

3BH R_Ident_High

The user sets the parameters for the

Ident_Number_High value.

3CH R_GC_Command

The Control_Command of Global_Control

last received

3DH R_Len_Spec_Prm_Buf

If parameters are set for the

Spec_Prm_Buffer_Mode (see Mode

Register 0), this cell defines the length of

the Prm_Buf.

3EH R_DXBout_Buf_Ptr2 Segment base address of DXBout_Buf 2

3FH R_DXBout_Buf_Ptr3 Segment base address of DXBout_Buf 3

Figure 4-4: Assignment of the Organizational Parameters

18 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

ASIC Interface 5

5 ASIC Interface

5.1 Mode Registers

In the VPC3+C parameter bits that access the controller directly or which

the controller directly sets are combined in three Mode Registers (0, 1 and

2).

5.1.1 Mode Register 0

Setting parameters for Mode Register 0 may take place in the Offline

state only (for example, after power-on). The VPC3+C may not exit the

Offline state until Mode Register 0, all Control and Organizational Parameters are loaded (START_VPC3 = 1 in Mode Register 1).

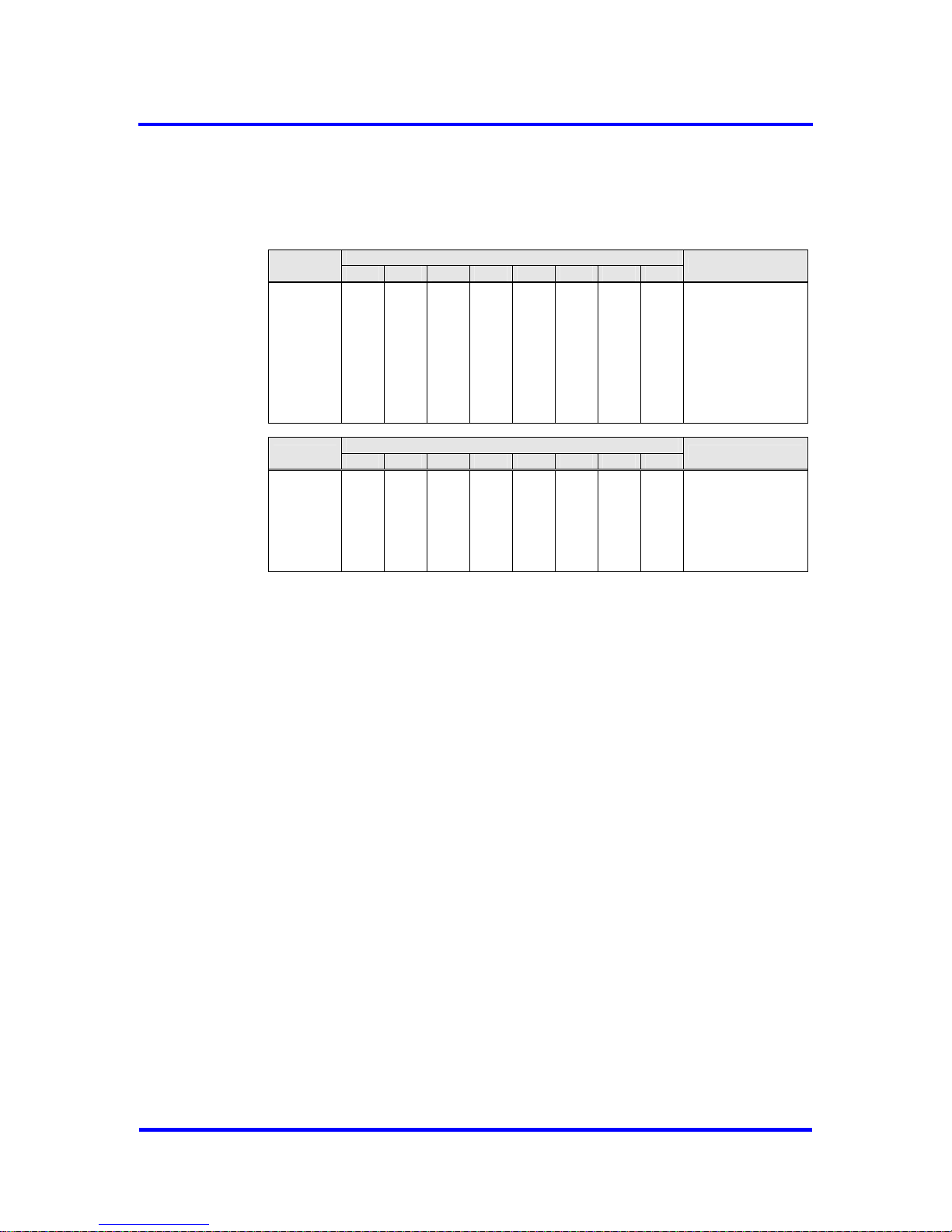

Bit Position

Address

7 6 5 4 3 2 1 0

Designation

06H

(Intel)

Freeze_

Supported

Sync_

Supported

Early_Rdy

Int_Pol

minT

SDR

WD_Base

Dis_Stop_

Control

Dis_Start_

Control

Mode Reg 0

7 .. 0

See below for

coding

Bit Position

Address

15 14 13 12 11 10 9 8

Designation

07H

(Intel)

Reserved

PrmCmd_

Supported

Spec_Clear_

Mode *)

Spec_Prm_

Buf_Mode **)

Set_Ext_Prm

_Supported

User_Time_

Base

EOI_Time_

Base

DP_Mode

Mode Reg 0

15 .. 8

See below for

coding

*) If Spec_Clear_Mode = 1 (Fail Safe Mode) the VPC3+C will accept Data_Exchange

telegrams without any output data (data unit length = 0) in the state DATA-EXCH. The

reaction to the outputs can be parameterized in the parameterization telegram.

**) When a large number of parameters have to be transmitted from the DP-Master to the

DP-Slave, the Aux-Buffer 1/2 must have the same length as the Parameter-Buffer.

Sometimes this could reach the limit of the available memory in the VPC3+C. When

Spec_Prm_Buf_Mode = 1 the parameterization data are processed directly in this special

buffer and the Aux-Buffers can be held compact.

VPC3+C User Manual

Revision 1.03 19

Copyright © profichip GmbH 2004-2006

5 ASIC Interface

Mode Register 0, Low-Byte, Address 06H (Intel):

bit 7

Freeze_Supported: Freeze_Mode support

0 = Freeze_Mode is not supported.

1 = Freeze_Mode is supported

bit 6

Sync_Supported: Sync_Mode support

0 = Sync_Mode is not supported.

1 = Sync_Mode is supported.

bit 5

Early_Rdy: Early Ready

0 = Normal Ready: Ready is generated when data is valid (write) or when data

has been accepted (read).

1 = Ready is generated one clock pulse earlier

bit 4

INT_Pol: Interrupt Polarity

0 = The interrupt output is low-active.

1 = The interrupt output is high-active.

bit 3

minT

SDR

: Default setting for the minT

SDR

after reset for DP operation or

combi operation.

0 = Pure DP operation (default configuration!)

1 = Combi operation

bit 2

WD_Base: Watchdog Time Base

0 = Watchdog time base is 10 ms (default state)

1 = Watchdog time base is 1 ms

bit 1

Dis_Stop_Control: Disable Stopbit Control

0 = Stop bit monitoring is enabled.

1 = Stop bit monitoring is switched off

Set_Prm telegram overwrites this memory cell in the DP_Mode. (Refer to the

user specific data.)

bit 0

Dis_Start_Control: Disable Startbit Control

0 = Monitoring the following start bit is enabled.

1 = Monitoring the following start bit is switched off

Set_Prm telegram overwrites this memory cell in the DP_Mode. (Refer to the

user specific data.)

Figure 5-1: Coding of Mode Register 0, Low-Byte

20 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

ASIC Interface 5

Mode Register 0, High-Byte, Address 07H (Intel):

bit 15

Reserved

bit 14

PrmCmd_Supported: PrmCmd support for redundancy

0 = PrmCmd is not supported.

1 = PrmCmd is supported

bit 13

Spec_Clear_Mode: Special Clear Mode (Fail Safe Mode)

0 = No special clear mode.

1 = Special clear mode. VPC3+C will accept data telegrams with data unit = 0

bit 12

Spec_Prm_Buf_Mode: Special-Parameter-Buffer Mode

0 = No Special-Parameter-Buffer.

1 = Special-Parameter-Buffer mode. Parameterization data will be stored

directly in the Special-Parameter-Buffer.

bit 11

Set_Ext_Prm_Supported: Set_Ext_Prm telegram support

0 = SAP 53 is deactivated

1 = SAP 53 is activated

bit 10

User_Time_Base: Timebase of the cyclical User_Time_Clock-Interrupt

0 = The User_Time_Clock-Interrupt occurs every 1 ms.

1 = The User_Time_Clock-Interrupt occurs every 10 ms.

bit 9

EOI_Time_Base: End-of-Interrupt Timebase

0 = The interrupt inactive time is at least 1 µs long.

1 = The interrupt inactive time is at least 1 ms long

bit 8

DP_Mode: DP_Mode enable

0 = DP_Mode is disabled.

1 = DP_Mode is enabled. VPC3+C sets up all DP_SAPs (default configuration!)

Figure 5-2: Coding of Mode Register 0, High-Byte

5.1.2 Mode Register 1

Some control bits must be changed during operation. These control bits are

combined in Mode Register 1 and can be set independently of each other

(Mode-Reg_1_S) or can be reset independently of each other (ModeReg_1_R). Separate addresses are used for setting and resetting. A logical

‘1’ must be written to the bit position to be set or reset.

For example, to set START_VPC3 write a '1' to address 08H, in order to

reset this bit, write a '1' to address 09H.

VPC3+C User Manual

Revision 1.03 21

Copyright © profichip GmbH 2004-2006

5 ASIC Interface

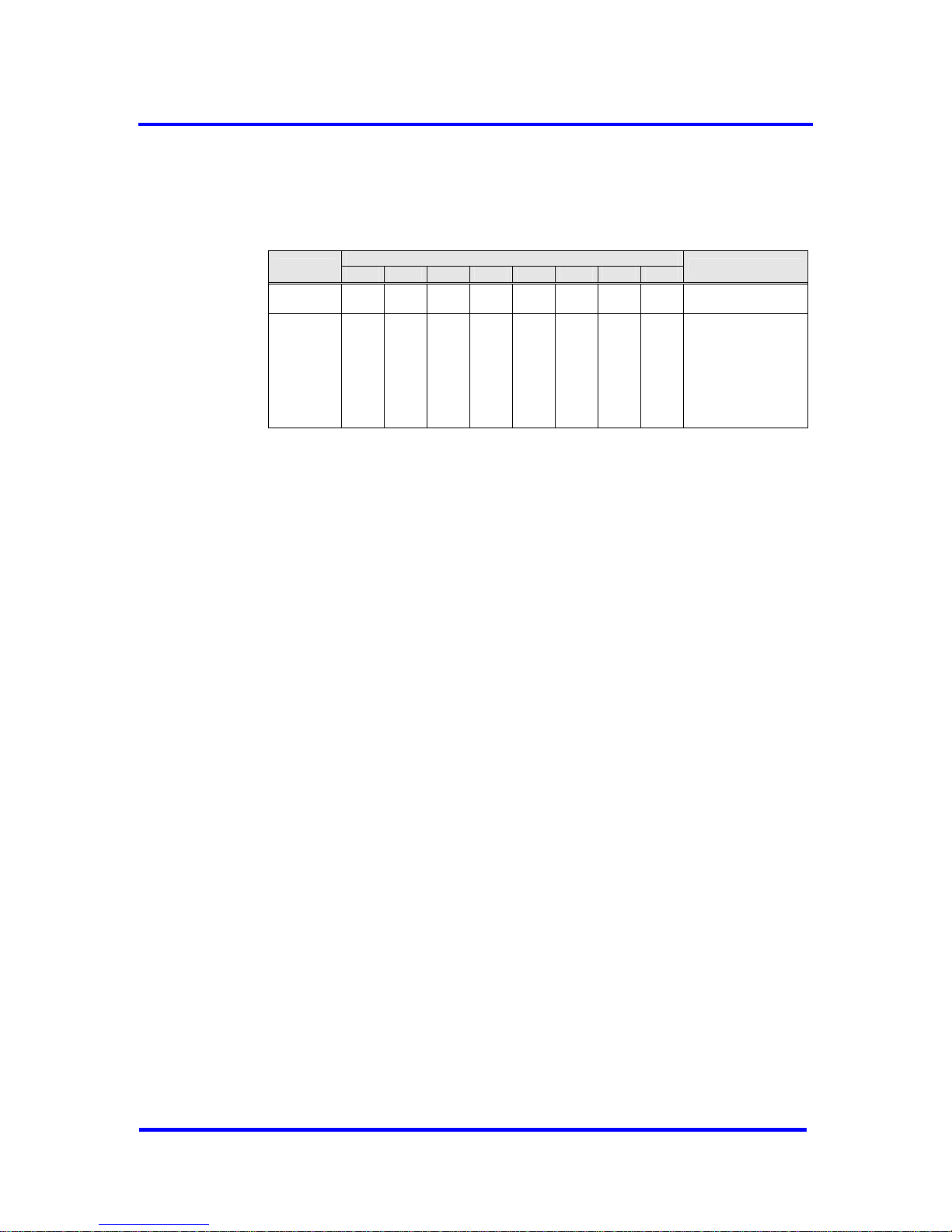

Bit Position

Address

7 6 5 4 3 2 1 0

Designation

08H

Reserved

Reserved

Res_

User_WD

En_Change_

Cfg_Buffer

User_LEAVE-

MASTER

Go_Offline

EOI

START_

VPC3

Mode-Reg_1_S

7..0

09H

Reserved

Reserved

Res_

User_WD

En_Change_

Cfg_Buffer

User_LEAVE-

MASTER

Go_Offline

EOI

START_

VPC3

Mode-Reg_1_R

7..0

See below

for coding

Mode Register 1, Set, Address 08H:

bit 7

Reserved

bit 6

Reserved

bit 5

Res_User_WD: Resetting the User_WD_Timer

1 = VPC3+C sets the User_WD_Timer to the parameterized value

User_WD_Value. After this action, VPC3+C sets Res_User_WD to ’0'.

bit 4

En_Change_Cfg_Buffer: Enabling buffer exchange (Config-Buffer for

Read_Config-Buffer)

0 = With User_Cfg_Data_Okay_Cmd, the Config-Buffer may not be exchanged

for the Read_Config-Buffer.

1 = With User_Cfg_Data_Okay_Cmd, the Config-Buffer must be exchanged for

the Read_Config-Buffer.

bit 3

User_LEAVE-MASTER. Request to the DP_SM to go to WAIT-PRM.

1 = The user causes the DP_SM to go to WAIT-PRM.

After this action, VPC3+ sets User_LEAVE-MASTER to ’0’ again.

bit 2

Go_Offline: Going into the Offline state

1 = After the current request ends, VPC3+C goes to the Offline state and sets

Go_Offline to ’0’ again.

bit 1

EOI: End-of-Interrupt

1 = VPC3+C disables the interrupt output and sets EOI to ’0‘ again.

bit 0

Start_VPC3: Exiting the Offline state

1 = VPC3+C exits offline and goes to Passive_Idle

In addition the Idle Timer and Watchdog Timer are started and

‘Go_Offline = 0’ is set

Figure 5-3: Coding of Mode Register 1

22 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

ASIC Interface 5

5.1.3 Mode Register 2

Setting parameters for Mode Register 2 may take place in the Offline

State only (like Mode Register 0).

Bit Position

Address

7 6 5 4 3 2 1 0

Designation

0 0 0 0 0 0 0 1

Reset Value

0CH

4kB_Mode

No_Check_

Prm_Reserved

SYNC_Pol

SYNC_Ena

DX_Int_Port

DX_Int_Mode

No_Check_

GC_Reserved

New_GC_

Int_Mode

Mode Reg 2

7 .. 0

VPC3+C User Manual

Revision 1.03 23

Copyright © profichip GmbH 2004-2006

5 ASIC Interface

Mode Register 2, Address 0CH:

bit 7

4KB_Mode: size of internal RAM

0 = 2K Byte RAM (default).

1 = 4K Byte RAM

bit 6

No_Check_Prm_Reserved: disables checking of the reserved bits in

DPV1_Status_2/3 of Set_Prm telegram

0 = reserved bits of a Set_Prm telegram are checked (default).

1 = reserved bits of a Set_Prm telegram are not checked.

bit 5

SYNC_Pol: polarity of SYNC pulse (for Isochron Mode only)

0 = negative polarity of SYNC pulse (default)

1 = positive polarity of SYNC pulse

bit 4

SYNC_Ena: enables generation of SYNC pulse (for Isochron Mode only)

0 = SYNC pulse generation is disabled (default)

1 = SYNC pulse generation is enabled

bit 3

DX_Int_Port: Port mode for DX_Out interrupt (ignored if SYNC_Ena set)

0 = DX_Out interrupt is not assigned to port DATAEXCH (default).

1 = DX_Out Interrupt (synchronized to SYNCH telegram) is assigned to port

DATAEXCH.

bit 2

DX_Int_Mode: Mode of DX_out interrupt

0 = DX_Out interrupt is only generated, if Len_Dout_Buf is unequal 0 (default).

1 = DX_Out interrupt is generated after every Data_Exchange telegram

bit 1

No_Check_GC_Reserved: Disables checking of the reserved bits in

Global_Control telegram

0 = reserved bits of a Global_Control telegram are checked (default).

1 = reserved bits of a Global_Control telegram are not checked.

bit 0

GC_Int_Mode: Controls generation of New_GC_Command interrupt

0 = New_GC_Command interrupt is only generated, if a changed

Global_Control telegram is received

1 = New_GC_Command interrupt is generated after every Global_Control

telegram (default)

Figure 5-4: Coding of Mode Register 2

24 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

ASIC Interface 5

5.2 Status Register

The Status Register shows the current VPC3+C status and can be read

only.

Bit Position

Address

7 6 5 4 3 2 1 0

Designation

WD_State DP_State

04H

(Intel)

1 0 1 0

Reserved

Diag_Flag

Reserved

Offline/

Passive_Idle

Status-Reg

7..0

See below

for coding

Bit Position

Address

15 14 13 12 11 10 9 8

Designation

VPC3+ Release Baud Rate

05H

(Intel)

3 2 1 0 3 2 1 0

Status-Reg

15..8

See below

for coding

Status Register,Low-Byte, Address 04H (Intel):

bit 7,6

WD_State 1..0: State of the Watchdog State Machine

00 = BAUD_SEARCH state

01 = BAUD_CONTROL state

10 = DP_CONTROL state

11 = Not possible

bit 5,4

DP_State 1..0: State of the DP State Machine

00 = WAIT-PRM state

01 = WAIT-CFG state

10 = DATA-EXCH state

11 = Not possible

bit 3

Reserved

bit 2

Diag_Flag: Status of the Diagnosis-Buffer

0 = The Diagnosis-Buffer had been fetched by the DP-Master.

1 = The Diagnosis-Buffer had not been fetched by the DP-Master yet.

bit 1

Reserved

bit 0

Offline/Passive-Idle: Offline-/Passive_Idle state

0 = VPC3+C is in Offline.

1 = VPC3+C is in Passive_Idle.

Figure 5-5: Status Register, Low-Byte

VPC3+C User Manual

Revision 1.03 25

Copyright © profichip GmbH 2004-2006

5 ASIC Interface

Status Register, High-Byte, Address 05H (Intel):

bit 15-12

VPC3+-Release 3..0 : Release number for VPC3+

0000 = Step A

1011 = Step B

1100 = Step C

1101 = Step D

Rest = Not possible

bit 11-8

Baud Rate 3..0 : The baud rate found by VPC3+D

0000 = 12,00 Mbit/s

0001 = 6,00 Mbit/s

0010 = 3,00 Mbit/s

0011 = 1,50 Mbit/s

0100 = 500,00 Kbit/s

0101 = 187,50 Kbit/s

0110 = 93,75 Kbit/s

0111 = 45,45 Kbit/s

1000 = 19,20 Kbit/s

1001 = 9,60 Kbit/s

1111 = after reset and during baud rate search

Rest = not possible

Figure 5-6: Status Register, High-Byte

26 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

ASIC Interface 5

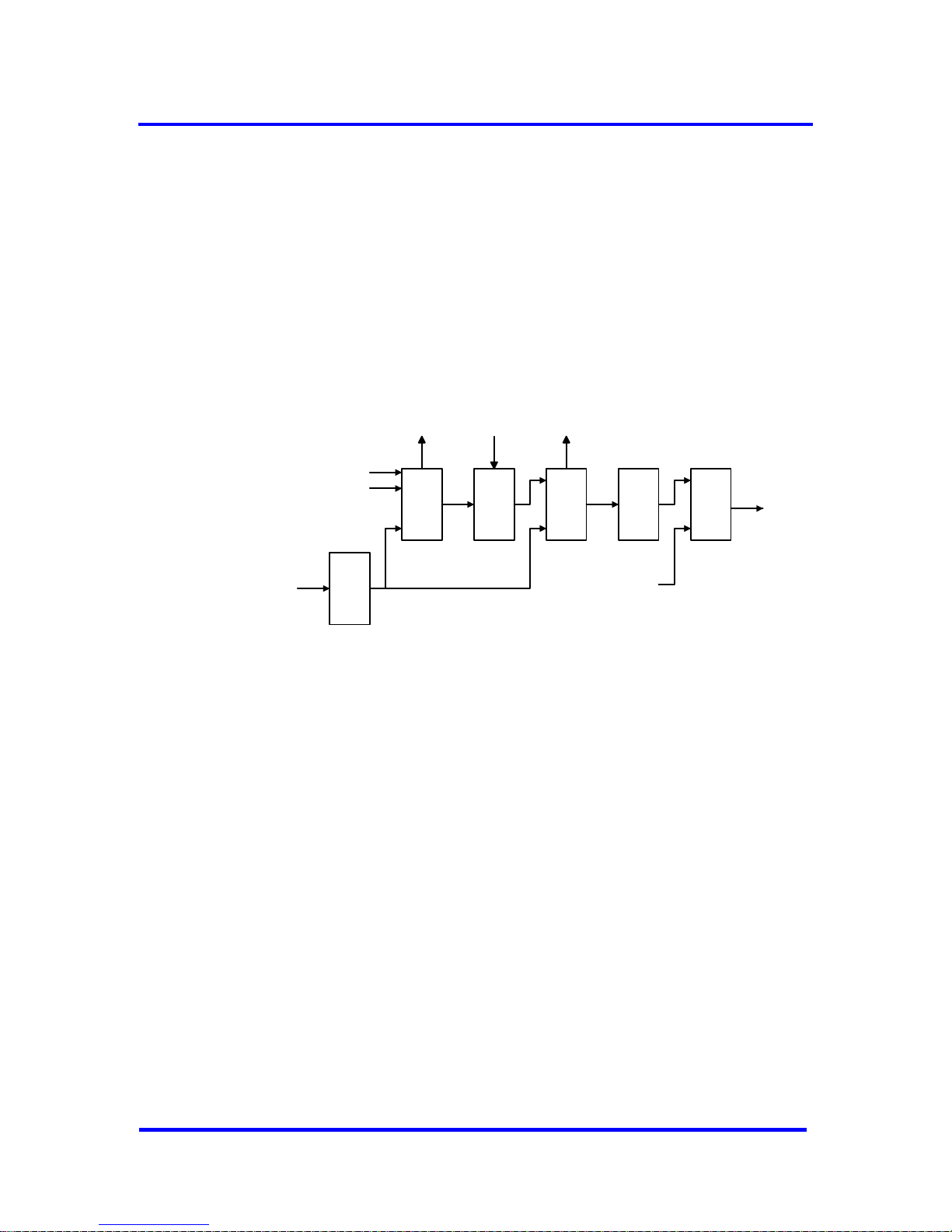

5.3 Interrupt Controller

The processor is informed about indication messages and various error

events via the interrupt controller. Up to a total of 16 events are stored in

the interrupt controller. The events are summed up to a common interrupt

output. The controller does not have a prioritization level and does not

provide an interrupt vector (not 8259A compatible!).

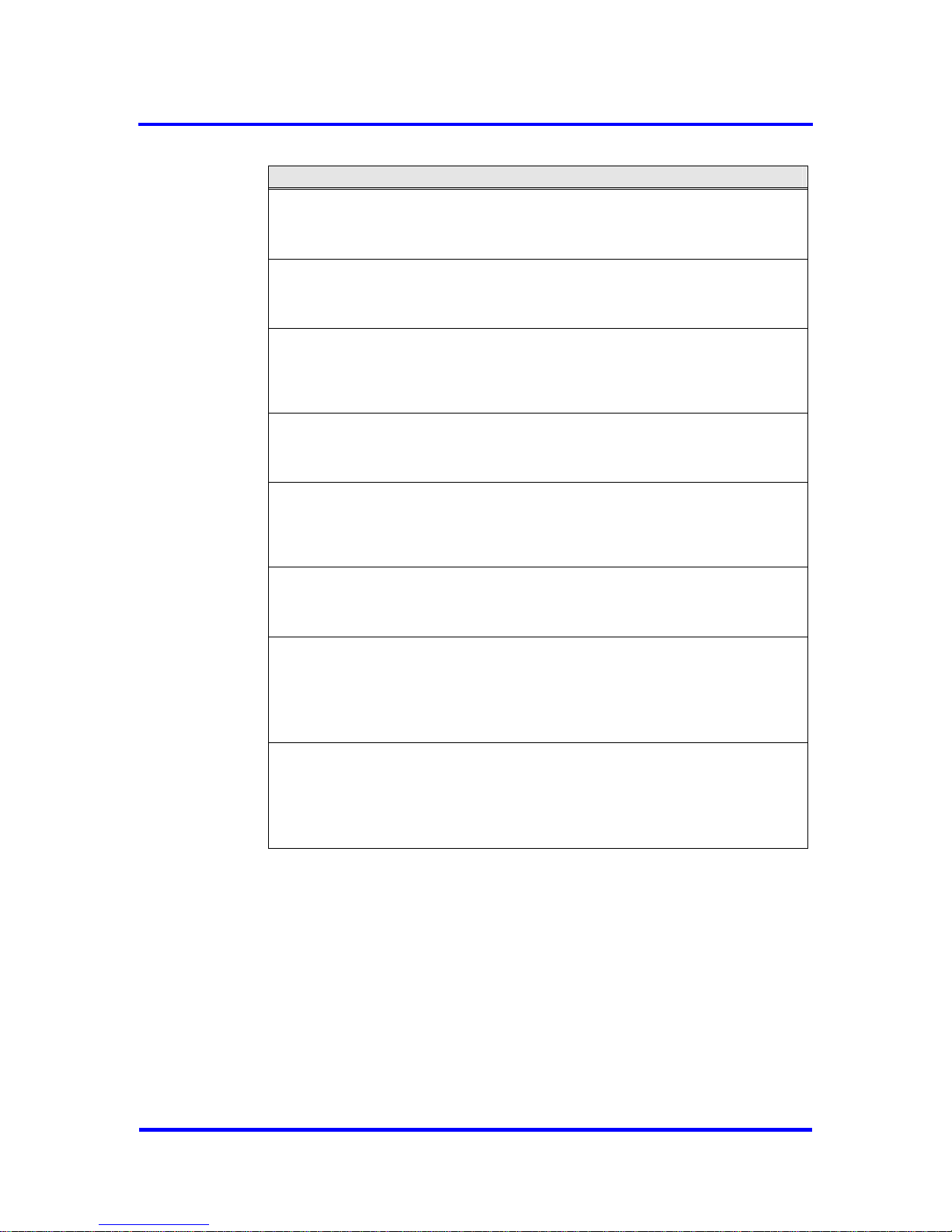

The controller consists of an Interrupt Request Register (IRR), an Interrupt

Mask Register (IMR), an Interrupt Register (IR) and an Interrupt Acknowledge Register (IAR).

IRR

S

R

IMR IR

S

R

IAR

VPC3+

µP

µP

Σ

INT_POL

X/INT

µP µP µP

Figure 5-7: Block Diagram of Interrupt Controller

Each event is stored in the IRR. Individual events can be suppressed via

the IMR. The input in the IRR is independent of the interrupt masks. Events

that are not masked in the IMR set the corresponding IR bit and generate

the X/INT interrupt via a sum network. The user can set each event in the

IRR for debugging.

Each interrupt event that was processed by the microcontroller must be

deleted via the IAR (except for New_(Ext_)Prm_Data and New_Cfg_Data).

A logical ‘1’ must be written on the specific bit position. If a new event and

an acknowledge from the previous event are present at the IRR at the

same time, the event remains stored. If the microcontroller enables a mask

subsequently, it must be ensured that no prior IRR input is present. To be

on the safe side, the position in the IRR must be deleted prior to the

enabling of the mask.

Before leaving the interrupt routine, the microprocessor must set the ‘end of

interrupt bit' (EOI = 1) in Mode Register 1. The interrupt output is switched

to inactive with this edge change. If another event occurs, the interrupt

output is not activated again until the interrupt inactive time of at least 1 µs

or 1 ms expires. This interrupt inactive time can be set via EOI_Time_Base

in Mode Register 0. This makes it possible to enter the interrupt routine

again when an edge-triggered interrupt input is used.

VPC3+C User Manual

Revision 1.03 27

Copyright © profichip GmbH 2004-2006

5 ASIC Interface

The polarity of the interrupt output is parameterized via the Int_Pol bit in

Mode Register 0. After hardware reset, the output is low-active.

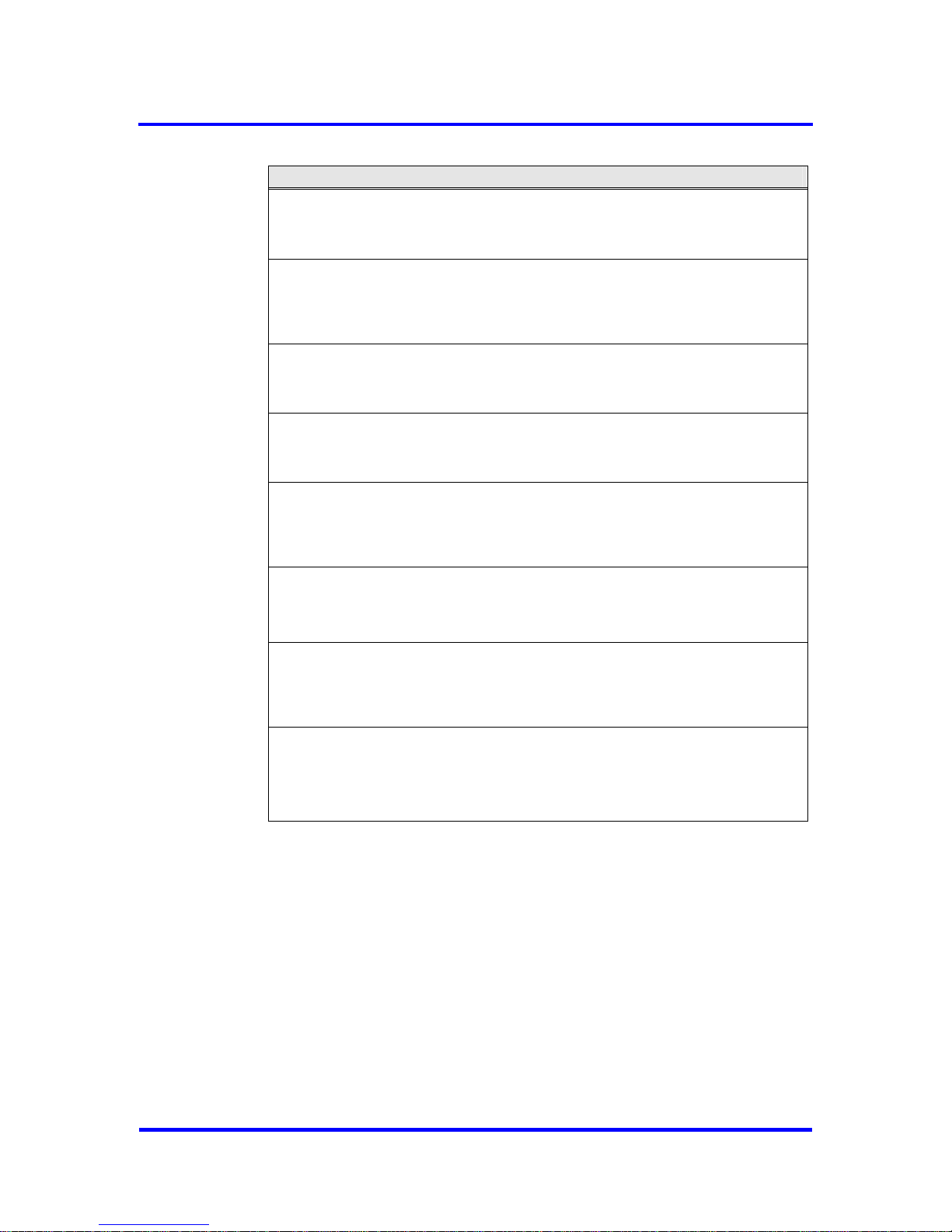

5.3.1 Interrupt Request Register

Bit Position

Address

7 6 5 4 3 2 1 0

Designation

00H

(Intel)

DXB_Out

New_Ext_

Prm_Data

DXB_Link_

Error

User_Timer_

Clock

WD_DP_

CONTROL_Timeout

Baud_Rate_

Detect

Go/Leave_

DATA-EXCH

MAC_Reset

Int-Req-Reg

7 .. 0

See below

for coding

Bit Position

Address

15 14 13 12 11 10 9 8

Designation

01H

(Intel)

FDL_Ind

Poll_End_Ind

DX_Out

Diag_Buffer_

Changed

New_Prm_

Data

New_Cfg_

Data

New_SSA_

Data

New_GC

Command

Int-Req-Reg

15 .. 8

See below

for coding

28 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

ASIC Interface 5

Interrupt-Request-Register, Low-Byte, Address 00H (Intel):

bit 7

DXB_Out:

VPC3+C has received a DXB telegram and made the new output data available

in the ‘N’ buffer.

bit 6

New_Ext_Prm_Data:

The VPC3+C has received a Set_Ext_Prm telegram and made the data

available in the Parameter-Buffer.

bit 5

DXB_Link_Error:

The Watchdog cycle is elapsed and at least one Publisher-Subscriber

connection breaks down.

bit 4

User_Timer_Clock:

The time base for the User_Timer_Clocks is run out (1 / 10ms).

bit 3

WD_DP_CONTROL_Timeout:

The watchdog timer expired in the DP_CONTROL state.

bit 2

Baud_Rate_Detect:

The VPC3+C has left the BAUD_SEARCH state and found a baud rate.

bit 1

Go/Leave_DATA-EXCH:

The DP_SM has entered or exited the DATA-EXCH state.

bit 0

MAC_Reset:

After processing the current request, the VPC3+C has entered the Offline state

(by setting the Go_Offline bit).

Figure 5-8: Interrupt-Request-Register, Low-Byte

VPC3+C User Manual

Revision 1.03 29

Copyright © profichip GmbH 2004-2006

5 ASIC Interface

Interrupt Request Register 0, High-Byte, Address 01H (Intel):

bit 15

FDL_Ind:

The VPC3+C has received an acyclic service request and made the data

available in an Indication-Buffer.

bit 14

Poll_End_Ind:

The VPC3+C have send the response to an acyclic service.

bit 13

DX_Out:

The VPC3+C have received a Data_Exchange telegram and made the new

output data available in the ‘N’ buffer.

bit 12

Diag_Buffer_Changed:

Due to the request made by New_Diag_Cmd, the VPC3+C exchanged the

Diagnosis-Buffers and made the old buffer available to the user again.

bit 11

New_Prm_Data:

The VPC3+C have received a Set_Prm telegram and made the data available

in the Parameter-Buffer.

bit 10

New_Cfg_Data:

The VPC3+C have received a Chk_Cfg telegram and made the data available

in the Config-Buffer.

bit 9

New_SSA_Data:

The VPC3+C have received a Set_Slave_Add telegram and made the data

available in the Set_Slave_Add-Buffer.

bit 8

New_GC_Command:

The VPC3+C have received a Global_Control telegram and stored the

Control_Command in the R_GC_Command RAM cell.

Figure 5-9: Interrupt Request Register, High-Byte

30 Revision 1.03

VPC3+C

User Manual

Copyright © profichip GmbH 2004-2006

Loading...

Loading...