Page 1

Application Note AN-69

LinkSwitch-4 Family

Design Guide and Considerations

Introduction

The LinkSwitch™-4 family of ICs dramatically simplies low power

CV/CC charger/adapter design by eliminating an optocoupler and

secondary control circuitry. The LinkSwitch-4 family adaptive BJT drive

technology uses combined base and emitter switching to boost switching

performance and deliver higher efciency, wider Reverse Bias Safe

Operating Area (RBSOA) margin and the exibility to accommodate a

wide range of low cost BJT. The device incorporates a multimode PWM

/ PFM controller with quasi-resonant switching to maximize the efciency,

meets <30 mW no-load and at same time maintains fast transient

response greater than 4.3 V with a load change from 0% to 100%.

Advanced Performance Features

• Dynamic base drive technology provides exibility in choice of BJT

transistor by dynamically optimizing BJT switching characteristics

• Extends RBSOA of BJT

• Dramatically reduces sensitivity to BJT gain

• Compensates for transformer inductance tolerances

• Compensates for input line voltage variations

• Compensates for cable voltage drop

• Compensates for external component temperature variations

• Very accurate IC parameter tolerances using proprietary trimming

technology

• Frequency up to 65 kHz to reduce transformer size

• The minimum peak current is xed to improve transient load

response

Advanced Protection/Safety Features

• Single fault output overvoltage and short-circuit

• Over-temperature protection

EcoSmart™ – Energy Efcient

• Meets DoE 6 and CoC V5 2016 via an optimized quasi-resonant

switching PWM / PFM control

• No-load consumption of <30 mW at 230 VAC input

Green Package

• Halogen free and RoHS compliant package

Applications

• Chargers for cell/cordless phones, PDAs, MP3/portable audio

devices, adapters, etc.

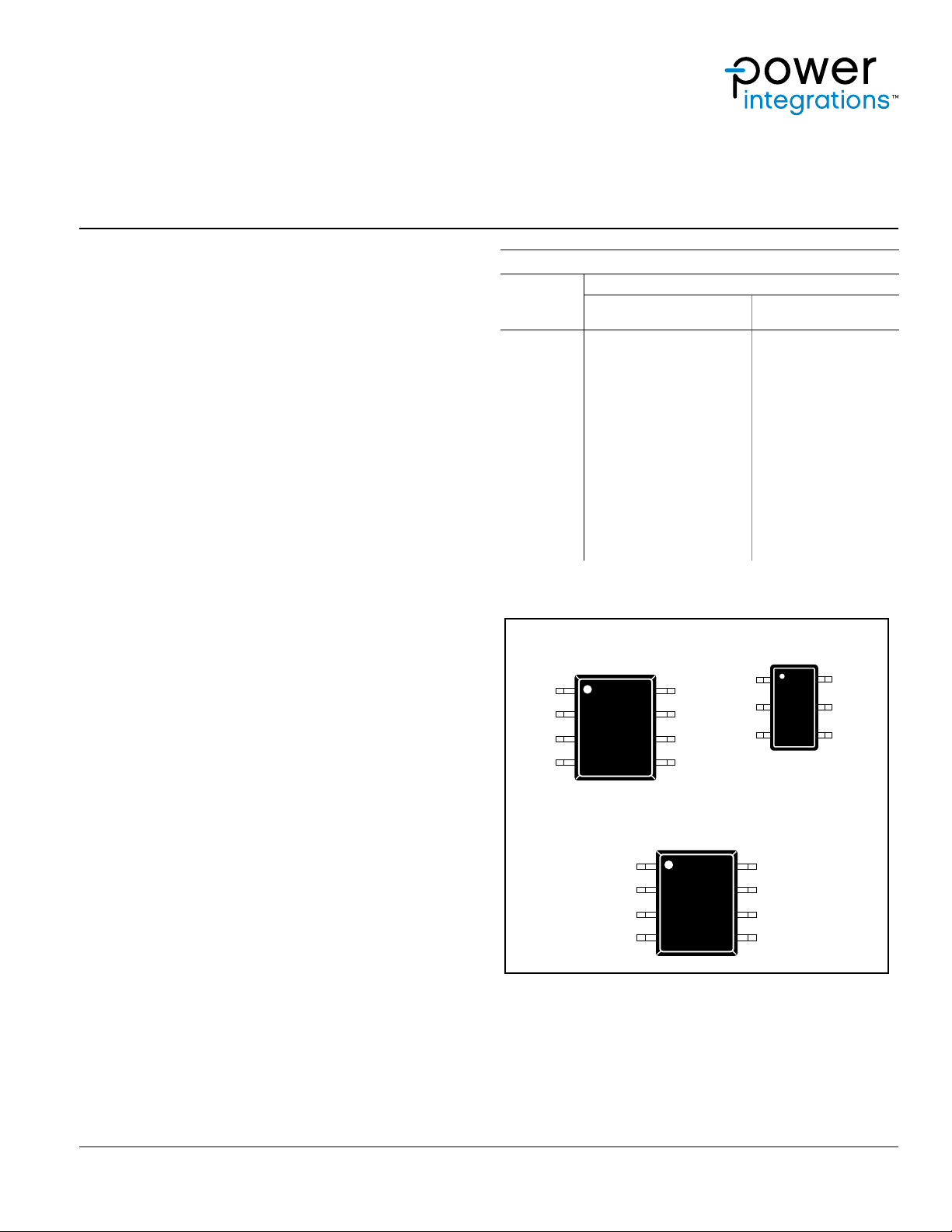

LinkSwitch-4 Family

There are four main family groups covering a power range of nominally

2 W to 18 W and they come in either a SOT23-6 or SO-8 package.

Groups are further subdivided by cable drop compensation levels of

0%, 3% and 6%.

LNK43xxx and LNK4x15D devices have an enhanced base drive

optimization for reduced BJT losses. For example, the LNK4322S can

output 5 W using a TO92 13003 BJT instead of a TO251 13005 and

remain thermally safe. The LNK43x3 devices also include a debounce

delay after a low output voltage is detected to prevent false UVP

foldback being triggered in noisy environments.

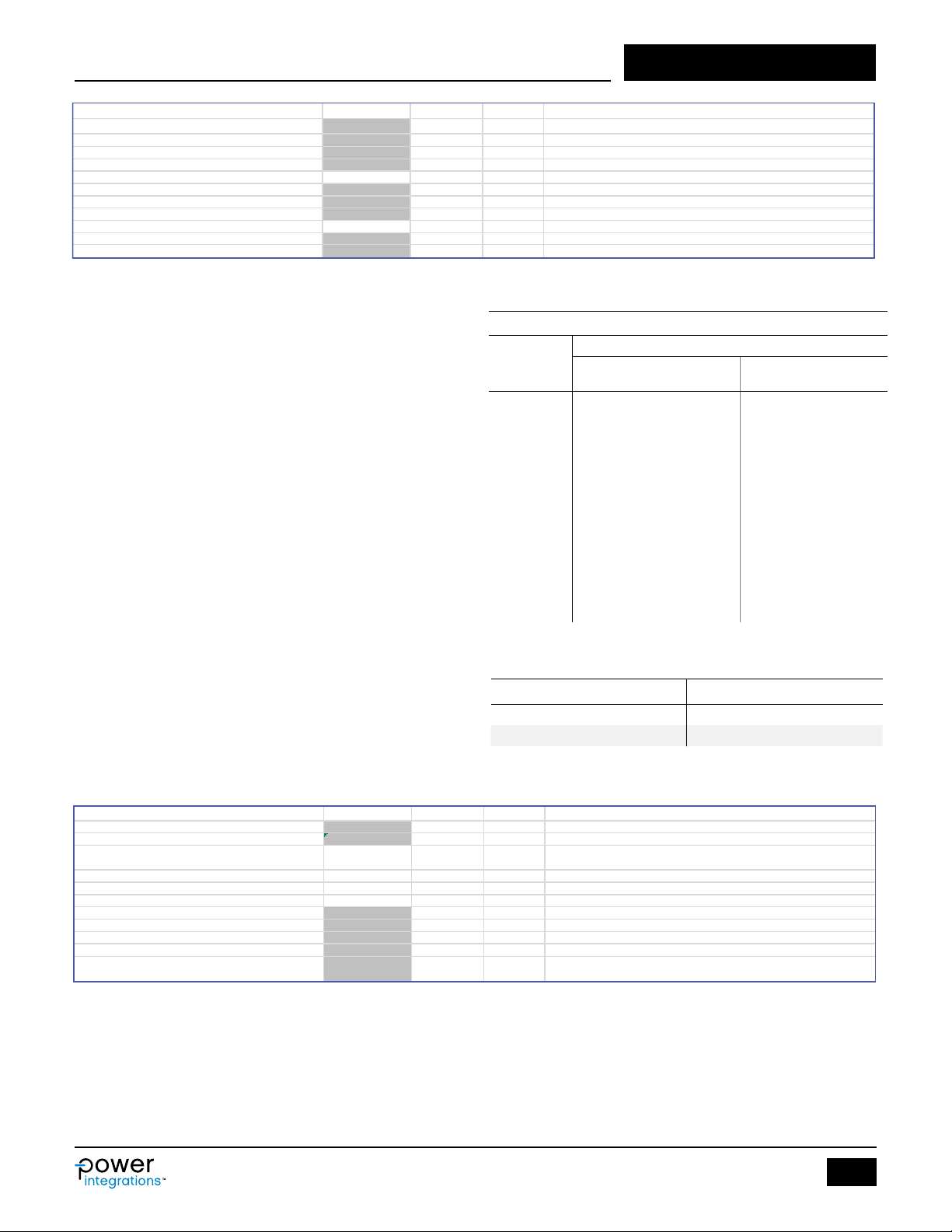

Output Power Table

8

FB

7

GND

6

GND

5

ED

85 - 265 VAC

5

Open Frame

S Package (SOT-23-6)

FB

GND

ED

8

FB

7

GND

6

GND

5

ED

Adapter

61

CS

52

VCC

43

BD

PI-7673-061516

1

2

Product

3,4

Features

LNK43x2S 13003 Drive 5 W

LNK40x2S STD 6.5 W

LNK40x3S STD 8 W

LNK4323S STD 8 W

LNK40x3D STD 10 W

LNK4323D STD 10 W

LNK40x4D STD 15 W

LNK4114D Easy Start 15 W

LNK4214D Easy Start + Constant Power 15 W

LNK4115D Easy Start 18 W

LNK4215D Easy Start + Constant Power 18 W

Table 1. LinkSwtich-4 Selection Table Based on Output Power.

D Package (SO-8)

(LNK40x3D, LNK4323D)

1

CS

2

VCC

3

SBD

4

BD

D Package (SO-8)

(LNK40x4D, LNK4114D, LNK4214D,

LNK4115D, LNK4215D)

1

CS

2

VCC

3

BD

4

SBD

Figure 1. LinkSwitch-4 Packages.

Note that the LNK4xx3D and LNK4xx4D SO-8 packages have the

SUPPLEMENTARY BASE DRIVE (SBD) pin and BASE DRIVE (BD) pins

swapped. This is to avoid problems with charger/adapter reliability.

The 10 W rated LNK40X3D would otherwise work in a 15 W LNK40X4D

design and may pass production nal test, but it would be overstressed and probably result in eld failures.

www.power.com October 2017

Page 2

Application Note AN-69

Scope

This application note is intended for engineers designing an isolated

AC-DC yback power supply using the LinkSwitch-4 family of devices.

It provides guidelines to enable an engineer to quickly select key

components and to complete a suitable transformer design. To

simplify the task this application note refers directly to the PIXls

design spreadsheet, part of the PI Expert design software suite.

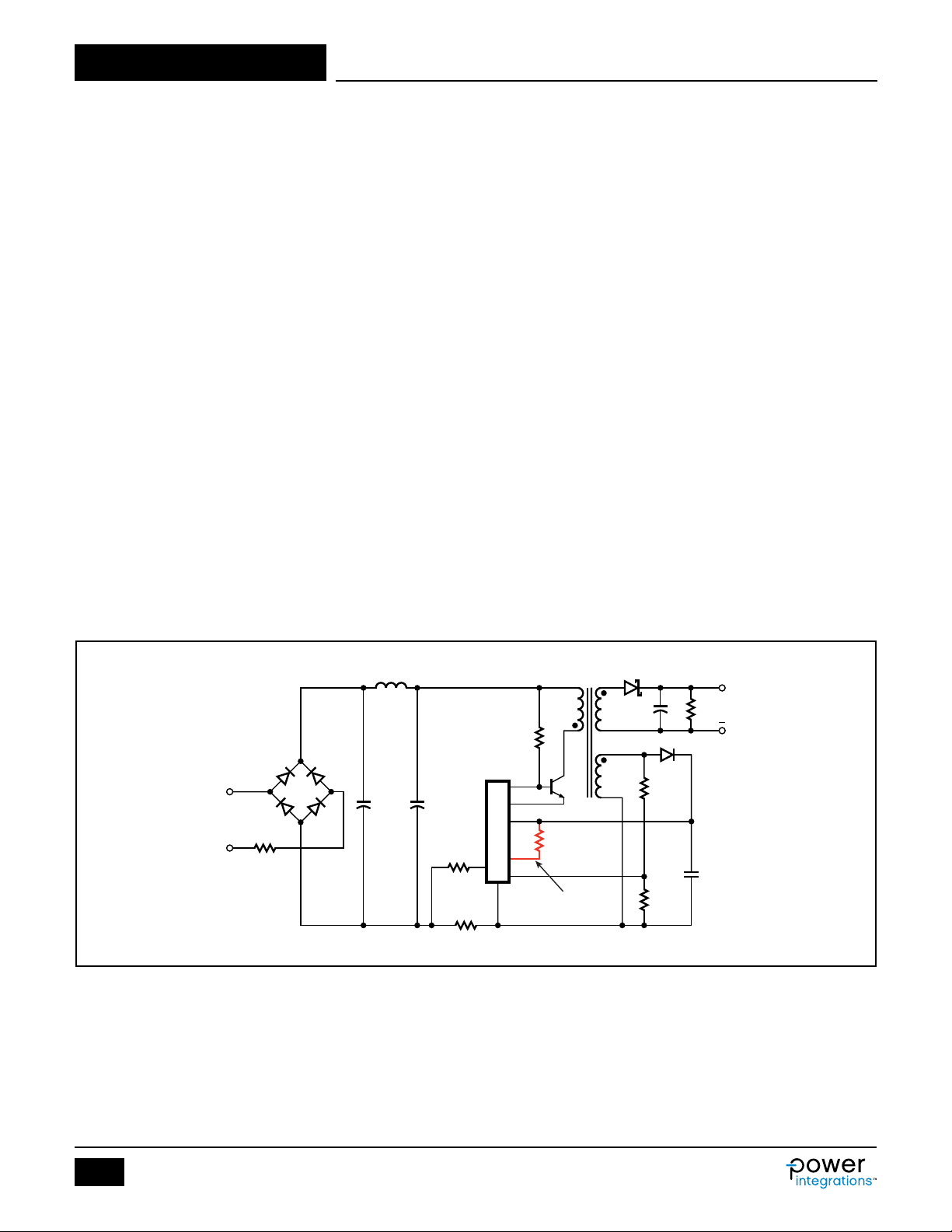

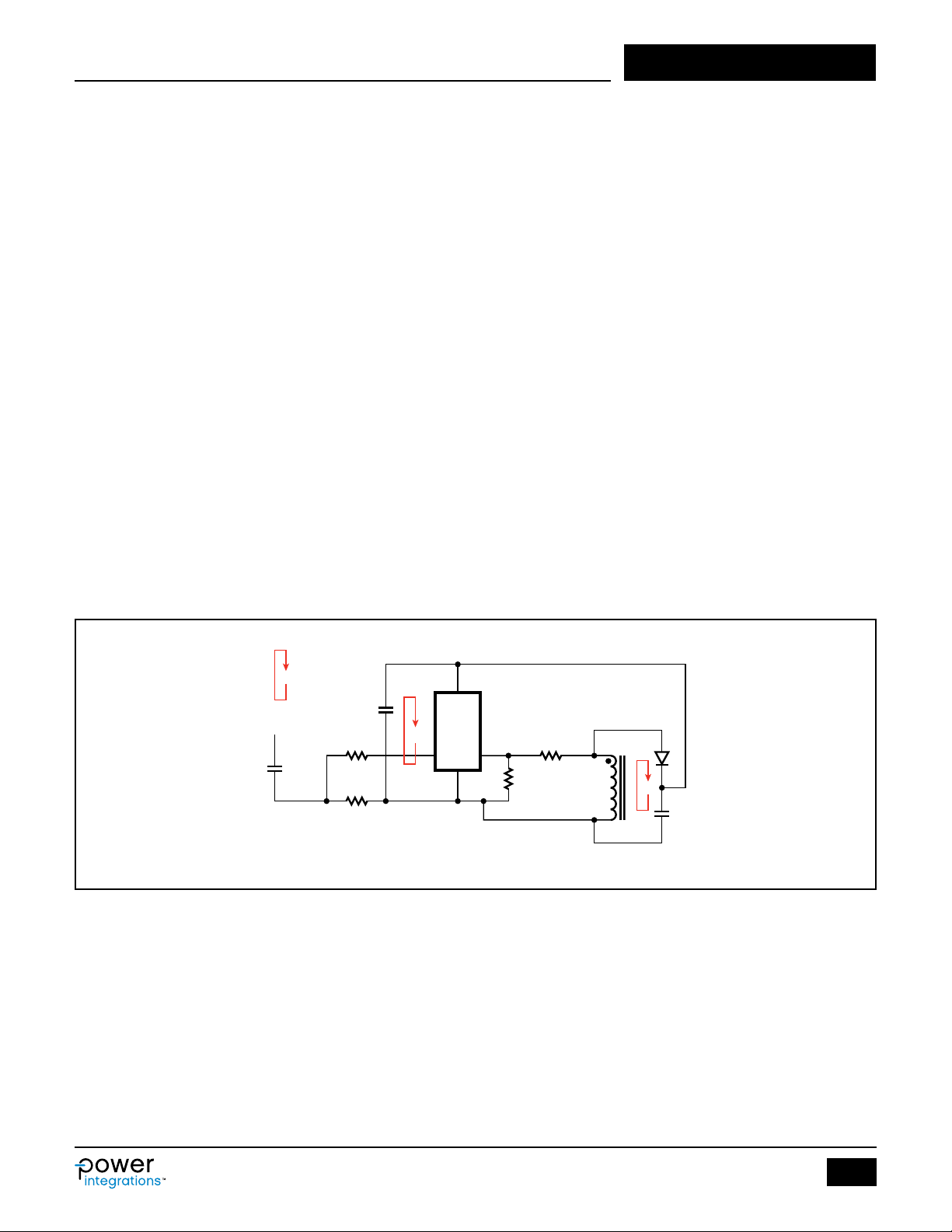

Basic Circuit Topology

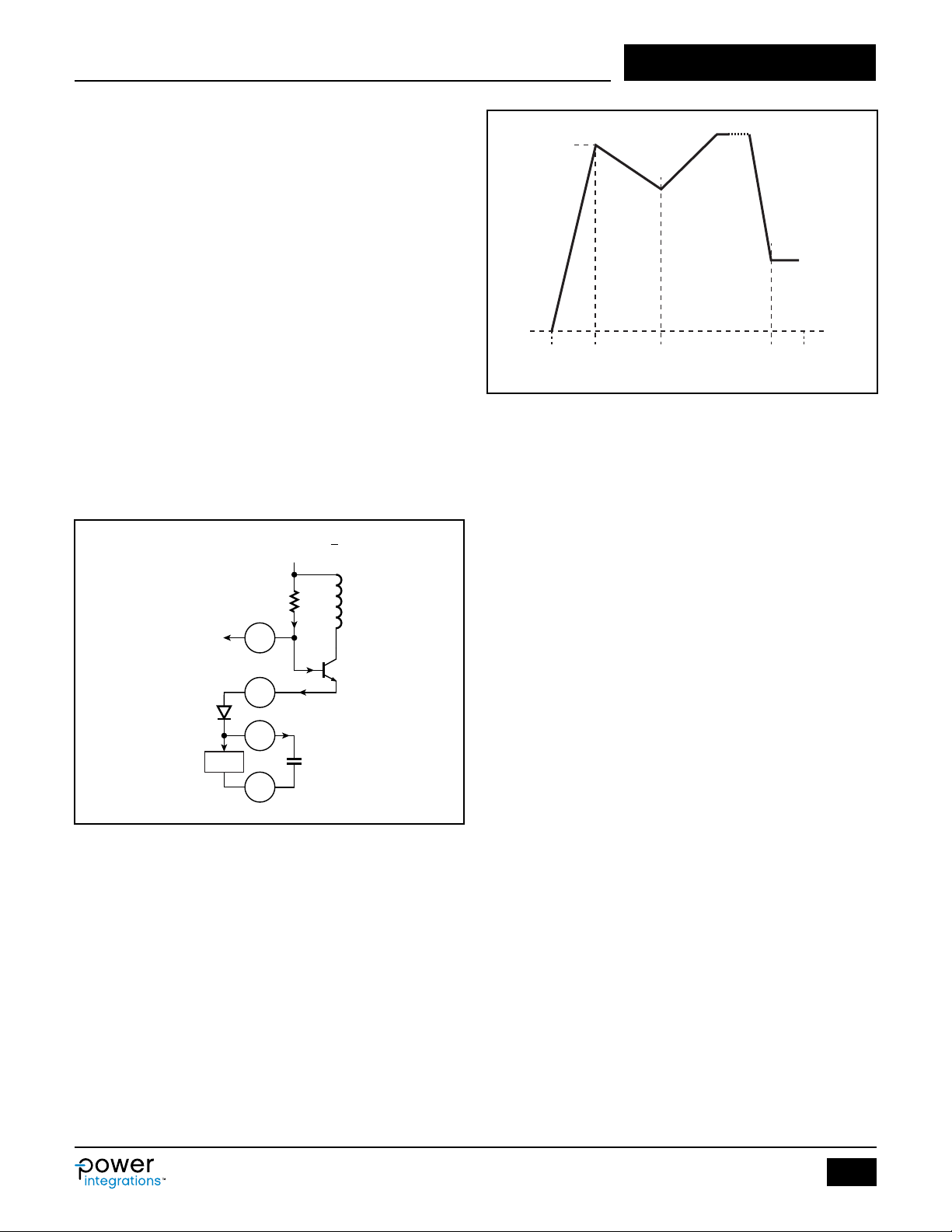

The circuit in Figure 2 shows the basic topology of a yback power

supply designed using LinkSwitch-4. Because of the high-level

integration of LinkSwitch-4, far fewer design issues are left to be

addressed externally, resulting in one common circuit conguration

for all applications. For example, different output power levels may

require different values for some circuit components, but the circuit

topology stays unchanged. The exception to this is the optional SBD

resistor used with the SO-8 package parts. This increases the

available base drive current for higher power designs without

increasing the package power dissipation.

Schematic Features

• R

provides inrush current limiting at turn-on and under transient

IN

surge conditions.

• C

, C

and L

IN1

IN2

upon the AC supply, the capacitors also provide energy storage to

power the convertor during the valleys of the rectied AC.

• R

provides start-up current, which is amplied by the BJT to

HT

charge CVCC via the EMITTER DRIVER (ED) and VOLTAGE SUPPLY

(VCC) pins.

provide ltering to reduce switching noise impressed

FI LT

• R

converts the positive ramping primary current into a negative

CS

ramping voltage, which is monitored by the PRIMARY CURRENT

SENSE (CS) pin. It allows cycle-by-cycle peak primary current and

hence output power control, primary current limiting and, with the

transformer turns ratio, sets the maximum output current limit.

• R

reduces ESD susceptibility on all devices. Though highly

CS2

recommended, it is not strictly necessary on LNK40x2S parts.

On the remaining parts, it sets one of four minimum primary

current levels to control no-load behavior.

• R

is only used on SO-8 packaged parts. It allows for extra base

SBD

drive in higher power designs without increasing package dissipation

signicantly.

• T1 is the yback transformer. It stores energy in the primary wind-

ing and transfers it to the secondary and bias windings. There are

usually additional screen windings, not shown, to reduce EMI.

• The bias diode and C

• The bias winding is also used to measure the output voltage level

provide operational power to the controller IC.

VCC

on the secondary winding.

• For FEEDBACK (FB) pin positive voltage excursions, R

the turns ratio between the secondary and bias windings set the

, R

and

FB1

FB2

output voltage.

• For negative voltage excursions, the FEEDBACK pin is a virtual

earth amplier and is held at zero volts by sourcing current into

R

. This is translated internally into a voltage that represents the

FB1

HT voltage across C

detection, brown-out detection and BJT desaturation detection.

• R

is a dummy load for controlling no-load behavior.

OUT

. This is used to provide input undervoltage

IN2

In addition to this application note, you may also nd the LinkSwitch-4

Design Examples Reports (DER). Further details on downloading PI

Expert, Design Example Reports, and updates to this document can

be found at www.power.com.

D

BRIDGE

~

R

IN

Figure 2. Typical LinkSwitch-4 Circuit Topology.

D

OUT

T1

+

C

L

FILT

2 × R

HT

Q1

BD

C

IN1

C

IN2

LNK40x3D

R

CS2

R

CS

ED

VCC

SBD

CS

FB

GND

SBD pin only available

on SOP-8 package parts

R

SBD

OUT

PI-7962-052416

R

OUT

R

FB1

C

VCC

R

FB2

2

Rev. B 10/17

www.power.com

Page 3

Application NoteAN-69

Quick Start

To start immediately, use the following information to quickly design

the transformer and select the components for a rst prototype.

Only the information described below needs to be entered into the

PIXls spreadsheet gray cells in column [B]. Some gray cells have

entries in bold font, these contain drop down selections. If an invalid

selection is made, then Info or Warning text will appear in column [C]

and [D], a description of the error is displayed in column [H]. Other

parameters and component values will be automatically calculated.

References to spreadsheet cell locations are provided in square

brackets [cell reference].

The default design presented in a blank spreadsheet is for a 5 V, 2 A

adapter with 6% cable compensation and standard universal AC input

voltage range. All gray cells are blank except for those with bold text

drop down selections, which are set to the appropriate selections for

the default adapter. The default values are displayed in column [E]

and [F]. When an entry is made in a column [B] gray cell, its value is

transferred into the corresponding cell in columns [E] and [F] and

from there, used in the calculations.

It is only necessary to enter values into column [B] if they are

different to the default values in column [E].

• If a non-standard AC input voltage range is required, enter the

values for VAC

• Enter the nominal output voltage (at the end of the cable if

applicable), VO [B6].

• Entre the output diode forward volt drop if different to the

standard Schottky value, VD [B8].

• Enter the minimum required output current value, I

that cell [E10] is updated with a suggested minimum CC value for

ICC. See Figure 4.

• Enter the required CC limit, ICC [B10], if it is higher than the

suggested minimum I [E10]. See Figure 4.

• Enter an efciency estimate, η [B12]. Use the target gure from

the applicable efciency standard.

• Use the drop down selection menu in [B19] to select the desired

cable compensation. Output voltage at the PCB, VO_PCB, is now

given in [E7].

• The minimum recommended bulk capacitance value (C

given in [E13]. If a larger value, or standard values are to be used,

enter their total value into [B13].

• Using the value for ‘rated output power’ in cell [E11], use table 1

on page 1, to choose the correct LinkSwitch-4 device. Use the

drop down selection menu in [B18] to select that device.

• BJT types TS13003 and TS13005 are auto selected based on

output power. To use a different BJT, enter PART_NUMBER, HFE_

STARTUP (low current gain), HFE (high current gain) and VSWMAX

(V

) into [B24,B25,B26,B27].

CBO

• Use the drop down selection menu in [B35] to select ‘AUTO’. A

suitable core, bobbin and parameters will automatically be entered

into cells [E35 – E43].

• To optimize for efciency enter an alternative value for the

reected output voltage, VOR in [B49], the default is 100 V. While

trying different values, observe the changes in KCRMV [E65] and

aim to get between 0.95 and 0.98. At the same time ensure

MIN

, VAC

and fL into cells [B3, B4, B5] as required.

MAX

[B9]. Notice

O

+ C

IN1

IN2

) is

VCRMV-VMIN [E56-E57] is less than 15 V, but the higher VCRMV

the better. The spreadsheet will produce a reasonable solution if

VOR is left at the default 100 V.

• Fixing the number of secondary turns in [B50] while sweeping the

VOR value [B49] offers further optimization possibilities.

• The default primary inductance tolerance is 10%, an alternative

value can be entered in [B88]. Tighter tolerance allows better

average efciency across production.

• The default number of primary winding layers is 3 [E98], if the

primary current density [E103] is less than 3.8 Amps / mm2 it can

be reduced to 2 by an entry into [B98]. If greater than 10 Amps /

mm2, increase to 4 etc. The fewer layers the better for leakage

inductance and hence efciency.

• The default calculated number of turns for the bias winding, NB

[E105] is based on providing a no-load bias voltage, VB_NOLOAD

[E107] that achieves the lowest no-load power. However, start-up

may be compromised so enter a value between 8 and 9 into

VB_NOLOAD [B107]. NB will be recalculated; check the value of

VB_NOLOAD_MEASURED [E109] is between 8 and 9 V. If not,

adjust the value in [B107] and recheck.

• One secondary layer is optimal for efciency, but if the output

voltage is high resulting in the secondary wire being impractically

thin, DIAS [E120], then it can be increased by entering a value in

LS [B116]. The spreadsheet calculates for a triple insulated wire

size that will ll the bobbin width in an integer number of layers

given in [E116].

• For low voltage designs, particularly at higher powers and larger

cores, the wire thickness becomes impracticably thick to wind. By

winding the secondary with a number of parallel conductors, the

wire thickness is reduced to a practical value, also leakage

inductance is decreased which improves efciency. To use more

than one conductor, enter a value into Filars [B117] and recheck

the new calculated wire size, DIAS [E120].

• Enter a BJT voltage derating factor into SWITCH_DERATING

[B126] if other than 0.10 (10%) is required.

• Use the drop down selection menu in VCS_MIN [B135] to set the

minimum value of peak primary current at no-load. It is repre-

sented by the peak mV across RCS. For the LNK40X2S devices, only

88 mV should be selected and a 1 kW value be used for R

ltering. For other devices select the lowest value (56 mV) for the

CS2

for

rst iteration.

• If the application requires no-load to partial or full load transient

capability, where the output voltage must not fall below a minimum

value as in USB charger applications, check the value of CBIAS

[E138] if it is more than 2 mF, enter the value ‘2’ into [B138].

Check DELTA_BIAS [E139] is less than 1.6 V.

• Output capacitor calculation for starting up into a resistive load:

Use the drop down selection menu in LOAD_TYPE [B141] to select

‘Resistive Load’. The spreadsheet calculates the maximum value of

output capacitance the circuit will start up into i.e. before CBIAS

runs out of charge.

• For a CC load at start-up, use [B141] to select ‘CCLoad’. The

default start-up CC load current is 75% of IO, the rated output

current (not the CC limited value) if another value is specied,

enter it into ICC_STARTUP [B142].

• If the suggested output capacitance value needs to be rounded up

to a preferred value, enter this into COUT_FINAL [B145].

www.power.com

3

Rev. B 10/17

Page 4

Application Note AN-69

If no-load to partial or full load transient step is required as in USB

chargers:

• Enter the load step value into I_LOADSTEP [B148] if it is different

to the rated output current.

• Enter the minimum load voltage allowed during no-load to partial

or full load transient testing into V_UNDERSHOOT [B149].

• Check that FSW_NOLOAD value in [E154] is greater than FSW_

UNDERSHOOT in [E150]. If not, select a lower value for VCS_MIN

[B135], if already at the lowest setting or a LNK40x2S device is

being used, enter a lower value for R_PRELOAD [B152] untill the

condition is met.

• Check that the no-load power specication is met, P_NOLOAD_TO-

TAL [E174], if not select a higher value of VCS_MIN [B135] (not

LNK40X2S) and recheck that the FSW_

NOLOAD>FSWUNDERSHOOT and no-load power requirements are

met. If using a LNK40X2S, R_PRELOAD [B152] can be increased,

but no more than 2x.

If no transient step requirement:

• Select a value of VCS_MIN [B135] and R_PRELOAD [B153] that

gives a FSW_NOLOAD of between 1 kHz and 2 kHz and still meets

the no-load specication.

• Enter the maximum allowed start-up time into STARTUP_TIME

[B156] if it is not to be 1 second. Or enter a preferred value into

R_STARTUP [B157], a new value of the resultant startup time is

given in STARTUP_TIME_FINAL [E158].

Supplementary Base Drive

Resistor R

drive in higher power applications (7.5 W to 18 W). It should have a

is used on SO-8 packaged devices to provide extra base

SBD

value of between 390 W and 220 W for standard designs, or 120 W for

applications using the EasyStart feature. Refer to the ‘Design

Testing’ section to check that correct value has been selected.

Component values for the design are found in:

+ C

C

IN1

Selected device – [E20]

, CIN [E13]

IN2

Q1 BJT – [E24]

T1 Core - [E35]

T1 Bobbin – [C37]

T1 Primary turns – [E51]

T1 Primary layers – [E98]

T1 Primary wire diameter – [E101, E102]

T1 secondary turns – [E50]

T1 Secondary layers – [E116]

T1 Secondary lars – [E117]

T1 Secondary wire diameter – [E120, E121]

T1 Bias turns – [E106]

T1 Core gap – [E93]

C

, Bias capacitor value – [E138]

VCC

Total output capacitance C

Output capacitance ripple – [E81]

R

Dummy load – [E152]

OUT

RHT Start-up resistor – [E157]

R

Upper feedback resistor – [E161]

FB1

R

Lower feedback resistor – [E162]

FB2

RCS Current sense resistor – [E74]

R

Bias diode V

D

D

D

setting resistor – [E136]

CS2 VCSMIN

OUT VRRM

Peak current – [E79]

OUT

RMS current – [E780]

OUT

– [E129] usually 1N4148

RRM

– [E128]

, [E145]

OUT

Explore the spreadsheet for more informative data.

4

Rev. B 10/17

www.power.com

Page 5

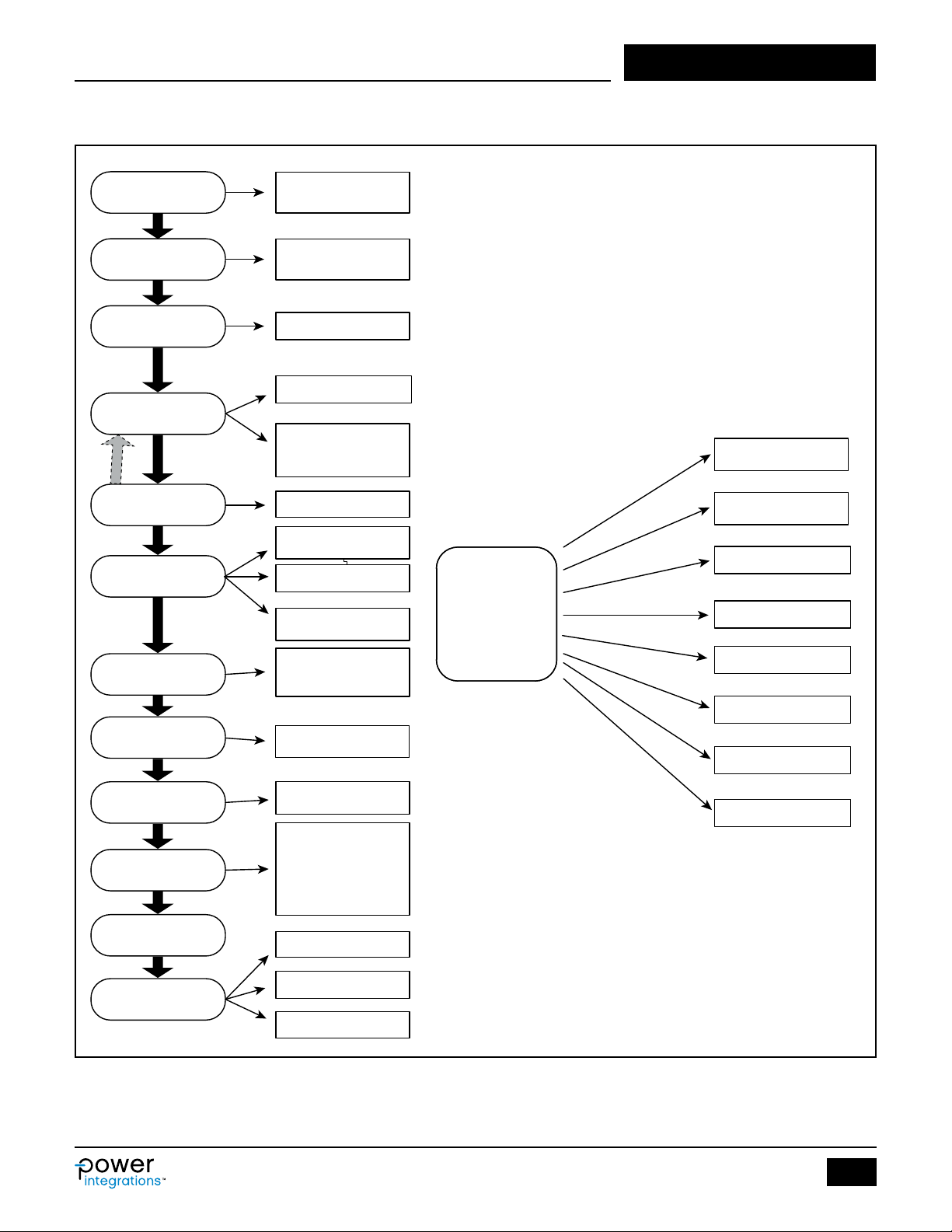

Step-by-Step Design Procedure

Application NoteAN-69

Specify Application

Parameters

Bulk Capacitor

Election

IC and BJT

Selection

Transformer Core,

Bobbin, Turns

Optimize Turns Ratio

for Efficiency

Resulting HT, Primary

and Secondary

Conditions

.

Customer / Data Sheet

Defined; Assumptions

Determines Minimum HT

Voltage at Full Load

Power Range, CDC

Core Type; Size ; Material

Calculations: Turns,

Primary Inductance,

Peak Current, etc

VOR, NS, N

Minimum HT Voltage,

Brown-Out HT Voltage

Peak Primary Current

Current Sense

Resistor Value

P

Testing and

Troubleshooting

Collector Voltage at

100%, 50%, 0% Load

Assess Switching

Frequency vs. Load

AUX Voltage vs. Load

Startup / Load Pull-Up

Secondary Waveform

Parameters

Transformer

Construction

Bias Winding

Parameters

Additional Parameters

No-Load Power Estimate

PCB Layout

Figure 3. Design Flow Char t.

Peak, RMS Secondary

Current and C

Ripple Current

Wire Gauge, Number of

Layers, Filars

Bias Turns for Required

Bias Voltage

Bias Capacitor

Output Capacitor

Loadstep Undershoot

Dummy Load

Start-Up

Feedback Resistors

Function Consideration

EMC Consideration

Thermal Consideration

OUT

Efficiency

No-Load Power

Ripple

Thermal

PI-7977-012417

www.power.com

5

Rev. B 10/17

Page 6

Application Note AN-69

P

V

2

22

c

m

General Guidance for Using the PIXls Design

Spreadsheet

Only the information described below needs to be entered into the

PIXls spreadsheet gray cells in column [B]. Some gray cells already

have entries in bold font, these contain drop down selections. If an

invalid selection is made, then Info or Warning text will appear in

column [C] and [D], a description of the error is displayed in column

[H]. Other parameters and component values will be automatically

calculated. References to spreadsheet cell locations are provided in

square brackets [cell reference].

The default design presented in a blank spreadsheet is for a 5 V, 2 A

adapter with 6% cable compensation and standard universal AC input

voltage range. All gray cells are blank except for those with bold text

drop down selections, which are set to the appropriate selections for

the default adapter. The default values are displayed in column [E]

and [F]. When an entry is made in a column [B] gray cell, its value is

transferred into the corresponding cell in columns [E] and [F] and

from there, used in the calculations.

Do not read off calculated component values etc, until all the data

has been entered.

It is only necessary to enter values into column [B] if they are

different to the default values in column [E].

Step 1 – Enter Application Variables VAC

V

, VD, IO, ICC, η

O

AC Input Voltage Range, VAC

Determine the input voltage from Table 2 for common choices, or

enter the application specication values into [B3, B4].

Nominal Input Voltage (VAC) VAC

100/115 85 132

230 195 265

Universal 85 265

Table 2. Standard Worldwide Input Line Voltage Ranges.

Note: For designs that have a DC rather than an AC input, enter the

values for minimum and maximum DC input voltages, V

V

[B58], directly into the grey override cell on the design spread-

MAX

sheet (see Figure 5).

Line Frequency, ƒ

Typical line frequencies are 50 Hz for universal or single 100 VAC,

L

60 Hz for single 115 VAC, and 50 Hz for single 230 VAC inputs. These

values represent typical, rather than minimum, frequencies. For most

applications this gives adequate overall design margin. To design for

the absolute worst case, or based on the product specications,

reduce these numbers by 6% (to 47 Hz or 56 Hz). For half-wave

rectication use F /2. For DC input enter the voltage directly into

cells, V

[B57] and V

MIN

MAX

[B58].

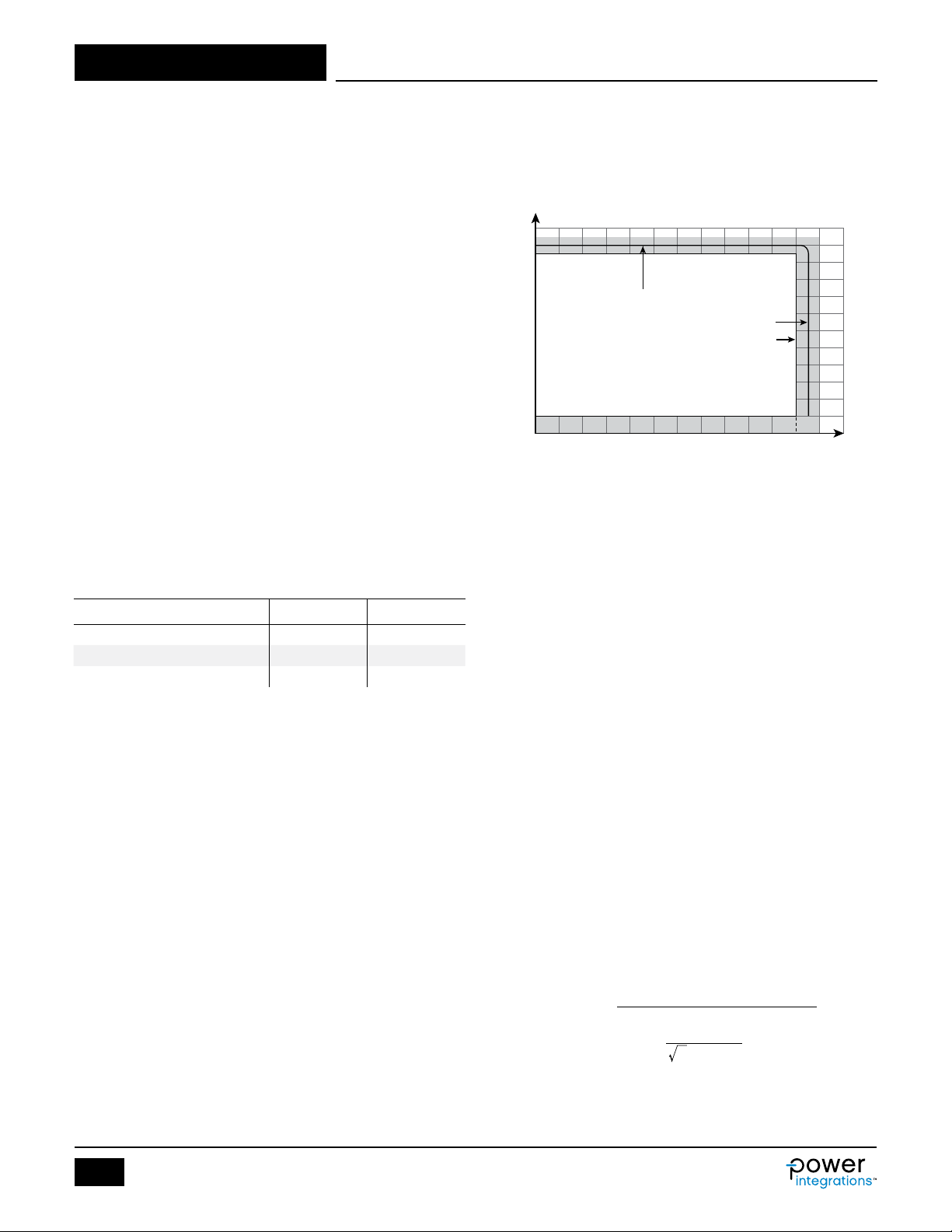

Nominal Output Voltage, VO (V)

For both CV/CC and CV only designs, V is the nominal output voltage

measured at the end of an attached cable carrying nominal output

current. The tolerance for the output voltage is ±5% (including initial

tolerance and over the data sheet junction temperature range).

Output Diode Forward Voltage Drop, VD (V)

Enter the average forward-voltage drop of the output diode. Use

0.4 V for a Schottky diode or 0.7 V for a PN-junction diode (if specic

diode data is not available). VD has a default value of 0.4 V.

MIN

, VAC

MAX

MIN

MIN

, VAC

VAC

[B57] and

MIN

MAX

MAX

, ƒL,

Minimum Required Output Current, I

This is the nameplate current and is the current that must be

O

(A)

supplied at the nameplate voltage, before the VI curve follows the

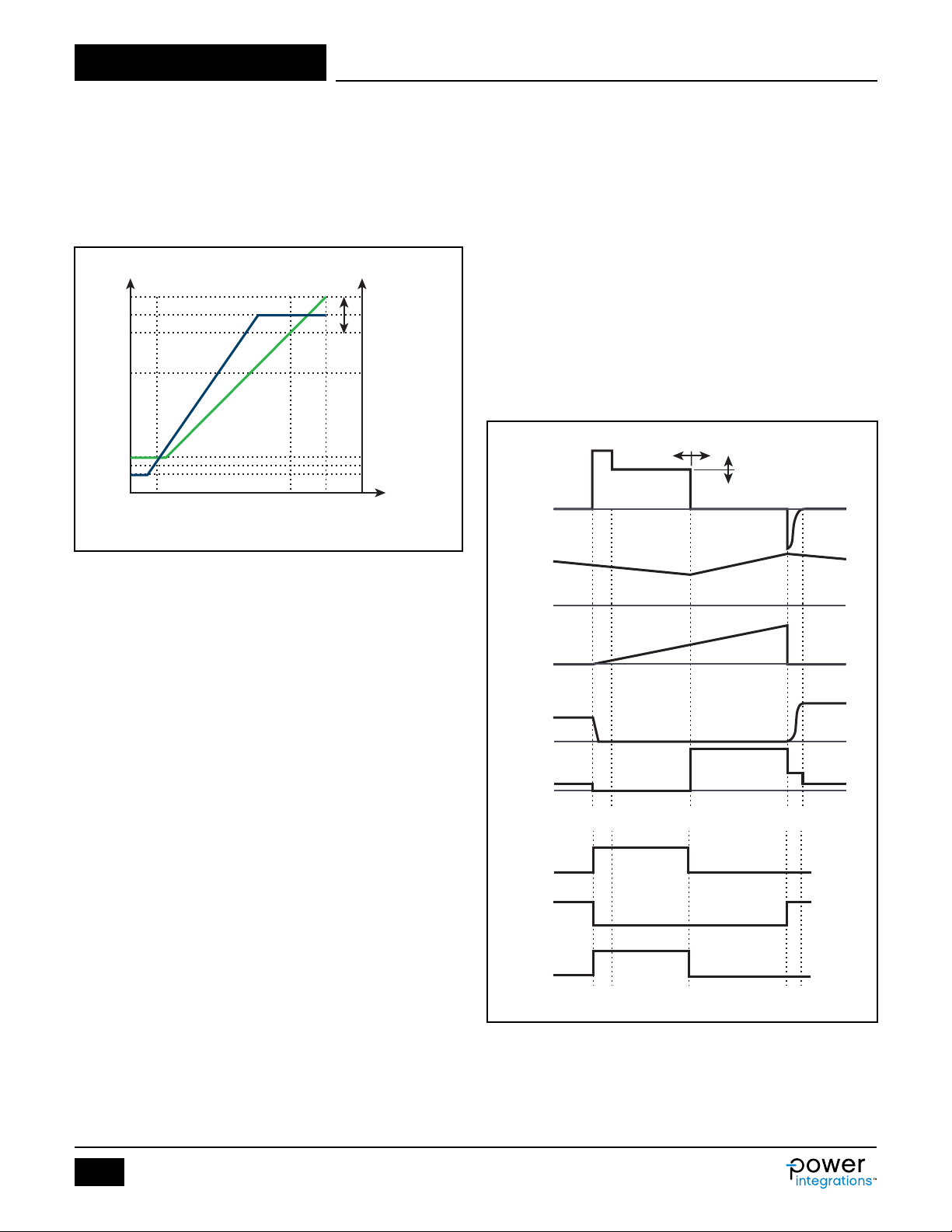

decreasing voltage CC characteristic. It is the output current level at

which efciency measurements are taken. See Figure 4.

V

OUT

100%

VO [B6]

I

[B10]

CC

I

O

0

Figure 4. VI Curve With Parameter Positions Identied.

[B9]

100%

PI-8108-092116

I

OUT

CC Mode Current Output Level, ICC (A)

In CC mode, the output current is regulated to the ICC value. There is

a 7% overall tolerance on the regulated value, so the spreadsheet

automatically defaults to setting this level to IO + 8%. It is possible

to set ICC to a higher level by entering a value into [B10], a higher

value will help start-up into CC and/or high capacitance loads. It is

recommended that ICC < IO+ 20% else efciency will be signicantly

reduced.

Power Supply Efciency, η

Enter the estimated efciency of the complete power supply, as

would be measured at the output cable end (if applicable). In

practice, use the applicable energy saving standard value. If the

completed power supply fails to meet this value of efciency, some

components may be over stressed, but as the design has failed the

efciency specication it will need modifying anyway, before being

accepted for production.

Total Input Capacitance, C

This is calculated from the maximum power drawn from the bulk

capacitors at VAC

(V

) at which the convertor will operate efciently, nominally 80 V,

MIN

and the line frequency (FL). The value calculated in [E13] - with [B13]

, the minimum allowable bulk capacitor voltage

MIN

IN

blank, is the minimum required capacitance. A higher value may be

entered into [B13] to round up to the nearest standard value, or

increase the operating efciency of the converter stage over the AC

input voltage range. The total value of CIN is then split into two

approximately equal values, C

It is advisable to make at least C

and C

IN1

IN2

a low ESR type.

IN2

, to provide the input pi lter.

The following equation may be used to calculate the minimum

capacitance required:

CC

IN IN

12

$

+

^

h

FVV

h

()

LMIN ACMIN MIN

arccos

O

^

2

##

V

-

MIN

#

ACMIN

#

h

-

Use higher values to allow for capacitor tolerance.

6

Rev. B 10/17

www.power.com

Page 7

Application NoteAN-69

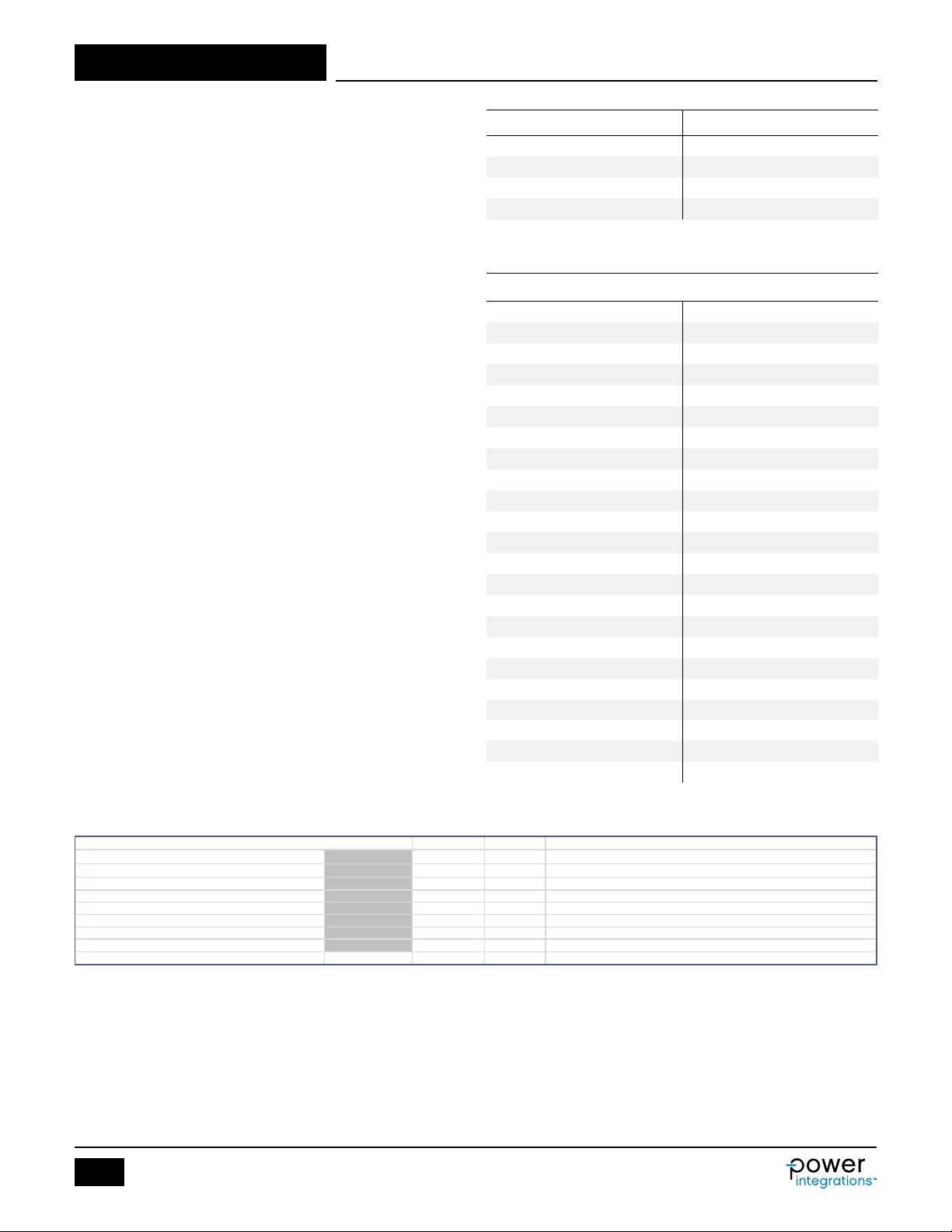

ENTER APPLICATION VARIABLES

VACMAX

265 Volts Maximum AC Input Voltage

fL 50 Hertz AC Mains Frequency

VO 5.00 Volts Output Voltage at the end of the cable

VO_PCB 5.30 Volts Output Voltage at PCB. Changes with cable compensation selection

VD 0.40 Volts Output Winding Diode Forward Voltage Drop

IO 2.00 Amps Full load rated current. Used for all waveshape related calculations.

ICC 2.16 Amps CC setpoint. Must be >= IO+7%. Affects Rc s.

PO 10.60 Watts Rated output power including cable drop compensation. Calculated from IO

n 0.80 %/100 Effic iency Estimate

ENTER LINKSWTCH-4 VARIABLES

LinkSwitch-4 LNK40X4D Select LNK-4

Cable drop compensation option 6% 6% Select level of cable drop compensation

DEVICE

Complete reference of select part number with the selected cable drop

compensation option

FSW 65000 Hertz LinkSwitch-4 typical switching frequency

ILIM_MAX 1.10 A Maximum emi tter pin sink current

Transistor

PART_NUMBER TS13005 Example transistor for the current application

HFE_STARTUP 12 Minimum DC current gain at no load and startup. Affects start-up delay

HFE 25 Minimum DC current gain for load transient

VSWMAX

700 Volts Switch Breakdown voltage

V_CGND_ON

BJT + LNK-4 on-state Collector to ground Voltage (3V if no better information

available)

VACMIN

CIN 20.0 uFarads Total input bulk Capacitance

Figure 5. Application Variables Section of the Design Spreadsheet.

Step 2 – Enter LinkSwitch-4 Selection

90 Volts Minimum AC Input Voltage

Output Power Table

Select the Cable Drop Compensation Option

Select the cable compensation option from the drop down selection

menu in [B19] to most closely match the percentage output voltage

drop in the output cable. For example, a 5 V, 2 A LNK40x4D design

with a cable impedance of 150 mW has a cable voltage drop of

-0.3 V. With a desired nominal output voltage of 5 V (at the end of

the cable), this represents a voltage drop of 6%. In this case, select

the +6% compensation, to give the smallest error. 0%, 3% or 6%

can be selected.

Selecting the Correct LinkSwitch-4 Part

Using the value for rated output power’ in cell [E11], use Table 1 on

page 1, to choose the correct LinkSwitch-4 device. Use the drop

down selection menu in [B18] to select that device. The full part

number is given in [E20].

The full load switching frequency of standard LinkSwitch-4 devices is

65 kHz.

Enter BJT selection

BJT types TS13003 (up to 5 W) and TS13005 (up to 18 W) are auto

LNK43x2S 13003 Drive 5 W

LNK40x2S STD 6.5 W

LNK40x3S STD 8 W

LNK4323S STD 8 W

LNK40x3D STD 10 W

LNK4323D STD 10 W

LNK40x4D STD 15 W

LNK4114D Easy Start 15 W

LNK4214D Easy Start + Constant Power 15 W

LNK4115D Easy Start 18 W

LNK4215D Easy Start + Constant Power 18 W

Table 3. Selection Table of LinkSwitch-4 Parts by Power and Maximum BJT

selected based on output power. There are 800 V and 900 V rated

Design title

Product

3,4

Features

Emitter Current (Primary Current).

TS13003 parts for special circumstances, such as snubberless design

or higher AC input voltage e.g. 420 VAC. To use a different BJT, enter

PART_NUMBER, HFE_STARTUP (low current gain), HFE (high current

gain) and VSWMAX (V

) into [B24, B25, B26, B27].

CBO

BJT Output Power

TS13005 Up to 15 W

TS13003 Up to 5 W

85 - 265 VAC

5

Adapter

1

Open Frame

2

Table 4. Recommended BJTs.

LNK4024D

3.0 Volts

Figure 6. LinkSwitch-4 and BJT Selection.

www.power.com

7

Rev. B 10/17

Page 8

Application Note AN-69

Core Type

EPC17 EPC17 Core Type

Custom Core (Optional)

If Custom core is used - Enter Part number here

Bobbin

P/N: BEPC-17-1110CPH

AE 0.23 cm^2 Core Effective Cross Sectional Area

LE 4.02 cm Core Effective Path Length

AL 1150 nH/T^2 Ungapped Core Effective Inductance

BW 9.55 mm Bobbin Physical Winding Width

M

0 mm Safety Margin Width (Half the Primary to Secondary Creepage Distance)

BWE

9.6 mm Effective Bobbin Width

ENTER TRANSFORMER CORE/CONSTRUCTION VARIABLES

Step 3 – Core and Bobbin Selection Based on Output

Power and Enter A

These symbols represent core effective cross-sectional area AE (cm2),

core effective path length LE (cm), core ungapped effective inductance

AL (nH/ Tu r n2), bobbin width BW (mm) and safety margin width M (mm).

Due to the small transformer size that results at these power levels,

triple insulated wire is generally used for the secondary, so Safety

Margin Width is not used and left set to the default ‘0’ setting. If the

Safety Margin method is preferred and standard wire used, enter the

safety margin width. The spreadsheet will double it and subtract it

from the bobbin width (BW) and give the effective bobbin width, or

winding width (BWE). Universal input designs typically require a total

margin of 6.2 mm, and a value of 3.1 mm entered into [B42]. The

spreadsheet uses the value of BWE to calculate the required wire diam-

eter to ll the available bobbin width to minimize leakage inductance.

For designs using triple-insulated wire it may still be necessary to

enter a small margin to meet required safety creepage distances.

Typically many bobbins exist for each core size, each with different

mechanical spacing. Refer to the bobbin data sheet or seek guidance

from your safety expert or transformer vendor, to determine the

requirement for your design. The margin reduces the available area

for windings, so margin construction may not be suitable for

transformers with smaller cores. If, after entering the margin, more

than three primary layers (L) are required, either select a larger core

or switch to a zero-margin design using triple-insulated wire.

If the drop down selection menu in [B35] is used and ‘AUTO’ selected,

the spreadsheet selects the smallest core size, by AE, that meets the

peak ux density limit. The user can select an alternative core from

drop down list of commonly available cores (shown in Table 6). Table 5

provides guidance on the power capability of specic core sizes.

If the user has a preferred core not in the list, then the appropriate

parameters can be entered into [B36 – B42].

, LE, AL, BW, M

E

Core Size Output Power Capability

EF12.6 3.3 W

EE13 3.3 W

EE16 6.1 W

EF20 10 W

Table 5. Output Power Capability of Commonly used Sizes in LinkSwitch-4

Designs.

Transformer Core Size

EE10 EF32

EF12.6 EFD15

EE13 EFD25

E24/25 EFD30

EE16 EI16

EE19 EI19

EE22 EI22

EEL16 EI25

EE16W EI28

EEL19 EI30

EEL22 EI35

EE25 EI40

EEL25 EPC17

EEL28 EPC19

EER28 EPC25

EER28L EPC30

EER35 ETD29

EER40 ETD34

EES16 ETD39

EF16 EE42/21/15

EF20 EE55/28/21

EF25 EF32

EF30

Table 6. List of Cores Provided in LinkSwitch-4 PIXls Spreadsheet.

Figure 7. Transformer Core Selection.

8

Rev. B 10/17

www.power.com

Page 9

Application NoteAN-69

MAIN OPTIMIZATION INPUTS

Turns and ratio

VOR 100.00 Volts Reflected Output Voltage. Use Goal Seek to get VCRMV to desired value.

NS

Number of Secondary Turns. Adjusting up or down along with VOR may improve

efficiency.

NP

105 Primary Winding Number of Turns

DC INPUT VOLTAGE PARAMETERS

VCRMV

94 Volts Vbulk at CRMV, at max LP tolerance. Higher value typically more efficient.

VMIN

Bulk cap "trough" voltage at VACMIN. Leave blank to calculate from capacitance

and load.

VMAX 375 Volts

Maximum DC Input Voltage

VBROWN

51

Volts

Bulk voltage it loses regulation

PRIMARY WAVEFORM PARAMETERS

F_RES 400 kHz Anticipated resonant frequency on the primary side (180<Ftrf<1200)

KCRMV 0.95 Ratio of primary switch off time to secondary conduction plus first valley time

IRMS 0.25 Amps Primary RMS Current (calculated at load=IO, VMIN)

IP 0.60 Amps Peak Primary Current (calculated at load=IO, VMIN)

IOCP

Pulse by pulse current limit. Appears during large load transients and brownout

operation.

IAVG 0.16 Amps Average Primary Current (calculated at load=IO, VMIN)

IP_CRMV 0.56 Amps Ipeak when Vin=Vcrm

F_CRMV 65000 Hz Fsw when Vin=Vcrm

FVMIN

62410 Hz Fsw at VMIN. If < 65kHz, is in frequency reduction mode

VCS_VMIN 0.273 Volts Vcs_pk at VMIN and load = IO

RCS

0.453 Ohm Calculated RCS value. Changes with Icc and VOR

SECONDARY WAVEFORM PARAMETERS

ISP 10.53 Amps Peak Secondary Current @ VMIN

ISRMS 3.67 Amps Secondary RMS Current @ VMIN

IRIPPLE

3.08 Amps Output Capacitor RMS Ripple Current @ VMIN

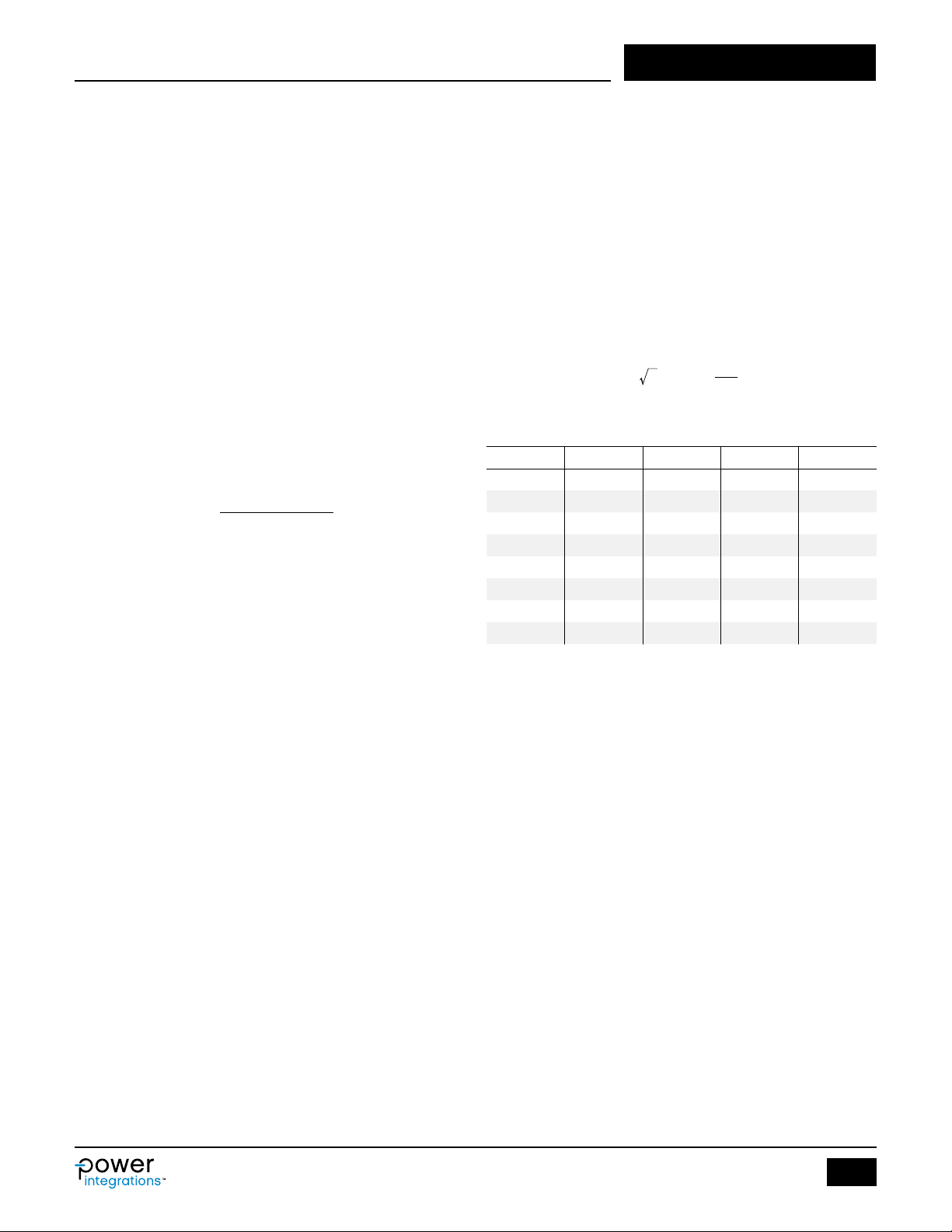

Step 4 – Select Reected Voltage and Secondary Turns

These are the main optimization inputs that effect efciency and the

minimum DC bulk capacitor voltage the converter will operate at,

under full load. The spreadsheet will produce a reasonably optimized

design, but further improvement may be possible. To optimize for

efciency enter an alternative value for the reected output voltage,

VOR in [B49], the default is 100 V. Whilst trying different values,

observe the changes in KCRMV [E65] and aim to get between 0.95

and 0.98, though 0.945 to 1.05 is acceptable. At the same time

ensure VCRMV-VMIN [E56-E57] is less than 15 V. The higher VCRMV

the better for efciency at the cost of some twice line frequency

ripple in the output at ICC and VO (maximum power point). Fixing

Figure 8. VOR and Secondary Turns Selection - Main Optimization Values.

the number of secondary turns in [B50] while sweeping the VOR

value [B49] offers further optimization possibilities.

The default primary inductance tolerance is 10%, an alternative value

can be entered in [B88]. Tighter tolerance allows better average

efciency across production.

F_RES is the idle ring frequency of the transformer whilst in the

application, so includes the effects of BJT collector capacitance and

and snubber capacitance. Use the default 400 kHz if no other gure

is available. Once the application has been tested, the true gure can

be entered and further optimization performed as required. Usually a

lower F_RES in the application will have an adverse effect, but it would

have to be signicantly lower to have a measurable effect, say -25%.

6

82.6 Volts

Figure 9. DC Input Parameter Entry and VCRMV Optimization Watch Value.

0.79 Amps

Figure 10. Figure 10: Primary Waveform Parameters and KCRMV Optimization Watch Value.

Figure 11. Secondary Waveform Design Parameters.

www.power.com

9

Rev. B 10/17

Page 10

Application Note AN-69

TRANSFORMER CORE PARAMETERS

BP

Peak Flux Density @ max IOCP & max LP. 3900 Gauss. Lower BP may reduce

LP 1099 uHenries Nominal Primary Inductance

LP Tolerance

Tolerance of Primary Inductance. Tighter tolerance allows better average

efficiency across production.

ALG 100 nH/T^2 Gapped Core Effective Inductance

BM 2763 Gauss Maximum Flux Density at PO, VMIN, LP (BM<3000)

BAC 1381 Gauss AC Flux Density for Core Loss Curves (0.5 X Peak to Peak)

ur 1614 Relative Permeability of Ungapped Core

LG

0.26 mm Gap Length (Lg > 0.1 mm)

L 3.0 Number of Primary Layers

OD 0.25 mm Maximum Primary Wire Diameter including insulation to fill layers

INS 0.05 mm Estimated Total Insulation Thickness (= 2 * film thickness)

DIA 0.20 mm Bare conductor diameter

AWG 33 AWG Primary Wire Gauge (Rounded to next smaller standard AWG value)

Primary Current Density (J) 5.23 Amps/mm^2 Primary Winding Current density (3.8 < J < 10)

Bias/Feedback Winding

NB 9 Turns Suggested number of turns for the bias / feedback winding

VDB 0.70 Volts Bias Winding Diode Forward Voltage Drop

VB_NOLOAD 7.40 Volts Desired Minimum Bias voltage at no load

PB_NOLOAD 4.14 mW Bias winding power consumption estimate at no load

VB_NOLOAD_MEASURED

7.40 Volts Measured Bias voltage at no load

TRANSFORMER PRIMARY DESIGN PARAMETERS

Step 5 – Transformer Core Parameters

The default peak core ux is set to 3900 Gauss. If the users selected

core material requires a different value, enter it into [B86].

The default tolerance on the primary inductance is ±10%. A tighter

tolerance allows better average efciency across production, an

alternative value may be entered into [B88].

Step 6 – Transformer Primary Winding Design

Parameters

The default number of primary winding layers is 3, however if [H103]

indicates that the current density is low, then 2, or even 1, can be

Figure 12. Transformer Core Operational Parameters.

entered into [B98] and the wire diameter will be reduced accordingly.

The lower the number of primary layers, the lower leakage inductance is likely to be. However it may be possible that sandwiching

the secondary between 2 primary layers would result in the lowest

leakage inductance at the cost of a more complicated transformer

construction.

If [H103] indicates that the current density is high, then a higher

value must be entered into [B98]. More than 3 primary layers will

result in high primary to secondary leakage inductance, resulting in

high-voltage stress on the BJT or increased clamp/snubber losses, so

it may be necessary to sandwich the secondary between layers of the

primary.

3900 Gauss

10

efficiency

Figure 13. Transformer Primary Design Parameters.

10

Rev. B 10/17

www.power.com

Page 11

Application NoteAN-69

V

VV

V

OUTDOUT

+

+

N

N

P

=+

^^hh

Step 7 – Bias / Feedback Winding Design Parameters

The bias / feedback winding performs two functions, as its name

suggests. Firstly, it provides power to the controller after the start-up

period and secondly, it provides the feedback signal to monitor output

voltage and bulk capacitor voltage.

During the start-up period, the controller is powered by the charge

held on the VCC capacitor C

V

, 4.5 V, the output voltage from the bias winding must exceed

VCC(SLEEP)

V

VCC(SLEEP)+VDB

related to the voltage on the secondary winding, which in turn, is

. The voltage from the Bias winding during start-up is

related to the voltage on the output capacitor, which is charging from

0 V to V

starting with high output capacitance or constant current loads, but

. Hence more turns on the bias winding results in easier

OUT

results in a higher no-load power. Conversely, a lower number of

turns results in a reduced output capacitance or constant current load

start-up capability, but lower no-load power. A good starting point is

to aim for a no-load VCC voltage of between 8 V and 9 V, 7 V is the

minimum. The no-load level of VCC is determined by the turns ratio of

the secondary and bias turns, whereas the VCC level with load applied

is increased by energy scavenged from leakage inductance and is not

practical to calculate. Check the VCC level on the completed design,

checking that at the maximum AC input voltage and at maximum load

or start-up, VCC does not exceed 16.5 V.

N

BIAS

The bias supply diode should be a silicon junction device, a Schottky

has too much reverse leakage and may prevent start-up. The spreadsheet has 0.7 V entered as the default forward volt drop of the bias

supply diode, suitable for a silicon junction diode. An alternative

value may be entered into [B106] if required.

The spreadsheet defaults to calculating the required number of bias

wind turns to give at least 7 V with an integer number of turns. The

number of turns calculated is given in [E105] and the resulting VCC

level, at no-load, is given in [E109]. As previously discussed, between

8 V and 9 V is recommended, so enter ‘8’ into [B107]. The spread-

sheet will recalculate the number of turns to achieve a level of at

least 8 V. The revised number of Bias wind turns are given in [E105]

and the actual VCC level, at no-load, is given in [E109].

. Before the voltage on C

VCC

^h

CC No Load

-

DBIAS

#=

falls to

VCC

N

S

For applications that have challenging start-up conditions, CC load

and/or high output capacitance, a higher value of target V

entered into [B107], 9 V for example. Note however, that the Bias

may be

CC

winding power, given in [E108], increases with Bias voltage. Check

the no-load power estimation in [E174] is within specication. Check

the VCC level on the completed design, conrm that at the maximum

AC input voltage and at maximum load or start-up, VCC does not

exceed 16.5 V.

Bias Supply Diode Selection

In most circumstances a 1N4148 is adequate. In situations where

more leakage energy scavenging is required, to assist start-up for

example, a higher current ultrafast silicon diode may be used.

The maximum reverse voltage across the Bias diode is calculated in

[E129], add margin to this value before selecting a suitable part.

Suggested parts are given in Table 7.

VV

DBIASMAX ACMAX

Where V

= 16.5 V worst case.

CC(MAX )

Typ e TRR (ns) V

#

(V) VFD (V) @ IF (A)

RRM

A

V2

CC MAX

1N4148 4 75 1.0 0.15

1N4933 50 50 1.0 1.0

SF11G 35 50 1.0 2.0

UF4001 50 50 1.0 2.0

BY V27-50 25 50 1.0 2.0

UG1A 25 50 1.0 3.0

ES1A 35 50 1.0 3.0

ST TH1R02 15 200 1.0 3.0

Table 7. Suggested Bias Supply Diodes.

www.power.com

11

Rev. B 10/17

Page 12

Application Note AN-69

LS 1.0 Number of Secondary Layers

FilarS 2 # of paralleled secondary wires

ODS 0.76 mm Maximum Secondary Wire Diameter including insulati on to fill layers

INSS 0.20 mm Estimated Total Insulation Thickness (= 2 * film thickness)

DIAS 0.56 mm Bare conductor diameter

AWGS 24 AWG Secondary Wire Gauge (Rounded to next smaller standard AWG value)

Secondary Current Density (J)

7.56 Amps/mm^2 Winding Current density (3.8 < J < 10)

TRANSFORMER SECONDARY DESIGN PARAMETERS

Step 8 – Secondary Winding Design Parameters

Generally only one winding layer is used for the secondary, but for

high output voltage designs or very narrow winding window bobbins,

more may be needed. However, be aware that more layers mean

more leakage inductance and probably a reduction in efciency.

The spreadsheet defaults to 1 layer and calculates the required wire

diameter that will ll the bobbin width in the calculated number of

secondary turns.

Figure 14. Transformer Secondary Design Parameters.

If more layers are required to increase wire diameter, enter the value

into [B116].

For low voltage designs with a wide bobbin width, the required wire

thickness to ll the bobbin width may result in a wire thickness that is

too large to easily wind on the bobbin. To alleviate this problem, the

secondary can be wound in a number of lars (strands) in parallel and

side by side with each other. The spreadsheet calculates a recom-

mended number of lars displayed in [E117] required to keep wire

diameter practical. Approximately 1 mm outside diameter is the

spreadsheet target limit, but by entering the number of required lars

in [B117] the wire diameter can be reduced or increased as required.

From the effective bobbin width, number of turns, layers and lars,

the maximum outside diameter of the secondary wire is calculated.

A custom value can be entered into [B118], but this does not

recalculate the number of layers or lars. It does recalculate the bare

conductor diameter in [E120] and is useful for investigating the effect

on secondary winding current density.

The default secondary wire insulation thickness is 0.1 mm, as would

be found on available triple insulated wire. This is doubled to give

the space required for the insulation on the bobbin in [E119]. A

custom value (2 x insulation thickness) can be entered into [B119].

[E120] gives the bare conductor diameter, this can be used to select

the nearest available diameter e.g. the 0.56 mm value in the example

can be rounded down to 0.55 mm standard diameter. [E121] gives

the closest rounded down AWG standard wire gauge. If using AWG

sized wire, check that the rounded down AWG size is not too big a

reduction on the optimum size and not ll the bobbin width. If the

reduction is signicant, add a turn to the value in [B50] and check if

the AWG size suggested is closer to the optimum diameter. Then

re-check the primary wind results. A small adjustment to the

reected voltage VOR in [B49] can be used to optimize the primary

winding to ll the bobbin winding width.

Secondary winding current density is given in [E122], a value below

10 should be the target to limit transformer temperature rise at full

load. If the value is below 3.8, a smaller transformer may be possible,

but this is also determined by the primary winding parameters.

12

Rev. B 10/17

www.power.com

Page 13

Step 9 – Voltage Stress Parameters

VOLTAGE STRESS PARAMETERS

SWITCH_DERATING 0.10 %/100 Desired derating factor for switch

VCOLLECTOR 605 Volts Maximum Collector Voltage Estimate (Includes Effect of Leakage Inductance)

PIVS 27 Volts Output Rectifier Maximum Peak Inverse Voltage

PIVB

49 Volts Bias Rectifier Maximum Peak Inverse Voltage

Figure 15. Voltage Stress Parameters.

Application NoteAN-69

The default BJT switch derating factor is given in [E126] as 10%,

enter a custom value in [B126] if required. [E127] gives an estimate

of the maximum collector voltage of the switching BJT based on the

maximum bulk capacitor voltage, VOR and an estimate of the leakage

inductance spike. If this exceeds the maximum allowed BJT collector

voltage, a warning is given in [C127]. If a warning is given, check the

BJT derating factor is correct, if it is, select a BJT with a higher V

CBO

The maximum reverse voltage across the secondary diode is

calculated in [E128], add margin to this value before selecting a

suitable part. For low output voltage designs i.e. 5 V, the forward

voltage drop of the output diode greatly affects efciency, so it is

usual to choose a higher current part to help achieve the target

efciency i.e. >10 times rated output current.

.

Series Number Type VR Range (V) IF (A) Package Manufacturer

1N5817 to 1N5819 Schottky 20-40 1 Leaded Vishay

SB120 to SB1100 Schottky 20-10 0 1 Leaded Vishay

11DQ50 to 11DQ60 Schottky 50-60 1 Leaded Vishay

1N5820 to 1N5822 Schottky 20-40 3 Leaded Vishay

MBR320 to MBR360 Schottky 20-60 3 Leaded Vishay

SB320 to SB360 Schottky 20-60 3 Leaded Vishay

SB520 to SB560 Schottky 20-60 5 Leaded Vishay

MBR1045 Schottky 35/45 10 Leaded Vishay

UF4002 to UF4006 Ultrafast 100-600 1 Leaded Vishay

UF5401 to UF5408 Ultrafast 100-800 3 Leaded Vishay

MUR820 to MUR860 Ultrafast 200-600 8 Leaded Vishay

BYW29-50 to BYW29-300 Ultrafast 50-20 0 8 Leaded/SMD Vishay

ESA1A to ES1D Ultrafast 50 -20 0 1 SMD Vishay

ES2A to ES2D Ultrafast 50-200 2 SMD Vishay

SL12 to SL23 Schottky (low VF) 20-30 1 SMD Vishay

SL22 to SL23 Schottky (low VF) 20-30 2 SMD Vishay

SL42 to SL4 4 Schottky (low VF) 20-30 4 SMD Vishay

SBR1045SD1 Schottky (low VF) 45 10 Leaded Diodes

SL42 to SL4 Schottky (low VF) 20-30 4 SMD Vishay

SBR1045SP5 Schottky (low VF) 45 10 SMD Diodes

Table 8. List of Recommended Secondary Diodes That May be used with LinkSwitch-4 Designs.

www.power.com

13

Rev. B 10/17

Page 14

Application Note AN-69

Bias Capacitor

CBIAS

Voltage ripple on VCC capacitor at zero-load (should be between 0.05 V and

1.6 V

Zero-load Collector peak current

VCS_MI N

Drives peak current at zero load. Affects zero load frequency and consumption,

and 0-100% load step

RCS2

270 Ohm Resistance for setting VCS_MIN

Dummy load and no load

R_PRELOAD

Pre load resistor (1%). Affects FSW_NOLOAD, zero load consumption, and

P_PRELOAD 4.4 mW Preload resistor power consumption at no load

FSW_NOLOAD

Estimated switching frequency at no load. Adjust with VCS_MIN and

R_PRELOAD

Step 10 – Additional Parameters

Bias Capacitor - CVCC

DELTAV_BIAS

Figure 16. Bias Capacitor Selection.

The bias capacitor serves three purposes:

1. Energy storage during the start-up procedure. The bias capacitor

powers the controller until the bias winding generates enough

voltage, which is limited by the voltage on the output capacitor,

to power the controller.

2. Acts as an energy reserve between switching cycles to power the

controller, particularly at no-load where the switching frequency

is low.

3. Forms part of the timing mechanism for the switching frequency

oscillator at no-load.

For easy starting into large output capacitance the bias capacitor

value can be made large. However, it must be a ceramic type

capacitor, an electrolytic capacitor will leak and possibly prevent

start-up especially as it ages. Also the bias capacitor must not be so

large that the ripple voltage on the VCC pin will be less than 50 mV at

the zero load switching frequency. If the ripple is less than 50 mV at

zero load, the controller will cease switching and power cycle. It

must detect the step in VCC when the transformer discharges to

move to the next state in the switching cycle when at zero load.

If the design has a zero load to partial or full load transient requirement, as found for USB charger designs, where the output voltage

must not fall below a given limit, the bias capacitor value should not

exceed 2 mF. Larger values of bias capacitor result in a very shallow

discharge curve across the capacitor. A voltage shifted version of this

curve is used to intersect with the internal switching frequency

oscillator capacitor charge voltage to start the next switching cycle.

If the angle of intersection is too shallow, thermal noise will make the

trigger point less predictable and the zero load frequency will vary

erratically. The average frequency will be such as to keep the output

voltage under zero load to be within specication, but the resulting

minimum frequency will allow a transient load to pull the output

voltage below the minimum allowed, if the transient coincides with a

low frequency cycle.

The bias capacitor ripple should not be allowed to exceed 1.6 V. If

VCC falls by more than 1.6 V in a switching cycle, an extra minimum

primary current pulse is issued. This will recharge the bias capacitor

5.38 uF

100 mV

to prevent V

cause a power reset cycle. If this happens too often, the output

Bias capacitor is greater than 2uF! Transient response could be unpredictable.

For improved and repeatable transient response keep capacitor value < 2 uF

falling inadvertently to the sleep level, which would

CC

voltage will rise and may exceed the specication.

The spreadsheet calculates the bias capacitor size to give 100 mV of

ripple [E139]. Alternative values can be entered into [B138] and the

new ripple level (Delta_Vbias) will be given in [E139].

Zero-Load Collector Peak Current

VCS_MIN is the minimum peak voltage that the controller can set

across the RCS resistor. This sets the minimum primary current and

hence the minimum energy per switching cycle. On LNK4xx3x,

LNK4x14D and LNK4x15D devices there are four discrete levels that

can be set, 58 mV, 73 mV. 94 mV and 127 mV. These are set by the

resistor R

No other values can be used, there are no intermediate values of

which can be 100 W, 270 W, 470 W or 1 kW respectively.

CS2

VCS_MIN. LNK40x2S devices only have one level for VCS_MIN, 88 mV.

VCS_MIN is used to control the zero load behavior of the circuit,

particularly the zero load switching frequency. The higher the VCS_

MIN level, the lower the zero load switching frequency and the lower

the zero load power. However, the lower the zero load switching

frequency, the larger the output capacitors must be if there is a zero

load transient requirement. Larger output capacitors require a larger

bias capacitor which cannot be greater than 2 mF in this situation.

A zero load switching frequency of between 1 kHz and 2 kHz should

be the target, calculated in [E154].Use the drop down selection table

in [B145] to select the required VCS_MIN. The required value of R

is given in [E136]. The higher the frequency, the easier it is to

start-up and meet zero load transient requirements, but zero load

power will be greater.

Dummy Load Resistor R

The value of R_PRELOAD (R

switching frequency [E154] by entering a value in [B152]. Aim to

OUT

) can be used to trim the zero load

OUT

have the dummy load power dissipation [E153] no lower than the bias

winding power at no-load [E108]. This aids consistent zero load

behavior across production.

CS2

73 73 mV

Figure 17. Zero-Load Peak Collector Current Selection.

5620 Ohm

1116 Hz

Figure 18. Dummy Load Resistor Selection.

0-100% load step dip

14

Rev. B 10/17

www.power.com

Page 15

Application NoteAN-69

Output Capacitor

LOAD_TYPE

ICC_STARTUP 1.50 A Not used for resistive startup calculation

R_LOAD

COUT_ADVISED 2281 uF Maximum Cout to guarantee proper startup and stability

COUT_FINAL

2281 uF Total output capacitance on the secondary of the power supply

Load step and undershoot

RCABLE_EST 0.150 Ohm Estimated charger cable resistance

I_LOADSTEP 2.00 A Required maximum current load step from zero load

V_UNDERSHOOT 3.70 V Accepted undershoot during maximum load step

FSW_UNDERSHOOT

877 Hz Minimum frequency at no load in order to satisfy undershoot requirements

Startup

STARTUP_TIME 1.00 second Desired startup delay time

R_STARTUP

Startup resistor (default calculation assumes a standard resistor for desired

startup)

STARTUP_TIME_FINAL

1.00 second

Final startup time assuming resistor value Rstartup

Output Capacitor C

The spreadsheet will calculate the maximum size of output capacitor

OUT

into which the circuit can start up. This is mainly governed by the

size of the bias capacitor [E138], which has to supply power to the

controller during start-up, and the ratio between secondary and bias

winding turns. It can be selected to calculate this for either a

constant current load at start-up or a resistive load via the drop down

selection menu in [B141]. The level of the constant current load at

start-up can be set in [B142], the default level is 75% of IO [E9]. The

resistive load is made equal to that required to draw IO [E9] and

includes any cable resistance implied by the selected cable compensation [E19].

The calculations do not take into account the effects of primary to

secondary leakage inductance. The bias winding is quite effective in

harvesting some of this energy and allows for a larger output

capacitance than that given in [E144]. It would be reasonable to

enter a value into [B145] that is 25% higher than that given in [E144]

if the end design is thoroughly tested across a pre-production run.

Output capacitors must be rated to have sufcient current ripple

capability i.e. ≥[E81]. Do not simply increase the capacitor value to

meet the ripple requirement, else starting difculties may occur, the

capacitance must not exceed [E145]. Selecting a capacitor with a

higher rated voltage will also achieve a higher ripple current rating.

Select the capacitor voltage to be ≥1.2 × VO_PCB.

Resistive Load Resistive Load

Load Step and Undershoot

In this section the zero load transient response is evaluated. It is

essential to have the zero load switching frequency in [E154] greater

than the minimum undershoot switching frequency given in [E150].

Adjust VCS_MIN [B135], COUT_FINAL [B145 via E144] and R

[B152] to achieve this. Parameters for load step current can be

OUT

entered in [B148] and minimum undershoot voltage set in [B149].

The zero load switching frequency requirement comes from the

operation of a primary side sensing yback convertor. The controller

can only sample the output voltage at the end of the transformer

discharge period. If a load transient occurs just after the discharge

period, the output capacitor will be discharged until the next switching

cycle measures the drop in output voltage. Therefor, if the output is

not to fall too much, the output must be sampled often enough.

Start-Up

Enter the allowed start-up time into [B156], 1 second is the default.

The spreadsheet calculates the size of the start-up resistor from the

current required to charge up the bias capacitor C

‘run voltage’ V

adds pin leakage currents.

and divides it by the BJT low current gain and

CC(RUN)

from zero to the

VCC

Round down the value in [E157] to the nearest standard value and

enter that into [B157]. An estimate of the start-up time is given in

[E158].

Select load type for startup testing. This will help estimate the maximum output

capacitance that will allow proper startup under any normal operating conditions

Figure 19. Output Capacitor Selection.

Figure 20. Load Step and Undershoot Parameters.

Figure 21. Start-up Resistor Value.

2.65 Ohm Equivalent resistive load placed at the end of PCB for simulating load and cable

14.70 MOhm

www.power.com

15

Rev. B 10/17

Page 16

Application Note AN-69

Feedback Resistors

V_UV+ 92.9 V

DC voltage at which power supply will start up

RFB1 7500 Ohm

Initial estimate for top feedback resistor (std value, use 1% tolerance)

RFB2

2370 Ohm Initial estimate for bottom feedback resistor (std value, use 1% tolerance)

NO LOAD POWER ESTIMATOR

EFF_NOLOAD 0.60 %/100 Assumed efficiency at no load (0.6 if no better data available)

VAC_INPUT 230 Volts AC input voltage for no load power estimation

PB_NOLOAD 4.1 mW Bias winding power consumption estimate at no load

P_PRELOAD 4.4 mW Preload resistor power consumption at no load

P_STARTUPRES 7.2 mW Energy dissipated by the startup resistor

PSW 6.6 mW Power losses of the switch and clamp

P_NOLOAD_TOTAL

28 mW Estimated no load power consumption. Affected by Vcs_min

Feedback Resistors

R

sets the minimum HT voltage at start-up that will allow the

FB1

controller to continue to run. 73% of root(2) × VAC

and will generally be satisfactory for most designs but an alternative

is the default

MIN

value may be entered in [B160] for special circumstances. It also

sets the brown-out level which is 43% of this value.

R

, in conjunction with R

FB2

in [E162]. Two resistors in series can be used to make up R

high value and one low value. The low value may be trimmed in

Figure 22. Feedback Resistor Values.

Figure 23. No-Load Power Estimation.

sets the output voltage and is calculated

FB1

FB1

, one

value to obtain an accurate output voltage. In fact the spreadsheet

will tend to result in a slightly high output voltage as the high current

value of output diode volt drop is used, but the chip measures the

output voltage when the secondary discharge current is close to zero.

Step 11 – No-Load Power Estimator

Here, all the no-load losses are calculated and summed to give a

no-load power estimate. Aiming for a 27 mW target should result in a

30 mW design with adequate margin.

16

Rev. B 10/17

www.power.com

Page 17

Step 12 – Results Check

Now that all the variables have been entered, the results can be

assessed.

1. Check entered values and options are correct.

2. Check core gap is manufacturable [E93], generally >0.1 mm. If

not, increase secondary turns [B50] which will increase the gap

for the same inductance, or reduce Flux Density [B86] which

lowers inductance, then re-optimize transformer.

3. Check primary current density [E103]. If low, try decreasing

layers [B98]. This will reduce leakage inductance and improve

efciency.

4. If primary current density too high, increase layers.

5. Check bias voltage at no-load [E107] is between 8 V and 9 V.

Lower voltage improves no-load power, higher voltage aids

start-up into difcult loads.

6. Check secondary wire diameter is practical to wind on bobbin

used i.e. not too large. If so, increase lars [B117], if this results

in the secondary current density being too high [E122] increase

layers [B116]. Alternatively, just reduce the single lar wire size

to an acceptable diameter. This will not fully ll the bobbin winding

window width and leakage inductance will increase, but it might

be acceptable. Spreading the secondary winding evenly across

the bobbin width will lessen the increase in leakage inductance.

7. Check peak collector voltage [E127] is lower than the derated

maximum level.

8. Check PIV applied to the output diode [E128] is below the

derated voltage rating of the selected output diode.

9. Check PIV applied to the bias diode [E129] is below the derated

voltage rating of the selected bias diode.

10. Check high frequency ripple current rating of the chosen output

capacitors against the secondary RMS current [E81].

11. Check bias voltage delta at no-load [E139] is between 50 mV and

1.6 V. It will tend to be a few hundred mV.

12. If there is a no-load transient test for the design, check that

[E150] < [E154]. As [E154] is an estimate, this relationship must

be tested and veried on the prototype circuit.

Application NoteAN-69

Component values for the design are found in:

C

+ C

, CIN ....................................................................... [E13]

IN1

IN2

Selected device ...................................................................... [E20]

Q1 BJT ................................................................................... [E24]

T1 Core .................................................................................. [E35]

T1 Bobbin ............................................................................... [C37]

T1 Primary turns ..................................................................... [E51]

T1 Primary layers .................................................................... [E98]

T1 Primary wire diameter ............................................. [E101, E102]

T1 Secondary turns ................................................................. [E50]

T1 Secondary layers .............................................................. [E116]

T1 Secondary lars ............................................................... [E117]

T1 Secondary wire diameter ......................................... [E120, E121]

T1 Bias turns ........................................................................ [E106]

T1 Core gap ............................................................................[E93]

C

, Bias capacitor value ....................................................... [E138]

VCC

Total output capacitance C

Output capacitance ripple ........................................................ [E8 1]

R

Dummy load .................................................................. [E152]

OUT

RHT Start-up resistor .............................................................. [E157]

R

Upper feedback resistor ...................................................[E 161]

FB1

R

Lower feedback resistor .................................................. [E162]

FB2

RCS Current sense resistor ........................................................ [E74]

R

Bias diode V

D

D

D

setting resistor ...................................................... [E136]

CS2 VCSMIN

OUT VRRM

Peak current .................................................................... [E79]

OUT

RMS current .................................................................. [E780]

OUT

.............................................. [E129] usually 1N4148

RRM

.............................................................................. [E128]

Explore the spreadsheet for more informative data.

................................................ [E145]

OUT

www.power.com

17

Rev. B 10/17

Page 18

Application Note AN-69

P

=+

PI-5118-042308

+

D

IN2

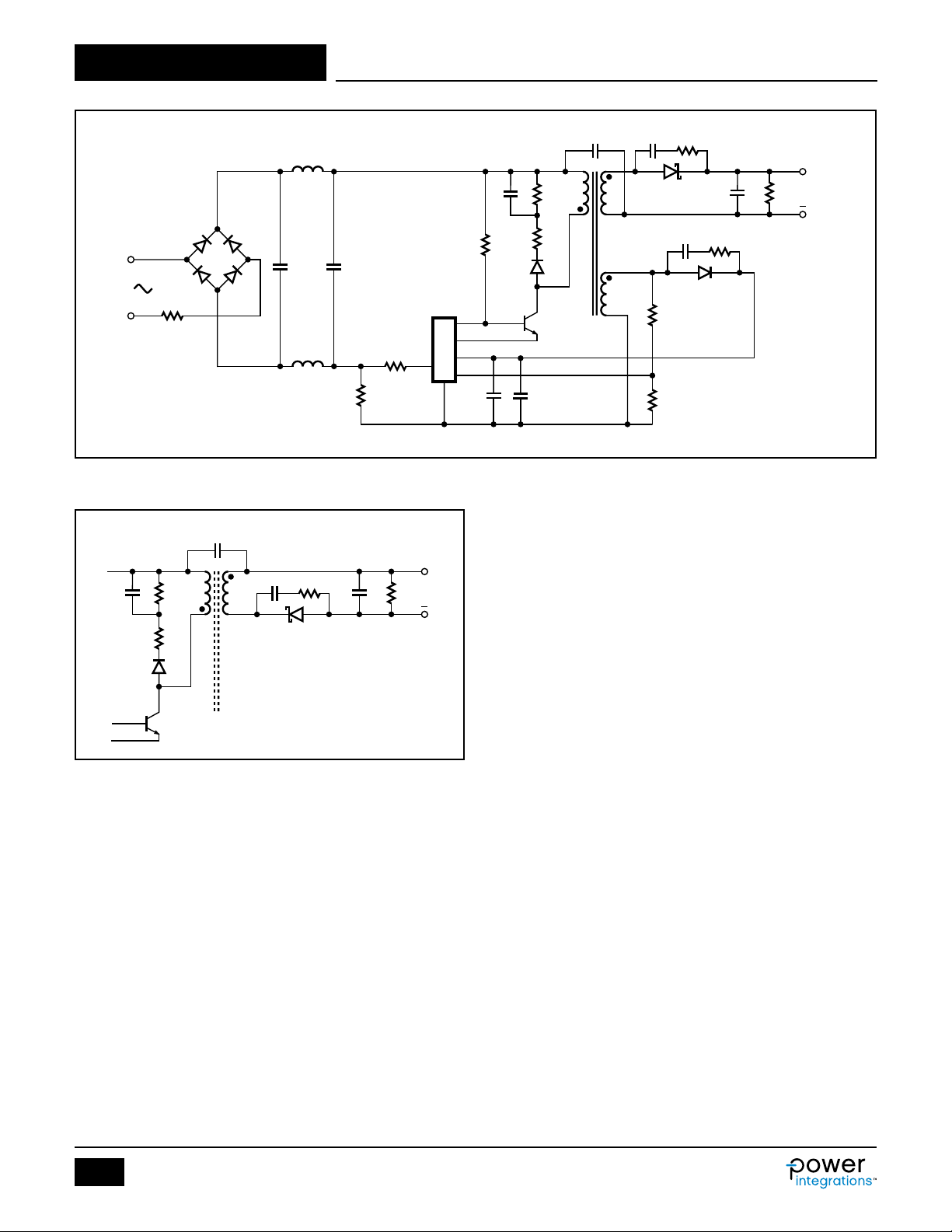

Step 13 - Further Component Selection Input Stage

IN1-4

L

R

AC IN

Figure 24. Input Stage.

F1

IN1

C

IN1

L

C

IN2

The recommended input stage is shown in Figure 24. It consists of a

fusible element (RF1), input rectication (D

(C

IN1 CIN2 LIN1

and L

).

IN2

), and line lter network

IN1- 4

The fusible element can be either a fusible resistor or a fuse. If a

fusible resistor is selected to limit switch on inrush current, use a

ameproof type.

Depending on the differential line input surge requirements, a

wire-wound type may be required. Avoid using metal or carbon lm

types as these can fail due to the inrush current when VAC applied

repeatedly to the supply. A value of 10 W, 2 W is a typical value.

C

and C

IN1

lter. It is advisable to make at least C

L

should be between 220 mH to 2.2 mH, and have a current rating

IN1

of approximately:

are approximately equal values, to provide the input pi

IN2

^h

ILC

40 10

IN IN

1

##

IN2

3

a low ESR type.

V

OUT

HT(MIN)

2

Although inductors have a current rating for a given temperature rise,

that current is often the level at which the inductance has fallen to

90% of its low current value. So given that it is not desirable that the

inductor saturates and reduces in inductance, hence reducing its

ltering capability, it is a reasonable guide, though the inductor will

be operating at a much lower average current than its rating.

The best EMI results are not always achieved by putting in the

highest available inductor value. The inductor will have a self

resonant frequency (SRF) which tends to decrease with inductor

value. A high value inductor may well have a SRF that coincides with

one of the switching generated frequencies and it will have minimal

attenuating effect upon it. Decreasing the inductor value may move

the SRF out of a sensitive frequency band and give better EMI

results. Alternatively, a resistor can be placed in parallel with the

inductor to damp the SRF, about 4.7 kW would sufce.

L

is optional and helps with higher frequency EMI emissions, >20

IN2

Mhz. It is usually a low value SMT ferrite bead inductor of the order

of 150 W to 1000 W impedance at 100 MHz.

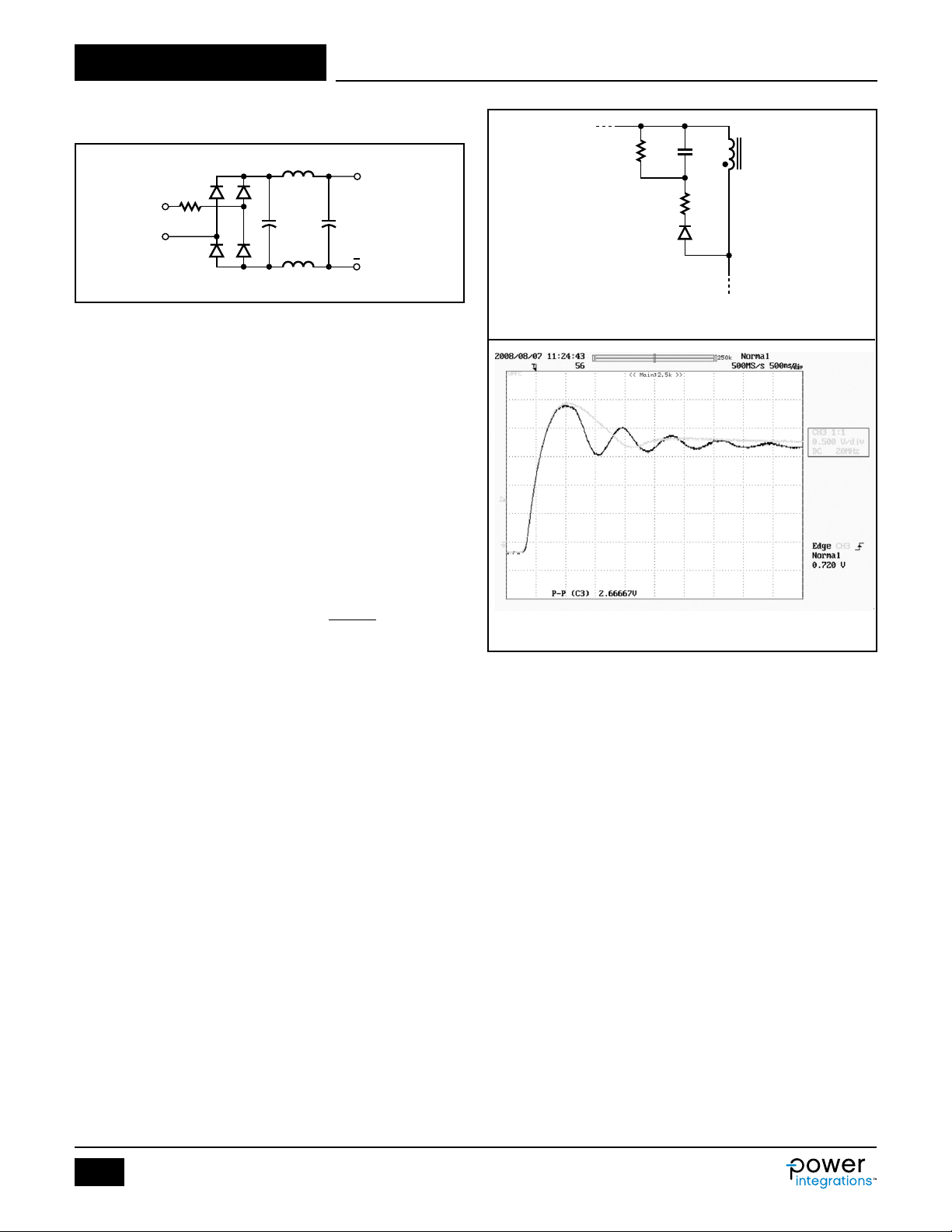

Primary Clamp Components

DC1: 1N4007 / FR107, 1 A, 1000 V

RC1: 100 W – 300 W

CC1: 220 pF – 1000 pF 500 V

RC1: 330 KW - 680 KW

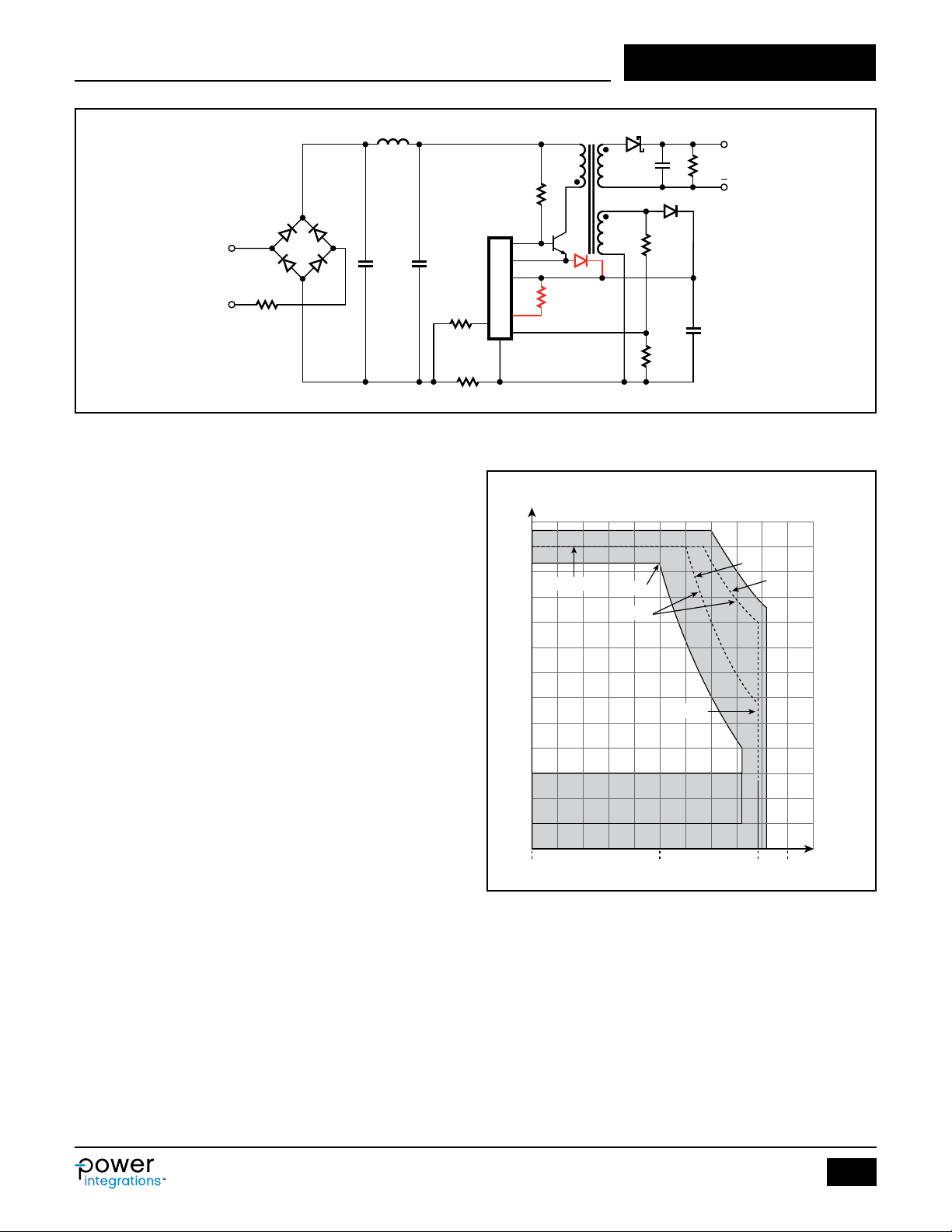

The clamp arrangement, shown in Figure 25, is suitable for LinkSwitch-4

designs. Minimize the value of CC1 and maximize RC2 while maintain-

ing the peak Collector voltage to <(V

× derating factor). Larger

CBO

R

C1

D

C1

C

C1

PI-5107-012615

R

C2

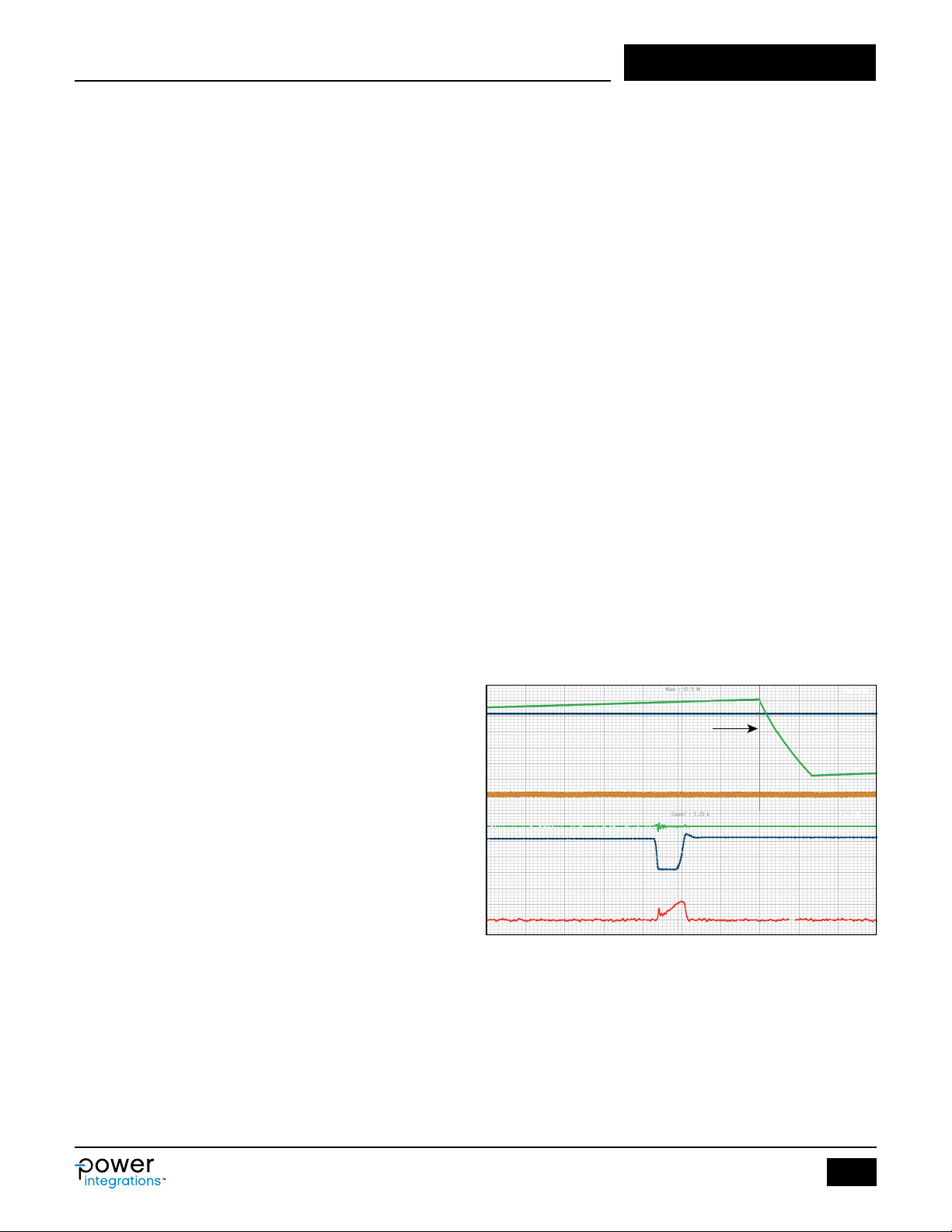

Black Trace: DC1 is a FR107 (fast type, trr = 500 ns)

Gray Trace: D

Figure 25. Primary Clamp Components and Effect of Diode Recovery Time of

FEEDBACK Pin Voltage.

is a 1N4007G (standard recovery, trr = 2 us)

C1

values of CC1 may cause higher output ripple voltages due to the

longer settling time of the clamp voltage impacting the sampled

voltage on the feedback winding, particularly at low loads. A value of

470 KW for RC2 with 470 pF for CC1 and 100 W for RC1 is a recommend-

ed starting point for the RCD design. Verify that the peak collector

voltage is less than (V

conditions including start-up.

× derating factor) under all line and load

CBO

The clamp diode choice is governed by what weight is given to

various performance factors and cost. Customers usually favor

lowest cost at the power level and application type covered by

LinkSwitch-4 devices. This indicates the use of a low-cost 1N4007

slow recovery type diode. Note from Figure 25, that a slow recovery

diode has a lower frequency ring, and faster settling time, this can be

useful in reducing EMI.

The choice of snubber components affects no-load power, no-load

frequency, no-load output voltage stability, peak collector voltage,

efciency and EMI.

Reducing CC1 will reduce energy lost in the clamp, reduce the no-load

switching frequency and hence reduce the no-load power. The

compromise is that the peak collector voltage is increased and EMI

emissions may increase, but as long they are within the set limits it is

an option to control no-load power.

18

Rev. B 10/17

www.power.com

Page 19

Application NoteAN-69

Supplementary Base Drive

Resistor R

drive in higher power applications (7.5 W – 18 W) without increasing

is used on SO-8 packaged devices to provide extra base

SBD

package dissipation.

It should have a value of between 220 W and 390 W for standard

designs, or 100 W to 150 W for applications using the EasyStart

feature. Refer to ‘Step 15 – First Time Start-up and Troubleshooting’

to check that correct value has been selected.

Output Diode Snubber

It is advisable to allow for a output diode snubber in the application

design. It may not be required, but will aid EMC development if there

are places allocated on the PCB for these components. The snubber

consists of a resistor in series with a capacitor and are then placed in

parallel with the output diode. The snubber dissipates energy during

operation and reduces efciency, so it is advisable to only provide as

much snubbing as is required to pass EMC requirements. A 10 W

resistor in series with a 1 nF ceramic capacitor is a good starting

point. As a guide, the capacitor voltage rating should be equal or

greater than the output diode voltage rating.

Current Sense Resistor R

The value of RCS [E74] may need some adjustment to obtain the

CS

desired maximum output current i.e. the position of the constant

current region of the VI curve. This is due to the effects of the bias

winding, primary clamp and core losses drawing energy that would

otherwise go to the secondary. There is a nominal correction factor

in the calculations, but the amount of correction required varies with

power level and transformer design. Once the value has been

adjusted to give the desired current level, it will not change much

across production of the particular design. Some effort will have to

be made in centralizing the design so it remains within specication

across production, due to component tolerances, if required.

V

Setting Resistor R

CS(MIN)

LNK4xx2S parts do not need this resistor to set V

resistor should be included to enhance ESD immunity.

Voltage Feedback Resistor R

If R

is to be SMT then it should be at least 0805 size, preferably

FB1

two in series. During ESD events, a large voltage can be present

CS2

FB1

, but a 1 kW

CS(MIN)

across this resistor and it can be damaged.

Step 14 - Transformer Topology

The starting point for transformer design is not always the same

because it depends on constraints such as operating frequency and

transformer size. The transformer interacts with nearly all other

design considerations so it is impossible to design the transformer in

isolation. These interactions need constant consideration and review,

and the transformer design needs to be iterated to accommodate an

acceptable compromise throughout the design of the power supply.

For best efciency, use a core with as high a cross section area as

affordable. Also ensure that the winding window width is enough to

accommodate the secondary winding. The aim is a single layer of

secondary that fully lls the winding width; a 12 V design will there-

fore need a wider width than a 5 V design at the same power level.

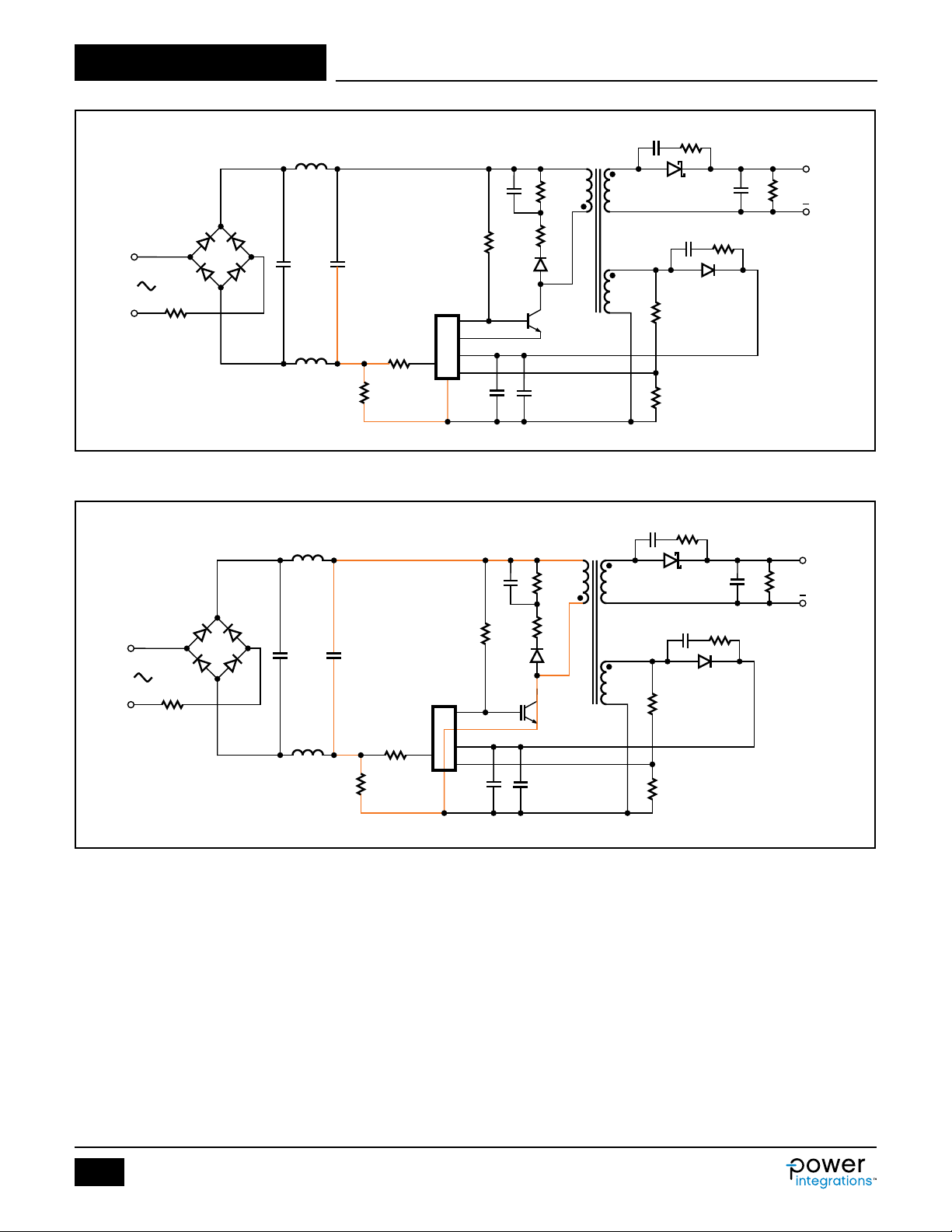

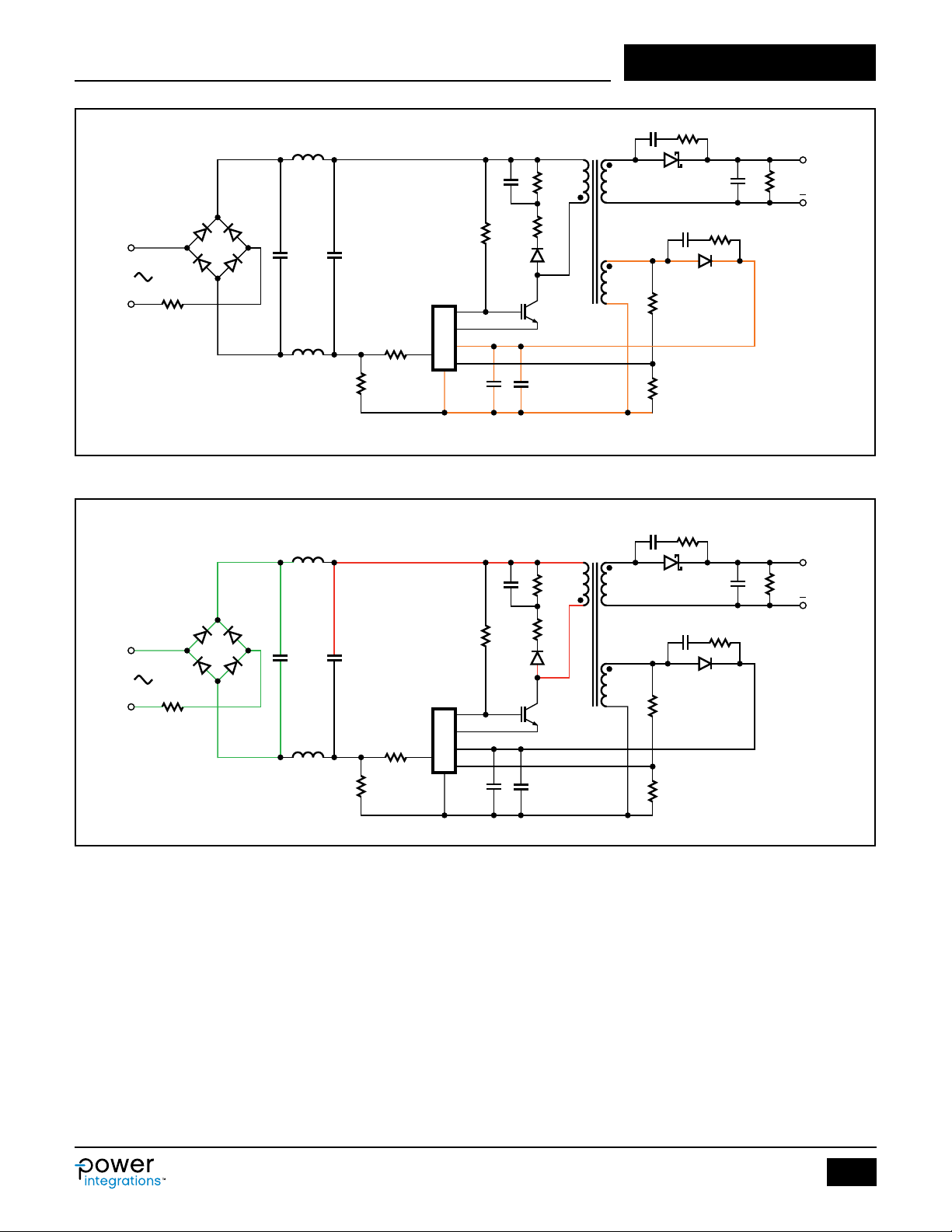

Common LinkSwitch-4 Transformer Topologies

A simple 3 winding transformer structure has been developed that is

suitable for all LinkSwitch-4 designs up to 18 W. It may be necessary

to use a more complicated sandwiched secondary type structure with

5 windings, including a foil screen, at 7.5 W or greater to minimize