Page 1

PROGRAMMABLE SLIC OVERVOLTAGE PROTECTION

negative protection voltage is controlled by the voltage,

● Programmable Voltage Triggered SCR

with high Holding Current

TISP61CAP3

PROGRAMMABLE

OVERVOLTAGE PROTECTOR

SEPTEMBER 1994 - REVISED SEPTEMBER 1997Copyright © 1997, Power Innovations Limited, UK

P PACKAGE

(TOP VIEW)

● Transistor Buffered Inputs for Low V

current

● Rated for International Surge Wave Shapes

I

WAVE SHAPE STANDARD

10/700 µs CCITT IX K17 38

10/1000 µs REA PE-60 30

TSP

A

description

The TISP61CAP3 is a programmable

overvoltage protector designed to protect SLIC

applications against lightning and transients

induced by ac power lines. Normally the V

(Gate) terminal will be connected to the negative

supply rail of the SLIC

When a negative transient exceeds the negative

supply rail voltage of the SLIC it will cause the

thyristor to crowbar, shunting the surge to

ground. The high crowbar holding current

prevents dc latchup as the transient subsides.

Positive transients are clipped by diode action.

GG

GG

1

K1

(Tip)

2

G

(Gate)

3

NC

4 5

K2

(Ring)

NC - No internal connection

Terminal typical application names shown in

parenthesis

8

7

A

6

A

K2

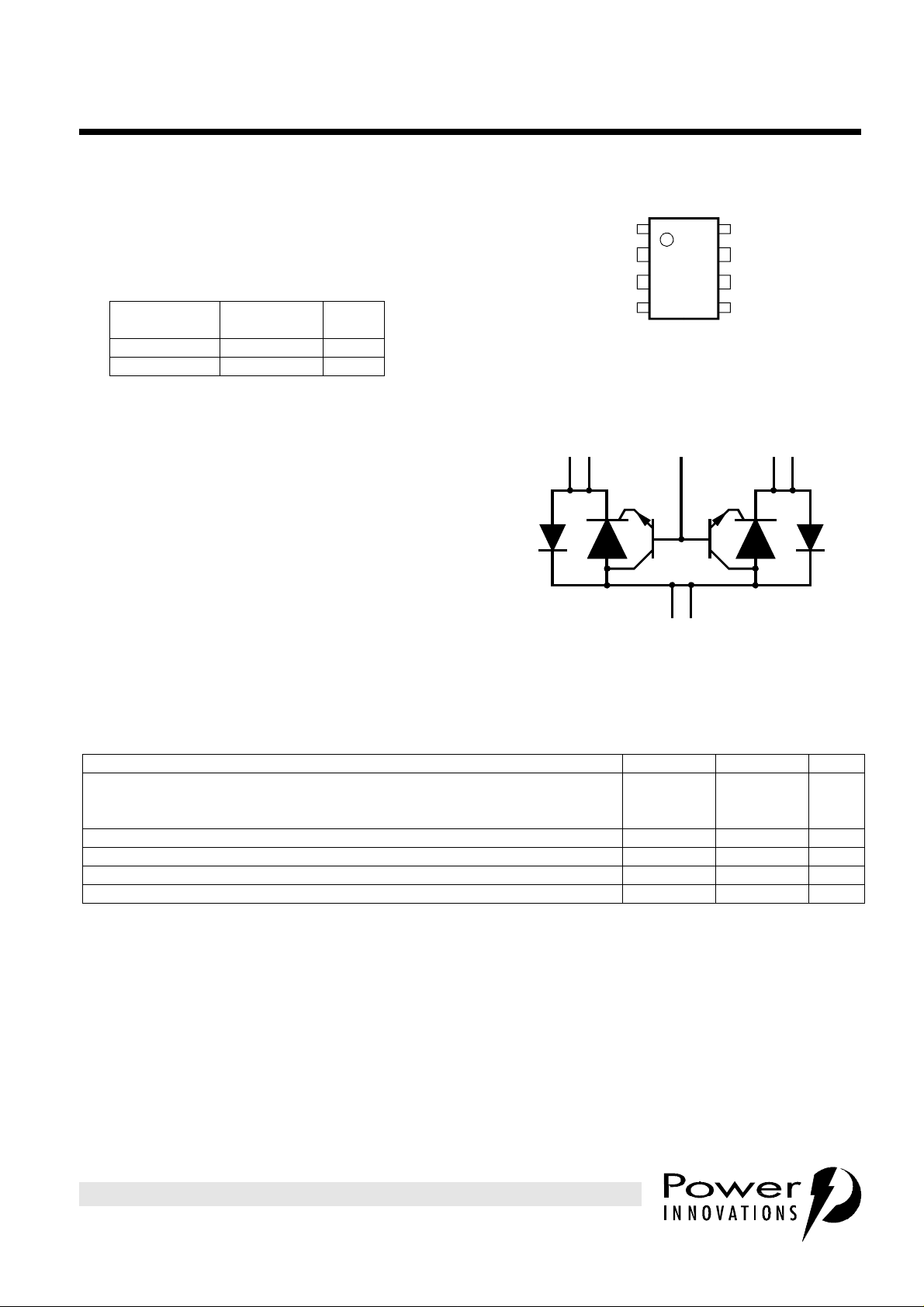

device symbol

K1 G K2

A

Terminals K1, K2 and A correspond to the alternative

line designators of T, R and G or A, B and C. The

K1

(Tip)

(Ground)

(Ground)

(Ring)

MD6XAV

SD6XAE

V

applied to the G terminal.

GG,

absolute maximum ratings

RATING SYMBOL VALUE UNIT

Non-repetitive peak on-state pulse current(see Notes 1, 2 and 3)

10/1000 µs(REA PE-60, open-circuit voltage wave shape 10/1000 µs) 30

Non-repetitive peak on-state current, 50 Hz, 1 s(see Notes 1 and 2) I

Maximum gate current I

Repetitive peak off-state voltage V

Maximum gate supply voltage V

NOTES: 1. Above 70°C, derate linearly to zero at 150°C case temperature

2. This value applies when the initial case temperature is at (or below) 70°C. The surge may be repeated after the device has

returned to thermal equilibrium.

3. Most PTT’s quote an unloaded voltage waveform. In operation the TISP essentially shorts the generator output. The resulting

loaded current waveform is specified.

I

TSP

TSM

GM

DRM

GG(max)

A5/310 µs(CCITT IX K17, open-circuit voltage wave shape 1.5 kV, 10/700 µs) 38

2.5 A rms

2 A

- 80 V

- 80 V

PRODUCT INFORMATION

Information is current as of publication date. Products conform to specifications in accordance

with the terms of Power Innovations standard warranty. Production processing does not

necessarily include testing of all parameters.

1

Page 2

TISP61CAP3

PROGRAMMABLE

OVERVOLTAGE PROTECTOR

SEPTEMBER 1994 - REVISED SEPTEMBER 1997

electrical characteristics, TJ = 25°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Forward voltage IF = 5 A 3 V

V

F

V

FR

Forward recovery

voltage

dv/dt = 300 V/

Gate cathode voltage

V

GK(BO)

V

GK(BO)

I

GAO

I

at breakover

- VGG)

(V

(BO)

Impulse gate cathode

voltage at breakover

- VGG)

(V

(BO)

On-state voltage IT = -4 A -72 < VGG < -10 V -3 V

V

T

Off-state current VD = -80 V VGG = -80 V -10 µA

I

D

Switching current dv/dt = -250 V/ms -72 < VGG < -10 V R

I

S

Holding current di/dt = 30 mA/µs -72 < VGG < -10 V -0.15 A

I

H

Gate reverse current

with cathode open

Gate reverse current

GAT

in the on-state

dv/dt = -250 V/ms -72 < V

dv/dt = -300 V/

di/dt < -10 A/

= -72 V -10 µA

V

GG

= -72 V IT = -0.5 A -1 mA

V

GG

Gate reverse current

I

GAF

in the forward

V

GG

= -72 V

conducting state

Peak gate switching

I

GSM

current

Off-state capacitance -72 < VGG < -10 V

C

off

Critical rate of rise of

dv/dt

off-state voltage

dv/dt = -250 V/ms -72 < V

= -72 V, linear ramp, Maximum ramp value > 0.85 V

V

GG

NOTE 4: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The third terminal is

connected to the guard terminal of the bridge.

µs di/dt < 10 A/µs R

< -10 V R

GG

µs

µs

-72 < V

I

T

I

T

V

D

V

D

= 1 A

= 5 A

= -3 V

= -48 V

< -10 V R

GG

< -10 V R

GG

= 30 Ω 7 V

SOURCE

= 300 Ω -3 V

SOURCE

= 30 Ω -15 V

SOURCE

= 300 Ω -0.15 A

SOURCE

= 300 Ω 5 mA

SOURCE

(see Note 4)

GG

-10

-30

150

80

mA

pF

-50 V/µs

PRODUCT INFORMATION

2

Page 3

V

GK(BO)

OVERVOLTAGE PROTECTOR

SEPTEMBER 1994 - REVISED SEPTEMBER 1997

PARAMETER MEASUREMENT INFORMATION

+i

I

TSP

I

TSM

I

F

V

F

TISP61CAP3

PROGRAMMABLE

Quadrant I

Forward

Conduction

Characteristic

-v

I

(BO)

V

Quadrant III

Switching

Characteristic

(BO)

V

GG

I

S

V

S

V

D

I

D

I

H

V

T

I

T

I

TSM

I

TSP

-i

+v

PM6XAA

Figure 1. VOLTAGE-CURRENT CHARACTERISTIC

PRODUCT INFORMATION

3

Page 4

TISP61CAP3

NOTE A: Each pin centerline is located within 0,25 (0.010) of its true longitudinal position

PROGRAMMABLE

OVERVOLTAGE PROTECTOR

SEPTEMBER 1994 - REVISED SEPTEMBER 1997

MECHANICAL DATA

P008

plastic dual-in-line package

This dual-in-line package consists of a circuit mounted on a lead frame and encapsulated within a plastic

compound. The compound will withstand soldering temperature with no deformation, and circuit performance

characteristics will remain stable when operated in high humidity conditions The package is intended for

insertion in mounting-hole rows on 7,62 (0.300) centers. Once the leads are compressed and inserted,

sufficient tension is provided to secure the package in the board during soldering. Leads require no

additional cleaning or processing when used in soldered assembly.

P008

Index

Dot

10,2 (0.400) MAX

8

1 2 3 4

7 6 5

1,78 (0.070) MAX

4 Places

Designation per JEDEC Std 30:

C

L

PDIP-T8

7,87 (0.310)

7,37 (0.290)

T.P.

6,60 (0.260)

6,10 (0.240)

C

L

0,51 (0.020)

MIN

2,54 (0.100) T.P.

6 Places

(see Note A)

ALL LINEAR DIMENSIONS ARE IN MILLIMETERS AND PARENTHETICALLY IN INCHES

0,533 (0.021)

0,381 (0.015)

8 Places

PRODUCT INFORMATION

4

5,08 (0.200)

MAX

3,17 (0.125)

MIN

Seating

Plane

105°

90°

8 Places

0,36 (0.014)

0,20 (0.008)

8 Places

MDXXABA

Page 5

TISP61CAP3

PROGRAMMABLE

OVERVOLTAGE PROTECTOR

SEPTEMBER 1994 - REVISED SEPTEMBER 1997

IMPORTANT NOTICE

Power Innovations Limited (PI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to verify, before placing orders, that the

information being relied on is current.

PI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with PI's standard warranty. Testing and other quality control techniques are utilized to the extent PI

deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except as mandated by government requirements.

PI accepts no liability for applications assistance, customer product design, software performance, or infringement

of patents or services described herein. Nor is any license, either express or implied, granted under any patent

right, copyright, design right, or other intellectual property right of PI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

PI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE

SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS.

Copyright © 1997, Power Innovations Limited

PRODUCT INFORMATION

5

Loading...

Loading...