Power Innovations TISP61089AP, TISP61089ADR, TISP61089AD Datasheet

PROGRAMMABLE SLIC OVER VOLTAGE PROTECTION FOR LSSGR ‘1089

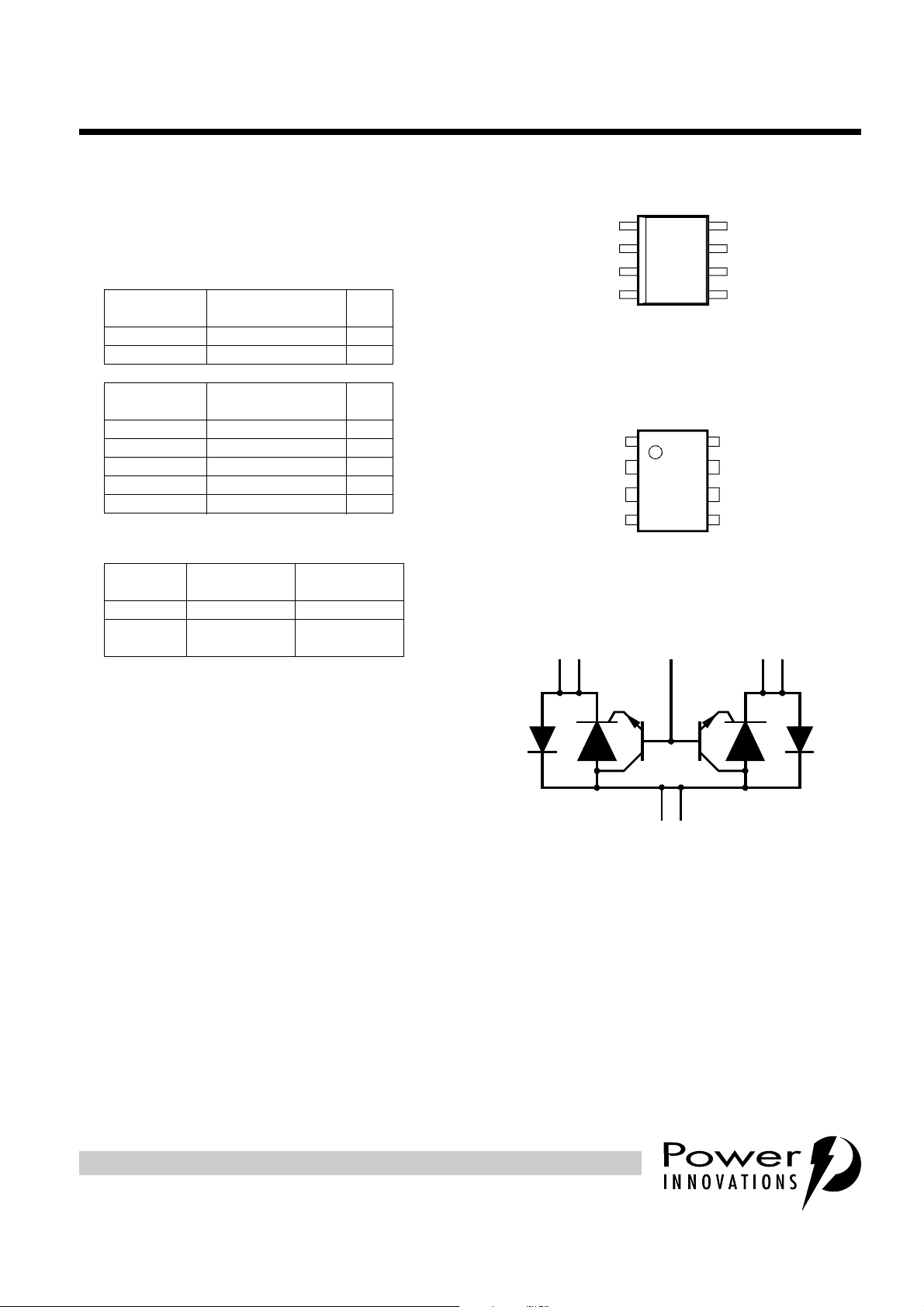

device symbol

Terminals K1, K2 and A correspond to the alternative

line designators of T, R and G or A, B and C. The

negative protection voltage is controlled by the voltage,

V

GG,

applied to the G terminal.

SD6XAE

A

K1 G K2

●

Dual Voltage-Programmable Protectors

- Wide 0 to -110 V Programming Range

- Low 5 mA max. Gate Triggering Current

- High 150 mA min. Holding Current

●

Rated for LSSGR ‘1089 Conditions

WAVE SHAPE

2/10 µs 4.5.8 Second-Level 1 120

10/1000 µs 4.5.7 First-Level 3 30

‘1089 TEST CLAUSE

AND TEST #

TISP61089A

DUAL FORWARD-CONDUCTING P-GATE THYRISTORS

PROGRAMMABLE OVERVOLTAGE PROTECTORS

D PACKAGE

(TOP VIEW)

I

TSP

(Tip)

(Gate)

K1

G

NC

K2

(Ring)

A

NC - No internal connection

Terminal typical application names shown in

1

2

3

45

parenthesis

8

K1

(Tip)

7

A

(Ground)

6

A

(Ground)

K2

(Ring)

JUNE 1999Copyright © 1999, Power Innovations Limited, UK

MD6XAN

60 Hz POWER

FAULT TIME

100 ms 4.5.13 Second-Level 2 10

1 s 4.5.13 Second-Level 2 4.4

5 s 4.5.13 Second-Level 2 2.1

300 s 4.5.13 Second-Level 1 0.84

900 s 4.5.13 Second-Level 1 0.83

●

2/10 Protection Voltage Specified

ELEMENT

Diode 6 8

Crowbar

= -48 V

V

GG

●

Also Rated for ITU-T 10/700 impulses

●

Surface Mount and Through-Hole Options

‘1089 TEST CLAUSE

AND TEST #

FIRST-LEVEL

V @ 56 A

-57 -60

I

TSM

A

SECOND-LEVEL

V @ 100 A

P PACKAGE

(TOP VIEW)

(Tip)

(Gate)

(Ring)

Terminal typical application names shown in

1

K1

2

G

3

NC

45

K2

NC - No internal connection

parenthesis

8

7

6

K1

A

A

K2

(Tip)

(Ground)

(Ground)

(Ring)

MD6XAV

- TISP61089AP for Plastic DIP

- TISP61089AD for Small-Outline

- TISP61089ADR for Small-Outline Taped

and Reeled

description

The TISP61089A is a dual forward-conducting

buffered p-gate overvoltage protector. It is

designed to protect monolithic SLICs (Subscriber

Line Interface Circuits) against overvoltages on

the telephone line caused by lightning, a.c.

power contact and induction. The TISP61089A lim its voltages that exceed the SLIC supply rail voltage. The

TISP61089A parameters are specified to allow equipment compliance with Bellcore GR-1089-CORE,

Issue 1.

The SLIC line driver section is typically powered from 0 V (ground) and a negative voltage in the region of

-10 V to -100 V. The protector gate is connected to this negative supply. This references the protection

(clipping) voltage to the negat ive supply voltage. As the p rotecti on voltage will th en track the negati ve supply

voltage the overvoltage stress on the SLIC is minimised.

PRODUCT INFORMATION

Information is current as of publication date. Products conform to specifications in accordance

with the terms of Power Innovations standard warranty. Production processing does not

necessarily include testing of all parameters.

1

TISP61089A

DUAL FORWARD-CONDUCTING P-GATE THYRISTORS

PROGRAMMABLE OVERVOLTAGE PROTECTORS

JUNE 1999

Positive over voltages are clipp ed to ground by diode forward conduction. Ne gative overvoltages are initially

clipped close to the SLIC negative supply rail value. If sufficient current is available from the overvoltage, then

the protector will c rowbar in to a l ow voltage on-state cond ition. As the overvoltage sub side s the hi gh hol ding

current of the crowbar prevents d.c. latchup.

The TISP61089A is intended to be used with a ser ies combination of a 25Ω or higher resistance and a

suitable overcurrent protector. Power fault compliance requires the serie s overcurrent element to open- cir cuit

or become high impedance (see Applications Information). For equipment compliant to ITU-T

recommendations K20 or K21 only, the series resistor value is set by the power cross requirements. For K20

and K21, a minimum series resistor value of 10Ω is recommended.

These monolithic prote ction devices are fabricated in ion-implanted planar vertic al power structures for high

reliability and in normal system operation they are virtually transparent. The TISP61089A buffered gate

design reduces the loading on the SLIC supply dur ing overvoltages caused by power cross and induction.

The TISP61089A is available in 8-pin plas tic small-outlin e surface mount package and 8-pi n plastic dual-in line package.

absolute maximum ratings

RATING SYMBOL VALUE UNIT

≤

Repetitive peak off-state voltage, I

Repetitive peak gate-cathode voltage, V

Non-repetitive peak on-state pulse current (see Notes 1 and 2)

10/1000 µs (Bellcore GR-1089-CORE, Issue 1, November 1994, Section 4)

5/320 µs (ITU-T recommendation K20 & K21, open-circuit voltage wave shape 10/700)

1.2/50 µs (Bellcore GR-1089-CORE, Issue 1, November 1994, Section 4, Alternative) 100

2/10 µs (Bellcore GR-1089-CORE, Issue 1, November 1994, Section 4) 120

Non-repetitive peak on-state current, 60 Hz (see Notes 1 and 2)

0.1 s 10

1s

5s

300 s

900 s

Non-repetitive peak gate current, 1/2 µs pulse, cathodes commoned (see Notes 1 and 2) I

Operating free-air temperature range T

Junction temperature T

Storage temperature range T

= 0, -40°C≤T

G

= 0, -40°C≤T

KA

85°C V

J

≤

85°C V

J

DRM

GKRM

I

TSP

I

TSM

GSM

A

J

stg

-120 V

-120 V

30

40

4.4

2.1

0.84

0.83

40 A

-40 to +85 °C

-40 to +150 °C

-40 to +150 °C

A

A

NOTES: 1. Initially the protector must be in thermal equilibrium with -40°C≤T

its initial conditions.

2. The rated current values may be applied either to the Ring to Ground or to the Tip to Ground ter minal pairs. Additionally, both

terminal pairs may have their rated current values applied simultaneously (in this case the Ground terminal current will be twice the

rated current value of an individual terminal pair). Above 85°C, derate linearly to zero at 150°C lead temperature.

recommended operating conditions

C

Gate decoupling capacitor 100 220 nF

G

TISP61089A series resistor for first-level and second-level surge survival

R

S

TISP61089A series resistor for first-level surge survival

PRODUCT INFORMATION

2

≤

85°C. The surge may be repeated after the device returns to

J

MIN TYP MAX UNIT

40

25

Ω

DUAL FORWARD-CONDUCTING P-GATE THYRISTORS

PROGRAMMABLE OVERVOLTAGE PROTECTORS

electrical characterist ics, TJ = 25°C (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I

D

V

V

V

I

H

I

GKS

I

GT

V

Q

C

(BO)

F

FRM

GT

GS

AK

Off-state current VD=V

2/10 µs, I

Breakover voltage

2/10 µs, I

1.2/50 µs, I

1.2/50 µs, I

, IG=0

DRM

=-56A, RS=45

T

= -100 A, RS=50

T

= -53 A, RS=47

T

= -96 A, RS=52

T

Ω,

VGG=-48V, CG= 220 nF

Ω,

VGG=-48V, CG= 220 nF

Ω,

VGG=-48V, CG= 220 nF

Ω,

VGG=-48V, CG= 220 nF

Forward voltage IF= 5 A, tw= 200 µs 3V

Ω,

VGG=-48V, CG= 220 nF

Ω,

VGG=-48V, CG= 220 nF

Ω,

VGG=-48V, CG= 220 nF

Ω,

VGG=-48V, CG= 220 nF

Peak forward recovery

voltage

2/10 µs, I

2/10 µs, I

1.2/50 µs, I

1.2/50 µs, I

=56A, RS=45

F

= 100 A, RS=50

F

=53A, RS=47

F

=96A, RS=52

F

Holding current IT= -1 A, di/dt = 1A/ms, VGG= -48 V -150 mA

Gate reverse current VGG=VGK=V

Gate trigger current IT= 3 A, t

Gate trigger voltage IT= 3 A, t

p(g)

p(g)

GKRM

≥

20 µs, V

≥

20 µs, V

, VKA=0

=-48V 5 mA

GG

=-48V 2.5 V

GG

Gate switching charge 1.2/50 µs, IT=53A, RS=47Ω, VGG= -48 V CG= 220 nF 0.1 µC

Anode-cathode off-

state capacitance

f=1MHz, V

=1V, IG= 0, (see Note 3)

d

T

T

T

T

V

V

TISP61089A

JUNE 1999

= 25°C -5 µA

J

= 85°C -50 µA

J

-57

-60

-60

-64

6

8

8

12

= 25°C -5 µA

J

= 85°C -50 µA

J

= -3 V 100 pF

D

=-48V 50 pF

D

V

V

NOTE 3: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured

device terminals are a.c. connected to the guard terminal of the bridge.

thermal characteristics

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

T

= 25 °C, EIA/JESD51-3

A

R

Junction to free air thermal resistance

θ

JA

PCB, EIA/JESD51-2

environment, P

TOT

= 1.7 W

D Package 120

°C/W

P Package 100

PRODUCT INFORMATION

3

TISP61089A

DUAL FORWARD-CONDUCTING P-GATE THYRISTORS

PROGRAMMABLE OVERVOLTAGE PROTECTORS

JUNE 1999

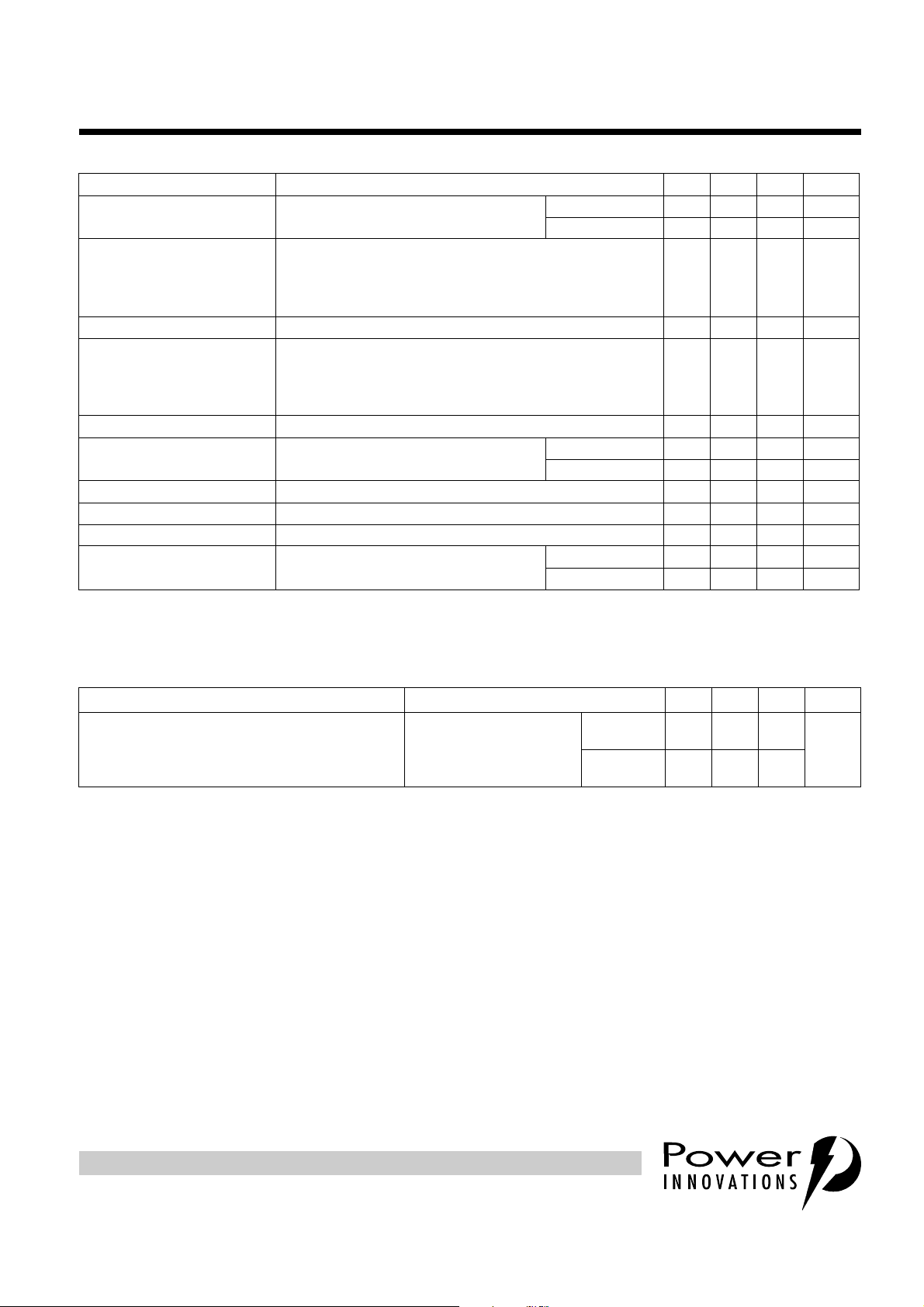

PARAMETER MEASUREMENT INFORMATION

-v

I

(BO)

V

Quadrant III

Switching

Characteristic

V

(BO)

GK(BO)

V

+i

I

(= |I

TSP

|)

FSP

Characteristic

I

(= |I

FSM

GG

I

S

V

S

V

D

|)

TSM

I

F

V

F

I

D

I

H

V

T

I

T

I

TSM

I

TSP

-i

Quadrant I

Forward

Conduction

+v

PM6XAAA

Figure 1. VOLTAGE-CURRENT CHARACTERISTIC

PRODUCT INFORMATION

4

DUAL FORWARD-CONDUCTING P-GATE THYRISTORS

PROGRAMMABLE OVERVOLTAGE PROTECTORS

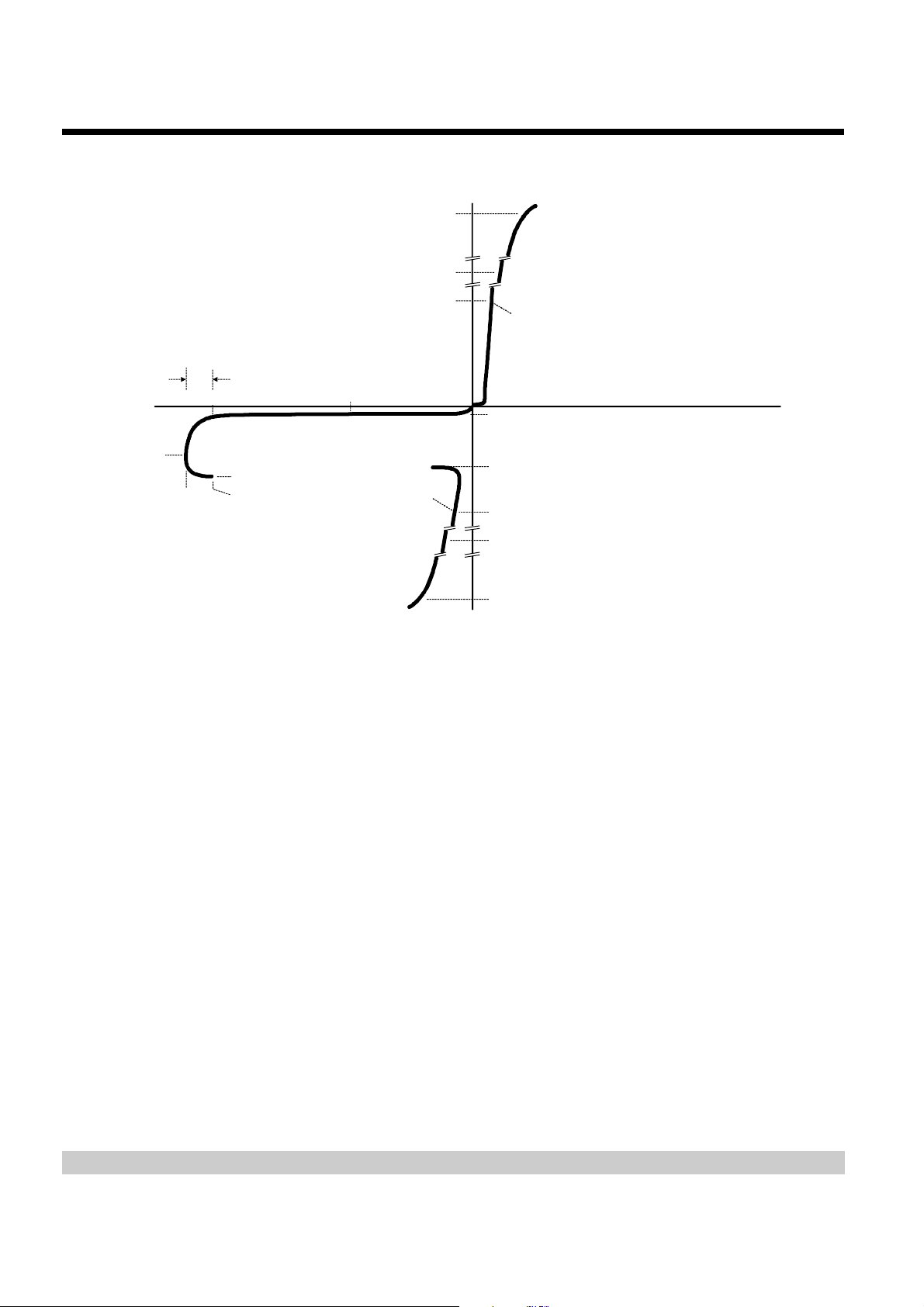

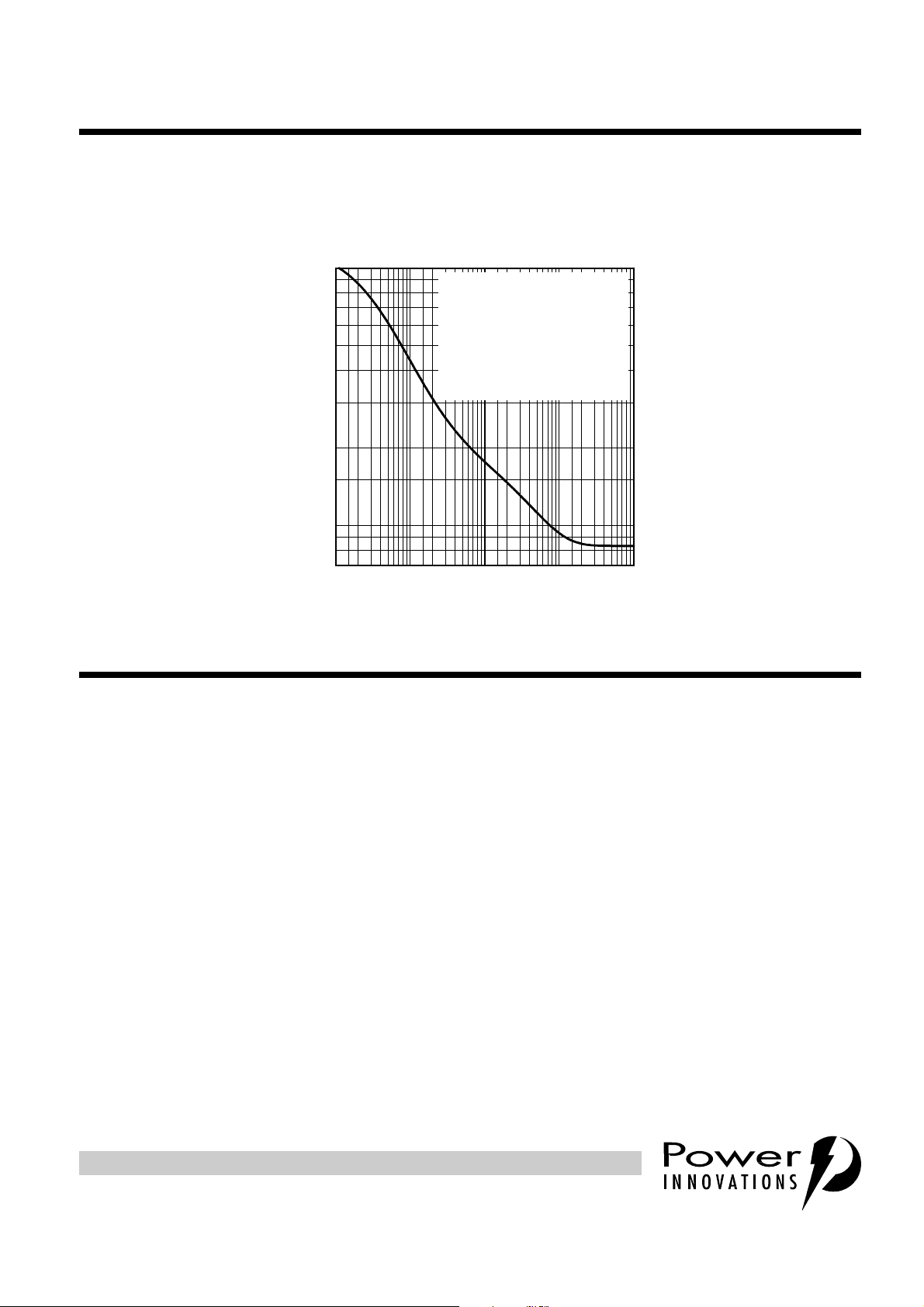

THERMAL INFORMATION

NON-REPETITIVE PEAK ON-STAT E CURRENT

vs

10

1.5

CURRENT DURATION

9

8

7

6

5

4

3

2

V

= 600 Vrms, 50/60 Hz

GEN

= 1.4*V

R

GEN

EIA/JESD51-2 ENVIRONMENT

EIA/JESD51-3 PCB

= 25 °C

T

A

GROUND RETURN = 2x

GEN

/I

TSM(t)

I

TSM(t)

TI6HAC

TISP61089A

JUNE 1999

- Non-Repetitive Peak On-State Current - A

1

0.9

TSM(t)

0.8

I

0.7

0·1 1 10 100 1000

t - Current Duration - s

Figure 2. NON-REPETITIVE PEAK ON-STATE CURRENT AGAINST DURATION

APPLICATIONS INFORMATION

gated protectors

This section covers three topics. Firstly, it is explained why gated protectors ar e n eed ed. S econd, the voltage

limiting action of the protector is described. Third, an example application circuit is described.

purpose of gated protectors

Fixed voltage thyristor overvoltage protectors have been used since the early 1980s to protect monol ithic

SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c.

power contact and induction. As the SLIC was usually powered from a fixed voltage negative supply rail, the

limiting voltage of the protector could als o be a fixed value. The TISP1072F3 is a typical example of a fixed

voltage SLIC protector.

SLICs have become more sophisticated. To minimise power consumption, some designs automatically adjust

the supply voltage, V

supply voltage would be set low, but for long lines, a higher supply voltage would be generated to drive

sufficient line curre nt. The optimum protection for this type of SLIC would be given by a protection voltage

which tracks the SLIC supply voltage. This can be achieved by connecting the protection thyristor ga te to th e

SLIC supply, Figure 3. This gated (programmable) protection arrangement mi nimises the voltage stress on

the SLIC, no matter what value of supply voltage.

, to a value that is just sufficient to drive the requir ed line curre nt. For shor t lines th e

BAT

PRODUCT INFORMATION

5

TISP61089A

DUAL FORWARD-CONDUCTING P-GATE THYRISTORS

PROGRAMMABLE OVERVOLTAGE PROTECTORS

JUNE 1999

TIP

WIRE

ΩΩΩΩ

600

GENERATOR

SOURCE

RESISTANCE

ΩΩΩΩ

600

RING

WIRE

A.C.

GENERATOR

0 - 600 Vrms

50

50

R1

R2

TISP61089A

ΩΩΩΩ

ΩΩΩΩ

Th4

Th5

C1

220 nF

SLIC

SWITCHING MODE

POWER SUPPLY

Tx

I

I

SLIC

G

I

BAT

C2

V

BAT

D1

AI6XAGA

Figure 3. TISP61089A BUFFERED GATE PROTECTOR (SECTION 4.5.12 TESTING CONDITION)

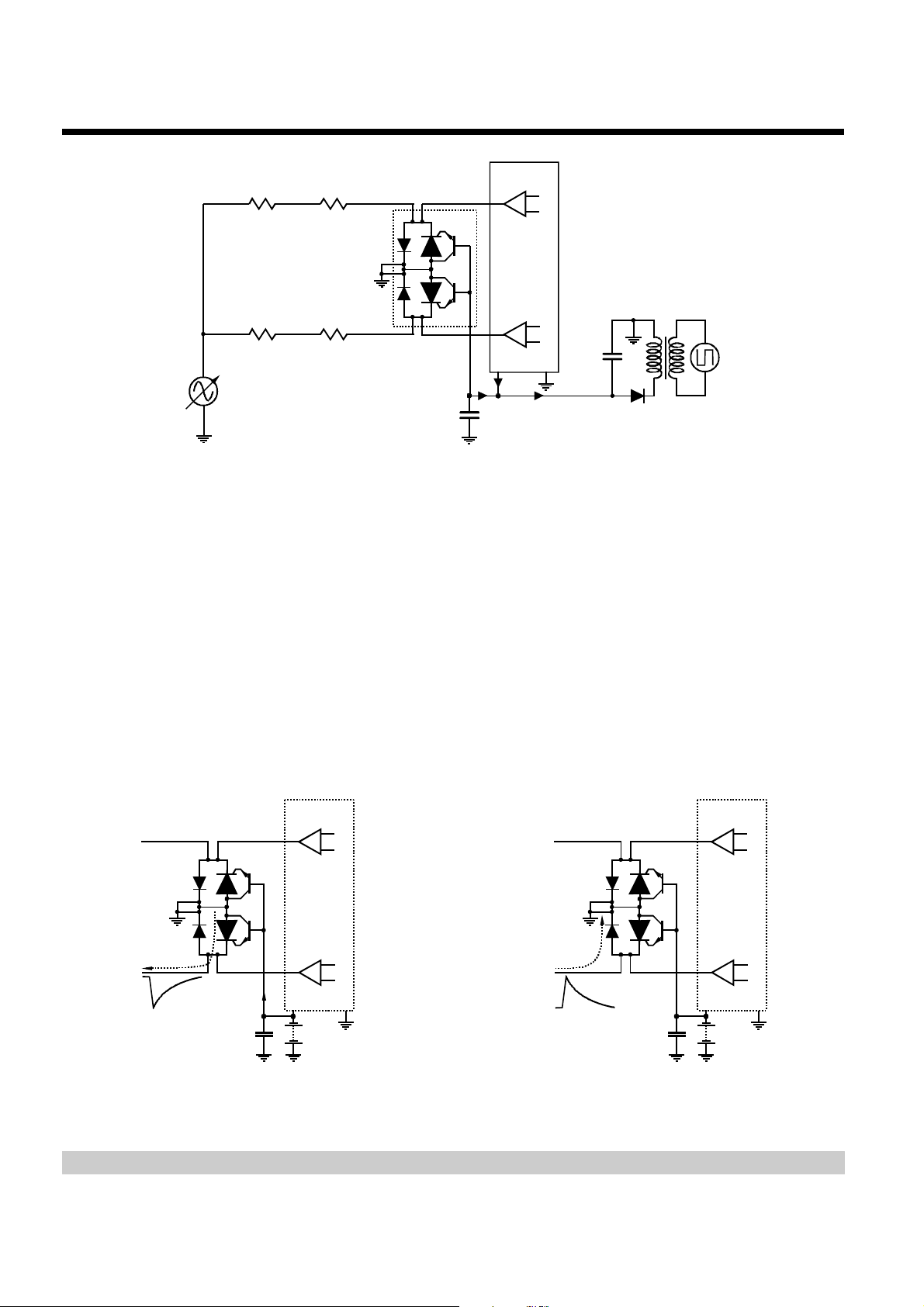

operation of gated protectors

Figures 4. and 5. show how the TISP61089A limit s negati ve and positive overvoltages. Positive overvoltages

(Figure 5) are clipped by the antiparallel di odes in the TISP61089A and the resulti ng current is diverted to

ground. Negative overvoltages (Figure 4.) are initially c lipped close to the SLIC negative supply rail value

(V

). If sufficient current i s available from the overvoltage, then the protector (Th5) wil l crowbar into a low

BAT

voltage on-state conditio n. As the overvoltage subsi des th e high holding curren t of the crowbar prevents d.c.

latchup. The protection voltage will be th e sum of the gate s upply (V

(V

). The protection voltage wi ll be increased if the re i s a l ong c on nec tio n bet ween th e gate d ec oup li ng

GK(BO)

capacitor, C1, and the gate terminal. During the in iti al rise of a fast impulse, the gate cur rent ( I

as the cathode current (I

). Rates of 70 A/µs can cause inductive voltages of 0.7 V in 2.5 cm of printed wiring

K

) and the peak gate-cathode voltage

BAT

) is the same

G

track. To minimise this inductive voltage increase of protection voltage, the length of the capacit or to gate

terminal tracking should be minimised. Inductive voltages in the protector cathode wiring will also increase the

protection voltage. These voltages can be minimised by routing the SLIC connection through the protector as

shown in Figure 3.

I

K

AI6XAHA

SLIC

PROTECTOR

Th5

TISP

61089A

C1

220 nF

SLIC

I

F

I

G

V

BAT

AI6XAIA

SLIC

PROTECTOR

Th5

TISP

61089A

C1

220 nF

SLIC

V

BAT

Figure 4. NEGATIVE OVERVOLTAGE CONDITION Figure 5. POSITIVE OVERVOLTAGE CONDITION

PRODUCT INFORMATION

6

Loading...

Loading...