POWER INT202TFI2, INT202PFI2, INT202PFI1, INT202TFI1 Datasheet

INT202

Low-side Driver IC

Low-side Drive and High-side Control

for Simultaneous Conduction

Product Highlights

5 V CMOS Compatible Control Inputs

• Combines logic inputs for low and high-side drives

• Schmidt-triggered inputs for noise immunity

HV

®

Built-in High-voltage Level Shifters

• Integrated level shifters simplify high-side interface

• Can withstand up to 800 V for direct interface to the

INT201 high-side driver

• Pulsed high-voltage level shifters reduce power

consumption

Gate Drive Output for an External MOSFET

• Provides 300 mA sink/150 mA source current

• Can drive MOSFET gate at up to 15 V

• External MOSFET allows flexibility in design for various

motor sizes

Built-in Protection Features

• UV lockout

Description

The INT202 Low-side driver IC provides gate drive for an

external low-side MOSFET switch and high-side level shifting.

When used in conjunction with the INT201 high-side driver, the

INT202 provides a simple, cost-effective interface between

low-voltage control logic and high-voltage loads. The INT202

is designed to be used with rectified 110 V or 220 V supplies.

Both high side and low side switches can be controlled

independently from ground-referenced 5 V logic inputs on the

low side driver.

INT201

V

DD

HS IN

LS IN

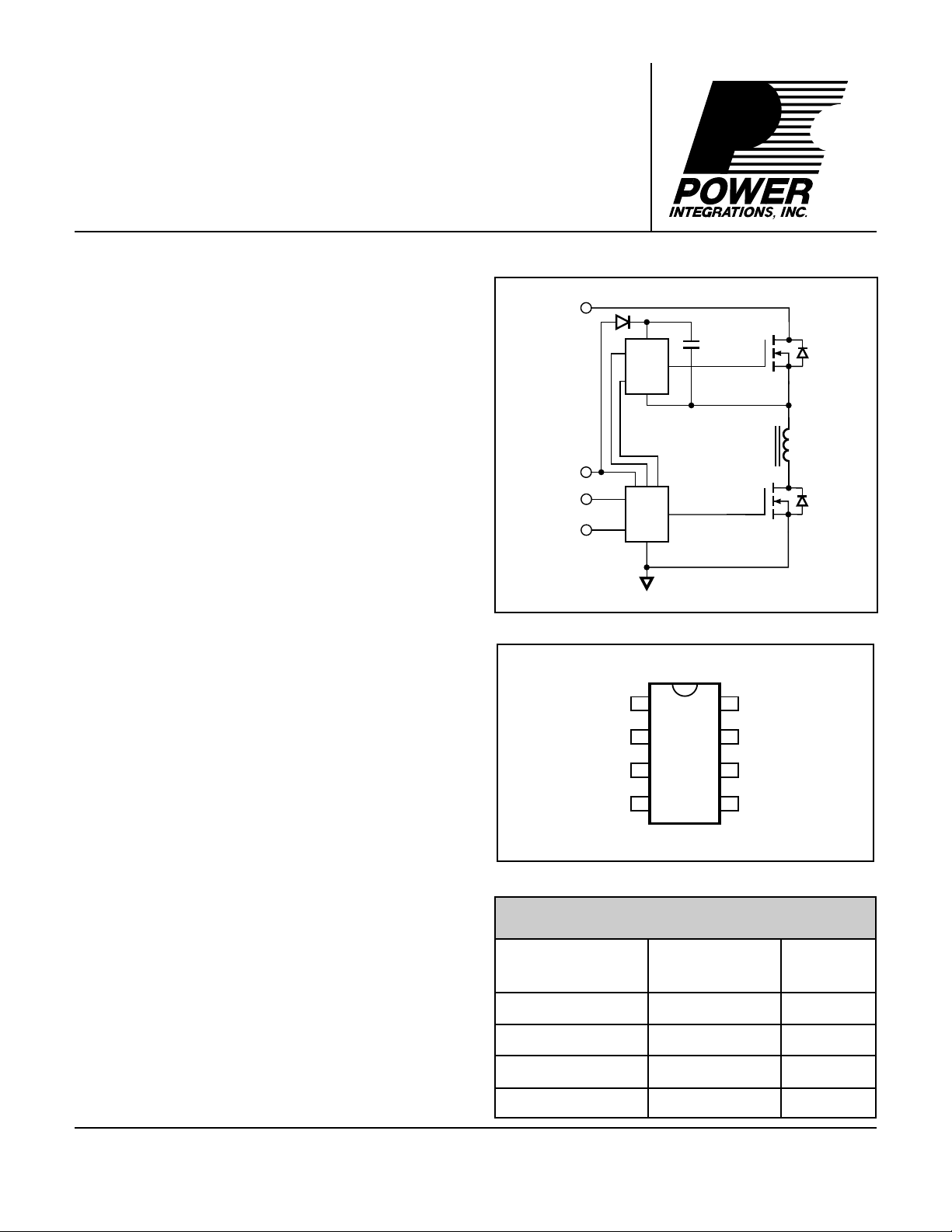

Figure 1. Typical Application

LS OUT

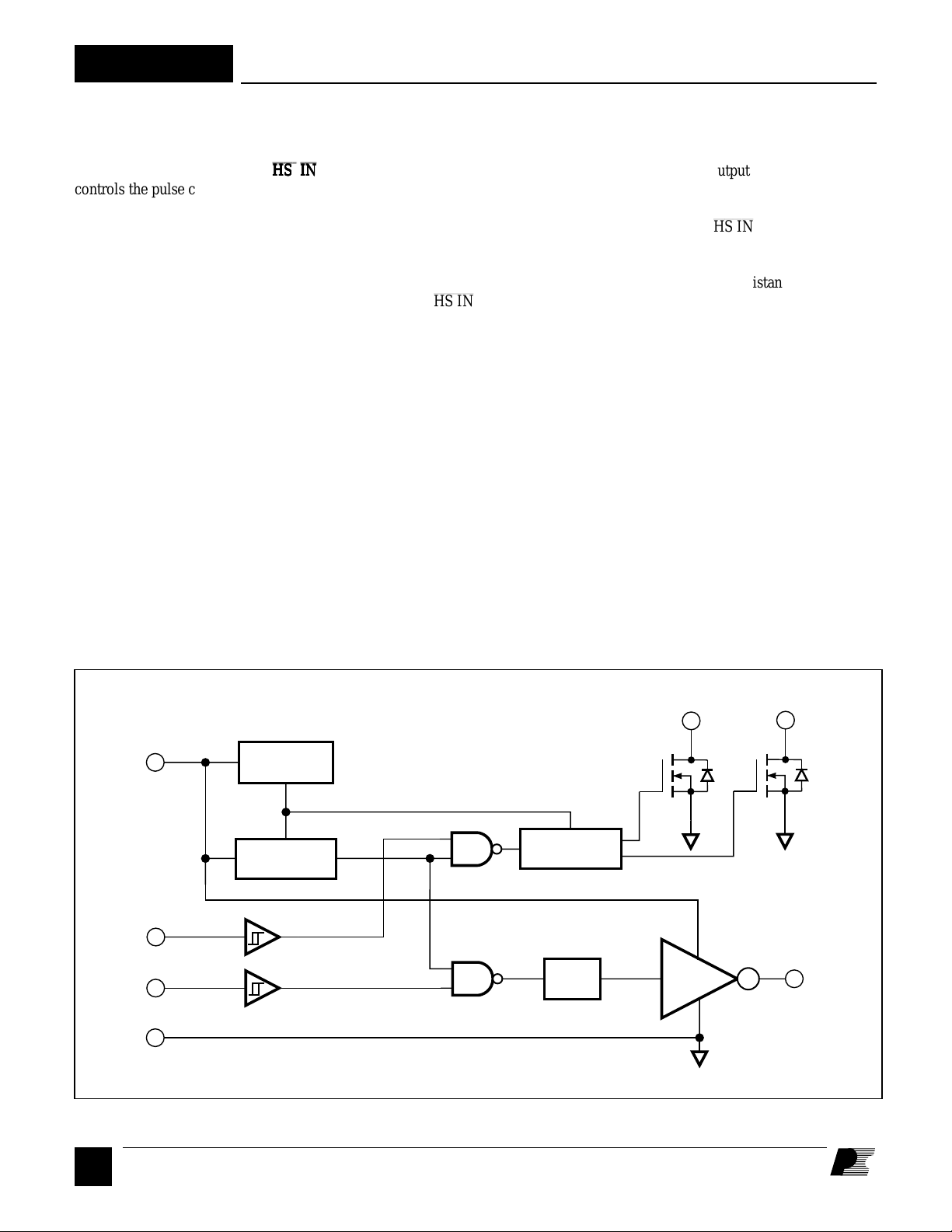

Figure 2. Pin Configuration.

HS IN

LS IN

COM

INT202

1

2

3

4

8

7

6

5

V

DD

N/C

HSD1

HSD2

LOAD

PI-1765-020296

PI–539–091191

Pulsed level shifting saves power and provides enhanced noise

immunity. The circuit is powered from a nominal 15 V supply

to provide adequate gate drive for external N-channel MOSFETs.

Applications include switched reluctance motor drives. The

INT202 can also be used to implement multi-phase

configurations.

The INT202 is available in 8-pin plastic DIP and SOIC packages.

ORDERING INFORMATION

PART PACKAGE ISOLATION

NUMBER OUTLINE VOLTAGE

INT202PFI1 PO8A 600 V

INT202TFI1 TO8A 600 V

INT202PFI2 PO8A 800 V

INT202TFI2 TO8A 800 V

February 1996

INT202

Pin Functional Description

Pin 1:

Active-high logic-level input

HS INHS IN

HS IN

HS INHS IN

controls the pulse circuit which signals

the INT201 high-side driver.

Pin 2:

Active-high logic level input LS IN

controls the low side driver output.

Pin 3:

LS OUT is the driver output which

controls the low-side MOSFET.

Pin 4:

COM connection; analog reference point

for the circuit.

Pin 5:

Level shift output HSD 2 signals the

high-side driver to turn off. One short,

precise pulse is sent on each positive

transition of

HS IN

.

Pin 6:

Level shift output HSD 1 signals the

high-side driver to turn on. Two short,

precise pulses are sent on each negative

transition of

HS IN

.

Pin 7:

N/C for creepage distance.

Pin 8:

V

supplies power to the logic, high-

DD

side interface, and low-side driver.

V

DD

LINEAR

REGULATOR

UV

LOCKOUT

HS IN

LS IN

COM

Figure 3. Functional Block Diagram of the INT202

PULSE

CIRCUIT

DELAY

HSD1 HSD2

LS OUT

PI-1766-020296

F

2

2

2/96

INT202 Functional Description

INT202

5 V Regulator

The 5 V linear regulator circuit provides

the supply voltage for the control logic

and high-voltage level shift circuit. This

allows the logic section to be directly

compatible with 5 V CMOS logic

without the need of an external 5 V

supply.

Undervoltage Lockout

The undervoltage lockout circuit disables

the LS OUT pin and both HSD pins

whenever the VDD power supply falls

below typically 9.0 V, and maintains

this condition until the VDD power supply

rises above typically 9.35 V. This

guarantees that both MOSFETs will

remain off during power-up or fault

conditions.

HSD1/HSD2

The HSD1 and HSD2 outputs are

connected to integrated high-voltage Nchannel MOSFET transistors which

perform the level-shifting function for

communication to the high-side driver.

Controlled current capability allows the

drain voltage to float with the high-side

driver. Two individual channels produce

a true differential communication

channel for accurately controlling the

high-side driver in the presence of fast

moving high-voltage waveforms.

Pulse Circuit

The pulse circuit provides the two highvoltage level shifters with precise timing

signals. Two pulses are sent over HSD1

to signal the high-side driver to turn on.

One pulse is sent over HSD2 to signal

the high-side driver to turn off. The

combination of differential

communication with the precise timing

provides maximum immunity to noise.

Driver

The CMOS drive circuit provides drive

power to the gate of the MOSFET used

on the low side of the half bridge circuit.

The driver consists of a CMOS buffer

capable of driving an external transistor

gate at up to 15 V.

HV+

V

DD

CONTROL

D1

C2

C1

8765

INT201

1234

8765

INT202

1234

R1

R2

Q2

Q1

HV-

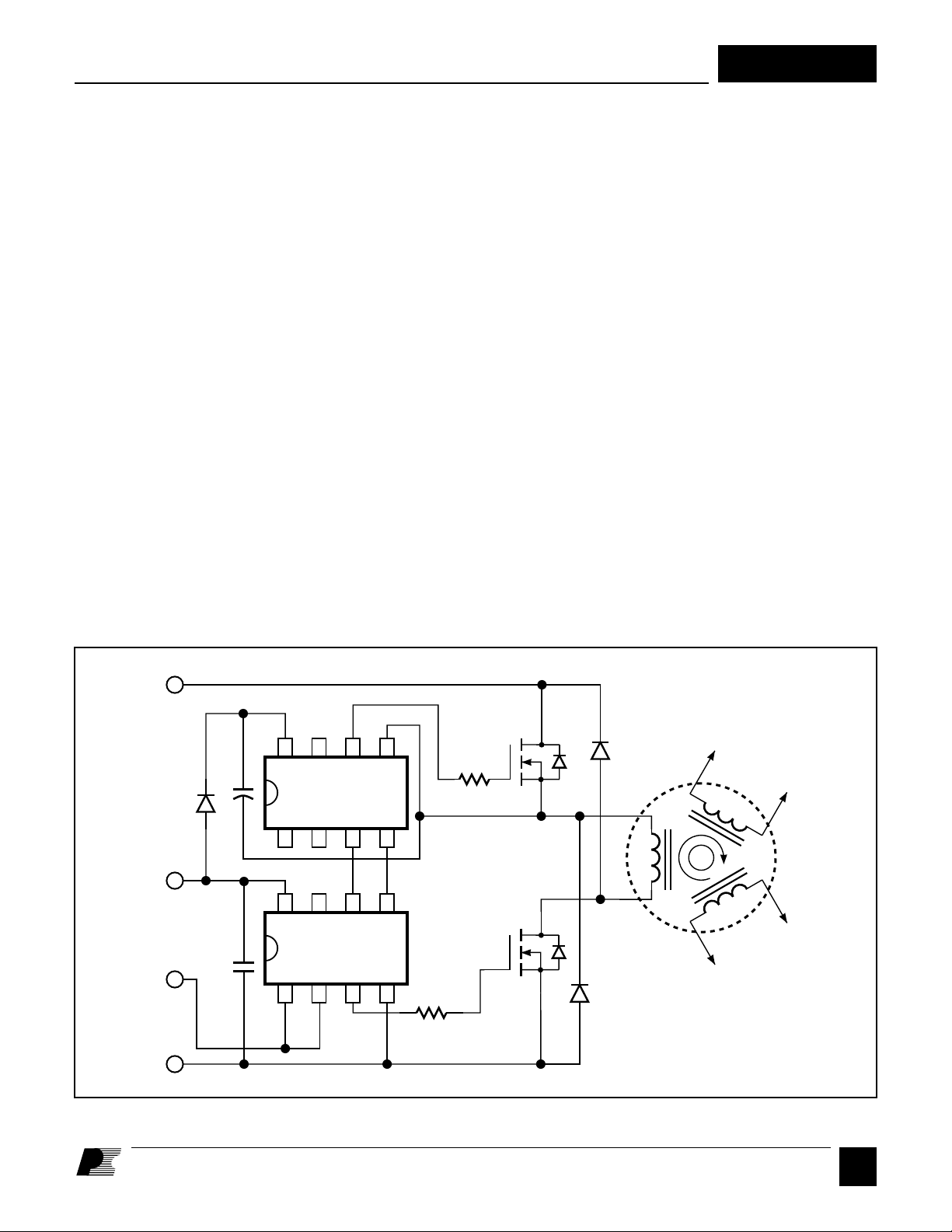

Figure 4. Using the INT202 and INT201 to Drive a Switched Reluctance Motor.

D3

PHASE 2

3-PHASE

SRM

PHASE 1

PHASE 3

D2

PI-1473-042695

2/96

F

3

3

INT202

100

0

0 100 200

Gate Charge (nC)

Switching Frequncy (kHz)

200

300

400

PI-1785-020696

VIN = 200 V

VIN = 300 V

VIN = 400 V

SOIC

General Circuit Operation

The three-phase switched reluctance

motor drive circuit shown in Figure 4

illustrates a typical application for the

INT202/201. The LS IN signal directly

controls MOSFET Q1. The

HS IN

signal

causes the INT202 to command the

INT201 to turn MOSFET Q2 on or off as

required.

Local bypassing for the low-side driver

is provided by C1. Bootstrap bias for the

high-side driver is provided by D1 and

C2. Slew rate and effects of parasitic

oscillations in the load waveforms are

controlled by resistors R1 and R2.

The inputs are designed to be compatible

with 5 V CMOS logic levels and should

not be connected to VDD. Normal CMOS

power supply sequencing should be

observed. The order of signal application

should be VDD, logic signals, and then

HV+. V

should be supplied from a

DD

low impedance voltage source.

The length of time that the high-side can

remain on is limited by the size of the

bootstrap capacitor. Applications with

extremely long high-side on times

require special techniques discussed in

AN-10.

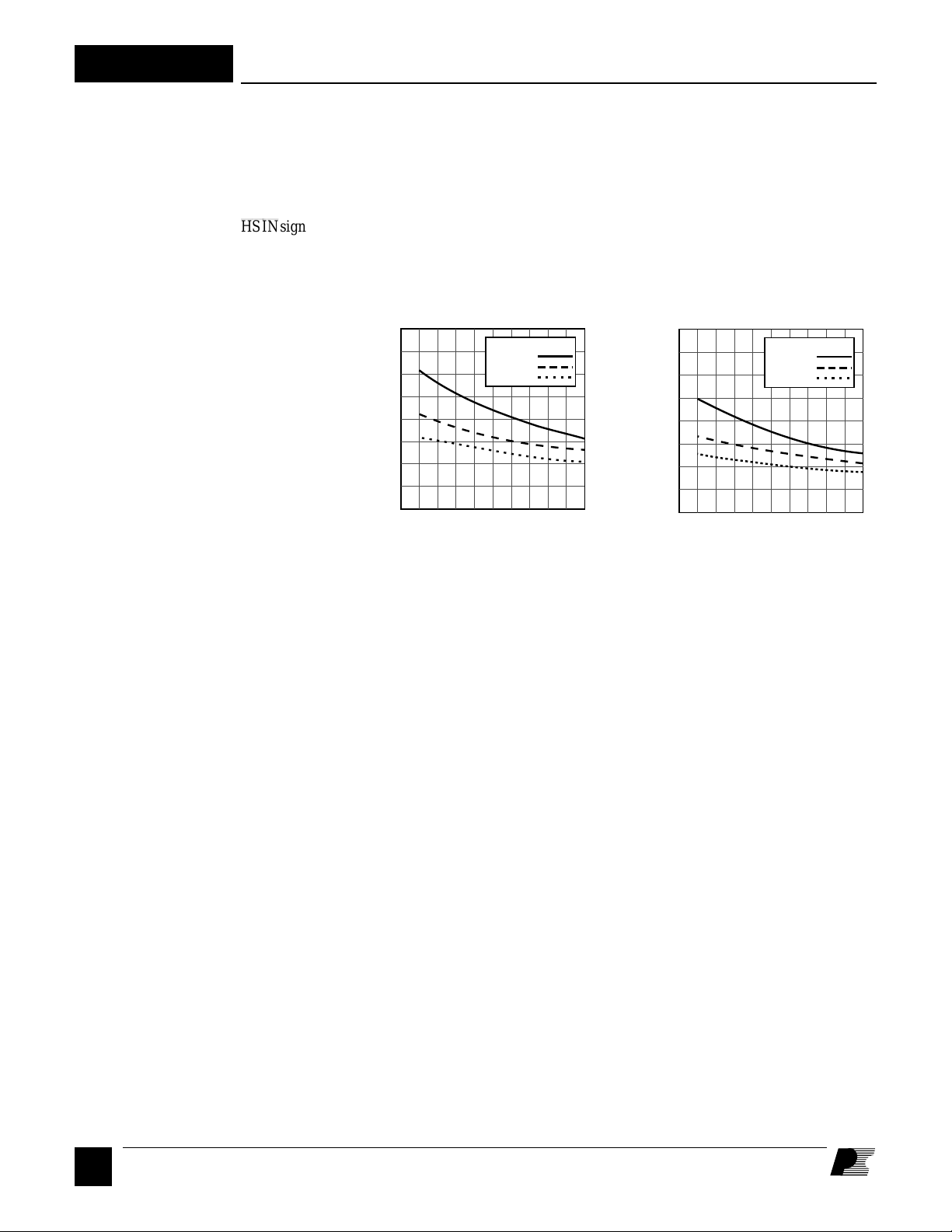

voltage switching, gate charge, and bias

power. Figure 5 indicates the maximum

switching frequency as a function of

input voltage and gate charge. For higher

ambient temperatures, the switching

frequency should be derated linearly.

Maximum frequency of operation is

limited by power dissipation due to high-

400

PDIP

VIN = 200 V

300

200

100

Switching Frequncy (kHz)

0

0 100 200

VIN = 300 V

VIN = 400 V

Gate Charge (nC)

Figure 5. Switching Frequency versus Gate Charge for a) PDIP and b) SOIC.

PI-1782-020696

4

4

F

2/96

Loading...

Loading...