POSEICO AT303S08 Datasheet

Tj

From 75% VDRM up to 1200 A, gate 10V 5ohm

-30 /

standard specification

ANSALDO

Ansaldo Trasporti s.p.a.

Unita' Semiconduttori

PHASE CONTROL THYRISTOR AT303

Repetitive voltage up to 800 V

Mean on-state current 1100 A

Surge current 12 kA

FINAL SPECIFICATION

feb 97 - ISSUE : 02

Via N. Lorenzi 8 - I 16152 GENOVA - ITALY

Tel. int. +39/(0)10 6556549 - (0)10 6556488

Fax Int. +39/(0)10 6442510

Tx 270318 ANSUSE I -

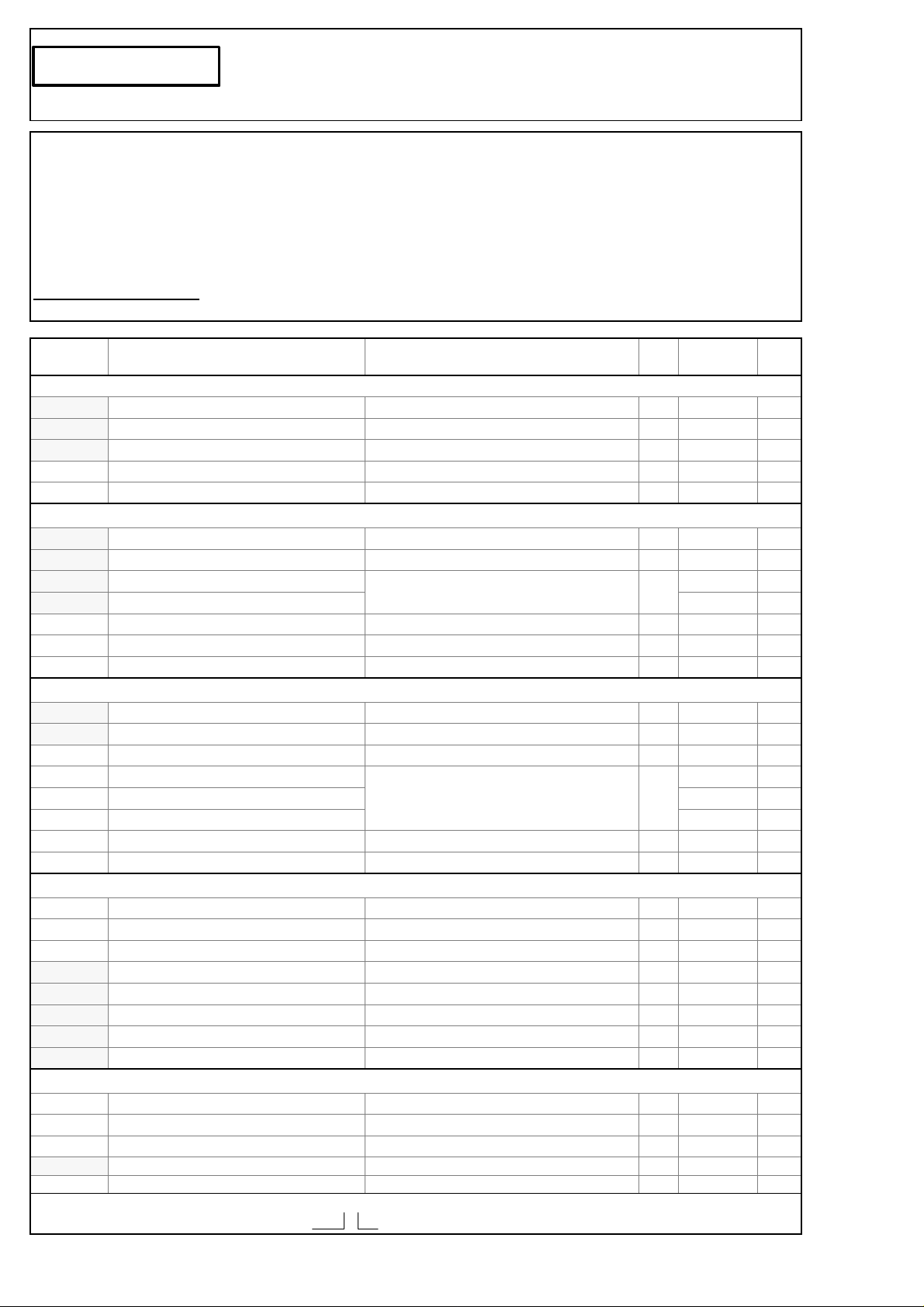

Symbol Characteristic Conditions

[°C]

Value Unit

BLOCKING

V RRM Repetitive peak reverse voltage 150 800 V

V RSM Non-repetitive peak reverse voltage 150 900 V

V DRM Repetitive peak off-state voltage 150 800 V

I RRM Repetitive peak reverse current V=VRRM 150 50 mA

I DRM Repetitive peak off-state current V=VDRM 150 50 mA

CONDUCTING

I T (AV) Mean on-state current 180° sin, 50 Hz, Th=55°C, double side cooled 1100 A

I T (AV) Mean on-state current 180° sin, 50 Hz, Tc=85°C, double side cooled 1085 A

I TSM Surge on-state current sine wave, 10 ms 150 12 kA

I² t I² t without reverse voltage 720 x1E3 A²s

V T On-state voltage On-state current = 1900 A 25 1.45 V

V T(TO) Threshold voltage 150 0.8 V

r T On-state slope resistance 150 0.340 mohm

SWITCHING

di/dt Critical rate of rise of on-state current, min.

dv/dt Critical rate of rise of off-state voltage, min. Linear ramp up to 75% of VDRM 150 500 V/µs

td Gate controlled delay time, typical VD=200V, gate source 20V, 10 ohm , tr=.5 µs 25 1.5 µs

tq Circuit commutated turn-off time, typical dV/dt = 20 V/µs linear up to 80% VDRM µs

Q rr Reverse recovery charge di/dt=-60 A/µs, I= 1000 A 150 µC

I rr Peak reverse recovery current VR= 50 V A

I H Holding current, typical VD=5V, gate open circuit 25 300 mA

I L Latching current, typical VD=12V, tp=30µs 25 mA

150 200 A/µs

GATE

V GT Gate trigger voltage VD=5V 25 3.5 V

I GT Gate trigger current VD=5V 25 200 mA

V GD Non-trigger gate voltage, min. VD=VDRM 150 0.25 V

V FGM Peak gate voltage (forward) 30 V

I FGM Peak gate current 10 A

V RGM Peak gate voltage (reverse) 5 V

P GM Peak gate power dissipation Pulse width 100 µs 150 W

P G Average gate power dissipation 2 W

MOUNTING

R th(j-h) Thermal impedance, DC Junction to heatsink, double side cooled 50 °C/kW

R th(c-h) Thermal impedance Case to heatsink, double side cooled 15 °C/kW

T j Operating junction temperature

F Mounting force 8.0 / 9.0 kN

Mass 85 g

ORDERING INFORMATION : AT303 S 08

VDRM&VRRM/100

150 °C

AT303 PHASE CONTROL THYRISTOR

ANSALDO

FINAL SPECIFICATION feb 97 - ISSUE : 02

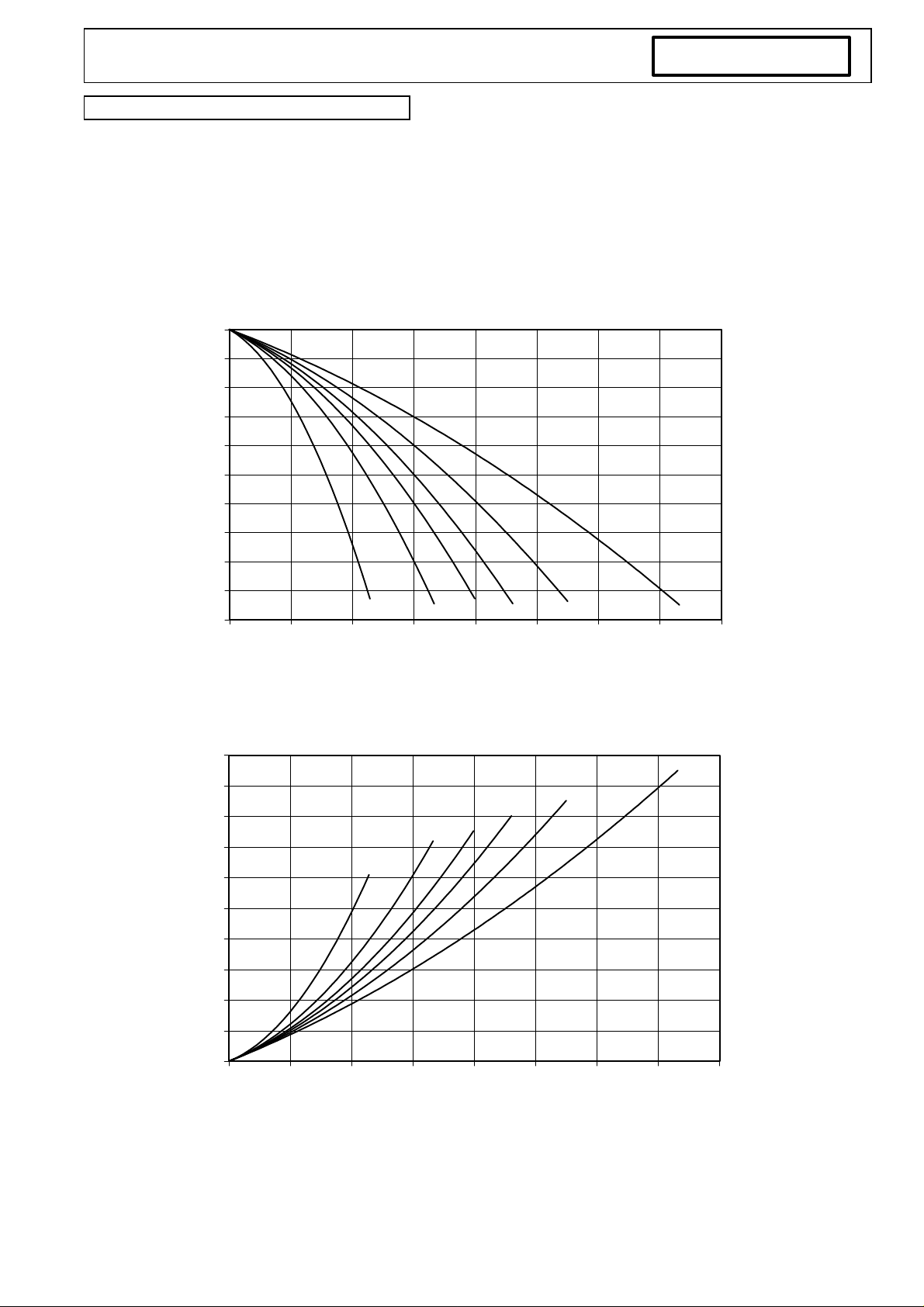

DISSIPATION CHARACTERISTICS

SQUARE WAVE

Th [°C]

150

140

130

120

110

100

90

80

70

60

50

PF(AV) [W]

2000

1800

1600

1400

1200

1000

800

30°

60°

90°

120°

180°

DC

0 200 400 600 800 1000 1200 1400 1600

IF(AV) [A]

DC

180°

120°

90°

60°

30°

600

400

200

0

0 200 400 600 800 1000 1200 1400 1600

IF(AV) [A]

Loading...

Loading...