Page 1

TLA-01901C Service Manual

1

Page 2

Content

Chapter 1 - Specifications and Composition………………………………2

Chapter 2 - Brief introduction of the main

integrated circuit function……………………………………5

Chapter 3 - Analysis of the Signal process

Flowchart and Key Point Measure Data

Chapter 4 - Spare part list …………………………………………………38

Chapter 5 - The factory mode setting

and noticeable proceeding ……………………………………39

Chapter 6 - The flow of software update

and noticeable proceedin g……………………………………41

Annex : 1、 TLA-01901C Circuit diagram

2、 TLA-01901C exploded mechanical diagram

*Annex parts hasn’t been attached in this file. They will be provided

in separated files.

*The chassises of this LCD TV are called LS16 or L16W in this file.

LS16 and LS16W use the same TV resolution. The difference is the

connectors arrangement between these two chasises.

………………………25

2

Page 3

Chapter 1 - Specifications and Composition

1、Models of the chassis

LS16:TBD

LS16W: TLA-01901C

2、Main Feature

RF Input , including CATV Function(capable of compatible receiving

NTSC/ATSC/CLEAR-QAM ).

Capable of receiving the program of ATSC/NTSC within 54MHZ – 803MHz.

● AV Input

● HDMI Digital Signal Input

● VGA Input

● YPbPr Input

● Headphone Output

● SPDIF Digital Audio Output (Optional)

● 191 sets of programs presetting

In ATV mode, the TV can save 191 sets of program which fully prepared for the

richness programs in the future .

● Timer Function

Automatically on/off in certain preset time.

● Blue Background with Noise Silence (Optional)

The soft blue background will be displayed if there is no signal input in TV、

AV modes

● Automatic off if no signal input

LCD TV will go to the standby mode 15 or 5 minutes after there is no signal

input in TV mode.

● English / French/Spanish OSD menu

Simple graphic OSD menu makes the operation more convenient and more direct

viewing

● Power Energy Saving Function(power management mode)(only for LS16)

In PC mode, the LCD TV will automatically power off within 30 seconds and

enter into the Power Energy Saving Mode if there is no VGA signal input. It will

automatically exit from the Power Energy Saving Mode and work again when it

received a valid VGA signal or press any button on the panel/remote control.

● Plug and Play

It is no need to equip any installation software when the product is used as

computer terminal display equipment.

(In order to obtain a good image quality, perhaps,some minor adjustment should

be done with the PC display setting or TV pc set up. )

● Legerity , Convenience and Low power consumption

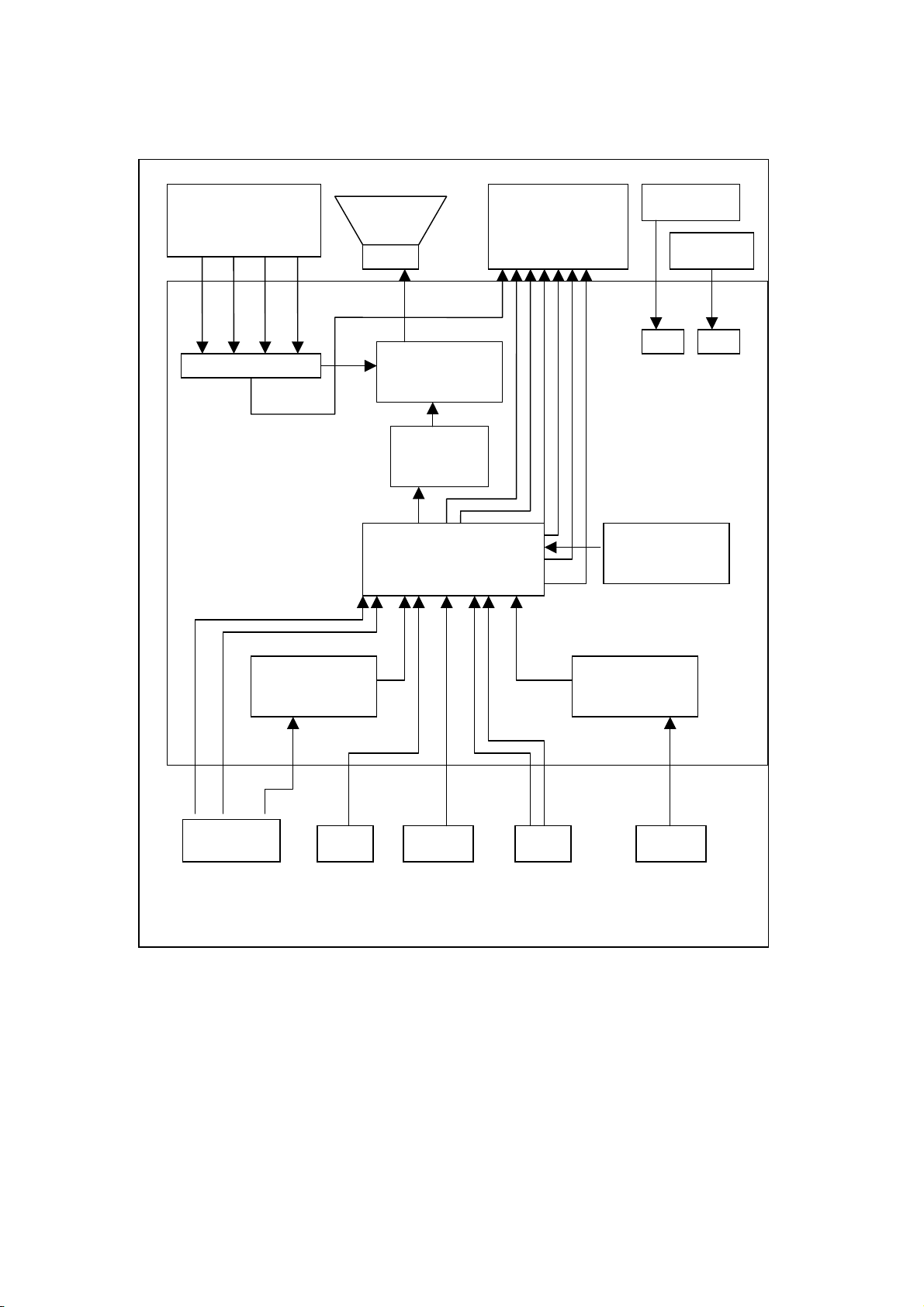

3、Unit circuit modules:

LS16 and LS16W chassis LCD TV is mainly composed of regulator IC,RF IC, video

processor IC ,power amplify IC, analog video IC, system control IC and key control

3

Page 4

IC. See the IC frame as below:

r

[

]

[

]

Power Board

+5V

+5V

+12V

+12V

Main Board

+5V

+12V

Speake

TDA1517

TL062

MSD116

TS

0…7

LCD Panel

AUDIO

K Panel

IR Panel

L V D S

S-FLASH

HD

0…7

CVBS

SIF

TUNER

4、PCB assembly introduction:

LS16 and LS16W LCD TV is mainly composed of AV Board , Remote Receiver Board,

Local Key Board and Main Board. The under sheet is the function introduction of every

MSD809

IF-D

AV

MST3383

HDMI PCYPbPr

4

Page 5

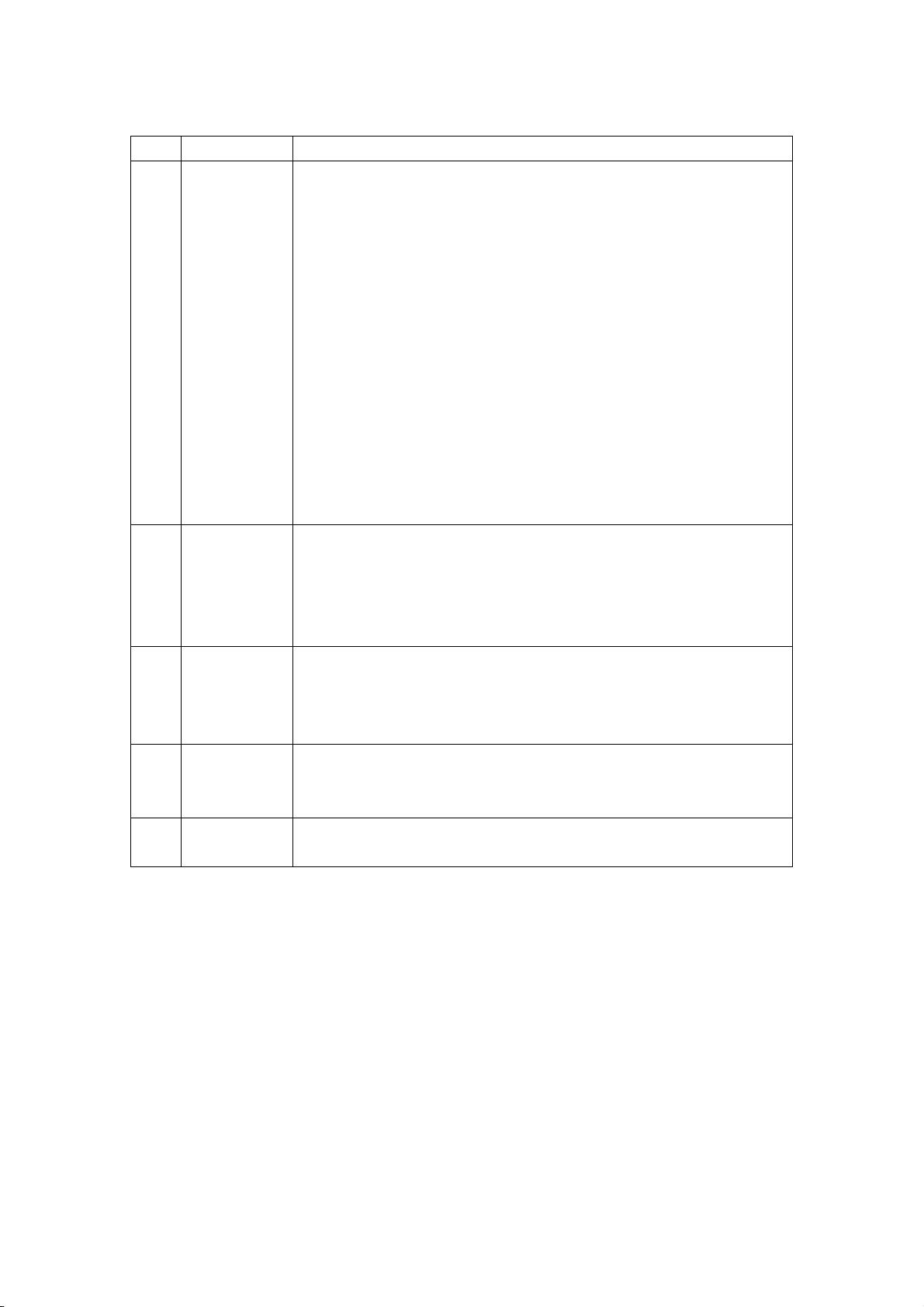

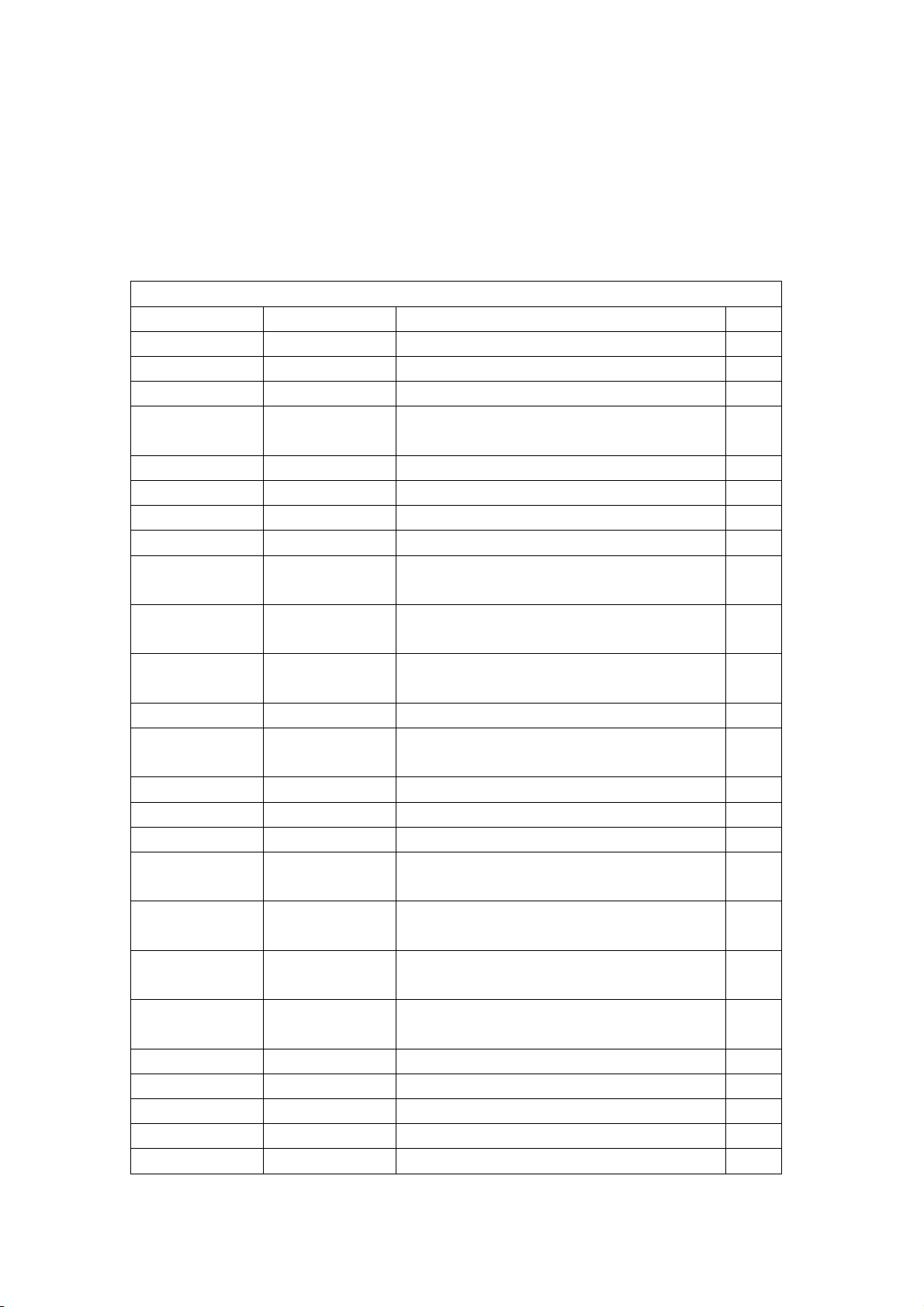

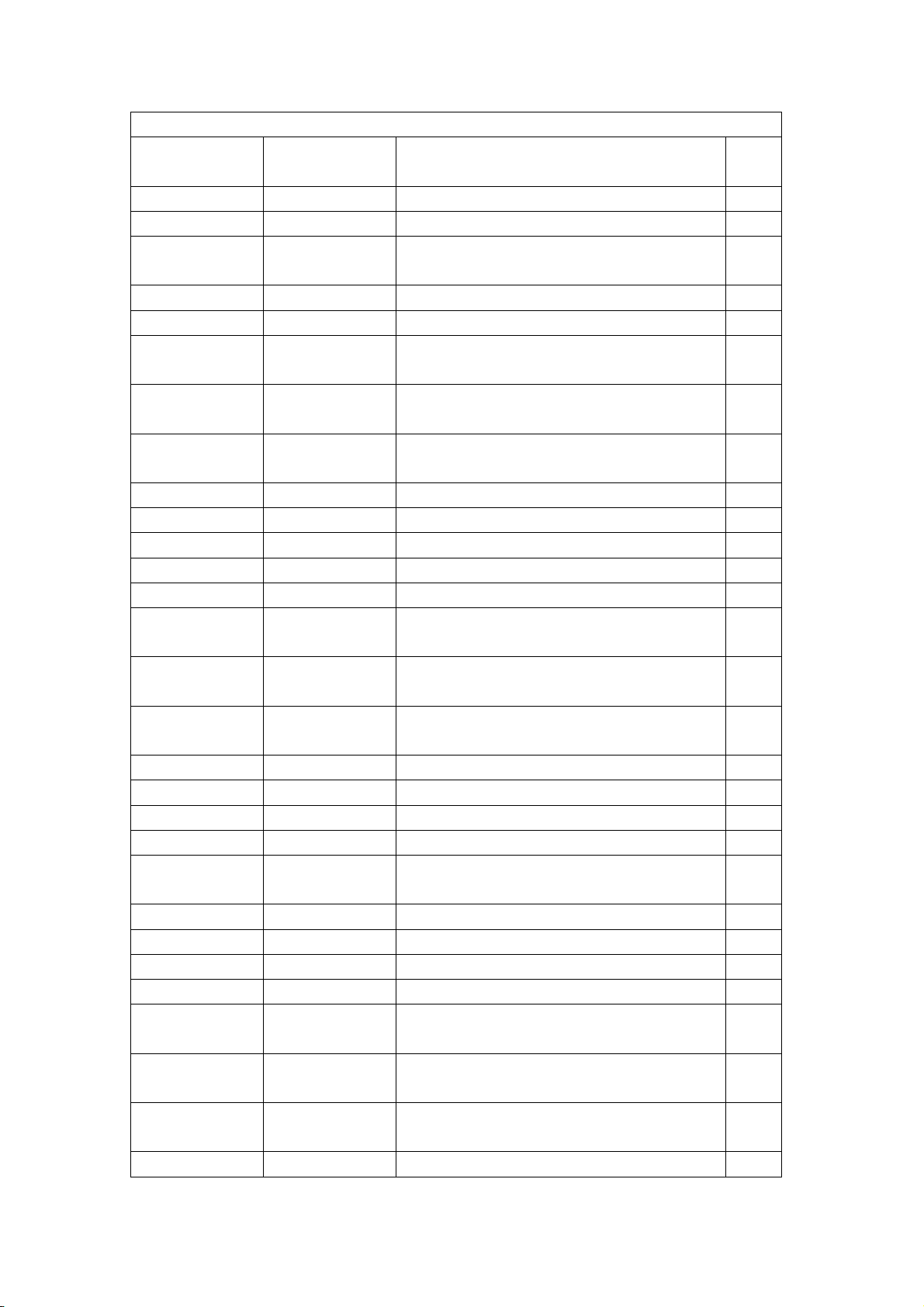

PCD Assembly:

NO. Parts Function Description

1

Main Board

module

3

4

5

6

Remote

Control

Receiver

Assembly

Built-in

Power Board

Assembly

Key Board

Assembly

Panel

Assembly

Main Board module is the core of LCD TV signal processing.

Under the control of the System Control Circuit, It undertakes the

task of converting the external input signal into the unified digital

signal that the LCD screen could identify 。 After RF signal

processed by tuner, It was sent to the main chip (analog signal was

sent to MSD116 for processing ,and digital signal was sent to

MSD809 for decoding first and then to MSD116 for processing ),

then the main chip(MSD116 ) produce LVDS signal displayed on

the screen .In addition, signals input from VGA、AV、SVIDEO and

YPbPr would directly enter into MSD116 for processing, format

transformation and on screen display. HDMI signal was sent to

MST3383 for processing first and then transmitted to MSD116 for

processing, format transformation and on screen display. And there

is a headphone output interface near the tuner. For LS16 only, it

has a digital audio output interface(SPDIF).

It is composite of one light indicator and one remote control

receiver, which enable users operate the TV conveniently and

know its current working status simply with a remote control.

It can transform AC power into DC for ICs including+12V,+5V and

ADJ for switching the backlight of LCD on or off and adjusting the

brightness.

It consists of 7 function buttons by which users can operate the TV

freely.

The LCD screen is used to display the image after the image signal

has been processed by the main board.

5

Page 6

Chapter 2 - Brief introduction of the main integrated circuit

function

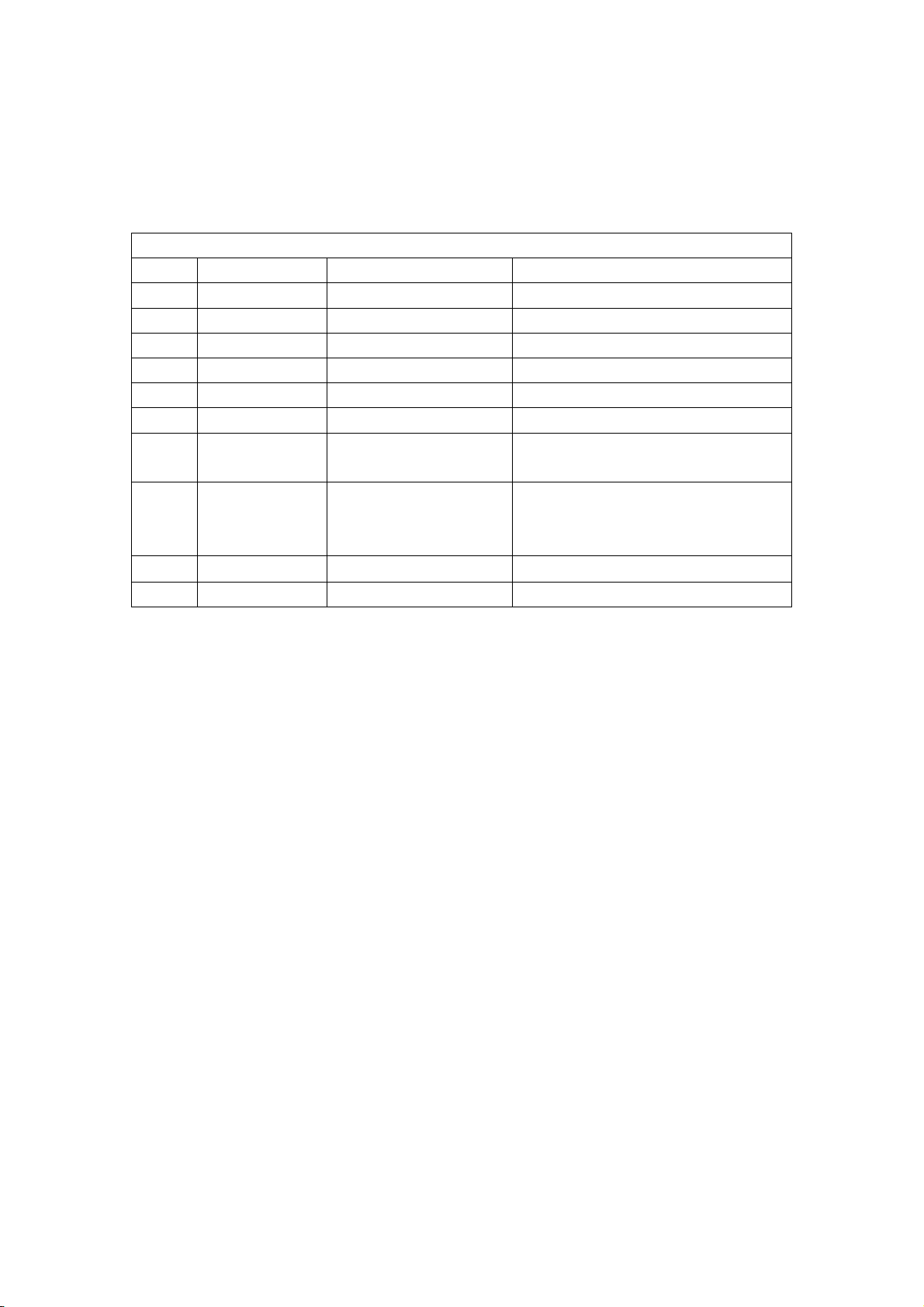

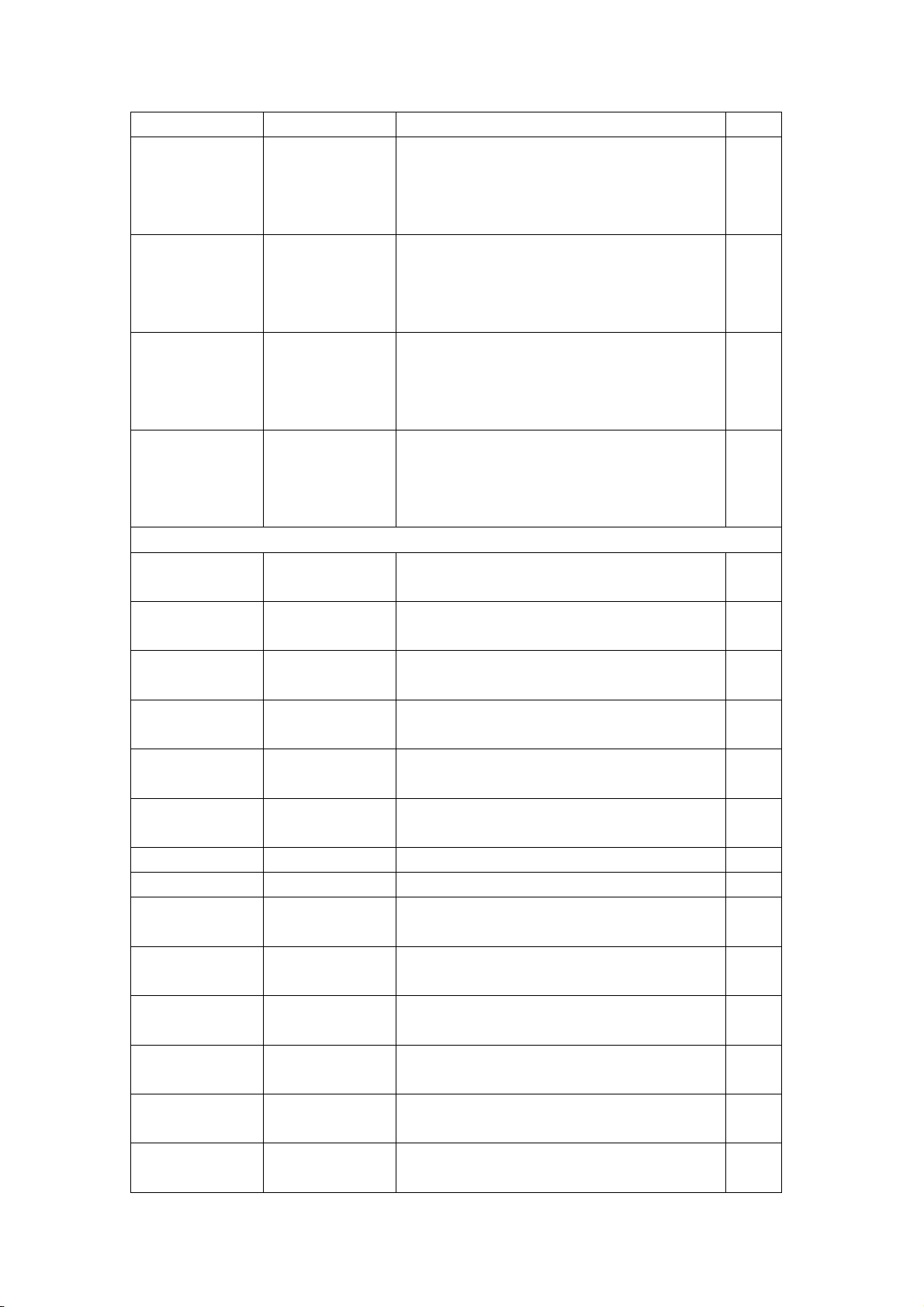

1、LS16 and LS16W Chassis Main ICs and function:

Main Board

Number Position Part Number Main function

1 U12,U6 24LC02 EEPROM

2 U23 24LC512 EEPROM

3 U7 MSD809 Demodulator

4 U9 MST3383AMCK-LF-170 HDMI Decoder

5 U8 DTVS205CH201A Tuner

6 U22 MSD116L Video and audio processor.

7 U24 M25P16-VMN6P/

S25FL016A0LMFI013

8 U28,U29,U30 IS42S16400D-6TL/

W9864G6GH-6/

K4S641632K-UC60

9 U31 TDA1517P Audio amplifier

10 U32 TL062CD Integration amplifier

Flash for code storage

SDRAM

2、LS16 and LS16W Chassis IC function.

2.1 TUNER(DTVS205CH201A)

GENERAL DESCRIPTION:

Receiving System: ATSC/NTSC system

Intermediate Frequency: Digital(center): 44MHz

Analog(P-carrier):45.75MHz

Input Impedance: 75Ω,Unbalanced

IF Output Impedance: 10Ω,Balanced

Band Change-Over System: PLL system

Tuning System: PLL system

Internal RF AGC function:

Built in wideband AGC detector with 6 programmable take-over points

Narrow band output to be filtering by a 5.6MHz SAW filter

Built in the additional IF amplifier with AGC circuit

Reference Frequency The X-tal the RF block’s PLL:4MHz

Control Data Bus: I²C (BUS VOLT AGE:3.3V)

Control Data Format: Refer to 6 Section

DTVS205CH201A BLOCK DIAGRAM:

6

Page 7

PIN FUNCTION DESCRIPTION:

PIN PIN NAME DESCRIPTION

1 NC not connected

2 NC not connected

3 NC not connected

4 NC not connected

5 NC not connected

6 NC not connected

7 RF AGC TP

8 NC not connected

9 VT 30V

10 IF OUT (+) digital IF

11 IF OUT (-) digital IF

12 IF AGC

13 TP(IF)

14 CLOCK

15 DATA

16 GND

17 5V

18 NC

19 AFT analog demod

20 SIF analog demod

21 CVBS analog demod

EXTERNAL

7

Page 8

2.2 MSD116L

GENERAL DESCRIPTION:

The MSD116L is a highly integrated SOC for LCD/PDP DTV applications with

resolutions up to SXGA/WXGA+.It is configured with an integrated triple-ADC/PLL,

a multi-standard TV video and audio decoder, a DTV video and audio decoder, a

video de-interlacer, a scaling engine, the MStarACE-3 color engine, a graphics engine,

an 8-bit MCU and a built-in output panel interface. The built-in DTV decoder

including transport stream de-multiplexer and MPEG-2 AV decoder are designed to

support ATSC HD/SDTV program while handling ATSC CC and EPG. For analog TV,

the MSD116L receives NTSC/PAL/SECAM CVBS/S-Video and component video

signals from various analog graphic & video sources. To further reduce system costs,

the MSD116L also integrates intelligent power management control capability for

green-mode requirements and spread-spectrum support for EMI management.

FEATURES

●Twin-turbo 8051 Micro-controller

●Transport Stream De-multiplexer

●MPEG-2 A/V Decoder

●NTSC/PAL/SECAM Video Decoder

●

Multi-Standard TV Sound Processor

●Digital Audio Interface

I2S digital audio input & output

S/PDIF digital audio input & output

●Analog RGB Compliant Input Ports

●Auto-Configuration/Auto-Detection

Two analog ports support up to 135MHz

Supports PC RGB input up to SXGA@75Hz

Supports HDTV RGB/YPbPr/YCbCr

Supports Composite Sync and SOG (Sync-on-Green) separator

Automatic color calibration

●High-Performance Scaling Engine

●

Video Processing & Conversion

●

Output Interface

Supports up to 8-bit dual LVDS SXGA/WXGA+ panel interface

Supports 2 data output formats: Thine & TI data mappings

Compatible with TIA/EIA

With 6/8 bits options

Spread spectrum output frequency for EMI suppression

Supports flexible spread spectrum frequency

●2D Graphics Engine

●Digital PWM Controller

●Miscellaneous

8

Page 9

SDRAM controller to support up to 48-bit data bus

Supports serial flash with up to 2M address

Two I2C interfaces in master/slave mode

One IR receiver input with power-down wakeup

256-LQFP package

Operating at 1.8V (core) and 3.3V (I/O and analog)

PIN FUNCTION DESCRIPTION:

Analog Interface

Pin Name Pin Type Function Pin

VCLAMP CVBS/YC Mode Clamp Voltage Bypass 20

REFM Internal ADC Bottom De-coupling Pin 18

REFP Internal ADC Top De-coupling Pin 19

SOGIN1 Analog Input Sync-on-Green slicer input from

channel 1

BINP Analog Input Analog B Input of VGA 1

GINP Analog Input Analog G Input of VGA 3

RINP Analog Input Analog R Input of VGA 4

PBINP Analog Input Analog Pb Input 11

VCOMB Analog Input Common Negative Input for

12

B-component ADC

SOGIN0 Analog Input Sync-on-Green slicer input from

13

channel 0

VCOMG Analog Input Common Negative Input for

15

G-component ADC

YINP Analog Input Analog Y Input 14

VCOMR Analog Input Common Negative Input for

17

R-component ADC

PRINP Analog Input Analog Pr Input 16

C0INP Analog Input Analog Chroma Input for TV S-Video0 23

YS0INP Analog Input Analog Luma Input of TV S-Video0 24

C1INP Analog Input Analog Chroma Input for TV S-Video1

25

/ Analog Composite Input of TV CVBS4

YS1INP Analog Input Analog Luma Input of TV S-Video0 /

26

Analog Composite Input of TV CVBS3

VCOMY Analog Input Common Negative Input for

27

Y-component ADC

CVBSOUT Analog

CVBS Output buffered from CVBS input 32

Output

CVBS0 Analog Input Analog Composite Input for TV CVBS0 31

CVBS1 Analog Input Analog Composite Input for TV CVBS1 30

CVBS2 Analog Input Analog Composite Input for TV CVBS2 29

CVBS3 Analog Input Analog Composite Input for TV CVBS3 28

DREXT Analog Input Reference Current Generator, 820 170

2

9

Page 10

ohm to Ground

HSYNC0 Schmitt

Trigger

HSYNC / Composite Sync for VGA Input

from channel 0

Input w/

5V-tolerant

VSYNC0 Schmitt

VSYNC for VGA Input from channel 1 10

Trigger

Input w/

5V-tolerant

HSYNC1 Schmitt

Trigger

HSYNC / Composite Sync for VGA Input

from channel 1

Input w/

5V-tolerant

VSYNC1

Schmitt Trigger

Input

w/ 5V-tolerant

VSYNC for VGA Input from channel 1

Digital Panel Output Interface

LVA0M Output

LVA0P Output

LVA1M Output

LVA1P Output

LVA2M Output

LVA2P Output

LVDS A-Link Channel 0 Negative Data

Output

LVDS A-Link Channel 0 Positive Data

Output

LVDS A-Link Channel 1 Negative Data

Output

LVDS A-Link Channel 1 Positive Data

Output

LVDS A-Link Channel 2 Negative Data

Output

LVDS A-Link Channel 2 Positive Data

Output

186

185

184

183

182

181

LVACKM Output LVDS A-Link Negative Clock Output 180

LVACKP Output LVDS A-Link Positive Clock Output 179

LVA3M Output

LVA3P Output

LVB0M Output

LVB0P Output

LVB1M Output

LVB1P Output

LVDS A-Link Channel 3 Negative Data

Output

LVDS A-Link Channel 3 Positive Data

Output

LVDS B-Link Channel 0 Negative Data

Output

LVDS B-Link Channel 0 Positive Data

Output

LVDS B-Link Channel 1 Negative Data

Output

LVDS B-Link Channel 1 Positive Data

Output

178

177

199

198

197

196

9

8

7

10

Page 11

LVB2M Output

LVB2P Output

LVDS B-Link Channel 2 Negative Data

Output

LVDS B-Link Channel 2 Positive Data

Output

195

194

LVBCKM Output LVDS B-Link Negative Clock Output 190

LVBCKP Output LVDS B-Link Positive Clock Output 189

LVB3M Output

LVB3P Output

LVDS B-Link Channel 3 Negative Data

Output

LVDS B-Link Channel 3 Positive Data

Output

188

187

Internal MCU Interface with Serial Flash Memory

SAR3 Analog Input SAR Low Speed ADC Input 3 204

SAR2 Analog Input SAR Low Speed ADC Input 2 203

SAR1 Analog Input SAR Low Speed ADC Input 1 202

SAR0 Analog Input SAR Low Speed ADC Input 0 201

SCK Output SPI Interface Sampling Clock 171

SDI Output SPI Interface Data-In 172

SDO

Input w/

5V-tolerant

SPI Interface Data-Out 173

CSZ Output SPI Interface Chip Select 174

GPIO_P10-GPI

O_P17

UART_TX

UART_RX

I/O w/

5V-tolerant

I/O w/

5V-tolerant

I/O w/

5V-tolerant

General Purpose Input/Output; 4mA

driving strength

41-4

8

Universal Asynchronous Transmitter 55

Universal Asynchronous Receiver 56

Input

IRIN

w/5V-toleran

IR Receiver Input 57

t

INT Input

MCU Bus Interrupt; 4mA driving

strength

58

SCLM Output I2C Master Clock 59

SDAM

I/O w/

5V-tolerant

I2C Master Data 60

DDC_SCL I/O DDC Clock for D-SUB Input 33

DDC_SDA I/O DDC Data for D-SUB Input 34

DDC_ROMSCL I/O DDC ROM Clock for D-SUB Input 35

DDC_ROMSDA I/O DDC ROM Data for D-SUB Input 36

SDRAM Interface

SDR_CSZ Output SDRAM Chip Select; active low 134

SDR_CKE Output SDRAM Clock Enable 126

SDR_AD[11:0] Output SDRAM Address Bus

148137

11

Page 12

SDR_BA[1:0] Output SDRAM Bank Select

129,

130

168161,

157-

SDR_DQ[31:0] I/O SDRAM Data Bus

150,

124117,

114107

SDR_RASZ Output SDRAM Row Address Strobe; active low 131

SDR_CASZ Output

SDRAM Column Address Strobe; active

low

132

SDR_WEZ Output SDRAM Write Enable 133

169,

SDR_DQM[3:0] Output

SDRAM Data Mask for Low Byte; active

high

149,

125,

106

SDR_MCLKO Output Master Clock Output to SDRAM 128

SDR1_CKE Output SDRAM1 Clock Enable 225

SDR1_AD[11:0

]

Output SDRAM1 Address Bus

SDR1_BA[1:0] Output SDRAM1 Bank Select

224-

213

233,

232

251-

245,

SDR1_DQ[15:0

]

I/O SDRAM1 Data Bus

243,

242,

240-

234

SDR1_RASZ Output

SDR1_CASZ Output

SDRAM1 Row Address Strobe; active

low

SDRAM1 Column Address Strobe;

active low

231

230

SDR1_WEZ Output SDRAM1 Write Enable 227

SDR1_DQM[1:0

]

Output

SDRAM1 Data Mask for Low Byte;

active high

229,

228

SDR1_MCLKO Output Master Clock Output to SDRAM1 226

TS Input Interface

TSCLK Input TS Clock 95

TSDATA[7:0] Input

TS Data in Parallel; LSB (bit 0) is

for serial TS data

96-1

03

TSVALID Input TS Data Valid 104

TSSYNC Input TS Sync-Byte Indicator 105

12

Page 13

Audio Input/Output Interface

SIF0M Analog Input

Reference Ground for SIF Audio Input

Channel 0

50

SIF0P Analog Input SIF Audio Input Channel 0 51

SIF1P Analog Input SIF Audio Input Channel 1 53

SIF1M Analog Input

Reference Ground for SIF Audio Input

Channel 1

54

I2S_OUT_MCK Output Audio Master Clock Output 85

I2S_OUT_BCK Output Audio Bit Clock Output 86

I2S_OUT_WS Output

I2S_OUT_SD Output

SPDIFO Output

Word Select Output; 4mA driving

strength

Audio Serial Data Output; 4mA

driving strength

S/PDIF Audio Output; 4mA driving

strength

87

88

90

I2S_OUT_MUTE Output Audio Output Mute Control 89

I2S_IN_BCK Input Audio Bit Clock Input 81

I2S_IN_WS Input Word Select Input 82

I2S_IN_SD Input Audio Serial Data Input 83

SPDIFI Input S/PDIF Audio Input 84

AUVRM

AUVRP

AUVAG

Analog

Output

Analog

Output

Analog

Output

Negative Reference Voltage for

Audio ADC

Positive Reference Voltage for

Audio ADC

Reference Voltage for Audio Common

Mode

64

65

66

AUL0 Analog Input Audio Line Input Left Channel 0 68

AUR0 Analog Input Audio Line Input Right Channel 0 69

AUL1 Analog Input Audio Line Input Left Channel 1 70

AUR1 Analog Input Audio Line Input Right Channel 1 71

AUCOM Analog Input

Reference Ground for Audio Line

Input

72

AUL2 Analog Input Audio Line Input Left Channel 2 73

AUR2 Analog Input Audio Line Input Right Channel 2 74

AUL3 Analog Input Audio Line Input Left Channel 3 75

AUR3 Analog Input Audio Line Input Right Channel 3 76

AUOUTL1

AUOUTR1

AUOUTL0

Analog

Output

Analog

Output

Analog

Output

Main Audio Output Left Channel 0 77

Main Audio Output Right Channel 0 78

Main Audio Output Left Channel 0 79

AUOUTR0 Analog Main Audio Output Right Channel 0 80

13

Page 14

Output

Power Pins

AVDD_ADC 3.3V Power ADC Power

6,

22

AVDD_SIF 3.3V Power SIF Power 52

AVDD_AU 3.3V Power Audio Power 67

AVDD_SDRPLL 3.3V Power SDRPLL Power 127

AVDD_LPLL 3.3V Power LPLL Power 193

AVDD_XTAL 3.3V Power XTAL Power 254

94,

VDDC 1.8V Power Digital Core Power

160,

200,

253

91,

115,

135,

VDDP 3.3V Power Digital Input/Output Power

158,

176,

192,

211,

244

5,

21,

49,

62,

63,

92,

93,

GND Ground Ground

116,

136,

159,

175,

191,

212,

241,

252,

2.3 MST3383 Description:

GENERAL DESCRIPTION:

14

Page 15

The MST3383AMCK integrates the HDMI compliant receiver for enabling

advanced digital display devices such as digital TVs, plasma displays, LCD TVs and

projectors to receive and display. Compatible with the HDMI 1.2 specification, the

MST3383AMCK enables consumer electronic devices to receive uncompressed, high

quality, digital audio and video HD content over a single, low-cost HDMI cable. The

MST3383AMCK is available in a 128-pin PQFP package.

FEATURES:

●Highly integrated HDMI interface for 25~170 MHz pixel rates

●Compatible with VGA through UXGA RGB graphics signals, and component TV,

DTV and HDTV

●One DVI/HDMI single link input

●HDMI 1.2 compliant

●Smart sync detection with HSYNC, VSYNC and DE period report

●Serial port programming interface

●Integrated HDCP keys

●HDMI Interface

25 MHz ~ 170 MHz operation

Supports HDMI (High Definition Multimedia Interface) 1.2

Supports High bandwidth Digital Content Protection (HDCP) 1.1

Backward compatible to DVI 1.0

Supports up to 25m cable

Supports encrypted video contents

Supports authentication of video receiver with decryption of encoded data at the

receiver

Supports pin-swap to DVI/HDMI connector for low EMI

●Digital Audio Output Interface

Supports 2-channel serial audio output

Supports S/PDIF digital audio output

Supports audio sample rates of 32~192kHz, with a sample size of 16~24 bits

Pop sound suppression with auto fading

Volume control, 0 to -138 dB, -0.75 dB/step

Supports DSD audio stream with external DSD DAC

●Digital Video Output Interface

Supports color space conversion and sRGB

Supports 24-bit 4:4:4 YCbCr/RGB output formats

Supports 16-bit 4:2:2 YCbCr output formats (ITU-R BT.601)

Supports 8-bit 4:2:2 YCbCr output formats (ITU-R BT.656)

MST3383BLOCK DIAGRAM:

15

Page 16

PIN FUNCTION DESCRIPTION:

CPU Interface

Pin Name Pin Type Function Pin

Schmitt

HWRESET

Trigger

Input w/

Hardware Reset; Active High 35

5V-tolerant

A0

SCL

SDA

Input w/

5V-tolerant

Input w/

5V-tolerant

I/O w/

5V-tolerant

Serial Interface Address Input 36

2-Wire Serial Bus Clock Input 37

2-Wire Serial Bus Data I/O 38

Output

INT

w/Pull-Down

CPU Interrupt Programmable By User 40

Resistor

DVI/HDMI Interface

RX0N

RX0P

RX1N

RX1P

DVI/HDMI

Input

DVI/HDMI

Input

DVI/HDMI

Input

DVI/HDMI

Input

Negative DVI/HDMI Input for Data

Channel 0

Positive DVI/HDMI Input for Data

Channel 0

Negative DVI/HDMI Input for Data

Channel 1

Positive DVI/HDMI Input for Data

Channel 1

108

109

111

112

RX2N DVI/HDMI Negative DVI/HDMI Input for Data 114

16

Page 17

Input Channel 2

RX2P

RXCKN

RXCKP

DVI/HDMI

Input

DVI/HDMI

Input

DVI/HDMI

Input

Positive DVI/HDMI Input for Data

Channel 2

Negative DVI/HDMI Input for Clock

Channel

Positive DVI/HDMI Input for Clock

Channel

115

117

118

Misc. Interface

XOUT Crystal Oscillator Output 33

XIN Crystal Oscillator Input 34

REXT

DDCSCL

DDCSDA

Input w/

5V-tolerant

I/O w/

5V-Tolerant

External Resistor 390 Ohm connected

to AVDD_DVI

HDCP Slave Serial Bus Clock Input for

DVI

120

124

HDCP Slave Serial Bus Data I/O for DVI 125

Output Interface

DATA[23:0]

DATACK

SOGOUT/DE

HSOUT

VSOUT

FIELD/GPO

AUSD

AUSCK

AUWS

Output

w/Pull-Down

Resistor

Output

w/Pull-Down

Resistor

Output

w/Pull-Down

Output

w/Pull-Down

Resistor

Output

w/Pull-Down

Resistor

Output

w/Pull-Down

Resistor

Output

w/Pull-Down

Resistor

Output

w/Pull-Down

Resistor

Output

w/Pull-Down

Resistor

Data Output Bit [23:0]; 4~12 mA

Driving Strength Programmable by User

Clock Output A; 4~12 mA Driving

Strength Programmable by User

Sync-on-Green Output for Analog 69

HSYNC Output; 4~12 mA Driving

Strength Programmable by User

VSYNC Output; 4~12 mA Driving

Strength Programmable by User

Frame Indication Output During

Interlace Input / General Purpose

Output Programmable by User

Audio Serial Data Output Bit; 4~12 mA

Driving Strength Programmable by User

Audio Serial Clock Output; 4~12 mA

Driving Strength Programmable by User

Audio Serial Word Select Output; 4~12

mA Driving Strength Programmable by

User

43-50,

55-62,

76-83

68

70

71

72

96

97

98

AUMUTE Output Audio Output Mute Control 99

17

Page 18

w/Pull-Down

Resistor

Output w/

MCKO

pull-Down

Audio Master Clock Output 100

Resistor

SPDIFO

Output

w/Pull-Down

Resistor

Audio SPDIF Output; 4~12 mA Driving

Strength Programmable by User

101

Power Pins

AVDD_DVI 3.3V Power DVI Power Supply

4, 29, 113,

119, 126

AVDD_MPLL 3.3V Power Master PLL Power Supply 32

AVDD_AUPLL 2.5V Power Audio PLL Power Supply 106

AVDD_PLL 3.3V Power PLL Power Supply 123

VDDP 3.3V Power Digital Output Power Supply

39, 53, 65, 73,

86, 88, 90, 102

VDDC 2.5V Power Digital Core Power Supply 67, 75, 92

5, 30, 31, 54,

66, 74, 87,89,

GND Ground System Ground

91, 103-105,

107, 110,

116, 122, 127

2.4 MSD809 Description:

GENERAL DESCRIPTION:

The MSD809 is a DTV receiver, which contains a digital receiver compatible with

ATSC 8-VSB mode for terrestrial broadcasting and ITU-J.83B which is in compliant

with 64-QAM and 256-QAM modes for digital cable appliances. It achieves

extremely high performance employing direct IF sampling architecture, robust

synchronization, and robust channel equalization. It contains a 12-bit A/D converter

and a PWM generator for automatic gain control. A host interface with an I2C bus is

also included to control the behavior of the MSD809.

FEATURES:

●Integrated 8-VSB and 64/256QAM Receiver

Direct 44MHz IF sampling scheme from tuner

Internal digital SAW filter for reduction external IF circuitry

12-bit A/D converter for sampling

MPEG-2 transport output with parallel/serial mode

GPIO control for tuner bypass mode

Enhanced FEC architecture with efficient high performance

Segment error rate measurement from the output of RS decoder

18

Page 19

External ADC @24.69MHz

Optional dual AGC

49.38111MHz oscillator or crystal is used for reference clock

100-pin TQFP package

Low power consumption

Sleep mode and auto recovery mode

3.3V/1.2V operation

●8-VSB ATSC Receiver

Integrated de-interleaver RAM for VSB FEC

Symbol timing recovery range up to ± 200ppm

Carrier recovery range up to ± 250kHz

De-ghosting range up to –37usec to +47usec

Improvement of all delay echo cancellation

Full digital carrier/timing recovery and matched filtering

Phase tracking loop for compensating phase error

●64/256QAM ITU-T J.83B Receiver

ITU-T J.83B compliant 64/256 QAM demodulator and FEC

Symbol timing recovery range up to ±200ppm

Carrier recovery range up to ±400kHz

De-ghosting range up to ±12usec

Improvement of all delay echo cancellation

Full digital carrier/timing recovery and matched filtering

Phase tracking loop for compensating phase error

Digital HD/SDTV

Digital set-top box

Digital TV PC card

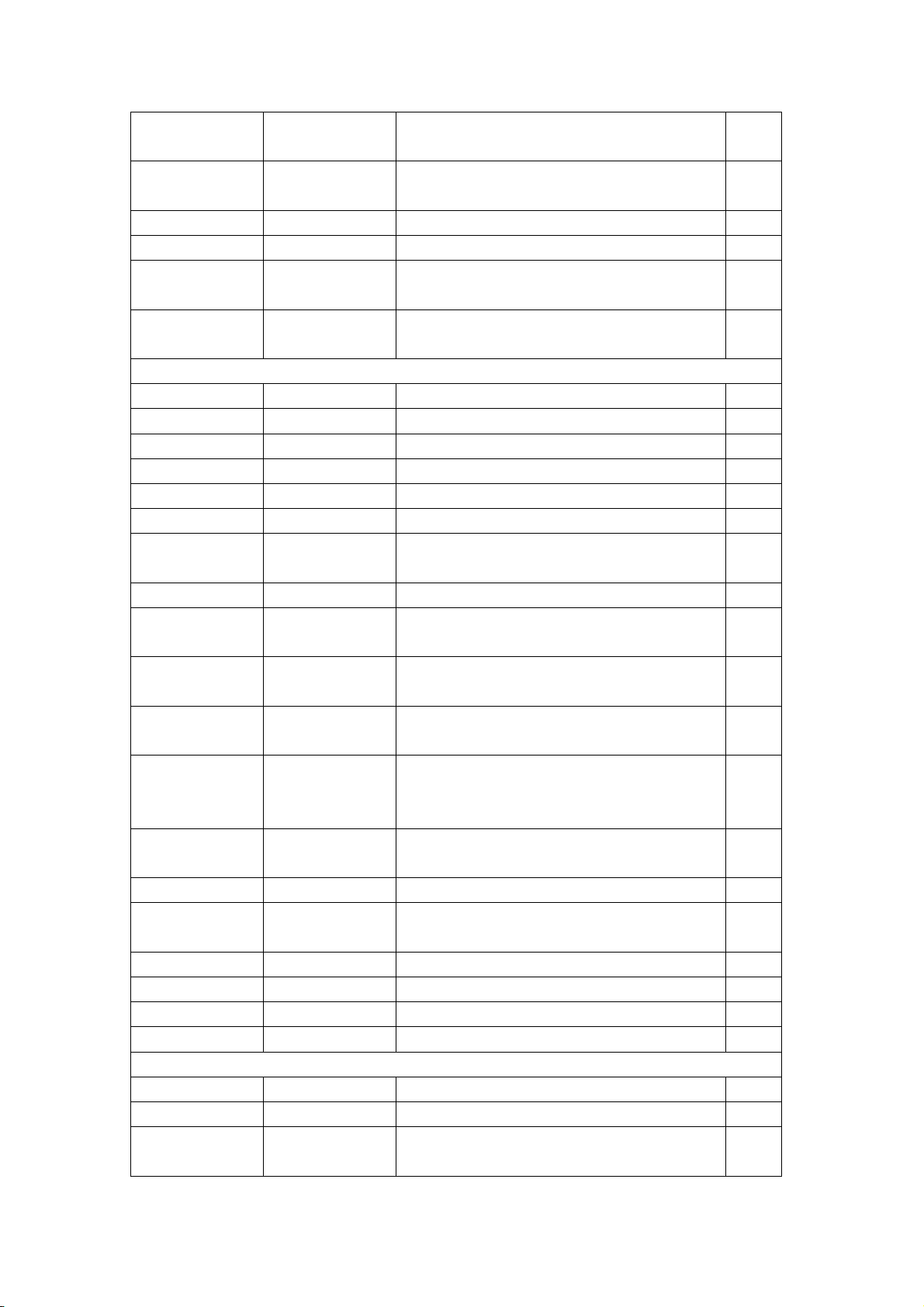

PIN FUNCTION DESCRIPTION:

Pin Name

Pin

Type

Function Pin

GPIO_IN0 I/O TUNER_SDA 1

GPIO_IN1 I GPIO 2

3, 9, 21,

31, 35,

VDD12IH Power Internal Power (1.2V nominal)

45, 50,

63, 69,

86, 91, 93

4, 10, 22,

VSSIPH Power Internal Ground

30, 34,

44, 49,

19

Page 20

61, 68,

85, 92, 94

PK_DATA[7:0] O MPEG Transport Stream Data 5-8, 11-14

15, 27,

VDD33OPH Power Pad Power (3.3V nominal)

41, 60,

75, 99

VSSOH Power Pad Ground

16, 74,

100

RESET_N I System Reset 17

TEST_BIRA I Connected to GND 18

TEST_SIG[3:0] I Connected to GND

24, 23,

20, 19

PK_CLK O MPEG Clock Signal 25

VSSOH Power Pad Ground 26, 40, 57

PK_SYNC O MPEG Sync Signal 28

PK_ERR O MPEG Error Signal 29

PK_VAL O MPEG Valid Signal 32

EXT_PLL_SEL I Internal/External PLL Selection 33

SDA I/O Serial Bus Data Signal 36

SCL I Serial Clock Signal 37

I2CADDR[1:0] I Device ID Selection 39, 38

20

Page 21

TEST_SEL[4:0] I

Test Mode Selection (Connected to

GND)

42, 43,

46-48

VDD12T_ABB Power PLL Power (1.2V) 51, 56

VSST_ABB Power PLL Ground 52

VBB_ABB Power PLL Bulk Ground 53

FILTER AI PLL Filter 54

VSSBB_ABB Power PLL Ground 55

OSC_XIN AI Crystal Input 58

OSC_XOUT AI Crystal Output 59

CLK_EXT_ADC AI Clock for External ADC 62

64-67,

70-73,

87-90

D_IN[11:0] I

External ADC Input

(optional/normally GND)

VSSBBH_ABB Power Analog Ground for ADC (3.3V) 76

VDD33TH_ABB Power Analog Power for ADC (3.3V) 77, 84

CML AB 1.65V Common Mode Level 78

RN_ADC AB Reference Bottom Bias 79

RP AB Reference Top Bias 80

AIN AI Analog Input 81

21

Page 22

AIP AI Analog Input 82

VSSBBTH_ABB Power Analog Sub Bias for ADC (Ground) 83

IF_GAIN O Sigma-delta IF AGC 95

TU_GAIN O Sigma-delta Tuner AGC 96

GPIO_OUT1 O GPIO_FEC Lock 97

GPIO_OUT0 O TUNER_SCL 98

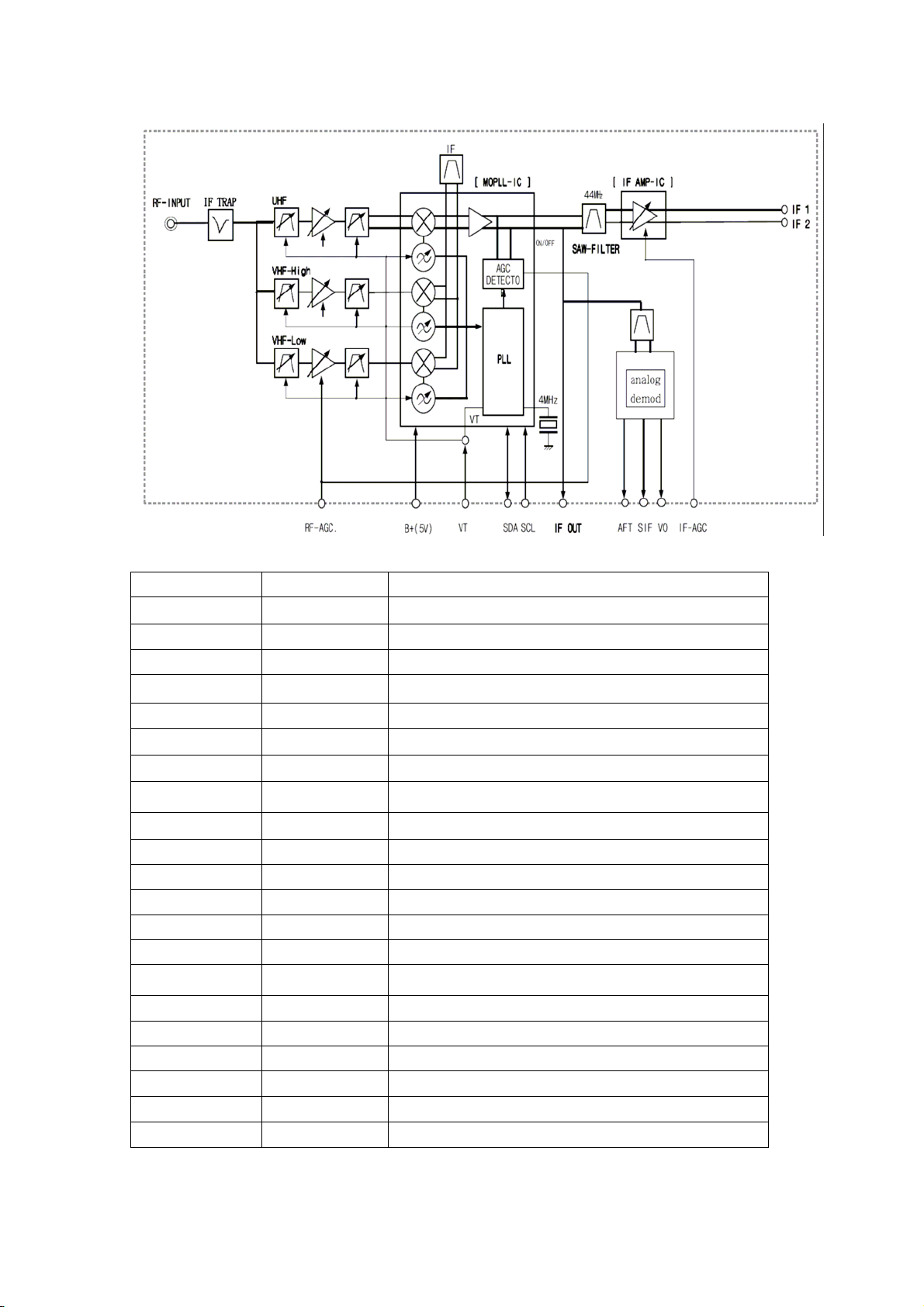

MSD809 Functional Block Diagram:

2.5 TDA1517 Description:

GENERAL DESCRIPTION:

The TDA1517P is an integrated class-AB output amplifier contained in a plastic

heatsink thin shrink small outline package (HTSSOP20/16). The device is primarily

developed for multimedia applications.

FEATURES:

22

Page 23

● Requires very few external components

● Flexibility in use: mono Bridge-Tied Load (BTL) and stereo Single-Ended (SE); it

should be noted that in stereo applications the outputs of both amplifiers are in

opposite phase

●High output power

● Low offset voltage at output (important for BTL)

● Fixed gain

● Good ripple rejection

● Mode select switch (operating, mute and standby)

● AC and DC short-circuit safe to ground and VP

● Electrostatic discharge protection

● Thermal protection

● Reverse polarity safe

● Capable of handling high energy on outputs (VP = 0 V)

● No switch-on/switch-off plop

● Low thermal resistance.

TDA1517 BLOCK DIAGRAM:

23

Page 24

PIN FUNCTION DESCRIPTION:

PIN PIN NAME DESCRIPTION

1 NC not connected

2 NC not connected

3

4

5

6 NC not connected

7 NC not connected

IN1+

SGND

SVRR

non-inverting input 1

signal ground

supply voltage ripple rejection

8

9

10

11

24

OUT1a

OUT1b

PGND1

PGND2

output 1a

output 1b

power ground 1

power ground 2

Page 25

12

13

OUT2a

OUT2b

output 2a

output 2b

14 NC not connected

15

16

17

VP1

VP2

MODE

supply voltage 1

supply voltage 2

mode select switch

18 IN2− inverting input 2

19 NC not connected

20 NC not connected

25

Page 26

Chapter 3 - Analysis of the Signal process Flowchart

and Key Point Measure Data

The chapter mainly introduces the receive and dispose of the video and audio

signal , the power supply system and system control process of this TV.

1. Video Signal Flow:

Analog RF signal enter into the tuner for decoding and output the CVBS signal, and

then this signal is sent to the MSD116L through low pass filter for processing, format

transformation and producing LVDS signal displayed on the screen. Digital RF signal

enter into the tuner for decoding and output the digital IF signal, and then this signal is

sent to MSD809 for decoding and output the transport stream which is sent to MSD116L

for processing in order to form uniform up-screen signal format.

Signals input from VGA、AV、SVIDEO and YPbPr would directly enter into MSD116

for processing to form uniform up-screen signal.

HDMI signal was sent to MST3383 for processing first and then transmitted to

MSD116 for processing to form uniform up-screen signal.

2. Sound process Flow:

ATV:RF signal which is demodulated by tuner convert SIF signal ,then it would be

sent to MSD116L for sound disposal, the output audio signal is zoomed in by TL062 and

TDA1517, and is sent into the speaker at last.

DTV: RF signal which is demodulated by tuner convert digital IF signal, then it would

be sent to MSD809 for decoding, and then the signal is sent to MSD116L for sound

disposal, the output audio signal is zoomed in by TL062 and TDA1517, and is sent into the

speaker at last.

AV、PC、YPbPr: Audio signal is directly sent into MSD116L for sound disposal, the

output audio signal is zoomed in by TL062 and TDA1517, and is sent into the speaker at

last.

SPDIF: Audio signal which decode by MST3383(HDMI) is sent to MSD116L for sound

disposal, then the output audio signal is sent into the Digital Power Amplifier.

3. The TV power supply system:

2 channels voltage are transported from the power supply board, they are +12V and +5V, they

will not be cut off in standby mode. +12V is provided for PA (TDA1517), and it is transformed

into +6V to provide for U32 and U33,+12V is also transformed by U5(MP1411) into +5V which is

provided for the panel, +12V is still transformed by U4 (MP1411) into +1.8V to provide for

MSD116L; +5V is provided for infrared receiver and EEPROM, +5V is transformed by

D0(AZ1117) into 3.3V、2.5V and 1.2V which are provided for IC, and they will be shut off under

standby mode. +12V and +5V is controlled by U3 (7413), +12V and +5V of the 7413 will be cut

off under standby mode, and it will output +12V and +5V when power on.

3.1 The composition and distribution of the TV power supply:

26

Page 27

N

CON1

,

PIN 1

2

U4(MP1411DH)

L8 Output

(for 116 ,1.8V)

U31(TDA1517)PIN 7

CON4

PIN 5,6

CON5

PIN 1 - 4

CON3

PIN2、3

+12V

U3(7314)

U25(1117-3.3)

U26(1117-3.3)

U3(7314)

U5(MP1411DH)

U32、U33 PIN 8

DD13(4148)

egative (30V)

CON11

PIN 28 - 30

U10(1117-2.5)

U20

(1117-3.3)

U22(MSD116L)

U19

U9

MST3383

U7

MSD809

U9

MST3383

U22(MSD116L)

U4

(MP1411DH)

SDRAM(U28-U30)

27

Page 28

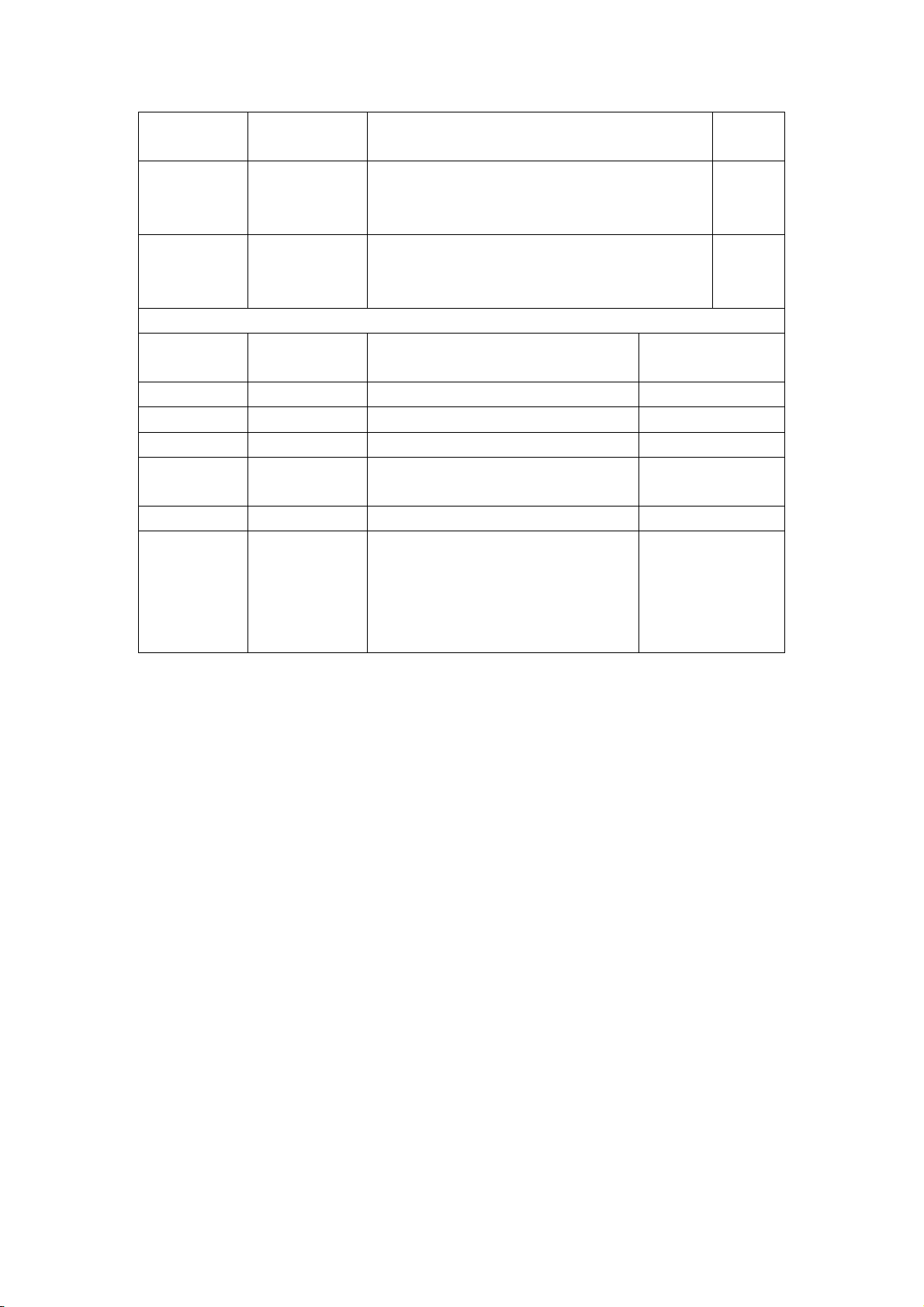

3.2 The Pin Voltage of regulator on Main Board (Following voltage are center

value)

PIN1(V) PIN2(V) PIN3(V) PIN4(V)

Position Part number

U10 NCP1117ST25T3G/

LD1117S25TR/

AZ1117H-2.5TRE1

U19 AP1122EL 0 1.2 3.3 1.2

U20 NCP1117ST33T3G/

LD1117S33TR/

AZ1117H-3.3TRE1

U25 NCP1117ST33T3G/

LD1117S33TR/

AZ1117H-3.3TRE1

U26 NCP1117ST33T3G/

LD1117S33TR/

AZ1117H-3.3TRE1

0 2.5 5 2.5

0 3.3 5 3.3

0 3.3 5 3.3

0 3.3 5 3.3

28

Page 29

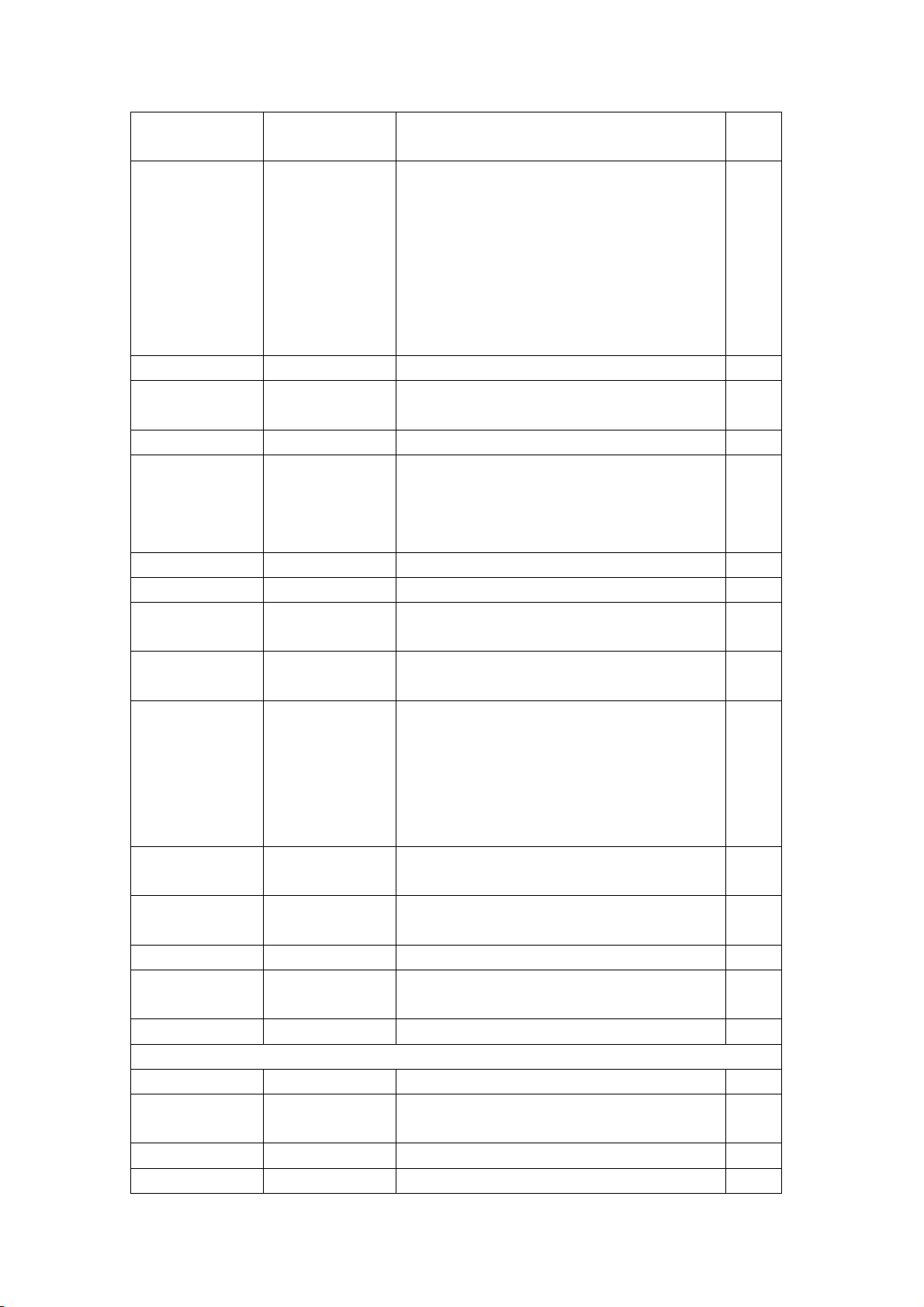

4. Main Components and Socket Locations and Definitions

2 1 3 4

G

14

15

16

17

18

13

B

A

D

F

H

E

5

19

20

21

12

L

11

10

I

K

9

C

8

6

7

J

Socket Definition:

Number Position Connected Object Function Description

1 CON5 Power supply board NO use

2 CON1 Power supply

board(FSP066-1E01)

3 CON4 Power supply board +12V,for backlight switch and

+12V

29

Page 30

brightness adjust

4 CON3 Power supply board +5V, for backlight switch and

brightness adjust

5 CON11 Up screen LVDS interface

6 CON27 K board

7 CON31 Remote receiver board

8 CON39 Speaker

9 CON30 AV borad

10 CON13 Upgrade Equipment

11 CON29 AV borad

12 CON28 AV borad

13 CON38 No use

14 CON2 Power adapter +12V

15 CON9 HDMI port HDMI signal input

16 CON7 VGA port VGA signal input

17 CON8 VGA audio input VGA audio signal input

18 CON18 YPbPr audio input YPbPr audio signal input

19 CON35 YPbPr video input YPbPr video signal input

20 U18 Digital Power Amplifier SPDIF digital audio output

21 CON16 Headphone

Main Components Description:

Number

Position Part number

Function Description

A

B

C

D

U22

U9

U7

U28

MSD116L Audio decoder

MST3383AMCK-LF-170 HDMI decoder

MSD809 Digital signal demodulator

IS42S16400D-6TL/

Memory for SDRAM

W9864G6GH-6/

K4S641632K-UC60

E

U29 IS42S16400D-6TL/

Memory for SDRAM

W9864G6GH-6/

K4S641632K-UC60

F

U30 IS42S16400D-6TL/

Memory for SDRAM

W9864G6GH-6/

K4S641632K-UC60

G

U3

H

I U8 DTVS205CH201A Tuner

J

U24

U31

NTMD6P02R2G/

IRF7314TRPBF/

KMA5D8DP20Q

M25P16-VMN6P/

S25FL016A0LMFI013

TDA1517P Audio Power Amplifier

Memory for SDRAM

Flash for code storage

30

Page 31

K

L

U32

U33

TL062CD Integration Amplifier

TL062CD Integration Amplifier

5 Key point waveform diagram:

5.1 RF input color bar signal, TV signal waveform in the 21

these:

th

pin of tuner U8, is like

5.2 RF input gray ladder signal, TV signal waveform in the 21

like these:

th

pin of tuner U8, is

31

Page 32

5.3 RF input 720P color bar signal, TV signal(IF OUT+) waveform in the 10

of tuner U8, is like these:

th

pin

5.4The BTSC sound signal input, the SIF waveform of the 20th pin of U8 is like this:

32

Page 33

5.6 The BTSC sound signal input, the waveform of the 1st pin of U32 is like this:

5.7 The BTSC sound signal input, the waveform of the 7th pin of U32 is like this:

33

Page 34

5.8 The BTSC sound signal input, the waveform of the 1st pin of U31 is like this:

5.9

The BTSC sound signal input, the waveform of the 9th pin of U31 is like this:

34

Page 35

5.10 The BTSC sound signal input, the waveform of the 4

th

pin of U31 is like this:

Note: this waveform is about with the value of volume.

5.11 The BTSC sound signal input, the waveform of the 6th pin of U31 is like this:

35

Page 36

Note: this waveform is about with the value of volume.

36

Page 37

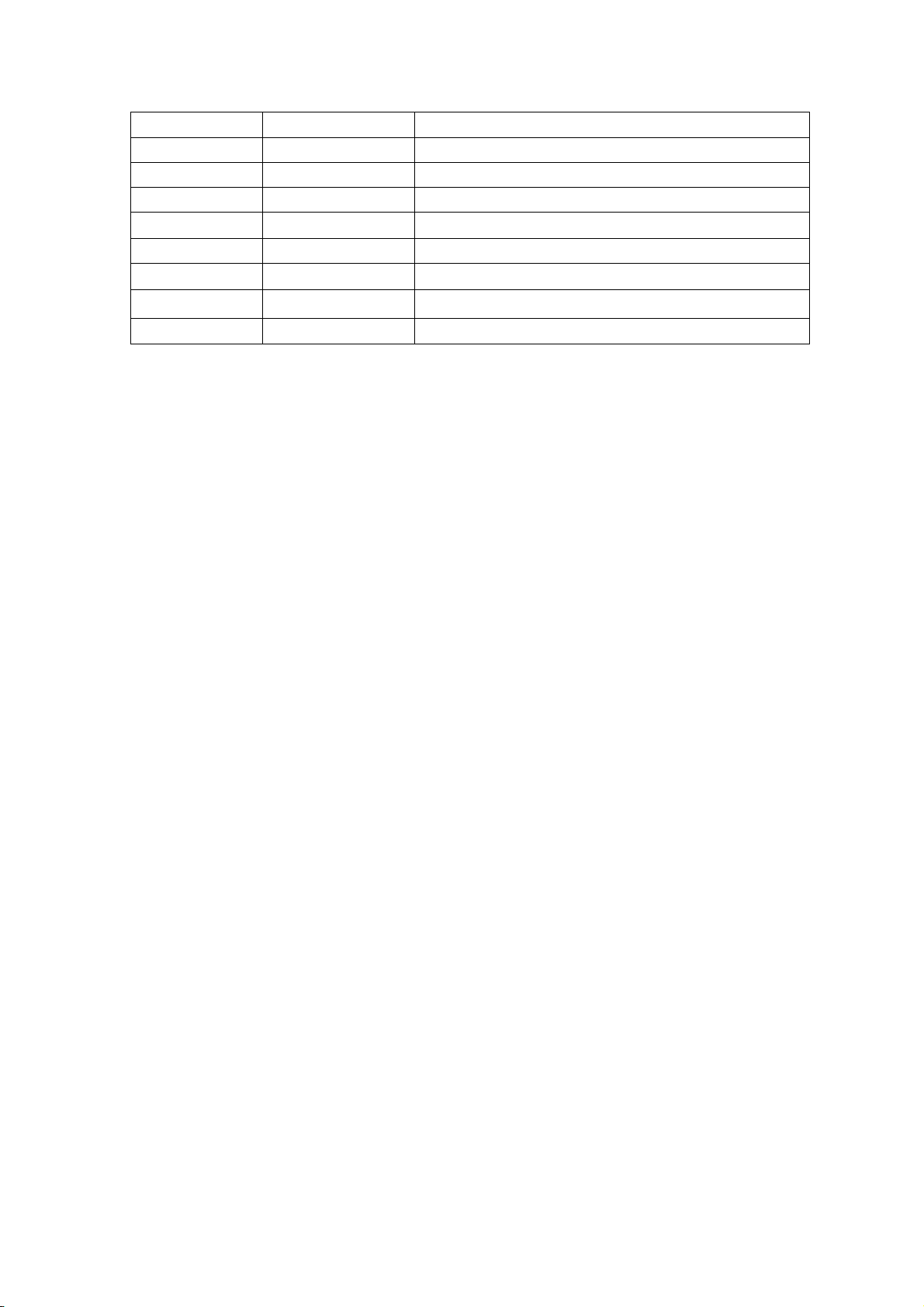

Chapter 4 - Spare part list

This list is provided for reference, if change the parameters of

those maintain parts of an apparatus ,we do not notice in the future.

The newest data regard as The correct type or specification.

TLA01901C spare parts:

NO. Name Code Number PCB Number

1.

Front frame

2.

faceplate 810035324

3.

Back cover 810035322

4.

Pedestal 810031032

5.

plank 810031035

Mainboard

6.

assembly 810029634 JUG6.690.417 1

7. AV board assembly 810032621 JUG6.693.150

Remote receive

8.

board assembly 810032625 JUG6.695.204

Key panel board

9.

assembly 810032623 JUG6.694.202

Inside power

10.

supply module 810023889 FSP048-2PI04 Inside power supply module

LCD Panel

11.

12. Remote controller 810034697 G6C52D-C2 Remote controller 1

810035325

810016916 HT190WG1-100

810016919 SVA190WX01TB

JUG8.074.090-0

08

JUG8.081.062-0

07 1

JUG8.074.091-0

08 1

JUG8.071.011-0

05 1

JUG8.078.044-0

05 1

PCB JUG7.820.146

PCB JUG7.820.158

PCB JUG7.820.156

LCD Panel

Breakabl

e

Proporti

on

(‰)

1

0.5

0.5

0.5

3

TBD

This is a reference spare parts list only. Please ask our sales for final

spare part list.

37

Page 38

Chapter5 Factory mode and notice

Data in Factory mode is strictly prohibited to adjust without the

author’s approve because the data is closely relative to TV’s

performance.

1. Factory mode

This mode is mostly used in adjust balance and setup some special data.

2. Enter into factory menu

Entering“2580” continuously after pressed “INPUT”,you can enter

into factory mode menu.

2.1 Factory menu and setup

2.1.1 How to adjusting the factory menu

You can see a software version and its issued date displaying in the LCD TV.

Use “UP” /“DOWN” keys selecting the item and “LEFT”/“RIGHT”

Keys debugging it.

2.1.2 The following items can be selected and adjusted of the factory

menu about ls16:

Factory Menu

Video Quality

Picture Mode

Contrast

Brightness

Sharpness

Color

Save to EEPROM

White Balance

Source YPbPr

R-Gain

G-Gain

B-Gain

R-Offset

G-Offset

38

Page 39

B-Offset

ADC Auto

MACE Setting

Input Source TV

Color Mode

Color Temp.Red

Color Temp.Green

Color Temp.Blue

Save to EEPROM

Advanced Setting (Don’t adjust this item)

About (software version and its issued date)

The following items can be selected and adjusted of the factory menu about

ls16W:

Video Quality

Picture Mode

Contrast

Brightness

Sharpness

Color

Save to EEPROM

White balance

R-Offset

G-Offset

B-Offset

R-Gain

G-Gain

B-Gain

Save to EEPROM

Factory Option

AGING Mode

Color Temp

Restore Default

(Software version)

YPBPR Phase

Phase

39

Page 40

Save to EEPROM

Chapter 6 The flow of software update and noticeable proceeding

7.1 、The connection of the equipment is shown bellow:

PC usb port

7.2、software update flow

Use the application software ISP_Tool_V4.3.3.exe (the following digit

means the version of this software)

Open this application software, as is shown bellow:

Usb cable VGA cable

Updata Tool

VGA PORT of

LCD TV

7.2.1 First, test the connection

Press the button “Connect”, the computer will display “ Device ”on the screen when it is

well connected ,if not, please check the connection again.

7.2.2 Press button “Read” when the connection is OK to load the software

7.2.3 Press button “Auto” to write the software into the flash

40

Page 41

The softeware will be provided according to custom’s request.

41

Loading...

Loading...