Magellan™

Magellan™

Magellan™Magellan™

Electrical Specification

Electrical Specification

Electrical SpecificationElectrical Specification

Motion Processor

Motion Processor

Motion ProcessorMotion Processor

MC55000

MC55000

MC55000 MC55000

for Pulse and Direction Motion Control

Preliminary

Performance Motion Devices, Inc.

55 Old Bedford Rd

Lincoln, MA 01773

Revision 0.6, November 2003

NOTICE

NOTICE

NOTICENOTICE

This document contains proprietary and confidential information of Performance Motion Devices,

Inc., and is protected by federal copyright law. The contents of this document may not be disclosed

to third parties, translated, copied, or duplicated in any form, in whole or in part, without the express

written permission of PMD.

The information contained in this document is subject to change without notice. No part of this

document may be reproduced or transmitted in any form, by any means, electronic or mechanical,

for any purpose, without the express written permission of PMD.

Copyright 2003 by Performance Motion Devices, Inc.

Magellan and C-Motion are trademarks of Performance Motion Devices, Inc

Warranty

Warranty

WarrantyWarranty

PMD warrants performance of its products to the specifications applicable at the time of sale in

accordance with PMD's standard warranty. Testing and other quality control techniques are utilized

to the extent PMD deems necessary to support this warranty. Specific testing of all parameters of

each device is not necessarily performed, except those mandated by government requirements.

Performance Motion Devices, Inc. (PMD) reserves the right to make changes to its products or to

discontinue any product or service without notice, and advises customers to obtain the latest version

of relevant information to verify, before placing orders, that information being relied on is current

and complete. All products are sold subject to the terms and conditions of sale supplied at the time

of order acknowledgement, including those pertaining to warranty, patent infringement, and

limitation of liability.

Safety Notice

Safety Notice

Safety NoticeSafety Notice

Certain applications using semiconductor products may involve potential risks of death, personal

injury, or severe property or environmental damage. Products are not designed, authorized, or

warranted to be suitable for use in life support devices or systems or other critical applications.

Inclusion of PMD products in such applications is understood to be fully at the customer's risk.

In order to minimize risks associated with the customer's applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent procedural hazards.

Disclaimer

Disclaimer

DisclaimerDisclaimer

PMD assumes no liability for applications assistance or customer product design. PMD does not

warrant or represent that any license, either express or implied, is granted under any patent right,

copyright, mask work right, or other intellectual property right of PMD covering or relating to any

combination, machine, or process in which such products or services might be or are used. PMD's

publication of information regarding any third party's products or services does not constitute PMD's

approval, warranty or endorsement thereof.

MC55000 Electrical Specification – Preliminary 11/14/2003

iii

MC55000 Electrical Specification – Preliminary 11/14/2003

iv

Related Documents

Related Documents

Related DocumentsRelated Documents

MC50000 Motion Processor User’s Guide (MC50000UG)

How to set up and use all members of the MC50000 Motion Processor family.

MC50000 Motion Processor Programmer’s Command Reference (MC50000PR)

Descriptions of all MC50000 Motion Processor commands, with coding syntax and examples,

listed alphabetically for quick reference.

MC50000 Motion Processor Electrical Specifications

Three booklets containing physical and electrical characteristics, timing diagrams, pinouts, and

pin descriptions of each:

MC55000 Series, for stepping motion control (MC55000ES);

MC58000 Series, for brushed and brushless servo, microstepping and stepping motion

control (MC58000ES).

MC50000 Motion Processor Developer’s Kit Manual (DK50000M)

How to install and configure the DK50000 developer’s kit PC board.

MC55000 Electrical Specification – Preliminary 11/14/2003

v

MC55000 Electrical Specification – Preliminary 11/14/2003

vi

Table of Contents

Table of Contents

Table of ContentsTable of Contents

Warranty...................................................................................................................................................... iii

Safety Notice ................................................................................................................................................ iii

Disclaimer..................................................................................................................................................... iii

Related Documents....................................................................................................................................... v

Table of Contents........................................................................................................................................ vii

1 The MC50000 Family................................................................................................................................ 9

1.2 How to Order................................................................................................................................ 11

2 Functional Characteristics...................................................................................................................... 12

2.1 Configurations, parameters, and performance .............................................................................. 12

2.2 Physical characteristics and mounting dimensions....................................................................... 14

2.2.1 CP chip ................................................................................................................................. 14

2.2.2 IO chip .................................................................................................................................. 15

2.3 Environmental and electrical ratings ............................................................................................16

2.4 MC55110 System configuration – Single chip, 1 axis control ..................................................... 16

2.5 MC55020 System configuration – Two chip, 1 to 4 axis control................................................. 17

2.6 Peripheral device address mapping...............................................................................................18

3 Electrical Characteristics........................................................................................................................ 19

3.1 DC characteristics......................................................................................................................... 19

3.2 AC characteristics......................................................................................................................... 19

4 I/O Timing Diagrams .............................................................................................................................. 22

4.1 Clock ............................................................................................................................................ 22

4.2 Quadrature encoder input ............................................................................................................. 22

4.3 Reset ............................................................................................................................................. 22

4.4 Host interface, 8/16 mode............................................................................................................. 23

4.4.1 Instruction write, 8/16 mode................................................................................................. 23

4.4.2 Data write, 8/16 mode...........................................................................................................23

4.4.3 Data read, 8/16 mode............................................................................................................24

4.4.4 Status read, 8/16 mode..........................................................................................................24

4.5 Host interface, 16/16 mode........................................................................................................... 25

4.5.1 Instruction write, 16/16 mode............................................................................................... 25

4.5.2 Data write, 16/16 mode......................................................................................................... 25

4.5.3 Data read, 16/16 mode.......................................................................................................... 26

4.5.4 Status read, 16/16 mode........................................................................................................ 26

4.6 External memory timing............................................................................................................... 27

4.6.1 External memory read........................................................................................................... 27

4.6.2 External memory write ......................................................................................................... 28

4.7 Peripheral device timing............................................................................................................... 29

4.7.1 Peripheral device read........................................................................................................... 29

4.7.2 Peripheral device write .........................................................................................................30

5 Pinouts and Pin Descriptions.................................................................................................................. 31

5.1 Pinouts for the MC55110 ............................................................................................................. 31

5.1.1 MC55110 CP chip pin description........................................................................................ 32

MC55000 Electrical Specification – Preliminary 11/14/2003

vii

Pinouts for the MC55420 ............................................................................................................. 36

5.2

5.2.1 MC55020 IO chip pin description........................................................................................ 37

5.2.2 MC55020 CP chip pin description........................................................................................ 40

5.3 External oscillator filter ................................................................................................................ 43

MC55000 Electrical Specification – Preliminary 11/14/2003

viii

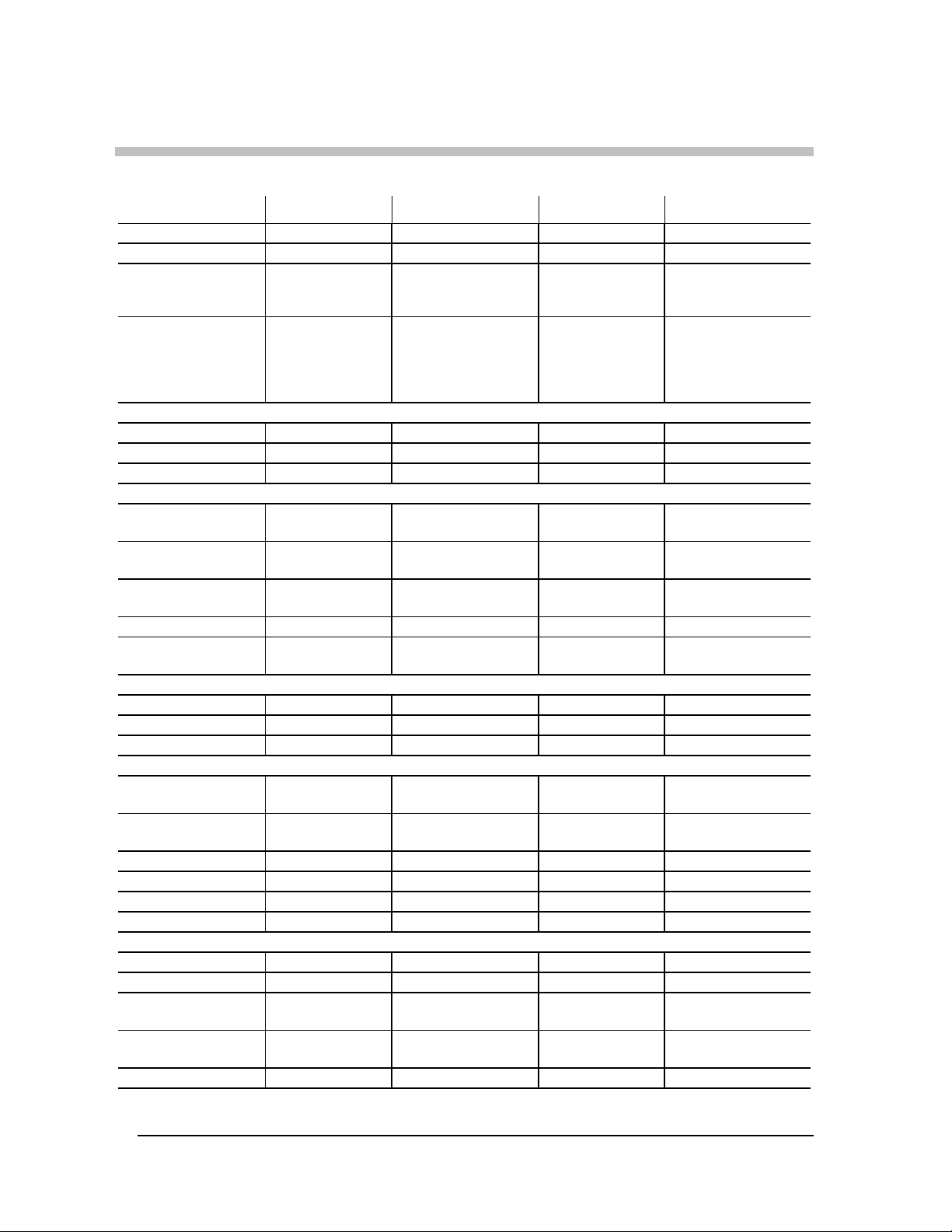

1111 The MC50000 Family

The MC50000 Family

The MC50000 FamilyThe MC50000 Family

MC55020 Series

Number of axes

Number of chips

Motor type

Output format

Parallel

Asynchronous serial

CAN 2.0B

Incremental encoder

input

Parallel word device

input

Index & Home

signals

Position capture

Directional limit

switches

PWM output Parallel DAC output SPI DAC output -

Pulse & direction

output

Trapezoidal

profiling

S-curve profiling

Velocity profiling

Electronic gearing

On-the-fly changes

PID position loop Dual encoder loop Derivative sampling

time

Feedforward (accel

& vel)

Dual bi-quad filter -

MC55020 Series MC58020 Series

MC55020 SeriesMC55020 Series

4,3,2 or 1 4,3,2 or 1 1 1

2 (CP and IO) 2 (CP and IO) 1 (CP) 1 (CP)

Stepping

Pulse and direction

MC58020 Series MC55110

MC58020 SeriesMC58020 Series

Brushed DC servo

Brushless DC servo

Stepping

Brushed single phase

Sinusoidal

commutation

Microstepping

Pulse and direction

Communication interface

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

Position input

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

Motor command output

√√√√

√√√√

√√√√

Trajectory generation

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

Servo filter

√√√√

√√√√

-

-

√√√√

√√√√

√√√√

MC55110 MC58110

MC55110MC55110

Stepping

Pulse and direction

-

-

-

-

-

-

-

-

MC58110

MC58110MC58110

Brushed DC servo

Brushless DC servo

Brushed single phase

Sinusoidal

commutation

Microstepping

Pulse and direction

Stepping

√√√√

√√√√

√√√√

√√√√

√√√√

√√√√

√√√√

√√√√

MC55000 Electrical Specification – Preliminary 11/14/2003

9

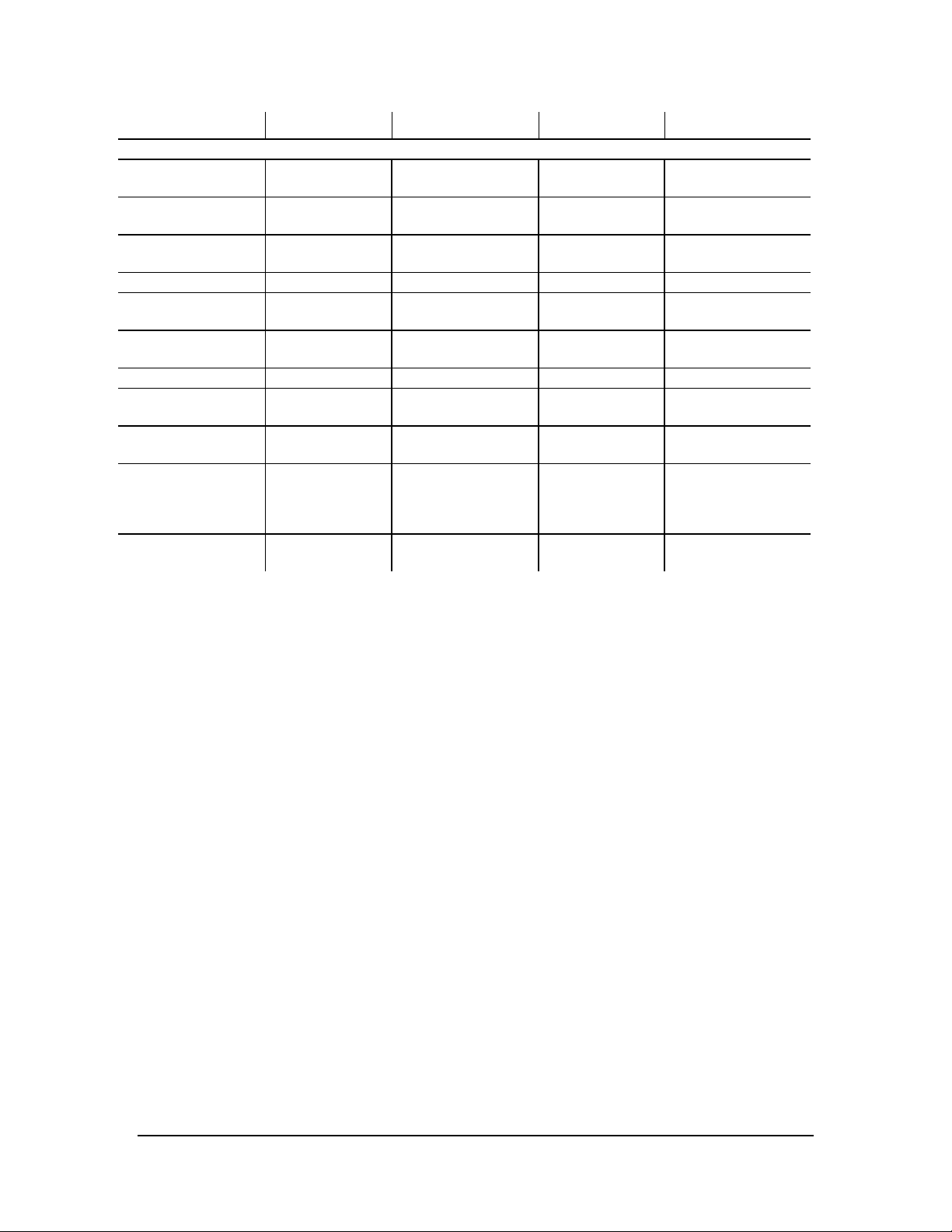

MC55020 Series

Data

trace/diagnostics

Motion error

detection

Axis settled

indicator

Analog input

Programmable bit

output

Software-invertible

signals

User-defined I/O

External RAM

support

Multi-chip

synchronization

Chipset part

numbers

Developer's Kit

p/n's:

MC55020 Series MC58020 Series

MC55020 SeriesMC55020 Series

√√√√ √√√√ √√√√ √√√√

(with encoder)

√√√√

(with encoder)

√√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

√√√√ √√√√ √√√√ √√√√

MC55120

MC55220

MC55320

MC55420

DK55420 DK58420 DK55110 DK58110

MC58020 Series MC55110

MC58020 SeriesMC58020 Series

Miscellaneous

√√√√

√√√√

MC58120

MC58220

MC58320

MC58420

MC55110 MC58110

MC55110MC55110

√√√√ (with encoder)

√√√√ (with encoder)

MC55110 MC58110

MC58110

MC58110MC58110

√√√√

√√√√

Introduction

This manual describes the operational characteristics of the MC55000 Series Motion Processors from

PMD. These devices are members of PMD’s third-generation motion processor family.

Each of these devices is a complete chip-based motion processor. They provide trajectory

generation, related motion control functions and high-speed pulse and direction outputs. Together

these products provide a software-compatible family of dedicated motion processors that can handle

a large variety of system configurations.

Each of these chips utilize a similar architecture, consisting of a high-speed computation unit, along

with an ASIC (Application Specific Integrated Circuit). The computation unit contains special onboard hardware that makes it well suited for the task of motion control.

Along with similar hardware architecture these chips also share most software commands, so that

software written for one series may be re-used with another, even though the type of motor may be

different.

MC55000 Electrical Specification – Preliminary 11/14/2003

10

Family Summary

MC55000 Series – These chipsets provide high-speed pulse and direction signals for step motor

systems. For the MC55020 series two TQFP ICs are required: a 100-pin Input/Output (IO) chip,

and a 144-pin Command Processor (CP) chip, while the MC55110 has all functions integrated into a

single chip a 144-pin Command Processor (CP) chip.

MC58000 Series – This series outputs motor commands in Sign/Magnitude PWM or DACcompatible format for use with DC-Brush motors or Brushless DC motors having external

commutation; two-phase or three-phase sinusoidally commutated motor signals in PWM or DACcompatible format for brushless servo motors; pulse and direction output for step motors; and two

phase signals per axis in either PWM or DAC-compatible signals for microstepping motors.

For the MC58020 series two TQFP ICs are required: a 100-pin Input/Output (IO) chip, and a 144pin Command Processor (CP) chip, while the MC58110 has all functions integrated into a single 144pin CP chip.

1.2 How to Order

When ordering a single-chip configuration, only the CP part number is necessary. For two-IC and

multi-axis configurations, both the CP and the IO part numbers are required.

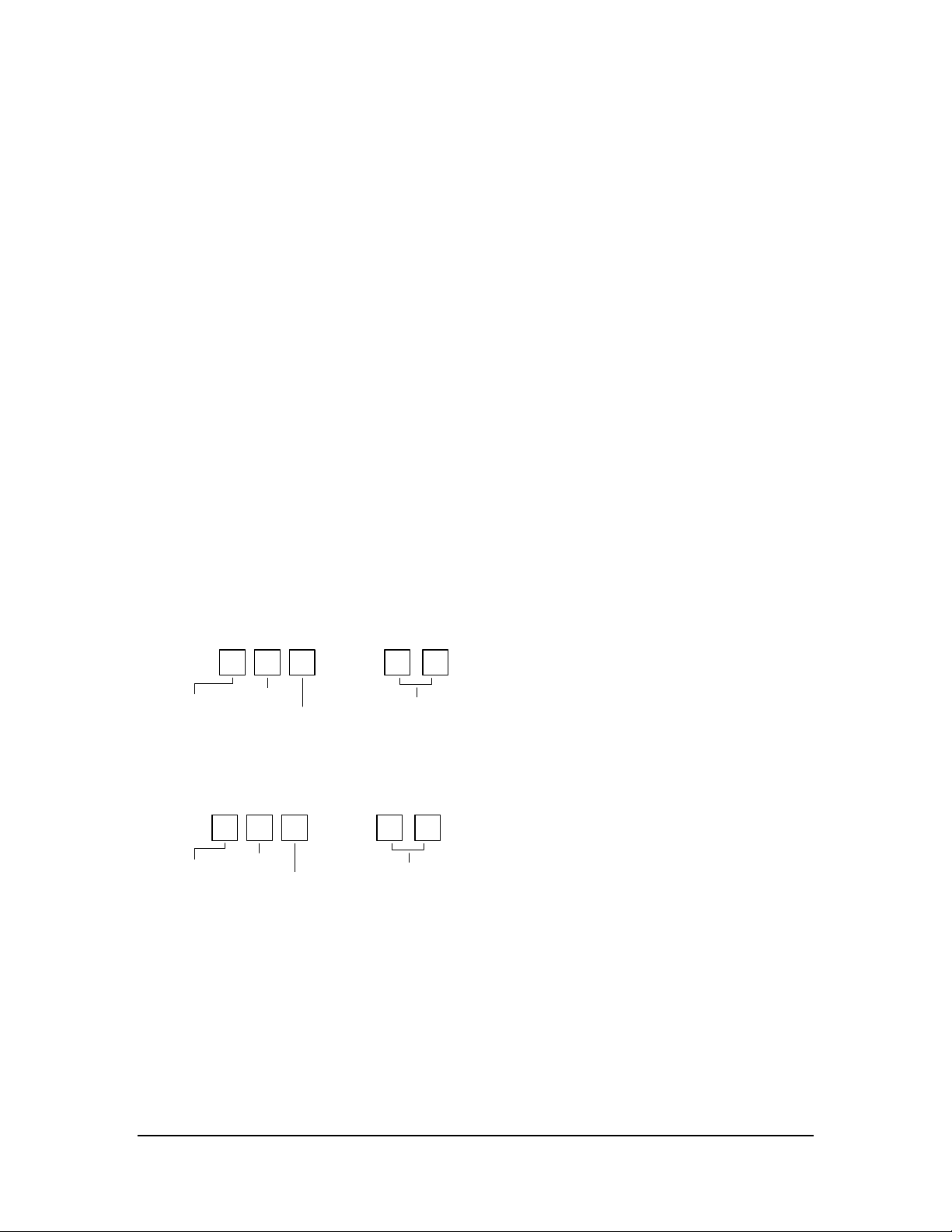

CP (1 or 2 chip configurations)

MC5 0CP .

Motor Type

8 = Multi Motor

5 = Pulse & Direction

# Axes

1,2,3,4

# Chips

1 (CP only)

2 (CP & IO)

CP Version

(Call PMD)

IO (2 chip configurations only)

MC50000IO

Developer’s Kit

DK5 0CP . 50000IO

Motor Type

8 = Multi Motor

5 = Pulse & Direction

# Axes

1,2,3,4

# Chips

1 (CP only)

2 (CP & IO)

CP Version

(Call PMD)

MC55000 Electrical Specification – Preliminary 11/14/2003

11

2222 Functional Characteristics

Functional Characteristics

Functional CharacteristicsFunctional Characteristics

2.1 Configurations, parameters, and performance

Configuration

Configuration

ConfigurationConfiguration

Operating modes

Operating modes

Operating modesOperating modes

Communication modes

Communication modes

Communication modesCommunication modes

Serial port baud rate range

Serial port baud rate range

Serial port baud rate rangeSerial port baud rate range

Profile modes

Profile modes

Profile modesProfile modes

Position range

Position range

Position rangePosition range

Velocity range

Velocity range

Velocity rangeVelocity range

Acceleration and deceleration

Acceleration and deceleration

Acceleration and deceleration Acceleration and deceleration

ranges

ranges

rangesranges

Jerk rang

Jerk rangeeee

Jerk rangJerk rang

Electronic gear ratio range

Electronic gear ratio range

Electronic gear ratio rangeElectronic gear ratio range

Position error tracking

Position error tracking

Position error trackingPosition error tracking

Motor output modes

Motor output modes

Motor output modesMotor output modes

Maximum encoder rate

Maximum encoder rate

Maximum encoder rateMaximum encoder rate

Parallel encoder word size

Parallel encoder word size

Parallel encoder word sizeParallel encoder word size

4 axes (MC55420)

3 axes (MC55320)

2 axes (MC55220)

1 axis (MC55120 or MC55110)

Open loop (pulse generator is driven by trajectory generator output, encoder input used

for stall detection)

8/16 parallel 8 bit external parallel bus with 16 bit command word size

16/16 parallel 16 bit external parallel bus with 16 bit command word size

Point to point asynchronous serial

Multi-drop asynchronous serial

CAN bus 2.0B, protocol co-exists with CANOpen

1,200 baud to 416,667 baud

S-curve point-to-point Velocity, acceleration, jerk, and position parameters

Trapezoidal point-to-point Velocity, acceleration, deceleration, and position

parameters

Velocity-contouring Velocity, acceleration, and deceleration parameters

Electronic Gear Encoder or trajectory position of one axis used to drive a

second axis. Master and slave axes and gear ratio

parameters

External All commanded profile parameters are generated by the

host and stored in external RAM

-2,147,483,648 to +2,147,483,647 steps

-32,768 to +32,767 steps per cycle

with a resolution of 1/65,536 steps per cycle

0 to +32,767 steps per cycle2

with a resolution of 1/65,536 steps per cycle

0 to ½ steps per cycle

with a resolution of 1/4,294,967,296 steps per cycle 3

-32,768 to +32,767 with a resolution of 1/65,536 (negative and positive direction)

Motion error window Allows axis to be stopped upon exceeding programmable

window

Tracking window Allows flag to be set if axis exceeds a programmable

position window

Axis settled Allows flag to be set if axis exceeds a programmable

position window for a programmable amount of time after

trajectory motion is compete

Step and Direction (4.98 Mpulses/sec maximum)

Incremental (up to 10 Mcounts/sec)

Parallel-word (up to 160 Mcounts/sec)

16 bits

3

2

MC55000 Electrical Specification – Preliminary 11/14/2003

12

Parallel encoder

Parallel encoder read rate

Parallel encoderParallel encoder

Cycle timing range

Cycle timing range

Cycle timing rangeCycle timing range

Minimum cycle time

Minimum cycle time

Minimum cycle timeMinimum cycle time

Limit switches

Limit switches

Limit switchesLimit switches

Position

Position----capture triggers

PositionPosition

Other digital signals (per axis)

Other digital signals (per axis)

Other digital signals (per axis)Other digital signals (per axis)

Software

Software----invertable signals

SoftwareSoftware

Analog input

Analog input

Analog inputAnalog input

User defin

User defined discrete I/O

User definUser defin

RAM/external memory

RAM/external memory

RAM/external memory RAM/external memory

support

support

supportsupport

Trace modes

Trace modes

Trace modesTrace modes

Maximum number of trace

Maximum number of trace

Maximum number of trace Maximum number of trace

variables

variables

variablesvariables

Numbe

Number of traceable variables

r of traceable variables

NumbeNumbe

r of traceable variablesr of traceable variables

Number of host instructions

Number of host instructions

Number of host instructionsNumber of host instructions

read rate

read rate read rate

capture triggers

capture triggerscapture triggers

invertable signals

invertable signalsinvertable signals

ed discrete I/O

ed discrete I/Oed discrete I/O

20 kHz (reads all axes every 50 µsec)

51.2 microseconds to 1.048576 seconds

51.2 microseconds

2 per axis: one for each direction of travel

2 per axis: index and home signals

1 AxisIn signal per axis, 1 AxisOut signal per axis

Encoder A, Encoder B, Index, Home, AxisIn, AxisOut, PositiveLimit, NegativeLimit

8 10-bit analog inputs

256 16-bit wide user defined I/O

65,536 blocks of 32,768 16 bit words per block. Total accessible memory is

2,147,483,648 16 bit words

one-time

continuous

4

19

103

MC55000 Electrical Specification – Preliminary 11/14/2003

13

2.2 Physical characteristics and mounting dimensions

2.2.1 CP chip

All dimensions are in millimeters.

MC55000 Electrical Specification – Preliminary 11/14/2003

14

2.2.2 IO chip

All dimensions are in millimeters.

MC55000 Electrical Specification – Preliminary 11/14/2003

15

2.3 Environmental and electrical ratings

Storage Temperature (T

Storage Temperature (T

Storage Temperature (TStorage Temperature (T

Operating Temperature: Standard (T

Operating Temperature: Standard (T

Operating Temperature: Standard (TOperating Temperature: Standard (T

Operating Temperature: Extended (T

Operating Temperature: Extended (T

Operating Temperature: Extended (TOperating Temperature: Extended (T

Power Dissipation (P

Power Dissipation (P

Power Dissipation (PPower Dissipation (P

ssss

)

aaaa

)

aaaa

)

dddd

)

-65 °C to 150 °C

-40 °C to 85 °C*

-40 °C to 125 °C*

CP 445 mW

IO 110 mW

Nominal Clock Frequency (F

Nominal Clock Frequency (F

Nominal Clock Frequency (FNominal Clock Frequency (F

Su

Supply Voltage limits (V

pply Voltage limits (V

SuSu

pply Voltage limits (Vpply Voltage limits (V

Supply Voltage operating range (V

Supply Voltage operating range (V

Supply Voltage operating range (VSupply Voltage operating range (V

clk

clk

)

clkclk

cc

cc

)

cccc

cc

cc

)

cccc

40.0 MHz

-0.3V to +4.6V

3.0V to 3.6V

2.4 MC55110 System configuration – Single chip, 1 axis control

The following figure shows the principal control and data paths in an MC55110 system.

CANOpen/CAN 2.0B network

Host

Serial network

HostIntrpt

Parallel port

40 MHz clock

HostData0-15

Parallel Communication

HostRdy

~HostSlct

PLD/FPGA

~HostRead

~HostWrite

16 bit data/address bus

HostCmd

2

0

M

Serial port configuration

CAN bus configuration

Parallel word i nput

Home

k

o

H

c

c

l

z

AxisOut

External me moryUser I/O

CP

AxisIn

Positive

Limit

switches

Negative

Pulse & Direction Output

Motor

Amplifier

Index

B

A

Analog inputs

The shaded area shows the CPLD/FPGA that must be provided by the designer if parallel

communication is required. A description and the necessary logic (in the form of schematics) of this

device are detailed in section Parallel FPGA of this manual.

Encoder

MC55000 Electrical Specification – Preliminary 11/14/2003

16

The CP chip is a self-contained motion processor. In addition to handling all system functions, the

CP chip contains the profile generator, which calculates velocity, acceleration, and position values for

a trajectory. Then the CP chip generates step and direction signals.

Optional axis position information returns to the motion processor in the form of encoder feedback

using either the incremental encoder input signals, or via the bus as parallel word input.

The MC55110 can co-exist in a CANOpen network as a slave device. It is CAN 2.0B compliant.

2.5 MC55020 System configuration – Two chip, 1 to 4 axis control

The following figure shows the principal control and data paths in an MC55020 system.

Host

Serial network

CANOpen/CAN 2.0B network

Parallel port

40 MHz

clock

HostRdy

~HostSlct

HostData0-15

HostCmd

~HostRead

~HostWrite

20MHz clock

HostIntrpt

IO CP

A

B

Index

Home

Encoder

Pulse & Direction Output

Motor amplif ier

The IO chip contains the parallel host interface, the incremental encoder input along with pulse and

direction motor output signals.

The CP chip contains the profile generator, which calculates velocity, acceleration, and position

values for a trajectory and communicates the results to the IO chip for output.

Optional axis position information returns to the motion processor in the form of encoder feedback

using either the incremental encoder input signals, or via the bus as parallel word input.

The MC55020 can co-exist in a CANOpen network as a slave device. It is CAN 2.0B compliant.

16-bit data bus

Serial port configuration

CAN bus configuration

Parallel word input

Other user devices

AxisIn

AxisOut

External me mory

User I/O

Positive

Limit

switches

Negative

Analog inpu ts

MC55000 Electrical Specification – Preliminary 11/14/2003

17

2.6 Peripheral device address mapping

Device addresses on the CP chip’s external bus are memory-mapped to the following locations:

Address Device Description

0200h Serial port configuration Contains the configuration data (transmission rate,

0400h CAN port configuration Contains the configuration data (baud rate and node

0800h Parallel-word encoder Base address for parallel-word feedback devices

1000h User-defined Base address for user-defined I/O devices

2000h RAM page pointer Page pointer to external memory

8000h Reserved

parity, stop bits, etc) for the asynchronous serial port

ID) for the CAN controller

MC55000 Electrical Specification – Preliminary 11/14/2003

18

3333 Electrical Characteristics

Electrical Characteristics

Electrical Characteristics Electrical Characteristics

3.1 DC characteristics

(Vcc and Ta per operating ratings, F

Symbol Parameter Minimum Maximum Conditions

Vcc Supply Voltage 3.00 V 3.6 V

Idd Supply Current 135 mA CP

Vih Logic 1 input voltage 2.0 V Vcc @CP

Vil Logic 0 input voltage 0.8 V @CP

Voh Logic 1 Output Voltage 2.4 V -2 mA@CP

Vol Logic 0 Output Voltage 0.4 V 8 mA@CP

I

Tri-State output leakage current

out

Iin Input current

I

Input current, CPClk

inclk

Cio Input/Output capacitance 2/3 pF

= 40.0 MHz)

clk

Input Voltages

Output Voltages

Other

-2 µA 2 µA

-25 µA 25 µA

-25 µA 25 µA

open outputs

33 mA IO

@CP

0 < V

< Vcc

out

@CP

< Vcc

0 < V

i

0 < Vi < Vcc

@CP typical

Zai Analog input source impedance

E

Differential nonlinearity error.

dnl

Difference between the step width

and the ideal value.

E

Integral nonlinearity error.

inl

Maximum deviation from the best

straight line through the ADC

transfer characteristics, excluding

the quantization error.

3.2 AC characteristics

See timing diagrams, Section 4, for Tn numbers. The symbol “~” indicates active low signal.

Timing Interval Tn Minimum Maximum

Clock Frequency (F

Clock Pulse Width T1 20 nsec 30 nsec

Clock Period (note 3) T2 50 nsec 250 nsec

Encoder Pulse Width T3 150 nsec

Dwell Time Per State T4 75 nsec

) 4 MHz 40 MHz (note 1)

clk

Analog Input

10Ω

-1 ±2 LSB

±2 LSB

MC55000 Electrical Specification – Preliminary 11/14/2003

19

Timing Interval Tn Minimum Maximum

Index Setup and Hold (relative to Quad A

and Quad B low)

~HostSlct Hold Time T6 0 nsec

~HostSlct Setup Time T7 0 nsec

HostCmd Setup Time T8 0 nsec

HostCmd Hold Time T9 0 nsec

Read Data Access Time T10 25 nsec

Read Data Hold Time T11 10 nsec

~HostRead High to HI-Z Time T12 20 nsec

HostRdy Delay Time T13 100 nsec 150 nsec

~HostWrite Pulse Width T14 70 nsec

Write Data Delay Time T15 25 nsec

Write Data Hold Time T16 0 nsec

Read Recovery Time (note 2) T17 60 nsec

Write Recovery Time (note 2) T18 60 nsec

Read Pulse Width T19 70 nsec

External Memory Read Timing

ClockOut low to control valid T20 4 nsec

ClockOut low to address valid T21 8 nsec

Address valid to ~ReadEnable low T22 31 nsec

ClockOut high to ~ReadEnable low T23 5 nsec

Data access time from Address valid T24 40 nsec

Data access time from ~ReadEnable low T25 31 nsec

Data hold time T26 0 nsec

ClockOut low to control inactive T27 5 nsec

Address hold time after ClockOut low T28 2 nsec

ClockOut low to Strobe low T29 5 nsec

ClockOut low to Strobe high T30 6 nsec

W/~R low to R/~W rising delay time T31 5 nsec

External Memory Write Timing

ClockOut high to control valid T32 4 nsec

ClockOut high to address valid T33 10 nsec

Address valid to ~WriteEnable low T34 29 nsec

ClockOut low to ~WriteEnable low T35 6 nsec

Data setup time before ~WriteEnable high T36 33 nsec

Data bus driven from ClockOut low T37 -3 nsec

Data hold time T38 2 nsec

ClockOut high to control inactive T39 5 nsec

Address hold time after ClockOut low T40 -5 nsec

ClockOut low to Strobe low T41 6 nsec

ClockOut low to Strobe high T42 6 nsec

R/~W low to W/~R rising delay time T43 5 nsec

ClockOut high to control valid T44 6 nsec

Peripheral Device Read Timing

Address valid to ~ReadEnable low T22-45 56 nsec

Data access time from Address valid T24-46 65 nsec

Data access time from ~ReadEnable low T25-47 56 nsec

T5 0 nsec

MC55000 Electrical Specification – Preliminary 11/14/2003

20

Timing Interval Tn Minimum Maximum

Peripheral Device Write Timing

Address valid to ~WriteEnable low T34-48 54 nsec

Data setup time before ~WriteEnable high T36-49 58 nsec

Device Ready/ Outputs Initialized T57 1 msec

Note 1 Performance figures and timing information valid at F

information and performance parameters at F

< 40.0 MHz, contact PMD.

clk

= 40.0 MHz only. For timing

clk

Note 2 For 8/16 interface modes only.

Note 3 The clock low/high split has an allowable range of 40-60%.

MC55000 Electrical Specification – Preliminary 11/14/2003

21

4444 I/O Timing Diagrams

I/O Timing Diagrams

I/O Timing DiagramsI/O Timing Diagrams

For the values of Tn, please refer to the table in Section 3.2.

4.1 Clock

MasterClkIn

4.2 Quadrature encoder input

T3

Quad A

Quad B

~Index

4.3 Reset

V

cc

T1 T2

T3

T4 T4

T5

(= ~QuadA * ~QuadB * ~Index)

T1

T5

Index

I/OClk

~RESET

T50

MC55000 Electrical Specification – Preliminary 11/14/2003

22

T57

4.4 Host interface, 8/16 mode

4.4.1 Instruction write, 8/16 mode

T7

~HostSlct

see note

T6

HostCmd

~HostWrite

HostData0-7

HostRdy

Note: If setup and hold times are met, ~HostSlct and HostCmd may be de-asserted at this point.

4.4.2 Data write, 8/16 mode

~HostSlct

T7

T8

T15

T14

T16

T18

T9

see note

T14

T16

Low byteHigh byte

T15

T13

T6

see note

HostCmd

~HostWrite

HostData0-7

HostRdy

T8

see note

T16

T18

T14

T15

T14

High byte

T15

Note: If setup and hold times are met, ~HostSlct and HostCmd may be de-asserted at this

point.

T9

T16

Low byte

T13

MC55000 Electrical Specification – Preliminary 11/14/2003

23

4.4.3 Data read, 8/16 mode

~HostSlct

T7

T6

see note

HostCmd

~HostRead

HostData0-7

High-Z

HostRdy

Note: If setup and hold times are met, ~HostSlct and HostCmd may be de-asserted at this

point.

4.4.4 Status read, 8/16 mode

~HostSlct

T8

T7

T10

T19

High

byte

T11

T12

see note

High-Z

Low byte

T13

T9

High-Z

T6

HostCmd

~HostRead

HostData0-7

T8

T17

T19

T12

High-Z High-Z

T10

High

byte

T11

MC55000 Electrical Specification – Preliminary 11/14/2003

24

Low byte

T9

High-Z

4.5 Host interface, 16/16 mode

4.5.1 Instruction write, 16/16 mode

~HostSlct

HostCmd

T7 T6

~HostWrite

HostData0-15

HostRdy

4.5.2 Data write, 16/16 mode

~HostSlct

HostCmd

T8

T14

T15

T13

T7 T6

T8

T9

T16

T9

~HostWrite

HostData0-15

HostRdy

T14

T15

T13

MC55000 Electrical Specification – Preliminary 11/14/2003

25

T16

4.5.3 Data read, 16/16 mode

~HostSlct

HostCmd

~HostRead

HostData0-15

HostRdy

T7

T8

High-Z

T10

T19

T13

T6

T9

T12

High-Z

T11

4.5.4 Status read, 16/16 mode

~HostSlct

HostCmd

~HostRead

HostData0-15

T7

T8

High-Z

T10

T19

T6

T9

T11

T12

High-Z

MC55000 Electrical Specification – Preliminary 11/14/2003

26

4.6 External memory timing

4.6.1 External memory read

Note: PMD recommends using memory with an access time no greater than 15 nsec.

ClockOut

~RAMSlct

Addr0-Addr15

W/~R

R/~W

~ReadEnable

Data0-Data15

T31

T23

T20

T21

T27

T28

T22

T26

T25

T24

~Strobe

T30T29

MC55000 Electrical Specification – Preliminary 11/14/2003

27

4.6.2 External memory write

ClockOut

~RAMSlct

Addr0-Addr15

R/~W

W/~R

~WriteEnable

Data0-Data15

T33

T44

T32

T43

T34

T35

T37

T39

T40

T38

T36

~Strobe

T42T41

MC55000 Electrical Specification – Preliminary 11/14/2003

28

4.7 Peripheral device timing

4.7.1 Peripheral device read

ClockOut

~PeriphSlct

Addr0-Addr15

W/~R

R/~W

~ReadEnable

Data0-Data15

T31

T23

T20

T21

T27

T28

T45

T26

T47

T46

~Strobe

T30T29

MC55000 Electrical Specification – Preliminary 11/14/2003

29

4.7.2 Peripheral device write

ClockOut

~PeriphSlct

Addr0-Addr15

R/~W

W/~R

~WriteEnable

Data0-Data15

T33

T44

T32

T43

T48

T35

T37

T39

T40

T38

T49

T42T41

~Strobe

MC55000 Electrical Specification – Preliminary 11/14/2003

30

5555 Pinouts

Pinouts and Pin Descriptions

Pinouts Pinouts

and Pin Descriptions

and Pin Descriptions and Pin Descriptions

5.1 Pinouts for the MC55110

133

~Reset

~WriteEnable89

93

~ReadEnable

96 ~Strobe

92

R/~W

19

W/~R

120

Ready

82

~PeriphSlct

87

~RAMSlct

25

SrlXmt

26

SrlRcv

72

CANXmt/SrlEnable

70

CANRcv

3530SPIClock

SPIXmt

23 IOInterrupt

123

MasterClkIn

73 ClockOut

Addr0

80

Addr1

78

Addr2

74

Addr3

71

Addr4

68

Addr5

64

Addr6

61

Addr7

57

Addr8

53

Addr9

51

Addr10

48

Addr11

45

Addr12

43

Addr13

39

Addr14

34

Addr15

31

Data0

127

Data1

130

132

Data2

Data3

134

Data4

136

Data5

138

Data6

143

Data7

5

Data8

9

Data9

13

Data10

15

Data11

17

Data12

20

Data13

22

Data14

24

Data15

27

4, 29, 42, 50, 67, 77, 86, 95,

122, 129, 141

VCC

AnalogRefHigh

AnalogRefLow

CP

~ParallelEnable 8

~HostInterrupt

GND

AnalogVcc

AnalogGnd

Analog0

Analog1

Analog2

Analog3

Analog4

Analog5

Analog6

Analog7

PosLim1

NegLim1

AxisOut1

AxisIn1

Pulse1

Direction1

AtRest1

QuadA1

QuadB1

~Home1

QuadAuxA1

QuadAuxB1

Synch

OscFilter1

OscFilter2

Vcc5

Vssf

116

115

114

117

112

113

110

111

107

109

105

108

46

38

32

16

56

54

52

83

79

75

88

81

69~Index1

131

21

11

10

58

12

3, 28, 41, 49, 66, 76, 85, 94, 125,

1, 2, 6, 7, 14, 18, 33, 36, 37, 40,

128, 140

AGND

98, 99, 100, 101,

102, 103, 104, 106

No connection

44, 47, 55, 59, 60, 62, 63, 65,

84, 90, 91, 97, 118, 119, 121,

124, 126, 135, 137, 139, 142,

144

MC55000 Electrical Specification – Preliminary 11/14/2003

31

5.1.1 MC55110 CP chip pin description

Pin Name and number Direction Description

~Reset 133

~WriteEnable 89

~ReadEnable 93

~Strobe 96

R/~W 92

W/~R 19

Ready 120

~PeriphSlct 82

~RAMSlct 87

SrlXmt 25

SrlRcv 26

CANXmt

SrlEnable

CANRcv 70

SPIClock 35

SPIXmt 30

IOInterrupt 23

MasterClkIn 123

ClockOut 73

72

input

output

output

output

output

output

input

output

output This signal is low when external memory is being accessed.

output This pin outputs serial data from the asynchronous serial port.

input This pin inputs serial data to the asynchronous serial port.

output

output This pin receives serial data from the CAN transceiver.

output

output This pin transmits synchronous serial data to the serial DAC(s).

input

input

output

CP

This is the master reset signal. When brought low, this pin resets the chipset to its

initial conditions.

This signal is the write-enable strobe. When low, this signal indicates that data is

being written to the bus.

This signal is the read-enable strobe. When low, this signal indicates that data is

being read from the bus.

This signal is low when the data and address are valid during CP

communications. If the parallel interface is used, this pin should be connected

to the PLD/FPGA IO chip signal

This signal is high when the CP chip is performing a read, and low when it is

performing a write. If the parallel interface is used, this pin should be connected

to the PLD/FPGA IO chip signal

This signal is the inverse of

some decode circuits and devices this is more convenient than

Ready can be pulled low to add wait states for external accesses. Ready indicates

that an external device is prepared for a bus transaction to be completed. If the

device is not ready, it pulls the

one cycle and checks

Ready again.

This signal can be left unconnected if it is not used.

This signal is low when peripheral devices on the data bus are being addressed. If

the parallel interface is used, this pin should be connected to the PLD/FPGA

IO chip signal

CPPeriphSlct.

When the CAN host interface is used, this pin transmits serial data to the CAN

transceiver.

When the multi-drop serial interface is used, this pin sets the serial port enable

line and the CANXmt function is not available. SrlEnable is high during

transmission for the multi-drop protocol and low at all other times.

This pin is the clock signal used for strobing synchronous serial data to the serial

DAC(s). This signal is only active when SPI data is being transmitted.

This interrupt signal is used for IO to CP communication. If the parallel

interface is used, this pin should be connected to the PLD/FPGA IO chip signal

CPInterrupt.

This signal can be left unconnected if it is not used.

This is the clock signal for the Motion Processor. It is driven at a nominal

20MHz.

This signal is the reference output clock. Its frequency is twice the frequency of

the input clock (which is normally 20MHz) resulting in a nominal output

frequency of 40MHz.

CPStrobe.

CPR/~W.

R/~W; it is high when R/~W is low, and vice versa. For

R/~W.

Ready pin low. The motion processor then waits

MC55000 Electrical Specification – Preliminary 11/14/2003

32

Pin Name and number Direction Description

Addr0

Addr1

Addr2

Addr3

Addr4

Addr5

Addr6

Addr7

Addr8

Addr9

Addr10

Addr11

Addr12

Addr13

Addr14

Addr15

Data0

Data1

Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

Data12

Data13

Data14

Data15

AnalogVcc 116

AnalogRefHigh 115

AnalogRefLow 114

AnalogGND 117

Analog0

Analog1

Analog2

Analog3

Analog4

Analog5

Analog6

Analog7

80

78

74

71

68

64

61

57

53

51

48

45

43

39

34

31

127

130

132

134

136

138

143

5

9

13

15

17

20

22

24

27

112

113

110

111

107

109

105

108

output

bi-directional

input

input

input

input

input

Multi-purpose address lines. These pins comprise the CP chip’s external address

bus, used to select devices for communication over the data bus. If the parallel

interface is used, pins

PLD/FPGA IO chip signals

communicate between the CP and IO chips.

Other address pins may be used for DAC output, parallel word input, or userdefined I/O operations. See the User’s Guide for a complete memory map.

Multi-purpose data lines. These pins comprise the CP chip’s external data bus,

used for all communications with peripheral devices such as external memory or

DACs. They may also be used for parallel-word input and for user-defined I/O

operations.

If the parallel interface is used, these pins should be connected to the

PLD/FPGA IO chip signals

Analog input Vcc. This pin should be connected to the analog input supply

voltage, which must be in the range 3.0-3.6 V.

If the analog input circuitry is not used, this pin should be tied to V

Analog high voltage reference for A/D input. The allowed range is

AnalogVcc.

to

If the analog input circuitry is not used, this pin should be tied to V

Analog low voltage reference for A/D input. The allowed range is

AnalogRefHigh.

If the analog input circuitry is not used, this pin should be tied to GND.

Analog input ground. This pin should be connected to the analog input power

supply return.

If the analog input circuitry is not used, this pin should be tied to GND.

These signals provide general-purpose analog voltage levels which are sampled

by an internal A/D converter. The A/D resolution is 10 bits.

The allowed signal input range is

Any unused pins should be tied to AnalogGND.

If the analog input circuitry is not used, these pins should be tied to GND.

CP

Addr0, Addr1, and Addr15 should be connected to the

CPAddr0, CPAddr1 and CPAddr15. They are used to

CPData0-15.

AnalogRefLow to AnalogRefHigh.

.

cc

AnalogRefLow

.

cc

AnalogGND to

MC55000 Electrical Specification – Preliminary 11/14/2003

33

Pin Name and number Direction Description

PosLim1 46

NegLim1 38

AxisOut1 32

AxisIn1 16

Pulse1 56

Direction1 54

AtRest1 52

QuadA1

QuadB1

~Home1 75

QuadAuxA1

QuadAuxB1

~Index1

83

79

88

81

69

input

input

output This pin can be programmed to track the state of any bit in the status registers.

input This pin is a general-purpose input that can also be used as a breakpoint input.

output

output

output

input

input

input

This signal provides input from the positive-side (forward) travel limit switch.

On power-up or after reset this signal defaults to active low interpretation, but

the interpretation can be set to active high interpretation using the

SetSignalSense instruction.

If this pin is not used it may be left unconnected.

This signal provides input from the negative-side (reverse) travel limit switch.

On power-up or after reset this signal defaults to active low interpretation, but

the interpretation can be set to active high interpretation using the

SetSignalSense instruction.

If this pin is not used it may be left unconnected.

If this pin is not used it may be left unconnected.

If this pin is not used it may be left unconnected.

This pin provides the pulse (step) signal to the motor. A step occurs when the

signal transitions from a high to a low state. This default behavior can be changed

to a low to high state transition using the command

If this pin is not used it may be left unconnected.

This pin indicates the direction of motion and works in conjunction with the

pulse signal. A high level on this signal indicates a positive direction move and a

low level indicates a negative direction move.

This signal indicates that the axis is at rest and the step motor can be switched to

low power or standby mode. A high level on this signal indicates the axis is at

rest while a low signal indicates the axis is in motion.

These pins should be connected to the A and B quadrature signals from the

incremental encoder. When the axis is moving in the positive (forward)

direction, signal A leads signal B by 90°.

The theoretical maximum encoder pulse rate is 5.1 MHz. Actual maximum rate

will vary, depending on signal noise.

NOTE: Many encoders require a pull-up resistor on each signal to establish a

proper high signal. Check your encoder’s electrical specification.

If these pins are not used they may be left unconnected.

This pin provides the home signal, a general-purpose input to the position

capture mechanism. A valid home signal is recognized by the motion processor

when

~Home transitions from high to low.

If this pin is not used it may be left unconnected.

If index capture is required, the encoder A and B signals connected to

and QuadB1 signals must also be connected to QuadAuxA1 and QuadAuxB1.

The index pin should be connected to the index signal from the incremental

encoder. A valid index pulse is recognized by the motion processor when this

signal transitions from high to low.

If these pins are not used they may be left unconnected.

CP

SetSignalSense.

QuadA1

WARNING! There is no internal gating of the index signal with

the encoder A and B inputs. This must be performed externally if

desired. Refer to the Application Notes section at the end of this

manual for an example.

MC55000 Electrical Specification – Preliminary 11/14/2003

34

Pin Name and number Direction Description

ParallelEnable 8

input

This signal enables/disables the parallel communication with the host. If this

signal is tied high, the parallel interface is enabled. If this signal is tied low the

parallel interface is disabled. Contact PMD for more information on parallel

communication.

WARNING! This signal should only be tied high if an external

logic device that implements the parallel communication logic is

included in the design.

CP

~HostInterrupt 131

Synch 21

OscFilter1

OscFilter2

V

58

cc5

V

12

ssf

Vcc

11

10

4, 29, 42, 50, 67, 77,

output When low, this signal causes an interrupt to be sent to the host processor.

input/output

86, 95, 122, 129, 141

GND

3, 28, 41, 49, 66, 76,

85, 94, 125, 128, 140

AGND

98, 99, 100, 101, 102,

103, 104, 106

No connection

1, 2, 6, 7, 14, 18, 33,

36, 37, 40, 44, 47, 55,

59, 60, 62, 63, 65, 84,

90, 91, 97, 118, 119,

121, 124, 126, 135,

137, 139, 142, 144

This pin is the synchronization signal. In the disabled mode, the pin is

configured as an input and is not used. In the master mode, the pin outputs a

synchronization pulse that can be used by slave nodes or other devices to

synchronize with the internal chip cycle of the master node. In the slave mode,

the pin is configured as an input and should be connected to the Synch pin on

the master node. A pulse on the pin synchronizes the internal chip cycle to the

signal provided by the master node.

If this pin is not used it may be left unconnected.

These signals connect to the external oscillator filter circuitry. Section 5.3 shows

the required filter circuitry.

This signal can optionally be tied to a 5V logic supply, which is required for

reprogramming the chipset firmware.

This signal must be tied to pin 28 using a bypass capacitor. A ceramic capacitor

with a value between 0.1µF and 0.01µF should be used.

CP digital supply voltage. All of these pins must be connected to the supply

voltage. V

must be in the range 3.0 – 3.6 V.

cc

CP digital supply ground. All of these pins must be connected to the digital

power supply return.

These signals must be tied to AnalogGND.

If the analog input circuitry is not used, these pins must be tied to GND.

These signals must be left unconnected.

MC55000 Electrical Specification – Preliminary 11/14/2003

35

5.2 Pinouts for the MC55420

16, 17, 40, 65, 66, 67, 90

4, 29, 42, 50, 67, 77, 86, 95,

122, 129, 141

100

81

92

94

77

53

54

52

41

43

50

89

24

91

12

10

99

98

11

97

95

76

74

73

75

38

36

35

32

31

8

5

1

2

3

7

6

HostCmd

HostRdy

~HostRead

~HostWrite

~HostSlct

CPInterrupt

CPR/~W

CPStrobe

CPPeriphSlct

CPAddr0

CPAddr1

CPAddr15

MasterClkIn

CPClock

HostMode0

HostMode1

HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

HostData8

HostData9

HostData10

HostData11

HostData12

HostData13

HostData14

HostData15

CPData0

CPData1

CPData2

CPData3

CPData4

4, 9, 22, 34, 46, 57, 64, 72, 84, 96

VCC

IO

GND

No connection

19, 27, 55, 56, 62, 78, 87

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

CPData12

CPData13

CPData14

CPData15

Pulse1

Pulse2

Pulse3

Pulse4

Direction1

Direction2

Direction3

Direction4

AtRest1

AtRest2 86

AtRest3

AtRest4

QuadA1

QuadB1

~Index1

~Home1

QuadA2

QuadB2

~Index2

~Home2

QuadA3

QuadB3

~Index3

~Home3

QuadA4

QuadB4

~Index4

~Home4

37

42

39

18

14

71

13

70

15

69

68

21

85

20

79

61

60

59

26

23

63

80

47

25

49

82

48

44

93

29

33

51

83

88

30

58

28

45

133

~Reset

~WriteEnable89

~ReadEnable

93

96 ~Strobe

92

R/~W

W/~R

19

120

Ready

~PeriphSlct

82

87

~RAMSlct

25

SrlXmt

26

SrlRcv

72

CANXmt/SrlEnable

70

CANRcv

3530SPIClock

SPIXmt

23

IOInterrupt

123

IOClock

73 ClockOut

80

Addr0

78

Addr1

74

Addr2

71

Addr3

68

Addr4

64

Addr5

61

Addr6

57

Addr7

53

Addr8

51

Addr9

48

Addr10

45

Addr11

43

Addr12

39

Addr13

34

Addr14

31

Addr15

127

Data0

130

Data1

132

Data2

134

Data3

136

Data4

138

Data5

143

Data6

Data7

5

9

Data8

13

Data9

15

Data10

17

Data11

20

Data12

22

Data13

24

Data14

27

Data15

VCC

CP

GND

AnalogVcc

AnalogRefHigh

AnalogRefLow

AnalogGnd

Analog0

Analog1

Analog2

Analog3

Analog4

Analog5

Analog6

Analog7

PosLim1

PosLim2

PosLim3

PosLim4

NegLim1

NegLim2

NegLim3

NegLim4

AxisOut1

AxisOut2

AxisOut3

AxisOut4

AxisIn1

AxisIn2

AxisIn3

AxisIn4

~HostInterrupt

Synch

OscFilter1

OscFilter2

Vcc5

Vssf

116

115

114

117

112

113

110

111

107

109

105

108

46

59

65

81

38

55

62

69

32

119

88

54

16

8

52

83

131

21

11

10

58

12

3, 28, 41, 49, 66, 76, 85, 94, 125,

1, 2, 6, 7, 14, 18, 33, 36, 37, 40,

128, 140

AGND

98, 99, 100, 101,

102, 103, 104, 106

No connection

44, 47, 56, 60, 63, 75, 79 , 84,

90, 91, 97, 118, 121, 124, 126,

135, 137, 139, 142, 144

MC55000 Electrical Specification – Preliminary 11/14/2003

36

5.2.1 MC55020 IO chip pin description

Pin Name and Number Direction Description

HostCmd 81

HostRdy 8

~HostRead 92

~HostWrite 100

~HostSlct 94

CPInterrupt 77

CPR/~W 53

CPStrobe 54

CPPeriphSlct 52

CPAddr0

CPAddr1

CPAddr15

MasterClkIn 89

CPClock 24

HostMode0

HostMode1 5 91

41

43

50

input

output

input When ~HostRead is low, a data word is read from the motion processor.

input When ~HostWrite is low, a data word is written to the motion processor.

input

output

input

input

input

input

input

output

input These two signals determine the host communications mode, as follows:

IO

This signal is asserted high to write a host instruction to the motion

processor, or to read the status of the

is asserted low to read or write a data word.

This signal is used to synchronize communication between the motion

processor and the host.

HostRdy (HostReady) will go low indicating host

port busy at the end of a read or write operation according to the

interface mode in use, as follows:

Interface Mode

HostRdy goes

8/16 after the second byte of the instruction word

after the second byte of each data word is transferred

16/16 after the 16-bit instruction word

after each 16-bit data word

HostRdy will go high, indicating that the host port is ready to transmit,

when the last transmission has been processed. All host port

communications must be made with

A typical busy-to-ready cycle is 10 microseconds, but can be substantially

longer, up to 50 microseconds.

~HostSlct is low, the host port is selected for reading or writing

When

operations.

IO chip to CP chip interrupt. It should be connected to CP chip pin 23,

IOInterrupt.

This signal is high when the CP chip is reading data from the IO chip, and

low when it is writing data. It should be connected to CP chip pin 92,

R/~W.

This signal goes low when the data and address become valid during

motion processor communication with peripheral devices on the data

bus, such as external memory or a DAC. It should be connected to CP

chip pin 96,

~Strobe.

This signal goes low when a peripheral device on the data bus is being

addressed. It should be connected to CP chip pin 82,

These signals are high when the CP chip is communicating with the IO

chip (as distinguished from any other device on the data bus). They

should be connected to CP chip pins 80 (

(

Addr15).

This is the master clock signal for the motion processor. It is driven at a

nominal 40 MHz

This signal provides the clock pulse for the CP chip. Its frequency is half

MasterClkIn (pin 89), or 20 MHz nominal. It is connected directly

that of

to the CP chip

HostMode1 HostMode0

IOClock signal (pin 123).

0 0 16/16 parallel (16-bit bus, 16-bit instruction)

0 1 not used

1 0 8/16 parallel (8-bit bus, 16-bit instruction)

1 1 Parallel disabled

HostRdy and HostInterrupt signals. It

low

HostRdy high (ready).

~PeriphSlct.

Addr0), 78 (Addr1), and 31

MC55000 Electrical Specification – Preliminary 11/14/2003

37

Pin Name and Number Direction Description

HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

HostData8

HostData9

HostData10

HostData11

HostData12

HostData13

HostData14

HostData15

CPData0

CPData1

CPData2

CPData3

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

CPData12

CPData13

CPData14

CPData15

Pulse1

Pulse2

Pulse3

Pulse4

Direction1

Direction2

Direction3

Direction4

AtRest1

AtRest2

AtRest3

AtRest4

12

10

99

98

1

11

97

95

76

74

73

75

2

3

7

6

38

36

35

32

31

37

42

39

18

14

71

13

70

15

69

68

21

85

20

79

61

60

59

26

23

86

63

80

bi-directional,

tri-state

bi-directional

output

output

output

These signals transmit data between the host and the motion processor

through the parallel port. Transmission is mediated by the control signals

~HostSelect, ~HostWrite, ~HostRead and HostCmd.

In 16-bit mode, all 16 bits are used (

low-order 8 bits of data are used (

HostMode1 signals select the communication mode this port operates in.

These signals transmit data between the IO chip and pins

CP chip.

These pins provide the pulse (step) signal to the motor. This signal is

always a square wave, regardless of the pulse rate. A step occurs when

the signal transitions from a high state to a low state. This default

behavior can be changed to a low to high state transition using the

command SetSignalSense.

The number of available axes determines which of these signals are valid.

Invalid axis pins may be left unconnected.

These pins indicate the direction of motion and work in conjunction with

the pulse signal. A high level on this signal indicates a positive direction

move and a low level indicates a negative direction move.

The number of available axes determines which of these signals are valid.

Invalid axis pins may be left unconnected.

The AtRest signal indicates the axis is at rest and the step motor can be

switched to low power or standby. A high level on this signal indicates

the axis is at rest. A low signal indicates the axis is in motion.

The number of available axes determines which of these signals are valid.

Invalid axis pins may be left unconnected.

IO

HostData0-15). In 8-bit mode, only the

HostData0-7). The HostMode0 and

Data0-15 of the

MC55000 Electrical Specification – Preliminary 11/14/2003

38

Pin Name and Number Direction Description

QuadA1

QuadB1

QuadA2

QuadB2

QuadA3

QuadB3

QuadA4

QuadB4

47

25

48

44

33

51

30

58

input

These pins provide the A and B quadrature signals for the incremental

encoder for each axis. When the axis is moving in the positive (forward)

direction, signal A leads signal B by 90°.

The theoretical maximum encoder pulse rate is 10.2 MHz. Actual

maximum rate will vary, depending on signal noise.

NOTE: Many encoders require a pull-up resistor on each signal to

establish a proper high signal. Check your encoder’s electrical

specification.

The number of available axes determines which of these signals are valid.

WARNING! If a valid axis pin is not used, its signal should

be tied high.

Invalid axis pins may be left unconnected or connected to ground.

~Index1

~Index2

~Index3

~Index4

49

93

83

28

input

These pins provide the Index quadrature signals for the incremental

encoders. A valid index pulse is recognized by the chipset when

B are all low.

and

The number of available axes determines which of these signals are valid.

WARNING! If a valid axis pin is not used, its signal should

be tied high.

IO

~Index, A,

~Home1

~Home2

~Home3

~Home4

Vcc

GND

Not connected

82

29

88

45

input

16, 17, 40, 65, 66, 67,

90

4, 9, 22, 34, 46, 57, 64,

72, 84, 96

19, 27, 55, 56, 62, 78,

87

Invalid axis pins may be left unconnected or connected to ground.

These pins provide the Home signals, general-purpose inputs to the

position-capture mechanism. A valid Home signal is recognized by the

chipset when

~Homen goes low. These signals are similar to ~Index, but are

not gated by the A and B encoder channels.

The number of available axes determines which of these signals are valid.

WARNING! If a valid axis pin is not used, its signal should

be tied high.

Invalid axis pins may be left unconnected or connected to ground.

All of these pins must be connected to the IO chip digital supply voltage,

which should be in the range 3.0 to 3.6 V.

IO chip ground. All of these pins must be connected to the digital power

supply return.

These pins must be left unconnected (floating).

MC55000 Electrical Specification – Preliminary 11/14/2003

39

5.2.2 MC55020 CP chip pin description

Pin Name and number Direction Description

~Reset 133

~WriteEnable 89

~ReadEnable 93

~Strobe 96

R/~W 92

W/~R 19

Ready 120

~PeriphSlct 82

~RAMSlct 87

SrlXmt 25

SrlRcv 26

CANXmt

SrlEnable

CANRcv 70

SPIClock 35

SPIXmt 30

IOInterrupt 23

IOClock 123

ClockOut 73

72

input

output

output

output

output

output

input

output

output This signal is low when external memory is being accessed.

output This pin outputs serial data from the asynchronous serial port.

input This pin inputs serial data to the asynchronous serial port.

output

output This pin receives serial data from the CAN transceiver.

output

output This pin transmits synchronous serial data to the serial DAC(s).

input

input

output

CP

This is the master reset signal. When brought low, this pin resets the chipset to its

initial conditions.

This signal is the write-enable strobe. When low, this signal indicates that data is

being written to the bus.

This signal is the read-enable strobe. When low, this signal indicates that data is

being read from the bus.

This signal is low when the data and address are valid during CP

communications. It should be connected to IO chip pin 54,

This signal is high when the CP chip is performing a read, and low when it is

performing a write. It should be connected to IO chip pin 53,

This signal is the inverse of

R/~W; it is high when R/~W is low, and vice versa. For

some decode circuits and devices this is more convenient than

Ready can be pulled low to add wait states for external accesses. Ready indicates

that an external device is prepared for a bus transaction to be completed. If the

device is not ready, it pulls the

one cycle and checks

Ready again.

Ready pin low. The motion processor then waits

This signal can be left unconnected if it is not used.

This signal is low when peripheral devices on the data bus are being addressed. It

should be connected to IO chip pin 52,

CPPeriphSlct.

When the CAN host interface is used, this pin transmits serial data to the CAN

transceiver.

When the multi-drop serial interface is used, this pin sets the serial port enable

line and the CANXmt function is not available. SrlEnable is high during

transmission for the multi-drop protocol and low at all other times.

This pin is the clock signal used for strobing synchronous serial data to the serial

DAC(s). This signal is only active when SPI data is being transmitted.

This interrupt signal is used for IO to CP communication. It should be

connected to IO chip pin 77,

CPInterrupt.

This is the CP chip clock signal. It should be connected to IO chip pin 24,

CPClock.

This signal is the reference output clock. Its frequency is the same as the

MasterClkIn signal to the IO chip, nominally 40MHz.

CPStrobe.

CPR/~W.

R/~W.

MC55000 Electrical Specification – Preliminary 11/14/2003

40

Pin Name and number Direction Description

Addr0

Addr1

Addr2

Addr3

Addr4

Addr5

Addr6

Addr7

Addr8

Addr9

Addr10

Addr11

Addr12

Addr13

Addr14

Addr15

Data0

Data1

Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

Data12

Data13

Data14

Data15

AnalogVcc 116

AnalogRefHigh 115

AnalogRefLow 114

AnalogGND 117

Analog0

Analog1

Analog2

Analog3

Analog4

Analog5

Analog6

Analog7

80

78

74

71

68

64

61

57

53

51

48

45

43

39

34

31

127

130

132

134

136

138

143

5

9

13

15

17

20

22

24

27

112

113

110

111

107

109

105

108

output

bi-directional

input

input

input

input

input

Multi-purpose Address lines. These pins comprise the CP chip’s external address

bus, used to select devices for communication over the data bus.

and

Addr15 are connected to the corresponding CPAddr pins on the IO chip, and

are used to communicate between the CP and IO chips.

Other address pins may be used for DAC output, parallel word input, or userdefined I/O operations. See the User’s Guide for a complete memory map.

Multi-purpose data lines. These pins comprise the CP chip’s external data bus,

used for all communications with the IO chip and peripheral devices such as

external memory or DACs. They may also be used for parallel-word input and

for user-defined I/O operations.

Analog input Vcc. This pin should be connected to the analog input supply

voltage, which must be in the range 3.0-3.6 V.

If the analog input circuitry is not used, this pin should be tied to V

Analog high voltage reference for A/D input. The allowed range is

AnalogVcc.

to

If the analog input circuitry is not used, this pin should be tied to V

Analog low voltage reference for A/D input. The allowed range is

AnalogRefHigh.

If the analog input circuitry is not used, this pin should be tied to GND.

Analog input ground. This pin should be connected to the analog input power

supply return.

If the analog input circuitry is not used, this pin should be tied to GND.

These signals provide general-purpose analog voltage levels which are sampled

by an internal A/D converter. The A/D resolution is 10 bits.

The allowed signal input range is

Any unused pins should be tied to AnalogGND.

If the analog input circuitry is not used, these pins should be tied to GND.

CP

AnalogRefLow to AnalogRefHigh.

Addr0, Addr1,

.

cc

AnalogRefLow

.

cc

AnalogGND to

MC55000 Electrical Specification – Preliminary 11/14/2003

41

Pin Name and number Direction Description

PosLim1

PosLim2

PosLim3

PosLim4

NegLim1

NegLim2

NegLim3

NegLim4

AxisOut1

AxisOut2

AxisOut3

AxisOut4

AxisIn1

AxisIn2

AxisIn3

AxisIn4

~HostInterrupt 131

Synch 21

OscFilter1

OscFilter2

V

58

cc5

V

12

ssf

Vcc

GND

AGND

No connection

46

59

65

81

38

55

62

69

32

119

88

54

16

8

52

83

input

input

output

input These are general-purpose inputs that can also be used as a breakpoint input.

output When low, this signal causes an interrupt to be sent to the host processor.

input/output

11

10

4, 29, 42, 50, 67, 77,

86, 95, 122, 129, 141

3, 28, 41, 49, 66, 76,

85, 94, 125, 128, 140

98, 99, 100, 101, 102,

103, 104, 106

1, 2, 6, 7, 14, 18, 33,

36, 37, 40, 44, 47, 56,

60, 63, 75, 79, 84, 90,

91, 97, 118, 121, 124,

126, 135, 137, 139,

142, 144

These signals provide inputs from the positive-side (forward) travel limit

switches. On power-up or after reset these signals default to active low

interpretation, but the interpretation can be set explicitly using the

SetSignalSense instruction.

The number of available axes determines which of these signals are valid.

Invalid or unused pins may be left unconnected.

These signals provide inputs from the negative-side (reverse) travel limit

switches. On power-up or after reset these signals default to active low

interpretation, but the interpretation can be set explicitly using the

SetSignalSense instruction.

The number of available axes determines which of these signals are valid.

Invalid or unused pins may be left unconnected.

Each of these pins can be conditioned to track the state of any bit in the Status

registers associated with its axis.

The number of available axes determines which of these signals are valid.

Invalid or unused pins may be left unconnected.

The number of available axes determines which of these signals are valid.

Invalid or unused pins may be left unconnected.

This pin is the synchronization signal. In the disabled mode, the pin is

configured as an input and is not used. In the master mode, the pin outputs a

synchronization pulse that can be used by slave nodes or other devices to

synchronize with the internal chip cycle of the master node. In the slave mode,

the pin is configured as an input and should be connected to the Synch pin on

the master node. A pulse on the pin synchronizes the internal chip cycle to the

signal provided by the master node.

If this pin is not used it may be left unconnected.