Page 1

Advanced Step Motor

j

Control Chipset

Features

Advanced control of up to 4 step motors

per chipset

High speed pulse and direction output

S-curve, trapezoidal, velocity contouring,

and electronic gearing trajectory modes

Optional incremental encoder feedback

Software & feature compatible with other

versions of PMD's chipset family

Available in 1, 2, or 4 axis configurations

32-bit position, velocity, acceleration and

erk trajectory profile registers

Pulse and direction output for each axis at

up to 1.5 Mpulses/sec

On-the -fly stall detection

Two travel-limit switches per axis

External motion breakpoint per axis

Intelligent easy-to-use packet-oriented

command protocol

Programmable pulse output modes

Chipset Developer's kit available

MC1451A, MC1451A-E

MC1251A, MC1251A-E

MC1151A, MC1151A-E

General Description

The MC1451A is a dedicated motion processor which functions

as a complete chip-based step motor controller . Packaged in a

2-IC chipset, this device performs trajectory generation and

pulse and direction signal generation for use in a wide variety of

stepper-based systems. The MC1451A provides an optional

third IC which allows incremental encoder signal input for

position verificat i on and on-the-fly stall detection. The MC1451A

is available in a one, a two, and a four-axis configuration.

Typical Configuration

Host

Processor

Amp

Amp

MC1451A

(I/O & CP

& ENC)

Amp

Amp

Performance Motion Dev ices, In c. 12 Waltham St. Le xington, M A 02421 te l: 781. 674.98 60 fax: 781.674.9 861

E

M

E

M

(MC1451A, MC1251A

E

M

E

M

Axis 1

Axis 2

only)

Axis 3

(MC1451A only)

Axis 4

(MC1451A only)

The MC1451A is functionally similar to other PMD motion

processors however it is dedicated to the control of step motors,

instead of servo motors. All of these devices provide

sophisticated trajectory generation and synch ronization features

allowing the creation of complex motion sequences.

In addition to pulse and direction circuitry which can output at

up to 1.5 mega pulses per second the chipset provides two limit

switches per axis, a programmabl e external signal b reakpoint

per axis, and an 'At Rest' output signal.

The chipset is controlled by a host processor which interfaces

with the chipset via an 8-bit bi-directional port. Communications

to/from the chi pset consist of packet-oriented messages. A host

interrupt line is provided so tha t t he chipset can signal the host

when special conditions occur such as stall detection.

The chipset is packaged in 2 68-pin PLCC packages. An

optional third 44 pin PLCC chip provides encoder input. All

chips are CMOS and are powered by 5 volts.

Doc. Rev. 12.02, Nov. 1997

www.pmdcorp.com

Page 2

Table of Contents

Product Family Overview.......................................Page 3

Introduction........................................................... Page 3

Family Summary................................................... Page 3

Electrical Characteristics....................................... Page 4

Absolute Maximum Ratings..................................Page 5

Operating Ratings................................................. Page 5

DC Electrical Characteristics................................ Page 5

AC Electrical Characteristics................................Page 5

I/O Timing Diagrams............................................. Page 7

Pinouts....................................................................Page 11

MC1451A.............................................................. Page 11

MC1251A, MC1151A............................................ Page 12

Pin Descriptions.................................................... Page 13

Theory of Operations............................................. Page 17

Trajectory Profile Generation................................ Page 18

S-curve Point to Point....................................... Page 19

Trapezoidal Point to Point.................................Page 20

Velocity Contouring...........................................Page 20

Electronic Gear.................................................Page 21

Trajectory Control................................................. Page 21

Halting The Trajectory......................................Page 21

Motion Complete Status...................................Page 22

Parameter Loading & Updating............................Page 22

Manual Update.................................................Page 22

Breakpoints....................................................... Page 23

External Breakpoints and Homing.................... Page 23

Disabling Automatic Profile Update..................Page 24

Travel Limit Switches............................................ Page 24

Axis Timing........................................................... Page 24

Host Communications .......................................... Page 25

Electrical Interface............................................ Page 25

Packet Format ...................................................Page 25

Packet Checksum.............................................Page 26

Illegal Commands .............................................Page 26

Command Errors...............................................Page 26

Axis Addressing.................................................Page 26

Axis Status............................................................Page 27

Status Word ......................................................Page 27

Miscellaneous Mode Status Word.....................Page 27

Host Interrupts.......................................................Page 28

Pulse & Direction Signal Generation.....................Page 29

Pulse Generation Control...........................................Page 29

At Rest Indicator.........................................................Page 29

Encoder Position Feedback..................................Page 29

Stall Detection............................................................Page 30

Position Error.............................................................Page 30

Recovering From A Motion Error ...............................Page 30

Host Commands .....................................................Page 32

Command Summary.............................................Page 32

Command Reference............................................Page 34

Axis Control.......................................................Page 34

Profile Generation.............................................Page 35

Parameter Update.............................................Page 39

Interrupt Processing..........................................Page 41

Status/Mode......................................................Page 42

Pulse Generation ..............................................Page 43

Encoder.............................................................Page 44

Miscellaneous ...................................................Page 45

Application Notes ...................................................Page 48

ISA bus interfacing................................................Page 48

Performance Motion Devices, Inc. does not assume any responsibility for use of any circuitry described in this manual, nor does it make

any guarantee as to the accuracy of this manual. Performance Motion Devices, Inc. reserves the right to change the circuitry described in

this manual, or the manual itself, at any time.

The components described in this manual are not authorized for use in life-support systems without the express written permission of

Performance Motion Devices, Inc.

2

Page 3

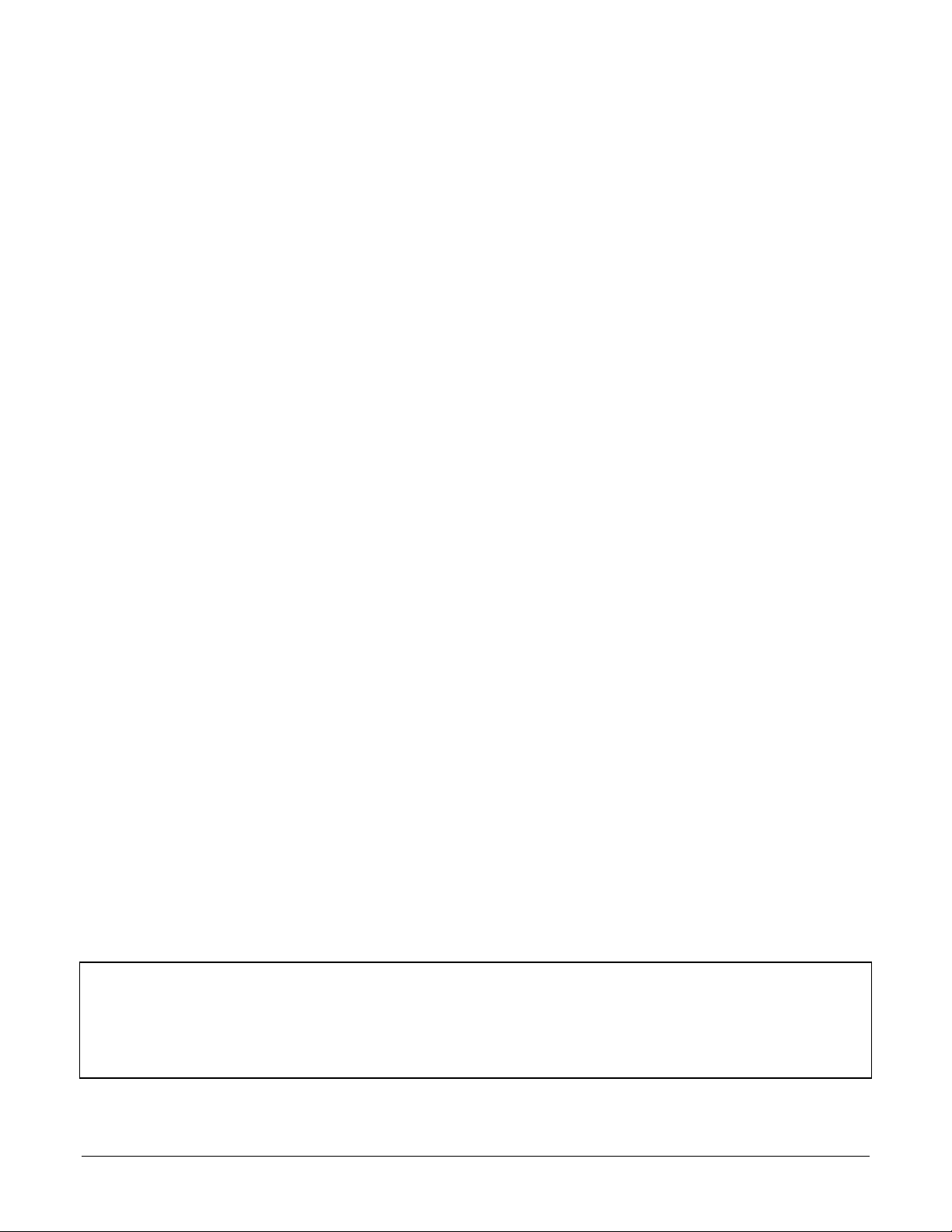

Product Family Overview

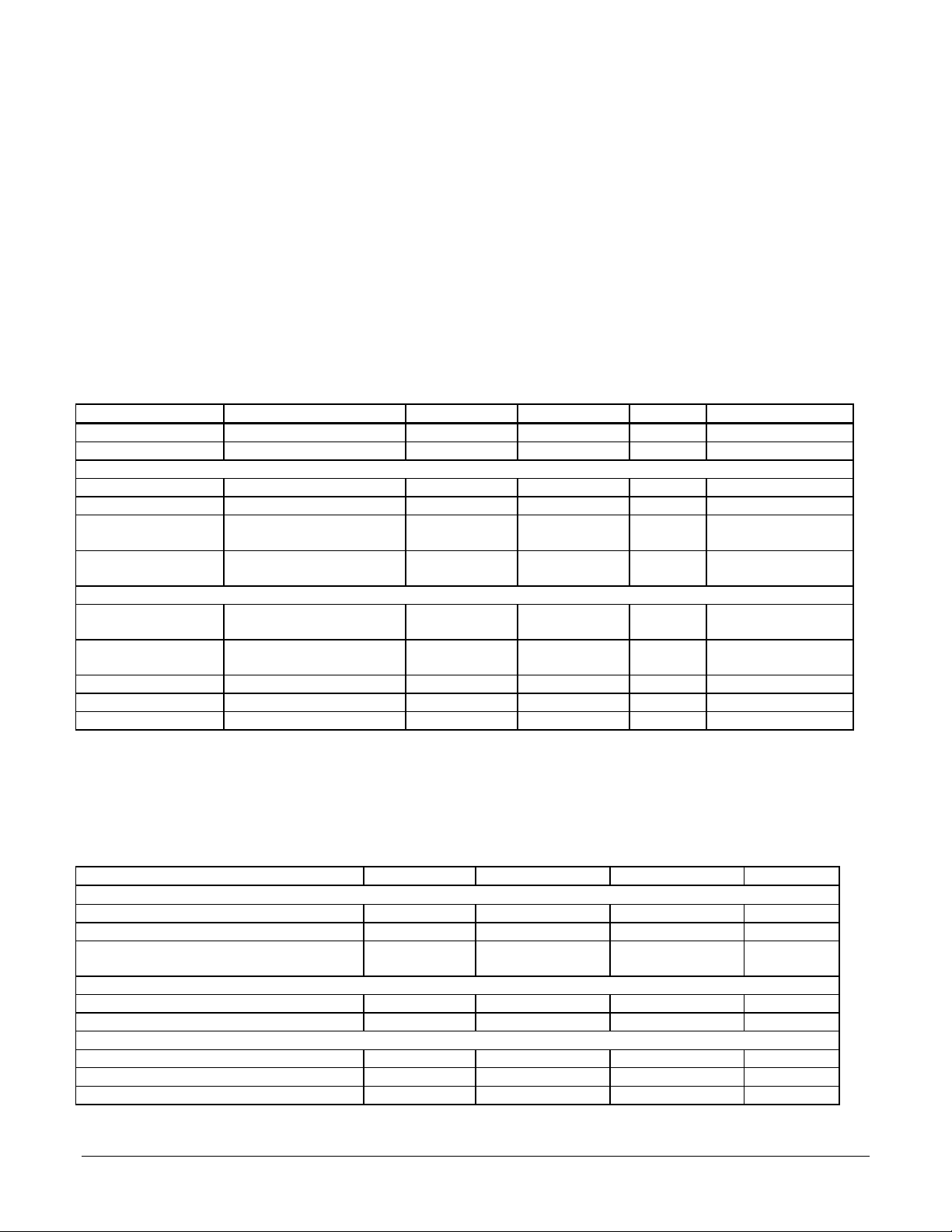

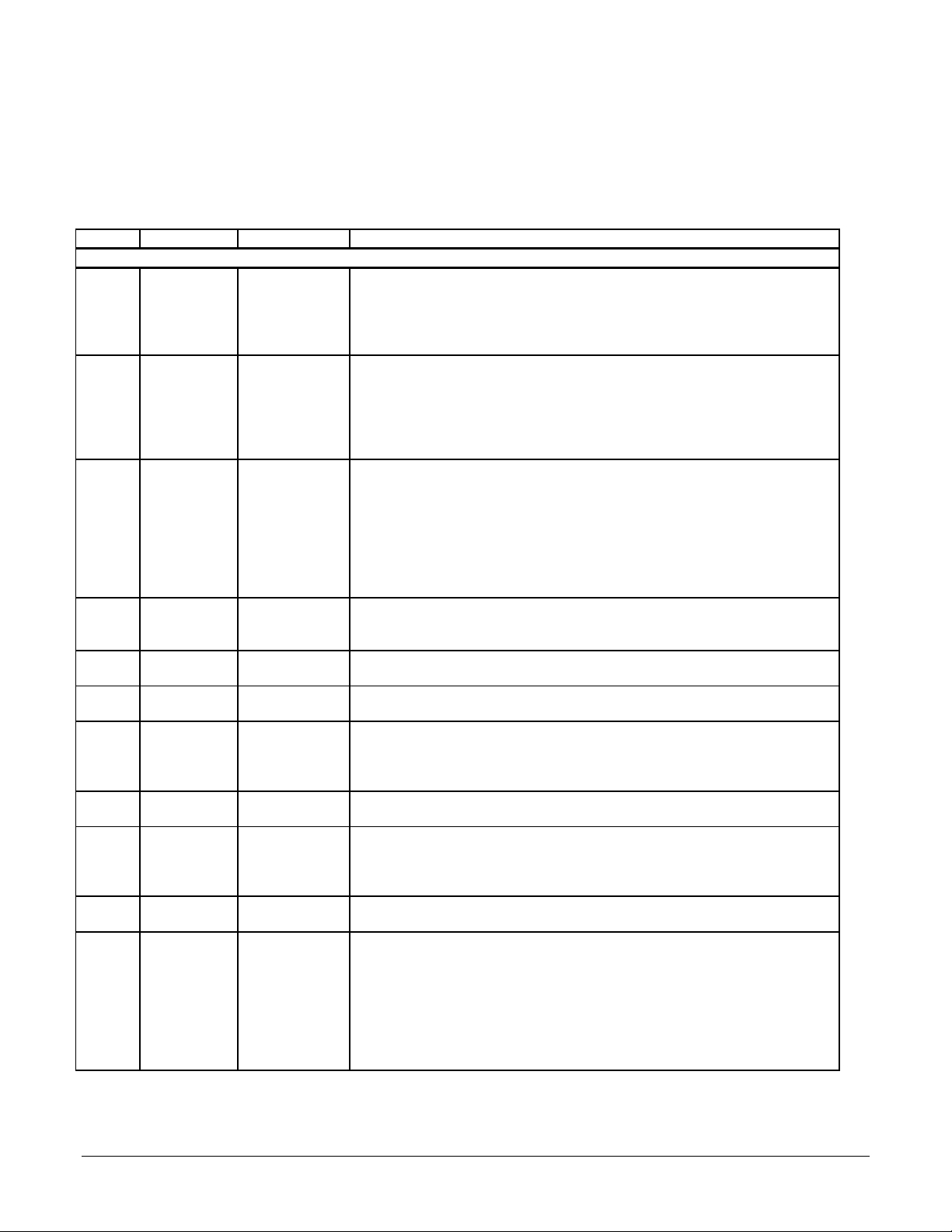

MC1401 series MC1231 series MC1241 series MC1451 series

# of axes 4, 2, or 1 2 or 1 2 or 1 4, 2, or 1

Motors Supported DC Servo Brushless Servo Stepper Stepper

Encoder Format Incremental (no dash version)

and Parallel ('-P' version)

Output Format DC servo Sinusoidally

S-curve profiling Yes Yes Yes Yes

Electronic gearing Yes Yes Yes Yes

On-the-fly changes Yes Yes Yes Yes

Limit switches Yes Yes Yes Yes

PID & feedforward Yes Yes - -

PWM output Yes Yes Yes -

DAC-compatible output Yes Yes Yes -

Pulse & direction output ---Yes

Index & Home signal Yes Yes Yes Yes

Chipset p/n's MC1401A, MC1401A-P (4 axes)

MC1201A, MC1201A-P (2 axes)

MC1101A, MC1101A-P (1 axis)

Developer's Kit p/n's: DK1401A, DK1401A-P DK1231A DK1241A DK1451A

* optional using third I.C. ('-E' version)

Incremental Incremental Incremental*

Microstepping Pulse and Direction

commutated

MC1231A (2 axes)

MC1131A (1 axis)

MC1241A (2 axes)

MC1141A (1 axis)

MC1451A, MC1451A-E (4 axes)

MC1251A, MC1251A-E (2 axes)

MC1151A, MC1151A-E (1 axis)

Introduction

This manual describes the operational characteristics of the MC1451A,

MC1251A, MC1151A, MC1451A-E, MC1251A-E, and MC1151A-E

Motion Processors. These devices are members of PMD's 1st

generation motion processor family, which consists of 16 separate

products organized into four groups.

Each of these devices are complete chip-based motion controllers.

They provide trajectory generation and related motion control functions.

Depending on the type of motor controlled they provide servo loop

closure, on-board commutation for brushless motors, and high speed

pulse and direction outputs. Together these products provide a

software-compatible family of dedicated motion processor chips which

can handle a large variety of system configurations.

Each of these chips utilize a similar architecture, consisting of a highspeed DSP (Digital Signal Processor) computation unit , along with an

ASIC (Application Specific Integrated Circuit). The computation unit

contains special on-board hardware such as a multiply instruction that

makes it well suited for the task of motion control.

Along with a similar hardware architecture these chips also share most

software commands, so that software written for one chipset may be reused with another, even though the type of motor may be different.

This manual describes the operation of the MC1451A, MC1251A,

MC1151A, MC1451A-E, MC1251A-E, and MC1151A-E chipsets. For

technical details on other members of PMD's first generation

motion processors see the corresponding product manual.

Family Summary

MC1401 series (MC1401A, MC1201A, MC1101A, MC1401A-P,

MC1201A-P, MC1101A-P)

encoder signals (standard version) or parallel word encoder signals

(-P version) and output a motor command in either PWM or DACcompatible format. These chipsets come in 1, 2 or 4 axis versions

and can be used with DC brushed motors, or brushless motors using

external commutation.

MC1231 series (MC1231A, MC1131A) -

incremental quadrature encoder signals and output sinusoidally

commutated motor signals appropriate for driving brushless motors.

They are available in one or two axis versions. Depending on the

motor type they output two or three phased signals per axis in either

PWM or DAC-compatible format.

MC1241 series (MC1241A, MC1141A)

internal microstepping generation for stepping motors. They are

available in a one or a two-axis version. Two phased signals are

output per axis in either PWM or DAC-compatible format. An

incremental encoder signal can be input to confirm motor position.

MC1451 series (MC1451A, MC1251A, MC1151A, MC1451A-E,

MC1251A-E, MC1151A-E) -

pulse and direction signal output appropriate for driving step motorbased systems. They are available in a one, two, or four-axis version

and are also available with quadrature encoder input.

Each of these chipsets has an associated Chipset Developer's

Kit available for it. For more information contact your PMD

representative.

- These chipsets take in incremental

These chipsets take in

- These chipsets provide

These chipsets provide very high speed

3

Page 4

Electrical Characteristics

Overview

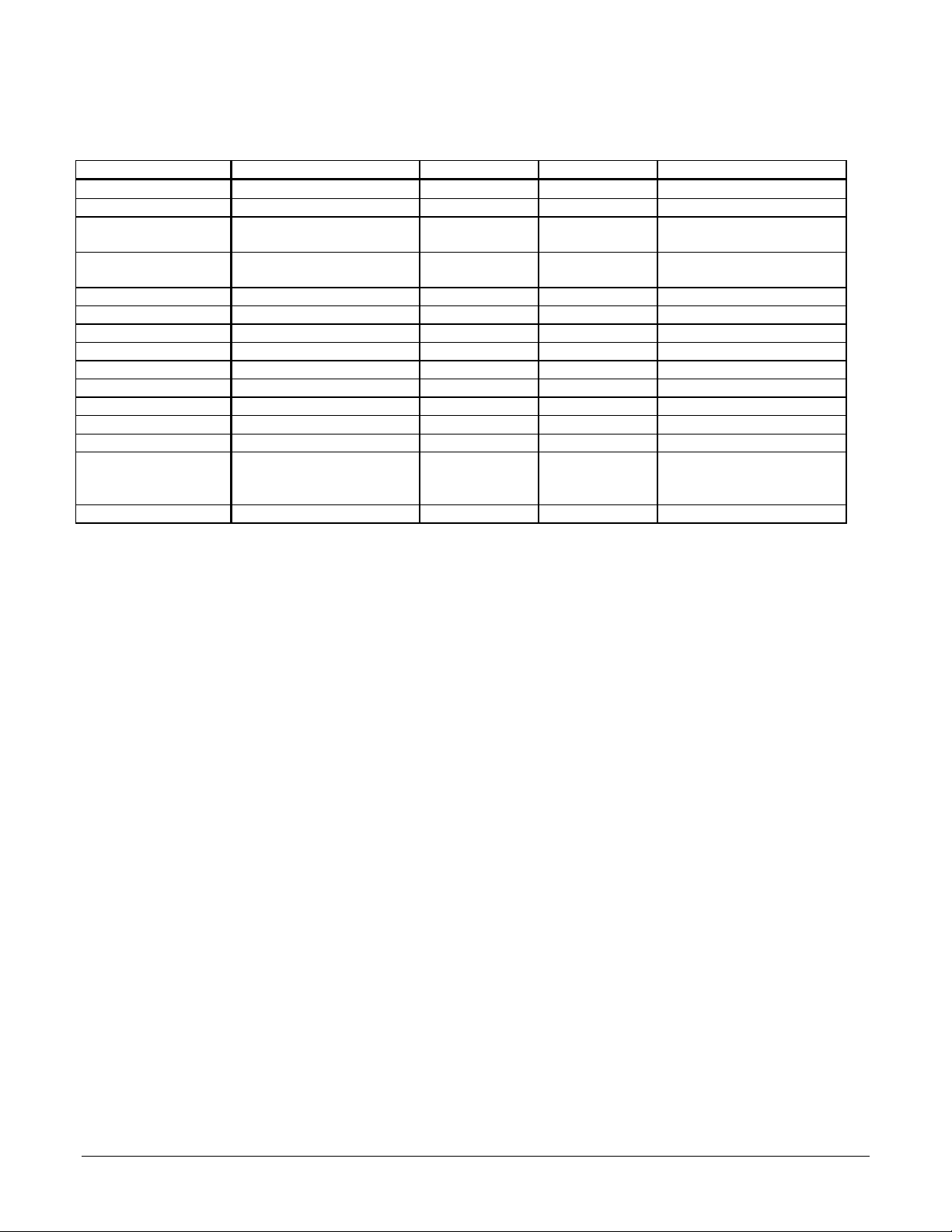

The MC1451A-consists of either two 68 pin PLCC's (standard version),

or these same two I.C.s with an additional 44 pin PLCC for incremental

encoder feedback (-E version). All of these devices are fabricated in

CMOS. The two 68 pin PLCCs are known as the I/O and the CP chips.

The 44-pin PLCC is known as the ENC chip.

The Peripheral Input/Output IC (I/O chip) is responsible for interfacing

to the host processor and for generating the high speed pulse and

direction output. The Command Processor IC (CP chip) is responsible

for all host command, trajectory, and related computations. The ENC

chip is responsible for incremental encoder feedback.

The following figure shows a typical system block diagram, along with

the pin connections between the I/O chip, CP chip, and ENC chip if it is

used.

Motor

(4 axis)

Amplifier

(1-4 axis)

I/O

Host

Processor

Data4-11

I/OAddr0-3

I/OWrite

I/OCntrl0-3

ClkOut

CP

Data4-11

I/OAddr0-3

I/OWrite

I/OCntrl0-3

ClkOut

Use of the ENC chip does not require a special version of the I/O or CP

chips. The CP chip automatically recognizes the presence or absence

of the ENC chip and functions accordingly.

The CP, I/O, and ENC chip (if used) form a complete chipset and

function together as one integrated motion processor. The major

components connected to the chipset are the step & direction

compatible amplifier (4, 2, or 1 axes), the optional encoder feedback

channels (4, 2, or 1 axes), and the host processor.

The chipset's pulse and direction output signals are connected to the

motor amplifier. Using this scheme the direction bit indicates whether

the motor should move in the positive or negative direction, and the

pulse signal indicates the desired motor speed. Pulse and direction

output is compatible with a wide variety of full, half, and microstepping

amplifiers.

Encoder

(1-4 axis)

ENC

Using the -E chipset parts it is possible to input quadrature encoder

feedback to the chipset. The encoder signals consist of the A and B

quadrature signals from the encoder.

The host processor is interfaced via an 8-bit bi-directional bus and

various control signals. Host communication is coordinated by a

ready/busy signal, which indicates when communication is allowed.

Interconnections between the I/O and the CP chip consist of a data bus

(8 bits) and various control and synchronization signals.

Interconnections between the CP and the ENC chip (if used) also

consist of a data bus (10 bits) and various control and synchronization

signals. Many of these signals are common between the I/O, CP, and

the ENC chips although there are no direct connections between just

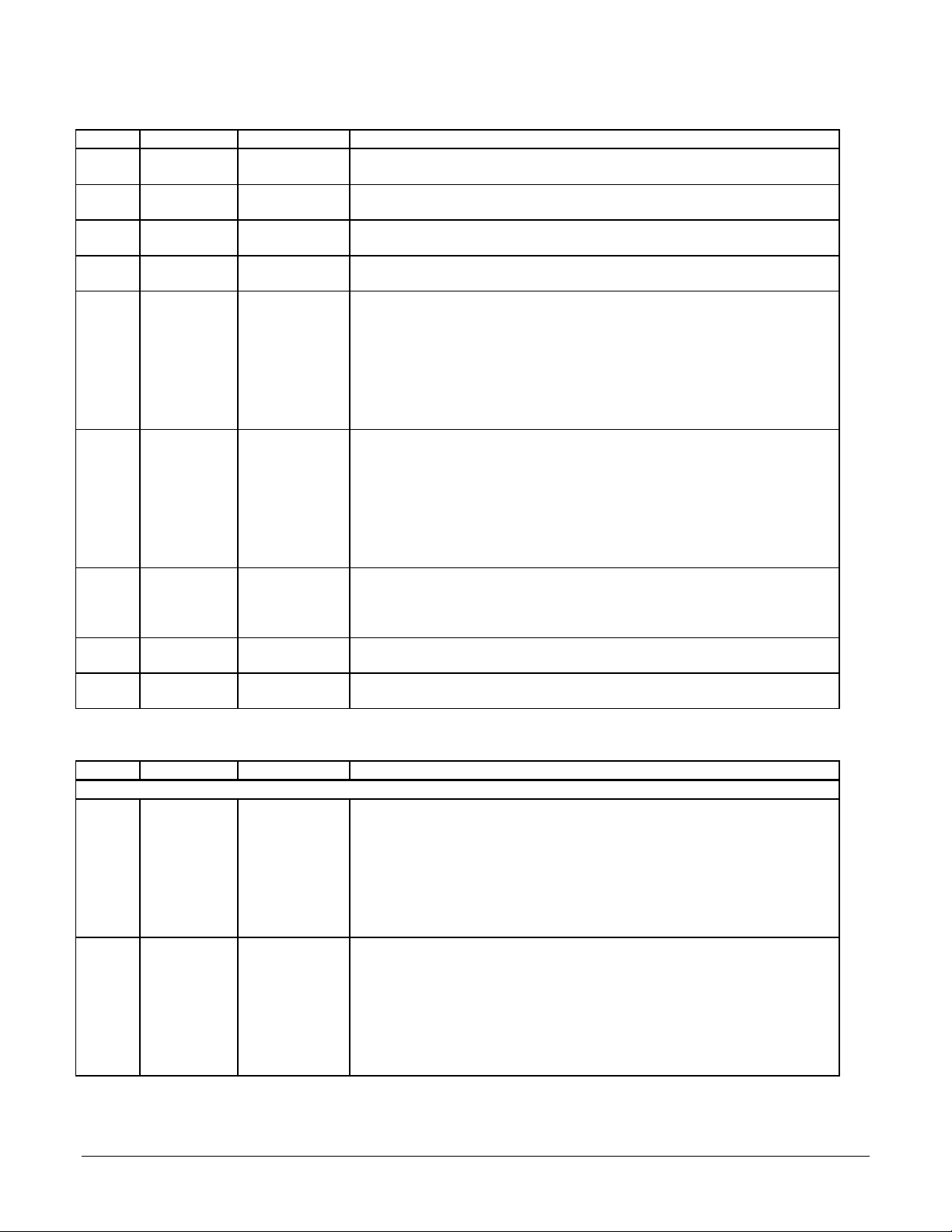

the ENC and the I/O chip. The following table summarizes the signals

that must be interconnected for the chipset to function properly. For

each listed signal the I/O chip pin on the left side of the table is

connected to the CP chip pin in the middle which is connected to the

ENC chip pin on the right side.

I/O Chip

Signal

Name

I/O

Chip

Pin

CP Chip

Signal

Name

CP

Chip

Pin

ENC Chip

Signal

Name

ENC

Chip

Pin

- - Data2 58 CPData2 22

- - Data3 57 CPData3 19

CPData4 18 Data4 50 CPData4 9

CPData5 5 Data5 49 CPData5 31

CPData6 6 Data6 46 CPData6 41

CPData7 7 Data7 43 CPData7 42

CPData8 8 Data8 40 CPData8 44

CPData9 17 Data8 39 CPData9 1

CPData10 3 Data10 36 CPData10 12

CPData11 1 Data11 35 CPData11 2

CPAddr0 68 I/OAddr0 28 CPAddr0 24

CPAddr1 27 I/OAddr1 9 - CPAddr2 29 I/OAddr2 6 CPAddr2 20

CPAddr3 12 I/OAddr3 5 CPAddr3 23

CPCntr0 20 I/OCntr0 16 CPCntr0 15

CPCntr1 36 I/OCntr1 18 - CPCntr2 22 I/OCntr2 68 - CPCntr3 63 I/OCntr3 67 - CPWrite 2 I/OWrite 15 CPWrite 13

CPClk 46 ClkOut 19 CPClk 7

CPReset 43 Reset 17 - -

For a complete description of all pins see the 'Pin Descriptions'

section of this manual.

Unless specifically noted otherwise, the term 'MC1451' or

'MC1451A' refers to the MC1451A, MC1251A, MC1151A, MC1451AE, MC1251A-E, and MC1151A-E Motion Processors.

4

Page 5

Absolute Maximum Ratings

Operating Ratings

Unless otherwise stated, all electrical specifications are for both

the I/O and CP chips.

Storage Temperature, Ts....................-55 deg. C to +150 deg. C

Supply Voltage, Vcc............................ -0.3 V to +7.0 V

Power Dissipation, Pd......................... 650 mW (I/O and CP

combined)

Operating Temperature, Ta .................0 deg. C to +70 deg. C*

Nominal Clock Frequency, Fclk...........25.0 Mhz

Supply Voltage, Vcc.............................4.75 V to 5.25 V

* Industrial and Military operating ranges also available. Contact your

PMD representative for more information.

DC Electrical Characteristics

(Vcc and Ta per operating ratings, Fclk = 25.0 Mhz)

Symbol Parameter Min. Max. Units Conditions

Vcc Supply Voltage 4.75 5.25 V

Idd Supply Current 100 mA open outputs

Input Voltages

Vih Logic 1 input voltage 2.0 Vcc + 0.3 V

Vil Logic 0 input voltage -0.3 0.8 V

Vihclk Logic 1 voltage for clock pin

(ClkIn)

Vihreset Logic 1 voltage for reset pin

(reset)

Output Voltages

Voh Logic 1 Output Voltage 2.4 V @CP Io = 300 uA

Vol Logic 0 Output Voltage 0.33 V @CP Io = 2 mA

Iout Tri-State output leakage current -20 20 uA 0 < Vout < Vcc

Iin Input current -50 50 uA 0 < Vi < Vcc

Iinclk Input current ClkIn -20 20 uA 0 < Vi < Vcc

3.0 Vcc+0.3 V

4.0 Vcc+0.3 V

@I/O Io = 4 mA

@I/O Io = 4 mA

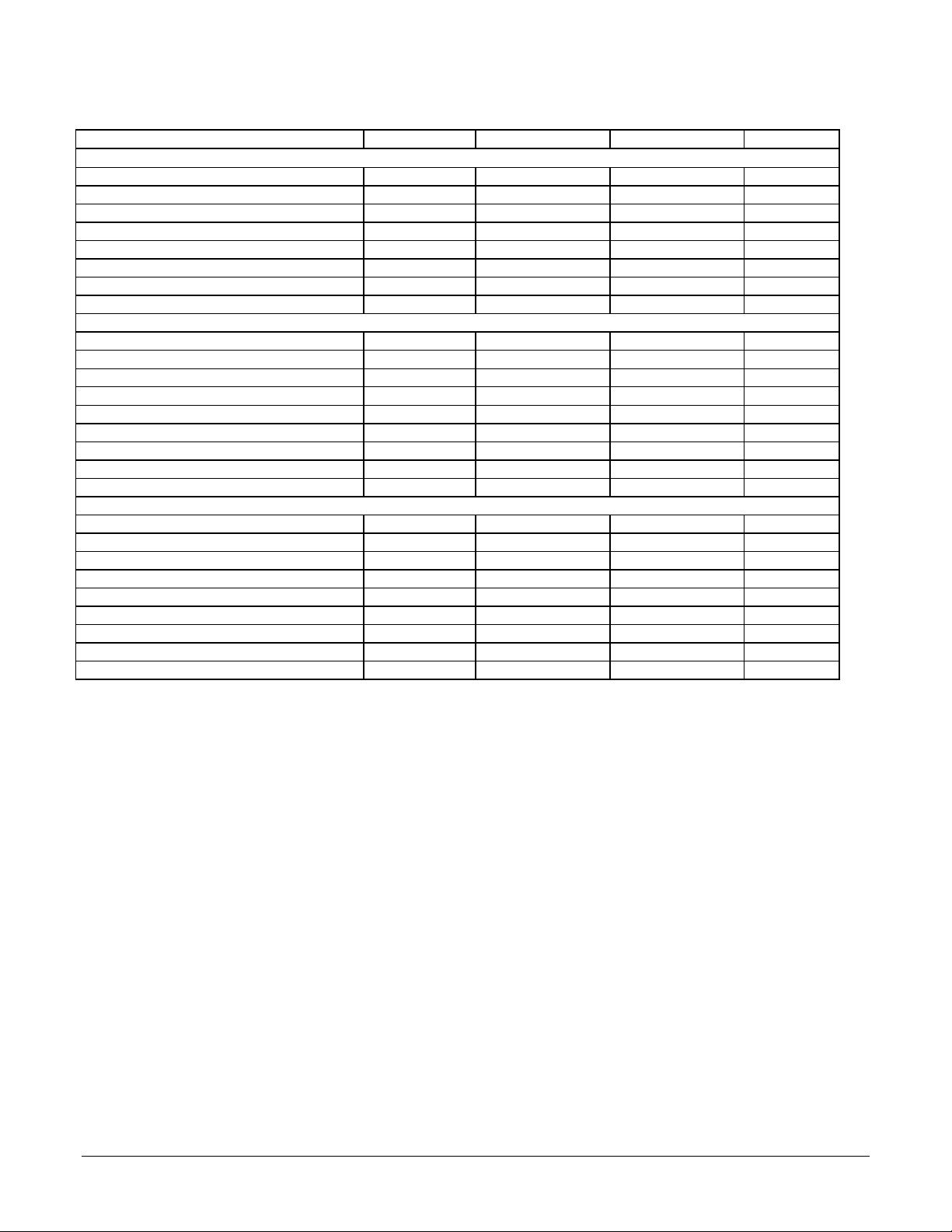

AC Electrical Characteristics

(see reference timing diagrams)

(Vcc and Ta per operating ratings; Fclk = 25.0 Mhz)

(~ character indicates active low signal)

Timing Interval T# Min. Max. Units

Encoder and Index Pulse Timing

Motor-Phase Pulse Width T1 1.6 uS

Dwell Time Per State T2 0.8 uS

Index Pulse Setup and Hold

(relative to Quad A and Quad B low)

Reset Timing

Stable Power to Reset 0.25 Sec

Reset Low Pulse Width 1.0 uS

Clock Timing

Clock Frequency (Fclk) 6.7 25.6 Mhz

Clock Pulse Width T4 19.5 75 (note 2) nS

Clock Period T5 39 149 (note 2) nS

T3 0 uS

5

Page 6

Timing Interval T# Min. Max. Units

Command Byte Write Timing

~HostSlct Hold Time T6 15 2000 (note 3) nS

~HostSlct Setup Time T7 10 nS

HostCmd Setup Time T8 10 nS

Host Cmd Hold Time T9 25 nS

HostRdy Delay Time T13 70 nS

~HostWrite Pulse Width T14 50 nS

Write Data Setup Time T15 35 nS

Write Data Hold Time T16 30 nS

Data Word Read Timing

~HostSlct Hold Time T6 15 2000 (note 3) nS

~HostSlct Setup Time T7 (read only) - 20 nS

HostCmd Setup Time T8 (read only) - 20 nS

HostCmd Hold Time T9 25 nS

Read Data Access Time T10 50 nS

Read Data Hold Time T11 10 nS

~HostRead high to HI-Z Time T12 50 nS

HostRdy Delay Time T13 70 nS

Read Recovery Time T17 60 nS

Data Word Write Timing

~HostSlct Hold Time T6 15 2000 (note 3) nS

~HostSlct Setup Time T7 10 nS

HostCmd Setup Time T8 10 nS

HostCmd Hold Time T9 25 nS

HostRdy Delay Time T13 70 nS

~HostWrite Pulse Width T14 50 nS

Write Data Setup Time T15 35 nS

Write Data Hold Time T16 30 nS

Write Recovery Time T18 60 nS

note 1 ~HostSlct and HostCmd may optionally be de-asserted if setup and hold times are met.

note 2 Chip-set performance figures and timing information valid at Fclk = 25.0 only. For timing information & performance parameters at Fclk <

25.0 Mhz, call PMD.

note 3 Two micro seconds maximum to release interface before chip set responds to command

note 4 ClkOut from CP is 1/4 frequency of ClkIn (CP chip).

6

Page 7

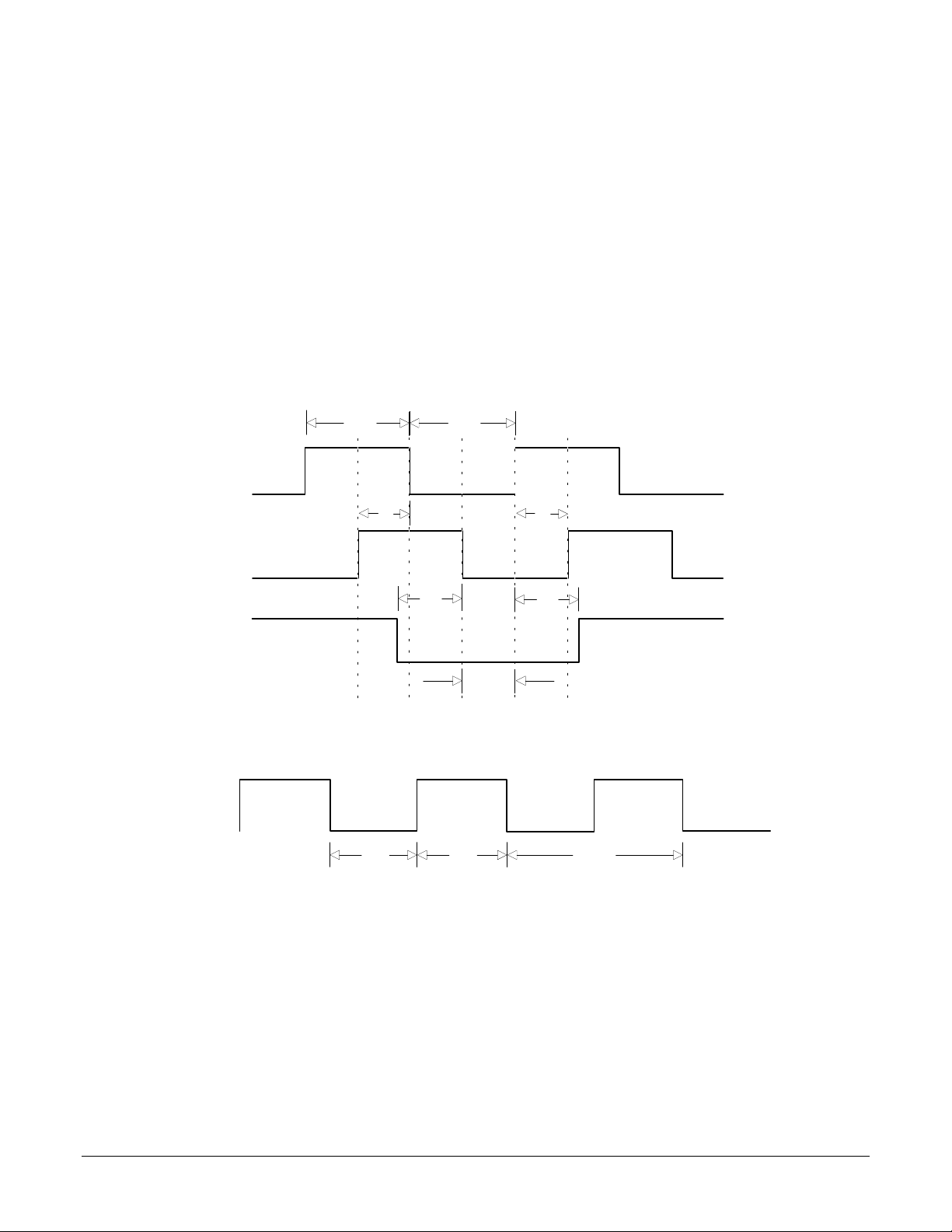

I/O Timing Diagrams

The following diagrams show the MC1451A electrical interface timing. T#' values are listed in the above timing chart.

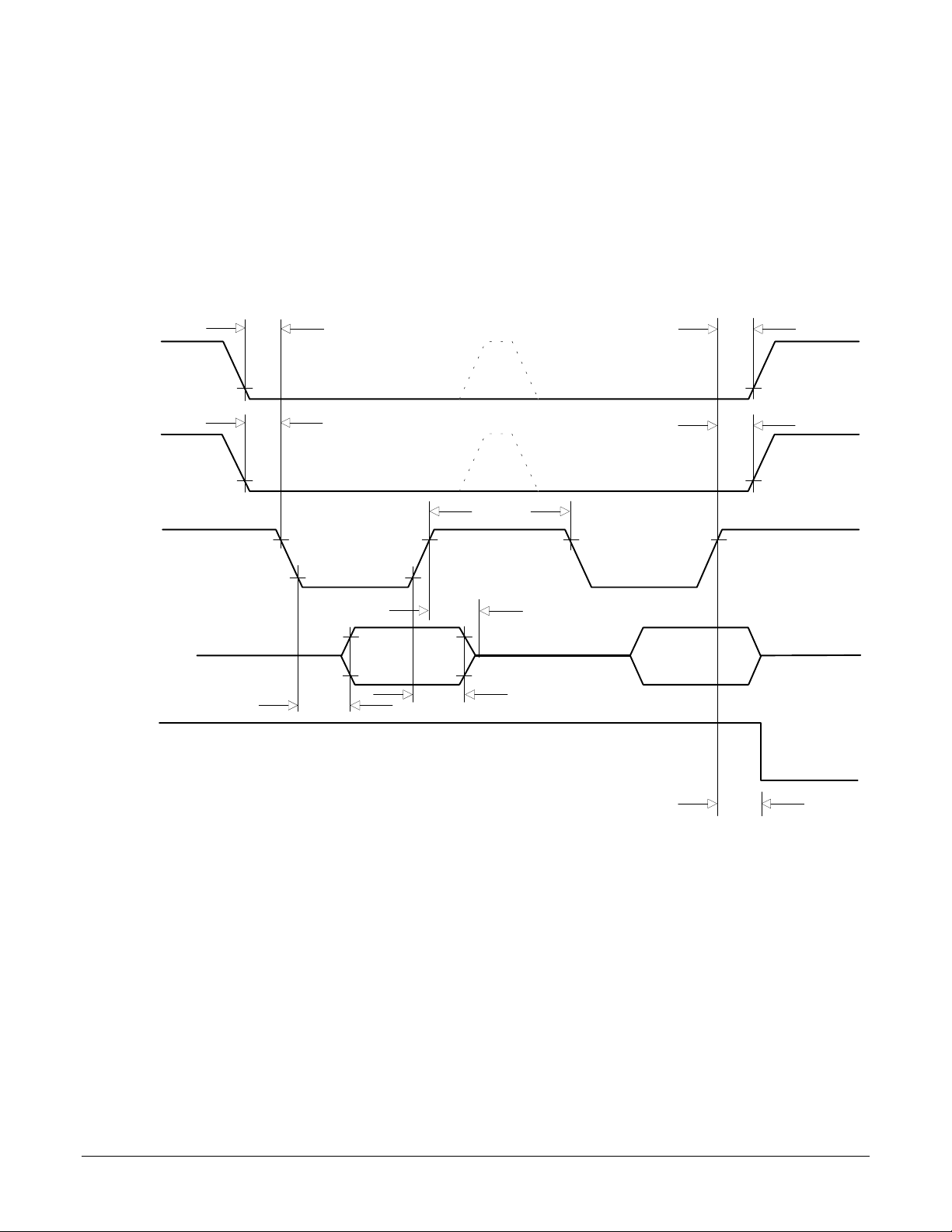

Quadrature Encoder Input Timing

Quad A

Quad B

~Index

ClkIn

T1

T1

T2 T2

T3

Clock Timing

T3

T4 T4 T5

Index = ~A * ~B * ~IN D

7

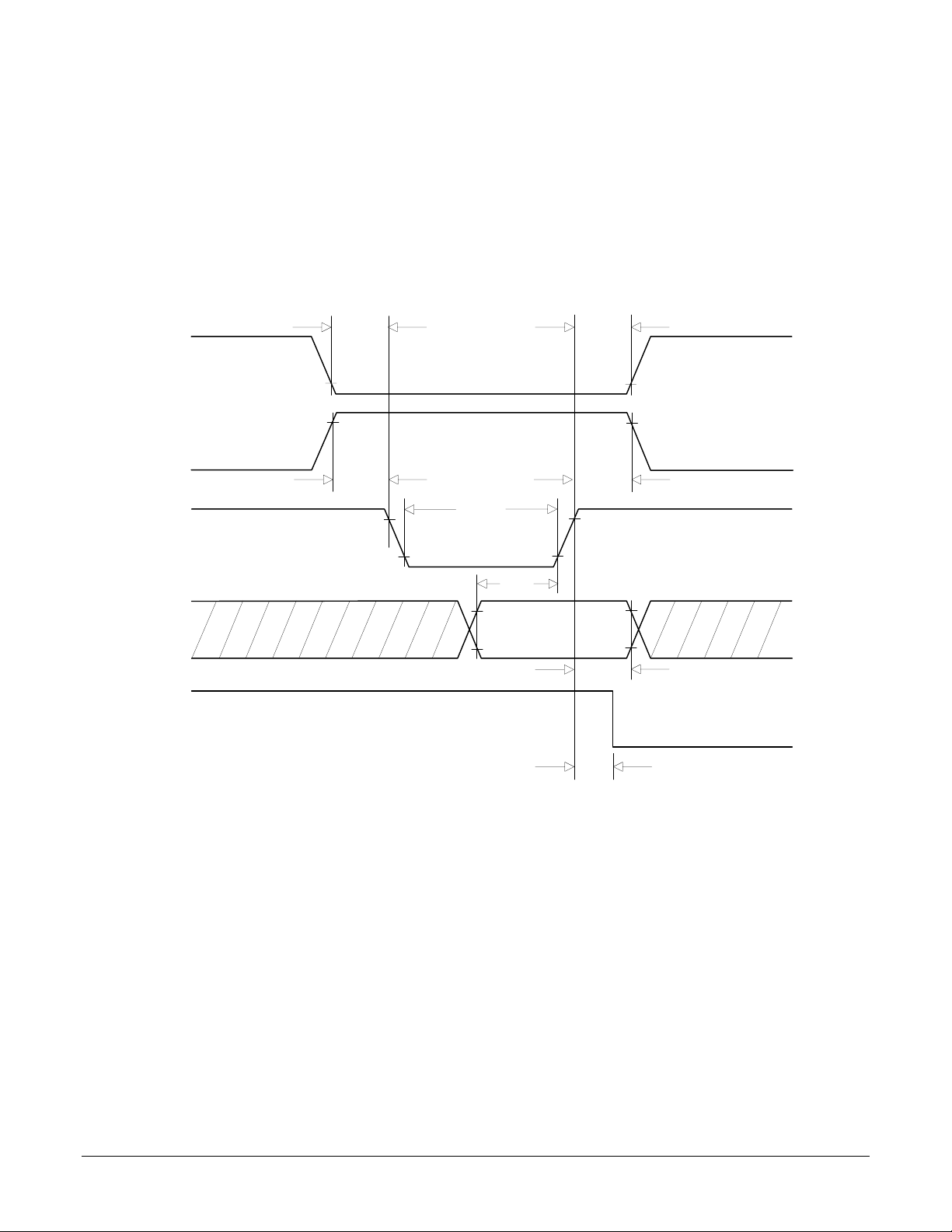

Page 8

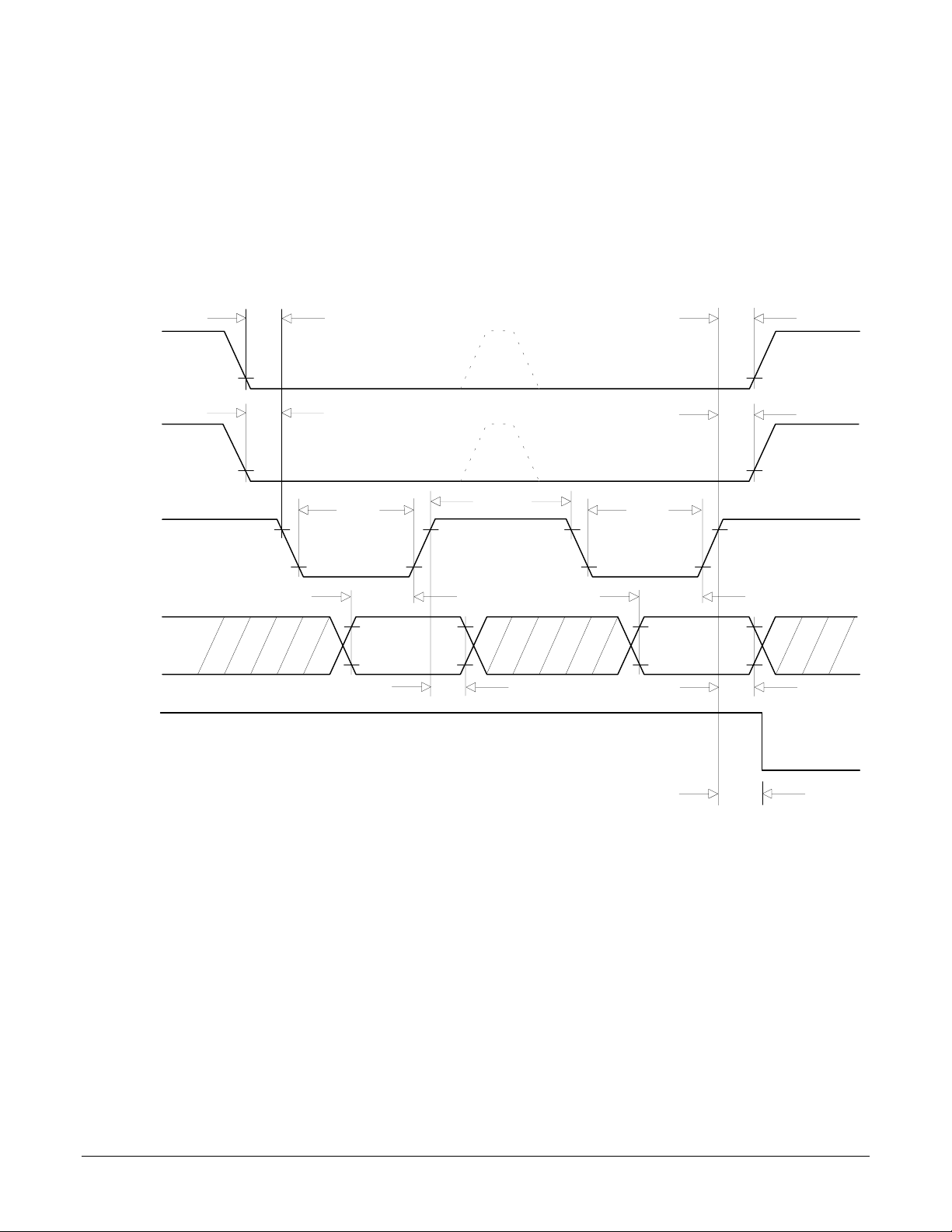

Command Byte Write TIming

~HostSlct

HostCmd

~HostWrite

HostData0-7

HostRdy

T7

T8

T6

T9

T14

T15

T16

T13

8

Page 9

Data Word Read TImi ng

~HostSlct

HostCmd

~HostRead

HostData0-7

HostRdy

T7

T6

Note 1

T8

Note 1

T9

T17

T12

High-Z High-Z High-Z

High

Byte

T10

T11

Low

Byte

T13

9

Page 10

Data Word Write TIming

~HostSlct

HostCmd

~HostWrite

HostData0-7

HostRdy

T7

T8

T14

T15

High

Byte

T16

T18

Note 1

Note 1

T6

T9

T14

T15

Low

Byte

T16

10

T13

Page 11

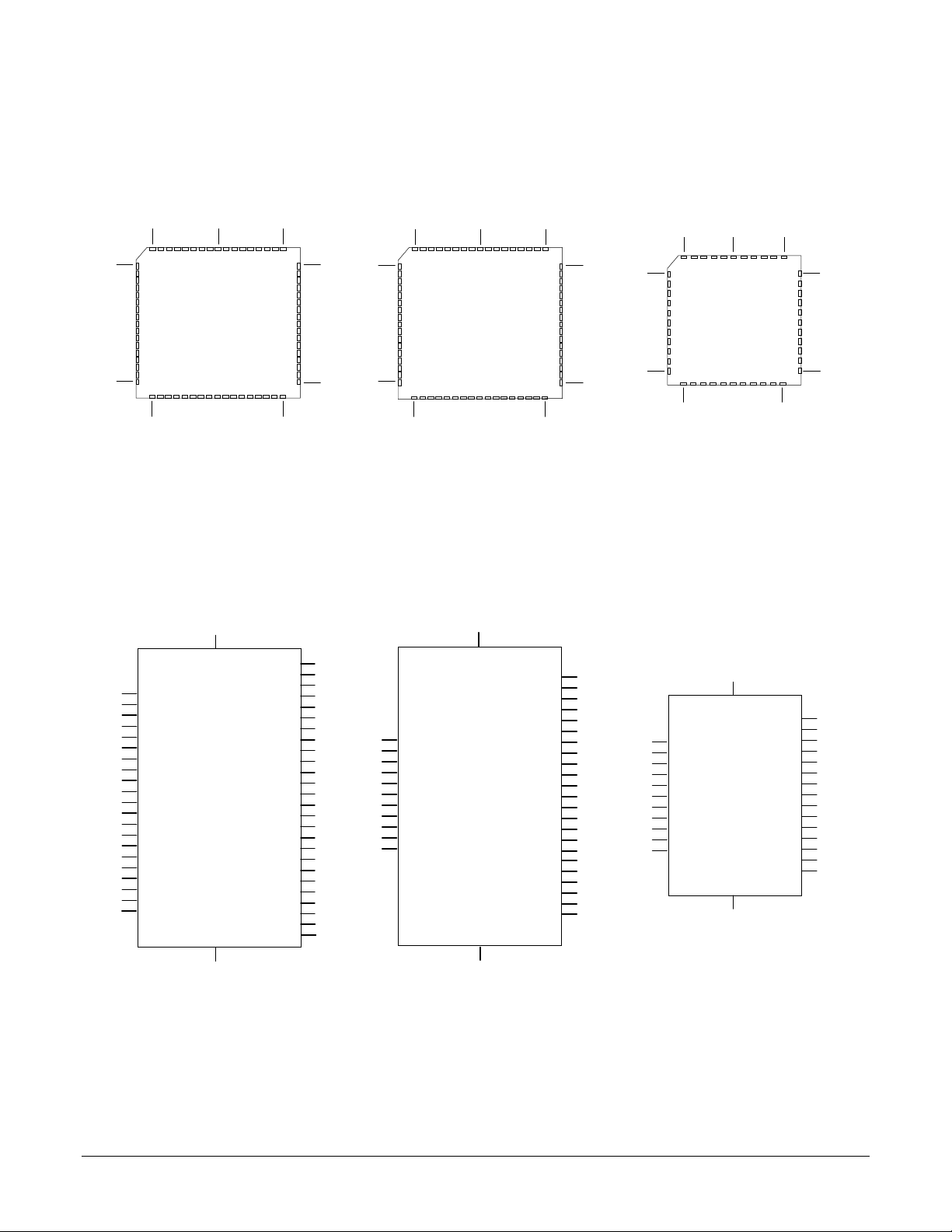

Pinouts

9

10

(Top view)

26

27 43

4, 21, 25, 38, 55

28

Pulse1

42

Dir1

13

Home1

26

Pulse2

30

Dir2

23

Home2

40

Pulse3

35

Dir3

11

Home3

39

Pulse4

34

Dir4

10

Home4

46

CPClk

52

I/OClkIn

45

I/OClkOut

29

CPAddr2

12

CPAddr3

2

CPWrite

20

CPCntrl0

36

CPCntrl1

43

CPReset

1

I/O

VCC

I/O

GND

61

CPCntrl2

CPCntrl3

HostCmd

HostRdy

HostRead

HostWrite

HostSlct

HostIntrpt

HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

CPAddr0

CPAddr1

9

60

10

1

CP

(Top view)

44

26

27 43

(Chip Outlines Not Drawn To Scale)

MC1451A & MC1451A-E Pinouts

4, 22, 33

22

63

41

37

51

47

48

44

56

50

61

53

65

67

62

64

60

18

5

6

7

8

17

3

1

68

27

AtRest1

55

AtRest2

54

AtRest3

53

AtRest4

24

ClkIn

19

ClkOut

17

Reset

16

I/OCntrl0

18

I/OCntrl1

68

I/OCntrl2

67

I/OCntrl3

VCC

CP

GND

61

Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

I/OAddr0

I/OAddr1

I/OAddr2

I/OAddr3

I/OWrite

PosLimit1

PosLimit2

PosLimit3

PosLimit4

NegLimit1

NegLimit2

NegLimit3

NegLimit4

6

60

7

1

40

39

ENC

(Top view)

17

44

18 28

58

57

50

49

46

43

40

39

36

35

28

9

6

5

15

52

45

42

38

51

44

41

37

30

36

17

18

27

28

5

29

7

33

6

3, 14, 16, 25, 35

QuadA1

QuadB1

QuadA2

QuadB2

QuadA3

QuadB3

QuadA4

QuadB4

CPClk

I/OClkIn

I/OClkOut

10, 21, 32, 34, 43

VCC

ENC

GND

CPAddr0

CPAddr2

CPAddr3

CPWrite

CPCntrl0

CPData2

CPData3

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

29

24

20

23

13

15

22

19

9

31

41

42

44

1

12

2

14, 15, 32, 49, 54, 66

3, 34

11

Page 12

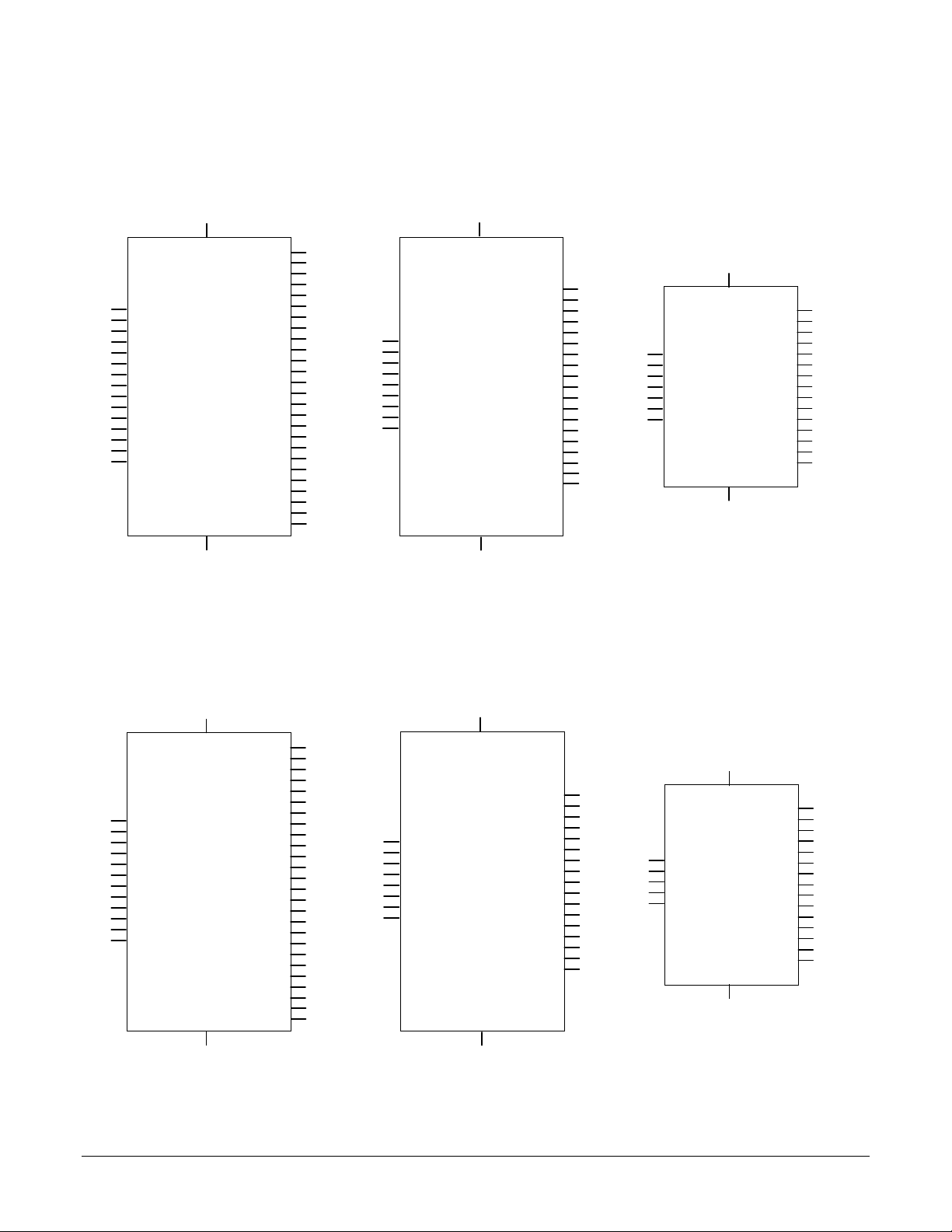

MC1251A & MC1251A-E Pinouts

4, 21, 25, 38, 55

VCC

28

Pulse1

42

Dir1

13

Home1

26

Pulse2

30

Dir2

23

Home2

46

CPClk

52

I/OClkIn

45

I/OClkOut

29

CPAddr2

12

CPAddr3

2

CPWri t e

20

CPCntrl0

36

CPCntrl1

43

CPReset

I/O

GND

14, 15, 32, 49, 54, 66

CPCntrl2

CPCntrl3

HostCmd

HostRdy

HostRead

HostWrite

HostSlct

HostIntrpt

HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

CPAddr0

CPAddr1

22

63

41

37

51

47

48

44

50

61

53

65

67

62

64

60

18

5

6

7

8

17

3

1

68

27

AtRest1

56

AtRest2

55

ClkIn

24

ClkOut

19

Reset

17

I/OCntrl0

16

I/OCntrl1

18

I/OCntrl2

68

I/OCntrl3

67

4, 22, 33

VCC

CP

GND

3, 34

Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

I/OAddr0

I/OAddr1

I/OAddr2

I/OAddr3

I/OWrite

PosLimit1

PosLimit2

NegLimit1

NegLimit2

3, 14, 16, 25, 35

58

57

50

49

46

43

40

39

36

35

28

9

6

5

15

52

45

51

44

QuadA1

30

QuadB1

36

QuadA2

17

QuadB2

18

CPClk

7

I/OClkIn

33

I/OClkOut

6

VCC

ENC

CPData10

CPData11

GND

10, 21, 32, 34, 43

CPAddr0

CPAddr2

CPAddr3

CPWrite

CPCntrl0

CPData2

CPData3

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

24

20

23

13

15

22

19

9

31

41

42

44

1

12

2

MC1151A & MC1151A-E Pinouts

4, 21, 25, 38 , 55

VCC

28

Pulse1

42

Dir1

13

Home1

46

CPClk

52

I/OClkIn

45

I/OClkOut

29

CPAddr2

12

CPAddr3

2

CPWri t e

20

CPCntrl0

36

CPCntrl1

43

CPReset

I/O

GND

14, 15, 32, 49, 54, 66

CPCntrl2

CPCntrl3

HostCmd

HostRdy

HostRead

HostWrite

HostSlct

HostIntrpt

HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

CPAddr0

CPAddr1

22

63

41

37

51

47

48

44

50

61

53

65

67

62

64

60

18

5

6

7

8

17

3

1

68

27

56

AtRest1

24

ClkIn

19

ClkOut

17

Reset

16

I/OCntrl0

18

I/OCntrl1

68

I/OCntrl2

67

I/OCntrl3

4, 22, 33

VCC

CP

GND

3, 34

Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

I/OAddr0

I/OAddr1

I/OAddr2

I/OAddr3

I/OWrite

PosLimit1

NegLimit1

3, 14, 16, 25, 35

58

57

50

49

46

43

40

39

36

35

28

9

6

5

15

52

51

QuadA1

30

QuadB1

36

CPClk

7

I/OClkIn

33

I/OClkOut

6

VCC

ENC

CPData10

CPData11

GND

10, 21, 32, 34, 43

CPAddr0

CPAddr2

CPAddr3

CPWr ite

CPCntrl0

CPData2

CPData3

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

24

20

23

13

15

22

19

9

31

41

42

44

1

12

2

12

Page 13

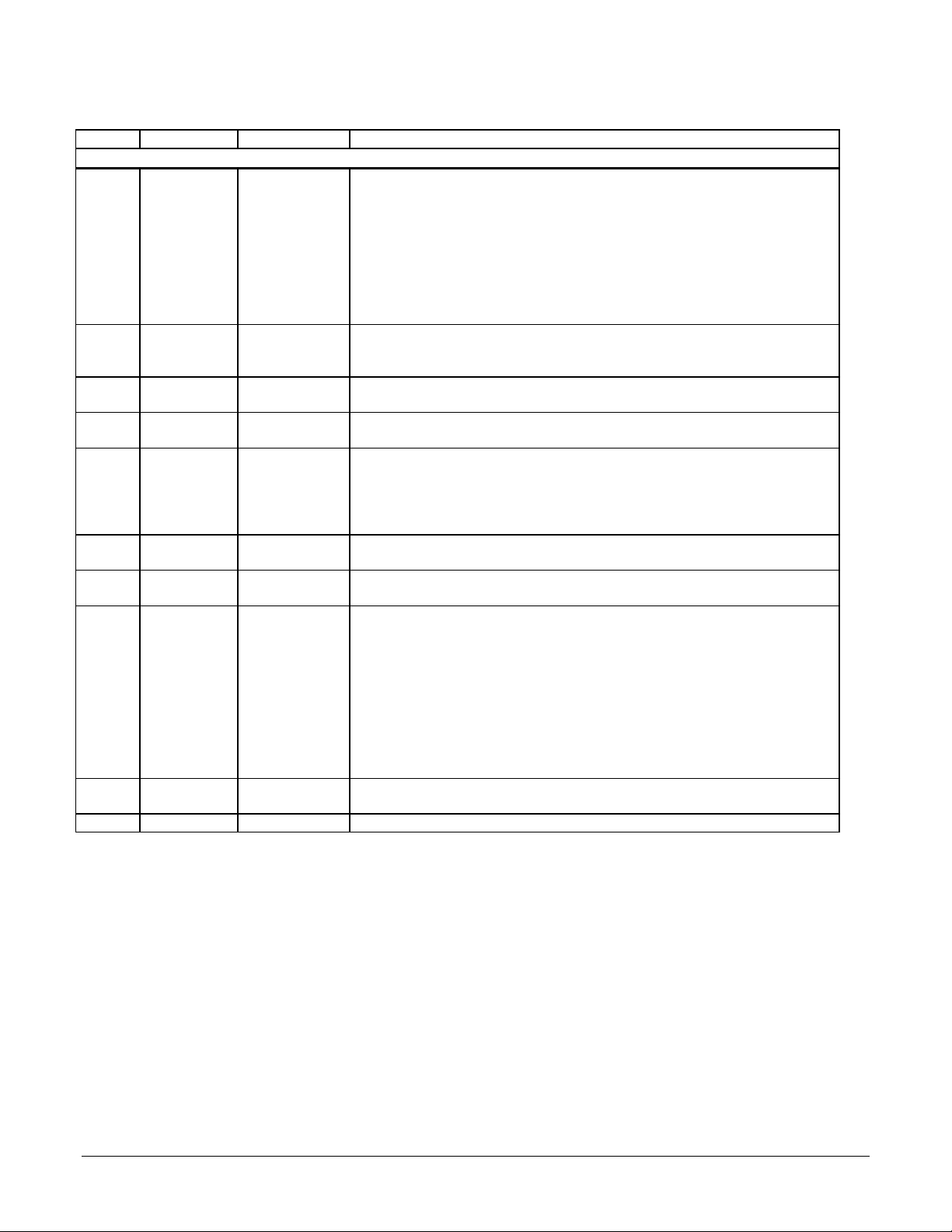

Pin Descriptions

The following tables provide pin descriptions for the MC1401 and MC1401-P series chipsets.

IC Pin Name Pin # Description/Functionality

I/O Chip Pinouts

I/O Pulse1

Pulse2

Pulse3

Pulse4

I/O Dir1

Dir2

Dir3

Dir4

I/O ~Home1

~Home2

~Home3

~Home4

I/O CPClk 46 I/O chip clock (input). This signal is connected directly to the ClkOut pin (CP chip) and

I/O I/OClkIn 52 Phase shifted clock (input). This signal is connected to I/OClkOut (I/O chip), and inputs a

I/O I/OClkOut 45 Phase shifted clock (output). This signal is connected to I/OClkIn (I/O chip), and outputs a

I/O CPAddr0

CPAddr1

CPAddr2

CPAddr3

I/O ~CPWrite 2 I/O chip to CP chip communication write (input). This signal is connected to the ~I/OWrite pin

I/O CPCntrl0

CPCntrl1

CPCntrl2

CPCntrl3

I/O HostCmd 41 Host Port Command (input). This signal is asserted high to write a host command to the chip

I/O HostRdy 37 Host Port Ready/Busy (output). This signal is used to synchronize communication between

28

26

40

39

42

30

35

34

13

23

11

10

68

27

29

12

20

36

22

63

Pulse signal for channels 1-4 (output). This signal is always a square wave, regardless of

pulse rate. Nominal 'step' occurs when signal goes from a high state to a low state.

NOTE: For MC1451A all 4 pins are valid. For MC1251A pins for axes 1 & 2 only are valid.

For MC1151A pins for axis 1 only are valid. Invalid axis pins can be left unconnected.

Direction signal for channels 1-4 (output). This signal indicates the direction of motion, and

works in conjunction with the pulse signal. A high level on this signal indicates a positive

direction move, and a low level indicates a negative direction move.

NOTE: For MC1451A all 4 pins are valid. For MC1251A pins for axes 1 & 2 only are valid.

For MC1151A pins for axis 1 only are valid. Invalid axis pins can be left unconnected.

Home signals for axis 1-4 (input). Each of these signals provide a general purpose input to

the external breakpoint mechanism. Using these signals it is possible to stop, start, or alter

the motion trajectory. See theory of operations for details.

An active home signal is recognized by the chipset as a low state.

NOTE: For MC1451A all 4 pins are valid. For MC1251A pins for axes 1 & 2 only are valid.

For MC1151A pin for axis 1 only is valid. Invalid axis pins can be left unconnected.

provides the clock signal for the I/O chip. The frequency of this signal is 1/4 the user-provided

ClkIn (CP chip) frequency.

phase shifted clock signal.

phase shifted clock signal.

I/O chip to CP chip communication address (input). These 4 signals are connected to the

corresponding I/OAddr0-3 pins (CP chip), and together provide addressing signals to

facilitate CP to I/O chip communication.

(CP chip) and provides a write strobe to facilitate CP to I/O chip communication.

I/O chip to CP chip communication control (mixed). These 4 signals are connected to the

corresponding I/OCntrl0-3 pins (CP chip), and provide control signals to facilitate CP to I/O

chip communication.

set. It is asserted low to read or write a host data word to the chipset

the DSP and the host. HostRdy will go low (indicating host port busy) at the end of a host

command write or after the second byte of a data write or read. HostRdy will go high

(indicating host port ready) when the command or data word has been processed and the

chip set is ready for more I/O operations. All host port communications must be made with

HostRdy high (indicating ready).

Typical busy to ready cycle is 82.5 uSec..

13

Page 14

IC Pin Name Pin # Description/Functionality

I/O ~HostRead 51 Host Port Read data (input). Used to indicate that a data word is being read from the chip set

(low asserts read).

I/O ~HostWrite 47 Host Port Write data (input). Used to indicate that a data word or command is being written to

the chip set (low asserts write).

I/O ~HostSlct 48 Host Port Select (input). Used to select the host port for reading or writing operations (low

assertion selects port). ~HostSlct must remain inactive (high) when the host port is not in use.

I/O ~HostIntrpt 44 Host Interrupt (output). A low assertion on this pin indicates that a host interrupt condition

exists that may require special host action.

I/O HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

I/O CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

I/O ~CPReset 43 I/O chip set reset (input). When brought low this pin resets the I/O chip to its initial condition.

I/O Vcc 4, 21, 25, 38, 55 I/O chip supply voltage pin. All of these pins must be connected to the supply voltage. Supply

I/O GND 14, 15, 32, 49, 54,66I/O chip ground pin. All of these pins must be connected to the power supply return.

50

61

53

65

67

62

64

60

18

5

6

7

8

17

3

1

Host Port Data 0-7 (bi-directional, tri-stated). These signals form the 8 bit host data port used

during communication to/from the chip set. This port is controlled by ~HostSlct, ~HostWrite,

~HostRead and HostCmd.

I/O chip to CP chip data port (bi-directional). These 8 bits are connected to the corresponding

Data4-11 pins on the CP chip, and facilitate communication to/from the I/O and CP chips..

Reset should occur no less than 250 mSec after stable power has been provided to the chip

set. This signal should be connected to the ~Reset pin of the CP chip, which in turn should

be connected to the master reset signal.

voltage = 4.75 to 5.25 V

IC Pin Name Pin # Description/Functionality

CP Chip Pinouts

CP AtRest1

AtRest2

AtRest3

AtRest4

CP PosLimit1

PosLimit2

PosLimit3

PosLimit4

56

55

54

53

52

45

42

38

At Rest indicator signals for axes 1-4 (output). A high level on this signal indicates the axis is

at rest. A low signal indicates the axis is in motion.

This signal is useful for driving amplifiers with an input bit to control running and holding

torque.

NOTE: For MC1451A all 4 pins are valid. For MC1251A pins for axes 1 & 2 only are valid.

For MC1151A pin for axis 1 only is valid. Invalid axis pins can be left un connected.

Positive limit switch input for axis 1-4. These signals provide directional limit inputs for the

positive-side travel limit of the axis. Upon powerup these signals default to "active high"

interpretation, but the interpretation can be set explicitly using the SET_LMT_SENSE

command. If not used these signals should be tied low for the default interpretation, or tied

high if the interpretation is reversed.

NOTE: For MC1451A all 4 pins are valid. For MC1251A pins for axes 1 & 2 only are valid.

For MC1151A pin for axis 1 only is valid. Invalid axis pins can be left un connected.

14

Page 15

IC Pin Name Pin # Description/Functionality

CP NegLimit1

NegLimit2

NegLimit3

NegLimit4

CP ClkIn 24 Clock In (input). This pin provides the chip set master clock (Fclk = 25.0 Mhz)

CP ClkOut 19 Clock Out (output). This pin provides a clock output which is 1/4 the ClkIn frequency. This pin

CP ~Reset 17 Master chip set reset (input). When brought low, this pin resets the chip set to its initial

CP I/OCntrl0

I/OCntrl1

I/OCntrl2

I/OCntrl3

CP Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

CP I/OAddr0

I/OAddr1

I/OAddr2

I/OAddr3

CP I/OWrite 15 Write (output). This pin is connected to CPWrite on the I/O and on the ENC chip. It provides a

CP Vcc 4, 22, 33 CP chip supply voltage pin. All of these pins must be connected to the supply voltage. Supply

CP GND 3, 34 CP chip ground pin. All of these pins must be connected to the power supply return.

51

44

41

37

16

18

68

67

58

57

50

49

46

43

40

39

36

35

28

9

6

5

Negative limit switch input for axis 1-4. These signals provide directional limit inputs for the

negative-side travel limit of the axis. Upon powerup these signals default to "active high"

interpretation, but the interpretation can be set explicitly using the SET_LMT_SENSE

command. If not used these signals should be tied low for the default interpretation, or tied

high if the interpretation is reversed.

NOTE: For MC1451A all 4 pins are valid. For MC1251A pins for axes 1 & 2 only are valid.

For MC1151A pin for axis 1 only is valid. Invalid axis pins can be left un connected.

is connected to the CPClk signals of the I/O chip and ENC chip

condition. Reset should occur no less than 250 mSec after stable power has been provided

to the chip set.

The master reset signal should be connected to this pin as well as the ~CPReset pin of the

I/O chip

I/O and ENC chip to CP chip communication control (mixed). These signals provide various

inter-chip control signals for the I/O and ENC chips. For the I/O chip these four signals are

connected to the corresponding CPCntrl0-3 pins. For the ENC chip only I/OCntrl0 is used

which is connected to the CPCntrl0 pin.

CP to I/O and ENC chip Data4-11. (Bi-directional). These pins are connected to the

corresponding CPData4-11 pins on the I/O chip, and on the corresponding CPData2-11 pins

on the ENC chip. These signals are used to communicate between the CP and the I/O and

ENC chips.

Address0-3 (output). These signals provide various inter-chip address control signals for the

I/O and ENC chips. For the I/O chip these four signals are connected to the corresponding

CPAddr0-3 pins. For the ENC chip only I/OAddr0, I/OAddr2, and I/OAddr3 are used and they

are connected to the corresponding pins on the ENC chip.

control signal to the I/O and ENC chip to facilitate communication between these chips and

the CP chip

voltage = 4.75 to 5,.25 V

15

Page 16

IC Pin Name Pin # Description/Functionality

ENC Chip Pinouts

ENC QuadA1

QuadB1

QuadA2

QuadB2

QuadA3

QuadB3

QuadA4

QuadB4

ENC CPClk 7 ENC chip clock (input). This signal is connected directly to the I/OClkOut pin (CP chip) and

ENC ENCClkIn 33 Phase shifted clock (input). This signal is connected to ENCClkOut (ENC chip), and inputs a

ENC ENCClkOut 6 Phase shifted clock (output). This signal is connected to ENCClkIn (ENC chip), and outputs a

ENC CPAddr0

CPAddr2

CPAddr3

ENC ~CPWrite 13 ENC chip to CP chip communication write (input). This signal is connected to the ~I/OWrite

ENC CPCntrl0 15 ENC chip to CP chip communication control (input). This signal is connected to the I/OCntrl0

ENC CPData2

CPData3

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

ENC Vcc 3, 14, 16, 25, 35 ENC chip supply voltage pin. All of these pins must be connected to the supply voltage.

ENC GND 10, 21, 32, 34, 43 ENC chip ground pin. All of these pins must be connected to the power supply return.

30

36

17

18

27

28

5

29

24

20

23

22

19

9

31

41

42

44

1

12

2

Quadrature A, B channels for axis 1 - 4 (input). Each of these 4 pairs of quadrature (A, B)

signals provide the position feedback for an incremental encoder. When the encoder is

moving in the positive, or forward direction, the A signal leads the B signal by 90 degs.

NOTE: Many encoders require a pull-up resistor on each of these signals to establish a

proper high signal (check the encoder electrical specifications)

NOTE: For MC1451A-E all 8 pins are valid. For MC1251A-E pins for axes 1 & 2 only are

valid. For MC1151A-E pins for axis 1 only are valid. Invalid axis pins can be left unconnected.

provides the clock signal for the ENC chip. The frequency of this signal is 1/4 the userprovided ClkIn (CP chip) frequency.

phase shifted clock signal.

phase shifted clock signal.

ENC chip to CP chip communication address (input). These 3 signals are connected to the

corresponding CPAddr0, 2, & 3 pins (CP chip), and together provide addressing signals to

facilitate CP to ENC chip communication.

NOTE: There is no CPAddr1 pin on the ENC chip.

pin (CP chip) and provides a write strobe to facilitate CP to ENC chip communication.

pin (CP chip), and provides control signals to facilitate CP to ENC chip communication.

ENC chip to CP chip data port (bi-directional). These 10 bits are connected to the

corresponding Data2-11 pins on the CP chip, and facilitate communication to/from the ENC

and CP chips.

Supply voltage = 4.75 to 5.25 V

16

Page 17

Theory of Operations

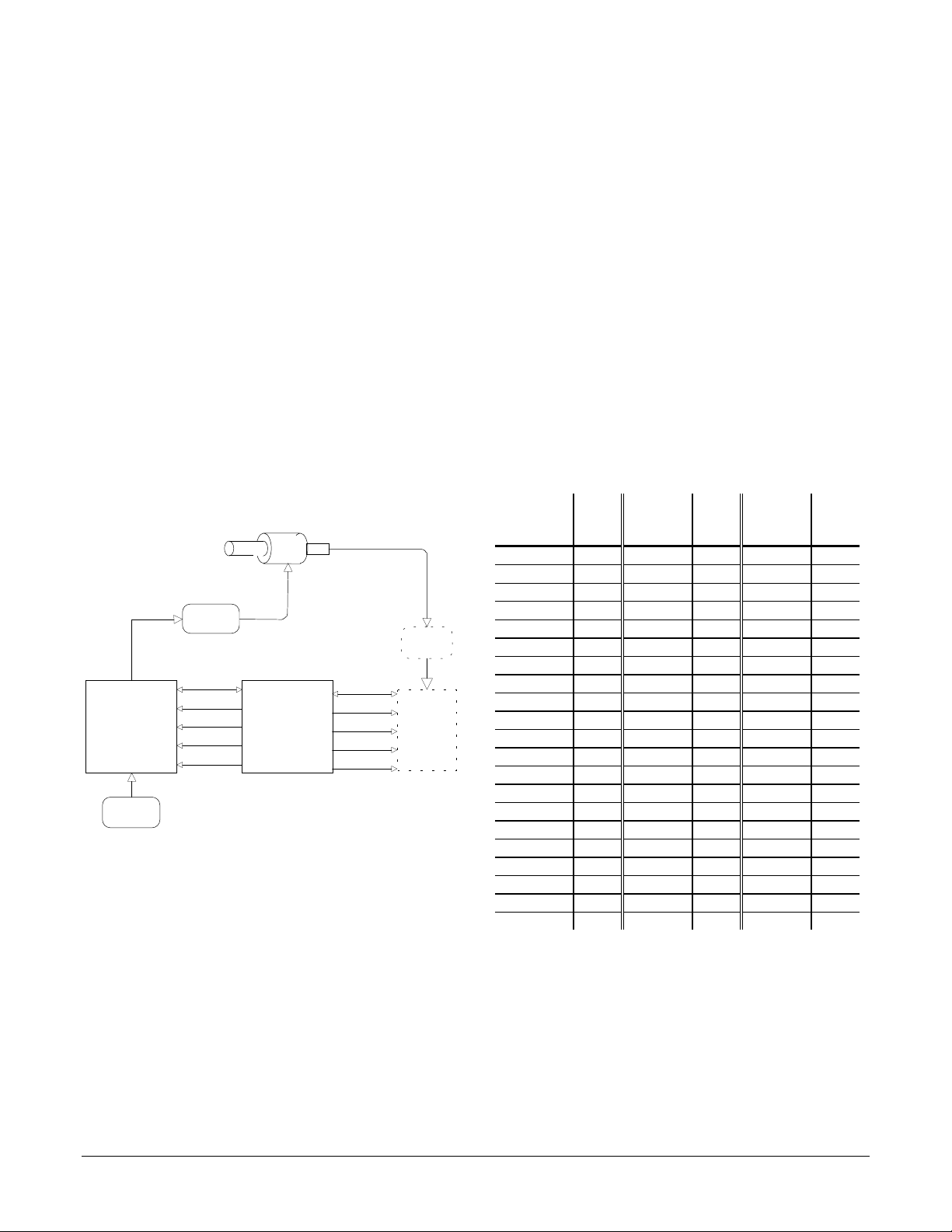

Internal Block Diagram

Home

Input

Motor Output Signals

Step Direction

1/a 1/a1/a

CP Chip

Pulse & Direction

Generator (1-4)

Trajectory profile

generator (1-4)

I/O Chip

System Registers (1-4)

Host I/O controller

185

host interr up tDataControl

Host I/O

The above figure shows an internal block diagram for the MC1451A

and MC1451A-E Motion Processors.

The MC1451-series chipsets consist of two chips, an ASIC (Application

Specific I.C.) called the I/O chip and a DSP (Digital Signal Processor)

called the CP chip. The MC1451-E series chipsets consist of these

same two chips along with an additional ASIC chip called the ENC chip.

The function of the I/O ASIC is to perform host I/O as well as pulse

generation. The function of the CP chip is to perform all motion

computations. The function of the ENC chip is to perform quadrature

position decoding.

The chipset supports up to four axes simultaneously. Each axis

provides programmable trajectory generation including electronic

gearing, trapezoidal point-to-point, s-curve point to point, and a velocity

contouring mode.

The chipset calculates all trajectory information on a cycle-by-cycle

basis. Each cycle results in a new desired pulse rate based on the

trajectory generator mode and the specified trajectory parameters. By

Host command

Miscellaneous Signals

At Rest

1/a

Encoder Inputs

BA

1/a 1/a

Quadrature

decoder

counter (1-4)

ENC

Chip

1/a

PosLimit

Overtrav el I npu t s

feeding the resulting pulse rate to the pulse generating circuitry of the

I/O ASIC at each cycle, continuous and smooth motion is achieved for

all four axes.

The I/O ASIC provides high speed pulse and direction generation

appropriate for interfacing to a wide variety of standard stepper drivers.

Two pulse rate operating modes are provided, one which results in a

pulse rate range of 0 - ~48,000 pulses per second (standard range),

and one which results in a pulse rate range of 0 - ~1,500,000 pulses per

second (high speed range).

The encoder feedback, which is available through the optional ENC

chip, is updated at each chipset cycle. This information can be used by

the host to check that the axis has achieved a desired position.

Additionally, the chipset can use the encoder information to

automatically detect a motor stall condition while a move is ongoing.

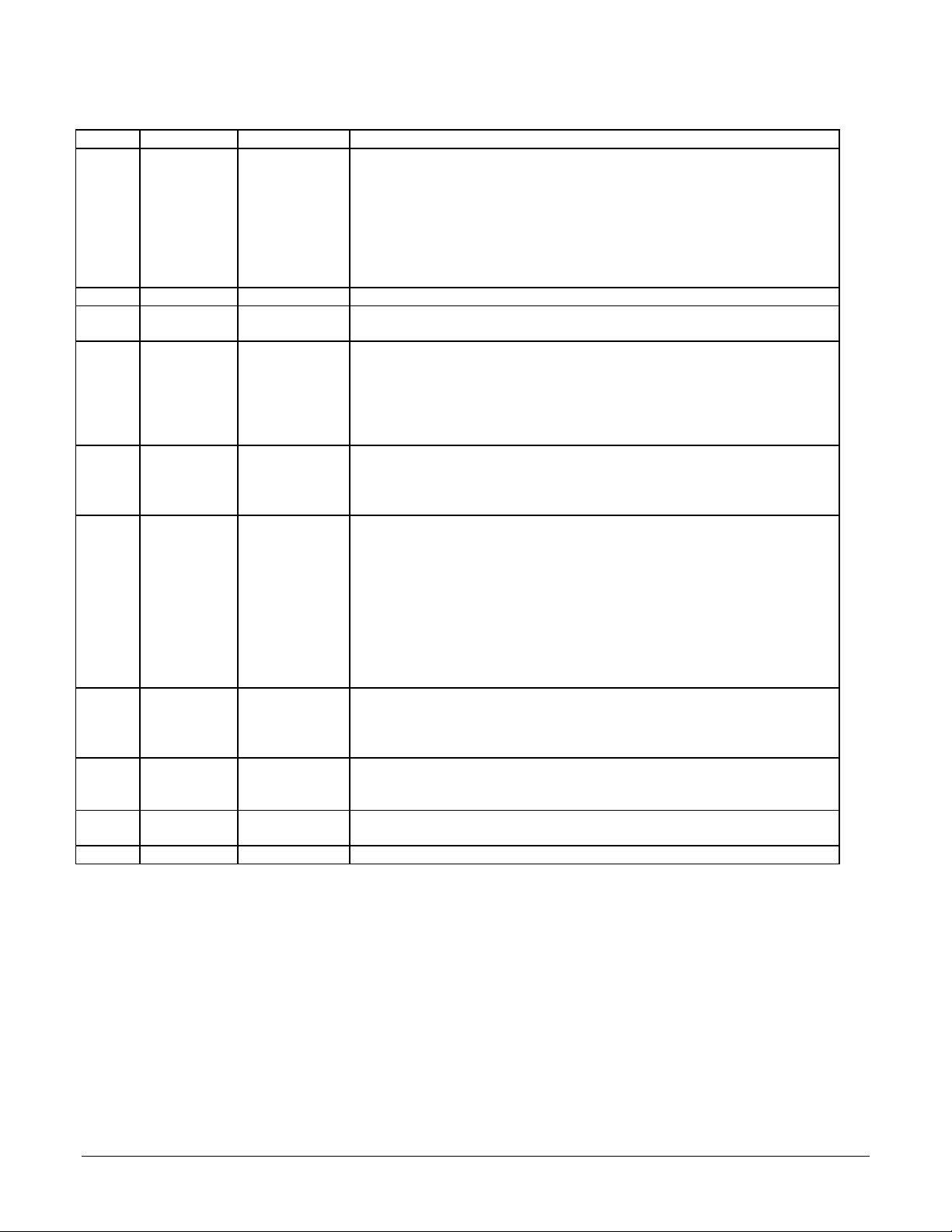

The following table summarizes the operational parameters of the

MC1451-series chipsets.

1/a

NegLimit

17

Page 18

MC1451-Series Chipset Operational Parameters

Available configurations: MC1451A 4 axis step and direction motion chipset

MC1251A 2 axis step and direction motion chipset

MC1151A 1 axis step and direction motion chipset

MC1451A-E 4 axis step and direction motion chipset with quadrature input

MC1251A-E 2 axis step and direction motion chipset with quadrature input

MC1151A-E 1 axis step and direction motion chipset with quadrature input

Position Range: -1,073,741,824 to 1,073,741,823 steps

Velocity Range: -16,384 to 16,383 steps/cycle with a resolution of 1/65,536 steps/cycle

Acceleration Range:

Jerk Range: -1/2 to +1/2 steps/cycle, with a resolution of 1/4,294,967,296 steps/cycle

Start velocity range -32,768 to +32,767 steps/cycle with a resolution of 1/65,536 steps/cycle

Trajectory Profile Generator Modes: S-curve (host commands final position, max velocity, max acceleration, and jerk)

Electronic Gear Ratio Range: 32768:1 to 1:32768 (negative and positive direction)

Motor output signals Pulse and direction (1 each per axis)

Max. pulse rate standard speed range: 48.828 Kpulses/sec

Encoder Input Signals: A, B quadrature signals (MC1451A-E, MC1251A-E, MC1151A-E chipsets only)

Maximum Encoder Input Rate: 1.25 MCounts/sec (MC1451A-E, MC1251A-E, MC1151A-E chipsets only)

Encoder Feedback Modes: Manual position read (host queries position) (MC1451A-E, MC1251A-E, MC1151A-E chipsets only)

Stall detection counts/steps ratio

range:

Cycle loop rate: 330 uSec*

# of limit switches per axis 2 (one for each direction of travel)

Per axis hardware control lines Home signal (one per axis)

# of Host commands: 72

S-curve profile: - 1/2 to + 1/2 steps/cycle with a resolution of 1/65,536 steps/cycle

All others: -16,384 to 16,383 steps/cycle with a resolution of 1/65,536 steps/cycle

(used with trapezoidal and velocity profile modes only)

Trapezoidal (host commands final position, max velocity, starting velocity, and acceleration)

Velocity contouring (host commands max velocity, starting velocity, acceleration)

Electronic Gear (Encoder position is used as position command for corresponding axis).

(available only with MC1451A-E, MC1251A-E, MC1151A-E chipsets)

high speed range: 1.5625 Mpulses/sec

Automatic stall detection (stall detected on-the-fly) (MC1451A-E, MC1251A-E, MC1151A-E chipsets only)

1/256 - 127 encoder counts/step (MC1451A-E, MC1251A-E, MC1151A-E chipsets only)

Limit Switch (two per axis)

At rest signal (one per axis, output to amplifier)

.

*exact time is 327.68 uSec, 330 is an approximation

Trajectory Profile Generation

The trajectory profile generator performs calculations to determine the

target position, velocity and acceleration at each calculation cycle.

These calculations are performed taking into account the current profile

mode, as well as the current profile parameters set by the host. Four

trajectory profile modes are supported:

- S-curve point to point

- Trapezoidal point to point

- Velocity contouring

- Electronic Gear

The commands to select these profile modes are

SET_PRFL_S_CRV (to select the s-curve mode), SET_PRFL_TRAP

(to select the trapezoidal mode) SET_PRFL_VEL (to select the

velocity contouring mode) and SET_PRFL_GEAR (to select the

electronic gear mode).

Throughout this manual various command mnemonics will be

shown to clarify chipset usage or provide specific examples. See

the Host Communications section for a description of host

command nomenclature.

18

Page 19

The profile mode may be programmed independently for each axis. For

example axis #1 may be in trapezoidal point to point mode while axis

#2 is in S-curve point to point.

Use the following figure showing a typical S-curve velocity vs. time

graph for reference in reading the next section:

Generally, the axis should be at rest when switching profile modes.

Under certain conditions however, switching into certain profile modes

"on-the-fly" is allowed. See specific profile descriptions for details.

S-curve Point to Point

The following table summarizes the host specified profile parameters

for the S-curve point to point profile mode:

Profile

Parameter

Destination

Position

Maximum

Velocity

Max. Accel.

Jerk

* uses 1/216 scaling. Chipset expects a 32 bit number which

has been scaled by a factor of 65,536 from units of

steps/cycle. For example to specify a velocity of 2.75

steps/cycle 2.75 is multiplied by 65,536 and the result is sent

to the chipset as a 32 bit integer (180,224 dec. or 2c000 hex.).

** uses 1/216 scaling. Chipset expects a 16 bit number which

has been scaled by a factor of 65,536 from units of

steps/cycle2. For example to specify an acceleration of .175

steps/cycle2, .175 is multiplied by 65,536 and the result is

sent to the chipset as a 16 bit integer (11,469 dec. or 2ccd

hex).

Representation & Range Units

signed 32 bits

steps

-1,073,741,824 to 1,073,741,823

unsigned 32 bits* (1/2

16

scaling)

steps/cycle

0 to 1,073,741,823

unsigned 16 bits ** (1/2

16

scaling)

steps/cycle

0 to 32,767

unsigned 32 bits *** (1/2

32

scaling)

steps/cycle

0 to 2,147,483,647

PhaseI.Phase

Phase

II.

III.

Phase

IV.

PhaseV.Phase

VI.

Phase

VII.

S-curve profile

The S-curve profile drives the axis at the specified jerk until the

maximum acceleration is reached. (phase I). it will then drive the axis at

2

jerk = 0 (constant acceleration) through phase II. It will then drive the

axis at the negative of the specified jerk though phase III, such that the

3

axis reaches the specified maximum velocity with acceleration = 0. This

completes the acceleration phase. At the end of the acceleration phase

of the move, the velocity will be constant, and the acceleration will be 0.

At the appropriate time, the profile will then decelerate (phases V, VI

and VII) symmetrically to the acceleration phase such that it arrives at

the destination position with acceleration and velocity = 0.

There are several conditions where the actual velocity graph of an Scurve motion will not contain all of the segments shown in the above

figure. For example, if the max. acceleration is not reached before the

"half-way" point to the max. velocity, then the actual velocity profile will

not contain a phase II or a phase VI segment (they will have a duration

of 0 cycles). Such a profile is shown below:

PhaseI.Phase

III.

Phase

IV.

PhaseV.Phase

VII.

*** uses 1/2

has been scaled by a factor of 4,294,967,296 (2

32

scaling. Chipset expects a 32 bit number which

32)

from units

of steps/cycle3. For example to specify a jerk value of .0075

steps/cycle3, .0075 is multiplied by 4,294,967,296 and the

result is sent to the chipset as a 32 bit integer (32,212,256

dec. or 1eb8520 hex).

S-curve that doesn't reach max. acceleration

Another such condition is if the position is specified such that max.

velocity is not reached. In this case there will be no phase IV, and there

may also be no phase II and VI, depending on where the profile is

"truncated".

While the S-curve profile is in motion, the user is not allowed to

change any of the profile parameters. The axis must be at rest

before a new set of profile parameters can be executed. If

parameters are changed during motion then a 'command error'

19

Page 20

will occur, and all new parameters will be ignored except the

position. See the section of this manual entitled "Command Error"

for more information..

Before switching to the S-curve point to point profile mode, the

axis should be at a complete rest.

When the axis is in the S-curve profile mode, the SET_MAX_ACC

command should be used to load the max. acceleration value. The

alternate acceleration loading command SET_ACC can not be

used.

The following figure shows a velocity profile for a typical point to point

trapezoidal move, along with a more complicated move involving on the

fly changes to the maximum velocity and the destination position.

Vel.

Time

Simple trapezoidal mode motion

Trapezoidal Point to Point

The following table summarizes the host specified profile parameters

for the trapezoidal point to point profile mode:

Profile

Parameter

Destination

Position

Maximum

Velocity

Starting

Velocity

Accel.

In the trapezoidal point to point profile mode the host specifies a

destination position, a maximum velocity, a starting velocity, and an

acceleration. The trajectory is executed by accelerating at the

commanded acceleration, beginning at the starting velocity, to the

maximum velocity where it coasts until decelerating such that the

destination position is reached with the axis at rest (zero velocity). If it is

not possible to reach the maximum velocity (because deceleration must

begin) then the velocity profile will have no "coasting" phase. The

acceleration rate is the same as the deceleration rate.

Representation & Range Units

signed 32 bits

steps

-1,073,741,824 to 1,073,741,823

unsigned 32 bits (1/2

16

scaling)

steps/cycle

0 to 1,073,741,823

unsigned 32 bits, (1/2

16

scaling)

steps/cycle

0 to 1,073,741,823

unsigned 32 bits (1/2

16

scaling)

steps/cycle

0 to1,073,741,823

2

Vel.

change max

velocity

change destination

position

Complex trapezoidal mode motion

change destination

position

Vel.

change max

starting

velocity

Trapezoidal Profile With Non-Zero Starting Velocity

velocity

Velocity Contouring

Time

Time

A new maximum velocity and destination position can be specified

while the axis is in motion. When this occurs the axis will accelerate or

decelerate toward the new destination position while attempting to

satisfy the new maximum velocity condition.

Before switching to the Trapezoidal point to point profile mode,

the axis should be at rest.

When in Trapezoidal point to point profile mode, to change the

acceleration, the axis must come to a complete stop. After this has

occurred, a new acceleration value can be loaded. If the

acceleration parameter is changed during motion then a

'command error' will occur, and all updated parameters will be

ignored except the position. See the section entitled 'Axis Status

for more informaton' on command errors.

The Starting Velocity can not be changed while the axis is in

motion.

The following table summarizes the host specified profile parameters

for the Velocity contouring profile mode:

Profile

Representation & Range Units

Parameter

Maximum

Velocity

Starting

Velocity

Acceleration

unsigned 32 bits (1/2

0 to 1,073,741,823

unsigned 32 bits, (1/2

0 to 1,073,741,823

signed 32 bits* (1/2

16

16

16

scaling)

scaling)

scaling)

-1,073,741,824 to 1,073,741,823

* negative numbers using 1/216 scaling are handled no

differently than positive numbers. For example if an

acceration value of -1.95 steps/cycle2 is desired, -1.95 is

20

steps/cycle

steps/cycle

steps/cycle

2

Page 21

multipled by 65,536 and the result is sent to the chipset (127,795 dec. or fffe0ccd hex).

In this profile mode the host specifies two parameters, the commanded

acceleration, and the maximum velocity. The trajectory is executed by

continuously accelerating the axis at the commanded rate until the max.

velocity is reached, or until a new acceleration command is given.

The maximum velocity value must always be positive. Motion

direction is controlled using the acceleration value. Positive

acceleration values result in positive motion, and negative values

result in negative motion.

There are no restrictions on changing the profile parameters on

the fly. Note that the motion is not bounded by position however.

It is the responsibility of the host to generate acceleration and

max. velocity command values which result in safe motion, within

acceptable position limits.

The following figure shows a typical velocity profile using this mode.

Example Velocity Contouring Mode

Vel.

change

acceler a tion

In this way the output of the pulse and direction generator will precisely

track the input encoder position factored by a programmable gear ratio.

This can be useful in many applications where continuous

synchronization with an external mechanism is important.

The following figure shows the arrangement for encoders and motor

drives in a typical electronic gearing application with the MC1451A

Master

Encoder

MC1451-E

Only one of four axes shown

Pulse &

Direction

Amplifier

Motor

The total number of geared axes supported per chipset is equal to the

number of motor axes. For each motor axes the encoder input for the

same axis is used as the master position command. In addition these

master/slave combinations are fixed, with the encoder for axis 1 driving

the axis 1 pulse and direction generator, and the encoder for axis 2

driving the axis 2 pulse and direction generator.

change

max velocity

change max

velocity and

acceler a tion

There are no restrictions on switching the profile mode to velocity

contouring while the axis is in motion.

The Starting Velocity can not be changed while the axis is in

motion.

Electronic Gear

The following table summarizes the host specified profile parameters

for the electronic gear profile mode:

Profile

Parameter

Gear Ratio

* for example to specify a gear ratio of +1.5 to 1 the value

1.5*65,536 is sent to the chipset (98,304). Alternatively to set

the gear ratio as -11.39 to 1 the value -11.39*65,536 is sent (746,455 dec. or fff49c29 hex.).

In this profile mode, the host specifies one parameter, the gear ratio.

The target position is generated by applying the specified gear ratio to

the encoder position of the same axis, multiplying by the specified gear

ratio and outputting the corresponding number of pulses.

Representation & Range Units

signed 32 bits* (1/2

16

scaling)

-

-1,073,741,824 to +1,073,741,823

Time

There are no restrictions on changing the gear ratio when the axis

is in motion, although care should be taken to select ratios such

that safe motion is maintained.

There are also no restrictions on changing to this profile mode

while the axis is in motion.

Trajectory Control

Normally each of the above trajectory modes will execute the specified

trajectory, within the specified parameter limits, until the profile

conditions are satisfied. For example for the point-to-point profile modes

this means that the profile will move the axis until the final destination

position has been reached, at which point the axis will have a velocity

of zero.

Halting The Trajectory

In some cases however it is necessary to halt the trajectory manually,

for safety reasons, or simply to achieve a particular desired profile. This

can be accomplished using one of two methods; abrupt stop, or smooth

stop.

Abrupt stops are accomplished using the STOP command. This

command instantaneously stops the trajectory generator by setting the

velocity of the axis to zero. This control mode is typically used during an

emergency stop, when no deceleration phase is desired.

Smooth stops are accomplished using the SMOOTH_STOP command.

This command causes the trajectory to decelerate at a rate equal to the

21

Page 22

specified acceleration rate, until a velocity of zero is reached. In

addition the form of the deceleration is symmetric to the acceleration

phase. For example if the profile mode is S-curve, and a

SMOOTH_STOP command is given, the profile will decelerate in a

manner exactly equal and opposite to the acceleration phase.

The STOP command functions in all profile modes; S-curve pointto-point, Trajectory point-to-point, Velocity Contouring, and

Electronic Gear.

Contouring profile modes only. They do not func tion when the

profile mode is set to electronic gearing.

The motion complete and in-motion bits indicate the state of the

trajectory generator, not the actual motor. Even if the trajectory

generator has completed a motion, the actual axis position may or

may not be at rest depending on motor stability, and other system

conditions.

The SMOOTH_STOP functions in S-curve point-to-point,

Trajectory point-to-point, and Velocity Contouring profiling mode.

It does not function in Electronic Gear mode.

Caution should be exercised when using the STOP command due

to the large and abrupt changes in motion that may occur.

Motion Complete Status

To simplify the programming of a complete motion system it is

convenient to have the motion chipset indicate when a particular profile

move has been completed.

This function is provided by two status bits in the chipset's status word

(See the section of this manual entitled "Axis Status " for more

information on the axis status word). These two bits are called the

motion complete bit, and the in-motion bit.

The motion complete bit is controlled interactively by the chipset and

the host. After a motion has completed, the chipset sets the motion

complete bit on. The host may then poll this bit to determine that motion

is complete, or if desired, the host can program the chipset to

automatically signal when the motion is complete (using an interrupt). In

either case once the host has recognized that the motion has been

completed the host clears the motion complete bit, enabling the bit to

indicate the end of motion for the next move.

The following list shows the conditions that will cause the motion

complete bit to occur:

- Profile has reached the destination position (point-to-point

profile modes only)

- Axis trajectory reaches a velocity of zero and the current

velocity command is zero

- SMOOTH_STOP command is given and axis trajectory

reaches a velocity of zero

- STOP command is given

- Limit switch condition occurs

Parameter Loading & Updating

Various profile & motor control parameters must be specified by the

host for an axis to be controlled in the desired manner. To facilitate

precisely synchronized motion, these parameters and related control

commands are loaded into the chip using a double-buffered scheme. In

this scheme, the parameters and action commands being loaded are

not acted upon (copied from the double-buffered to the active registers)

until an update signal is given.

This update signal can consist of either a "manual" update command or

one of several conditional breakpoints. Whichever update method is

used, at the time the update occurs, all of the double buffered registers

and commands will be copied to the active registers. Conversely,

before the update occurs, loading the double-buffered registers or

executing the double buffered commands will have no effect on the

system behavior.

The double buffered registers are listed below.

Register Name Command to set

destination position SET_POS

maximum velocity SET_VEL

acceleration SET_ACC

maximum acceleration SET_MAX_ACC

jerk SET_JERK

ratio SET_RATIO

buffered motor command SET_BUF_MTR_CMD

The double-buffered commands are: STOP, SMOOTH_STOP, and

SYNCH_PRFL.

Manual Update

There are two methods of manually updating the double-buffered

parameters & commands, one for a single axis instantaneous update

and one for a multiple-axis update.

The in-motion bit is similar to the motion complete bit except that it

continuously indicates the status of the axis without interaction with the

host. In addition this bit is used exclusively for polled mode operations.

It can not cause an interrupt to the host to be generated.

The motion complete and the in-motion indicator bits function in

the S-curve point-to-point, Trapezoidal point-to-point, and Velocity

The single axis instantaneous update, which is specified using the

UPDATE command, forces the parameters for the current axis to be

updated at the next cycle.

The multiple axis instantaneous update, which is specified using the

MULTI_UPDATE command, causes multiple axes to be updated

simultaneously. This can be useful when synchronized multi-axis

profiling is desired. This command takes a 1 word argument which

22

Page 23

consists of a bit mask, with 1 bit assigned to each axis. Executing this

command has the same affect as instantaneously switching to each

desired axes, and executing an UPDATE command.

Breakpoints

A breakpoint is a convenient way of programming a profile or other

double-buffered parameter change upon some specific condition. There

are two types of breakpoints, those that have a 32-bit comparitor value

associated with them and those that do not. For those that have the

comparitor, a 32-bit comparitor value is loaded into the breakpoint

compare register first, and then one of the breakpoint conditions is

specified. For those breakpoint modes without associated comparitor

values only the breakpoint condition needs to be specified.

The double-buffered registers and commands will be updated upon

satisfaction of the specified breakpoint condition.

Here is a list of all of the available breakpoint conditions.

Positive

A 32 bit position breakpoint can be specified which will result in

the parameters being updated when the current target position

(the instantaneous desired axis position output from the profile

generator) equals or exceeds the specified breakpoint value. This

breakpoint is set using the SET_POS_BRK command.

Negative

A 32 bit position breakpoint can be specified which will result in

the parameters being updated when the current target position

(the instantaneous desired axis position output from the profile

generator) equals or is less than the specified breakpoint

value.This breakpoint is set using the SET_NEG_BRK command.

Positive

A 32 bit position breakpoint can be specified which will result in

the parameters being updated when the current actual position

(the instantaneous position of the actual axis hardware) equals or

exceeds the specified breakpoint value.This breakpoint is set

using the SET_ACTL_POS_BRK command.

Position Breakpoint

Target

Position Breakpoint

Target

Position Breakpoint

Actual

Motion Complete Breakpoint

A breakpoint can be specified which will result in the parameters

being updated when the previous motion has been completed

(motion complete bit is set). When using this breakpoint no 32 bit

compare value is required.

External Breakpoint

A breakpoint can be specified which will result in the parameters

being updated when the home signal of the corresponding axis

becomes active (low). When using this breakpoint no 32 bit

compare value is required. This breakpoint is useful whenever it is

desired that an external signal starts, stops, or otherwise modifies

the profile movement.

Normally, whenever one of these conditions has been programmed and

the condition occurs, the double-buffered parameters will automatically

be shifted to the active registers. There is a mechanism to disable this

"automatic update upon breakpoint" however. This is discussed in the

next section.

The above breakpoint modes are particularly useful during multi-axis

motion. This is because the next profile commands (set of hostspecified trajectory commands) can be pre-loaded and activated at the

precise position or time required, with no delay incurred to send an

update or load parameters command.

After a breakpoint condition has been satisfied it i s no longer

active. To set up another breakpoint condition, a new one must be

explicitly set by the host.

The double-buffered registers that are shifted to the active

registers do not change upon being shifted, only the active

registers change.

Except for the MULTI_AXIS command, parameter loading and updating

is controlled individually for each axis. In addition each axis has a

separate 32-bit breakpoint register, and can be set to various individual

breakpoint conditions.

External Breakpoints and Homing

Negative

A 32 bit position breakpoint can be specified which will result in

the parameters being updated when the current actual position

(the instantaneous position of the actual axis hardware) equals or

is less than the specified breakpoint value.This breakpoint is set

using the SET_ACTL_NEG_BRK command.

Time Breakpoint

A 32 bit time break point can be specified which will result in the

parameters being updated when the # of cycles executed since

chip set reset (the current chip set time) is equal to the time

breakpoint value.The # of cycles continuously increases until it

rolls over from 232 - 1 back to 0.The time breakpoint is set using

the SET_TIME_BRK command.

Position Breakpoint

Actual

By connecting a home input sensor to the home signal input of the

MC1451-series chipsets it is possible to cause the chipset to halt a

motion at the moment it receives the home signal. This capability

makes it ideal for performing a home sequence. The following host I/O

sequence illustrates this:

GET_HOME ; check to make sure axis not already at

; home. If so, then a 'reverse' move must

; be made to retract axis from home switch.

; This ‘reversing’ sequence is not

; indicated here for simplicity sake

SET_POS 12345 ; load home move parameters

SET_VEL 23456

SET_ACC 345

UPDATE ; start home move

SET_EXT_BRK ; initiate external breakpoint mode

23

Page 24

STOP ; load (but do not update) a stop command

This sequence will start a homing move which will stop as soon as the

axis encounters the home switch.

As is the case for all of the breakpoint modes, the external breakpoint

can not only be use to stop an ongoing move, but to start or otherwise

modify a move as well. This flexibility makes it well suited for

applications such as cut-on-the-fly where externally-initiated motions

are required.

Disabling Automatic Profile Update

Normally, when a breakpoint condition has been satisfied, it causes the

profile and other double-buffered parameters to be automatically

updated. For certain types of profiles however, it may be desirable to

still use the breakpoint mechanism (to allow it to generate a host

interrupt for example), but not to have the profile update.

2) Upon entering an over-travel condition, the trajectory generator

will automatically be halted, so that the motor does not travel

further into the over travel region.

To recover from an over-travel condition the corresponding status bits

in the status word should be reset (see the section of this manual on

axis status for details on resetting status word bits). Once this has been

performed the host can command a trajectory move to bring the axis

out of the over-travel region.

The over-travel detector is 're-armed' when the axis exits the over travel

condition.

Only one over-travel signal can be processed at a time. For

example if the negative over travel switch becomes active, the

corresponding status bits must be cleared, and the axis moved

into the legal travel range before a positive over travel switch will

be recognized.

Whether the profiles are automatically updated or not for a given axis is

controlled by the commands SET_AUTO_UPDATE_ON and

SET_AUTO_UPDATE_OFF. When auto update is set to on, the

breakpoint/profile mechanism behaves as described above. When set

to off, upon a breakpoint condition, no profile update will occur. When in

this mode the only way to update the profile is to use the UPDATE

command or the MULTI_UPDATE command.

Travel Limit Swit ches

The MC1451-series chipsets support motion travel limit switches that

can be used to automatically recognize an "end of travel" condition.

The following figure shows a schematic representation of an axis with

travel-limit switches installed, indicating the "legal" motion area and the

over-travel regions.

negative limit

switch

negative

over-travel

region

There are two primary services that the MC1451A provides in

connection with the over-travel limit switch inputs:

1) The host can be automatically notified that an axis has entered

an over-travel condition, allowing the host to take appropriate

special action to manage the over-travel condition.

Legal travel region

positive limit

switch

positive

over-travel

region

Axis Timing

Each axis of the MC1451-series chipsets receives a "time slice" of the

available computation power of the CP chip. The amount of time

required for the chipset to perform one complete pass of calculations for

all of the axes is known as the chipset cycle time. This chipset cycle

time is important to the host processor because it determines the rate at

which profile trajectories are updated.

The cycle time is the same for all MC1451-series chipsets. The cycle

time value is 330 uSec*. All velocities, accelerations, and jerk values

are related to this cycle time via the various trajectory generator modes

that generate axis motion.

* exact cycle time is 327.68 uSec, 330 is an approximation.