Page 1

Advanced Brushless Moto r

j

Features

Supports 3-phase as well as 2-phase

brushless motors

Performs trajectory generation, servo

loop closure, and commutation

Ultra-smooth sinusoidal commutation

Open or closed loop operation

Software and feature-com pat ible w ith

other 1st generation PMD chipsets

Available in 1 or 2 axis configurations

32-bit position, velocity, acceleration and

erk trajectory profile registers

Choice of S-curve, trapezoidal, or

contoured velocity profile modes

Electronic Gearing

Two travel-limit switches per axis

Choice of PWM or DAC motor output

signals

Easy-to-use packet-oriented command

protocol

Control Chipset

General Description

The MC1231A is a dedicated motion processor which functions

as a complete chi p-based motor controller. Packaged i n a 2-IC

chipset, this device performs trajectory generation, servo loop

closure, and sinusoidal commutation. The chipset inputs

incremental encoder signals and outputs PWM or

DAC-compati b l e mo to r c omm and signals. The MC 1 231A is

available in a one, or a two-axis configuration.

MC1231A

MC1131A

The MC1231A is functionally similar to other members of

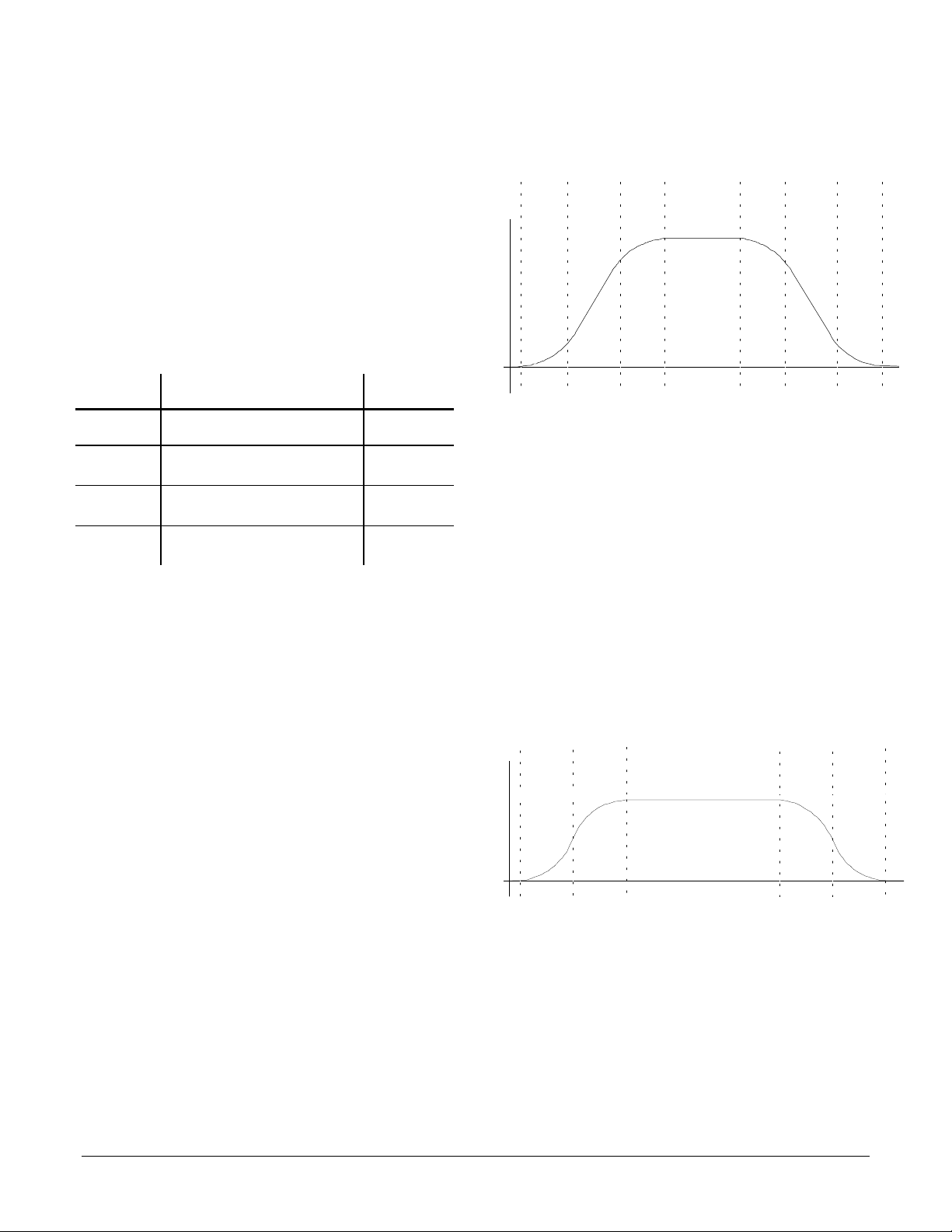

Commutation Waveforms

Phase A Phase B Phase C

Phase A Phase B

Performance Motion Dev ices, In c. 12 Waltham St. Le xington, M A 02421 te l: 781. 674.98 60 fax: 781.674.9 861

3-Phase Brushless

2-Phase Brushless

PMD's 1st generation chipset family however it adds the ability

to perform sinusoidal commutation of brushless motors. All of

these devices provide sophisticated motion control capabilities

allowing the creation of comp lex profile sequences with very low

tracking errors.

Both two and three-phase brushless motors are supported by

the MC1231A. Wh en used with two-phase brushless motors

each phase is separated by 90 d egrees. When used with

3-phase brushless motors each phase is separated by 120

degress. The commutation angle is continuously calculated

using the encoder position. User-programmable commutation

parameter s allow a very wide rang e of encoders and motors to

be controlled.

The chipset is controlled by a host processor which interfaces

with the chipse t via an 8-bit, bi-directional port. Commun ic ations

to/from the chi pset consist of pack et-oriented m essages.

The chipset is packaged in 2 68- pin PLCC package s. Both

chips utilize CMOS technology and are powered by 5 volts.

Doc. Rev. 10.05, Nov 1997

www.pmdcorp.com

Page 2

Table of Contents

Product Family Overview.......................................Page 3

Introduction........................................................... Page 3

Family Summary................................................... Page 3

Electrical Characteristics....................................... Page 4

Absolute Maximum Ratings.................................. Page 4

Operating Ratings................................................. Page 4

DC Electrical Characteristics................................ Page 5

AC Electrical Characteristics................................Page 5

I/O Timing Diagrams............................................. Page 7

Pinouts....................................................................Page 12

MC1231A, MC1131A............................................ Page 12

Pin Descriptions.................................................... Page 13

Theory of Operations............................................. Page 17

Operational Parameters.......................................Page 18

Trajectory Profile Generation................................ Page 18

S-curve Point to Point....................................... Page 19

Trapezoidal Point to Point.................................Page 20

Velocity Contouring...........................................Page 20

Electronic Gear................................................. Page 21

Trajectory Control................................................. Page 21

Halting the Trajectory ....................................... Page 21

Motion Complete Status...................................Page 22

Digital Servo Filtering ........................................... Page 22

Motor Bias........................................................ Page 23

Motor Limit........................................................Page 23

Parameter Loading & Updating............................Page 23

Manual Update.................................................Page 24

Breakpoints....................................................... Page 24

External Breakpoints and Homing.................... page 25

Disabling Automatic Profile Update..................Page 25

Travel Limit Switches............................................ Page 25

Motion Error Detection.......................................... Page 26

Recovering From a Motion Error......................Page 26

Servo Loop Control & Timing............................... Page 26

Host Communications .......................................... Page 27

Electrical Interface............................................ Page 27

Packet Format..................................................Page 27

Packet Checksum............................................. Page 28

Illegal Commands............................................. Page 28

Command Errors..............................................Page 28

Axis Addressing................................................ Page 29

Axis Status............................................................ Page 29

Status Word...................................................... Page 29

Miscellaneous Mode Status Word.....................Page 29

Host Interrupts.......................................................Page 30

Encoder Position Feedback..................................Page 31

Encoder FIltering...............................................Page 31

High Speed Position Capture............................Page 31

Index Pulses and Commutation........................Page 31

Motor Outputs.......................................................Page 31

Motor Output Control.........................................Page 32

Sinusoidal Commutation.......................................Page 31

Commutation Waveforms..................................Page 33

Commutation Parameters.................................Page 33

Index Pulse Referencing...................................Page 33

Commutation Error Detection............................Page 34

Phase Initialization............................................Page 34

Phase Initialization Programming......................Page 35

Adjusting The Commutation Angle....................Page 36

Encoder Pre-Scalar...........................................Page 37

Velocity-Based Phase Advance........................Page 37

Phase Info Status Word....................................Page 37

Commutation Command Summary...................Page 38

Motor Output Configuration...............................Page 38

Motor Output Signal Interpretation....................Page 38

DAC16 Decoding...............................................Page 39

PWM Decoding.................................................Page 39

Host Commands .....................................................Page 40

Command Summary.............................................Page 40

Command Reference............................................Page 42

Axis Control.......................................................Page 42

Profile Generation.............................................Page 43

Digital Filter.......................................................Page 46

Parameter Update.............................................Page 49

Interrupt Processing..........................................Page 51

Status/Mode......................................................Page 52

Encoder.............................................................Page 53

Motor.................................................................Page 54

Miscellaneous ...................................................Page 55

Commutation.....................................................Page 57

Application Notes ...................................................Page 62

Interfacing to ISA bus............................................Page 62

PWM Motor Interface............................................Page 64

16-Bit Parallel DAC Motor interface......................Page 66

Performance Motion Devices, Inc. does not assume any responsibility for use of any circuitry described in this manual, nor does it make

any guarantee as to the accuracy of this manual. Performance Motion Devices, Inc. reserves the right to change the circuitry described in

this manual, or the manual itself, at any time.

The components described in this manual are not authorized for use in life-support systems without the express written permission of

Performance Motion Devices, Inc..

2

Page 3

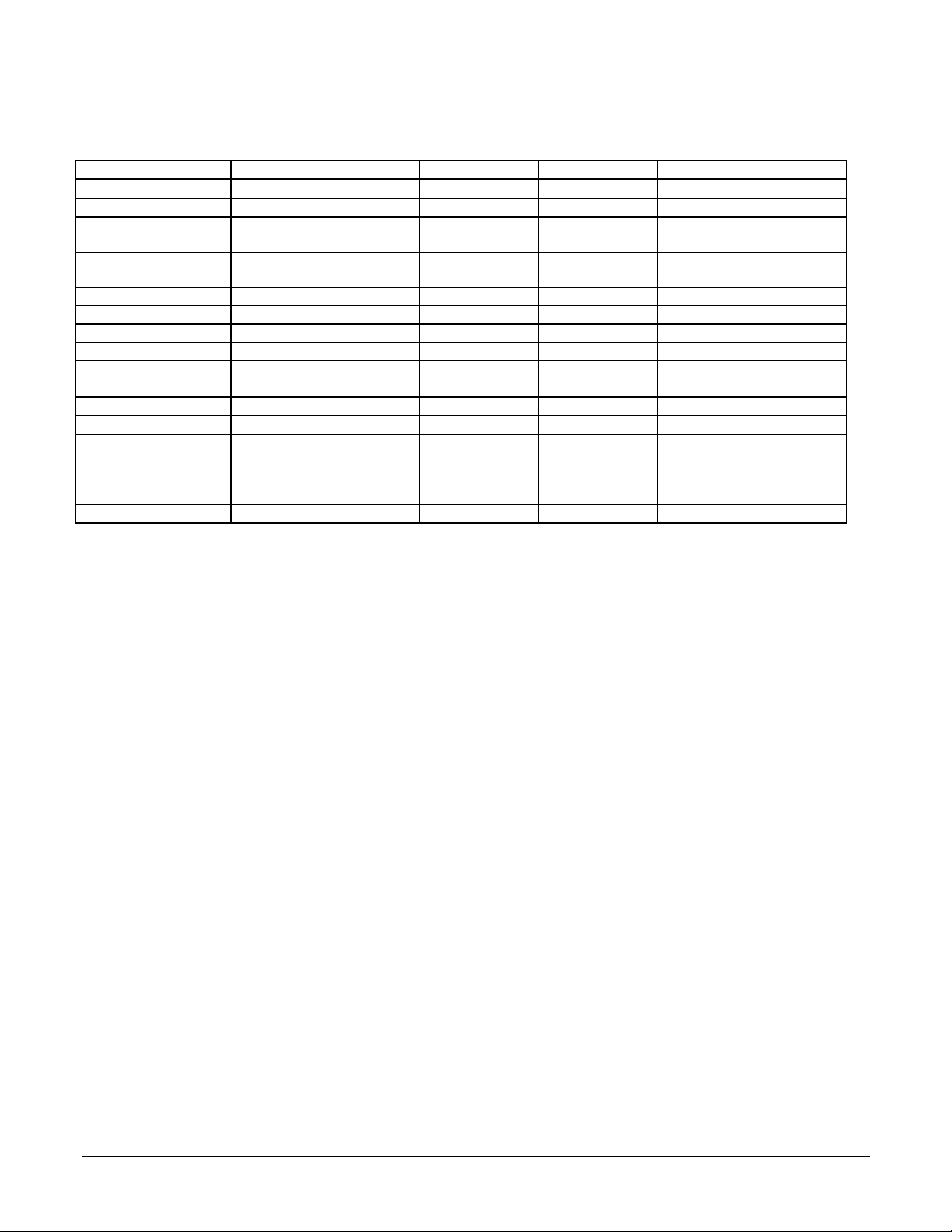

Product Family Overview

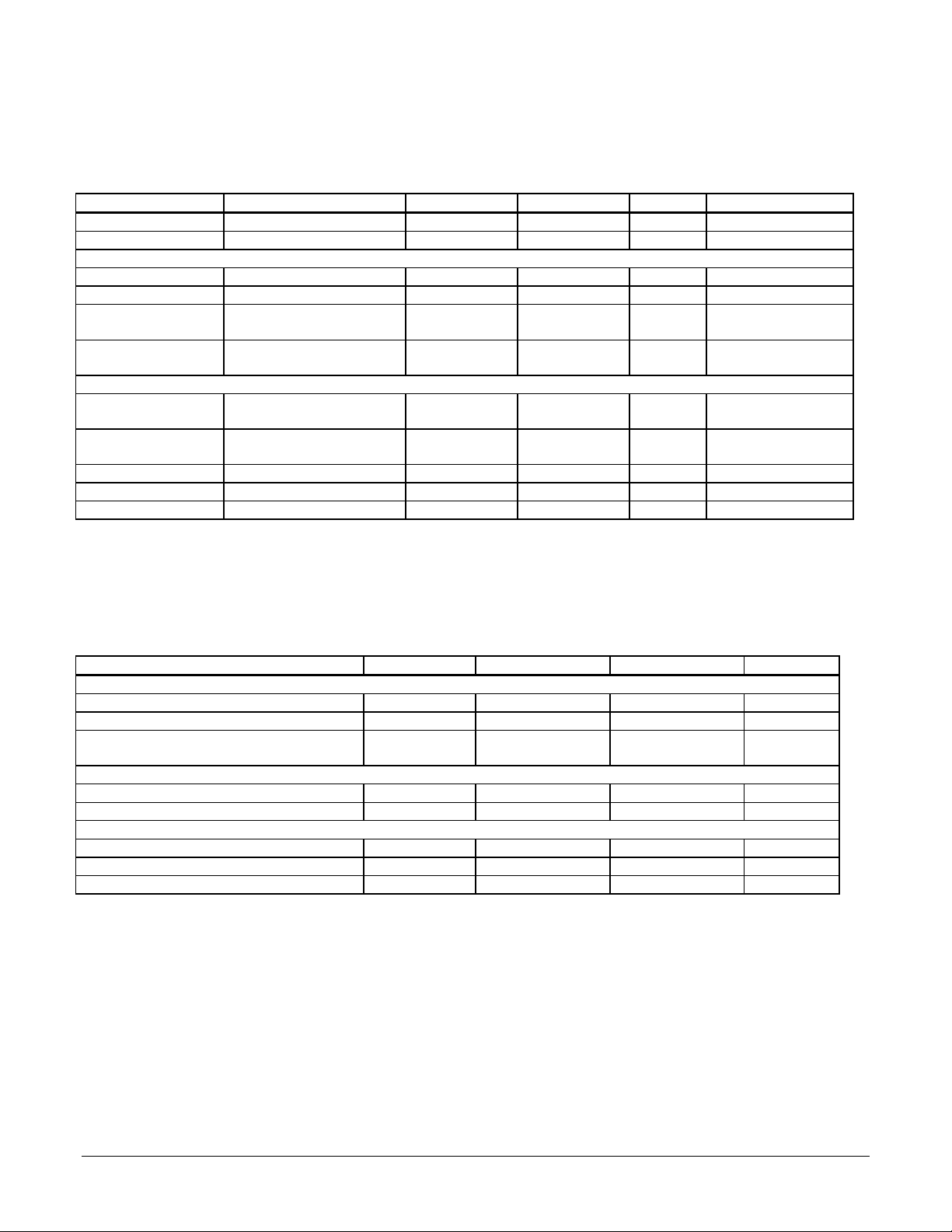

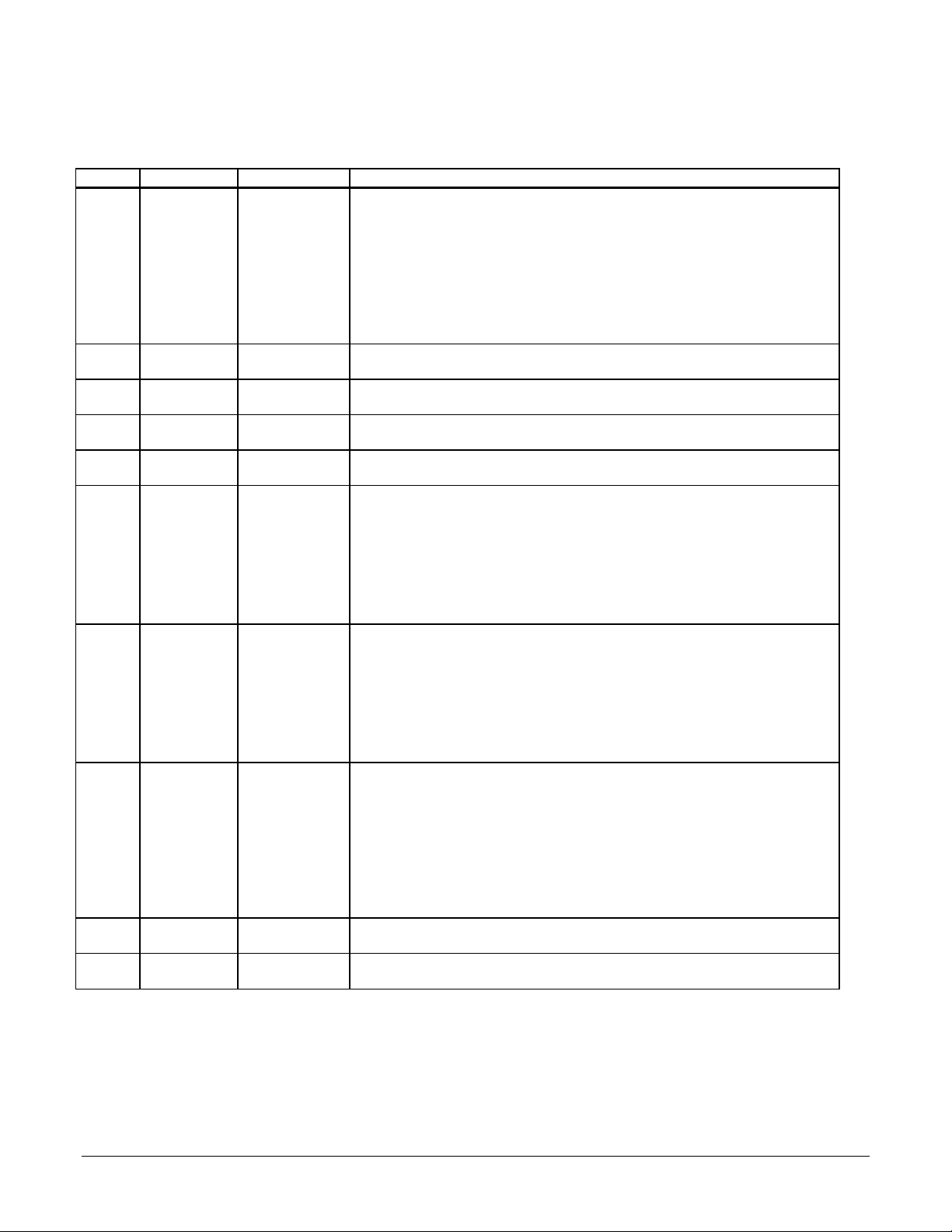

MC1401 series MC1231 series MC1241 series MC1451 series

# of axes 4, 2, or 1 2 or 1 2 or 1 4, 2, or 1

Motors Supported DC Servo Brushless Servo Stepper Stepper

Encoder Format Incremental (no dash version)

and Parallel ('-P' version)

Output Format DC servo Sinusoidally

S-curve profiling Yes Yes Yes Yes

Electronic gearing Yes Yes Yes Yes

On-the-fly changes Yes Yes Yes Yes

Limit switches Yes Yes Yes Yes

PID & feedforward Yes Yes - -

PWM output Yes Yes Yes -

DAC-compatible output Yes Yes Yes -

Pulse & direction output ---Yes

Index & Home signal Yes Yes Yes Yes*

Chipset p/n's MC1401A, MC1401A-P (4 axes)

MC1201A, MC1201A-P (2 axes)

MC1101A, MC1101A-P (1 axis)

Developer's Kit p/n's: DK1401A, DK1401A-P DK1231A DK1241A DK1451A

* optional using third I.C. ('-E' version)

Incremental Incremental Incremental*

Microstepping Pulse and Direction

commutated

MC1231A (2 axes)

MC1131A (1 axis)

MC1241A (2 axes)

MC1141A (1 axis)

MC1451A, MC1451A-E (4 axes)

MC1251A, MC1251A-E (2 axes)

MC1151A, MC1151A-E (1 axis)

Introduction

This manual describes the operational characteristics of the MC1231A,

and MC1131A Motion Processors. These devices are members of

PMD's 1st generation motion processor family, which consists of 16

separate products organized into four groups.

Each of these devices are complete chip-based motion controllers.

They provide trajectory generation and related motion control functions.

Depending on the type of motor controlled they provide servo loop

closure, on-board commutation for brushless motors, and high speed

pulse and direction outputs. Together these products provide a

software-compatible family of dedicated motion processor chips which

can handle a large variety of system configurations.

Each of these chips utilize a similar architecture, consisting of a highspeed DSP (Digital Signal Processor) computation unit , along with an

ASIC (Application Specific Integrated Circuit). The computation unit

contains special on-board hardware such as a multiply instruction that

makes it well suited for the task of servo control.

Along with a similar hardware architecture these chips also share most

software commands, so that software written for one chipset may be reused with another, even though the type of motor may be different.

This manual describes the operation of the MC1231A and

MC1131A chipsets. For technical details on other members of

PMD's 1st generation motion processors see the corresponding

product manual.

Family Summary

MC1401 series (MC1401A, MC1201A, MC1101A, MC1401A-P,

MC1201A-P, MC1101A-P)

encoder signals (standard version) or parallel word encoder signals

(-P version) and output a motor command in either PWM or DACcompatible format. These chipsets come in 1, 2 or 4 axis versions

and can be used with DC brushed motors, or brushless motors using

external commutation.

MC1231A series (MC1231A, MC1131A) -

incremental quadrature encoder signals and output sinusoidally

commutated motor signals appropriate for driving brushless motors.

They are available in one or two axis versions. Depending on the

motor type they output two or three phased signals per axis in either

PWM or DAC-compatible format.

MC1241 series (MC1241A, MC1141A)

internal microstepping generation for stepping motors. They are

available in a one or a two-axis version. Two phased signals are

output per axis in either PWM or DAC-compatible format. An

incremental encoder signal can be input to confirm motor position.

MC1451 series (MC1451A, MC1251A, MC1151A, MC1451A-E,

MC1251A-E, MC1151A-E) -

pulse and direction signal output appropriate for driving step motorbased systems. They are available in a one, two, or four-axis version

and are also available with quadrature encoder input.

Each of these chipsets has an associated Chipset Developer's

Kit available for it. For more information contact your PMD

representative.

- These chipsets take in incremental

These chipsets take in

- These chipsets provide

These chipsets provide very high speed

3

Page 4

Electrical Characteristics

Overview

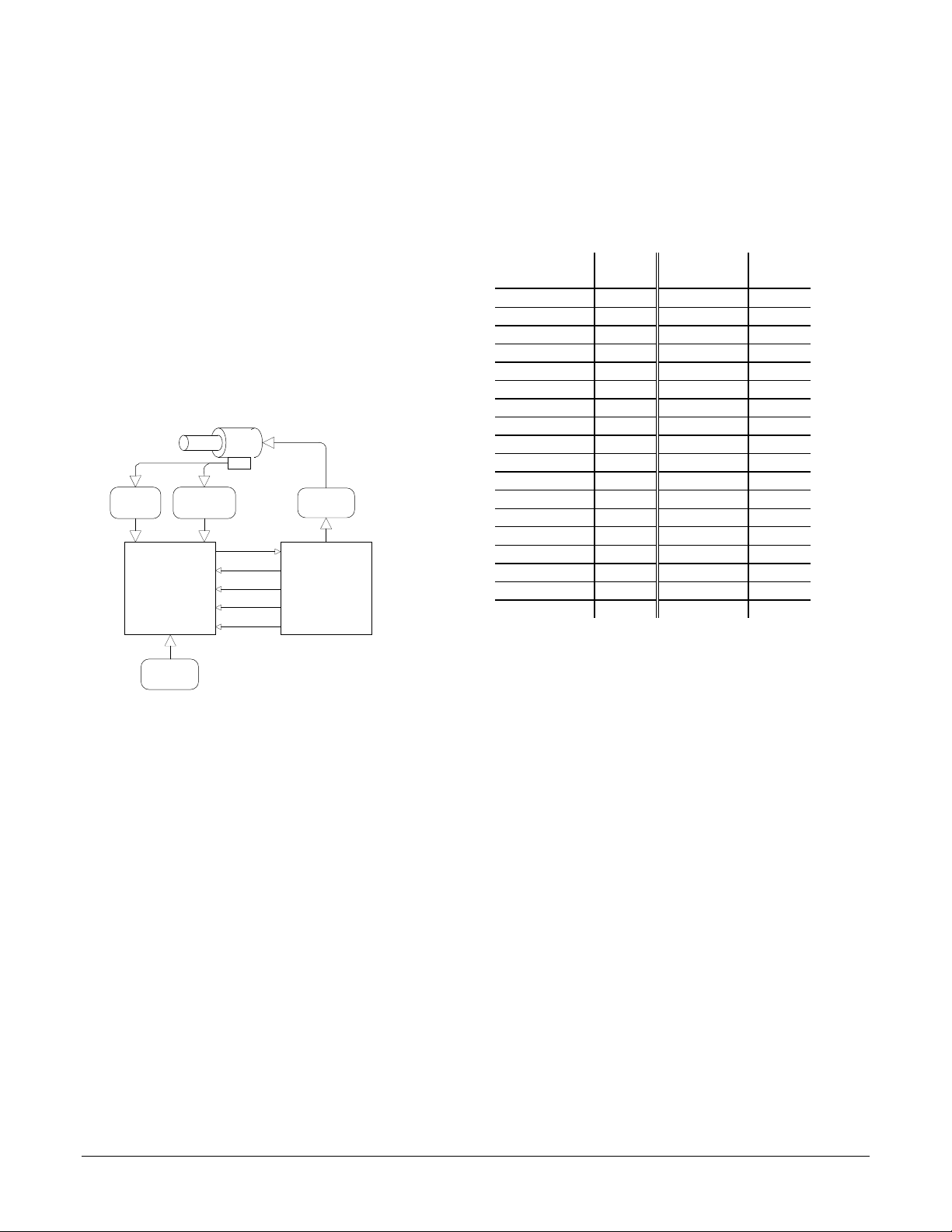

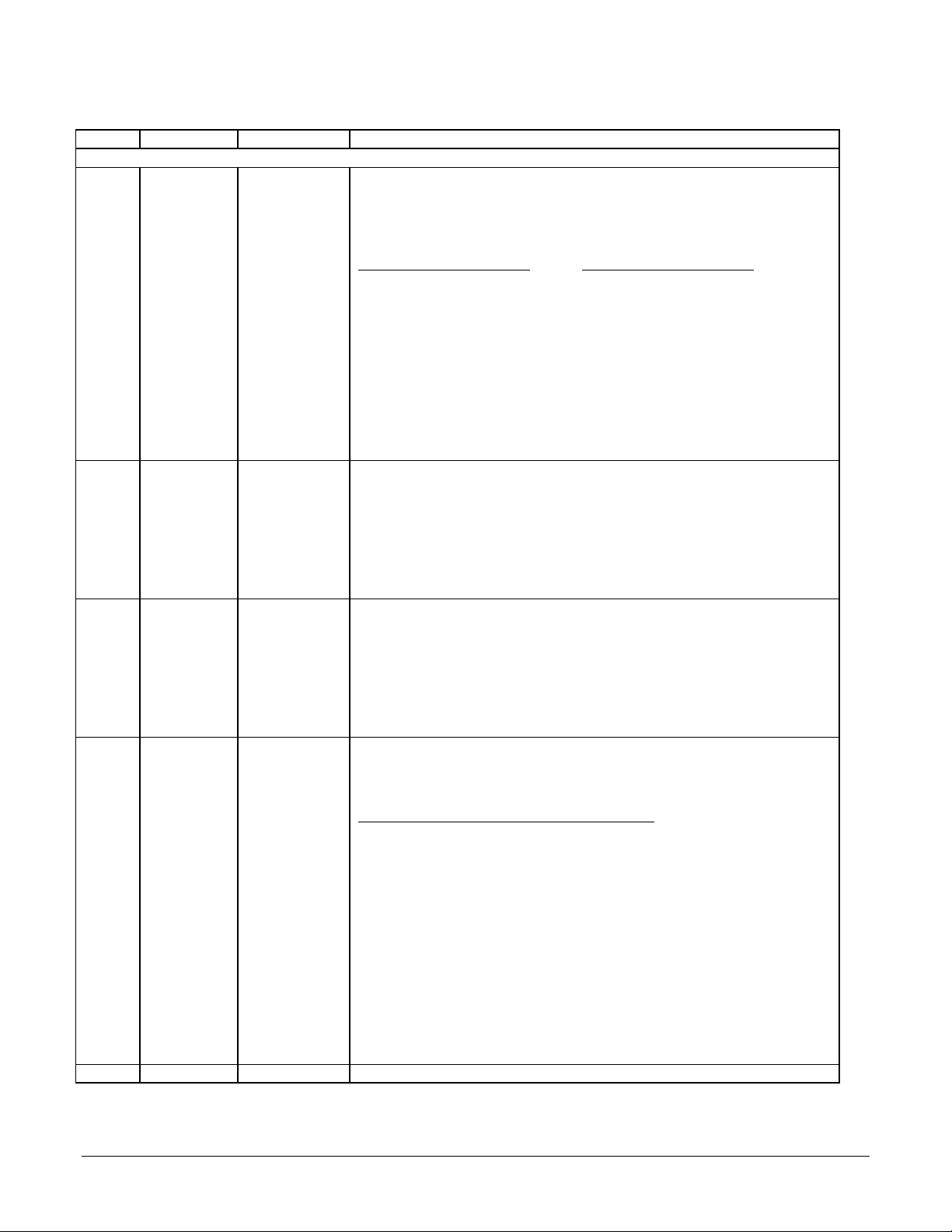

Interconnections between the two chips consist of a data bus and

various control and synchronization signals. The following table

summarizes the signals that must be interconnected for the chipset to

function properly. For each listed signal the I/O chip pin on the left side

of the table is directly connected to the pin to the right.

The MC1231A consists of two 68 pin PLCC's both fabricated in CMOS.

The Peripheral Input/Output IC (I/O chip) is responsible for interfacing

to the host processor and to the position input encoders. The Command

Processor IC (CP chip) is responsible for all host command, trajectory,

servo, and commutation computations, as well as for outputting the

PWM and DAC signals.

The following figure shows a typical system block diagram, along with

the pin connections between the I/O chip and the CP chip.

Motor

(4 axis)

Encoder

(1-2 axis)

Hall Sensors

I/O

Host

Processor

(1 - 2 axis)

Data4-11

I/OAddr0-3

I/OWrite

I/OCntrl0-3

ClkOut

Amplifier

(1-2 axis)

CP

I/O Chip Signal

Name

I/O Chip

Pin

CP Chip

Signal Name

CP Chip

Pin

CPData4 18 Data4 50

CPData5 5 Data5 49

CPData6 6 Data6 46

CPData7 7 Data7 43

CPData8 8 Data8 40

CPData9 17 Data8 39

CPData10 3 Data10 36

CPData11 1 Data11 35

CPAddr0 68 I/OAddr0 28

CPAddr1 27 I/OAddr1 9

CPAddr2 29 I/OAddr2 6

CPAddr3 12 I/OAddr3 5

CPCntr0 20 I/OCntr0 16

CPCntr1 36 I/OCntr1 18

CPCntr2 22 I/OCntr2 68

CPCntr3 63 I/OCntr3 67

CPWrite 2 I/OWrite 15

CPClk 46 ClkOut 19

For a complete description of all pins see the 'Pin Descriptions'

section of this manual.

The CP and I/O chips function together as one integrated motion

processor. The major components connected to the chip set are the

Encoder (2, or 1 axes), (optionally) the motor Hall-sensors (2 or 1 axes),

the motor amplifier (2, or 1 axes), and the host processor.

The encoder signals are input to the I/O chip in quadrature format. Two

signals encode the position, and an optional index signal contains a

once-per-rotation locating signal.

Hall sensors may be connected to the chipset to provide phase

initialization information, although this is not required. Three Hall sensor

signals are input per axis.

The chipset's motor output signals are connected to the motor amplifier.

Two types of output are provided; PWM (pulse width modulation), and

DAC-compatible signals used with an external DAC (digital to analog

converter). Because the output signals are commutated, more than one

motor output signal will be output per axis. See Theory of Operations

section on sinusoidal motor commutation for details.

The host processor is interfaced via an 8-bit bi-directional bus and

various control signals. Host communication is coordinated by a

ready/busy signal, which indicates when communication is allowed.

Absolute Maximum Ratings

Unless otherwise stated, all electrical specifications are for both

the I/O and CP chips.

Storage Temperature, Ts.....................-55 deg. C to +150 deg. C

Supply Voltage, Vcc.............................-0.3 V to +7.0 V

Power Dissipation, Pd..........................650 mW (I/O and CP

combined)

Operating Ratings

Operating Temperature, Ta .................0 deg. C to +70 deg. C

Nominal Clock Frequency, Fclk...........25.0 Mhz

Supply Voltage, Vcc.............................4.75 V to 5.25 V

* Industrial and Military operating ranges also available. Contact your

PMD representative for more information.

4

Page 5

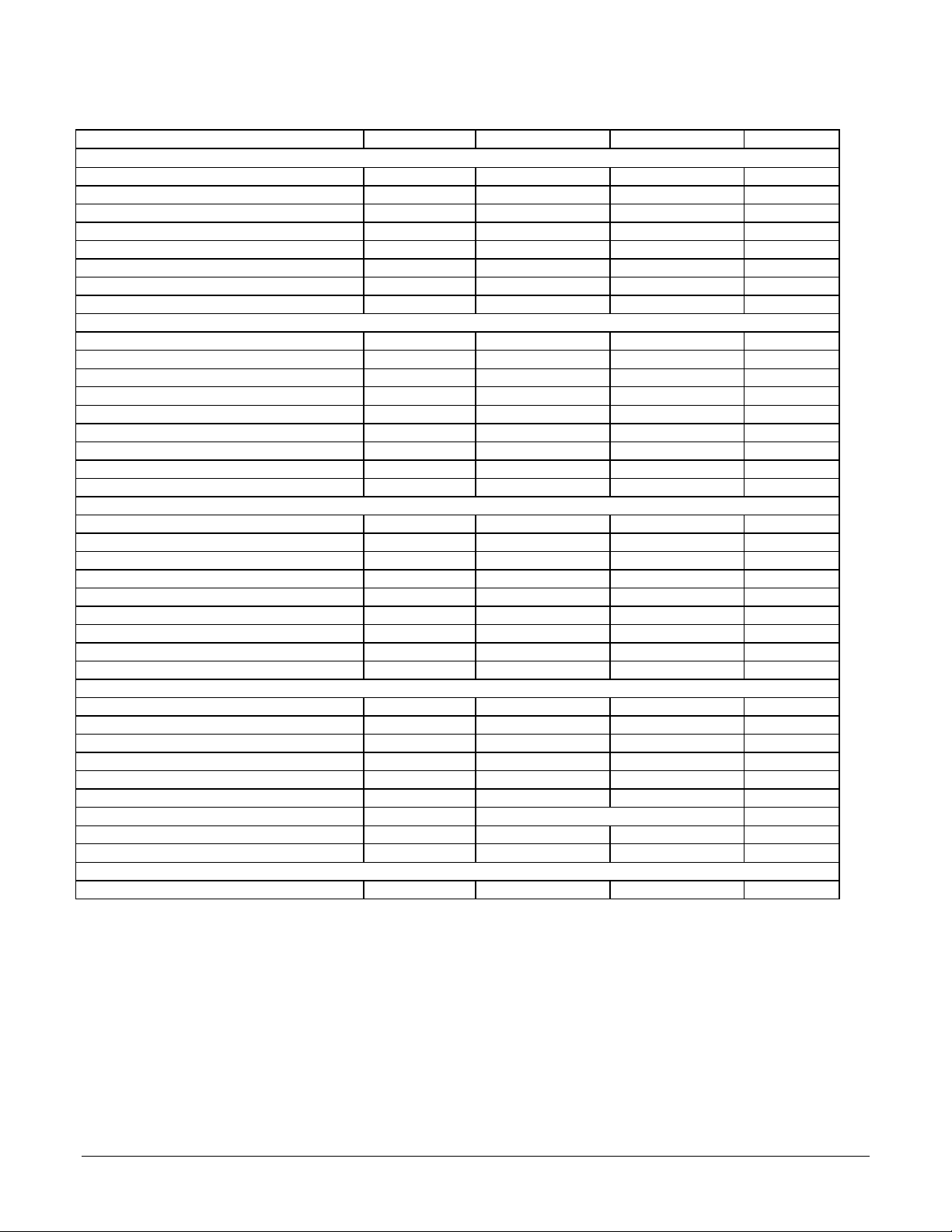

DC Electrical Characteristics

(Vcc and Ta per operating ratings, Fclk = 25.0 Mhz)

Symbol Parameter Min. Max. Units Conditions

Vcc Supply Voltage 4.75 5.25 V

Idd Supply Current 100 mA open outputs

Input Voltages

Vih Logic 1 input voltage 2.0 Vcc + 0.3 V

Vil Logic 0 input voltage -0.3 0.8 V

Vihclk Logic 1 voltage for clock pin

(ClkIn)

Vihreset Logic 1 voltage for reset pin

(reset)

Output Voltages

Voh Logic 1 Output Voltage 2.4 V @CP Io = 300 uA

Vol Logic 0 Output Voltage 0.33 V @CP Io = 2 mA

Iout Tri-State output leakage current -20 20 uA 0 < Vout < Vcc

Iin Input current -50 50 uA 0 < Vi < Vcc

Iinclk Input current ClkIn -20 20 uA 0 < Vi < Vcc

3.0 Vcc+0.3 V

4.0 Vcc+0.3 V

AC Electrical Characteristics

(see reference timing diagrams)

(Vcc and Ta per operating ratings; Fclk = 25.0 Mhz)

(~ character indicates active low signal)

@I/O Io = 4 mA

@I/O Io = 4 mA

Timing Interval T# Min. Max. Units

Encoder and Index Pulse Timing

Motor-Phase Pulse Width T1 1.6 uS

Dwell Time Per State T2 0.8 uS

Index Pulse Setup and Hold

(relative to Quad A and Quad B low)

Reset Timing

Stable Power to Reset 0.25 Sec

Reset Low Pulse Width 1.0 uS

Clock Timing

Clock Frequency (Fclk) 6.7 25.6 Mhz

Clock Pulse Width T4 19.5 75 (note 2) nS

Clock Period T5 39 149 (note 2) nS

T3 0 uS

5

Page 6

Timing Interval T# Min. Max. Units

Command Byte Write Timing

~HostSlct Hold Time T6 15 2000 (note 3) nS

~HostSlct Setup Time T7 10 nS

HostCmd Setup Time T8 10 nS

Host Cmd Hold Time T9 25 nS

HostRdy Delay Time T13 70 nS

~HostWrite Pulse Width T14 50 nS

Write Data Setup Time T15 35 nS

Write Data Hold Time T16 30 nS

Data Word Read Timing

~HostSlct Hold Time T6 15 2000 (note 3) nS

~HostSlct Setup Time T7 (read only) - 20 nS

HostCmd Setup Time T8 (read only) - 20 nS

HostCmd Hold Time T9 25 nS

Read Data Access Time T10 50 nS

Read Data Hold Time T11 10 nS

~HostRead high to HI-Z Time T12 50 nS

HostRdy Delay Time T13 70 nS

Read Recovery Time T17 60 nS

Data Word Write Timing

~HostSlct Hold Time T6 15 2000 (note 3) nS

~HostSlct Setup Time T7 10 nS

HostCmd Setup Time T8 10 nS

HostCmd Hold Time T9 25 nS

HostRdy Delay Time T13 70 nS

~HostWrite Pulse Width T14 50 nS

Write Data Setup Time T15 35 nS

Write Data Hold Time T16 30 nS

Write Recovery Time T18 60 nS

DAC Interface Timing

I/OAddr Stable to ~I/OWrite setup time T19 35 nS

~I/OWrite Pulse Width T20 56 95 nS

Data Hold Time After ~I/OWrite T21 17 nS

ClkOut Low to I/OAddr stable T22 10 40 nS

ClkOut Low to ~I/OWrite Low T23 75 92 nS

ClkOut Low to Data Valid T24 92 nS

ClkOut Cycle Time T25 160 typical (note 4) nS

I/OAddr Stable to DACSlct High T26 66 nS

~I/OWrite Low to DACSlct High T27 44.5 nS

PWM Output Timing

PWM Output Frequency 24.5 Khz

note 1 ~HostSlct and HostCmd may optionally be de-asserted if setup and hold times are met.

note 2 Chip-set performance figures and timing information valid at Fclk = 25.0 only. For timing information & performance parameters at Fclk <

25.0 Mhz, call PMD.

note 3 Two micro seconds maximum to release interface before chip set responds to command

note 4 ClkOut from CP is 1/4 frequency of ClkIn (CP chip).

6

Page 7

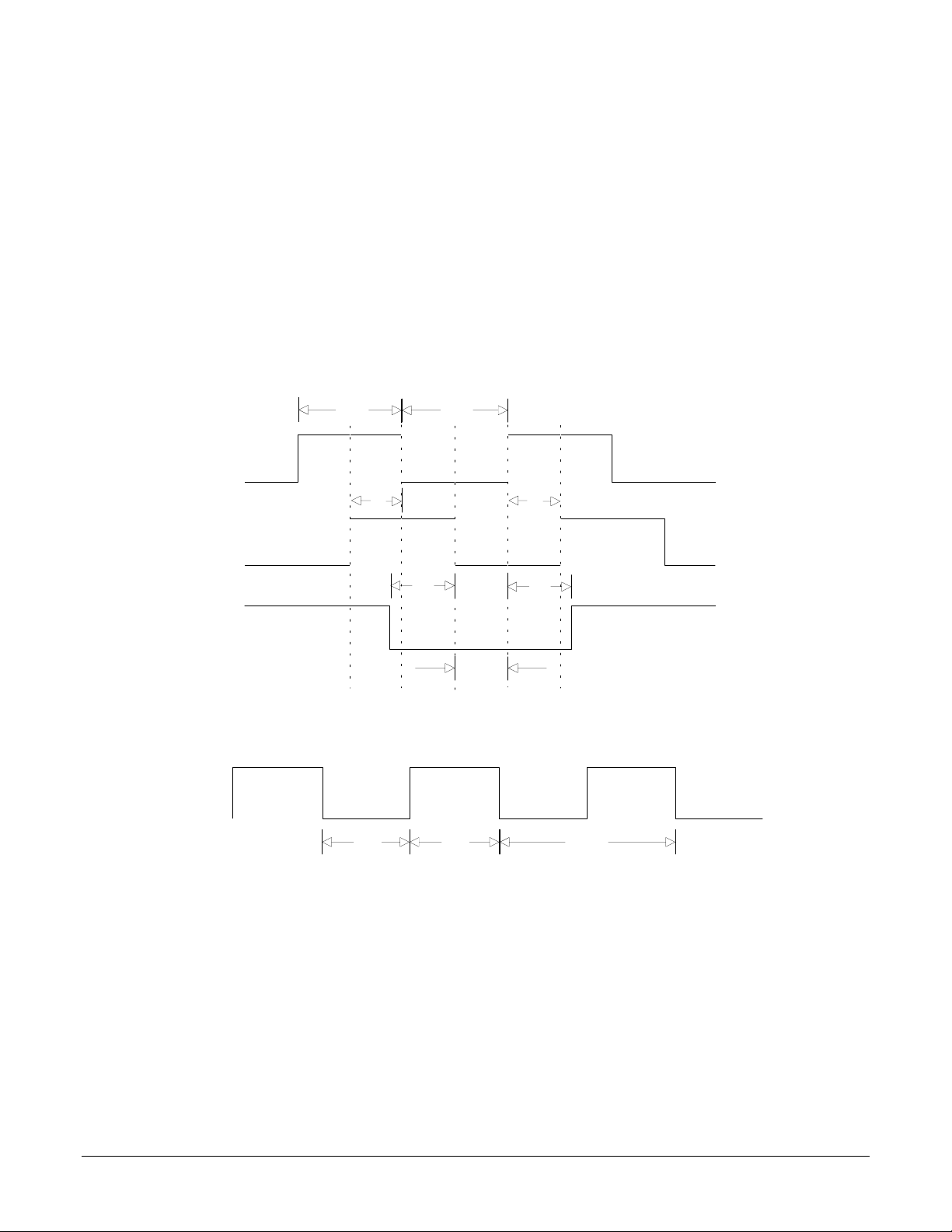

I/O Timing Diagrams

The following diagrams show the MC1231A electrical interface timing. T#' values are listed in the above timing chart.

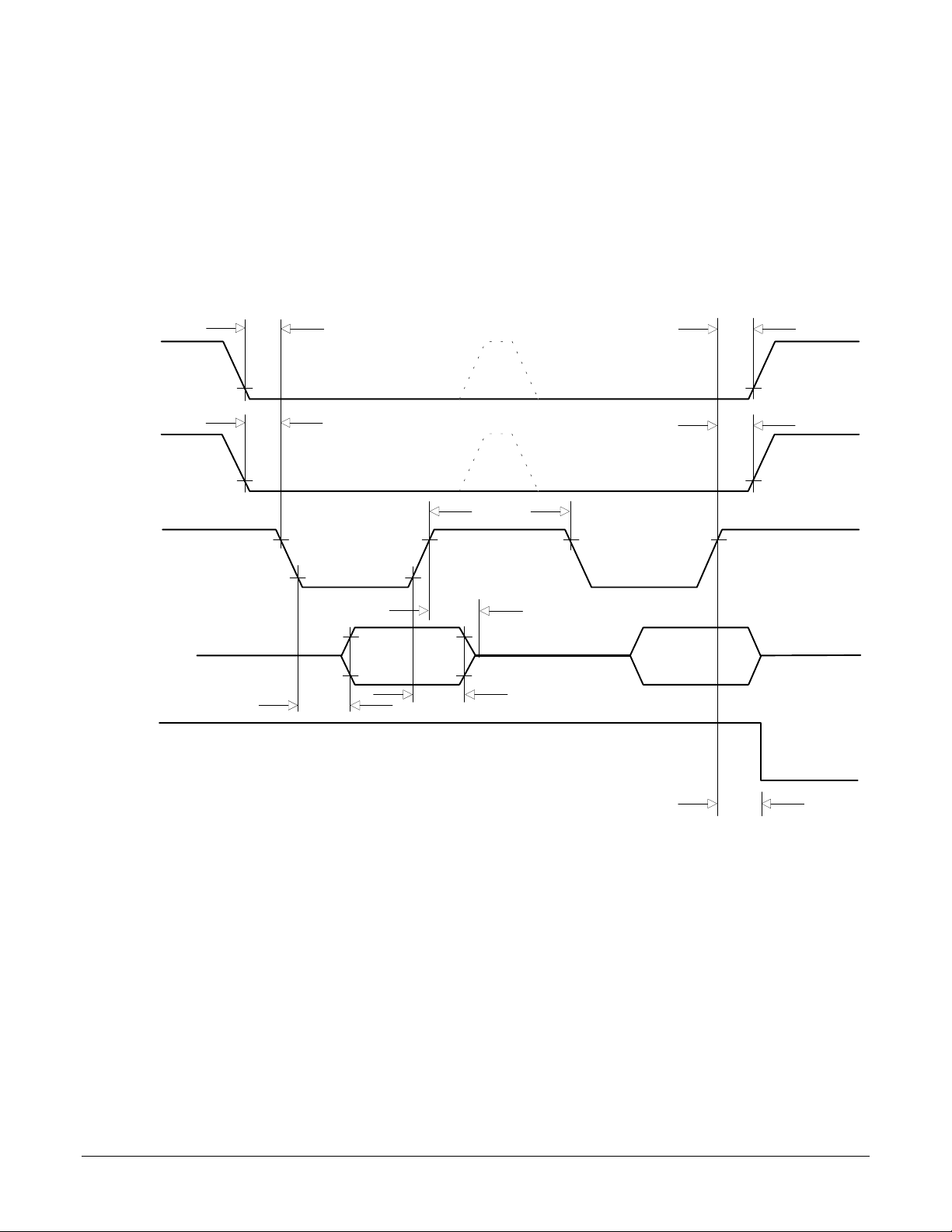

Quadrature Encoder Input Timing

Quad A

Quad B

~Index

ClkIn

T1

T1

T2 T2

T3

Clock Timing

T3

T4 T4 T5

Index = ~A * ~B * ~IND

7

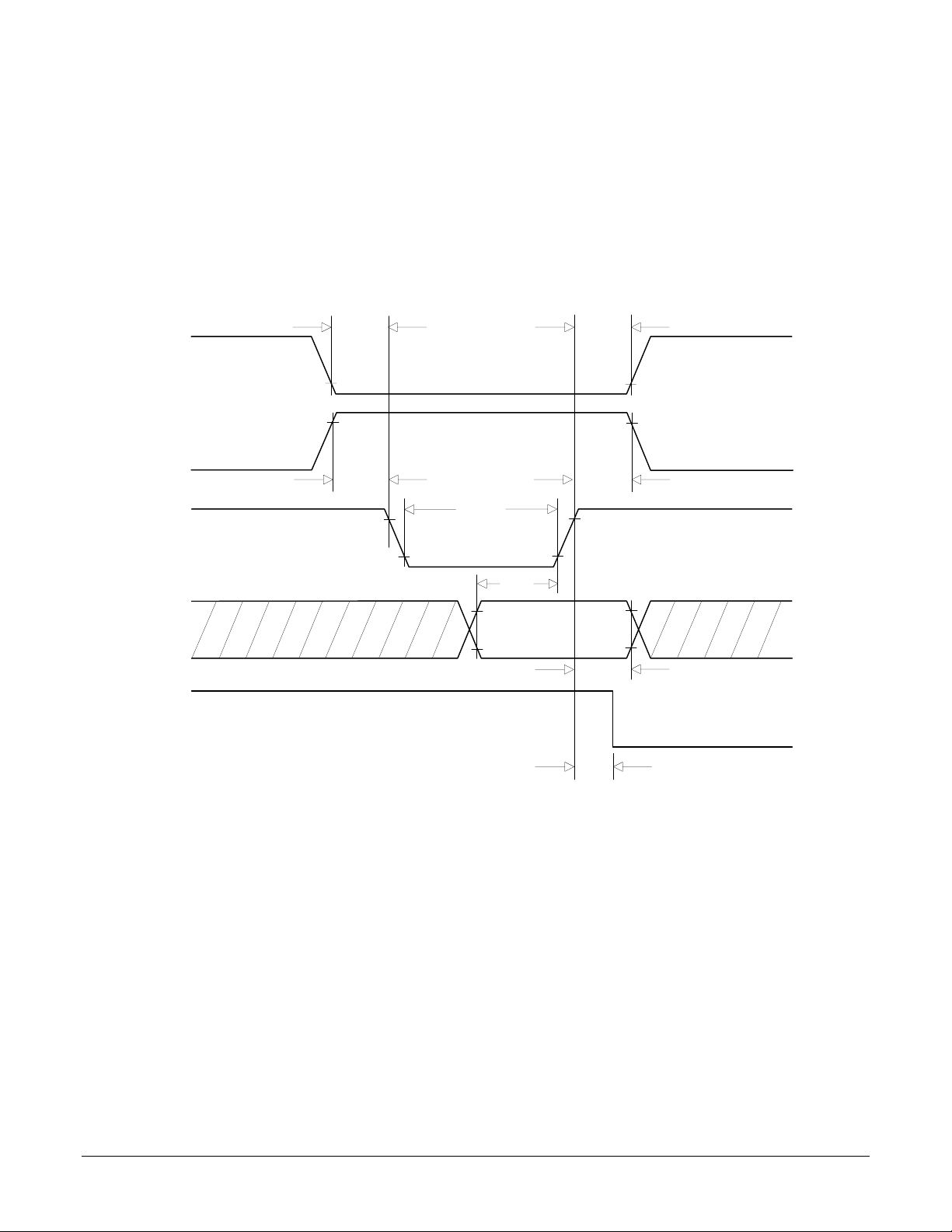

Page 8

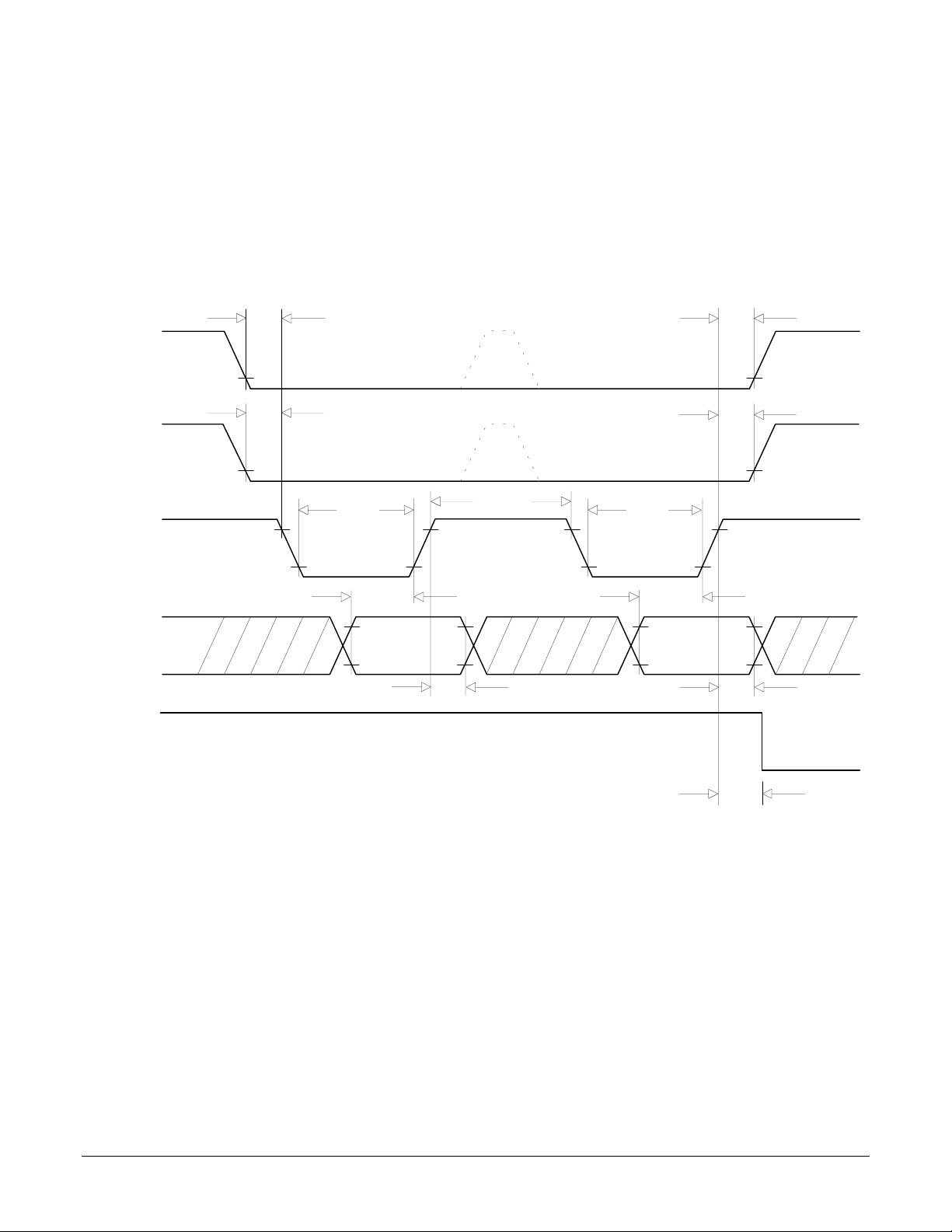

Command Byte Write TIming

~HostSlct

HostCmd

~HostWrite

HostData0-7

HostRdy

T7

T8

T6

T9

T14

T15

T16

T13

8

Page 9

Data Word Read TImi ng

~HostSlct

HostCmd

~HostRead

HostData0-7

HostRdy

T7

T6

Note 1

T8

Note 1

T9

T17

T12

High-Z High-Z High-Z

High

Byte

T10

T11

Low

Byte

T13

9

Page 10

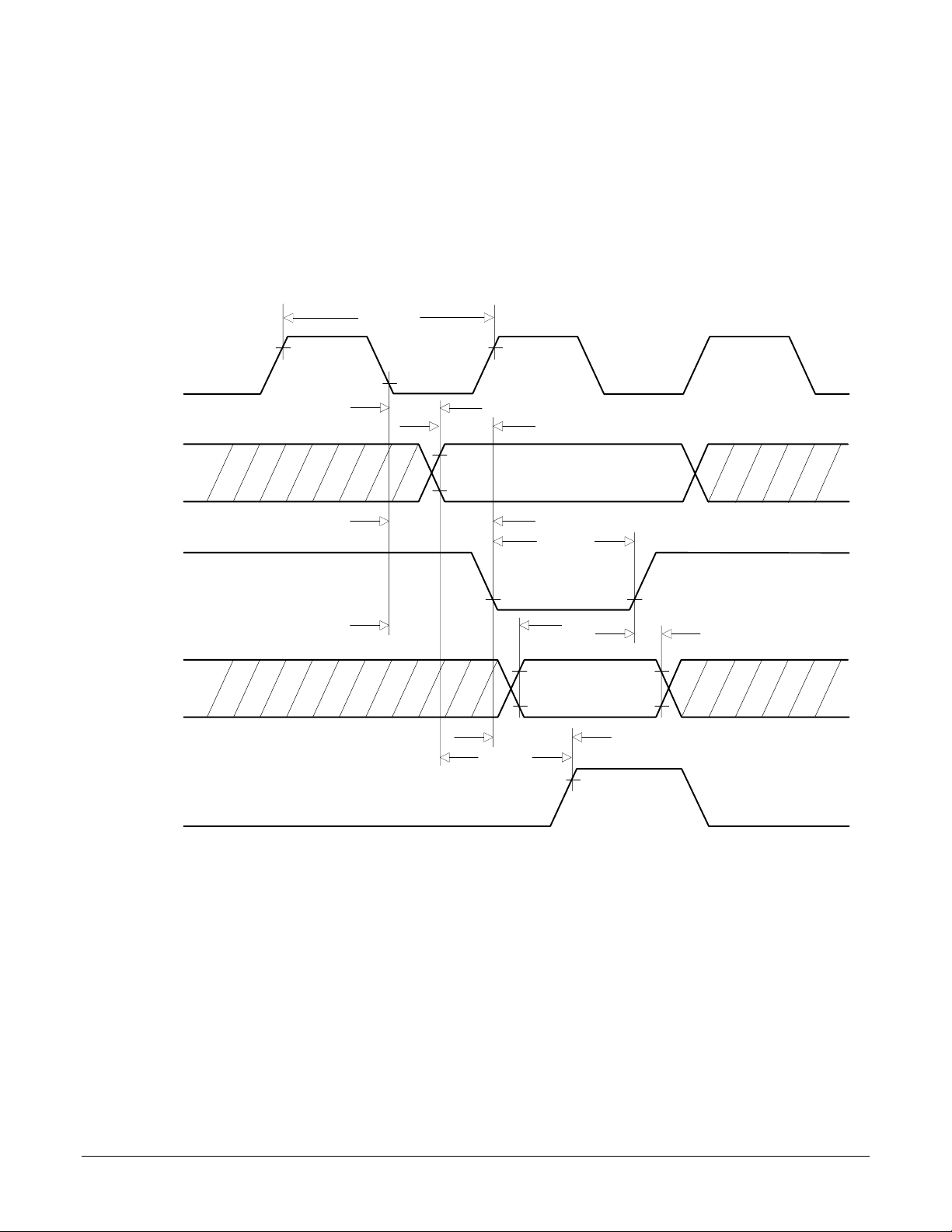

Data Word Write TIming

~HostSlct

HostCmd

~HostWrite

HostData0-7

HostRdy

T7

T8

T14

T15

High

Byte

T16

T18

Note 1

Note 1

T6

T9

T14

T15

Low

Byte

T16

10

T13

Page 11

ClkOut

I/OAddr

~I/OWrite

DAC Interface Timing

T25

T22

T19

T23

T20

Data 0-11,

DACAddr0,1

DACSlct

T24

T21

T27

T26

11

Page 12

Pinouts

9

1

61

9

1

61

10

I/O

(Top view)

26

27 43

60

10

60

CP

(Top view)

44

26

27 43

44

MC1231A Pinouts

4, 21, 25, 38, 55

VCC

QuadA1

28

QuadB1

42

Index1

24

Home1

13

QuadA2

26

QuadB2

30

Index2

9

Home2

23

Hall1A

40

Hall1B

35

Hall1C

19

Hall2A

39

Hall2B

34

Hall2C

16

DACSlct

33

CPClk

46

I/OClkIn

52

I/OClkOut

45

CPAddr2

29

CPAddr3

12

CPWrite

2

CPCntrl0

20

CPCntrl1

36

I/O

GND

CPCntrl2

CPCntrl3

HostCmd

HostRdy

HostRead

HostWrite

HostSlct

HostIntrpt

HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

CPAddr0

CPAddr1

22

63

41

37

51

47

48

44

50

61

53

65

67

62

64

60

18

5

6

7

8

17

3

1

68

27

66

65

30

29

24

19

17

16

18

68

67

64

63

62

61

8

7

2

1

PWMMag1

PWMMag2

PWMMag3

PWMMag4

PWMMag5

PWMMag6

DAC16Addr0

DAC16Addr1

ClkIn

ClkOut

Reset

I/OCntrl0

I/OCntrl1

I/OCntrl2

I/OCntrl3

DACLow0

DACLow1

DACLow2

DACLow3

4, 22, 33

VCC

CP

GND

Data0

Data1

Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

I/OAddr0

I/OAddr1

I/OAddr2

I/OAddr3

I/OWrite

PosLimit1

PosLimit2

NegLimit1

NegLimit2

60

59

58

57

50

49

46

43

40

39

36

35

28

9

6

5

15

52

45

51

44

14, 15, 32, 49, 54, 66

3, 34

MC1131A Pinouts

4, 21, 25, 38, 55

VCC

HostCmd

QuadA1

28

QuadB1

42

Index1

24

Home1

13

Hall1A

40

Hall1B

35

Hall1C

19

DACSlct

33

CPClk

46

I/OClkIn

52

I/OClkOut

45

CPAddr2

29

CPAddr3

12

CPWrite

2

CPCntrl0

20

CPCntrl1

36

CPCntrl2

22

CPCntrl3

63

CPAddr0

68

CPAddr1

27

I/O

GND

14, 15, 32, 49, 54, 66

HostRdy

HostRead

HostWrite

HostSlct

HostIntrpt

HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

41

37

51

47

48

44

50

61

53

65

67

62

64

60

18

5

6

7

8

17

3

1

30

29

24

19

17

16

18

68

67

64

63

62

61

8

7

2

PWMMag1

PWMMag2

PWMMag3

DAC16Addr0

DAC16Addr1

ClkIn

ClkOut

Reset

I/OCntrl0

I/OCntrl1

I/OCntrl2

I/OCntrl3

DACLow0

DACLow1

DACLow2

DACLow3

12

4, 22, 33

VCC

CP

GND

3, 34

Data0

Data1

Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

I/OAddr0

I/OAddr1

I/OAddr2

I/OAddr3

I/OWrite

PosLimit1

NegLimit 1

60

59

58

57

50

49

46

43

40

39

36

35

28

9

6

5

15

52

51

Page 13

Pin Descriptions

The following tables provide pin descriptions for the MC1231-series chipsets.

IC Pin Name Pin # Description/Functionality

I/O Chip Pinouts

I/O QuadA1

QuadB1

QuadA2

QuadB2

I/O ~Index1

~Index2

I/O ~Home1

~Home2

28

42

26

30

24

9

13

23

Quadrature A, B channels for axis 1 - 2 (input). Each of these 2 pairs of quadrature (A, B)

signals provide the position feedback for an incremental encoder. When the encoder is

moving in the positive, or forward direction, the A signal leads the B signal by 90 degs.

NOTE: Many encoders require a pull-up resistor on each of these signals to establish a

proper high signal (check the encoder electrical specifications)

NOTE: For MC1231A all 4 pins are valid. For MC1131A pins for axes 1 only are valid. Invalid

axis pins can be left unconnected

Index encoder signals for axis 1-2 (input). Each of these 2 signals indicate the index flag

state from the encoder. A valid index pulse is recognized by the chip set when the index flag

transitions low, followed by the corresponding A and B channels of the encoder transitioning

low. The index pulse is recognized at the later of the A or B transitions. If not used this signal

must be tied high.

NOTE: For MC1231A both pins are valid. For MC1131A pins for axes 1 only are valid.

Invalid axis pins can be left unconnected.

Home signals for axis 1-2 (input). Each of these signals provide a general purpose input to

the hardware position capture mechanism. A valid home signal is recognized by the chipset

when the home flag transitions low. These signals have a similar function as the ~Index

signals, but are not gated by the A and B encoder channels. For valid axis pins, If not used,

this signal must be tied high. See below for valid pin definitions for the MC1231A and

MC1131A.

NOTE: For MC1231A both pins are valid. For MC1131A pins for axes 1 only are valid.

Invalid axis pins can be left unconnected.

I/O DACSlct 33 DAC Select (output). This signal is asserted high to select any of the available DAC output

channels. For details on DAC decoding see description of DAC16Addr0-1 signals.

I/O CPClk 46 I/O chip clock (input). This signal is connected directly to the ClkOut pin (CP chip) and

provides the clock signal for the I/O chip. The frequency of this signal is 1/4 the user-provided

ClkIn (CP chip) frequency.

I/O I/OClkIn 52 Phase shifted clock (input). This signal must be connected to I/OClkOut (I/O chip), and inputs

a phase shifted clock signal.

I/O I/OClkOut 45 Phase shifted clock (output). This signal must be connected to I/OClkIn (I/O chip), and

outputs a phase shifted clock signal.

I/O CPAddr0

CPAddr1

CPAddr2

CPAddr3

I/O ~CPWrite 2 I/O chip to CP chip communication write (input). This signal is connected to the ~I/OWrite pin

I/O CPCntrl0

CPCntrl1

CPCntrl2

CPCntrl3

I/O HostCmd 41 Host Port Command (input). This signal is asserted high to write a host command to the chip

68

27

29

12

20

36

22

63

I/O chip to CP chip communication address (input). These 4 signals are connected to the

corresponding I/OAddr0-3 pins (CP chip), and together provide addressing signals to

facilitate CP to I/O chip communication.

(CP chip) and provides a write strobe to facilitate CP to I/O chip communication.

I/O chip to CP chip communication control (mixed). These 4 signals are connected to the

corresponding I/OCntrl0-3 pins (CP chip), and provide control signals to facilitate CP to I/O

chip communication.

set. It is asserted low to read or write a host data word to the chipset

13

Page 14

IC Pin Name Pin # Description/Functionality

I/O HostRdy 37 Host Port Ready/Busy (output). This signal is used to synchronize communication between

the DSP and the host. HostRdy will go low (indicating host port busy) at the end of a host

command write or after the second byte of a data write or read. HostRdy will go high

(indicating host port ready) when the command or data word has been processed and the

chip set is ready for more I/O operations. All host port communications must be made with

HostRdy high (indicating ready).

Typical busy to ready cycle is 67.5 uSec, although it can be longer when host port traffic is

high.

I/O ~HostRead 51 Host Port Read data (input). Used to indicate that a data word is being read from the chip set

(low asserts read).

I/O ~HostWrite 47 Host Port Write data (input). Used to indicate that a data word or command is being written to

the chip set (low asserts write).

I/O ~HostSlct 48 Host Port Select (input). Used to select the host port for reading or writing operations (low

assertion selects port). ~HostSlct must remain inactive (high) when the host port is not in use.

I/O ~HostIntrpt 44 Host Interrupt (output). A low assertion on this pin indicates that a host interrupt condition

exists that may require special host action.

I/O HostData0

HostData1

HostData2

HostData3

HostData4

HostData5

HostData6

HostData7

I/O CPData4

CPData5

CPData6

CPData7

CPData8

CPData9

CPData10

CPData11

I/O Hall1A

Hall1B

Hall1C

Hall2A

Hall2B

Hall2C

50

61

53

65

67

62

64

60

18

5

6

7

8

17

3

1

40

35

19

39

34

16

Host Port Data 0-7 (bi-directional, tri-stated). These signals form the 8 bit host data port used

during communication to/from the chip set. This port is controlled by ~HostSlct, ~HostWrite,

~HostRead and HostCmd.

I/O chip to CP chip data port (bi-directional). These 8 bits are connected to the corresponding

Data4-11 pins on the CP chip, and facilitate communication to/from the I/O and CP chips..

Hall Sensor A, B, and C commutation inputs for axis 1 and 2 (input). Each set of the three

signals for one axis (A, B and C) encodes 6 valid signal states as follows: A on, A and B on,

B on, B and C on, C on, C and A on. An on state is defined as a high signal.

NOTE: These signals should only be connected to Hall sensors that are mounted 120-deg

offset from each other. Schemes which provide Hall signals 60-deg apart will not work.

NOTE: For MC1231A all 6 pins are valid. For MC1131A pins for axis 1 only are valid. Invalid

axis pins can be left unconnected.

I/O Vcc 4, 21, 25, 38, 55 I/O chip supply voltage pin. All of these pins must be connected to the supply voltage. Supply

voltage = 4.75 to 5.25 V

I/O GND 14, 15, 32, 49, 54,66I/O chip ground pin. All of these pins must be connected to the power supply return.

14

Page 15

IC Pin Name Pin # Description/Functionality

CP Chip Pinouts

CP PWMMag1

PWMMag2

PWMMag3

PWMMag4

PWMMag5

PWMMag6

CP PosLimit1

PosLimit2

CP NegLimit1

NegLimit2

8

7

2

1

66

65

52

45

51

44

PWM motor output magnitude signals (output). When the chip set is in PWM output mode

these pins provide the Pulse Width Modulated magnitude signal to the motor amplifier.The

PWM signals are output for each motor axis as follows:

3-Phase Brushless 2-Phase Brushless

Signal Axis # Phase Signal Axis # Phase

PWMMag1 1 A PWMMag1 1 A

PWMMag2 1 B PWMMag2 1 B

PWMMag3 1 C PWMMag3 2 A

PWMMag4 2 A PWMMag4 2 B

PWMMag5 2 B

PWMMag6 2 C

NOTE: If using the MC1231A with one axis in 3-phase and the other axis in 2-phase mode, to

avoid pin conflict, axis 1 should be assigned to 2-phase output, and axis 2 to 3-phase

The PWM resolution is 10 bits, frequency = 24.5Kz.

Positive limit switch input for axis 1-2. These signals provide directional limit inputs for the

positive-side travel limit of the axis. Upon powerup these signals default to "active high"

interpretation, but the interpretation can be set explicitly using the SET_LMT_SENSE

command. (See Host Command Section for more info.) If not used these signals should be

tied low for the default interpretation, or tied high if the interpretation is reversed.

NOTE: For MC1231A both pins are valid. For MC1131A pins for axes 1 only are valid. Invalid

axis pins can be left un connected.

Negative limit switch input for axis 1-2. These signals provide directional limit inputs for the

negative-side travel limit of the axis. Upon powerup these signals default to "active high"

interpretation, but the interpretation can be set explicitly using the SET_LMT_SENSE

command. (See Host Command Section for more info.) If not used these signals should be

tied low for the default interpretation, or tied high if the interpretation is reversed.

NOTE: For MC1231A both pins are valid. For MC1131A pins for axis 1 only are valid. Invalid

axis pins can be left un connected.

CP DAC16Addr0

DAC16Addr13029

CP ClkIn 24 Clock In (input). This pin provides the chip set master clock (Fclk = 25.0 Mhz)

Axis Address used during 16-bit DAC motor command output (output). These signals encode

the motor output axis address as shown in the table below (both 3-phase and 2-phase

waveforms)

Dac16Addr1 Dac16Addr0 Addressed Encoder

Low Low Axis 1 phase A

Low High Axis 1 phase B

High Low Axis 2 phase A

High High Axis 2 phase B

Note: When connecting to 3-phase brushless motors only two of the three required phase

outputs are provided in the DAC output mode. The third phase (phase C) is constructed

external to the chipset, usually by the amplifier. See theory of operations for more

information.

To write a valid DAC motor command value DACSlct (I/O chip) and I/OAddr0-3 (CP chip)

must be high, and I/OWrite (CP chip) must be low. The 16 bit DAC data word is organized as

follows: High twelve bits are in Data0-11 (CP chip), and low 4 bits are in DACLow0-3 (CP

chip).

15

Page 16

IC Pin Name Pin # Description/Functionality

CP ClkOut 19 Clock Out (output). This pin provides a clock output which is 1/4 the ClkIn frequency. This pin

is connected to I/OClkin (I/O chip).

CP ~Reset 17 Master chip set reset (input). When brought low, this pin resets the chip set to its initial

condition. Reset should occur no less than 250 mSec after stable power has been provided

to the chip set.

CP I/OCntrl0

I/OCntrl1

I/OCntrl2

I/OCntrl3

CP Data0

Data1

Data2

Data3

Data4

Data5

Data6

Data7

Data8

Data9

Data10

Data11

CP DACLow0

DACLow1

DACLow2

DACLow3

CP I/OAddr0

I/OAddr1

I/OAddr2

I/OAddr3

CP I/OWrite 15 Multi-purpose write (output). This pin is connected to CPWrite on the I/O chip. It has 2

16

18

68

67

60

59

58

57

50

49

46

43

40

39

36

35

64

63

62

61

28

9

6

5

I/O chip to CP chip communication control (mixed). These signals are connected to the

corresponding CPCntrl0-3 pins on the I/O chip, and provide control signals to facilitate CP to

I/O communication.

Multi-purpose Data0-11. (Bi-directional). These pins have 2 functions:

1) Pins Data4-11 (8 bits total) are connected to the corresponding CPData4-11 pins on the

I/O chip, and are used to communicate between the CP and I/O chips

2) Pins Data0-11 hold the high 12 bits of the DAC output value when the output mode is set

to 16-bit DAC.

DACLow0-3 (output). These pins hold the lowest 4 bits of the 16 bit DAC output word when

the output mode is set to 16 bit DAC. These pins, in conjunction with Data0-11 (providing the

high 12 bits) make up the 16-bit DAC output word.

Multi-purpose Address0-3 (output). These pins are connected to the corresponding CPAddr03 pins on the I/O chip. They have 2 functions; They provide addressing signals to facilitate

communication between the I/O chip and CP chip, and they are used during DAC data

decoding. To read a valid DAC value from Data0-Data11 (CP chip), DACSlct (I/O chip) and

I/OAddr0-3 (CP chip) must all be high, and I/OWrite (CP chip) must be low.

functions:

1) It provides a control signal to the I/O chip to facilitate communication between the I/O chip

and CP chip.

2) It is used during DAC data decoding to read a valid DAC value from Data0-Data11 (CP

chip), DACSlct (I/O chip) and I/OAddr0-3 (CP chip) must all be high, and I/OWrite (CP chip)

must be low.

CP Vcc 4, 22, 33 CP chip supply voltage pin. All of these pins must be connected to the supply voltage. Supply

voltage = 4.75 to 5,.25 V

CP GND 3, 34 CP chip ground pin. All of these pins must be connected to the power supply return.

16

Page 17

Theory of Operations

g

Incremental Encoder

Index B A

Home

1/a

1/a

1/a 1/a

Internal Block Diagram

PWM ma

. DAC address

1/phase

DAC, PWM signal generator (6 channels)

Motor Output

2

DAC data

16

I/O Chip

CP Chip

Quadrature

decoder

counter (2)

Index capture

registe r (2)

Host I/O controller

185

host interruptDataControl

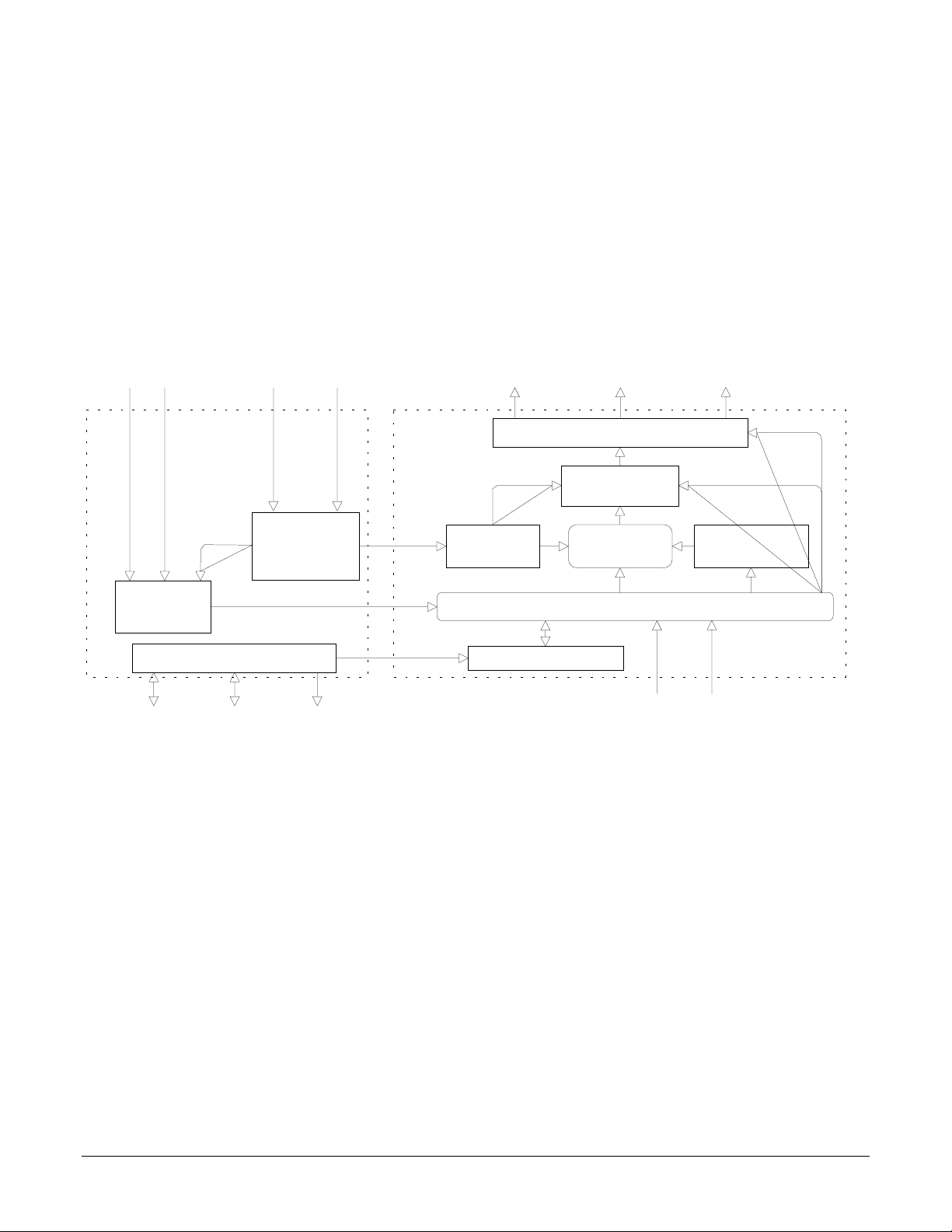

The above figure shows an internal block diagram for the MC1231A

motion processor.

Each servo axis inputs the actual location of the axis using incremental

encoder signals. These encoder signals are digitally filtered for

increased reliability and then passed on to a high speed up/down

counter. This counter is used to maintain a 32-bit actual axis position

register.

The chipset can be operated in two modes. Closed loop mode, which is

the normal operating mode of the chipset, performs trajectory

generation, digital servo loop closure, and sinusoidal commutation. In

this mode the motor output value is controlled by the servo filter. Open

loop mode performs commutation only. It allows the motor output value

to be controlled directly by the host processor.

Commutation

Generator (2)

Position

registe r (2)

Digital Servo

filtering (2)

Trajectory profile

generator (2)

System Reg isters (2)

Host command

1/a

PosLimit

1/a

NegLimit

motor encoder. Two or more commutated signals are generated for

each axis, with each signal being shifted either 90 or 120 degrees from

one another, depending on the motor type.

The resultant commutated signals are then output to the amplifier either

as PWM or DAC signals.

To perform continuous digital servoing, the trajectory and servo

calculations are performed at every sample time for all enabled axes.

The commutation is performed 4 times for each sample time.

The following table summarizes the operational parameters of the

MC1231A-series chipsets.

For either operating mode the desired motor output value is then

combined with the current commutation value from an internal

sinusoidal lookup. The commutation angle is determined using the

17

Page 18

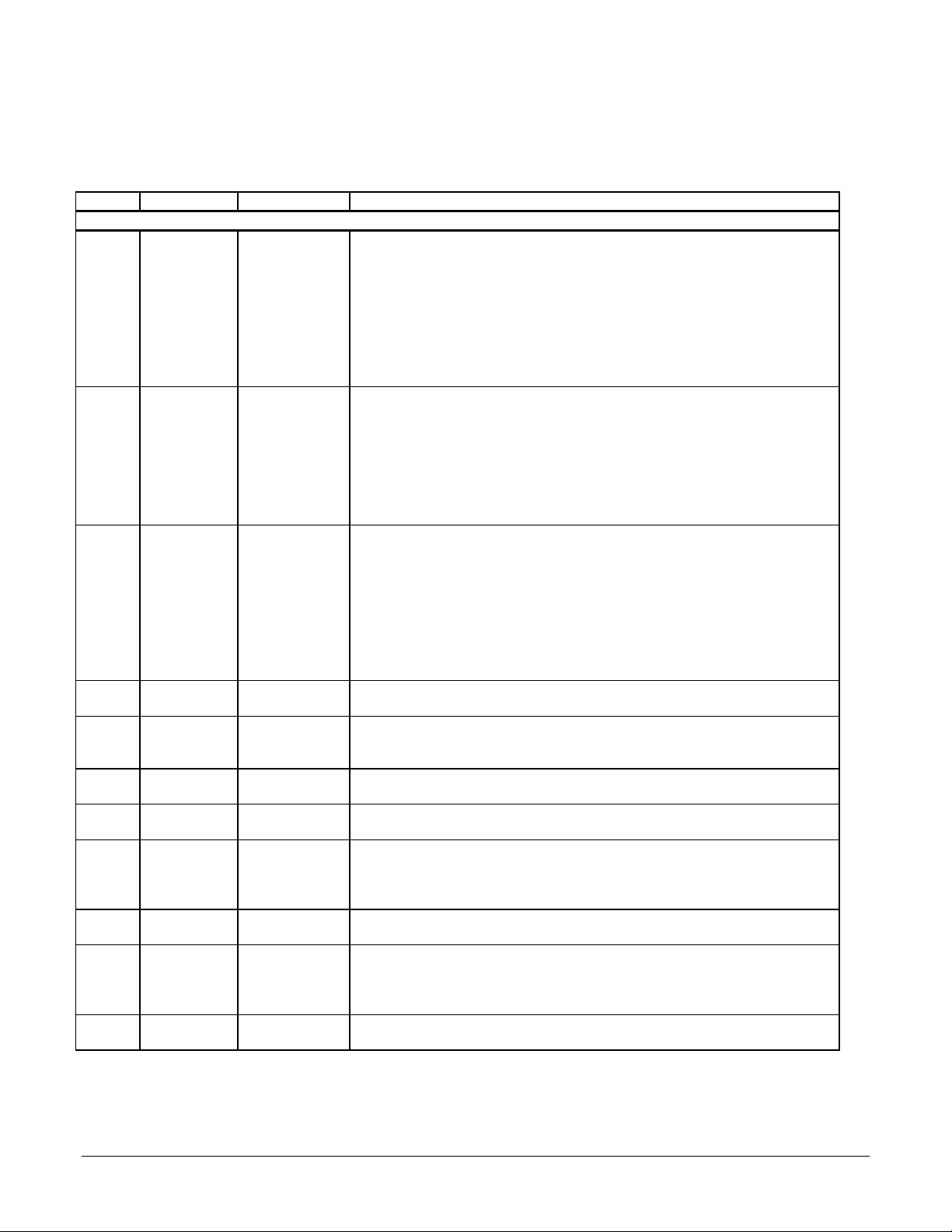

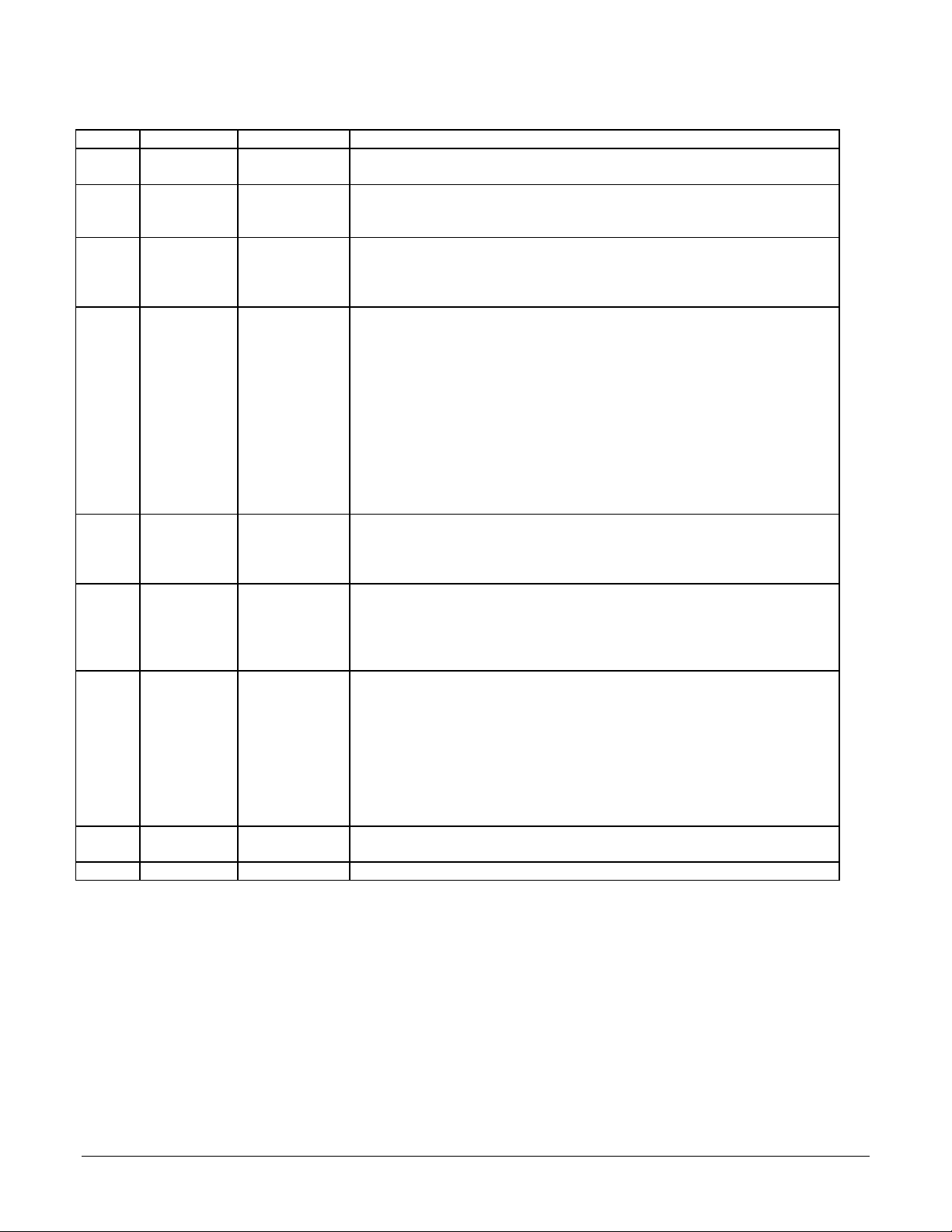

MC1231A-Series Chipset Operational Parameters

Available configurations: 2 axes with internal sinusoidal commutation (MC1231A)

1 axes with internal sinusoidal commutation (MC1131A)

Operating Modes: Closed loop (motor command is driven from output of servo filter)

Open loop (motor command is driven from user-programmed register)

Position Range: -1,073,741,824 to 1,073,741,823 counts

Velocity Range: -16,384 to 16,383 counts/sample with a resolution of 1/65,536 counts/sample

Acceleration Range:

Jerk Range:

Trajectory Profile Generator Modes: S-curve (host commands final position, max velocity, max acceleration, and jerk)

Electronic Gear Ratio Range: 32768:1 to 1:32768 (negative and positive direction)

Filter Modes: PID+Velocity feedforward and motor bias

Filter parameter resolution: 16 bits

Commutation Waveform: Sinusoidal

Phase Initialization Methods: Hall-Based

# of sinusoidal lookups: 256 per electrical cycle

range of commutation cycle: 129 to 2,097,088 (using pre-scalar) counts per electrical cycle

Commutation rate: 15 kHz

Phasing Modes: 120 degrees (used with 3-phase brushless motors)

# of PWM Output Phases: 3-phase brushless motors: 3

# of DAC Output Phases: 2 (all motor types)

Max Incremental. Encoder Rate: 1.75 Mcounts/sec

Servo loop rate range: 270 uSec*minimum, 4,423 mSec max.

Max servo loop rate: 270 uSec* per enabled axis.

# of limit switches per axis 2 (one for each direction of travel)

# of position capture triggers: 2 (index, home signal)

Capture trigger latency: 160 nSec

# of Host commands: 116

S-curve profile: - 1/2 to + 1/2 counts/sample2 with a resolution of 1/65,536 counts/sample

All others: -16,384 to 16,383 counts/sample2 with a resolution of 1/65,536 counts/sample

-1/2 to +1/2 counts/sample3, with a resolution of 1/4,294,967,296 counts/sample

Trapezoidal (host commands final position, max velocity and acceleration)

Velocity contouring (host commands max. velocity, acceleration)

Electronic Gear (Encoder position of one axis is used as position command for another axis). A total of 2

electronic gears are supported (2 encoders and 1 output each). Not available in MC1131A

Algorithmic (briefly energize motor coils)

Microstepping (advance motor to known phase position)

Direct set (explicitly set current commutation angle)

90 degrees (used with 2-phase brushless motors)

2-phase brushless motors: 2

2.

2

3

*Exact servo loop time is 271.36 uSec, 270 is an approximation

Trajectory Profile Generation

The trajectory profile generator performs calculations to determine the

target position, velocity and acceleration at each servo loop. These

calculations are performed using the current profile mode and profile

parameters set by the host. Four trajectory profile modes are supported:

- S-curve point to point

- Trapezoidal point to point

- Velocity contouring

- Electronic Gear

The commands to select these profile modes are

SET_PRFL_S_CRV (to select the s-curve mode), SET_PRFL_TRAP

(to select the trapezoidal mode) SET_PRFL_VEL (to select the

velocity contouring mode) and SET_PRFL_GEAR (to select the

electronic gear mod).

Throughout this manual various command mnemonics will be

shown to clarify chipset usage or provide specific examples. See

the Host Communications section for a description of host

command nomenclature.

18

Page 19

The profile mode may be programmed independently for each axis. For

example axis #1 may be in trapezoidal point to point mode while axis

#2 is in S-curve point to point.

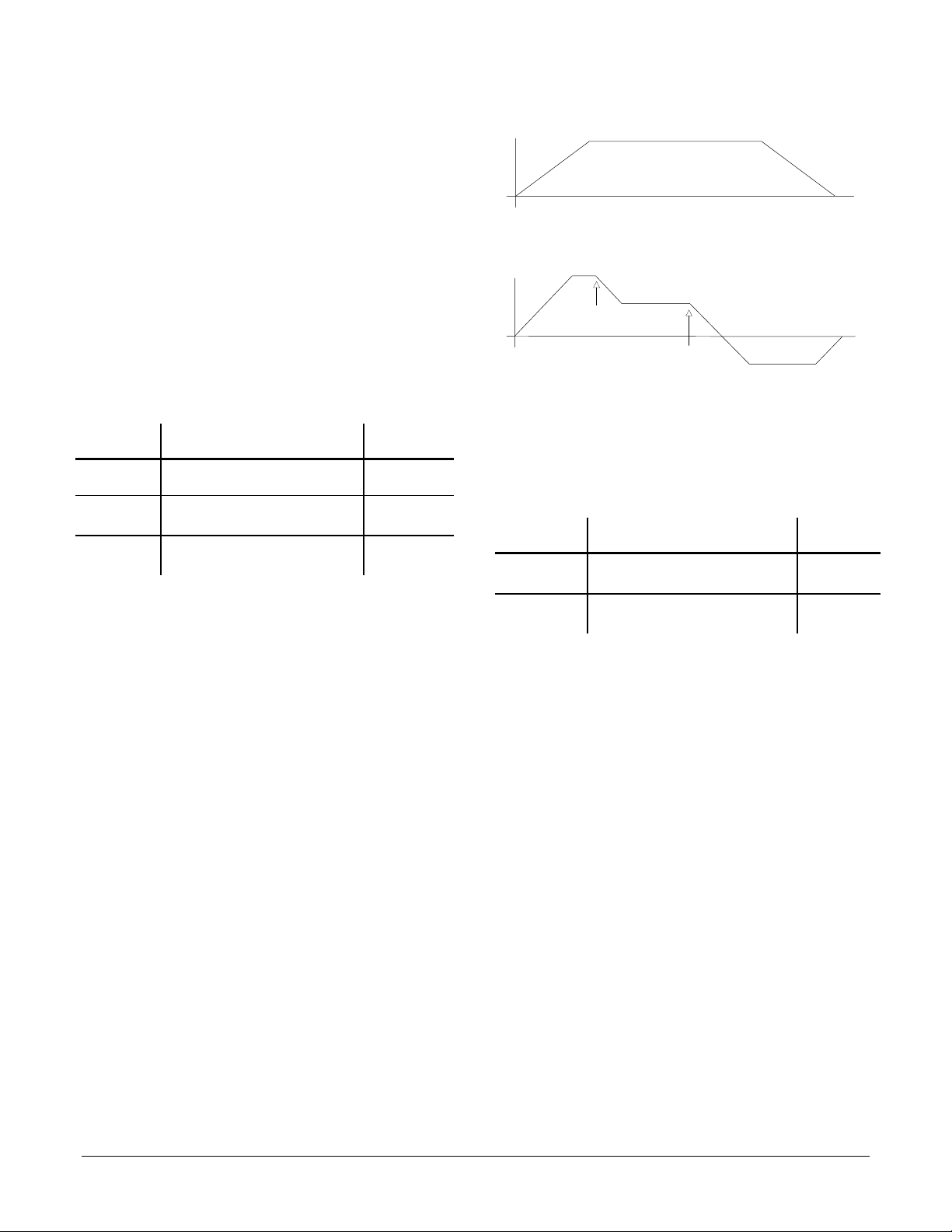

Use the following figure showing a typical S-curve velocity vs. time

graph for reference in reading the next section:

Generally, the axis should be at rest when switching profile modes.

Under certain conditions however, switching into certain profile modes

"on-the-fly" is allowed. See specific profile descriptions for details.

S-curve Point to Point

The following table summarizes the host specified profile parameters

for the S-curve point to point profile mode:

Profile

Parameter

Destination

Position

Maximum

Velocity

Max. Accel.

Jerk

* uses 1/216 scaling. Chipset expects a 32 bit number which

has been scaled by a factor of 65,536 from units of

counts/sample time. For example to specify a velocity of 2.75

counts/sample time, 2.75 is multiplied by 65,536 and the

result is sent to the chipset as a 32 bit integer (180,224 dec.

or 2c000 hex.).

** uses 1/216 scaling. Chipset expects a 16 bit number which

has been scaled by a factor of 65,536 from units of

counts/sample time2. For example to specify an acceleration

of .175 counts/sample time2, .175 is multiplied by 65,536 and

the result is sent to the chipset as a 16 bit integer (11,469

dec. or 2ccd hex).

Representation & Range Units

signed 32 bits

counts

-1,073,741,824 to 1,073,741,823

unsigned 32 bits* (1/2

16

scaling)

counts/smpl

0 to 1,073,741,823

unsigned 16 bits ** (1/2

16

scaling)

counts/smpl

0 to 32,767

unsigned 32 bits *** (1/2

32

scaling)

counts/smpl

0 to 2,147,483,647

PhaseI.Phase

Phase

II.

III.

Phase

IV.

PhaseV.Phase

VI.

Phase

VII.

S-curve profile

The S-curve profile drives the axis at the specified jerk until the

maximum acceleration is reached. (phase I). it will then drive the axis at

jerk = 0 (constant acceleration) through phase II. It will then drive the

2

axis at the negative of the specified jerk though phase III, such that the

axis reaches the specified maximum velocity with acceleration = 0. This

3

completes the acceleration phase. At the end of the acceleration phase

of the move, the velocity will be constant, and the acceleration will be 0.

At the appropriate time, the profile will then decelerate (phases V, VI

and VII) symmetrically to the acceleration phase such that it arrives at

the destination position with acceleration and velocity = 0.

There are several conditions where the actual velocity graph of an Scurve motion will not contain all of the segments shown in the above

figure. For example, if the max. acceleration is not reached before the

"half-way" point to the max. velocity, then the actual velocity profile will

not contain a phase II or a phase VI segment (they will have a duration

of 0 servo loops). Such a profile is shown below:

PhaseI.Phase

III.

Phase

IV.

PhaseV.Phase

VII.

*** uses 1/2

has been scaled by a factor of 4,294,967,296 (2

32

scaling. Chipset expects a 32 bit number which

32)

from units

of counts/sample time3. For example to specify a jerk value of

.0075 counts/sample time3, .0075 is multiplied by

4,294,967,296 and the result is sent to the chipset as a 32 bit

integer (32,212,256 dec. or 1eb8520 hex).

S-curve that doesn't reach max. acceleration

Another such condition is if the position is specified such that max.

velocity is not reached. In this case there will be no phase IV, and there

may also be no phase II and VI, depending on where the profile is

"truncated".

While the S-curve profile is in motion, the user is not allowed to

change any of the profile parameters. The axis must be at rest

before a new set of profile parameters can be executed. If

parameters are changed during motion then a 'command error'

19

Page 20

will occur, and all new parameters will be ignored except the

position. See the section of this manual entitled "Command Error"

for more information..

Vel.

Before switching to the S-curve point to point profile mode, the

axis should be at a complete rest.

When the axis is in the S-curve profile mode, the SET_MAX_ACC

command should be used to load the max. acceleration value. The

alternate acceleration loading command SET_ACC can not be

used.

Trapezoidal Point to Point

The following table summarizes the host specified profile parameters

for the trapezoidal point to point profile mode:

Profile

Parameter

Destination

Position

Maximum

Velocity

Accel.

In the trapezoidal point to point profile mode the host specifies a

destination position, a maximum velocity, and an acceleration. The

trajectory is executed by accelerating at the commanded acceleration to

the maximum velocity where it coasts until decelerating such that the

destination position is reached with the axis at rest (zero velocity). If it is

not possible to reach the maximum velocity (because deceleration must

begin) then the velocity profile will have no "coasting" phase. The

acceleration rate is the same as the deceleration rate.

A new maximum velocity and destination position can be specified

while the axis is in motion. When this occurs the axis will accelerate or

decelerate toward the new destination position while attempting to

satisfy the new maximum velocity condition.

When in Trapezoidal point to point profile mode, to change the

acceleration, the axis must come to a complete stop. After this has

occurred, a new acceleration value can be loaded. If the

acceleration parameter is changed during motion then a

'command error' will occur, and all updated parameters will be

ignored except the position. See the section of this manual

entitled "Command Errors" for more information.

Before switching to the Trapezoidal point to point profile mode,

the axis should be at a complete rest.

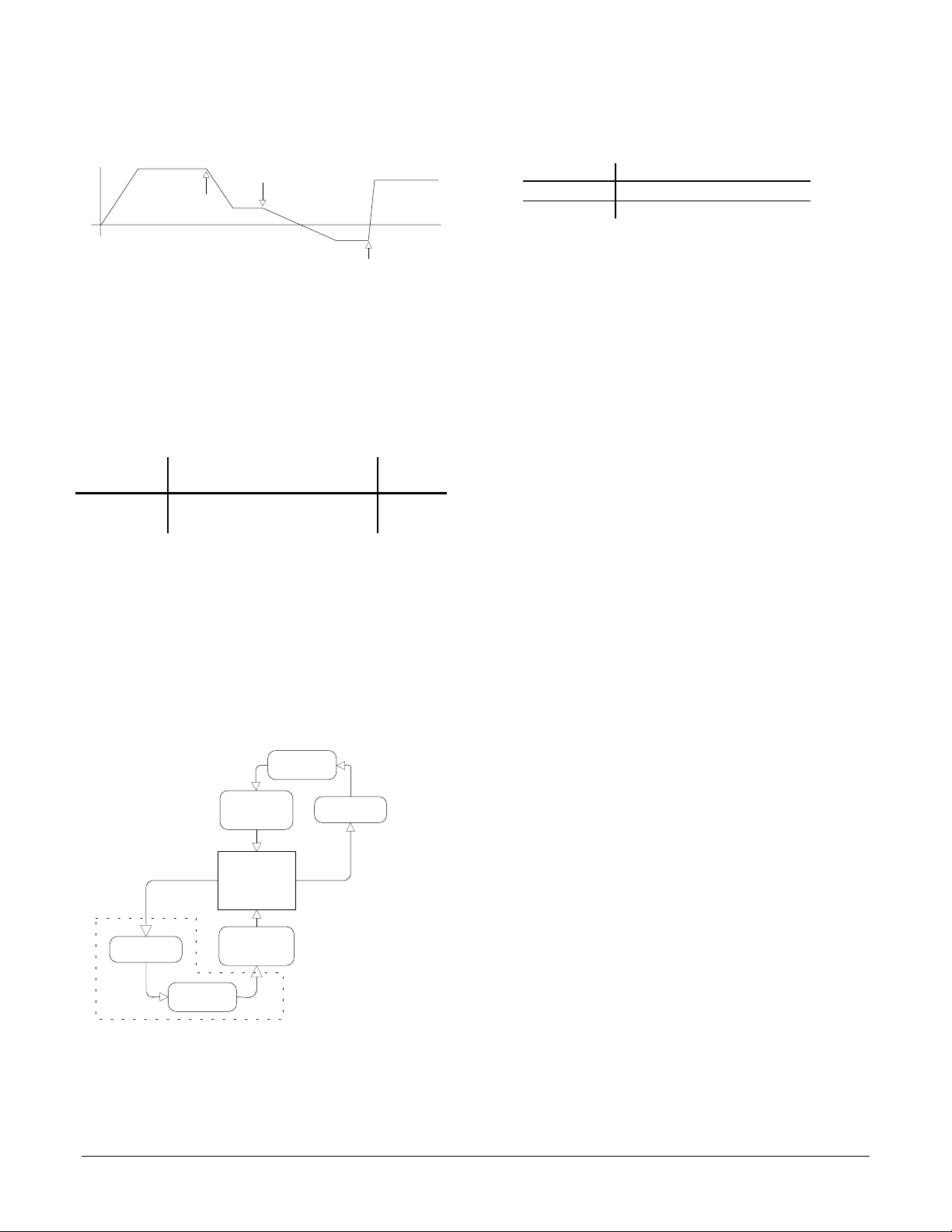

The following figure shows a velocity profile for a typical point to point

trapezoidal move, along with a more complicated move involving on the

fly changes to the maximum velocity and the destination position.

Representation & Range Units

signed 32 bits

counts

-1,073,741,824 to 1,073,741,823

unsigned 32 bits (1/2

16

scaling)

counts/smpl

0 to 1,073,741,823

unsigned 32 bits (1/2

16

scaling)

counts/smpl

0 to1,073,741,823

2

Simple trapezoidal mode motion

Vel.

change max

velocity

change target

position

Complex trapezoidal mode motion

Velocity Contouring

The following table summarizes the host specified profile parameters

for the Velocity contouring profile mode:

Profile

Parameter

Maximum

Velocity

Acceleration

* negative numbers using 1/216 scaling are handled no

differently than positive numbers. For example if an

acceration value of -1.95 counts/sample time2 is desired, -

1.95 is multipled by 65,536 and the result is sent to the

chipset (-127,795 dec. or fffe0ccd hex).

In this profile mode the host specifies two parameters, the commanded

acceleration, and the maximum velocity. The trajectory is executed by

continuously accelerating the axis at the commanded rate until the max.

velocity is reached, or until a new acceleration command is given.

The maximum velocity value must always be positive. Motion

direction is controlled using the acceleration value. Positive

acceleration values result in positive motion, and negative

acceleration values result in negative motion.

There are no restrictions on changing the prof ile parameters on

the fly. Note that the motion is not bounded by position however.

It is the responsibility of the host to generate acceleration and

max. velocity command values which result in safe motion, within

acceptable position limits.

The following figure shows a typical velocity profile using this mode.

Representation & Range Units

unsigned 32 bits (1/2

16

scaling)

counts/smpl

0 to 1,073,741,823

signed 32 bits* (1/2

16

scaling)

counts/smpl

-1,073,741,824 to 1,073,741,823

Time

Time

2

20

Page 21

Example Velocity Contouring Mode

Vel.

change

max velocity

change

acceler a tion

change max

velocity and

acceler a tion

There are no restrictions on switching the profile mode to velocity

contouring while the axis is in motion.

In addition, the master /slave axis combinations are fixed. The following

chart shows the allowed master/slave combinations for each chipset:

chipset p/n gear pairs (master -> slave)

MC1231A #2 -> #1

MC1131A not available

Time

Typically the master axis is only used for encoder input. It is possible

however to use the master axis as a normal driven axis by leaving it

enabled, and using one of the three trajectory modes other than

electronic gear for the master axis. The net effect of this will be to run

two servo motors off of the same trajectory profile (although at a

different ratio if so programmed).

Electronic Gear

The following table summarizes the host specified profile parameters

for the electronic gear profile mode:

Profile

Parameter

Gear Ratio

* for example to specify a gear ratio of +1.5 to 1 the value

1.5*65,536 is sent to the chipset (98,304). Alternatively to set

the gear ratio as -11.39 to 1 the value -11.39*65,536 is sent (746,455 dec. or fff49c29 hex.).

In this profile mode, the host specifies one parameter, the gear ratio.

The target position is generated by applying the specified gear ratio to

the current position of another axis, slaving the driven axis to the axis

providing the position input. The following figure shows the

arrangement for encoders and motor drives in a typical electronic

gearing application.

Representation & Range Units

signed 32 bits* (1/2

16

scaling)

-

-1,073,741,824 to +1,073,741,823

Motor

Slave

Encoder

Amplifier

This configuration is shown in the previous diagram as 'optional'

components. Using this configuration the chipset can be made to

perform useful functions such as linear interpolation of two axis.

There are no restrictions on changing the gear ratio when the axis

is in motion, although care should be taken to select ratios such

that safe motion is maintained.

The specified gear ratio (SET_RATIO command) indicates the

number of target counts generated per input encoder count. For

example a gear ratio of 1.5 means 1.5 counts of the slave axis are

generated for every count of the master axis.

There are also no restrictions on changing to this profile mode

while the axes is in motion.

Trajectory Control

Normally each of the above trajectory modes will execute the specified

trajectory, within the specified parameter limits, until the profile

conditions are satisfied. For example for the point-to-point profile modes

this means that the profile will move the axis until the final destination

position has been reached, at which point the axis will have a velocity

of zero.

MC1231A

Amplifier

Motor

Master

Encoder

Optional

Because a geared axis takes up two encoder channels, the total

number of geared axes supported per chipset is 1/2 the total # of axes.

Halting The Trajectory

In some cases however it is necessary to halt the trajectory manually,

for safety reasons, or simply to achieve a particular desired profile. This

can be accomplished using one of two methods; abrupt stop, or smooth

stop.

Abrupt stops are accomplished using the STOP command. This

command instantaneously stops the trajectory generator by setting the

velocity of the axis to zero. This control mode is typically used during an

emergency stop, when no deceleration phase is desired.

Smooth stops are accomplished using the SMOOTH_STOP command.

This command causes the trajectory to decelerate at a rate equal to the

specified acceleration rate, until a velocity of zero is reached. In

addition the form of the deceleration is symmetric to the acceleration

21

Page 22

phase. For example if the profile mode is S-curve, and a

SMOOTH_STOP command is given, the profile will decelerate in a

manner exactly equal and opposite to the acceleration phase.

The STOP command functions in all profile modes; S-curve pointto-point, Trajectory point-to-point, Velocity Contouring, and

Electronic Gear.

The SMOOTH_STOP functions in S-curve point-to-point,

Trajectory point-to-point, and Velocity Contouring profiling mode.

It does not function in Electronic Gear mode.

Caution should be exercised when using the STOP command due

to the large and abrupt changes in motion that may occur.

Motion Complete Status

The motion complete and in-motion bits indicate the state of the

trajectory generator, not the actual motor. Even if the trajectory

generator has completed a motion, the actual axis position may or

may not be at rest depending on servo lag, stability, and other

system conditions.

Digital Servo Filtering

A digital filter is available for use in calculating a motor output signal.

The filter used is a PID (proportional, integral, derivative) filter, along

with a velocity feedforward term and a term to adjust the offset, also

called the DC bias value. This filter type is known as a PID+Vff filter.

This filter uses programmable gain values which can be tuned to

provide excellent control accuracy and stability over a large range of

systems.

To simplify the programming of a complete motion system it is

convenient to have the motion chipset indicate when a particular profile

move has been completed.

This function is provided by two status bits in the chipset's status word

(See the section of this manual entitled "Axis Status " for more

information on the axis status word). These two bits are called the

motion complete bit, and the in-motion bit.

The motion complete bit is controlled interactively by the chipset and

the host. After a motion has completed, the chipset sets the motion

complete bit on. The host may then poll this bit to determine that motion

is complete, or if desired, the host can program the chipset to

automatically signal when the motion is complete (using an interrupt). In

either case once the host has recognized that the motion has been

completed the host clears the motion complete bit, enabling the bit to

indicate the end of motion for the next move.

The following list shows the conditions that will cause the motion

complete bit to occur:

- Profile has reached the destination position (point-to-point

profile modes only)

- Axis trajectory reaches a velocity of zero and the current

velocity command is zero

- SMOOTH_STOP command is given and axis trajectory

reaches a velocity of zero

- STOP command is given

- Limit switch condition occurs

The in-motion bit is similar to the motion complete bit except that it

continuously indicates the status of the axis without interaction with the

host. In addition this bit is used exclusively for polled mode operations.

It can not cause an interrupt to the host to be generated.

The motion complete and the in-motion indicator bits function in

the S-curve point-to-point, Trapezoidal point-to-point, and Velocity

Contouring profile modes only. They do not function when the

profile mode is set to electronic gearing.

The following schematic diagram shows the computational flow for the

PID+Vff digital filter.

Target

Velocity

Proportional Term

P = En * Kp

Bias

Kvff

Target

Position

+

-

Integral Term

I = (S+En)*Ki

S = S+En

Derivative Term

D = (En-E(n-1))*Kd

+

+

+

+

+

Actual Position

From Encoder

In the PID+Vff filter, the host-specified parameters are:

Symbol Name Representation & Range

Kp Proportional Gain unsigned 16 bits (0 to 32767)

Ki Integral Gain unsigned 16 bits (0 to 32767)

Kd Derivative Gain unsigned 16 bits (0 to 32767)

Ilim Integration Limit unsigned 16 bits (0 to 32767)

Kvff Velocity Feedforward

gain

MtrBias DC motor offset signed 16 bits (-32767 to 32767)

The PID+Vff filter is calculated as follows:

Position Errorn = En = TPn - AP

Outputn = En*Kp + (En-E

+ MtrBias

n-1

unsigned 16 bits (0 to 32767)

n

)*Kd + Int(En)*Ki/256 + TrgtVel*Kvff/4

Output

To Motor

22

Page 23

where: En is the position error at sample time n

TPn is the target position at sample time n

APn is the actual position at sample time n

Int(En) is the integration sum at time sample n

TrgtVel is the current desired velocity in counts/sample

MtrBias is the motor bias value

All multiplied error quantities are saturated to fit within a 16 bit number

so that no discontinuities in the output signal occur at values beyond +/-

2 15. The integral term is actually maintained to an accuracy of 24 bits,

but only the top 16 bits are used. This results in a more useful range for

Ki, the integral gain.

The result of this calculation is a 16 bit number. The top 10 bits of this

result become the output value if the motor output mode is PWM (10

bits magnitude), and the entire word is used if the mode is DAC16.

The motor bias value is applied to the filter value at all times when the

chipset is in closed loop mode. If the chipset transitions to open loop

mode (MTR_OFF command is given or a motion error occurs with

automatic motor stop enabled) than the motor bias value will be output

to the motor by itself, until a manual motor command value is given

(SET_MTR_CMD command), at which point this host-provided motor

command value, without modification by the motor bias value, becomes

the active motor command.

The following example illustrates this: If the chipset is in closed loop

mode with a motor bias value of 100, then if a motor off command is

given (MTR_OFF), then the output motor command will be exactly 100.

Thereafter if the host sends a manual motor command of 200 (using the

SET_MTR_CMD command), then the output motor command will be

200. At this instant the chipset is returned to closed loop mode however

(MTR_ON command), the motor bias value will again be added to the

filter output.

Care should be taken when setting a Ki value for the first time. If

the system has already been running and the integration value is

unknown, an abrupt 'jump' may occur when the Ki value is set to a

non-zero value. To avoid this set the I_LM (integration limit) to 0,

set the Ki to the desired value, and then set I_LM to the desired

integration limit value. This will 'clear' all prior integration values,

smoothly enabling the integration function from that point

forward.

Motor Limit

In addition to setting various PID gain values the MC1231A also allows

the maximum value output by the filter to be set. This motor limit value

is set using the command SET_MTR_LMT. It can be read back using

the command GET_MTR_LMT.

The specified motor limit affects the filter output such that if the

magnitude of the filter output value (positive as well as negative)

exceeds the motor limit than the output value is maintained at the motor

limit value. Once the filter output value returns below the specified limit

than normal servo filter values are output

The motor limit is only applied during closed loop servo operations,

when the servo filter controls the motor output value. It does not affect

the output motor value applied during open loop operations

Motor Bias

If the specified motor bias value does not properly compensate for

the offsetting DC load, then after a motion error with automatic

motor stop enabled or after a MTR_OFF command the axis may

move suddenly in one direction or another. It is the responsibility

of the host to select a motor bias value such that safe motion is

maintained.

Parameter Loading & Updating

Various profile & servo parameters must be specified by the host for an

axis to be controlled in the desired manner. To facilitate precisely

synchronized motion, these parameters and related control commands

are loaded into the chip using a double-buffered scheme. In this

scheme, the parameters and action commands being loaded are not

acted upon (copied from the double-buffered to the active registers)

until an update signal is given.

This update signal can consist of either a "manual" update command,

or one of several conditional breakpoints. Whichever update method is

used, at the time the update occurs, all of the double buffered registers

and commands will be copied to the active registers. Conversely,

before the update occurs, loading the double-buffered registers or

executing the double buffered commands will have no effect on the

system behavior.

The double buffered registers are listed below.

When using an axis which has a net force in one direction or the other

(such as a vertical axis which experiences the force of gravity) the

motor bias function of the PID compensation filter may be useful. By

adding a constant bias value to the filter output, the overall position

error of the filter can be reduced by directly compensating for the

constant force.

The motor bias value is set using the command SET_MTR_BIAS. It can

be read back using the command GET_MTR_BIAS.

23

Page 24

Register Name Command to set

destination position SET_POS

maximum velocity SET_VEL

acceleration SET_ACC

maximum acceleration SET_MAX_ACC

jerk SET_JERK

ratio SET_RATIO

Kp SET_KP

Ki SET_KI

Kd SET_KD

Kvff SET_KVFF

Integration limit SET_I_LM

The double-buffered commands are: STOP, SMOOTH_STOP, and

SYNCH_PRFL.

Manual Update

There are two methods of manually updating the double-buffered

parameters, one for a single axis instantaneous update and one for a

multiple-axis update.

The single axis instantaneous update, which is specified using the

UPDATE command, forces the parameters for the current axis to be

updated at the next servo loop.

The multiple axis instantaneous update, which is specified using the

MULTI_UPDATE command, causes multiple axes to be updated

simultaneously. This can be useful when synchronized multi-axis

profiling is desired. This command takes a 1 word argument which

consists of a bit mask, with 1 bit assigned to each axis. Executing this

command has the same affect as instantaneously switching to each

desired axes, and executing an UPDATE command.

generator) equals or exceeds the specified breakpoint value. This

breakpoint is set using the SET_POS_BRK command.

Negative Target Position Breakpoint:.

A 32 bit position breakpoint can be specified which will result in

the parameters being updated when the current target position

(the instantaneous desired axis position output from the profile

generator) equals or is less than the specified breakpoint

value.This breakpoint is set using the SET_NEG_BRK command.

Positive Actual Position Breakpoint

A 32 bit position breakpoint can be specified which will result in

the parameters being updated when the current actual position

(the instantaneous position of the actual axis hardware) equals or

exceeds the specified breakpoint value.This breakpoint is set

using the SET_ACTL_POS_BRK command.

Negative Actual Position Breakpoint:.

A 32 bit position breakpoint can be specified which will result in

the parameters being updated when the current actual position

(the instantaneous position of the actual axis hardware) equals or

is less than the specified breakpoint value.This breakpoint is set

using the SET_ACTL_NEG_BRK command.

Time Breakpoint

A 32 bit time break point can be specified which will result in the

parameters being updated when the # of servo loops executed

since chip set reset (the current chip set time) is equal to the time

breakpoint value.The # of servo loops continuously increases

until it rolls over from 232 - 1 back to 0.The time breakpoint is set

using the SET_TIME_BRK command.

Motion Complete Breakpoint

A breakpoint can be specified which will result in the parameters

being updated when the previous motion has been completed

(motion complete bit is set). When using this breakpoint no 32 bit

compare value is required.

Breakpoints

A breakpoint is a convenient way of programming a profile or filter

change upon some specific condition. There are two types of

breakpoints, those that have a 32-bit comparitor value associated with

them and those that do not. For those that have the comparitor, a 32-bit

comparitor value is loaded into the breakpoint compare register first,

and then one of the breakpoint conditions is specified. For those

breakpoint modes without associated comparitor values only the

breakpoint condition needs to be specified.

The double-buffered registers and commands will be updated upon

satisfaction of the specified breakpoint condition.

Here is a list of all of the available breakpoint conditions.

Positive Target Position Breakpoint

A 32 bit position breakpoint can be specified which will result in

the parameters being updated when the current target position

(the instantaneous desired axis position output from the profile

External Breakpoint

A breakpoint can be specified which will result in the parameters

being updated when the home signal of the corresponding axis

becomes active (low). When using this breakpoint no 32 bit

compare value is required. This breakpoint is useful whenever it is

desired that an external signal starts, stops, or otherwise modifies

the profile movement.

Normally, whenever one of these conditions has been programmed and

the condition occurs, the double-buffered parameters will automatically

be shifted to the active registers. There is a mechanism to disable this

"automatic update upon breakpoint" however. This is discussed in the

next section.

The above breakpoint modes are particularly useful during multi-axis

motion. This is because the next profile commands (set of hostspecified trajectory commands) can be pre-loaded and activated at the

precise position or time required, with no delay incurred to send an

update or load parameters command.

24

Page 25

After a breakpoint condition has bee n satisfied it is no longer

active. To set up another breakpoint condition, a new one must be

explicitly set by the host.

The double-buffered registers that are shifted to the active

registers do not change upon being shifted, only the active

registers change.

Disabling Automatic Profile Update

Normally, when a breakpoint condition has been satisfied, it causes the

profile & filter parameters to be automatically updated. For certain types

of profiles however, it may be desirable to still use the breakpoint

mechanism (to allow it to generate a host interrupt for example), but not

to have the profile update.

Except for the MULTI_AXIS command, parameter loading and updating

is controlled individually for each axis. In addition each axis has a

separate 32-bit breakpoint register, and can be set to various individual

breakpoint conditions.

External Breakpoints and Homing

By connecting a home input sensor to the home signal input of the

MC1231-series chipsets it is possible to cause the chipset to halt a

motion at the moment it receives the home signal. This capability

makes it ideal for performing a home sequence. The following host I/O

sequence illustrates this:

GET_HOME ; check to make sure axis not already at

; home. If so, then a 'reverse' move must

; be made to retract axis from home switch.

; This 'reverse' sequence is not indicated

; here for simplicity sake

SET_CAPT_HOME ; set trigger capture to home signal

CLR_STATUS ; clear status register

GET_CAPT ; clear out any previous captures

SET_POS 12345 ; load home move parameters

SET_VEL 23456

SET_ACC 345

UPDATE ; start home move

SET_EXT_BRK ; initiate external breakpoint mode

SMOOTH_STOP ; load (but do not update) a stop command

This sequence will start a homing move which will come to a smooth

stop as soon as the axis encounters the home switch. In addition the

capture register will be loaded with the exact location of the home

sensor. This register can be used in conjunction with the

GET_ACTL_POS and SET_ACTL_POS commands to set the position

to any desired location. For example if it is desired that the home

sensor be located at a position of 0, then the new position should be set

to the current actual axis position minus the capture position. This is

shown in the sequence below, which should be executed after the axis

has come to a stop.

current_pos = GET_ACTL_POS

capture_pos = GET_CAPT

SET_ACTL_POS (current _pos - capture_pos)

As is the case for all of the breakpoint modes, the external breakpoint

can not only be used to stop an ongoing move, but to start or otherwise

modify a move as well. This flexibility makes it well suited for