Page 1

PM5354

Released

S/UNI MULTI 2x12

Multi-rate SATURN User Network Interface for 2x622 and 4x155

FEATURES

• Single chip ATM and POS User

Network Interface that supports up to

2x622.08 Mbit/s, 4x155.52 Mbit/s,

1x622.08 + 3x155.52 Mbit/s, or

2x622.08 Mbit/s + 2x155.52 Mbit/s.

• Implements the ATM Forum User

Network Interface Specification and

the ATM physical layer for Broadband

ISDN according to CCITT

Recommendation I.43 2.

• Implements the Point-to-Poi nt Protocol

(PPP) over SONET/SDH specification

according to RFC 2615(1619)/1662 of

the PPP Working Group of th e Intern et

Engineering Task Force (IETF).

• Processes up to two duplex bit-serial

622.08 Mbit/s STS-12 (STM-4) data

streams with on-chip clock and data

recovery and clock synthe s is. Each

STS-12 (STM-4) may contain a single

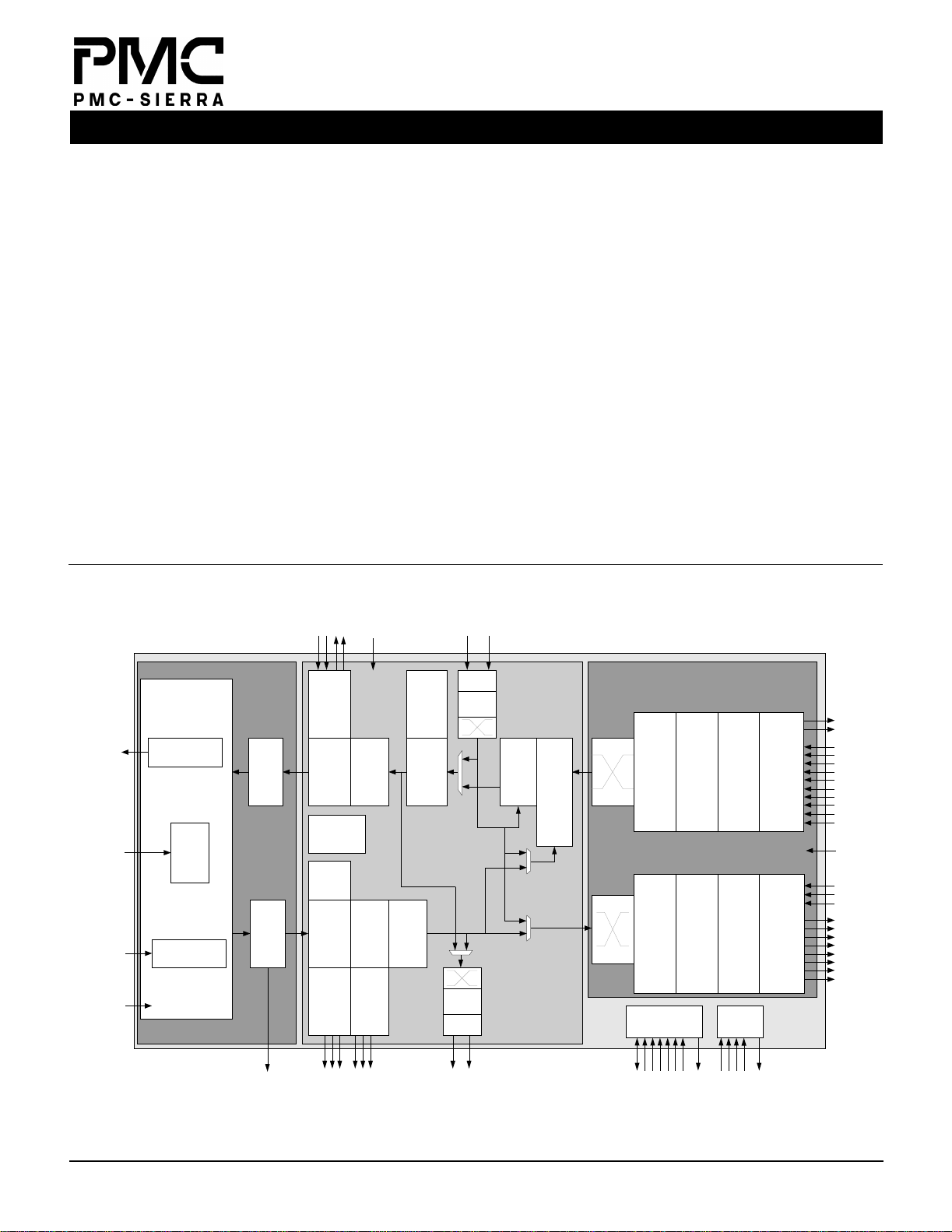

BLOCK DIAGRAM

STS-12c (AU-4-4c) or up to four

STS-3c (AU-4).

• Processes up to four duplex bit-serial

155.52 Mbit/s STS-3 (STM-1) data

streams with on-chip clock and data

recovery and clock synthesis. Each

STS-3 (STM-1) may contain a single

STS-3c (AU-4).

• Permits mixed OC-12 and OC-3 data

streams.

• Complies with Telcordia

GR-253-CORE jitter tolerance, jitter

transfer, and intrinsic jitter criteria.

• Provides termination for SONET

Section, Line, and Path overhead or

SDH Regenerator Section, Multiplex er

Section, and High Order Path

overhead.

• Provides cross bar functiona lit y to

swap STS-12 and STS-3 clients

to/from different line-side inte rfac es .

• Provides support for automatic

protection switching via a 4-bit LVDS

777.6 MHz port.

• Provides cross bar functionality to

swap STS-12 and STS-3 lines and/or

clients to/from differen t APS interfaces.

• Provides UTOPIA Level 3 32-bit wide

System Interface (clocked up to 104

MHz) with parity support for ATM

applications.

• Provides SATURN® POS-PHY™

Level 3 (32-bit System Interface

(clocked up to 104 MHz) for Packet

over SONET (POS) or ATM

applications.

• Supports independent loo p-ti me d

operation for each transmit serial

stream.

TXD_P/N[4:1]

REFCLK77_P/N

RXD_P/N[4:1]

SD[4:1]

SD_TEST

Transmit Analog

Circuitry

Clock

Synthesis

Unit

Receive Analog

Circuitry

TTOH[4:1]

TTOHEN[4:1]

TTOHCLK[4:1]

TTOHFP[4:1]

SYSCLK

LINE_IF PL3/UL3

Transmit

Line

Inte rface

Receive

Line

Interface

Transmit

Section

Trace

Processor

(4)

Transmit

Transmit

Virtual

Regen/

Container

Multiplexor

Processor

Multiplexor

Processor

Processor

RCLKO

(4)

SARC

Alarm Report

Controller (4)

Bit error

rate mon

(4)

Receive

Regen/

(4)

Receive

Section

Trace

(4)

RTOH[4:1]

RTOHFP[4:1]

RTOHCLK[4:1]

Aligner

(4)

Receive

Path

Processor

(4)

Receive

Path

Trace

Processor

(4)

SALM[4:1]

RALM[4:1]

Transmit

Path

Trace

Processor

(4)

Transmit

Path

Processor

(4)

Receive

Virtual

Container

Aligner

(4)

B3E[4:1]

X-Bar

Transmit

APS

(4)

LVDS I/f

(4)

APSO_P/N[4:1]

APSI_P/N[4:1]

LVDS I/f

(4)

Receive

APS

(4)

X-Bar

APSOFP

APSIFP

SONET/APS

band

Alarm

(4)

In

PRBS

generator

/ monitor

(4)

Transmit

X-Bar

Receive

X-Bar

Transmit

channel

Assigner

(4)

Receive

channel

Assigner

(4)

Microprocessor

Interface

RDB

WRB

A[13:0]

D[15:0]

ALE

CSB

Transmit

ATM/POS

processor

(4)

Receive

ATM/POS

processor

(4)

RSTB

INTB

Transmit

FIFO

Receive

FIFO

JTAG

Interface

TDI

TCK

TMS

TRSTB

UTOP IA L 3/

POS-PHY

L3

Transmit

Interface

UTOPIA L3/

POS-PHY

L3

Receive

Interface

TDO

STPA

TCA/PTPA

TADR[3:0]

TENB

TSX

TSOC/TSOP

TEOP

TDAT[31: 0]

TPRTY

TMOD[1:0]

TERR

TFCLK

PL3EN

RAD R[3:0]

RENB

RFCLK

RDAT[ 3 1:0]

RCA/RVAL

RPRTY

RSX

RSOC/RSOP

REOP

RMOD[1: 0]

RERR

PMC-2021540 (R3) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2003

Page 2

Released PM5354 S/UNI MULTI 2x12

Multi-rate SATURN User Network Interface for 2x622 and 4x155

• Supports independent line loop back

from each line side receive stream to

the corresponding trans mit stream and

independent diagn ostic loop back from

the line side transmit stream to the

corresponding line side receive stream

interface.

• Provides PRBS-23 generator/monitor

for off-line link verification

• Provides a standard 5 signal IEEE

1149.1 JTAG test port for boundary

scan board test purposes.

• Provides a generic 16-bit

microprocessor bus inter face for

configuration, control, and status

monitoring.

• Low power 1.8V CMOS core logic with

3.3V CMOS/TTL compatible digital

inputs and digital outputs. PECL

inputs and outputs are 3.3V

compatible.

• Industrial temperature range (-40°C to

+85° C).

• 500-ball UBGA package.

APPLICATIONS

• ATM and Multi-service switches,

routers, and switch/routers.

• SONET/SDH Add/Drop Multiplexers

with data processing capab ili ties.

• Uplink cards.

• SONET/SDH ATM/POS Test

Equipment.

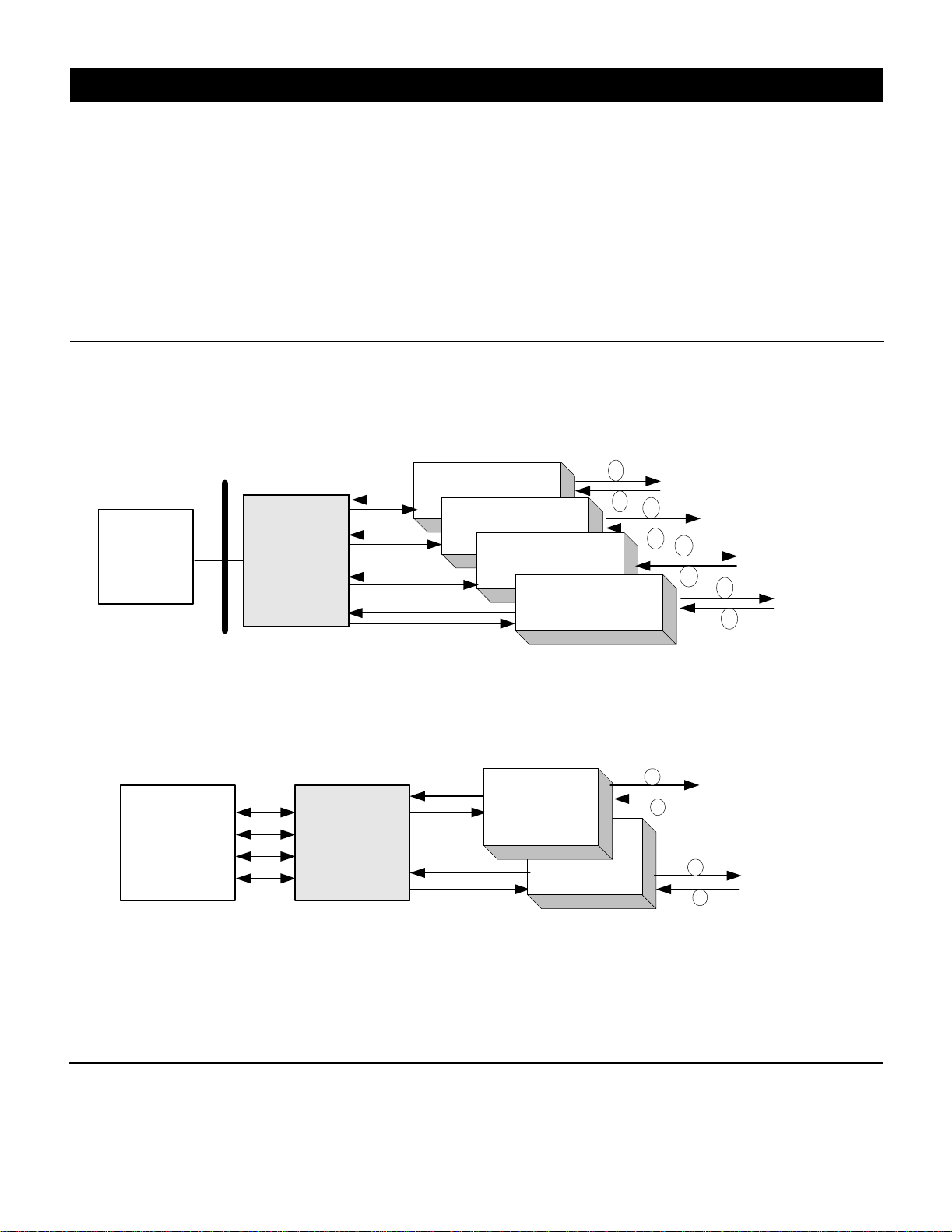

TYPICAL APPLICATIONS

2XOC-12 OR 4XOC-3 PORT CARD FOR MULTI-SERVICE SWITCHES OR ROUTERS

POS-PHY L3 or

ATM/Link Layer

Device

UTOPIA L3

PECL/CML

PM5354 S/UNI

MULTI 2x12

Multi-rate 622 Mbit/s or

155 Mbit/s Optical

Transceiver

Multi-rate 622 Mbit/s or

155 Mbit/s Optical

Transceiver

155 Mbit/s Optical

Transceiver

622 Mbit/s or

155 Mbit/s

622 Mbit/s or

155 Mbit/s

155 Mbit/s

155 Mbit/s Optical

2XGE TO 2XOC-12 ETHERNET OVER SONET/SDH APPLICATION

4 x 777.6

PM5397

ARROW 2xGE

MHz LDVS

PM5354

S/UNI

MULTI 2x12

PECL/CML

622 Mbit/s Optical

Transceiver

Transceiver

155 Mbit/s

622 Mbit/s

622 Mbit/s

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: +1.604.415.6000

Fax: +1.604.415.6200

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

All product documentation is

available on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

PMC-2021540 (R3)

Copyright PMC-Sierra, Inc. 2003. All

rights reserved.

For a complete list of PMC-Sierra’s

trademarks and registered trademarks,

visit: http://www.pmc-sierra.com/legal

Loading...

Loading...