RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

RM5261A™

Preliminary

RM5261A™ Microprocessor with 64-Bit

System Bus

Data Sheet

Proprietary and Confidential

Preliminary

Issue 2, September 2001

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

Document ID: PMC-2002240, Issue 2

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

Legal Information

Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers’ internal use. In

any event, you cannot reproduce any part of this document, in any form, without the express written

consent of PMC-Sierra, Inc.

PMC-2002240 (P2)

Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMCSierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the

fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts

or systems, of an y of t he pr oducts of PMC-Si erra , Inc., or an y port io n ther eof, r efer red to i n this document .

PMC-Sierra, Inc. expressly disclaims all representations and warranties of any ki nd regarding the contents

or use of the information, including, but not limited to, express and implied warranties of accuracy,

completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential

damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or

reliance upon the infor ma tion, whether or not PMC-Sierra, Inc . has been advised of the possib il it y of s uch

damage.

Trademarks

RM5261A is a trademark of PMC-Sierra, Inc.

Contacting PMC-Sierra

PMC-Sierra, Inc.

105-8555 Baxter Place Burnaby, BC

Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: document@pmc-sierra.com

Corporate Information: info@pmc-sierra.com

Technical Support: apps@pmc-sierra.com

Web Site: http://www.pmc-sierra.com

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 2

Document ID: PMC-2002240, Issue 2

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

Revision History

Issue

No. Issue Date Details of Change

2 September 2001 Added 1.8 V to the feature: 1.65 V or 1.8 V core with 3.3 V or 2.5 V I/O (p9).

Changed recommended operating conditions VccInt to 1.57 V to 1.85 V and

VccP to 1.57 V to 1.85 V. Added VssP commercial and industrial values.

Modified Note 4.

Added reference to VccInt to Power Consumption table. Changed standby

modes to 350. Changed maximum worst case instruction mix to 1250. Modified

Note 1.

Modified SysClock Frequency and SysClock Period values in the Clock

Parameters table.

1 March 2001 Applied PMC-Sierra template to existing MPD (QED) FrameMaker document.

Revised features list, Absolute Maximum Ratings table, Recommended

Operating Conditions table, DC Electrical Characteristics table, Power

Consumption table, Clock Parameters table and the System Interface

Parameters table.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 3

Document ID: PMC-2002240, Issue 2

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

Document Conventions

The following conventions are used in this datasheet:

• All signal, pin, and bus names described in the text, such as ExtRqst*, are in boldface

typeface.

• All bit and field names describe d in the text , such as Interrupt Mask, are in an italic -bold

typeface.

• All instruction names, such as MFHI, are in san serif typeface.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 4

Document ID: PMC-2002240, Issue 2

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

Table of Contents

Legal Information ...........................................................................................................................2

Revision History .............................................................................................................................3

Document Conventions .................................................................................................................4

Table of Contents ..........................................................................................................................5

List of Figures ................................. ...... ....... ...................................... ....... ...... ....... ...... ..................7

List of Tables................................................................... ...... ....... ...... ....... ...... ....... ...... . ...... ...... .... 8

1 Features.................................................................................................................................. 9

2 Block Diagram .......................... ...... ....... ...... ....... ...... ....................................... ...... ....... .........10

3 Hardware Overview ...............................................................................................................11

3.1 Superscalar Dispatch ...................................................................................................11

3.2 CPU Registers .............................................................................................................11

3.3 Integer Unit ..................................................................................................................11

3.4 Pipeline ........................................................................................................................12

3.5 Register File .................................................................................................................12

3.6 ALU ..............................................................................................................................12

3.7 Integer Multiply/Divide ..................................................................................................12

3.8 Floating-Point Co-Processor ........................................................................................13

3.9 Floating-Point Unit .......................................................................................................13

3.10 Floating-Point General Register File ............................................................................15

3.11 System Control Co-processor (CP0) ............................................................................16

3.12 System Control Co-Processor Registers .....................................................................16

3.13 Virtual to Physical Address Mapping ............................................................................17

3.14 Joint TLB ......................................................................................................................18

3.15 Instruction TLB .............................................................................................................18

3.16 Data TLB ......................................................................................................................19

3.17 Cache Memory .............................................................................................................19

3.18 Instruction Cache .........................................................................................................19

3.19 Data Cache ..................................................................................................................19

3.20 Write buffer ..................................................................................................................21

3.21 System Interface ............. ...................................... ....... ...... ....... ...... ....... ......................21

3.22 System Address/Data Bus .... ....................................... ...... ....... ...... ....... ......................22

3.23 System Command Bus ................................................ ...... ....... ...... .............................22

3.24 Handshake Signals ......................................................................................................22

3.25 Non-overlapping System Interface ...............................................................................23

3.26 Enhanced Write Modes ................................................................................................24

3.27 External Requests ........................................................................................................24

3.28 Interrupt Handling ........................................................................................................25

3.29 Standby Mode .... ...... ....... ...................................... ....... ...... ....... ...... .............................25

3.30 JTAG Interface .............................................................................................................25

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 5

Document ID: PMC-202240, Issue 2

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

3.31 Boot-Time Options .......................................................................................................25

3.32 Boot-Time Modes .........................................................................................................26

4 Pin Descriptions ....................................................................................................................27

5 Absolute Maximum Ratings ..................................................................................................30

6 Recommended Operating Conditions ...................................................................................31

7 DC Electrical Characteristics .................................................................................................32

8 Power Consumption ..............................................................................................................33

9 AC Electrical Characteristics .................................... ...... ....... ...... ....................................... .. .34

9.1 Capacitive Load Deration .............................................................................................34

9.2 Clock Parameters ........................................................................................................34

9.3 System Interface Parameters ............. ....... ...... ...... ....... ....................................... ...... ...35

9.4 Boot-Time Interface Parameters ..................................................................................35

10 Timing Diagrams ...................................................................................................................36

10.1 System Interface Timing ....................................... ....... ...... ....... ...... ....... ...... ....... ...... ...36

11 Packaging Information ..........................................................................................................37

12 RM5261A 208 QFP Package Numerical Pinout ...................................................................38

13 RM5261A 208 QFP Package Alphabetical Pinout ................................................................40

14 Ordering Information .............................................................................................................42

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 6

Document ID: PMC-202240, Issue 2

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

List of Figures

Figure 1 Block Diagram .............................................................................................................10

Figure 2 CPU Registers .............................................................................................................11

Figure 3 Pipeline ........................................................................................................................12

Figure 4 CP0 Registers .............................................................................................................16

Figure 5 Kernel Mode Virtual Addressing (32-bit) .....................................................................17

Figure 6 Typical Embedded System Block Diagram ................................................................22

Figure 7 Processor Block Read .................................................................................................23

Figure 8 Processor Block Write .................................................................................................24

Figure 9 Clock Timing ................................................................................................................36

Figure 10 Input Timing ...............................................................................................................36

Figure 11 Output Timing ............................................................................................................36

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 7

Document ID: PMC-2002240, Issue 2

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

List of Tables

Table 1 Integer Multiply/Divide Operations ................................................................................13

Table 2 Floating-Point Instruction Cycles ..................................................................................15

Table 3 Cache Attributes ...........................................................................................................21

Table 4 Boot-Time Mode Bit Stream .........................................................................................26

Table 5 System Interface ...........................................................................................................27

Table 6 Clock/Control Interface .................................................................................................28

Table 7 Interrupt Interface .........................................................................................................28

Table 8 JTAG Interface .............................................................................................................28

Table 9 Initialization Interface ....................................................................................................29

Table 10 Power Supply .............................................................................................................29

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 8

Document ID: PMC-2002240, Issue 2

1 Features

• Dual Issue superscalar microprocessor

• 250, 300, and 350 MHz operating frequencies

• Up to 420 Dhrystone 2.1 MIPS

• High-performance system interface

• 64-bit multiplexed system address/data bus for optimum price/performance

• High-performance write protocols maximize uncached write bandwidth

• Processor clock multipliers 2, 2.5, 3, 3.5, 4, 4.5, 5, 6, 7, 8, 9

• IEEE 1149.1 JTAG boundary scan

• Integrated on-chip caches

• 32 KB instruction and 32 KB data — 2 way set associative

• Per set locking

• Virtually indexed, physically tagged

• Write-back and write-through on a per page basis

• Pipeline restart on first doubleword for data cache misses

• Integrated memory management unit

• Fully associative joint TLB (shared by I and D translations)

• 48 dual entries map 96 pages

• Variable page size (4 KB to 16 MB in 4x increments)

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

• High-performance floating-point unit: up to 700 MFLOPS

• Single cycle repeat rate for commo n single -prec ision ope rati ons and some double-p recision operations

• Two cycle repeat rate for double-precision multiply and double precision combined

multiply-add operations

• Single cycle repeat rate for single-precision combined multiply-add operation

• MIPS IV instruction set

• Floating point multiply-add instruction increases performance in signal processing

and graphics applications

• Conditional moves to reduce branch frequency

• Index address modes (register + register)

• Embedded application enhancements

• Specialized DSP integer Multiply-Accumulate instructions and 3-operand multiply

instruction

• I and D cache locking by set

• Optional dedicated exception vector for interrupts

• Fully static 0.18 micron CMOS design with power down logic

• Standby reduced power mode with WAIT instruction

• 1.65 V or 1.8 V core with 3.3 V or 2.5 V I/O

• 208-pin QFP package

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 9

Document ID: PMC-2002240, Issue 2

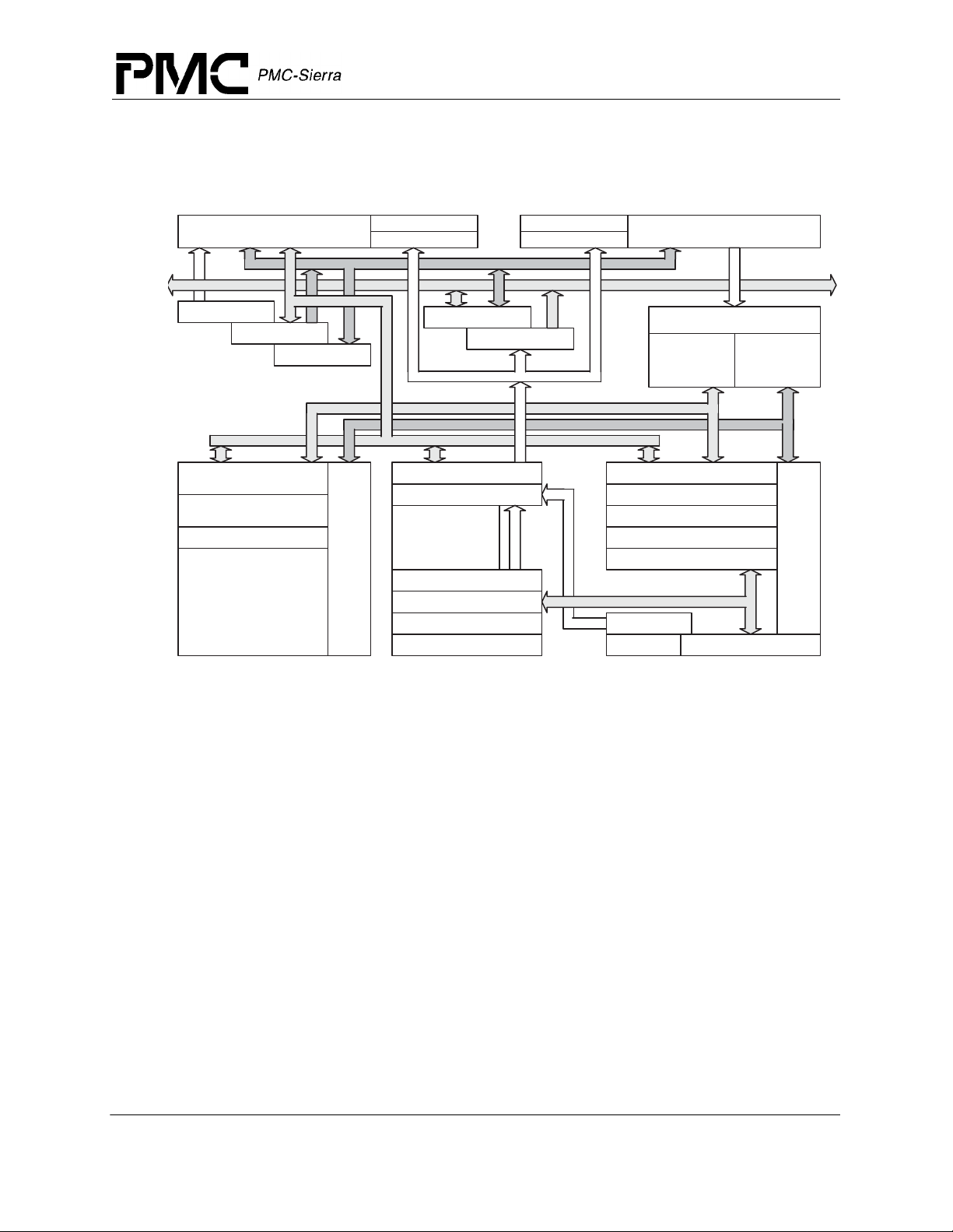

2 Block Diagram

Figure 1 Block Diagram

Primary Data Cache

2-way Set Associative

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

DTag

DTLB

ITag

ITLB

Primary Instruction Cache

2-way Set Associative

A/D Bus

Pad Bus

Store Buffer

Write Buffer

D Bus

Floating-Point

Load/Align

Floating-Point

Register File

Packer/Unpacker

Floating-Point

MultAdd, Add, Sub,

Cvt, Div, Sqrt

Read Buffer

Coprocessor 0

System/Memory

Control

PC Incrementer

Floating-Point Control

Branch PC Adder

ITLB Virtual

Program Counter Int Mult, Div, Madd

Pad Buffer

Joint TLB

Address Buffer

IVA

DVA

FP Bus

FA Bus

Instruction Dispatch Unit

FP

Instruction

Register

Load Aligner

Integer Register File

Integer Address/Adder

Shifter/Store Aligner

Logic Unit

DTLB Virtual

PLL/Clocks

Integer

Instruction

Register

Integer Bus

Integer Control

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 10

Document ID: PMC-2002240, Issue 2

3 Hardware Overview

The RM5261A offers a high-level of integration targeted at high-performance embedded

applications. The key elements of the RM5261A are briefly described below.

3.1 Superscalar Dispatch

The RM5261A has an asymmetric superscalar dispatch unit which allows it to issue an integer

instruction and a floating-point computation instruction simultaneously. Integer instructions

include alu, branch, load/store, and floating-point load/store, while floating-point computation

instructions include fl oat in g-point add, subtract, combined multipl y- add, and convert. In

combination with its high- throug hput fully pipel ined fl oatin g-p oint exe cutio n unit, the supersc alar

capability of the RM5261A provides unparalleled price/perf ormance in computationally intensive

embedded applications.

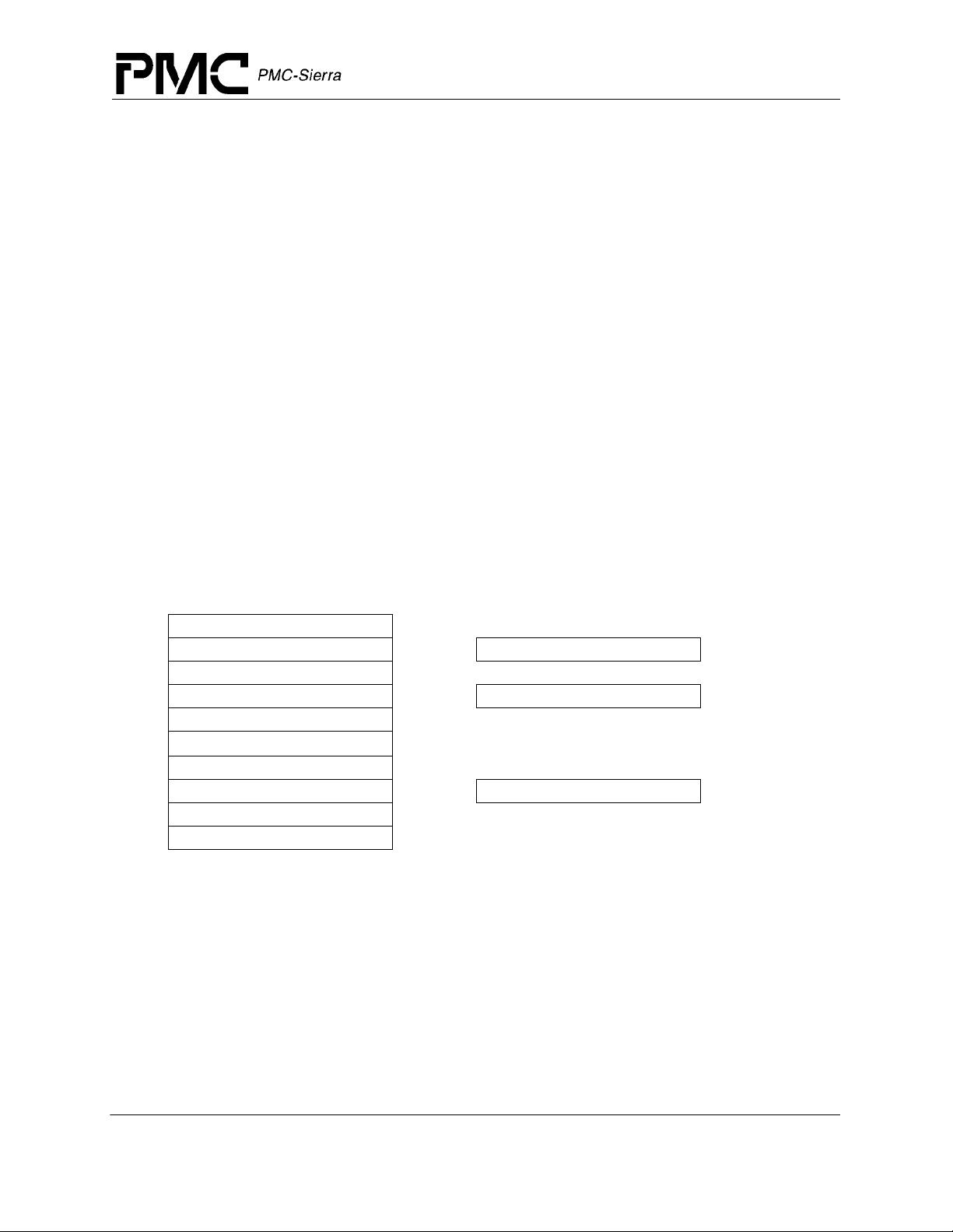

3.2 CPU Registers

The RM5261A CPU contains 32 general purpose registers, two special purpose registers for

integer multiplicati on and division, a program counter, and no condition code bits. Figure 2 shows

the user visible state.

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

Figure 2 CPU Registers

General Purpose Registers

63 0

0 63 0

r1 HI

r2 63 0

•LO

•

•

• 63 0

r29 PC

r30

r31

3.3 Integer Unit

The RM5261A implements t he MIPS IV I nstruct ion Set Ar chitect ure and i s there fore full y upward

compatible with applic ations that run on proce ssors implementing the earlier generation MIPS IIII instruction set s. Add it ion al ly, the RM5261A includes two implementat ion specific instruct io ns

not found in the baseline MIPS IV ISA but that are useful in the embedded market place. These

instructio ns are integer multiply-accumulat e (

Multiply/Divide Registers

Program Counter

MAD) and 3-operand integer multiply (MUL).

The RM5261A integer unit includes thirty-two general purpose 64-bit registers, a load/store

architecture with single cycle ALU operations (add, sub, logical, shift) and an autonomous

multiply/divide unit. Additional register resources include: the HI/LO resul t registers for the twooperand integer multiply/divide operations, and the program counter (PC).

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 11

Document ID: PMC-2002240, Issue 2

3.4 Pipeline

For integer operations, loads, stores, and other non-floating-point operations, the RM5261A

implements a 5-stage integer pipeline. In addi tion to the integer pipeline, the RM5261A

implements an extended 7-stage pipeline for floating-point operations.

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

The RM5261A multiplies th e input

pipeline clock.

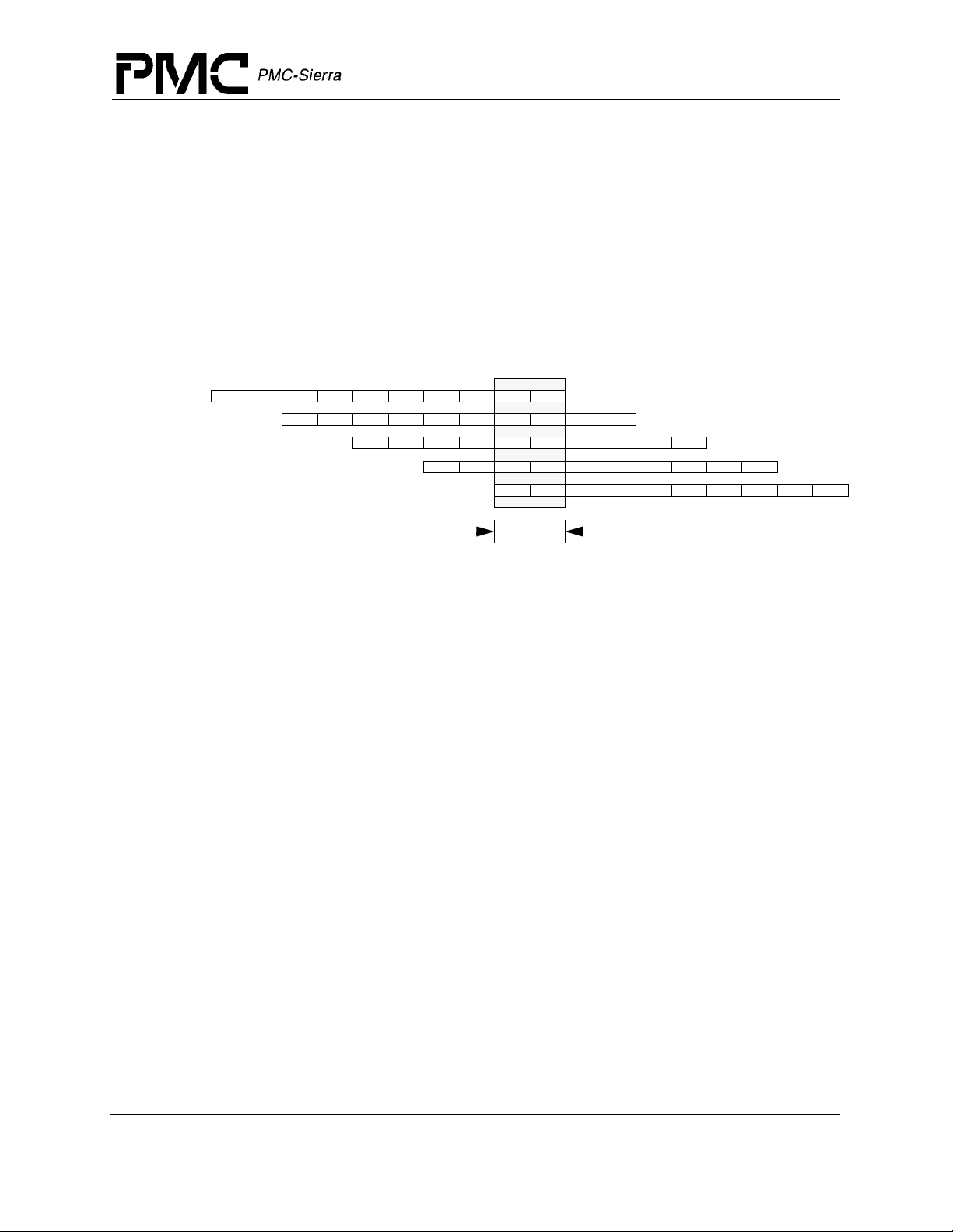

Figure 3 shows the RM5261A integer pipeline. As illustrated in the figure, up to five integer

instructions can be executing simultaneously.

Figure 3 Pipeline

I0

I1

I2

I3

I4

1I-1R:

2I:

2R:

1A:

1A:

1A-2A:

2A:

2A-2D:

1D:

2W:

2I1I 1R 2R 1A 2A 1D 2D 1W 2W

Instruction cache access

Instruction virtual to physical address translation

Register file read, Bypass calculation, Instruction decode, Branch address calculation

Issue or slip decision, Branch decision

Data virtual address calculation

Integer add, logical, shift

Store Align

Data cache access and load align

Data virtual to physical address translation

Register file write

3.5 Register File

SysClock by 2, 2.5, 3, 3.5, 4, 4.5, 5, 6, 7, 8, or 9 to prod uce the

2I1I 1R 2R 1A 2A 1D 2D 1W 2W

2I1I 1R 2R 1A 2A 1D 2D 1W 2W

2I1I 1R 2R 1A 2A 1D 2D 1W 2W

2I1I 1R 2R 1A 2A 1D 2D 1W 2W

one cycle

The RM5261A has thirty-two general purpose registers with register location 0 (r0) hard-wired to

a zero value. These registers are used for scalar integer operations and address calculation. The

register file has two read ports and one write port and is fully bypassed to minimize operation

latency in the pipeline.

3.6 ALU

The RM5261A ALU consists of an integer adder/subtractor, a logic unit, and a shifter. The adder

performs address calculations in addition to arithmetic operations. The logic unit performs all

logical and zero s hift d ata moves . The shift er per forms s hifts and store align ment o perat ions. Eac h

of these units is optimized to perfor m all operations in a sing l e processor cycle.

3.7 Integer Multiply/Divide

The RM5261A has a dedicated i ntege r multi ply/di vide un it opt imized f or hig h-spee d multip ly a nd

multiply-accumulate operations. Table 1 shows the performance of the multiply/divide unit on

each operation.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 12

Document ID: PMC-2002240, Issue 2

RM5261A™ Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

Table 1 Integer Multiply/Divide Operations

Operand

Opcode

MULT/U, MAD/U

MUL 16 bit 3 2 1

DMULT, DMUL TU

DIV, DIVD any 36 36 0 DDIV,

DDIVU

Size Latency

16 bit 3 2 0 32 bit 4 3 0

32 bit 4 3 2 any 7 6 0

any 68 68 0

Repeat

Rate

Stall

Cycles

The baseline MIPS IV ISA specifies that the results of a multiply or divide operation be placed in

the Hi and Lo registers. These values can then be transferred to the general purpose register file

using the Move-from-Hi and Move-from-Lo (

MFHI/MFLO) instructi ons.

In addition to the baseline MIPS IV integer multiply instructions, the RM5261A also implements

the 3-operand multiply instruction,

MUL. This instruction specifies that the multiply result go

directly to the integer register file rather than the Lo register. The portion of the multiply that

would have normally gone i nto the Hi re gister i s discard ed. For applicat ions where i t is known tha t

the upper half of the multiply result is not required, using the

necessity of executing an explicit

MFLO instruction.

MUL instruction eliminates the

The multiply-add instructions,

MAD and MADU, multiply two ope rands and add the resulting

product to the current contents of the Hi and Lo registers. The multip ly-accumulate operat ion is

the core primitive of almost all signal processing algorithms, allowing the RM5261A to eliminate

the need for a separate DSP engine in many embedded applications.

3.8 Floating-Point Co-Processor

The RM5261A incorporate s a hig h-p erfor mance fu lly pi pe lined float ing-p oint c o-proc ess or whic h

includes a floating-po int register file and autonomous execution units for multiply/a dd/convert and

divide/square root. The floating-point coprocessor is a tightly coupled execution unit, decoding

and executing instructions in parallel with, and in the case of floating-point loads and stores, in

cooperation with the integer unit. The superscalar capabilities of the RM5261A allow floatingpoint computation instructions to issue concurrently with integer instructions.

3.9 Floating-Point Unit

The RM5261A floating-point execution unit supports single and double precision arithmetic, as

specified in the IEEE S tanda rd 754. The ex ecution uni t is broken i nto a separa te divide /square ro ot

unit and a pipelined multiply/add unit. Overlap of the divide/square root and multiply/add

operations is supported.

The RM5261A maintains fully precise floating-point exceptions while allowing both overlapped

and pipelined operations. Precise exceptions are extremely important in object-oriented

programming environments and highly desirable for debugging in any environment.

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use 13

Document ID: PMC-2002240, Issue 2

Loading...

Loading...