64-Bit MIPS RISC Microprocessor with 32/64-Bit System Bus

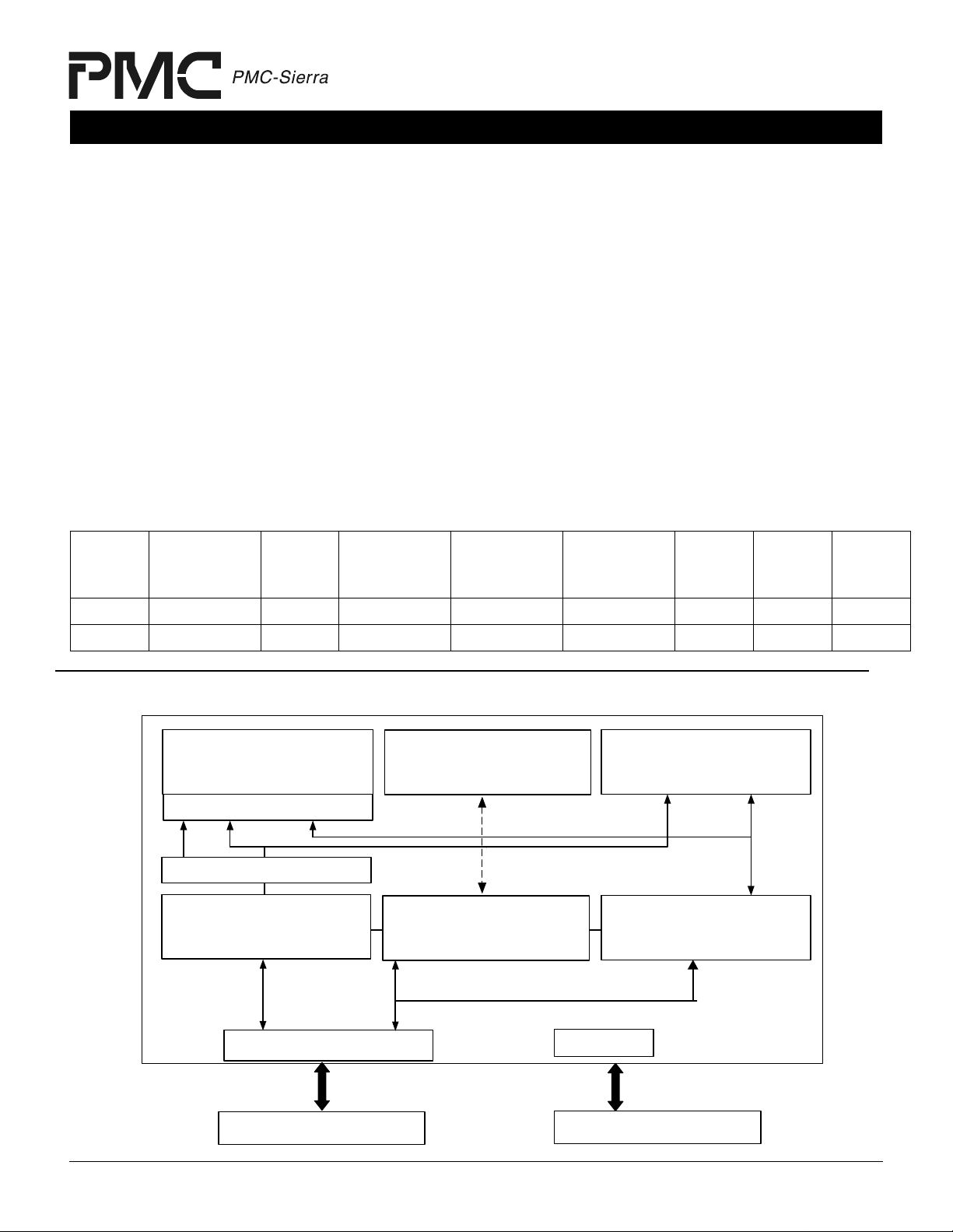

BLOCK DIAGRAM

RM5231A/5261A

FEATURES

• Dual-Issue 64-bit Superscalar

architecture

• High-performance 64-bit integer unit

• High-throughput fully pipelined 64-

bit floating point unit (IEEE754)

• High performance SysAD interface

• 32-bit or 64-bit multiplexed system

address/data bus for optimum

price/performance

• Available with 32-bit or 64-bit

external bus interface

• Supports fractional clock rati os

• IEEE 1149.1 JTAG boundary scan

• Integrated primary caches

• 32KB instruction - 2-way set

associative

• 32KB data - 2-way set associative

• Virtually indexed, physically tagged

• Write-back and write-through on

per-page basis

• Pipeline restart on first double word

for data cache misses

• 64-bit MIPS instruction set architecture

• Floating point multiply-add

instruction increases performance in

signal pro cessing and graphics

applications

• Conditional moves to reduce branc h

frequency

• Index address modes (register +

• Integrated memory management

• Fully associative joint TLB (shared

by I and D transistors)

• 48 dual entries map 96 pages

• Variable page size (4KB to 16MB)

• Embedded application enhancements

• Specialized DSP integer Multiply-

Accumulate instructions

(MAD/MADU) and 3 operand

Multiply instruction (MUL)

• Instruction and Data cache locking

by set

• Optional dedica ted except ion vect or

for interrupts

register)

External Bus

Frequency

(MHz)

VccInt

(V)

VccIO

(V)

Package

Device

CPU

Frequency

(MHz)

I/D

Cache

External

Cache

Support

External Bus

Width

RM5231A 250, 300, 350 32K/32K No 32-bit 100 1.65/1.8 2.5/3.3 128 QFP

RM5261A 250, 300, 350 32K/32K No 64-bit 125 1.65/1.8 2.5/3.3 208 QFP

System Control

PC Unit

64-bit FP Unit

Double / Single

IEEE 754

64-bit Integer unit

Dual-Issue

Superscalar

Integer Multiplier / Accum.

Instr. Dispatch

I-Cache 32KB,

2-way, lockable

Bus Interface Unit

MMU 96 Pages,

(4KB – 16 MB)

Int Ctlr

D-Cache 32KB, 2-

way, lockable

32-bit (5231A)

64-bit (5261A)

SysA / D Bus

PMC- 2010740 (R1) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2000

NMI, INT5 – INT0

64-Bit MIPS RISC Microprocessor with 32/64-Bit System Bus

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

RM5231A/5261A

DEVELOPMENT TOOLS

• Operating Systems:

• Linux by MontaVista and Red Hat

• VxWorks by Wind River Systems

• Nucleus by Accelerated Technology

• Neutrino by QNX Software Systems

• Compiler Suites

• Algorithmics

• Green Hills Software

• Red Hat

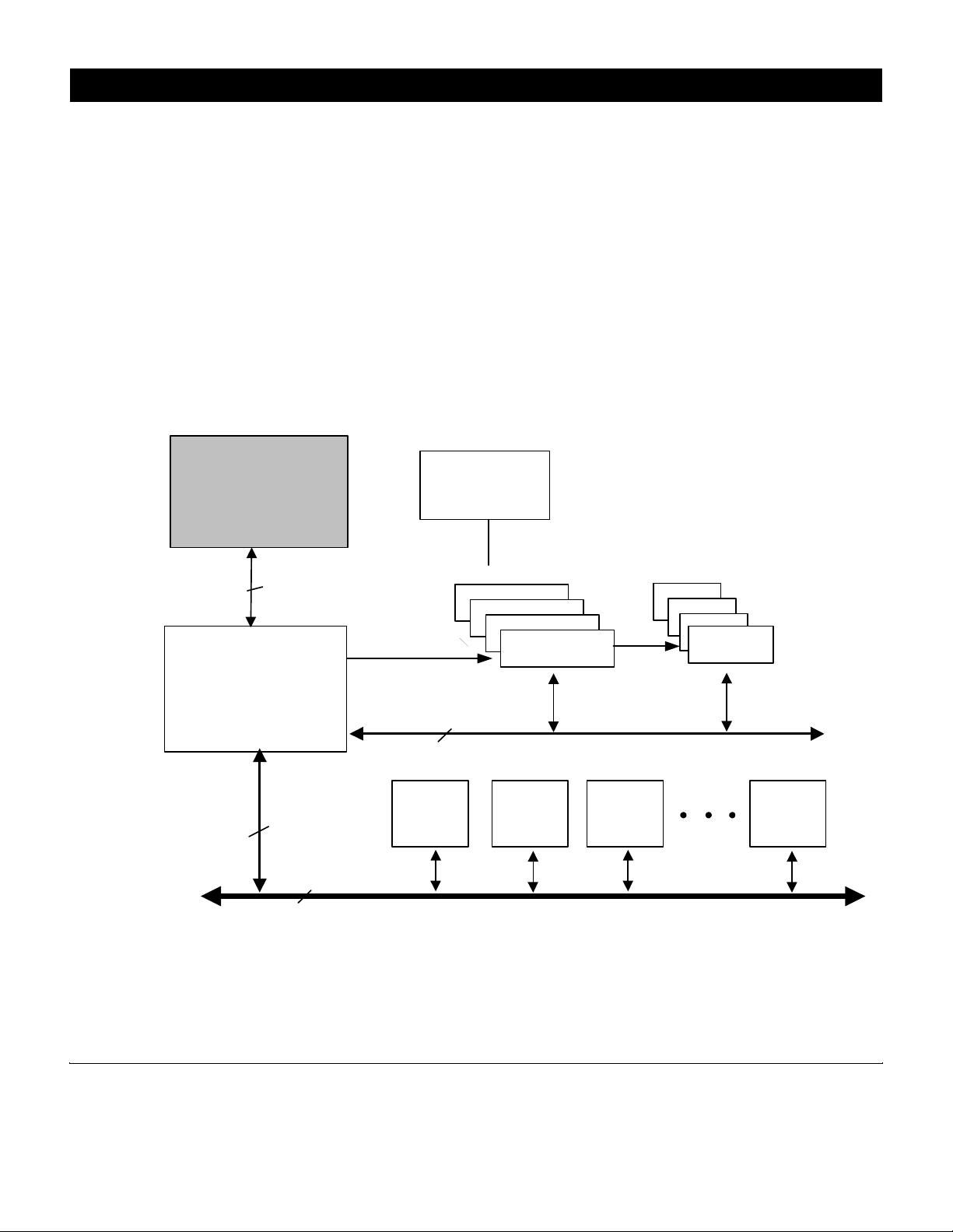

TYPICAL APPLICATION

RM52XX

• Evaluation Boards and Compan ion

Chips

• Algorithmics:

• P-6032 (RM5231A): 32-bit,

33MHz PCI

• P-4052 (RM5231A): 32-bit,

33MHz PCI

• Galileo Technology

• EV-6412 0A: (RM5 261 A): 32/64 -

bit, 33/66MHz PCI

• EV-64115 (RM5231A): 32-bit,

33/66MHz PCI

L3 Cache

(Optional)

• V3 Semiconductor

• V320USC (RM5231A): 32-bit,

50MHz PC

• V340HPC (RM5261A): 64-bit,

66MHz PCI

• Logic Analyzers and Emulation

• HP

• Tektronix

• Corelis

• Crescent Heart Software

SysAD 64/32-bit

Marvell/Galileo

64/32-bit

GT-64120

64/32-bit

Address &

Control

64/32-bit

SCSI Network

64/32-bit

SDRAM

PCI Bus

Data

PCI to

PCI

Bridge

Devices

64/32/16/8-bit

Other

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate informatio n,

send email to:

info@pmc-sierra.com

PMC- 2010740 (R1)

© Copyright PMC-Sierra, Inc. 2001. All

rights reserved. RM5231A/and RM 5261A

are trademarks of PMC-Sierra Inc.

Loading...

Loading...