PMC-Sierra,Inc.

4-Channel 1.0-1.25 Gbps Transceiver

PM8353 QuadPHY™

FEATURES

• Four independent 1.0-1.25 Gbit/s

transceivers

• Four secondary channels to support

channel redundancy

• Ultra low power operation: 1.25 Watt

typical

• Integrated serializ er/dese rializ er, cloc k

synthesis, clock recovery , and 8B/10B

encode/decode logic

• Physical Coding Sublayer (PCS) logic

for Gigabit Ethernet

• Selectable 8-bit , 10-bit, or IEE E 802.3z

GMII parallel interface

• Optional Receive FIFOs which

synchronize incoming data to local

clock domain

• “Trunking” feature to de-skew and

align received parall el data across four

channels

• 100-156 MHz Single Data Rate (SDR)

parallel transmit interface with clock

forwarding

• 100-125 MHz SDR parallel receive

interface

• Extensive control of loopback, BIST,

and operating modes via 802.3

compliant MDC/MDIO serial interface

• Built-in packet gener ator/ ch eck er

• IEEE 1149.1 JTAG testing support

• IEEE 802.3z Gigabit Ethernet and

ANSI X3T11 Fibre Channel support

• High speed outputs which feature

programmable output current to

directly drive dual-terminated line

• 2.5V, 0.25 micron CMOS technology

with 3.3V tolerant I/O

• Direct interface to optical modules,

coax, or serial backplanes

• Small footprint 19x19 mm, 289-pin

PBGA

APPLICATIONS

• High speed serial backplanes

• Gigabit Ethernet links

• Fibre Channel links

• Intra-system interconnect

• ASIC to PMD link

GENERAL DESCRIPTION

The QuadPHYTM is a Quad PHYsical

layer transceiver ideal for systems

requiring large numbers of po int-to-point

gigabit links. It provides four individual

serial channels capable of operation at

up to 1.25 Gbps each, which may be

grouped together to form a single 5.0

Gbps bidirectional link. Each of the four

primary channels has a corresponding

secondary channel that can be enabled

via the MDC/MDIO serial interface.

The QuadPHY includes 8B/10B block

coding logic (compliant with 802.3z

Gigabit Ethernet and Fibre Channel

requirements) which p roduces run length

limited data streams for serial transmission.

A receive FIFO optionally aligns all

incoming parallel data to the local cloc k

domain, adding or removing IDLE

sequences as required. This simplifies

implementation of the upstre am A SIC b y

removing the requirement to deal with

multiple clock domains.

When trunking is e nabled, the Quad PHY

can remove cable skew differences

equivalent to several meters, presenting

4-byte data vectors at the receive

interface exactly as they were transmitted.

EXAMPLE ARCHITECTURE

The first figure on the next page shows

the QuadPHY in a switch application.

This implementation uses four channels

of 1.25 Gbaud per linecard, requiring

only 16 signal pins per linecard and 64

for the switch card, providing up to

16 Gbps total payload capacity to the

switch fabric.

The dotted lines in the figure depict the

system clock domains. Note that even

though the recovered clock from any or

all serial links may be asynchronous to

the local clock, the QuadPHY bridgesthese domains so that the switch fabric

and linecards ma y b e designed in only a

single clock domain .

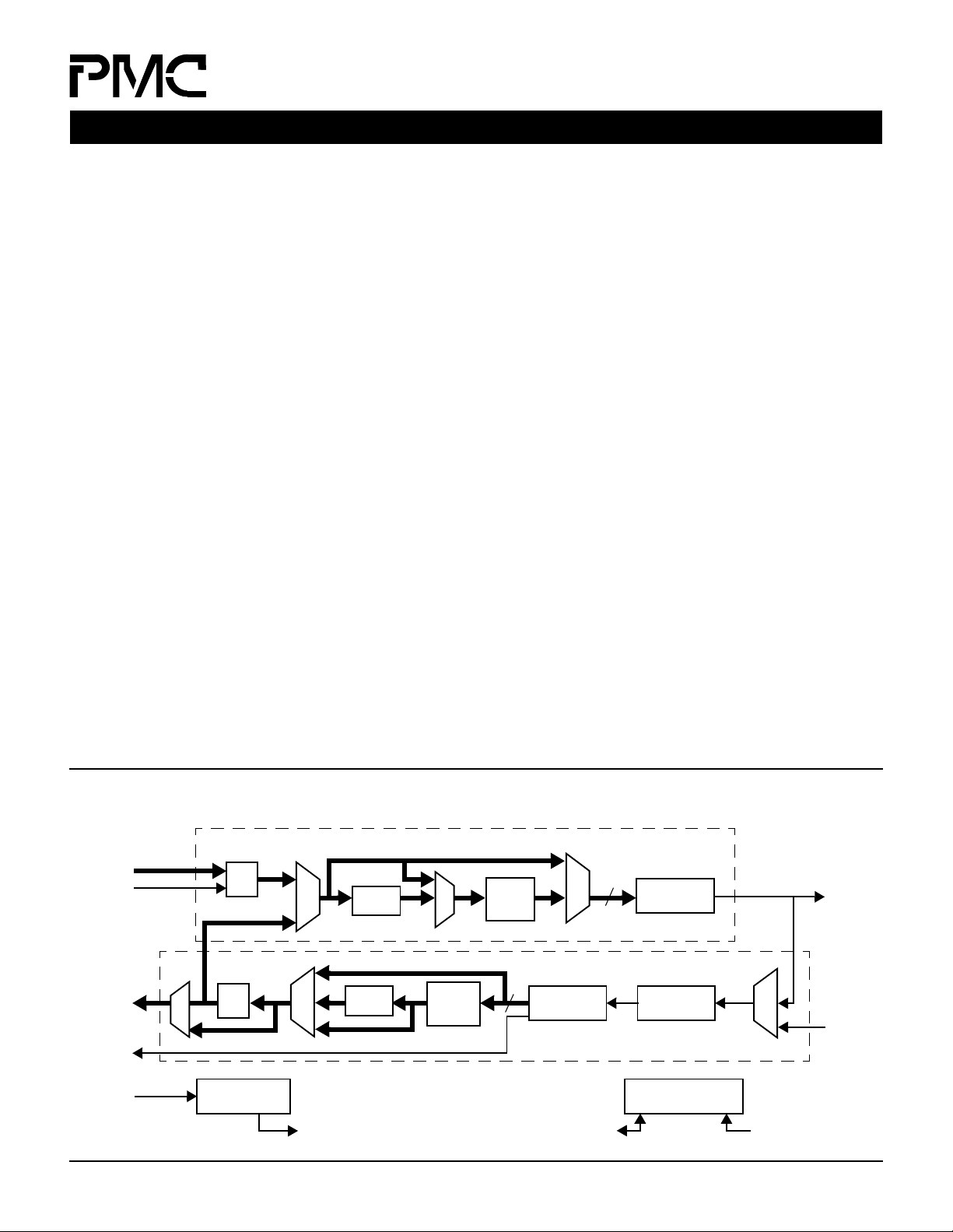

BLOCK DIAGRAM

Transmit Channel A (1 of 4)

Parallel

Data In

TX Byte

Clock

Parallel

Data Out

RX Byte

Clock

REFCLK

PMC-2000673 (R3) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2001

FIFO

FIFO

Clock Synthesizer

PLL LOCK

PCS

Receive Channel A (1 of 4)

PCS

10B/8B

Decoder

8B/10B

Encoder

10

10

Deserialize &

Byte Align

MDC/MDIO

Serial

Management Static Controls

Serializer

Clock

Recovery

Common Control Logic

Serial

Transmit

Data

Serial

Receive

Data

PM8353 QuadPHY™

4-Channel 1.0-1.25 Gbps Transceiver

The QuadPHY creates a highly integrated and cost effective physical layer solution for Gigabit Ethernet or Fibre Channel external

interfaces.

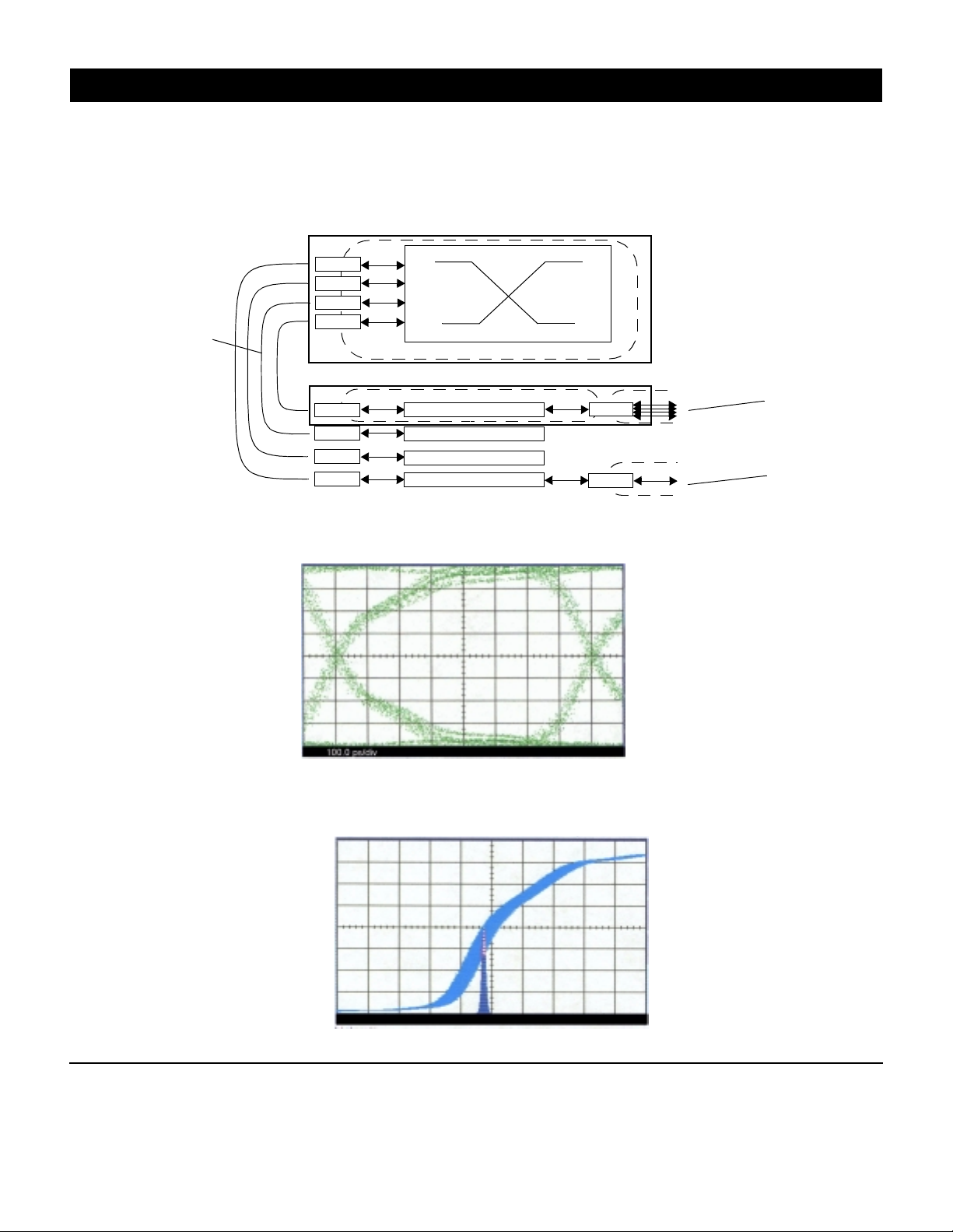

16 GBPS SWITCH APPLICATION

Switch Card

PM8353

PM8353

Serial Point-to-poin t

Backplane: 4Gbps

Per line card

PM8353

PM8353

Switch clock domain

Line Card

PM8353

PM8353

PM8353

PM8353

Line card clock domain

MAC/Packet processor

MAC/Packet processor

MAC/Packet processor

MAC/Packet processor

RX data clock domains

PM8353

Uplink clock domain

PM8353

EYE DIAGRAM

Produced by the QuadPHY when driving a 50 Ohm cable, terminated at both near and far ends.

JITTER

Jitter histogram of the QuadPHY showing 6.8 picoseconds, 1 σ jitter with all channels operating.

Gigabit Ethernet

or Fibre Channel

Interfaces

4 Gbps

(trunked)

uplink

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

100.0 ps/div

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

© Copyrigh t PMC-Sierra,

Inc. 2001. All rights reserved.

SATURN and S/UNI are

registered trademarks of

PMC-Sierra, Inc. POS-PHY

Level 3 is a trademark of

PMC-Sierra, Inc.

Loading...

Loading...