Preliminary

]

]

]

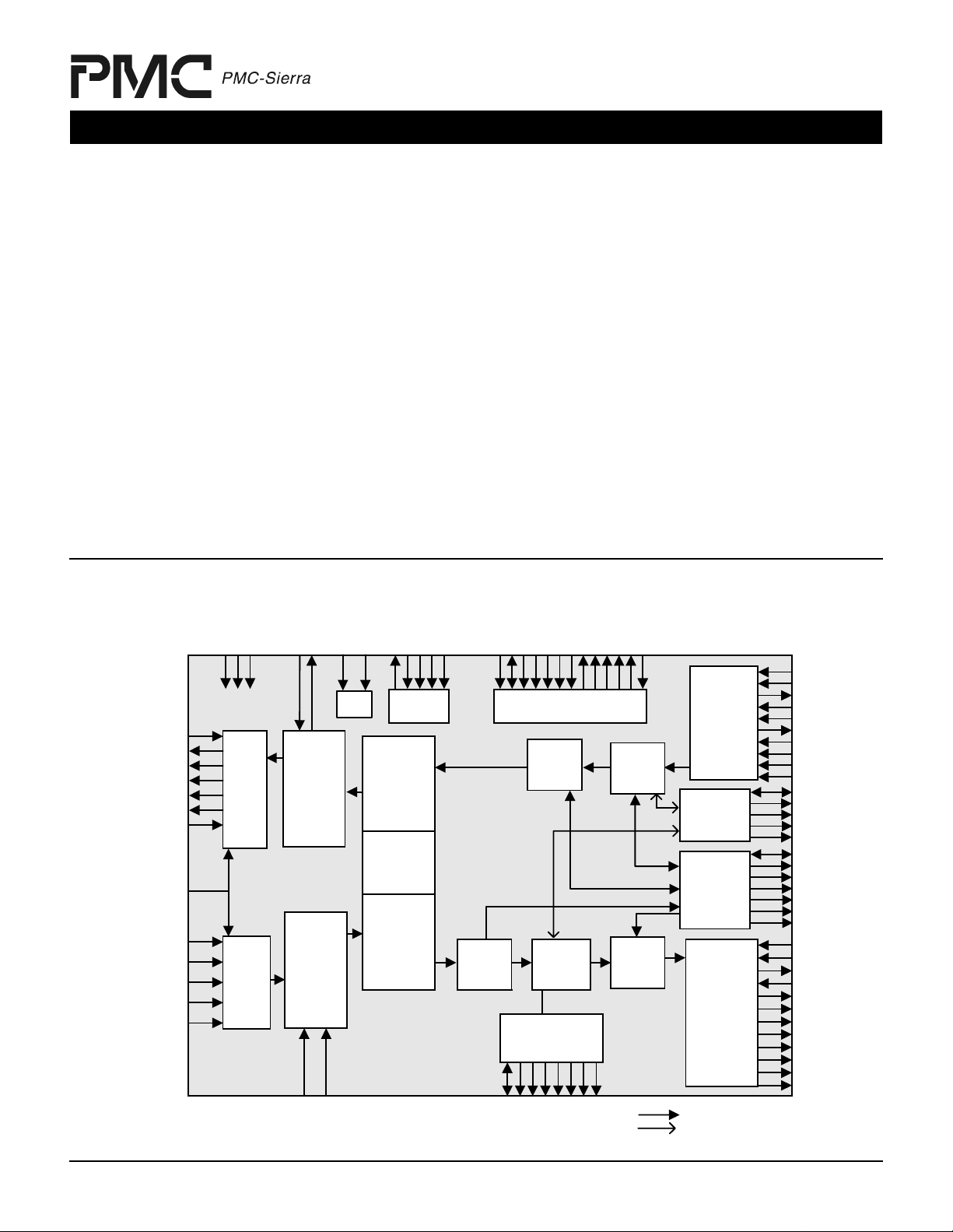

BLOCK DIAGRAM

Frame Engine and Datalink Manager

PM7388

FREEDM 336A1024

FEATURES

• Single-chip multi-channel packet

processor supporting line rate

throughput transfers of packet sizes

from 40 to 9.6 Kbytes, for up to an

aggregate of 336 T1s, 252 E1s, or 12

DS-3s.

• Provides simultaneous support of

PPP, Frame Relay, Multilink-PPP and

Multilink-Frame Relay protocols.

Alternative protocols supported via

HDLC termination an d full pac ket store

of the data within the HDLC structure.

MULTILINK PPP AND FRAME RELAY BUNDLES

• Capable of supporting fragment sizes

from 1 to 9.6 Kbytes.

• Support for 3 egress fragmentation

sizes (128, 256, and 512 bytes)

CIFPOUT

ADATA[7:0]

AJUST_REQ

REFCLK

DDATA[7:0]

ACIFP

ADP

APL

AV5

DDP

DPL

DV5

DC1FP

RSTB

PMCTEST

Insert

SBI

(INSBI-

336)

Extract

SBI

(EXSBI-

336)

configurable on a per multilink bundle.

Optionally full packet transfers are

supported on a per bundle basis.

• Supports up to 168 multilink bundles

with up to 12 member links per bundl e.

These bundles are composed of

independent HDLC channels.

• Support for up to 100 ms of intra

bundle skew in the receive direction

when supporting the minimum.

fragment si ze.

• Support for PPP header compression

as per RFC 1661.

PPP

• Support for 16 COS levels in

accordance with RFC 2686.

• Either 12 bit or 24 bit sequence

number, with short and long fragment

header formats, is supported.

]

0

:

1

1

[

K

L

C

T

TD[11:0]

SYSCLK

DLLTEST

TDO

TMS

TCK

TDI

SCAN_EN

DDLL-

140

Transmit

Channel

Assigner

(TCAS-12)

Receive

Channel

Assigner

(RCAS-12)

Tx HDLC

Processor /

Partial Packet

Buffer

(THDL-12)

Performance

Monitor

(PM-12)

Rx HDLC

Processor /

Partial Packet

Buffer

(RHDL-12)

TRSTB

JTAG

Fragment

(RFRAG)

AD[31:0]

BCLK

ADSB

Microprocessor I/F (BUMP2)

Manager

(EQM-12)

Rx

Builder

RS DRAM

Controller

(RS_DRAMC)

BURSTB

CSB

WR

Egress

Queue

Frame

Builder

(FRMBLD)

BLAST

• Link Control protocol packets are

identified by the PID as control

protocols and will be forwarded to the

Any-PHY interface.

FRAME RELAY

• Link layer address lookup can be

performed based on HDLC channel

and 10 bit DLCI for HDLC channels

supporting Frame Relay protocols.

• The lookup algorithm can support a

maximum of 16 K c onnection

identifiers (CIs) amongst multilink FR

bundles. The connection identifiers

are ignored in singlelink FR channels.

• Control frames are identified and

forwarded to Any-PHY interface.

• 12 bit sequence numbers supported.

• FECN, BECN, and DE ingress

processing as per FRF.12.

READYB

BTERMB

WRDONEB

INTHIB

Tx

Fragment

Builder

(TFRAG)

Ingress

Queue

Manager

(EQM-12)

INTLOB

BUSPOL

Tx ANY-PHY

I/F (TAPI-12)

SRAM

Controller

(SRAMC)

CB DRAM

Controller

(CB_DRAMC)

Rx ANY-PHY

I/F

(RAPI-12)

TXCLK

TXADDR[15:0

TPA

TXDATA[15:0]

TXPRTY

TRDY

TSX

TEOP

TMOD

TERR

CCDAT[35:0]

CCADD[17:0]

CCWEB

CCSELB

CCBSELB[1:0

CBDAT[47:0]

CBADD[12:0]

CBWEB

CBCSB

CBRASB

CBCASB

CBBS[1:0]

RXCLK

RXADDR[3:0]

RPA

RENB

RXDATA[15:0

RXPRTY

RVAL

RSX

RSOP

REOP

RMOD

RERR

Data

Control

RSRASB

RSCASB

DQM

RSBS[1:0]

RSCSB

RD[11:0]

RCLK[11:0]

PMC-1991475 (p2) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE Copyright PMC-Sierra, Inc. 2001

RSWEB

RSDAT[31:0]

RSADD[12:0]

Preliminary PM7388 FREEDM 336A1024

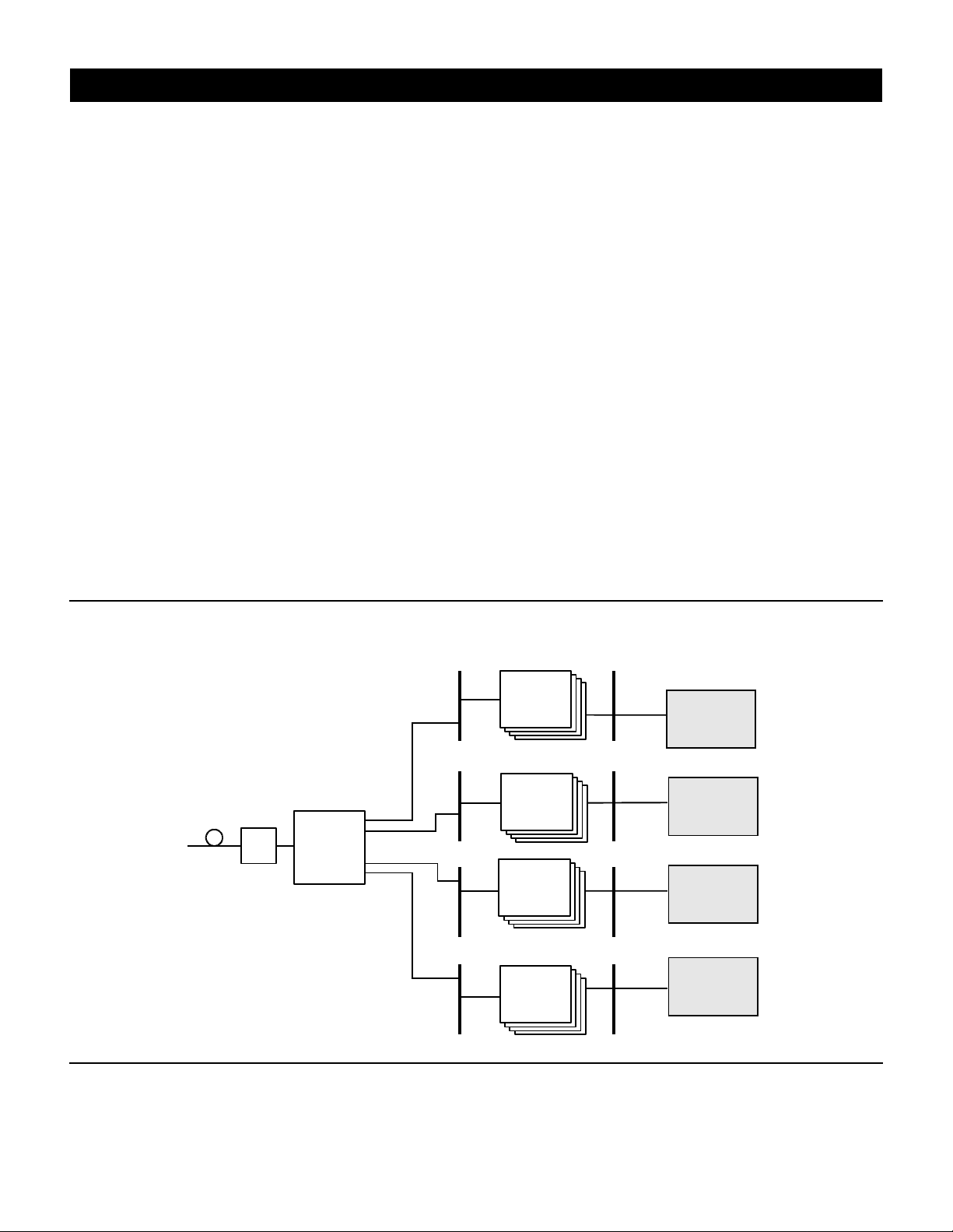

TYPICAL APPLICATION

O

Frame Engine and Datalink Manager

HDLC

• Support for up to 1024 bidirectional

HDLC channels, with individual HDLC

channel speeds ranging from 56 Kbps

to 52 Mbps. In a channelized

application, the number of time-slots

assigned to an HDLC channel is

programmable from 1 to 24 (for T1/J1)

and from 1 to 31 (for E1).

• The 1024 HDLC channels can be

assigned to a mixture of physical links

via the 77 MHz SBI interface. The SBI

transports the equivalent of 12 STS-1

synchronous payload envelopes

(SPE). Each STS-1 SPE can be

individually configured to carry 28

T1/J1s, 21 E1s or 1 DS3.

• For each channel, supports

programmable flag se quence detection

and generation, bit stuffing and destuffing, and validation and generation

of either CRC-CCITT or CRC-32 frame

check sequences.

• For each channel, the receiver checks

for packet abort sequences, octet

aligned packet l ength and fo r minimu m

and maximum packet length.

INTERFACES

• 104 MHz, 8 bit Any-PHY Level 3 or 52

MHz Any-PHY Level 2 packet interface

for transfer of packet, frame or

fragment data using an external

controller. The interface is capable of

supporting full datagram transfer on a

per Any-PHY channel basis, or

fragmented packets or frames on a per

Any-PHY channel basis.

• A 77 MHz SBI bus supporting up to

336 links.

• 12 separate clock and data interfaces

to support 12 links of arbitrary data rate

up to 52 MHz (eg, DS3/E3). The

device can be configured to process

data from either the clock and data

interfaces or from the SBI on a per

clock-data-link/SPE basis.

• A 100 MHz, 48-bit SDRAM interface

for ingress and egress per

packet/fragment storage.

• A 100 MHz, 32-bit SDRAM interface

for ingress re-sequencing data.

structures.

• A 100 MHz, 36-bit SSRAM interface

for Ingress/Egress Context storage.

• Provides a standard 5 signal P1149.1

JTAG test por t for boundary scan.

• A 32-bit microprocessor interface for

configuration and status monitoring.

TECHNOLOGIES

• 40 mm x 40 mm, 520 pin (1.27 mm

pitch) enhanced ball grid array (SBG A)

package.

• Low power 0.18 mm CMOS

technology using 1.8 V c ore power and

3.3 V I/O.

APPLICATIONS

• IETF PPP interfaces for routers.

• Frame Relay interfaces for ATM or

Frame Relay switch es and

multiplexers.

• Internet/Intranet access equ ipm en t.

C-48 PORT CARD SOLUTION

OC-48

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

TelecomBus

PM8316

TEMUX-84

PM8316

TEMUX-84

SER

DES

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5315

SPECTRA-

2488

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PM8316

TEMUX-84

PM8316

TEMUX-84

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

SBI

PM7388

FREEDM336A1024

PM7388

FREEDM336A1024

PM7388

FREEDM336A1024

PM7388

FREEDM336A1024

PMC-1991475 (p2)

Copyright PMC-Sierra, Inc. 2001.

All rights reserved. August 2001.

Any-PHY, SPECTRA-2488, TEMUX-

84, FREEDM-336A1024,SBI, and

PMC-Sierra are trademarks of

PMC-Sierra, Inc.

Loading...

Loading...