DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

PM7381

FREEDM™-32A672

FRAME ENGINE AND DATALINK

MANAGER 32A672

DATA SHEET

PROPRIETARY AND CONFIDENTIAL

ISSUE 6: AUGUST 2001

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

PUBLIC REVISION HISTORY

Issue No. Issue Date Details of Change

Issue 1 February 20, 2000 Created Document.

Issue 2 May 30, 1999 Added pinout.

Issue 3 January, 2000 Minor changes.

Issue 4 June 2000 Minor corrections and changes to some DC and AC

timing parameters.

Issue 5 October 2000 Re-issue for Minor corrections to Mechanical Drawing

and Design Summary sections. Because the changes

are so few, change bars have been kept to show both

Issue 4 and Issue 5 changes.

Issue 6 August 2001 Patent information included in legal footer. Change bars

reflect Issue 5.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE i

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS........................................................................................4

3 REFERENCES .........................................................................................5

4 BLOCK DIAGRAM....................................................................................6

5 DESCRIPTION .........................................................................................7

6 PIN DIAGRAM ........................................................................................ 11

7 PIN DESCRIPTION ................................................................................12

8 FUNCTIONAL DESCRIPTION................................................................43

8.1 HIGH SPEED MULTI-VENDOR INTEGRATION PROTOCOL

(H-MVIP) ......................................................................................43

8.2 HIGH-LEVEL DATA LINK CONTROL (HDLC) PROTOCOL.........43

8.3 RECEIVE CHANNEL ASSIGNER ................................................44

8.3.1 Line Interface Translator (LIT) .......................................46

8.3.2 Line Interface.................................................................47

8.3.3 Priority Encoder .............................................................47

8.3.4 Channel Assigner ..........................................................48

8.3.5 Loopback Controller.......................................................48

8.4 RECEIVE HDLC PROCESSOR / PARTIAL PACKET BUFFER ...48

8.4.1 HDLC Processor............................................................49

8.4.2 Partial Packet Buffer Processor.....................................49

8.5 RECEIVE ANY-PHY INTERFACE................................................51

8.5.1 FIFO Storage and Control..............................................52

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ii

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

8.5.2 Polling Control and Management...................................53

8.6 TRANSMIT ANY-PHY INTERFACE .............................................53

8.6.1 FIFO Storage and Control..............................................53

8.6.2 Polling Control and Management...................................55

8.7 TRANSMIT HDLC CONTROLLER / PARTIAL PACKET BUFFER56

8.7.1 Transmit HDLC Processor .............................................56

8.7.2 Transmit Partial Packet Buffer Processor ......................57

8.8 TRANSMIT CHANNEL ASSIGNER..............................................59

8.8.1 Line Interface Translator (LIT) .......................................61

8.8.2 Line Interface .................................................................61

8.8.3 Priority Encoder .............................................................62

8.8.4 Channel Assigner ..........................................................62

8.9 PERFORMANCE MONITOR .......................................................63

8.10 JTAG TEST ACCESS PORT INTERFACE...................................63

8.11 MICROPROCESSOR INTERFACE .............................................63

9 NORMAL MODE REGISTER DESCRIPTION ........................................66

9.1 MICROPROCESSOR ACCESSIBLE REGISTERS .....................66

10 TEST FEATURES DESCRIPTION .......................................................155

10.1 TEST MODE REGISTERS.........................................................155

10.2 JTAG TEST PORT .....................................................................156

10.2.1 Identification Register ..................................................157

10.2.2 Boundary Scan Register..............................................157

11 OPERATIONS.......................................................................................175

11.1 TOCTL CONNECTIONS............................................................175

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iii

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

11.2 JTAG SUPPORT........................................................................175

12 FUNCTIONAL TIMING..........................................................................182

12.1 RECEIVE H-MVIP LINK TIMING ...............................................182

12.2 TRANSMIT H-MVIP LINK TIMING.............................................183

12.3 RECEIVE NON H-MVIP LINK TIMING.......................................184

12.4 TRANSMIT NON H-MVIP LINK TIMING....................................186

12.5 RECEIVE APPI TIMING.............................................................187

12.6 TRANSMIT APPI TIMING ..........................................................191

12.7 BERT INTERFACE.....................................................................194

13 ABSOLUTE MAXIMUM RATINGS........................................................196

14 D.C. CHARACTERISTICS....................................................................197

15 FREEDM-32A672 TIMING CHARACTERISTICS.................................199

16 ORDERING AND THERMAL INFORMATION ......................................213

17 MECHANICAL INFORMATION.............................................................214

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iv

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

LIST OF FIGURES

FIGURE 1 – H-MVIP PROTOCOL.....................................................................43

FIGURE 2 – HDLC FRAME...............................................................................44

FIGURE 3 – CRC GENERATOR.......................................................................44

FIGURE 4 – PARTIAL PACKET BUFFER STRUCTURE ..................................50

FIGURE 5 – PARTIAL PACKET BUFFER STRUCTURE ..................................57

FIGURE 6 – INPUT OBSERVATION CELL (IN_CELL) ...................................171

FIGURE 7 – OUTPUT CELL (OUT_CELL)......................................................172

FIGURE 8 – BI-DIRECTIONAL CELL (IO_CELL)............................................173

FIGURE 9 – LAYOUT OF OUTPUT ENABLE AND BI-DIRECTIONAL CELLS174

FIGURE 10 – BOUNDARY SCAN ARCHITECTURE ......................................176

FIGURE 11 – TAP CONTROLLER FINITE STATE MACHINE.........................178

FIGURE 12 – RECEIVE 8.192 MBPS H-MVIP LINK TIMING .........................182

FIGURE 13 – RECEIVE 2.048 MBPS H-MVIP LINK TIMING .........................183

FIGURE 14 – TRANSMIT 8.192 MBPS H-MVIP LINK TIMING.......................183

FIGURE 15 – TRANSMIT 2.048 MBPS H-MVIP LINK TIMING.......................184

FIGURE 16 – UNCHANNELISED RECEIVE LINK TIMING ............................185

FIGURE 17 – CHANNELISED T1/J1 RECEIVE LINK TIMING........................185

FIGURE 18 – CHANNELISED E1 RECEIVE LINK TIMING ............................186

FIGURE 19 – UNCHANNELISED TRANSMIT LINK TIMING..........................186

FIGURE 20 – CHANNELISED T1/J1 TRANSMIT LINK TIMING .....................187

FIGURE 21 – CHANNELISED E1 TRANSMIT LINK TIMING..........................187

FIGURE 22 – RECEIVE APPI TIMING (NORMAL TRANSFER) .....................188

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE v

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

FIGURE 23 – RECEIVE APPI TIMING (AUTO DESELECTION) ....................189

FIGURE 24 – RECEIVE APPI TIMING (OPTIMAL RESELECTION)...............190

FIGURE 25 – RECEIVE APPI TIMING (BOUNDARY CONDITION) ...............191

FIGURE 26 – TRANSMIT APPI TIMING (NORMAL TRANSFER)...................192

FIGURE 27 – TRANSMIT APPI TIMING (SPECIAL CONDITIONS)................193

FIGURE 28 – TRANSMIT APPI TIMING (POLLING).......................................194

FIGURE 29 – RECEIVE BERT PORT TIMING................................................195

FIGURE 30 – TRANSMIT BERT PORT TIMING .............................................195

FIGURE 31 – RECEIVE DATA & FRAME PULSE TIMING (2.048 MBPS H-MVIP

MODE) ..................................................................................................201

FIGURE 32 – RECEIVE DATA & FRAME PULSE TIMING (8.192 MBPS H-MVIP

MODE) ..................................................................................................201

FIGURE 33 – RECEIVE DATA TIMING (NON H-MVIP MODE).......................202

FIGURE 34 – BERT INPUT TIMING ...............................................................202

FIGURE 35 – TRANSMIT DATA & FRAME PULSE TIMING (2.048 MBPS H-

MVIP MODE) ........................................................................................204

FIGURE 36 – TRANSMIT DATA & FRAME PULSE TIMING (8.192 MBPS H-

MVIP MODE) ........................................................................................205

FIGURE 37 – TRANSMIT DATA TIMING (NON H-MVIP MODE) ....................205

FIGURE 38 – BERT OUTPUT TIMING ...........................................................206

FIGURE 39 – RECEIVE ANY-PHY PACKET INTERFACE TIMING.................207

FIGURE 40 – TRANSMIT ANY-PHY PACKET INTERFACE TIMING ..............208

FIGURE 41 – MICROPROCESSOR READ ACCESS TIMING .......................209

FIGURE 42 – MICROPROCESSOR WRITE ACCESS TIMING...................... 211

FIGURE 43 – JTAG PORT INTERFACE TIMING............................................212

FIGURE 44 – 329 PIN PLASTIC BALL GRID ARRAY (PBGA)........................214

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vi

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

LIST OF TABLES

TABLE 1 – LINE SIDE INTERFACE SIGNALS (154) ........................................12

TABLE 2 – ANY-PHY PACKET INTERFACE SIGNALS (70) .............................22

TABLE 3 – MICROPROCESSOR INTERFACE SIGNALS (31).........................34

TABLE 4 – MISCELLANEOUS INTERFACE SIGNALS (9) ...............................36

TABLE 5 – PRODUCTION TEST INTERFACE SIGNALS (0 - MULTIPLEXED)38

TABLE 6 – POWER AND GROUND SIGNALS (65)..........................................39

TABLE 7 – TRANSMIT POLLING......................................................................55

TABLE 8 – NORMAL MODE MICROPROCESSOR ACCESSIBLE REGISTERS

................................................................................................................63

TABLE 9 – RECEIVE LINKS #0 TO #2 CONFIGURATION...............................98

TABLE 10 – RECEIVE LINKS #3 TO #31 CONFIGURATION...........................99

TABLE 11 – CRC[1:0] SETTINGS ...................................................................106

TABLE 12 – CRC[1:0] SETTINGS................................................................... 117

TABLE 13 – FLAG[2:0] SETTINGS .................................................................122

TABLE 14 – LEVEL[3:0]/TRANS SETTINGS ..................................................124

TABLE 15 – TRANSMIT LINKS #0 TO #2 CONFIGURATION ........................139

TABLE 16 – TRANSMIT LINKS #3 TO #31 CONFIGURATION.......................140

TABLE 17 – TEST MODE REGISTER MEMORY MAP...................................156

TABLE 18 – INSTRUCTION REGISTER.........................................................157

TABLE 19 – BOUNDARY SCAN CHAIN .........................................................157

TABLE 20 – FREEDM–TOCTL CONNECTIONS ............................................175

TABLE 21 – FREEDM-32A672 ABSOLUTE MAXIMUM RATINGS .................196

TABLE 22 – FREEDM-32A672 D.C. CHARACTERISTICS.............................197

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vii

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

TABLE 23 – FREEDM-32A672 LINK INPUT (FIGURE 31 TO FIGURE 34) ....199

TABLE 24 – FREEDM-32A672 LINK OUTPUT (FIGURE 35 TO FIGURE 38) 202

TABLE 25 – ANY-PHY PACKET INTERFACE (FIGURE 39 TO FIGURE 40)..206

TABLE 26 – MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 41)

..............................................................................................................208

TABLE 27 – MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 42)

..............................................................................................................210

TABLE 28 – JTAG PORT INTERFACE (FIGURE 43)...................................... 211

TABLE 29 – FREEDM-32A672 ORDERING INFORMATION..........................213

TABLE 30 – FREEDM-32A672 THERMAL INFORMATION ............................213

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE viii

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

1 FEATURES

· Single-chip multi-channel HDLC controller with a 50 MHz, 16 bit “Any-PHY”

Packet Interface (APPI) for transfer of packet data using an external

controller.

· Supports up to 672 bi-directional HDLC channels assigned to a maximum of

32 H-MVIP digital telephony buses at 2.048 Mbps per link. The links are

grouped into 4 logical groups of 8 links. A common clock and a type 0 frame

pulse is shared among links in each logical group. The number of time-slots

assigned to an HDLC channel is programmable from 1 to 32.

· Supports up to 672 bi-directional HDLC channels assigned to a maximum of 8

H-MVIP digital telephony buses at 8.192 Mbps per link. The links share a

common clock and a type 0 frame pulse. The number of time-slots assigned

to an HDLC channel is programmable from 1 to 128.

· Supports up to 672 bi-directional HDLC channels assigned to a maximum of

32 channelised T1/J1 or E1 links. The number of time-slots assigned to an

HDLC channel is programmable from 1 to 24 (for T1/J1) and from 1 to 31 (for

E1).

· Supports up to 32 bi-directional HDLC channels each assigned to an

unchannelised arbitrary rate link, subject to a maximum aggregate link clock

rate of 64 MHz in each direction. Channels assigned to links 0 to 2 support a

clock rate of up to 51.84 MHz. Channels assigned to links 3 to 31 support a

clock rate of up to 10 MHz.

· Supports three bi-directional HDLC channels each assigned to an

unchannelised arbitrary rate link of up to 51.84 MHz when SYSCLK is running

at 45 MHz.

· Supports a mix of up to 32 channelised, unchannelised and H-MVIP links,

subject to the constraint of a maximum of 672 channels and a maximum

aggregate link clock rate of 64 MHz in each direction.

· Links configured for channelised T1/J1/E1 or unchannelised operation

support the gapped-clock method for determining time-slots which is

backwards compatible with the FREEDM-8 and FREEDM-32 devices.

· For each channel, the HDLC receiver supports programmable flag sequence

detection, bit de-stuffing and frame check sequence validation. The receiver

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 1

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

supports the validation of both CRC-CCITT and CRC-32 frame check

sequences.

· For each channel, the receiver checks for packet abort sequences, octet

aligned packet length and for minimum and maximum packet length. The

receiver supports filtering of packets that are larger than a user specified

maximum value.

· Alternatively, for each channel, the receiver supports a transparent mode

where each octet is transferred transparently on the receive APPI. For

channelised links, the octets are aligned with the receive time-slots.

· For each channel, time-slots are selectable to be in 56 kbits/s format or 64

kbits/s clear channel format.

· For each channel, the HDLC transmitter supports programmable flag

sequence generation, bit stuffing and frame check sequence generation. The

transmitter supports the generation of both CRC-CCITT and CRC-32 frame

check sequences. The transmitter also aborts packets under the direction of

the external controller or automatically when the channel underflows.

· Alternatively, for each channel, the transmitter supports a transparent mode

where each octet is inserted transparently from the transmit APPI. For

channelised links, the octets are aligned with the transmit time-slots.

· Supports per-channel configurable APPI burst sizes of up to 256 bytes for

transfers of packet data.

· Provides 32 Kbytes of on-chip memory for partial packet buffering in both the

transmit and the receive directions. This memory may be configured to

support a variety of different channel configurations from a single channel with

32 Kbytes of buffering to 672 channels, each with a minimum of 48 bytes of

buffering.

· Provides a 16 bit microprocessor interface for configuration and status

monitoring.

· Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

test purposes.

· Supports 5 Volt tolerant I/O (except APPI).

· Low power 2.5 Volt 0.25 mm CMOS technology.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 2

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

· 329 pin plastic ball grid array (PBGA) package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 3

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

2 APPLICATIONS

· IETF PPP interfaces for routers

· TDM switches

· Frame Relay interfaces for ATM or Frame Relay switches and multiplexors

· FUNI or Frame Relay service inter-working interfaces for ATM switches and

multiplexors.

· Internet/Intranet access equipment.

· Packet-based DSLAM equipment.

· Packet over SONET.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 4

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

3 REFERENCES

1. International Organization for Standardization, ISO Standard 3309-1993,

"Information Technology - Telecommunications and information exchange between

systems - High-level data link control (HDLC) procedures - Frame structure",

December 1993.

2. RFC-1662 – “PPP in HDLC-like Framing" Internet Engineering Task Force, July

1994.

3. GO-MVIP, “MVIP-90 Standard”, October 1994, release 1.1.

4. GO-MVIP, “H-MVIP Standard”, January 1997, release 1.1a.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 5

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

4 BLOCK DIAGRAM

]

0

:

2

[

R

D

K

L

D

C

A

X

X

R

R

]

0

:

5

1

[

Y

A

T

T

B

A

N

A

D

X

E

P

R

R

R

Y

t

e

v

e

H

i

k

P

e

c

-

c

y

a

e

n

P

R

A

D

P

R

P

X

X

S

R

R

e

c

a

f

r

e

t

n

I

R

L

O

A

R

O

E

R

)

2

7

6

I

P

A

R

(

V

E

M

R

R

R

]

0

:

2

1

]

[

0

R

:

2

D

K

[

L

1

D

C

A

A

X

X

P

T

T

T

]

0

:

5

1

]

[

0

:

2

[

2

A

P

T

Y

A

T

T

Y

A

R

D

P

D

X

X

R

T

T

T

t

i

Y

t

e

H

m

k

s

P

c

-

n

y

a

a

r

n

P

T

A

D

P

R

O

X

O

S

T

e

c

a

f

r

e

t

n

I

R

M

E

E

T

T

T

)

2

7

6

I

P

A

T

(

SYSCLK

RSTB

PMCTEST

RBCLK

RBD

t

r

/

r

o

r

s

s

e

f

f

e

c

u

o

B

r

t

P

e

k

C

c

L

a

D

P

H

l

a

e

i

t

v

r

i

a

e

c

P

e

R

l

e

e

v

n

i

n

e

c

a

e

h

R

C

]

]

]

0

:

1

3

[

D

R

]

0

0

0

:

:

:

1

3

3

[

[

3

[

B

K

K

P

C

L

F

V

C

R

M

R

R

r

o

t

i

n

o

)

2

7

6

L

D

H

R

(

r

e

n

g

i

s

s

A

C

D

8

V

M

R

)

M

N

e

c

O

n

M

a

P

(

m

r

o

f

r

e

P

)

2

7

6

S

A

C

R

(

B

C

8

P

P

F

F

8

V

R

M

R

/

r

o

s

r

s

e

f

e

f

c

u

o

)

B

r

2

t

P

7

e

6

k

C

L

c

L

a

D

D

P

H

H

l

T

t

(

a

i

i

t

r

m

a

s

n

P

a

r

T

)

l

t

r

i

m

s

n

a

r

T

]

]

0

0

:

:

1

1

3

3

[

[

K

D

L

T

C

T

2

e

e

7

n

n

6

n

g

S

i

a

s

A

h

s

C

C

A

T

(

]

]

0

0

:

:

3

3

[

[

K

B

P

C

F

V

T

M

T

B

C

C

8

P

D

P

F

8

F

8

V

T

V

M

M

T

T

o

P

G

A

T

J

r

o

s

s

e

e

c

c

a

f

o

r

r

e

p

t

o

n

r

I

c

i

M

TDO

TDI

TCK

TMS

TRS TB

INTB

RDB

WRB

CSB

ALE

A[11:2]

D[15:0]

TBC LK

TBD

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 6

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

5 DESCRIPTION

The PM7381 FREEDM-32A672 Frame Engine and Datalink Manager device is a

monolithic integrated circuit that implements HDLC processing for a maximum of

672 bi-directional channels.

The FREEDM-32A672 may be configured to support H-MVIP, channelised

T1/J1/E1 or unchannelised traffic across 32 physical links.

The FREEDM-32A672 may be configured to interface with H-MVIP digital

telephony buses at 2.048 Mbps. For 2.048 Mbps H-MVIP links, the FREEDM32A672 allows up to 672 bi-directional HDLC channels to be assigned to

individual time-slots within a maximum of 32 H-MVIP links. The channel

assignment supports the concatenation of time-slots (N x DS0) up to a maximum

of 32 concatenated time-slots for each 2.048 Mbps H-MVIP link. Time-slots

assigned to any particular channel need not be contiguous within the H-MVIP

link. When configured for 2.048 Mbps H-MVIP operation, the FREEDM-32A672

partitions the 32 physical links into 4 logical groups of 8 links. Links 0 through 7, 8

through 15, 16 through 23 and 24 through 31 make up the 4 logical groups.

Links in each logical group share a common clock and a common type 0 frame

pulse in each direction.

The FREEDM-32A672 may be configured to interface with H-MVIP digital

telephony buses at 8.192 Mbps. For 8.192 Mbps H-MVIP links, the FREEDM32A672 allows up to 672 bi-directional HDLC channels to be assigned to

individual time-slots within a maximum of 8 H-MVIP links. The channel

assignment supports the concatenation of time-slots (N x DS0) up to a maximum

of 128 concatenated time-slots for each 8.192 H-MVIP link. Time-slots assigned

to any particular channel need not be contiguous within the H-MVIP link. When

configured for 8.192 Mbps H-MVIP operation, the FREEDM-32A672 partitions

the 32 physical links into 8 logical groups of 4 links. Only the first link, which

must be located at physical links numbered 4m (0£m£7), of each logical group

can be configured for 8.192 Mbps operation. The remaining 3 physical links in

the logical group (numbered 4m+1, 4m+2 and 4m+3) are unused. All links

configured for 8.192 Mbps H-MVIP operation will share a common type 0 frame

pulse, a common frame pulse clock and a common data clock.

For channelised T1/J1/E1 links, the FREEDM-32A672 allows up to 672 bidirectional HDLC channels to be assigned to individual time-slots within a

maximum of 32 independently timed T1/J1 or E1 links. The gapped clock

method to determine time-slot positions as per the FREEDM-8 and FREEDM-32

devices is retained. The channel assignment supports the concatenation of timeslots (N x DS0) up to a maximum of 24 concatenated time-slots for a T1/J1 link

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 7

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

and 31 concatenated time-slots for an E1 link. Time-slots assigned to any

particular channel need not be contiguous within the T1/J1 or E1 link.

For unchannelised links, the FREEDM-32A672 processes up to 32 bi-directional

HDLC channels within 32 independently timed links. The links can be of arbitrary

frame format. When limited to three unchannelised links, each link can be rated

at up to 51.84 MHz provided SYSCLK is running at 45 MHz. For lower rate

unchannelised links, the FREEDM-32A672 processes up to 32 links each rated

at up to 10 MHz. In this case, the aggregate clock rate of all the links is limited to

64 MHz.

The FREEDM-32A672 supports mixing of up to 32 channelised T1/J1/E1,

unchannelised and H-MVIP links. The total number of channels in each direction

is limited to 672. The aggregate instantaneous clock rate over all 32 possible

links is limited to 64 MHz.

The FREEDM-32A672 provides a low latency “Any-PHY” packet interface (APPI)

to allow an external controller direct access into the 32 Kbyte partial packet

buffers. Up to seven FREEDM-32A672 devices may share a single APPI. For

each of the transmit and receive APPI, the external controller is the master of

each FREEDM-32A672 device sharing the APPI from the point of view of device

selection. The external controller is also the master for channel selection in the

transmit direction. In the receive direction, however, each FREEDM-32A672

device retains control over selection of its respective channels. The transmit and

receive APPI is made up of three groups of functional signals – polling, selection

and data transfer. The polling signals are used by the external controller to

interrogate the status of the transmit and receive 32 Kbyte partial packet buffers.

The selection signals are used by the external controller to select a FREEDM32A672 device, or a channel within a FREEDM-32A672 device, for data transfer.

The data transfer signals provide a means of transferring data across the APPI

between the external controller and a FREEDM-32A672 device.

In the receive direction, polling and selection are done at the device level.

Polling is not decoupled from selection, as the receive address pins serve as

both a device poll address and to select a FREEDM-32A672 device. In response

to a positive poll, the external controller may select that FREEDM-32A672 device

for data transfer. Once selected, the FREEDM-32A672 prepends an in-band

channel address to each partial packet transfer across the receive APPI to

associate the data with a channel. A FREEDM-32A672 must not be selected

after a negative poll response.

In the transmit direction, polling is done at the channel level. Polling is

completely decoupled from selection. To increase the polling bandwidth, up to

two channels may be polled simultaneously. The polling engine in the external

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 8

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

controller runs independently of other activity on the transmit APPI. In response

to a positive poll, the external controller may commence partial packet data

transfer across the transmit APPI for the successfully polled channel of a

FREEDM-32A672 device. The external controller must prepend an in-band

channel address to each partial packet transfer across the transmit APPI to

associate the data with a channel.

In the receive direction, the FREEDM-32A672 performs channel assignment and

packet extraction and validation. For each provisioned HDLC channel, the

FREEDM-32A672 delineates the packet boundaries using flag sequence

detection, and performs bit de-stuffing. Sharing of opening and closing flags, as

well as sharing of zeros between flags are supported. The resulting packet data

is placed into the internal 32 Kbyte partial packet buffer RAM. The partial packet

buffer acts as a logical FIFO for each of the assigned channels. An external

controller transfers partial packets out of the RAM, across the receive APPI bus,

into host packet memory. The FREEDM-32A672 validates the frame check

sequence for each packet, and verifies that the packet is an integral number of

octets in length and is within a programmable minimum and maximum lengths.

Receive APPI bus latency may cause one or more channels to overflow, in which

case, the packets are aborted. The FREEDM-32A672 reports the status of each

packet on the receive APPI at the end of each packet transfer.

Alternatively, in the receive direction, the FREEDM-32A672 supports a

transparent operating mode. For each provisioned transparent channel, the

FREEDM-32A672 directly transfers the received octets onto the receive APPI

verbatim. If the transparent channel is assigned to a channelised link, then the

octets are aligned to the received time-slots.

In the transmit direction, an external controller provides packets to transmit using

the transmit APPI. For each provisioned HDLC channel, an external controller

transfers partial packets, across the transmit APPI, into the internal 32 Kbyte

transmit partial packet buffer. The partial packets are read out of the partial

packet buffer by the FREEDM-32A672 and a frame check sequence is optionally

calculated and inserted at the end of each packet. Bit stuffing is performed

before being assigned to a particular link. The flag or idle sequence is

automatically inserted when there is no packet data for a particular channel.

Sequential packets are optionally separated by a single flag (combined opening

and closing flag) or up to 128 flags. Zeros between flags are not shared in the

transmit direction although, as stated previously, they are accepted in the receive

direction. Transmit APPI bus latency may cause one or more channels to

underflow, in which case, the packets are aborted. The FREEDM-32A672

generates an interrupt to notify the host of aborted packets. For normal traffic, an

abort sequence is generated, followed by inter-frame time fill characters (flags or

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 9

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

all-ones bytes) until a new packet is sourced on the transmit APPI. The

FREEDM-32A672 will not attempt to re-transmit aborted packets.

Alternatively, in the transmit direction, the FREEDM-32A672 supports a

transparent operating mode. For each provisioned transparent channel, the

FREEDM-32A672 directly inserts the transmitted octets provided on the transmit

APPI. If the transparent channel is assigned to a channelised link, then the

octets are aligned to the transmitted time-slots. If a channel underflows due to

excessive transmit APPI bus latency, an abort sequence is generated, followed

by inter-frame time fill characters (flags or all-ones bytes) to indicate idle channel.

Data resumes immediately when the FREEDM-32A672 receives new data on the

transmit APPI.

The FREEDM-32A672 is configured, controlled and monitored using the

microprocessor interface. The FREEDM-32A672 is implemented in low power

2.5 Volt 0.25 mm CMOS technology. All FREEDM-32A672 I/O except those

belonging to the APPI are 5 volt tolerant. The APPI I/O are 3.3 volt tolerant. The

FREEDM-32A672 is packaged in a 329 pin plastic ball grid array (PBGA)

package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 10

DATASHEET

PM7381 FREEDM-32A672

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

ANY-PHY PACKET INTERFACE

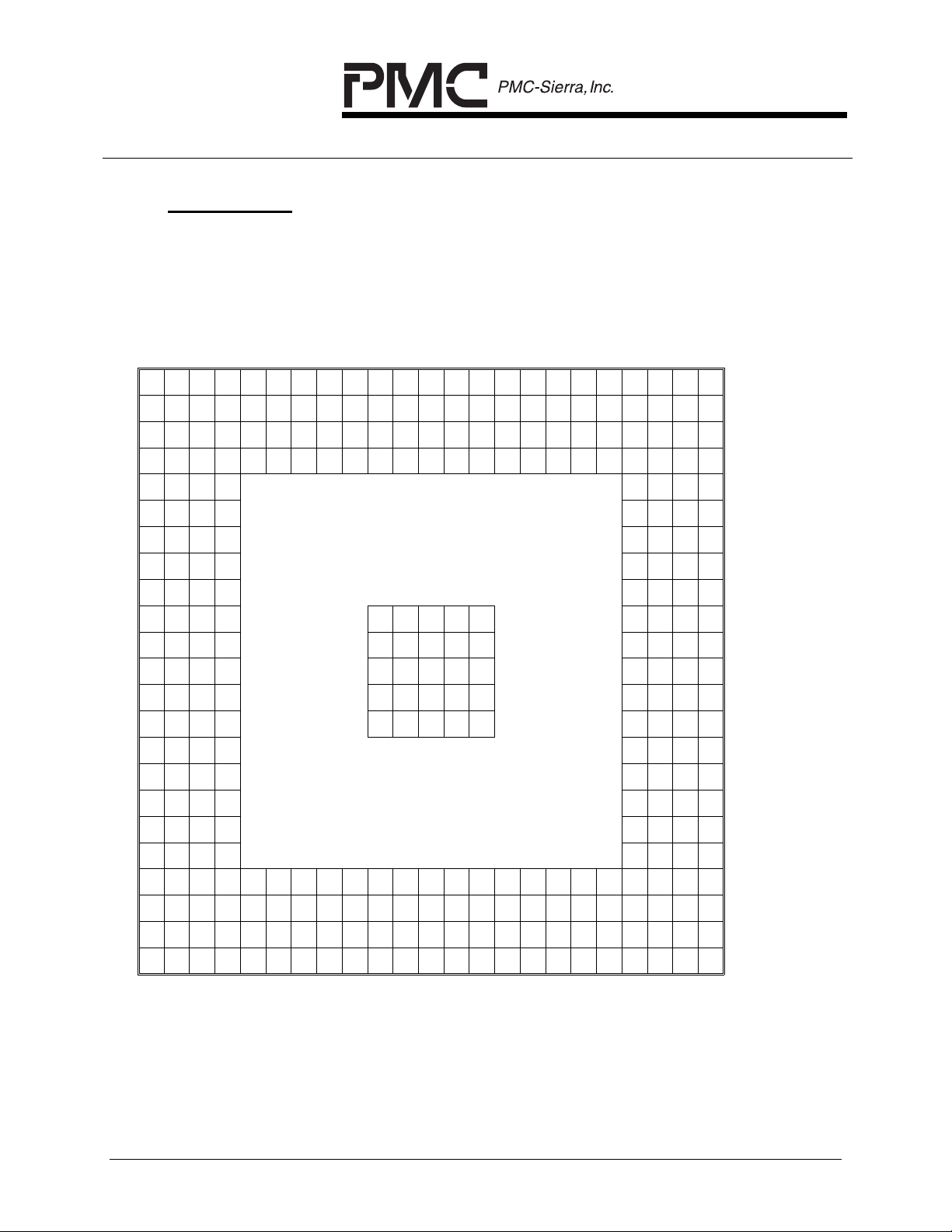

6 PIN DIAGRAM

The FREEDM-32A672 is manufactured in a 329 pin plastic ball grid array

package.

2322212019181716151413121110987654321

RMVCK[2] RD[16] RCLK[17] RCLK[19] RD[21] RD[22] RD[23] RD[24] RCLK[25] RCLK[27] RCLK[29] VDD2V5 RDB A[10] A[6] A[3] D[13] D[11] D[9] D[6] D[2] D[0] TPA2[2]

A

RFPB[2] RCLK[16] RD[18] RD[20] VDD2V5 RCLK[22] RFPB[3] RCLK[24] RCLK[26] RD[28] RD[30] RCLK[31] INTB A[11] A[8] A[4] D[15] D[12] VDD2V5 D[7] D[3] TPA2[0] TPA2[1]

B

RD[15] RSTB RCLK[15] RCLK[18] RCLK[20] RCLK[21] RMVCK[3] RD[25] RD[27] RCLK[28] RCLK[30] RD[31] CSB ALE A[9] A[5] A[2] D[10] D[8] D[4] D[1] N.C. TPA1[1]

C

RCLK[13] RD[13] RCLK[14] RD[17] RD[19] VDD3V3 RCLK[23] VSS RD[26] VDD3V3 RD[29] VSS WRB VDD3V3 A[7] VSS D[14] VDD3V3 D[5] TPA1[2] TPA1[0]

D

RD[12] VDD2V5 RCLK[12] RD[14]

E

RD[11] RCLK[10] RCLK[11] VSS VSS

F

RD[10] RD[9] RCLK[8] RCLK[9]

G

RD[8] RMVCK[1] RFPB[1] VDD3V3 VDD3V3

H

RCLK[7] RCLK[6] RD[6] RD[7]

J

SYSCLK RCLK[5] RD[5] VSS VSS VSS VSS VSS VSS VSS

K

RD[4] RD[3] RCLK[3] RCLK[4] VSS VSS VSS VSS VSS TXPRTY

L

VDD2V5 RCLK[2] RD[2] VDD3V3 VSS VSS VSS VSS VSS VDD3V3

M

RCLK[0] RD[1] RCLK[1] RD[0] VSS VSS VSS VSS VSS

N

RMV8FPC RFPB[0] RMVCK[0] VSS VSS VSS VSS VSS VSS VSS TEOP TMOD TERR

P

RBD RMV8DC RFP8B RBCLK RPA TRDY RVAL RENB

R

TCK TMS TRSTB VDD3V3 VDD3V3 REOP RMOD RERR

T

TFP8B TDO TDI TMV8DC

U

TFPB[0] TMV8FPC TMVCK[0] VSS VSS

V

TD[0] VDD2V5 TCLK[0] TD[2]

W

TCLK[1] TD[1] TCLK[2] TD[4] TMVCK[1] VDD3V3 TD[12] VSS TCLK[15] VDD3V3 TCLK[17] VSS TD[22] VDD3V3 TD[24] VSS TCLK[27] VDD3V3 TBD

Y

TCLK[3] TD[3] TCLK[6] TFPB[1] TD[9] TD[10] TD[13] TCLK[14] TMVCK[2] TD[17] TCLK[18] TD[20] TCLK[20] TCLK[22] TFPB[3] TD[25] TCLK[26] TCLK[29] TCLK[30] TBCLK

AA

TD[5] TCLK[4] TCLK[7] TCLK[8] VDD2V5 TD[11] TCLK[12] TD[14] TFPB[2] TCLK[16] TD[19] TCLK[19] TD[21] TD[23] TMVCK[3] TCLK[25] TD[27] TCLK[28] VDD2V5 TD[31] PMCTEST

AB

TCLK[5] TD[6] TD[7] TD[8] TCLK[9] TCLK[10] TCLK[11] TCLK[13] TD[15] TD[16] TD[18] VDD2V5 TCLK[21] TCLK[23] TCLK[24] TD[26] TD[28] TD[29] TD[30] TCLK[31]

AC

BOTTOM VIEW

TXADDR

[12]

TXADDR

TXDATA

[13]

TXDATA

RXDATA

[14]

RXDATA

RXADDR

TXADDR

TXADDR

VDD2V5

[9]

TXADDR

TXADDR

[7]

TXADDR

TXADDR

[3]

[1]

TXDATA

TXCLK

[15]

TXDATA

TXDATA

[11]

TXDATA

TXDATA

[8]

TXDATA

TXDATA

[6]

TXDATA

TXDATA

[5]

TXDATA

TXDATA

[0]

[2]

RXDATA

RXPRTY

RXDATA

RXDATA

[10]

RXDATA

VDD2V5

[6]

[8]

RXDATA

[1]

[5]

RXDATA

RXDATA

[2]

RXADDR

RXADDR

RXCLK

[0]

2322212019181716151413121110987654321

[10]

[5]

[2]

[12]

[9]

[7]

[4]

[3]

[15]

[12]

RSX

[4]

[2]

TXADDR

[11]

TXADDR

[8]

TXADDR

[6]

TXADDR

[4]

TXADDR

[0]

TXDATA

[14]

TXDATA

[10]

TSX

VDD2V5

TXDATA

[1]

RXDATA

[13]

RXDATA

[11]

RXDATA

[9]

RXDATA

[7]

RXDATA

[3]

RXDATA

[1]

RXDATA

[0]

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 11

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

7 PIN DESCRIPTION

Table 1 – Line Side Interface Signals (154)

Pin Name Type Pin

Function

No.

RCLK[0]

RCLK[1]

RCLK[2]

RCLK[3]

RCLK[4]

RCLK[5]

RCLK[6]

RCLK[7]

RCLK[8]

RCLK[9]

RCLK[10]

RCLK[11]

RCLK[12]

RCLK[13]

RCLK[14]

RCLK[15]

RCLK[16]

RCLK[17]

RCLK[18]

RCLK[19]

RCLK[20]

RCLK[21]

RCLK[22]

RCLK[23]

RCLK[24]

RCLK[25]

RCLK[26]

RCLK[27]

RCLK[28]

RCLK[29]

RCLK[30]

RCLK[31]

Input N23

N21

M22

L21

L20

K22

J22

J23

G21

G20

F22

F21

E21

D23

D21

C21

B22

A21

C20

A20

C19

C18

B18

D17

B16

A15

B15

A14

C14

A13

C13

B12

The receive line clock signals (RCLK[31:0])

contain the recovered line clock for the 32

independently timed links. Processing of

the receive links are on a priority basis, in

descending order from RCLK[0] to

RCLK[31]. Therefore, the highest rate link

should be connected to RCLK[0] and the

lowest to RCLK[31].

For channelised T1/J1 or E1 links, RCLK[n]

must be gapped during the framing bit (for

T1/J1 interfaces) or during time-slot 0 (for

E1 interfaces) of the RD[n] stream. The

FREEDM-32A672 uses the gapping

information to determine the time-slot

alignment in the receive stream.

RCLK[31:0] is nominally a 50% duty cycle

clock of frequency 1.544 MHz for T1/J1 links

and 2.048 MHz for E1 links.

For unchannelised links, RCLK[n] must be

externally gapped during the bits or timeslots that are not part of the transmission

format payload (i.e. not part of the HDLC

packet). RCLK[2:0] is nominally a 50% duty

cycle clock between 0 and 51.84 MHz.

RCLK[31:3] is nominally a 50% duty cycle

clock between 0 and 10 MHz.

The RCLK[n] inputs are invalid and should

be forced to a low state when their

associated link is configured for operation in

H-MVIP mode.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 12

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

RD[0]

RD[1]

RD[2]

RD[3]

RD[4]

RD[5]

RD[6]

RD[7]

RD[8]

RD[9]

RD[10]

RD[11]

RD[12]

RD[13]

RD[14]

RD[15]

RD[16]

RD[17]

RD[18]

RD[19]

RD[20]

RD[21]

RD[22]

RD[23]

RD[24]

RD[25]

RD[26]

RD[27]

RD[28]

RD[29]

RD[30]

RD[31]

Input N20

N22

M21

L22

L23

K21

J21

J20

H23

G22

G23

F23

E23

D22

E20

C23

A22

D20

B21

D19

B20

A19

A18

A17

A16

C16

D15

C15

B14

D13

B13

C12

The receive data signals (RD[31:0]) contain

the recovered line data for the 32

independently timed links in normal mode

(PMCTEST set low). Processing of the

receive links is on a priority basis, in

descending order from RD[0] to RD[31].

Therefore, the highest rate link should be

connected to RD[0] and the lowest to

RD[31].

For H-MVIP links, RD[n] contains 32/128

time-slots, depending on the H-MVIP data

rate configured (2.048 or 8.192 Mbps).

When configured for 2.048 Mbps H-MVIP

operation, RD[31:24], RD[23:16], RD[15:8]

and RD[7:0] are sampled on every 2

nd

rising

edge of RMVCK[3], RMVCK[2], RMVCK[1]

and RMVCK[0] respectively (at the ¾ point

of the bit interval). When configured for

8.192 Mbps H-MVIP operation, RD[4m]

(0£m£7) are sampled on every 2nd rising

edge of RMV8DC (at the ¾ point of the bit

interval).

For channelised links, RD[n] contains the 24

(T1/J1) or 31 (E1) time-slots that comprise

the channelised link. RCLK[n] must be

gapped during the T1/J1 framing bit position

or the E1 frame alignment signal (time-slot

0). The FREEDM-32A672 uses the location

of the gap to determine the channel

alignment on RD[n]. RD[31:0] are sampled

on the rising edge of the corresponding

RCLK[31:0].

For unchannelised links, RD[n] contains the

HDLC packet data. For certain transmission

formats, RD[n] may contain place holder bits

or time-slots. RCLK[n] must be externally

gapped during the place holder positions in

the RD[n] stream. The FREEDM-32A672

supports a maximum data rate of 10 Mbit/s

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 13

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

on an individual RD[31:3] link and a

maximum data rate of 51.84 Mbit/s on

RD[2:0]. RD[31:0] are sampled on the rising

edge of the corresponding RCLK[31:0].

RMVCK[0]

RMVCK[1]

RMVCK[2]

RMVCK[3]

Input P21

H22

A23

C17

The receive MVIP data clock signals

(RMVCK[3:0]) provide the receive data clock

for the 32 links when configured to operate

in 2.048 Mbps H-MVIP mode.

When configured for 2.048 Mbps H-MVIP

operation, the 32 links are partitioned into 4

groups of 8, and each group of 8 links share

a common data clock. RMVCK[0],

RMVCK[1], RMVCK[2] and RMVCK[3]

sample the data on links RD[7:0], RD[15:8],

RD[23:16] and RD[31:24] respectively.

Each RMVCK[n] is nominally a 50% duty

cycle clock with a frequency of 4.096 MHz.

RFPB[0]

RFPB[1]

RFPB[2]

RFPB[3]

Input P22

H21

B23

B17

RMVCK[n] is ignored and should be tied low

when no physical link within the associated

logical group of 8 links is configured for

operation in 2.048 Mbps H-MVIP mode.

The receive frame pulse signals (RFPB[3:0])

reference the beginning of each frame for

the 32 links when configured for operation in

2.048 Mbps H-MVIP mode.

When configured for 2.048 Mbps H-MVIP

operation, the 32 links are partitioned into 4

groups of 8, and each group of 8 links share

a common frame pulse. RFPB[0], RFPB[1],

RFPB[2] and RFPB[3] reference the

beginning of a frame on links RD[7:0],

RD[15:8], RD[23:16] and RD[31:24]

respectively.

When configured for operation in 2.048

Mbps H-MVIP mode, RFPB[n] is sampled

on the falling edge of RMVCK[n].

Otherwise, RFPB[n] is ignored and should

be tied low.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 14

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

RFP8B Input R21 The receive frame pulse for 8.192 Mbps H-

MVIP signal (RFP8B) references the

beginning of each frame for links configured

for operation in 8.192 Mbps H-MVIP mode.

RFP8B references the beginning of a frame

for any link configured for 8.192 Mbps HMVIP operation. Only links RD[4m] (0£m£7)

may be configured for 8.192 Mbps H-MVIP

operation.

When one or more links are configured for

8.192 Mbps H-MVIP operation, RFP8B is

sampled on the falling edge of RMV8FPC.

When no links are configured for 8.192

Mbps H-MVIP operation, RFP8B is ignored

and should be tied low.

RMV8FPC Input P23 The receive 8.192 Mbps H-MVIP frame

pulse clock signal (RMV8FPC) provides the

receive frame pulse clock for links

configured for operation in 8.192 Mbps HMVIP mode.

RMV8FPC is used to sample RFP8B.

RMV8FPC is nominally a 50% duty cycle,

clock with a frequency of 4.096 MHz. The

falling edge of RMV8FPC must be aligned

with the falling edge of RMV8DC with no

more than ±10 ns skew.

RMV8FPC is ignored and should be tied low

when no physical links are configured for

operation in 8.192 Mbps H-MVIP mode.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 15

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

RMV8DC Input R22 The receive 8.192 Mbps H-MVIP data clock

signal (RMV8DC) provides the receive data

clock for links configured to operate in 8.192

Mbps H-MVIP mode.

RMV8DC is used to sample data on RD[4m]

(0£m£7) when link 4m is configured for

8.192 Mbps H-MVIP operation. RMV8DC is

nominally a 50% duty cycle clock with a

frequency of 16.384 MHz.

RMV8DC is ignored and should be tied low

when no physical links are configured for

operation in 8.192 Mbps H-MVIP mode.

RBD Tristate

Output

R23 The receive BERT data signal (RBD)

contains the receive bit error rate test data.

RBD reports the data on the selected one of

the receive data signals (RD[31:0]) and is

updated on the falling edge of RBCLK.

RBD may be tristated by setting the RBEN

bit in the FREEDM-32A672 Master BERT

Control register low. BERT is not supported

for H-MVIP links.

RBCLK Tristate

Output

R20 The receive BERT clock signal (RBCLK)

contains the receive bit error rate test clock.

RBCLK is a buffered version of the selected

one of the receive clock signals

(RCLK[31:0]). RBCLK may be tristated by

setting the RBEN bit in the FREEDM32A672 Master BERT Control register low.

BERT is not supported for H-MVIP links.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 16

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

TCLK[0]

TCLK[1]

TCLK[2]

TCLK[3]

TCLK[4]

TCLK[5]

TCLK[6]

TCLK[7]

TCLK[8]

TCLK[9]

TCLK[10]

TCLK[11]

TCLK[12]

TCLK[13]

TCLK[14]

TCLK[15]

TCLK[16]

TCLK[17]

TCLK[18]

TCLK[19]

TCLK[20]

TCLK[21]

TCLK[22]

TCLK[23]

TCLK[24]

TCLK[25]

TCLK[26]

TCLK[27]

TCLK[28]

TCLK[29]

TCLK[30]

TCLK[31]

Input W21

Y23

Y21

AA23

AB22

AC23

AA21

AB21

AB20

AC19

AC18

AC17

AB17

AC16

AA16

Y15

AB14

Y13

AA13

AB12

AA11

AC11

AA10

AC10

AC9

AB8

AA7

Y7

The transmit line clock signals (TCLK[31:0])

contain the transmit clocks for the 32

independently timed links. Processing of

the transmit links is on a priority basis, in

descending order from TCLK[0] to

TCLK[31]. Therefore, the highest rate link

should be connected to TCLK[0] and the

lowest to TCLK[31].

For channelised T1/J1 or E1 links, TCLK[n]

must be gapped during the framing bit (for

T1/J1 interfaces) or during time-slot 0 (for

E1 interfaces) of the TD[n] stream. The

FREEDM-32A672 uses the gapping

information to determine the time-slot

alignment in the transmit stream.

For unchannelised links, TCLK[n] must be

externally gapped during the bits or timeslots that are not part of the transmission

format payload (i.e. not part of the HDLC

packet).

TCLK[2:0] is nominally a 50% duty cycle

clock between 0 and 51.84 MHz.

TCLK[31:3] is nominally a 50% duty cycle

clock between 0 and 10 MHz. Typical

values for TCLK[31:0] include 1.544 MHz

(for T1/J1 links) and 2.048 MHz (for E1

links).

AB6

AA6

AA5

AC4

The TCLK[n] inputs are invalid and should

be tied low when their associated link is

configured for operation in H-MVIP mode.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 17

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

TD[0]

TD[1]

TD[2]

TD[3]

TD[4]

TD[5]

TD[6]

TD[7]

TD[8]

TD[9]

TD[10]

TD[11]

TD[12]

TD[13]

TD[14]

TD[15]

TD[16]

TD[17]

TD[18]

TD[19]

TD[20]

TD[21]

TD[22]

TD[23]

TD[24]

TD[25]

TD[26]

TD[27]

TD[28]

TD[29]

TD[30]

TD[31]

Output

W23

Y22

W20

AA22

Y20

AB23

AC22

AC21

AC20

AA19

AA18

AB18

Y17

AA17

AB16

AC15

AC14

AA14

AC13

AB13

AA12

AB11

Y11

AB10

Y9

AA8

AC8

AB7

AC7

AC6

AC5

AB4

The transmit data signals (TD[31:0]) contain

the transmit data for the 32 independently

timed links in normal mode (PMCTEST set

low). Processing of the transmit links is on

a priority basis, in descending order from

TD[0] to TD[31]. Therefore, the highest rate

link should be connected to TD[0] and the

lowest to TD[31].

For H-MVIP links, TD[n] contain 32/128

time-slots, depending on the H-MVIP data

rate configured (2.048 or 8.192 Mbps).

When configured for 2.048 Mbps H-MVIP

operation, TD[31:24], TD[23:16], TD[15:8]

and TD[7:0] are updated on every 2

nd

falling

edge of TMVCK[3], TMVCK[2], TMVCK[1]

and TMVCK[0] respectively. When

configured for 8.192 Mbps H-MVIP

operation, TD[4m] (0£m£7) are updated on

every 2nd falling edge of TMV8DC.

For channelised links, TD[n] contains the 24

(T1/J1) or 31 (E1) time-slots that comprise

the channelised link. TCLK[n] must be

gapped during the T1/J1 framing bit position

or during the E1 frame alignment signal

(time-slot 0). The FREEDM-32A672 uses

the location of the gap to determine the

channel alignment on TD[n]. TD[31:0] are

updated on the falling edge of the

corresponding TCLK[31:0].

For unchannelised links, TD[n] contains the

HDLC packet data. For certain transmission

formats, TD[n] may contain place holder bits

or time-slots. TCLK[n] must be externally

gapped during the place holder positions in

the TD[n] stream. The FREEDM-32A672

supports a maximum data rate of 10 Mbit/s

on an individual TD[31:3] link and a

maximum data rate of 51.84 Mbit/s on

TD[2:0].

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 18

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

TD[31:0] are updated on the falling edge of

the corresponding TCLK[31:0] clock.

TMVCK[0]

TMVCK[1]

TMVCK[2]

TMVCK[3]

Input V21

Y19

AA15

AB9

The transmit MVIP data clock signals

(TMVCK[3:0]) provide the transmit data

clocks for the 32 links when configured to

operate in 2.048 Mbps H-MVIP mode.

When configured for 2.048 Mbps H-MVIP

operation, the 32 links are partitioned into 4

groups of 8, and each group of 8 links share

a common clock. TMVCK[0], TMVCK[1],

TMVCK[2] and TMVCK[3] update the data

on links TD[7:0], TD[15:8], TD[23:16] and

TD[31:24] respectively. Each TMVCK[n] is

nominally a 50% duty cycle clock with a

frequency of 4.096 MHz.

TFPB[0]

TFPB[1]

TFPB[2]

TFPB[3]

Input V23

AA20

AB15

AA9

TMVCK[n] is unused and should be tied low

when no physical links within the associated

group of 8 logical links is configured for

operation in 2.048 Mbps H-MVIP mode.

The transmit frame pulse signals

(TFPB[3:0]) reference the beginning of each

frame when configured for operation in

2.048 Mbps H-MVIP mode.

When configured for 2.048 Mbps H-MVIP

operation, the 32 links are partitioned into 4

groups of 8, and each group of 8 links share

a common frame pulse. TFPB[0], TFPB[1],

TFPB[2] and TFPB[3] reference the

beginning of a frame on links TD[7:0],

TD[15:8], TD[23:16] and TD[31:24]

respectively.

When configured for operation in 2.048

Mbps H-MVIP mode, TFPB[n] is sampled on

the falling edge of TMVCK[n]. Otherwise,

TFPB[n] is ignored and should be tied low.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 19

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

TFP8B Input U23 The transmit frame pulse for 8.192 Mbps H-

MVIP signal (TFP8B) references the

beginning of each frame for links configured

to operate in 8.192 Mbps H-MVIP mode.

TFP8B references the beginning of a frame

for any link configured for 8.192 Mbps HMVIP operation. Only links 4m (0£m£7)

may be configured for 8.192 Mbps H-MVIP

operation.

When one or more links are configured for

8.192 Mbps H-MVIP operation, TFP8B is

sampled on the falling edge of TMV8FPC.

When no links are configured for 8.192

Mbps H-MVIP operation, TFPB[n] is ignored

and should be tied low.

TMV8FPC Input V22 The transmit 8.192 Mbps H-MVIP frame

pulse clock signal (TMV8FPC) provides the

transmit frame pulse clock for links

configured for operation in 8.192 Mbps HMVIP mode.

TMV8FPC is used to sample TFP8B.

TMV8FPC is nominally a 50% duty cycle,

clock with a frequency of 4.096 MHz. The

falling edge of TMV8FPC must be aligned

with the falling edge of TMV8DC with no

more than ±10 ns skew.

TMV8FPC[n] is ignored and should be tied

low when no physical links are configured

for operation in 8.192 Mbps H-MVIP mode.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 20

DATASHEET

PMC-1990263 ISSUE 6 32 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH

Pin Name Type Pin

Function

PM7381 FREEDM-32A672

ANY-PHY PACKET INTERFACE

No.

TMV8DC Input U20 The transmit 8.192 Mbps H-MVIP data clock

signal (TMV8DC) provides the transmit data

clock for links configured to operate in 8.192

Mbps H-MVIP mode.

TMV8DC is used to update data on TD[4m]

(0£m£7) when link 4m is configured for

8.192 Mbps H-MVIP operation. TMV8DC is

nominally a 50% duty cycle clock with a

frequency of 16.384 MHz.

TMV8DC is unused and should be tied low

when no physical links are configured for

operation in 8.192 Mbps H-MVIP mode.

TBD Input Y5 The transmit BERT data signal (TBD)

contains the transmit bit error rate test data.

When the TBERTEN bit in the BERT Control

register is set high, the data on TBD is

transmitted on the selected one of the

transmit data signals (TD[31:0]). TBD is

sampled on the rising edge of TBCLK.

BERT is not supported for H-MVIP links.

TBCLK Tristate

AA4 The transmit BERT clock signal (TBCLK)

Output

contains the transmit bit error rate test clock.

TBCLK is a buffered version of the selected

one of the transmit clock signals

(TCLK[31:0]). TBCLK may be tristated by

setting the TBEN bit in the FREEDM32A672 Master BERT Control register low.

BERT is not supported for H-MVIP links.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 21

Loading...

Loading...