PMC-Sierra,Inc.

Frame Engine and Data Link Manager

PM7380

FREEDM-32P672

FEATURES

The FREEDM-32P672 chip offers the

following features:

• Single-chip multi-channel HDLC

controller with a 66 MHz, 32-bit

Peripheral Component Interconnect

(PCI) 2.1 compatible bus for

configuration, mo nitorin g, and tra nsfer

of packet data.

• An on-chip DMA controller with

scatter/ gather capabilities.

• Supports up to 672 bi-directional

HDLC channels assigned to a

maximum of 32 MVIP dig ital te lephony

buses (at 2.048 Mbit/s per link) or 8

H-MVIP buses (at 8.192 Mbit/s per

link).

• Supports up to 672 bi-directional

HDLC channels assigned to a

maximum of 32 channelized T1/J1 or

E1 links.

• The number of time-slots assigned to

an HDLC channel is programmable

from 1 to 24 (for T1/J1) and from 1 to

31 (for E1) .

• Supports up to 3 2 b i-di r ec tio nal HD LC

channels, each assigned to an

unchannelized arbitrary-rate link,

subject to a maximum aggregate link

clock-rate of 64 MHz in each direction.

• Channels assigned to links 0 to 2

support a clock rate of up to 52 MHz.

Channels assigned to links 3 to 31

support a clock rate of up to 10 MHz.

• In the special case, where no more

than three high-speed links are used,

the maximum aggregate link

clock-rate is 156 MHz.

• Links configured for channelized T1/

J1/E1 or unchannelized operation

support the gapped-clock method for

determining time-slots, which is

backwards compatible with the

FREEDM-8 and FREEDM-32 devices.

• For each channel, the HDLC receiver

supports programmable

flag-sequence detection, bit

de-stuffing, and frame-check

sequence validatio n.

• The receiver support s the validati on of

both CRC-CCITT and CRC-32

frame-check sequences.

• For each channel, the HDLC

transmitter supports programmable

flag-sequence generation, bit stuffing

and frame-check sequence

generation.

• The transmitter supports the

generation of both CRC-CCITT and

CRC-32 frame-check sequences.

• The transmitter also aborts packets

under the direction of the host, or

automatically when the channel

underflows.

• Provides 32 kbytes of on-chip memory

for partial-packet buffering in both the

transmit and receive directions.

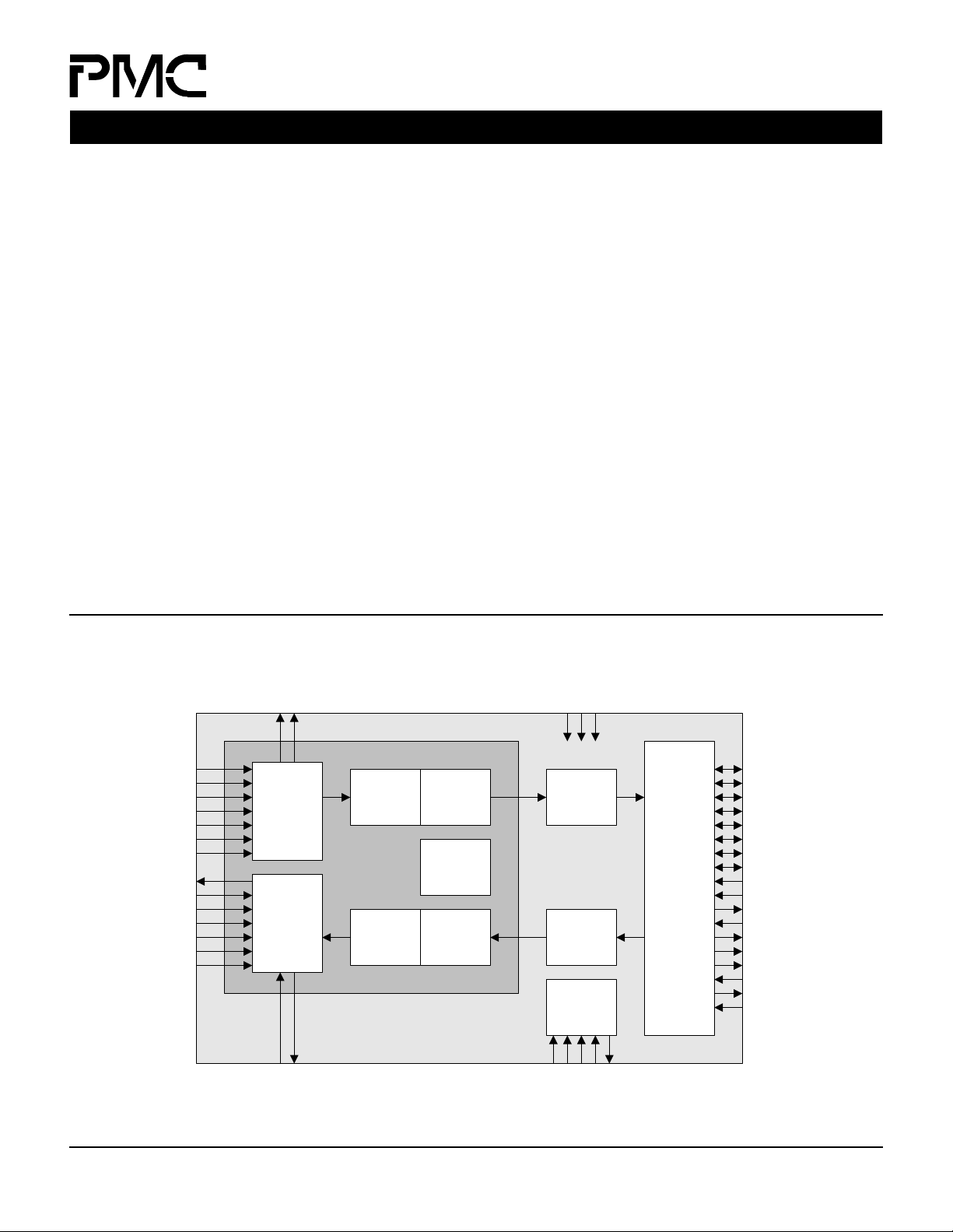

BLOCK DIAGRAM

RD[31:0]

RCLK[31:0]

RFPB[3:0]

RMVCK[3:0]

RMV8DC

RMV8FPC

RFP8B

TD[31:0]

TCLK[31:0]

TFPB[3:0]

TMVCK[3:0]

TMV8DC

TMV8FPC

TFP8B

RBD

RBCLK

Receive

Channel

Assigner

(RCAS672)

Transmit

Channel

Assigner

(TCAS672)

TBD

TBCLK

Receive

HDLC

Processor

(RHDL672)

Transmit

HDLC

Processor

(THDL672)

32 k Receive

Partial

Packet

Buffer

Performance

Monitor

(PMON)

32 k Transmit

Partial

Packet

Buffer

RSTB

SYSCLK

Receive

DMA

Controller

(RMAC672)

Transmit

DMA

Controller

(TMAC672)

JTAG

TCK

TMS

TRSTB

PMCTEST

TD1

AD[31:0]

C/BEB[3:0]

PAR

FRAMEB

TRDYB

IRDYB

STOPB

PCI

Controller

(GPIC672)

TD0

DEVSELB

IDSEL

LOCKB

REQB

GNTB

PERRB

SERRB

PCIINTB

PCICLK

PCICLKO

M66EN

PMC-1980245 (r2) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © 2001 PMC-Sierra, Inc.

Frame Engine and Data Link Manager

PM7380 FREEDM-32P672

• Y ou can configure the o n-chip memory

to support different channel

configurations: from a single channel

with 32 kbytes of buffering, to 672

channels, each with a minim um of 4 8

bytes of buffering.

• Provides a standard five-signal

P1149.1 JTAG test-port for

boundary-scan board-test purposes.

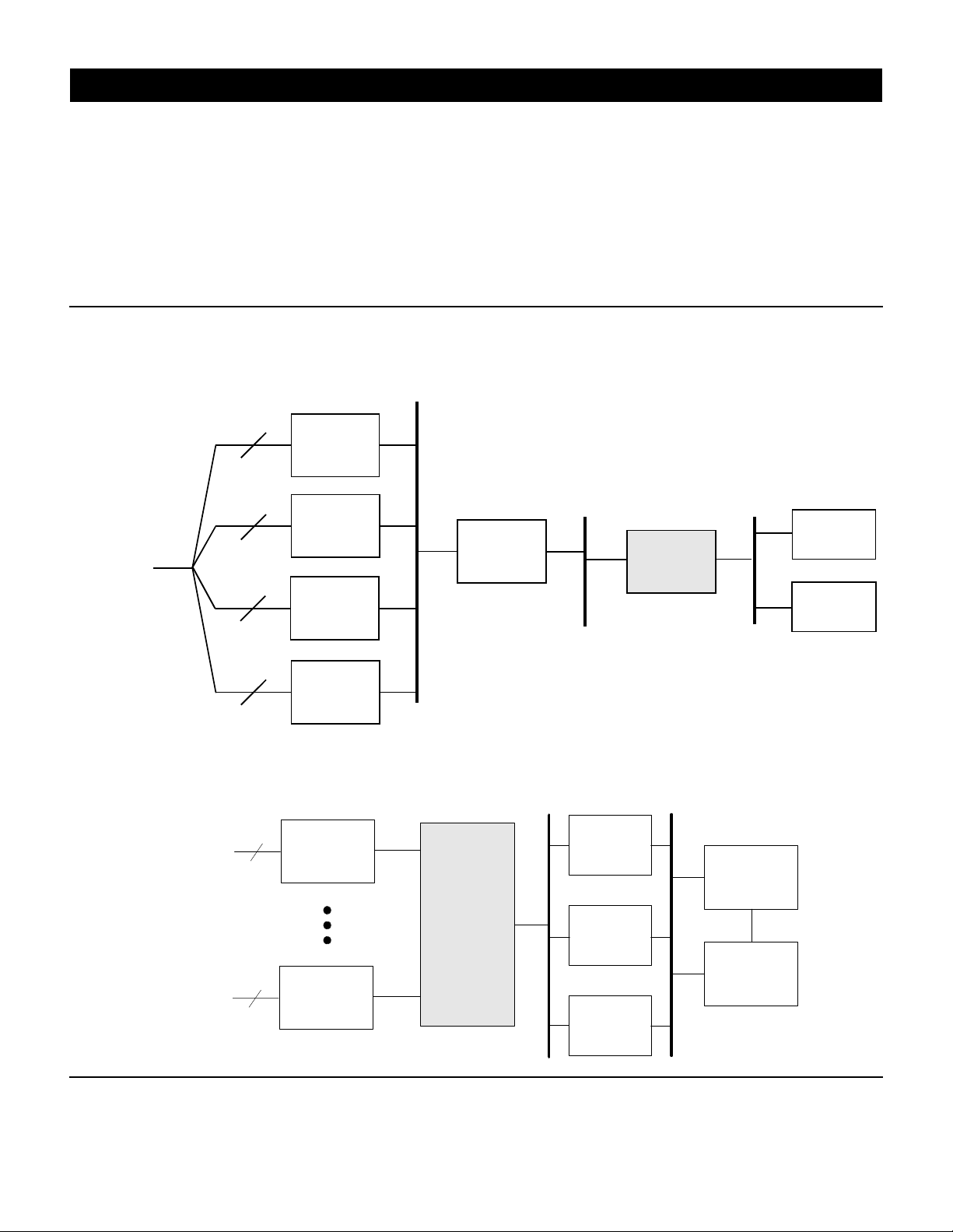

TYPICAL APPLICATIONS

HIGH DENSITY T1/E1 LINE CARD

8

8

32xT1/E1/J1

8

• Supports 5 Volt tolerant I/Os for

non-PCI signals. Suppo rts 3.3 V olt PC I

signaling environment.

• 329-pin plastic ball grid array (PBGA)

package.

SBI

PM4318

OCTLIU

PM4318

OCTLIU

PM4318

OCTLIU

PM4332

TE-32

APPLICATIONS

Use the FREEDM-32P672 chip in the

following applications:

• Remote Access Concentrators.

• Frame Relay/Multiservice Switches.

• Multiservice Access Concentrators.

• Internet/Edge Routers.

PCI Bus

Packet

PM7380

FREEDM-

32P672

Mamory

Processor

8

PM4318

OCTLIU

FRAME RELAY TO ATM INTERWORKING

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

4 T1/E1

4 T1/E1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM4354

COMET-

QUAD

x8

PM4354

COMET-

QUAD

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PM7380

FREEDM-

32P672

PCI Bus

Packet

Memory

Processor

(FRF.5,

FRF.8)

AAL5

SAR

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

Utopia

PM7329

S/UNI-APEX-

1K800

PM7328

S/UNI-

ATLAS-

1K800

PMC-1980245 (r2)

© 2001 PMC-Sierra, Inc. Aug.2001.

S/UNI is a registered trademark and

FREEDM-32P672, FREEDM-8,

FREEDM-32, OCTLIU, TE-32,

COMET-QUAD, SBI, and PMC-Sierra

are trademarks of PMC-Sierra, Inc.

Loading...

Loading...