PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

PM7375

TM

L

ASAR-

155

LOCAL ATM SEGMENTATION AND

REASSEMBLY & PHYSICAL LAYER

INTERFACE

DATA SHEET

ISSUE 6: JUNE 1998

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

PUBLIC REVISION HISTORY

Issue No. Issue Date Details of Change

6 June 1998 Data Sheet Reformatted — No Change in Technical

Content.

Generated R6 data sheet from PMC-931123, P8

5 May 2, 1997 Rev 8 eng doc

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

CONTENTS

1 FEATURES......................................................................................................................................1

2 APPLICATIONS...............................................................................................................................2

3 REFERENCES................................................................................................................................2

4 APPLICATION EXAMPLES.............................................................................................................4

4.1.2 STS-3C UTP-5 ATM OPERATION......................................................................5

4.1.3 STS-3C/1 OPTICAL ATM OPERATION..............................................................5

4.1.4 DS3/E3 ATM OPERATION..................................................................................6

5 BLOCK DIAGRAM...........................................................................................................................7

6 DESCRIPTION................................................................................................................................9

7 PIN DIAGRAM...............................................................................................................................11

8 PIN DESCRIPTION (TOTAL 208)..................................................................................................12

8.1 LINE SIDE INTERFACE SIGNALS (24)..........................................................................12

8.2 MULTIPURPOSE PORT INTERFACE SIGNALS (24).....................................................17

8.3 PCI HOST INTERFACE SIGNALS (52)...........................................................................23

8.4 MICROPROCESSOR INTERFACE SIGNALS (31).........................................................31

8.5 MISCELLANEOUS INTERFACE SIGNALS (77).............................................................35

9 FUNCTIONAL DESCRIPTION......................................................................................................42

9.1 RECEIVE LINE INTERFACE...........................................................................................42

9.1.1 CLOCK RECOVERY UNIT................................................................................42

9.1.2 SERIAL TO PARALLEL CONVERTER..............................................................43

9.2 RECEIVE FRAMER AND OVERHEAD PROCESSOR....................................................43

9.2.1 RECEIVE SECTION OVERHEAD PROCESSOR.............................................44

9.2.2 RECEIVE LINE OVERHEAD PROCESSOR.....................................................44

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

9.2.3 RECEIVE PATH OVERHEAD PROCESSOR....................................................45

9.3 RECEIVE ATM CELL PROCESSOR...............................................................................45

9.3.1 CELL DELINEATION.........................................................................................45

9.3.2 CELL FILTER AND HEC VERIFICATION..........................................................46

9.3.3 GFC EXTRACTION...........................................................................................48

9.3.4 PAYLOAD DESCRAMBLING.............................................................................48

9.4 RECEIVE ATM AND ADAPTATION LAYER CELL PROCESSOR ...................................48

9.4.1 ATM LAYER PROCESSING..............................................................................48

9.4.2 AAL LAYER PROCESSING ..............................................................................49

9.5 CONNECTION PARAMETER STORE ............................................................................50

9.6 SAR PERFORMANCE MONITOR...................................................................................50

9.7 TRANSMIT ATM TRAFFIC SHAPER ..............................................................................51

9.7.1 RATE QUEUE STRUCTURES..........................................................................51

9.7.2 PEAK CELL RATE (PCR) AND SUSTAINABLE CELL RATE (SCR)

TRANSMISSION...............................................................................................52

9.7.3 CBRC SUPPORT..............................................................................................53

9.8 TRANSMIT ATM AND ADAPTATION LAYER CELL PROCESSOR.................................53

9.8.1 AAL LAYER PROCESSING ..............................................................................53

9.8.2 ATM LAYER PROCESSING..............................................................................53

9.9 TRANSMIT ATM CELL PROCESSOR............................................................................54

9.10 TRANSMIT TRANSMITTER AND OVERHEAD PROCESSOR.......................................55

9.10.1 TRANSMIT SECTION OVERHEAD PROCESSOR ..........................................55

9.10.2 TRANSMIT LINE OVERHEAD PROCESSOR..................................................55

9.11 TRANSMIT PATH OVERHEAD PROCESSOR................................................................57

9.12 TRANSMIT LINE INTERFACE........................................................................................58

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

9.12.1 CLOCK SYNTHESIS........................................................................................59

9.12.2 PARALLEL TO SERIAL CONVERTER..............................................................59

9.13 JTAG TEST ACCESS PORT INTERFACE.......................................................................59

9.14 PCI DMA CONTROLLER INTERFACE ...........................................................................59

9.14.1 PCI INTERFACE AND MAILBOX......................................................................60

9.14.2 TRANSMIT REQUEST MACHINE....................................................................62

9.14.3 TRANSMIT DESCRIPTOR TABLE....................................................................62

9.14.4 TRANSMIT QUEUES AND OPERATION..........................................................64

9.14.5 TRANSMIT DESCRIPTOR DATA STRUCTURE...............................................69

9.14.6 RECEIVE REQUEST MACHINE.......................................................................75

9.14.7 RECEIVE PACKET DESCRIPTOR TABLE........................................................75

9.14.8 RECEIVE PACKET QUEUES AND OPERATION..............................................77

9.14.9 RECEIVE PACKET DESCRIPTOR DATA STRUCTURE...................................81

9.14.10 RECEIVE MANAGEMENT DESCRIPTOR TABLE............................................85

9.14.11 RECEIVE MANAGEMENT QUEUES................................................................87

9.14.12 RECEIVE MANAGEMENT DESCRIPTOR DATA STRUCTURE.......................89

9.15 MICROPROCESSOR INTERFACE.................................................................................91

9.16 MICROPROCESSOR AND PCI HOST NORMAL MODE REGISTER MEMORY MAP...91

9.16.1 NORMAL MODE REGISTER MEMORY MAP..................................................93

10 NORMAL MODE REGISTER DESCRIPTIONS.............................................................................99

10.1 SELECTABLE MASTER REGISTERS ..........................................................................100

10.1.1 REGISTER 0X00 (0X000): LASAR-155 MASTER RESET / LOAD METERS.100

10.1.2 REGISTER 0X01 (0X004): LASAR-155 MASTER CONFIGURATION............102

10.1.3 REGISTER 0X02 (0X008): LASAR-155 MASTER INTERRUPT STATUS.......105

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

10.1.4 REGISTER 0X03 (0X00C): LASAR-155 MASTER INTERRUPT ENABLE.....108

10.1.5 REGISTER 0X04 (0X010): LASAR-155 MASTER CLOCK MONITOR...........109

10.1.6 REGISTER 0X05 (0X014): LASAR-155 MASTER CONTROL........................ 111

10.1.7 REGISTER 0X06 (0X018): LASAR-155 CLOCK SYNTHESIS CONTROL AND

STATUS ...........................................................................................................114

10.1.8 REGISTER 0X07 (0X01C): LASAR-155 CLOCK RECOVERY CONTROL AND

STATUS ...........................................................................................................115

10.1.9 REGISTER 0X10 (0X040): RSOP CONTROL/INTERRUPT ENABLE............117

10.1.10 REGISTER 0X11 (0X044): RSOP STATUS/INTERRUPT STATUS.................119

10.1.11 REGISTER 0X12 (0X048): RSOP SECTION BIP-8 LSB................................121

10.1.12 REGISTER 0X13 (0X04C): RSOP SECTION BIP-8 MSB...............................121

10.1.13 REGISTER 0X14 (0X050): TSOP CONTROL.................................................123

10.1.14 REGISTER 0X15 (0X054): TSOP DIAGNOSTIC............................................124

10.1.15 REGISTER 0X18 (0X060): RLOP CONTROL/STATUS...................................125

10.1.16 REGISTER 0X19 (0X064): RLOP INTERRUPT ENABLE/STATUS.................126

10.1.17 REGISTER 0X1A (0X068): RLOP LINE BIP-8/24 LSB...................................128

10.1.18 REGISTER 0X1B (0X06C): RLOP LINE BIP-8/24..........................................128

10.1.19 REGISTER 0X1C (0X070): RLOP LINE BIP-8/24 MSB..................................129

10.1.20 REGISTER 0X1D (0X074): RLOP LINE FEBE LSB.......................................130

10.1.21 REGISTER 0X1E (0X078): RLOP LINE FEBE...............................................130

10.1.22 REGISTER 0X1F (0X07C): RLOP LINE FEBE MSB......................................131

10.1.23 REGISTER 0X20 (0X080): TLOP CONTROL.................................................132

10.1.24 REGISTER 0X21 (0X084): TLOP DIAGNOSTIC.............................................133

10.1.25 REGISTER 0X30 (0X0C0): RPOP STATUS/CONTROL..................................134

10.1.26 REGISTER 0X31 (0X0C4): RPOP INTERRUPT STATUS...............................135

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

10.1.28 REGISTER 0X33 (0X0CC): RPOP INTERRUPT ENABLE.............................136

10.1.32 REGISTER 0X37 (0X0DC): RPOP PATH SIGNAL LABEL..............................138

10.1.33 REGISTER 0X38 (0X0E0): RPOP PATH BIP-8 LSB.......................................139

10.1.34 REGISTER 0X39 (0X0E4): RPOP PATH BIP-8 MSB......................................140

10.1.35 REGISTER 0X3A (0X0E8): RPOP PATH FEBE LSB ......................................141

10.1.36 REGISTER 0X3B (0X0EC): RPOP PATH FEBE MSB.....................................142

10.1.37 REGISTER 0X40 (0X100): TPOP CONTROL/DIAGNOSTIC..........................143

10.1.38 REGISTER 0X41 (0X104): TPOP POINTER CONTROL................................144

10.1.41 REGISTER 0X45 (0X114): TPOP ARBITRARY POINTER LSB.....................146

10.1.42 REGISTER 0X46 (0X118): TPOP ARBITRARY POINTER MSB....................147

10.1.44 REGISTER 0X48 (0X120): TPOP PATH SIGNAL LABEL ...............................148

10.1.45 REGISTER 0X49 (0X124): TPOP PATH STATUS............................................149

10.1.52 REGISTER 0X50 (0X140): RACP CONTROL/STATUS...................................150

10.1.53 REGISTER 0X51 (0X144): RACP INTERRUPT ENABLE/STATUS ................152

10.1.54 REGISTER 0X52 (0X148): RACP MATCH HEADER PATTERN .....................154

10.1.55 REGISTER 0X53 (0X14C): RACP MATCH HEADER MASK ..........................155

10.1.56 REGISTER 0X54 (0X150): RACP CORRECTABLE HEC ERROR COUNT....156

10.1.57 REGISTER 0X55 (0X154): RACP UNCORRECTABLE HEC ERROR COUNT157

10.1.58 REGISTER 0X56 (0X158): RACP RECEIVE CELL COUNTER (LSB)............158

10.1.59 REGISTER 0X57 (0X15C): RACP RECEIVE CELL COUNTER.....................158

10.1.60 REGISTER 0X58 (0X160): RACP RECEIVE CELL COUNTER (MSB)...........159

10.1.61 REGISTER 0X59 (0X164): RACP CONFIGURATION.....................................160

10.1.62 REGISTER 0X60 (0X180): TACP CONTROL/STATUS....................................162

10.1.63 REGISTER 0X61 (0X184): TACP IDLE/UNASSIGNED CELL HEADER PATTERN

........................................................................................................................164

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

10.1.64 REGISTER 0X62 (0X188): TACP IDLE/UNASSIGNED CELL PAYLOAD OCTET

PATTERN........................................................................................................165

10.1.65 REGISTER 0X63 (0X18C): TACP FIFO CONFIGURATION............................166

10.1.66 REGISTER 0X64 (0X190): TACP TRANSMIT CELL COUNTER (LSB)..........167

10.1.67 REGISTER 0X65 (0X194): TACP TRANSMIT CELL COUNTER ....................167

10.1.68 REGISTER 0X66 (0X198): TACP TRANSMIT CELL COUNTER (MSB) .........168

10.1.69 REGISTER 0X67 (0X19C): TACP CONFIGURATION.....................................169

10.1.70 REGISTER 0X70 (0X1C0): SAR PMON COUNT CHANGE........................... 171

10.1.71 REGISTER 0X72 (0X1C8): SAR PMON RECEIVE UNPROVISIONED VPI/VCI

ERRORS (LSB)...............................................................................................174

10.1.72 REGISTER 0X73 (0X1CC): SAR PMON RECEIVE UNPROVISIONED VPI/VCI

ERRORS (MSB)..............................................................................................174

10.1.73 REGISTER 0X74 (0X1D0): SAR PMON RECEIVE CRC-10 ERRORS (LSB) 175

10.1.74 REGISTER 0X75 (0X1D4): SAR PMON RECEIVE CRC-10 ERRORS (MSB)175

10.1.75 REGISTER 0X76 (0X1D8): SAR PMON RECEIVE NON ZERO COMMON PART

INDICATOR ERRORS.....................................................................................176

10.1.76 REGISTER 0X77 (0X1DC): SAR PMON RECEIVE SDU LENGTH ERRORS177

10.1.77 REGISTER 0X78 (0X1E0): SAR PMON RECEIVE CRC-32 ERRORS...........178

10.1.78 REGISTER 0X79 (0X1E4): SAR PMON RECEIVE OVERSIZE PDU ERRORS

........................................................................................................................179

10.1.79 REGISTER 0X7B (0X1EC): SAR PMON RECEIVE PDU ABORT ERRORS..180

10.1.80 REGISTER 0X7C (0X1F0): SAR PMON RECEIVE BUFFER ERRORS.........181

10.1.81 REGISTER 0X7D (0X1F4): SAR PMON RECEIVE PDU COUNT..................182

10.1.82 REGISTER 0X7E (0X1F8): SAR PMON TRANSMIT OVERSIZE SDU ERRORS

........................................................................................................................183

10.1.83 MKT : HIDE REGISTER IN MKT DATASHEET ...............................................184

10.1.84 ENG : REGISTER 0X7F (0X1FC): SAR PMON TRANSMIT PDU COUNT.....184

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

10.1.85 REGISTER 0X80 (0X200): RALP CONTROL.................................................185

10.1.86 REGISTER 0X81 (0X204): RALP INTERRUPT STATUS................................189

10.1.87 REGISTER 0X82 (0X208): RALP INTERRUPT ENABLE...............................192

10.1.88 REGISTER 0X83 (0X20C): RALP MAX RX PDU LENGTH............................193

10.1.89 REGISTER 0X88 (0X220): TALP CONTROL..................................................194

10.1.90 REGISTER 0X89 (0X224): TALP INTERRUPT STATUS................................. 197

10.1.91 REGISTER 0X8A (0X228): TALP DIAGNOSTIC.............................................198

10.1.92 REGISTER 0X8B: (0X22C) TALP AGGREGATE PEAK CELL RATE..............199

10.1.93 REGISTER 0X8C (0X230): TALP AGGREGATE BUCKET CAPACITY...........201

10.1.94 REGISTER 0X8D (0X234): TALP MULTIPURPOSE PORT PEAK CELL RATE202

10.1.95 REGISTER 0X8E (0X238): TALP MULTIPURPOSE PORT BUCKET CAPACITY

........................................................................................................................204

10.1.96 REGISTER 0X90 (0X240): TATS CONTROL/INTERRUPT ENABLE..............205

10.1.97 REGISTER 0X91 (0X244): TATS INTERRUPT STATUS .................................207

10.1.98 REGISTER 0X92 (0X248): TATS SERVICE RATE QUEUE ENABLES...........208

10.1.99 REGISTER 0X93-0X96 (0X24C-0X258): TATS SERVICE RATE QUEUE 1, 2, 3, 4

PARAMETERS................................................................................................209

10.1.100REGISTER 0X97-0X9A (0X25C-268): TATS SERVICE RATE QUEUE 5, 6, 7, 8

PARAMETERS................................................................................................212

10.1.101REGISTER 0XA0 (0X280): COPS CONTROL................................................214

10.1.102REGISTER 0XA1 (0X284): COPS PARAMETER ACCESS CONTROL..........216

10.1.103REGISTER 0XA2 (0X288): COPS VC NUMBER ............................................218

10.1.104REGISTER 0XA3 (0X28C): COPS VPI (RX/TXB = 1, RX TABLE) ....219

10.1.105REGISTER 0XA3 (0X28C): COPS VPI (RX/TXB = 0, TX TABLE) .....220

10.1.106REGISTER 0XA4 (0X290): COPS VCI............................................................222

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

10.1.107REGISTER 0XA5 (0X294): COPS VC CONTROL AND STATUS (RX/TXB = 1,

RX TABLE) ......................................................................................................223

10.1.108REGISTER 0XA5 (0X294): COPS VC CONTROL AND STATUS (RX/TXB = 0,

TX TABLE).......................................................................................................228

10.1.109REGISTER 0XA6 (0X298) : COPS VC PARAMETERS (RX/TXB = 0, TX TABLE)

........................................................................................................................231

10.1.110REGISTER 0XA7 (0X29C): COPS INDIRECT CONTROL..............................234

10.1.111REGISTER 0XA8 (0X2A0): COPS INDIRECT ADDRESS..............................236

10.1.112REGISTER 0XA9 (0X2A4): COPS INDIRECT DATA.......................................237

10.2 10.2. MICROPROCESSOR ONLY ACCESS REGISTERS...........................................238

10.2.1 REGISTER 0XC0: PCID MICROPROCESSOR CONTROL............................238

10.2.2 REGISTER 0XC1: PCID MICROPROCESSOR INTERRUPT STATUS...........238

10.2.3 REGISTER 0XC2: PCID MICROPROCESSOR INDIRECT CONTROL..........240

10.2.4 REGISTER 0XC3: PCID MICROPROCESSOR INDIRECT DATA LOW WORD242

10.2.5 REGISTER 0XC4: PCID MICROPROCESSOR INDIRECT DATA HIGH WORD

........................................................................................................................243

10.2.6 REGISTER 0XC5: PCID MICROPROCESSOR WRITE MAILBOX CONTROL244

10.2.7 REGISTER 0XC6: PCID MICROPROCESSOR WRITE MAILBOX DATA........246

10.2.8 REGISTER 0XC8: PCID MICROPROCESSOR READ MAILBOX CONTROL247

10.2.9 REGISTER 0XC9: PCID MICROPROCESSOR READ MAILBOX DATA.........249

10.4 PCI HOST ONLY ACCESS REGISTERS......................................................................250

10.4.1 REGISTER 0X300: PCID CONTROL..............................................................250

10.4.2 REGISTER 0X304: PCID INTERRUPT STATUS.............................................256

10.4.3 REGISTER 0X308: PCID INTERRUPT ENABLE............................................260

10.4.4 REGISTER 0X30C: PCID MAILBOX / MICROPROCESSOR INTERRUPT

STATUS / ENABLE..........................................................................................261

10.4.6 REGISTER 0X314: PCID RX PACKET DESCRIPTOR TABLE BASE.............263

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

10.4.7 REGISTER 0X318: PCID RX MANAGEMENT DESCRIPTOR TABLE BASE .264

10.4.8 REGISTER 0X31C: PCID RX QUEUE BASE.................................................265

10.4.9 REGISTER 0X320: PCID RX PACKET DESCRIPTOR REFERENCE LARGE

BUFFER FREE QUEUE START .....................................................................266

10.4.10 REGISTER 0X324: PCID RX PACKET DESCRIPTOR REFERENCE LARGE

BUFFER FREE QUEUE WRITE.....................................................................267

10.4.11 REGISTER 0X328: PCID RX PACKET DESCRIPTOR REFERENCE LARGE

BUFFER FREE QUEUE READ.......................................................................268

10.4.12 REGISTER 0X32C: PCID RX PACKET DESCRIPTOR REFERENCE LARGE

BUFFER FREE QUEUE END.........................................................................269

10.4.13 REGISTER 0X330: PCID RX PACKET DESCRIPTOR REFERENCE SMALL

BUFFER FREE QUEUE START .....................................................................270

10.4.14 REGISTER 0X334: PCID RX PACKET DESCRIPTOR REFERENCE SMALL

BUFFER FREE QUEUE WRITE.....................................................................271

10.4.15 REGISTER 0X338: PCID RX PACKET DESCRIPTOR REFERENCE SMALL

BUFFER FREE QUEUE READ.......................................................................272

10.4.16 REGISTER 0X33C: PCID RX PACKET DESCRIPTOR REFERENCE SMALL

BUFFER FREE QUEUE END.........................................................................273

10.4.17 REGISTER 0X340: PCID RX PACKET DESCRIPTOR REFERENCE READY

QUEUE START...............................................................................................274

10.4.18 REGISTER 0X344: PCID RX PACKET DESCRIPTOR REFERENCE READY

QUEUE WRITE...............................................................................................275

10.4.19 REGISTER 0X348: PCID RX PACKET DESCRIPTOR REFERENCE READY

QUEUE READ ................................................................................................276

10.4.20 REGISTER 0X34C: PCID RX PACKET DESCRIPTOR REFERENCE READY

QUEUE END...................................................................................................277

10.4.21 REGISTER 0X350: PCID RX MANAGEMENT DESCRIPTOR REFERENCE

FREE QUEUE START.....................................................................................278

10.4.22 REGISTER 0X354: PCID RX MANAGEMENT DESCRIPTOR REFERENCE

FREE QUEUE WRITE....................................................................................279

10.4.23 REGISTER 0X358: PCID RX MANAGEMENT DESCRIPTOR REFERENCE

FREE QUEUE READ......................................................................................280

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

10.4.24 REGISTER 0X35C: PCID RX MANAGEMENT DESCRIPTOR REFERENCE

FREE QUEUE END........................................................................................281

10.4.25 REGISTER 0X360: PCID RX MANAGEMENT DESCRIPTOR REFERENCE

READY QUEUE START..................................................................................282

10.4.26 REGISTER 0X364: PCID RX MANAGEMENT DESCRIPTOR REFERENCE

READY QUEUE WRITE..................................................................................283

10.4.27 REGISTER 0X368: PCID RX MANAGEMENT DESCRIPTOR REFERENCE

READY QUEUE READ....................................................................................284

10.4.28 REGISTER 0X36C: PCID RX MANAGEMENT DESCRIPTOR REFERENCE

READY QUEUE END......................................................................................285

10.4.29 REGISTER 0X378: PCID TX DESCRIPTOR TABLE BASE............................286

10.4.30 REGISTER 0X37C: PCID TX QUEUE BASE..................................................287

10.4.31 REGISTER 0X380: PCID TX DESCRIPTOR REFERENCE FREE QUEUE

START.............................................................................................................288

10.4.32 REGISTER 0X384: PCID TX DESCRIPTOR REFERENCE FREE QUEUE

WRITE ............................................................................................................289

10.4.33 REGISTER 0X388: PCID TX DESCRIPTOR REFERENCE FREE QUEUE READ

........................................................................................................................290

10.4.34 REGISTER 0X38C: PCID TX DESCRIPTOR REFERENCE FREE QUEUE END

........................................................................................................................291

10.4.35 REGISTER 0X390: PCID TX DESCRIPTOR REFERENCE HIGH PRIORITY

READY QUEUE START..................................................................................292

10.4.36 REGISTER 0X394: PCID TX DESCRIPTOR REFERENCE HIGH PRIORITY

READY QUEUE WRITE..................................................................................293

10.4.37 REGISTER 0X398: PCID TX DESCRIPTOR REFERENCE HIGH PRIORITY

READY QUEUE READ....................................................................................294

10.4.38 REGISTER 0X39C: PCID TX DESCRIPTOR REFERENCE HIGH PRIORITY

READY QUEUE END......................................................................................295

10.4.39 REGISTER 0X3A0: PCID TX DESCRIPTOR REFERENCE LOW PRIORITY

READY QUEUE START..................................................................................296

10.4.40 REGISTER 0X3A4: PCID TX DESCRIPTOR REFERENCE LOW PRIORITY

READY QUEUE WRITE..................................................................................297

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

10.4.41 REGISTER 0X3A8: PCID TX DESCRIPTOR REFERENCE LOW PRIORITY

READY QUEUE READ....................................................................................298

10.4.42 REGISTER 0X3AC: PCID TX DESCRIPTOR REFERENCE LOW PRIORITY

READY QUEUE END......................................................................................299

10.4.43 REGISTER 0X3B0: PCID MAX TX SDU LENGTH..........................................300

10.4.44 REGISTER 0X3B4: PCID RAS AND TAS FIFO POINTERS...........................301

10.4.45 REGISTER 0X3C8: PCID RAM INDIRECT CONTROL..................................303

10.4.46 REGISTER 0X3CC: PCID RAM INDIRECT DATA LOW WORD......................305

10.4.47 REGISTER 0X3D0: PCID RAM INDIRECT DATA HIGH WORD.....................306

10.4.48 REGISTER 0X3D4: PCID HOST WRITE MAILBOX CONTROL.....................307

10.4.49 REGISTER 0X3D8: PCID HOST WRITE MAILBOX DATA..............................308

10.4.50 REGISTER 0X3E0: PCID HOST READ MAILBOX CONTROL.......................309

10.4.51 REGISTER 0X3E4: PCID HOST READ MAILBOX DATA................................310

11 PCI CONFIGURATION REGISTER DESCRIPTIONS.................................................................311

11.1.1 PCI CONFIGURATION REGISTER MEMORY MAP ......................................311

11.1.2 REGISTER 0X00 (0X00): VENDOR IDENTIFICATION / DEVICE

IDENTIFICATION............................................................................................312

11.1.3 REGISTER 0X01 (0X04): COMMAND / STATUS............................................313

11.1.4 REGISTER 0X02 (0X08): REVISION IDENTIFIER / CLASS CODE...............317

11.1.5 REGISTER 0X03 (0X0C): CACHE LINE SIZE / LATENCY TIMER / BIST /

HEADER TYPE...............................................................................................318

11.1.6 REGISTER 0X04 (0X10): LASAR-155 MEMORY BASE ADDRESS REGISTER

........................................................................................................................319

11.1.7 REGISTER 0X05 (0X14): EXTERNAL DEVICE MEMORY BASE ADDRESS

REGISTER......................................................................................................321

11.1.8 REGISTER 0X0C (0X30): EXPANSION ROM BASE ADDRESS....................323

11.1.9 REGISTER 0X0F (0X3C): INTERRUPT LINES / INTERRUPT PINS / MIN_GNT /

MAX_LAT ........................................................................................................324

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xi

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

12 TEST FEATURES DESCRIPTION ..............................................................................................325

12.1 TEST MODE REGISTER MEMORY MAP.....................................................................325

12.1.1 REGISTER 0X100: MASTER TEST................................................................329

12.2 TEST MODE 0 DETAILS...............................................................................................330

12.3 ANALOG TEST .............................................................................................................332

12.3.1 REGISTER 0X101: ANALOG TEST ACCESS................................................333

12.4 JTAG TEST PORT.........................................................................................................333

13 OPERATION................................................................................................................................339

13.1 BOARD DESIGN RECOMMENDATIONS......................................................................339

13.2 POWER SEQUENCING................................................................................................340

13.3 INTERFACING TO ECL OR PECL DEVICES................................................................340

13.4 CLOCK RECOVERY PASSIVES...................................................................................343

13.5 ATM MAPPING AND SONET OVERHEAD BYTE USAGE ...........................................345

13.6 ATM CELL FORMAT......................................................................................................348

13.7 CPCS AAL TYPE 5 FORMAT ........................................................................................352

13.8 JTAG SUPPORT............................................................................................................356

13.9 MULTIPURPOSE PORT FIFO CONNECTIONS........................................................... 362

13.10 MULTIPURPOSE PORT EXTERNAL PHY CONNECTIONS........................................363

14 FUNCTIONAL TIMING ................................................................................................................365

14.1 GFC AND DATA LINK ACCESS ....................................................................................365

14.2 MULTIPURPOSE PORT INTERFACE ...........................................................................367

14.3 PCI INTERFACE............................................................................................................371

15 ABSOLUTE MAXIMUM RATINGS...............................................................................................382

16 CHARACTERISTICS ...................................................................................................................383

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xii

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

17 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS .............................................386

18 LASAR-155 TIMING CHARACTERISTICS..................................................................................392

19 ORDERING AND THERMAL INFORMATION .............................................................................410

20 MECHANICAL INFORMATION....................................................................................................411

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiii

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiv

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

1

FEATURES

• Single-chip Peripheral Component Interface (PCI) Bus Local ATM Network

Interface using SONET/SDH framing at 155.52 or 51.84 Mbit/s and ATM

Adaptation Layer 5 (AAL-5).

• Implements the ATM Physical Layer according to the ATM Forum User Network

Interface Specification and ITU-TS Recommendation I.432, and the ATM

Adaptation Layer Type 5 (AAL-5) for Broadband ISDN according to ITU-TS

Recommendation I.363.

• Provides a direct interface to multimode or single mode optical modules or twisted

pair wiring (UTP-5) modules, with on-chip clock recovery and clock synthesis.

• Directly supports a 32-bit PCI bus interface for configuration, monitoring and

transfer of packet data, with an on-chip DMA controller with scatter/gather

capabilities. Other 32 bit system buses can be accommodated using external

glue logic.

• Provides an on-chip 96 cell receive buffer to accommodate up to 270 µs of PCI

Bus latency.

• Provides a optional microprocessor port with master and slave capabilities.

• Provides a SCI-PHY and Utopia compliant interface for connection to external

PHY layer devices.

• Supports simultaneous segmentation and reassembly of 128 virtual circuits (VCs)

in both transmit and receive directions.

• Provides leaky bucket peak cell rate enforcement using 8 programmable peak

queues coupled with sub peak control on a per VC basis; provides sustainable

cell rate enforcement using the programmable peak cell rate queues and per VC

token bucket averaging; and provides aggregate peak cell rate enforcement.

• Provides a generic constant bit-rate (CBR) port.

• Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

test purposes.

• Low power, 0.6 micron, +5 Volt CMOS technology.

• 208 copper slugged plastic quad flat pack (PQFP) package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

2

APPLICATIONS

• ATM Workstations and Servers

• ATM Bridges, Switches and Hubs

• Multimedia Terminals

3

REFERENCES

• ATM Forum - ATM User-Network Interface Specification, V3.1, September, 1994.

• ATM Forum - "An ATM PHY Data path Interface - Level 1", V2.0, February 1994

• ITU-TS Recommendation G.709 - "Synchronous Multiplexing Structure", Helsinki,

March 1993.

• ITU-TS Recommendation I.363 - "B-ISDN ATM Adaptation Layer (AAL)

Specification", Helsinki, March 1993.

• ITU-TS Recommendation I.432 DRAFT - "B-ISDN User-Network

Interface-Physical Interface Specification", Helsinki, March 1993.

• ITU-TS Recommendation I.610 - "B-ISDN Operation and Maintenance Principles

and Functions", Helsinki, March 1993.

• Bell Communications Research - SONET Transport Systems: Common Generic

Criteria, GR-253-CORE, Issue 1, December 1994.

Bell Communications Research - Broadband-ISDN User to Network Interface and

Network Node Interface Physical Layer Generic Criteria, TR-NWT-001112, Issue

1, June 1993.

• Bell Communications Research - Asynchronous Transfer Mode (ATM) and ATM

Adaptation Layer (AAL) Protocols Generic Requirements, TA-NWT-001113, Issue

2, July 1993.

• Bell Communications Research - Generic Requirements for Operations of

Broadband Switching Systems, TA-NWT-001248, Issue 2, October 1993.

• American National Standard for Telecommunications - B-ISDN ATM Adaptation

Layer Type 5, ANSI T1.635-1993.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

• T1X1.3/93-006R3, Draft American National Standard for Telecommunications,

Synchronous Optical Network (SONET): Jitter at Network Interfaces

• IEEE 1149.1 - Standard Test Access Port and Boundary Scan Architecture, May

21, 1990.

• PCI Special Interest Group, PCI Local Bus Specification, June 1995, Version 2.1.

• PMC-940212, ATM_SCI_PHY, "SATURN Compliant Interface For ATM Devices",

February 1994, Issue 1.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

4

APPLICATION EXAMPLES

The LASAR-155™ is typically used to implement the core of a SONET or SDH

STS-3c/STM-1 or SONET STS-1 ATM User Network Interface by which an ATM

terminal is linked to an ATM switching system. The LASAR-155 can be used in a

network interface card (NIC) or directly on a mother board. Though targeted for a

PCI bus based system, the LASAR-155 can also be used with other host buses

using external glue logic.

On the line side, the LASAR-155 is typically interfaced to UTP-5 twisted pair wiring

via a line receiver, a line driver and transformers. The line receiver should perform

fixed equalization and DC restoration for good bit error rate performance.

Alternatively, the LASAR-155 can be directly connected to an optical datalink. If

required, the LASAR-155 can be loop-timed where the recovered clock is used as

the transmit clock.

On the system side, the LASAR-155 can be directly attached to a PCI bus via the

packet port. An internal DMA controller is provided to support packet segmentation

from packet memory and reassembly to packet memory totally independent of the

PCI Host. PCI Host notification of segmentation and/or reassembly completion can

be on a per packet basis or on a multi packet basis.

The initial configuration and ongoing control and monitoring of the LASAR-155 can

be provided either via the generic microprocessor interface when in slave mode, the

PCI bus packet port when in master mode, or through a combination of both.

In addition, the LASAR-155 can interface to an external PHY device using the

SCI-PHY/Utopia port. The generic microprocessor interface can be configured in

master mode for configuration and ongoing control and monitoring. When this mode

of operation is selected an optional EPROM can also be supported by the generic

microprocessor interface.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

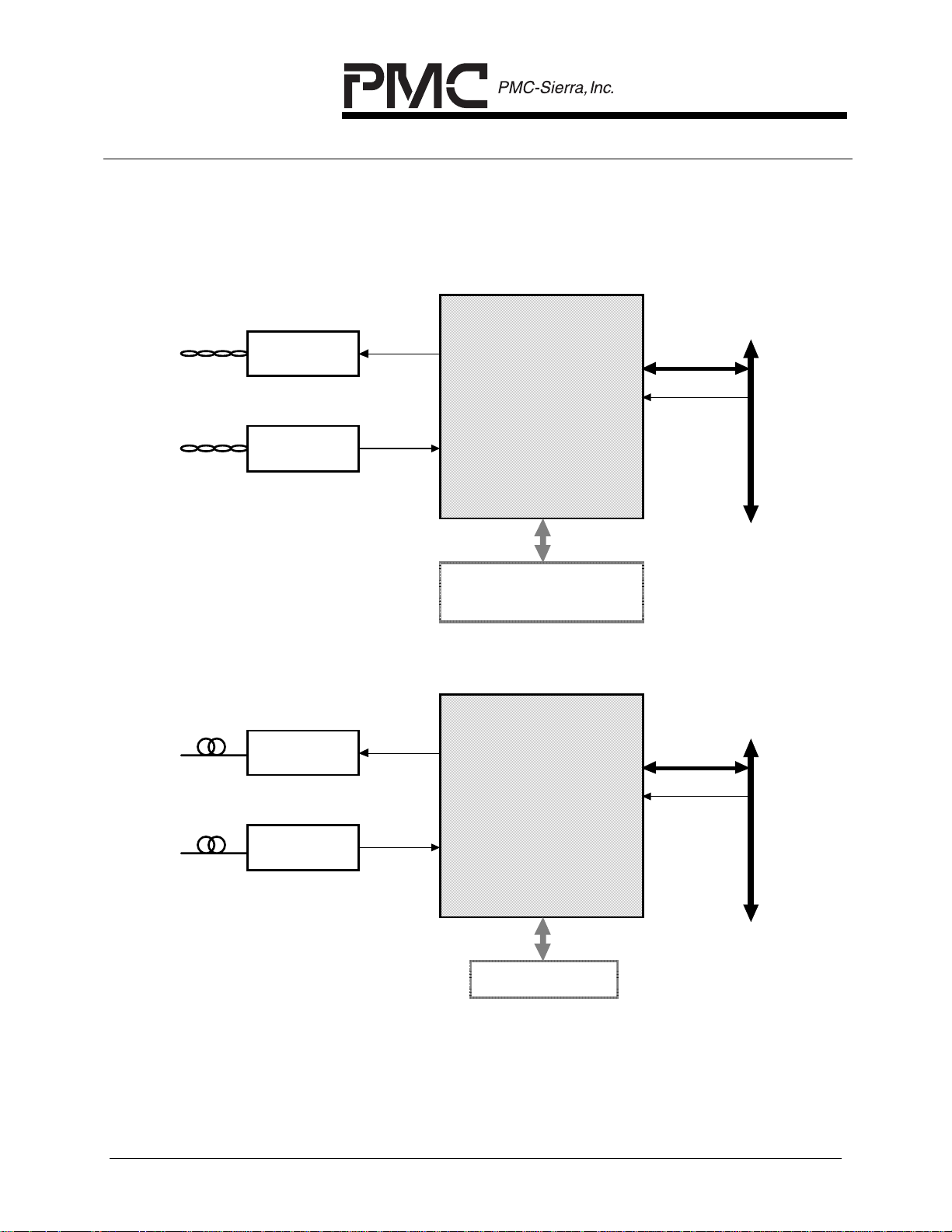

4.1.1.1 Fig. 4.1 Typical Applications

4.1.2 STS-3c UTP-5 ATM Operation

PCI

BUS

Line Driver

&

Transformer

UTP-5

Facility

Transformer,

Equalizer &

Line Receiver

TXD+/-

RXD+/-

PM7375

LASAR-155

AD[31:0]

Control

4.1.3 STS-3c/1 Optical ATM Operation

Electrical

to

Optical

TXD+/-

Optics

Facility

Optical

to

Electrical

RXD+/-

Optional Local

Microcontroller

PM7375

LASAR-155

Optional EPROM

PCI

BUS

AD[31:0]

Control

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

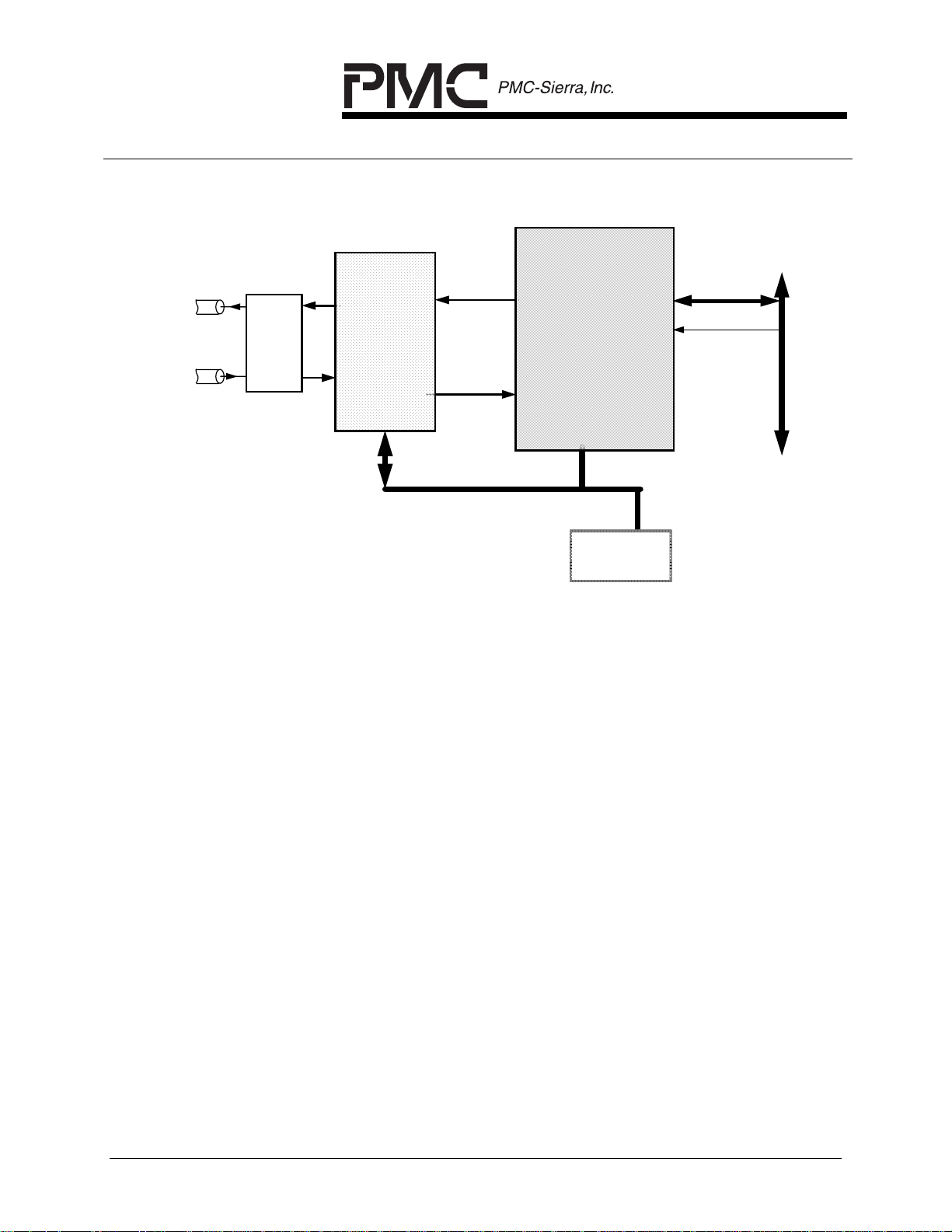

4.1.4 DS3/E3 ATM Operation

PCI

BUS

TDAT[7:0]

AD[31:0]

75 OHM

COAX

DS3/E3

LIU

PM7345

S/UNI-PDH

RDAT[7:0]

LASAR-155 LOCAL BUS

PM7375

LASAR-155

Optional

EPROM

Control

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

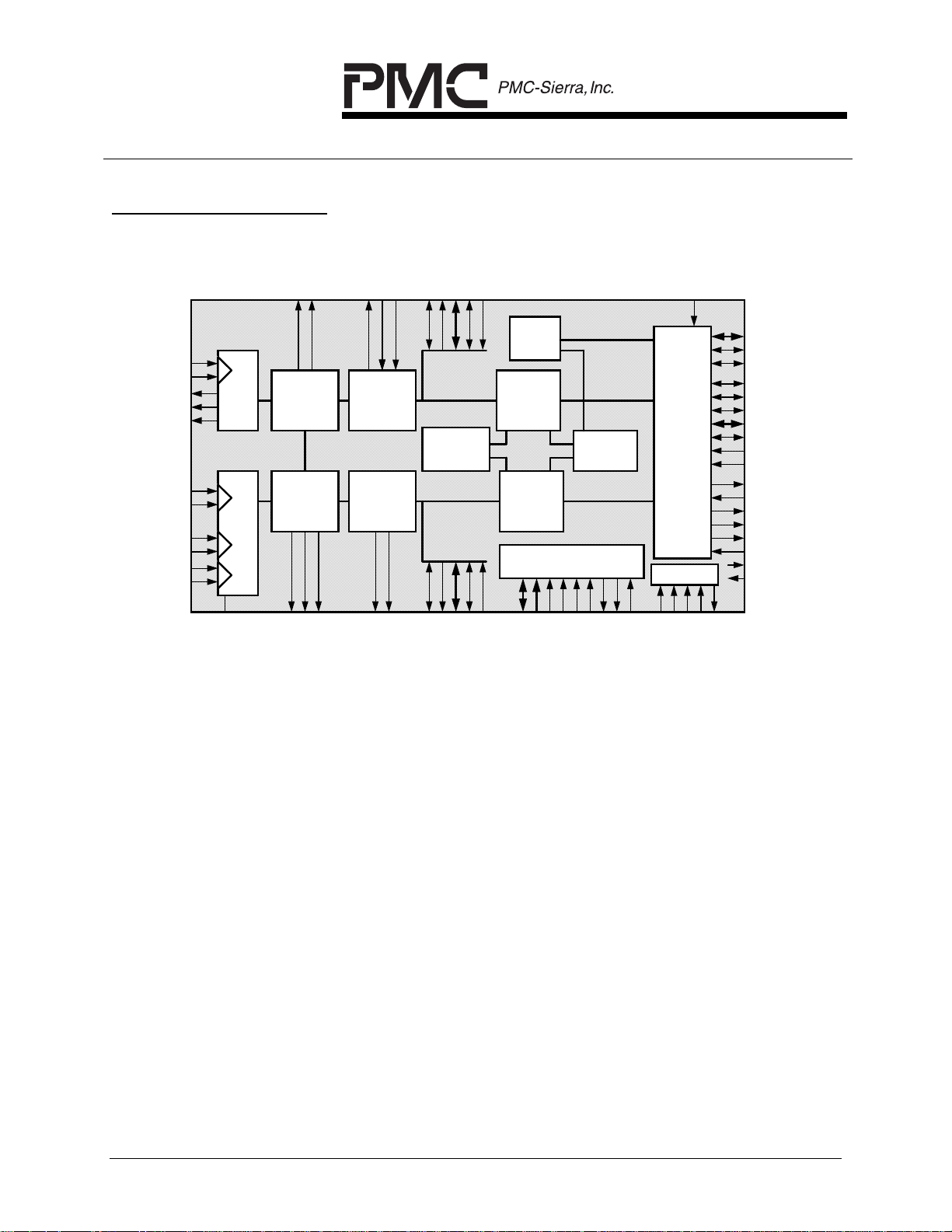

5

BLOCK DIAGRAM

TRCLK+

TRCLK-

TXC

TXD+

TXD-

RXD+

RXD-

RRCLK+

RRCLK-

ALOS+

ALOS-

Tx Line

I/F

Rx Line

I/F

LF+,LF-,LFO

TFPO

TCLK

Tx

Framer &

Overhead

Processor

Rx

Framer &

Overhead

Processor

RCLK

RALM

Tx ATM Cell

Rx ATM Cell

RFP

TGFC/TLD

TCP/TLDCLK

Processor

Processor

RGFC/RLD

RCP/RLDCLK

XOFF

TSOC

TWRENB

TDAT[7:0]

TXPHYBP

SAR

Performance

Monitor

RSOC

RRDENB

RDAT[7:0]

RXPHYBP

TFIFOFB/

TFIFOEB

Tx ATM

Traffic

Shaper

Tx ATM &

Adaptation

Layer

Processor

Rx ATM &

Adaptation

Layer

Processor

RFIFOFB

RFIFOEB/

Connection

Parameter

Microprocessor

I/F

ALE

CSB

WRB

A[8:0]

D[15:0]

Store

RDB

INTB

RSTB

MPENB

ROMP

PCI

DMA

Controller

JTAG Port

TCK

TMS

TRSTB

TDI

AD[31:0]

C/BEB[3:0]

PAR

FRAMEB

TRDYB

IRDYB

STOPB

DEVSELB

IDSEL

LOCKB

REQB

GNTB

PERRB

SERRB

PCIINTB

PCICLK

PCICLKO

SYSCLK

TDO

Normal Operating Mode (Slave Operation)

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

TFPO

TCLK

TGFC/TLD

TCP/TLDCLK

XOFF

TSOC

TWRENB

TXPHYBP

TRCLK+

TRCLK-

TXC

TXD+

TXD-

RXD+

RXD-

RRCLK+

Tx Line

I/F

Rx Line

I/F

Tx

Framer &

Overhead

Processor

Rx

Framer &

Overhead

Processor

Tx ATM Cell

Processor

Rx ATM Cell

Processor

SAR

Performance

Monitor

RRCLK-

ALOS+

ALOS-

RFP

RCLK

LF+,LF-,LFO

RALM

RGFC/RLD

RCP/RLDCLK

RSOC

RRDENB

RXPHYBP

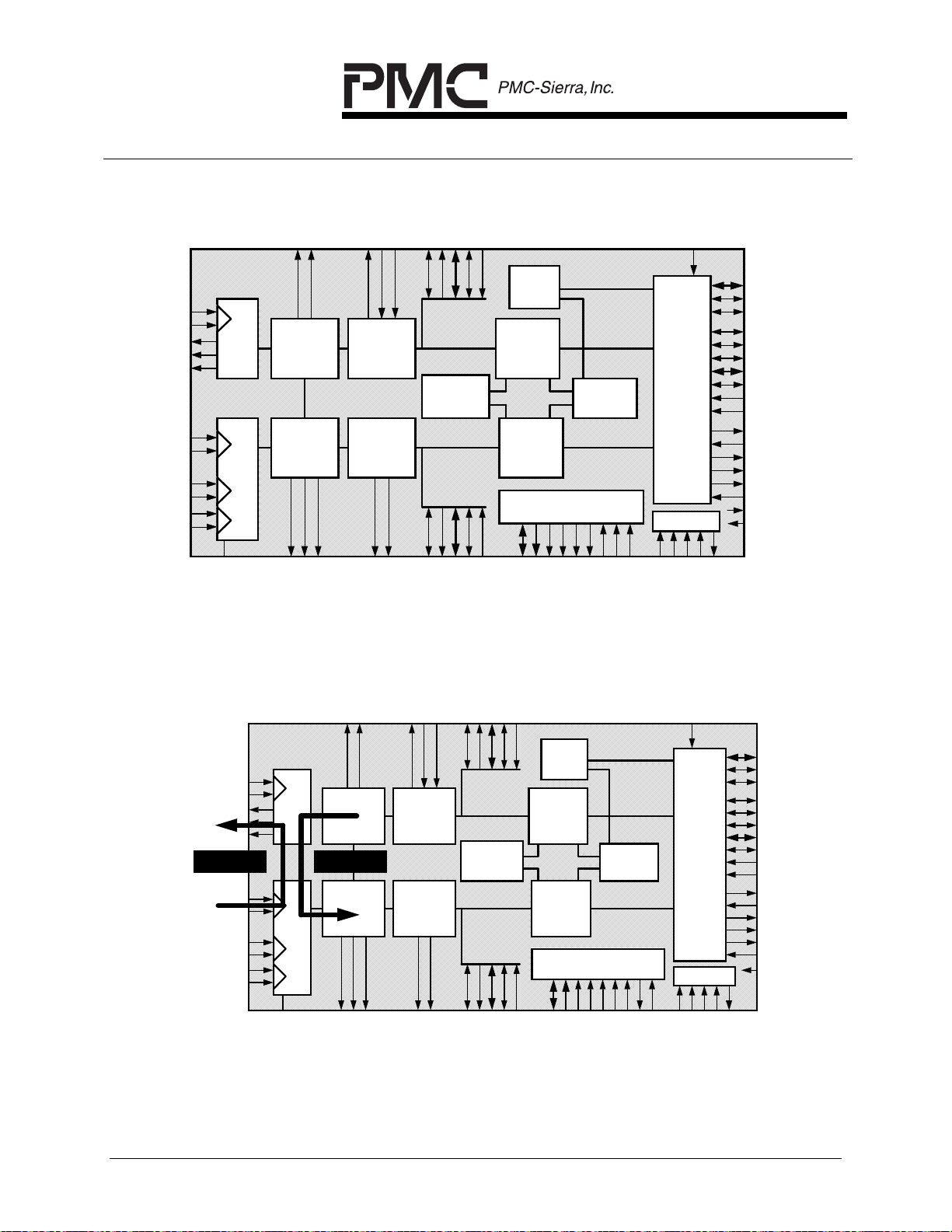

Normal Operating Mode ( Master Operation)

TFIFOFB/

TFIFOEB

TDAT[7:0]

Tx ATM &

Adaptation

Processor

Rx ATM &

Adaptation

Processor

RFIFOFB

RFIFOEB/

RDAT[7:0]

Tx ATM

Traffic

Shaper

Layer

Layer

Microprocessor

CS2B

D[7:0]

A[15:0]

Connection

Parameter

Store

I/F

RDB

WRB

CS1B

INTB

RSTB

MPENB

ROMP

PCI

DMA

Controller

JTAG Port

TCK

TMS

TRSTB

TDI

AD[31:0]

C/BEB[3:0]

PAR

FRAMEB

TRDYB

IRDYB

STOPB

DEVSELB

IDSEL

LOCKB

REQB

GNTB

PERRB

SERRB

PCIINTB

PCICLK

PCICLKO

SYSCLK

TDO

LINE

LOOPBACK

Loopback Modes

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

Tx Line

I/F

Rx Line

I/F

Tx

Framer &

Overhead

Processor

DIAGNOSTIC

LOOPBACK

Rx

Framer &

Overhead

Processor

Tx ATM Cell

Processor

Rx ATM Cell

Processor

SAR

Performance

Monitor

Tx ATM

Traffic

Shaper

Tx ATM &

Adaptation

Layer

Processor

Rx ATM &

Adaptation

Layer

Processor

Microprocessor

Connection

Parameter

Store

I/F

PCI

DMA

Controller

JTAG Port

8

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

6

DESCRIPTION

The PM7375 LASAR-155 Local ATM Segmentation and Reassembly & Physical

Layer device is a monolithic integrated circuit that implements SONET/SDH

transmission convergence, ATM cell mapping, ATM Adaptation Layer, and PCI Bus

memory management functions for a 155.52 or 51.84 Mbit/s ATM User Network

Interface.

The LASAR-155 receives SONET/SDH frames via a bit serial interface, recovers

clock and data, and processes section, line, and path overheads. It performs

framing (A1, A2), descrambling, detects alarm conditions, and monitors section, line,

and path bit interleaved parity (B1, B2, B3), accumulating error counts at each level

for performance monitoring purposes. Line and path far end block error indications

(Z2, G1) are also accumulated. The LASAR-155 interprets the received payload

pointers (H1, H2) and extracts the synchronous payload envelope which carries the

received ATM cell payload.

The LASAR-155 frames to the ATM payload using cell delineation. Payload

descrambling, HEC single bit error correction, cell filtering based on HEC errors and

idle/unassigned cell filtering is provided. The Generic Flow Control (GFC) field is

extracted from all received cell headers and serialized out a dedicated port. Counts

of received ATM cell headers that are in error and uncorrectable, cell headers that

are errored and correctable and all passed cells are accumulated independently for

performance monitoring purposes.

The LASAR-155 supports the simultaneous reassembly and Common Part

Convergence Sublayer (CPCS) processing for 128 open Virtual Circuits (VCs). All

receive VC parameters are stored locally in the LASAR-155 device to reduce

overhead traffic on the PCI Host bus. The LASAR-155 takes all received error free

cells and passes or blocks the cell based on an open VC. Passed cells are treated

as management, control or user cells. Management and control cell payloads are

optionally checked with a CRC-10 polynomial and are optionally DMA'd to receive

ready queues in packet memory.

User cells are associated with an open VC and DMA'd to reassembly queues in

packet memory. Once a packet is reassembled and verified using a CRC-32

polynomial, the entire packet is linked into a receive ready queue. The LASAR-155

alerts the PCI Host that there are reassembled packets or cells in a receive ready

queue by asserting an interrupt on the PCI bus.

All transmit VC parameters are stored in an internal transmit parameter table to

reduce overhead traffic on the PCI bus. After a PCI Host sets up a connection using

the transmit parameter table, the PCI Host can provide packets to transmit using a

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

high or low priority ready queue. The LASAR-155 automatically appends the AAL-5

trailer, segments the packet and subjects the cells to either peak cell rate or

sustainable cell rate enforcement.

The LASAR-155 generates most of a cell's header using the transmit parameter

table. The generic flow control (GFC) bits may optionally be inserted using a

dedicated serial port. The header error code (HEC) is automatically calculated and

inserted. The cell payload is optionally scrambled. Generated transmit cells are

automatically inserted into a STS-3c (STM-1) or STS-1 SONET/SDH Synchronous

Payload Envelope (SPE). In the absence of transmit cells, the LASAR-155

automatically inserts Idle/unassigned cells into the SPE.

The LASAR-155 transmits SONET/SDH frames, via a bit serial interface, and

formats SONET section, line, and path overhead appropriately. It performs framing

pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section,

line, and path bit interleaved parity (B1, B2, B3) as required to allow performance

monitoring at the far end. Line and path far end block error indications (Z2, G1) are

also inserted. The LASAR-155 generates the payload pointer (H1, H2) and inserts

the synchronous payload envelope which carries the ATM cell payload.

For system diagnostics, the LASAR-155 supports the insertion of a variety of errors

into the transmit stream, such as framing pattern errors, bit interleaved parity errors

and illegal pointers.

No auxiliary line clocks are required directly by the LASAR-155 as it is capable of

synthesizing the line rate transmit clock and recovering the receive clock

either a 19.44 MHz or 6.48 MHz reference clock

. The LASAR-155 is configured,

using

controlled and monitored via either the generic microprocessor port interface in

slave mode or the PCI bus interface in master mode. In slave mode, a mailbox

scheme with shared buffers is provided for communication between the

microprocessor and PCI Host.

The LASAR-155 can interface with external devices when the generic

microprocessor port interface is configured for master mode operation. In this mode

the PCI Host configures, controls and monitors the LASAR-155 and the external

devices.

The LASAR-155 is implemented in low power, 0.6 micron, +5 Volt CMOS

technology. It has TTL and pseudo ECL (PECL) compatible inputs and outputs and

is packaged in a 208 pin copper slugged plastic QFP package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

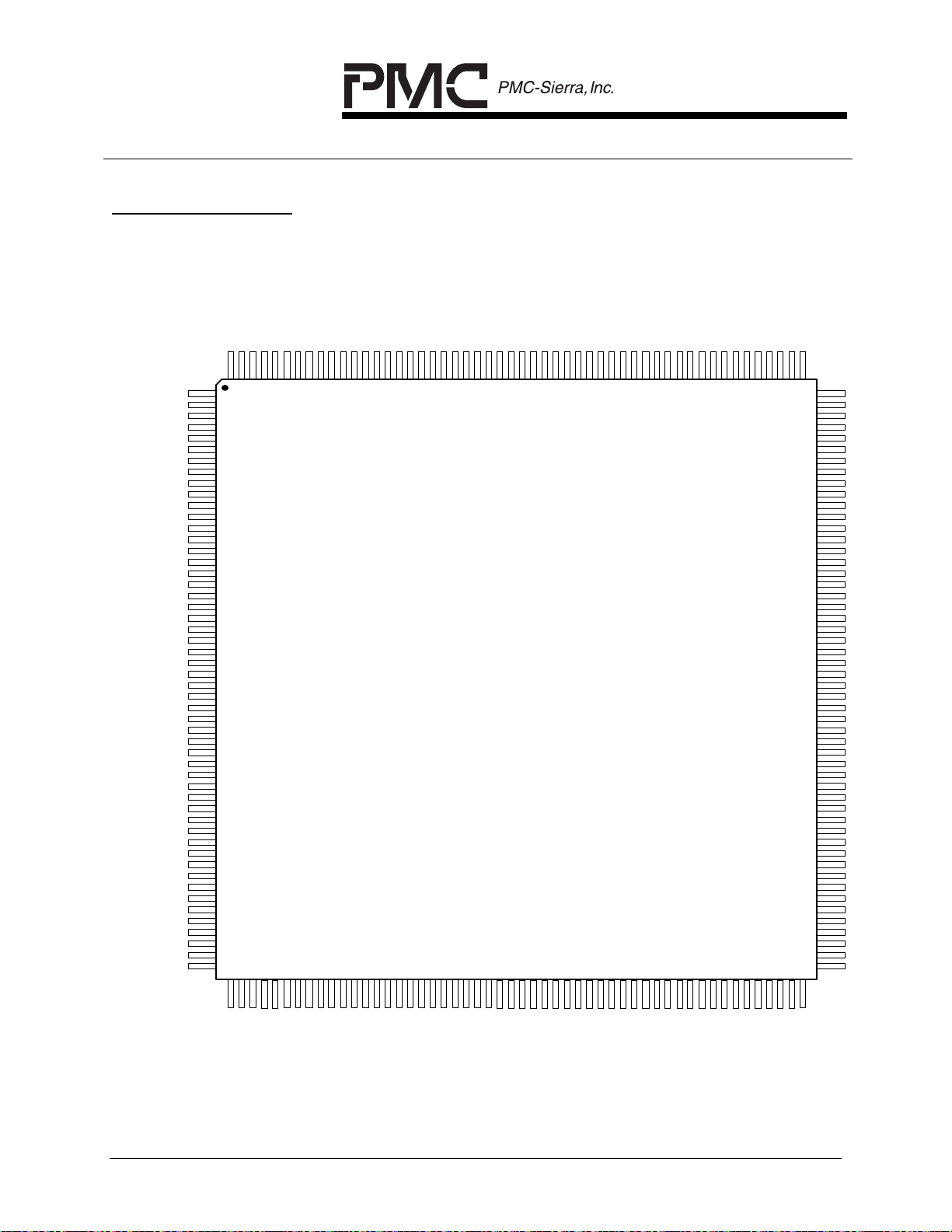

7

PIN DIAGRAM

The LASAR-155 is packaged in a 208 pin slugged plastic QFP package having a

body size of 28 mm by 28 mm and a pin pitch of 0.5 mm.

PIN 1

AD[27]

AD[26]

VSS_AC

VDD_AC

AD[25]

AD[24]

C/BEB[3]

VSS_AC

VSS_DC

VDD_DC

VDD_AC

IDSEL

AD[23]

AD[22]

AD[21]

VSS_AC

VDD_AC

AD[20]

AD[19]

AD[18]

VSS_AC

VDD_AC

AD[17]

AD[16]

C/BEB[2]

VSS_AC

VSS_DC

VDD_DC

FRAMEB

IRDYB

TRDYB

DEVSELB

STOPB

LOCKB

PERRB

SERRB

PAR

VDD_AC

C/BEB[1]

AD[15]

AD[14]

VSS_AC

VDD_AC

AD[13]

AD[12]

AD[11]

VSS_AC

VDD_AC

AD[10]

AD[9]

AD[8]

VSS_AC

PIN 52

VDD_AC

AD[28]

PIN 208

Index

VSS_AC

AD[30]

AD[29]

AD[31]

VDD_AC

REQB

GNTB

VSS_DC

VDD_DC

PCICLK

D[15]/A[15]

PCICLKO

PCIINTB

D[13]/A[13]

D[14]/A[14]

D[12]/A[12]

D[10]/A[10]

D[11]/A[11]

VSS_AC

A[8]

VSS_DC

VDD_DC

A[7]

D[9]/A[9]

A[6]

VDD_AC

PM7375

LASAR-155

TOP VIEW

A[5]

A[4]

A[3]

A[2]

A[1]

A[0]

D[8]

D[7]

D[6]

D[5]

D[4]

D[3]

D[2]

D[1]

VSS_DC

VDD_DC

D[0]

WRB

RDB

ALE/CS2B

CSB/CS1B

INTB

TFPO

RALM

PIN 157

PIN 156

VSS_DC

TCLK

VDD_DC

MPENB

RXPHYBP

RAVS1

RAVD2

LF+

LFLFO

RAVS2

RAVD1

RAVS4

RRCLKRRCLK+

RAVD4

RAVD3

ALOSALOS+

RXDRXD+

RAVS3

VSS_AC

VDD_AC

ROMP

VSS_DC

VSS_DC

VDD_DC

TXVSS

TXDTXD+

TXC

RSTB

TXVDD

TAVS3

TRCLKTRCLK+

TAVD3

TAVS2

TAVD2

TAVS1

TAVD1

XOFF

TGFC/TLD

TCP/TLDCLK

RGFC/RLD

RCP/RLDCLK

RFP

RRDENB

RSOC

RDAT[0]

RDAT[1]

PIN 105

TDI

TCK

TMS

VSS_DC

VDD_DC

PIN 53

AD[7]

C/BEB[0]

VDD_AC

AD[6]

VSS_AC

AD[5]

AD[4]

VDD_AC

AD[3]

VSS_AC

VDD_AC

AD[1]

AD[2]

AD[0]

VSS_AC

TDO

TRSTB

TDAT[7]

TDAT[6]

VSS_AC

VSS_DC

TFIFOFB/TFIFOEB

SYSCLK

VDD_DC

VDD_AC

TDAT[5]

TDAT[4]

VSS_DC

TDAT[1]

TDAT[2]

TDAT[3]

TSOC

TDAT[0]

TWRENB

RCLK

VSS_DC

VSS_AC

TXPHYBP

RFIFOEB/RFIFOFB

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

RDAT[7]

VDD_DC

VDD_AC

11

RDAT[5]

RDAT[4]

RDAT[6]

RDAT[2]

RDAT[3]

PIN 104

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

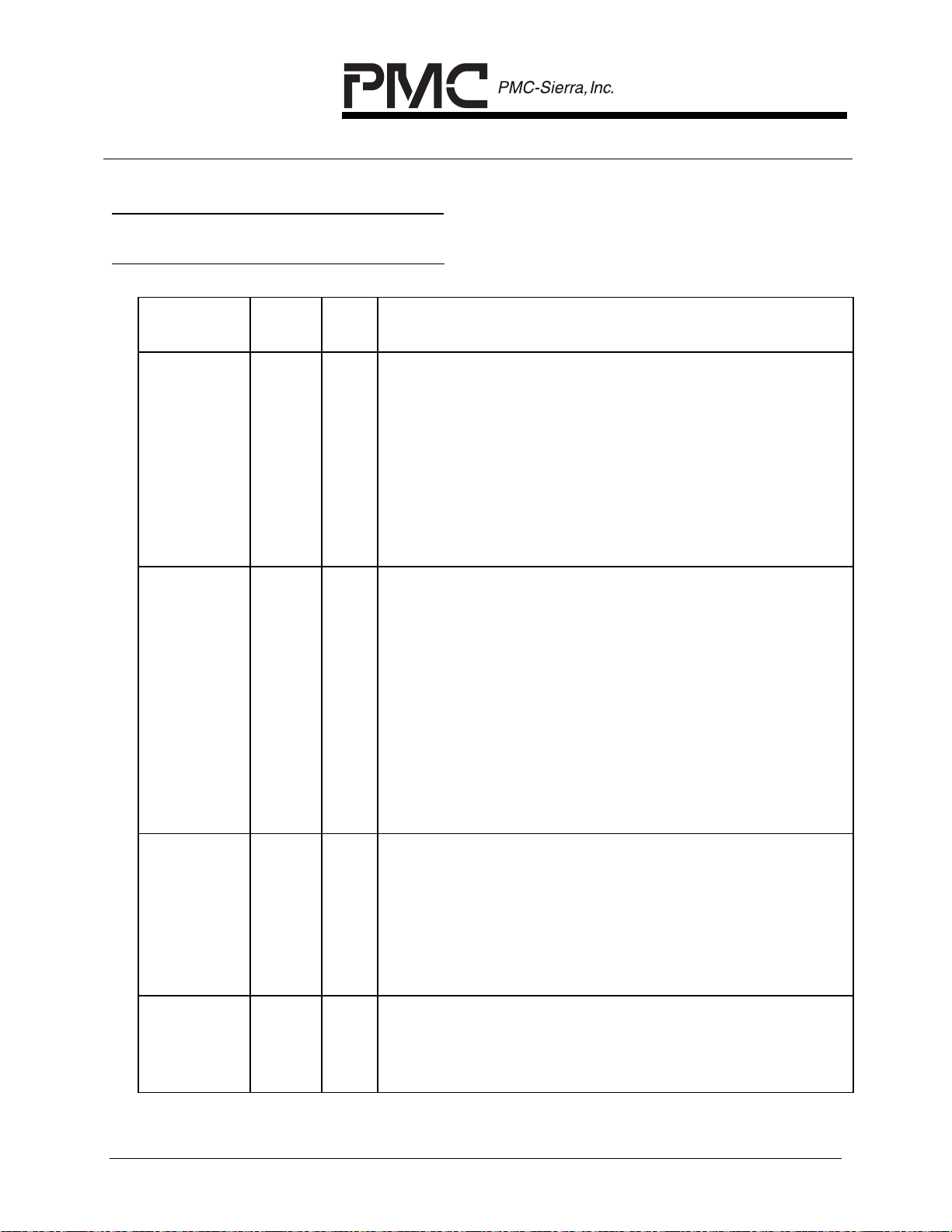

8

PIN DESCRIPTION (TOTAL 208)

8.1 Line Side Interface Signals (24)

Pin

Name

RXD+

RXD-

Type

PECL

Input

Pin

No.

136

137

Feature

The receive differential data inputs (RXD+, RXD-)

contain the 155.52 Mbit/s receive STS-3c (STM-1)

stream or the 51.84 Mbit/s receive STS-1 stream.

RXD+/- are sampled on the rising edge of RRCLK+/when clock recovery is disabled (the falling edge may

be used by reversing RRCLK+/-), otherwise the

receive clocks are recovered from the RXD+/- bit

stream. RXD+/- is expected to be NRZ encoded.

RRCLK+

RRCLK-

PECL

Input

142

143

The receive differential reference clock inputs

(RRCLK+, RRCLK-) contain a jitter-free 1 9.44 MHz or

6.48 MHz reference clock when clock recovery is

enabled. When clock recovery is bypassed, RRCLK+/is nominally a 155.52 MHz or 51.84 MHz, 50% duty

cycle clock and provide timing for the LASAR-155

receive functions. In this case, RXD+/- is sampled on

the rising edge of RRCLK+/-.

Clock recovery bypass is selectable using the RBYP

bit in the LASAR-155 Master Configuration register.

ALOS+

ALOS-

PECL

Input

138

139

The analog loss of signal (ALOS+/-) differential inputs

are used to indicate a loss of receive signal power.

When ALOS+/- is asserted, the data on the receive

data (RXD+/-) pin will be squelched and the phase

locked loop shall switch to the reference clock

(RRCLK+/-) to keep the recovered clock in range.

These inputs must be DC coupled.

LF+,

LF-,

LFO

Analog 149

148

147

Passive components connected to the recovery loop

filter (LF+, LF- and LFO) pins determine the dynamics

of the clock recovery unit. Refer to the Operation

section for details.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

RCLK Output 96 The receive clock (RCLK) output provides a timing

reference for the LASAR-155 receive line interface

outputs. RCLK is a 19.44 MHz or 6.48 MHz, nominally

50% duty cycle clock. RCLK is a divide by eight of the

recovered clock or the RRCLK+/- inputs as

determined using the RBYP bit in the LASAR-155

Master Configuration register.

RALM Output 157 The receive alarm (RALM) output indicates the state

of the receive framing. RALM is low if no receive

alarms are active. RALM is high if loss of signal

(LOS), line AIS, path AIS, loss of frame (LOF), loss of

pointer (LOP) or loss of cell delineation (LCD) is

detected. RALM is updated on the falling edge of

RCLK.

RFP Output 109 The receive frame pulse (RFP) output is an 8 kHz

signal derived from the receive line clock. RFP is

pulsed high for one RCLK cycle every 2430 RCLK

cycles for STS-3c (STM-1) or every 810 RCLK cycles

for STS-1. A single discontinuity in RFP position

occurs if a change of frame alignment occurs.

TRCLK+

TRCLK-

PECL

Input

120

121

The transmit differential reference clock inputs

(TRCLK+, TRCLK-) are a jitter-free 19.44 MHz or 6.48

MHz reference clock when clock synthesis is enabled.

When clock synthesis is bypassed, TRCLK+/- is

nominally a 155.52 MHz or 51.84 MHz, 50% duty

cycle clock. This clock provides timing for the

LASAR-155 transmit functions. TRCLK+/- may be left

unconnected when LASAR-155 loop timing is enabled

using the LASAR-155 Master Control Register.

TXC Output 125 The transmit clock (TXC) output is available when

STS-1 (51.84 Mbits/s) mode of operation is selected

using the LASAR-155 Master Configuration register.

When STS-3c (STM-1) mode of operation is selected,

TXC is held low. TXD+/- are updated on the falling

edge of TXC.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

PM7375 LASAR-155

DATA SHEET

PMC-931127 ISSUE 6 LOCAL ATM SAR & PHYSICAL LAYER

TXD+

TXD-

Output 126

127

The transmit differential data outputs (TXD+, TXD-)

contain the 155.52 Mbit/s transmit STS-3c (STM-1)

stream or the 51.84 Mbit/s transmit STS-1 stream.

When the STS-1 stream is selected, TXD+/- are

updated on the falling edge of TXC. TXD+/- is NRZ

encoded.

TCLK Output 155 The transmit byte clock (TCLK) is either a 19.44 MHz

or a 6.48 MHz clock derived from the transmit line

rate.

TFPO Output 158 The active high framing position output (TFPO) signal

is an 8 kHz timing marker for the transmitter. TFPO

goes high for a single TCLK period once every 2430 in

STS-3c (STM-1) mode or 810 in STS-1 mode TCLK

cycles. TFPO is updated on the rising edge of TCLK.

RGFC/RLD Output 111 The RGFC/RLD output is a dual function output

controlled using the UNI_POTS bit in the LASAR-155

Master Configuration register.

When the UNI_POTS bit is low, the receive generic

flow control (RGFC) output presents the extracted GFC

bits in a serial stream. The four GFC bits are

presented for each received cell, with the RCP output

indicating the position of the most significant bit. The

updating of RGFC by particular GFC bits may be

disabled through the RACP Configuration register. The

serial link is forced low if cell delineation is lost. RGFC

is updated on the rising edge of RCLK.

When the UNI_POTS bit is high, the receive line DCC

(RLD) signal contains the serial line data

communications channel (D4 - D12) extracted from the

incoming stream. RLD is updated on the falling edge

of RLDCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

Loading...

Loading...