PMC-Sierra,Inc.

ATM SAR and PHY Processor for PCI Bus

PM7375

LASAR-155

FEATURES

• Combines PHY, ATM, AAL5, and PCI

DMA Controller on a single device to

simplify the design, programming, and

manufacturing of ATM adapters.

• Conforms to ATM Forum UserNetwork Interface (UNI) Specification

Version 3.1, Bellcore Standard TANWT-001113, and ITU-T

Recommendations I.432 and I.363.

HOST INTERFACE

• Provides a 32-bit, 33 MHz Peripheral

Component Interconnect (PCI) Local

Bus Specifications Version 2.1

interface and supports both busmaster and bus-slave access modes.

Other 32-bit system buses can be

accommodated using external glue

logic.

• Implements an effic ient DMA controlle r

to manage the transfer of packets

between the SAR engine and the host

memory with minimum PCI Host

intervention. There is no need for a

local packet memory.

• The transmit and receive DMA

channels support scatter/g ath er

capabilities where a packet can be

stored in non-contiguous buffers.

• Provides an 8-cell FIFO in the transmit

direction and a 96-cell FIFO in the

receive direction to allow for up to

270 µs of PCI bus latency in the

receive direction.

PHYSICAL LAYER

• Incorporates the industry standard

PMC PM5346 S/UNI

SONET and SDH interfaces at STS3c/STM-1 (155.52 Mb/s) and STS-1

(51.84 Mb/s) rates.

• Provides on-chip clock recovery and

clock synthesis units that are com pliant

with Bellcore TR-NWT-00 0253 Is sue 2

and ITU-T Recommendation G.958

jitter requirements.

• Performs SONET/SDH framer,

overhead, and cell processing

functions at STS-3c/STM-1 and STS-1

rates.

®

-LITE to provide

• Provides leaky bucket Peak Cell Rate

(PCR) enforcement us ing eight

programmable peak queues coupled

with sub-rate control on a per-VC

basis.

• Implements Sustainable Cell Rate

(SCR) enforcement using a token

generation mechanism on a per-VC

basis.

• Provides an internal VC parameter

storage for both the 128 transmit and

128 receive VCs to simplify the design

of the ATM adapter and to sustain a

high data throughput rate.

MULTIPURPOSE PORT

• In bypass mode, provides an 8-bit

SCI-PHY™ or UTOPIA-compliant port

to connect to an external physical layer

processor such as PM7345 S/UNIPDH™ for DS3/E3 UNI.

• In non-bypass mode, supports the

insertion and extract ion of Const ant Bit

Rate (CBR) cells that carry encoded

video and audio signals.

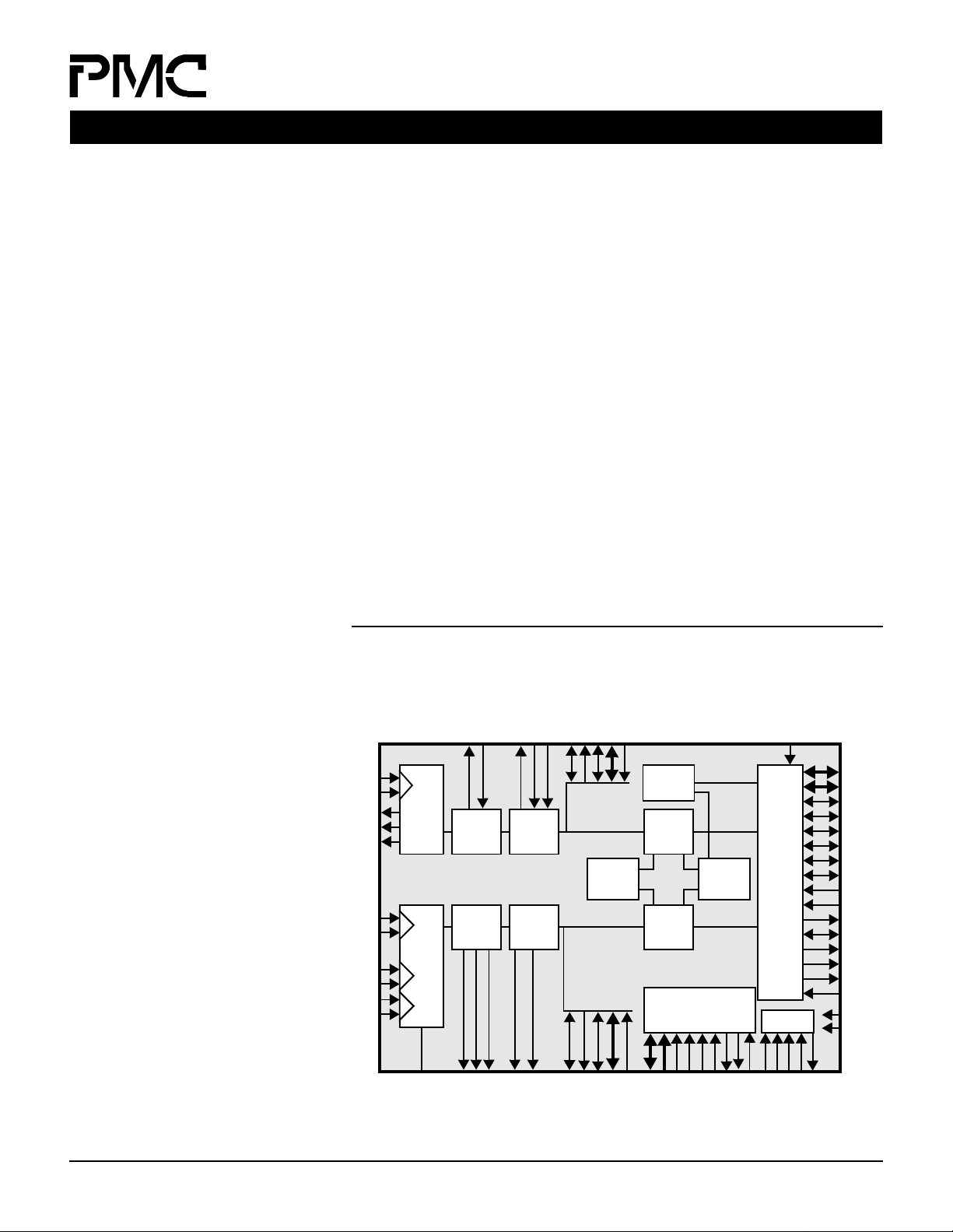

BLOCK DIAGRAM

TCP/TLDCLK

TGFC/TLD

Transmit

ATM Cell

Processor

Receive

ATM Cell

Processor

XOFF

TXPHYBP

TRCLK+

TRCLK-

TXC

TXD+

TXD-

RXD+

RXD-

RRCLK+

RRCLK-

ALOS+

ALOS-

Transmit

Line

Interface

Receive

Line

Interface

TCLK

TFPO

Transmit

Framer and

Overhead

Processor

Receive

Framer and

Overhead

Processor

MICROPROCESSOR INTERFACE

• In slave mode, provides a gene ric 8-bit

microprocessor port for the

configuration, contro l, and mon ito rin g

by an optional microprocessor.

• In master mode, allows for the control

of two exte rnal devices without glue

logic.

PACKAGING

• Provides a standard 5-signal P1149.1

JTAG test por t for boundary scan

board test purposes.

• Implemented in low power, 0.6 mic ron,

+5 V CMOS technology with TTL and

Pseudo ECL (PECL) compat ible inputs

and outputs.

• Packaged in 208-pin Pla sti c Q ua d Fl at

Pack (PQFP) package.

APPLICATIONS

• ATM Workstations and Adapters

• ATM Bridges, Switches, and Hubs

• Multimedia Terminals

TDAT[7:0]

TSOC

TWRENB

TFIFOFB/TFIFOEB

Transmit

ATM Traffic

Shaper

Transmit

ATM and

Adaptation

Processor

SAR

Performance

Monitor

Receive

ATM and

Adaptation

Processor

Microprocessor

Connection

Parameter

Interface

Store

PCI

DMA

Controller

JTAG Port

ROMP

AD[31:0]

C/BEB[3:0]

PAR

FRAMEB

TRDYB

IRDBY

STOPB

DEVSELB

IDSEL

LOCKB

REQB

GNTB

PERRB

SERRB

PCIINTB

PCICLK

PCICLKO

SYSCLK

ATM AND ADAPTATION LAYERS

• Supports the simultaneo us

segmentation and reassembly of 128

open Virtual Circuits (VCs) in both

LF+, LF-, LFO

RCLK

RFP

RALM

RGFC/RLD

RCP/RLDCLK

RSOC

RRDENB

RDAT[7:0]

RXPHYBP

RFIFOEB/

transmit and receive directions.

PMC-931138 (R6) © 1998 PMC-Sierra, Inc. October, 1998

ALE

CSB

RDB

INTB

WRB

A[8:0]

D[15:0]

RFIFOFB

RSTB

MPENB

TDI

TCK

TMS

TRSTB

TDO

ATM SAR and PHY Processor for PCI Bus

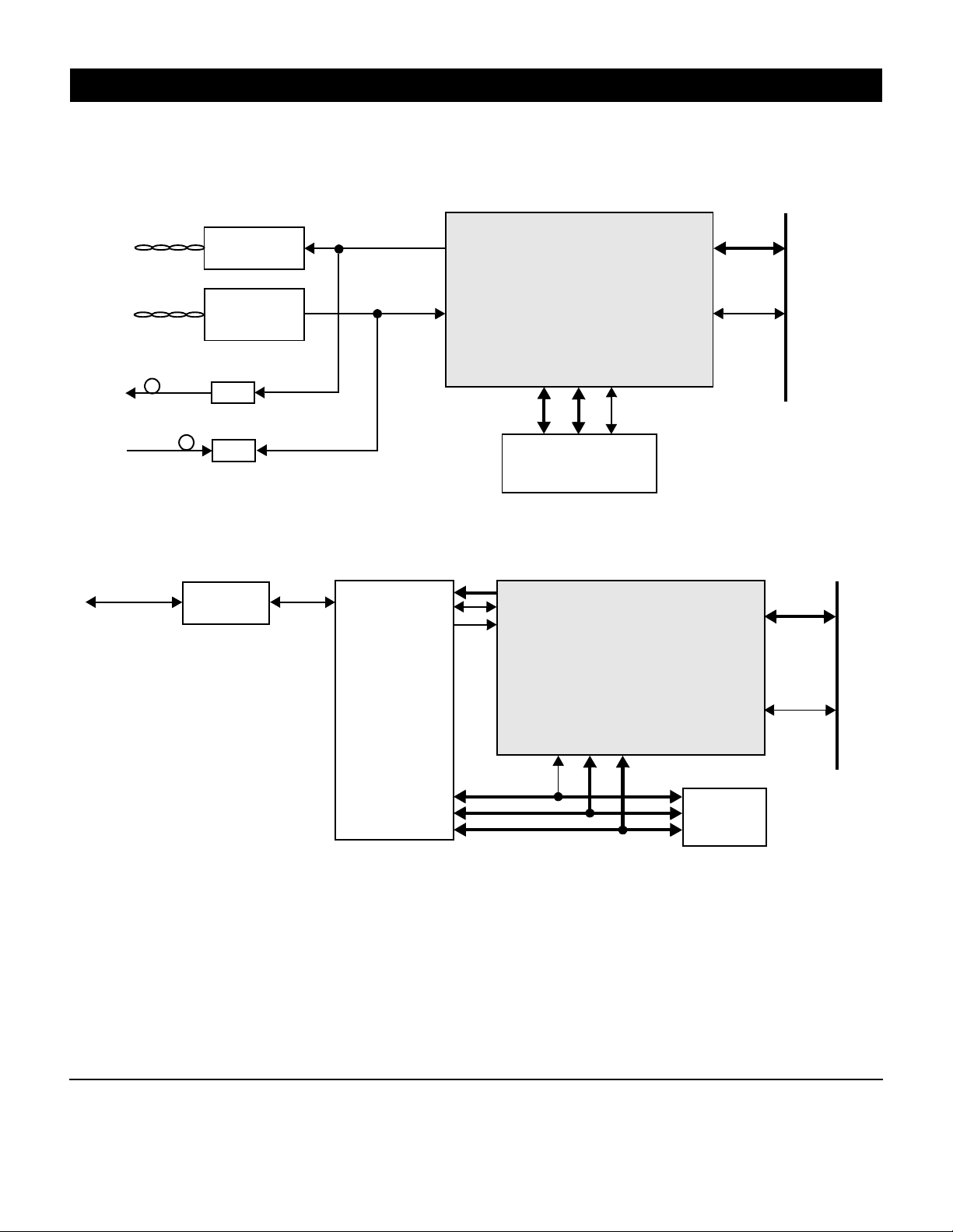

TYPICAL APPLICATIONS

ATM ADAPTER FOR PCI BUS

PM7375 LASAR-155

UTP-5 Facility

Fiber Facility

Line Driver and

Transformer

Transformer,

Equalizer, and

Line Receiver

Or

E/O

O/E

TXD+/-

RXD+/-

PM7375

LASAR-155 ATM SAR and PHY

LASAR-155

Processor for PCI Bus

A[15:0]

D[7:0]

Optional Microprocessor

INTERFACE TO EXTERNAL PHYSICAL LAYER PROCESSOR (S/UNI-PDH)

TDAT[7:0]

RDAT[7:0]

controls

LASAR-155 A TM SAR and PHY

LASAR-155

Processor for PCI Bus

controls

A[15:0]

75Ω Coax

DS3/E3

LIU

FWDATA[7:0]

FRDATA[7:0]

PM7345

®

-PDH

S/UNI

®

SATURN

User Net-

work Interface for

PDH

Applications

controls

AD[31:0]

controls

controls

PCI Bus

AD[31:0]

PM7375

controls

D[7:0]

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

controls

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

A[7:0]

D[7:0]

All product documentation is

available on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

PCI Bus

Optional EPROM

PMC-931138 (R6)

© 1998 PMC-Sierra, Inc.

October, 1998

SATURN, SCI-PHY, and S/UNI are

trademarks of PMC-Sierra, Inc.

Loading...

Loading...