PMC-Sierra,Inc.

Quad Cell Delineation Block Device

PM7339

S/UNI®-CDB

FEATURES

• Quad cell delineation block operating

up to a maximum rate of 52 Mbit/s.

• Provides a UTOPIA Level 2compatible ATM-PHY Interface.

• Implements the Physical Layer

Convergence Protocol (PLCP) for DS1

transmission systems according to the

ATM Forum User Network Interface

specification and ANSI TA-TSY000773, TA-TSY-000772, and E1

transmission systems according to the

ETSI 300-269 and ETSI 300-270.

• Supports SMDS PLCP and ATM Direct

Mapping into variou s rate tran smission

systems in the following formats:

• E1 (2.048 Mbit/s) in CRC-4 and

PCM30;

• T1 (1.544 Mbit/s) in ESF and SF;

• Arbitrary Cell Rate (up to 52 Mbit/s)

with ATM Direct Mapping only.

• Uses the PMC-Sierra PM4341 T1XC,

PM4344 TQUAD, PM6341 E1XC, and

PM6344 EQUAD T1 and E1

framer/line interface chips for DS-1

and E1 applications.

• Provides programmable pseudorandom test pattern generation,

detection and analysis features.

• Provides performance monitoring

counters suitable for accumulation

periods of up to 1 second.

RECEIVER SECTION

• Provides PLCP frame synchronization,

path overhead extraction and cel l

extraction for DS1 and E1 PLCP

formatted streams.

• Provides a 50 MHz 8-bit wide or 16-bit

wide UTOPIA FIFO buffer in the

receive path with parity support, and

multi-PHY (Level 2) control signals.

• Provides ATM framing using cell

delineation. ATM cell de lineation may

optionally be disabl ed to allow all cell

bytes to pass regardless of cell

delineati on status.

• Provides cell descrambling, header

check sequence (HC S) error detection ,

idle cell filtering, header des cra mb li ng

(for use with PPP packets), and

accumulates the number of r eceived

idle cells, the number of received cells

written to the FIFO and the number of

HCS errors.

• Provides a four cell FIFO for rate

decoupling between the line, and a

higher layer processing entity. FIFO

latency may be reduced by changing

the number of operational cell FIFOs.

• Provides programmable pseudorandom test-sequence detection and

analysis features.

TRANSMITTER SECTION

• Provides a 50 MHz 8-bit wide or 16-bit

wide Utopia FIFO buffer in the tran smit

path with parity support and mul ti-PHY

(Level 2) control signals.

• Provides optional AT M cell scrambling,

header scrambling (for use with PPP

packets), HCS generation/insertion,

programmable idle cell insertion,

diagnostics features and accumulates

transmitted cells read from the FIFO.

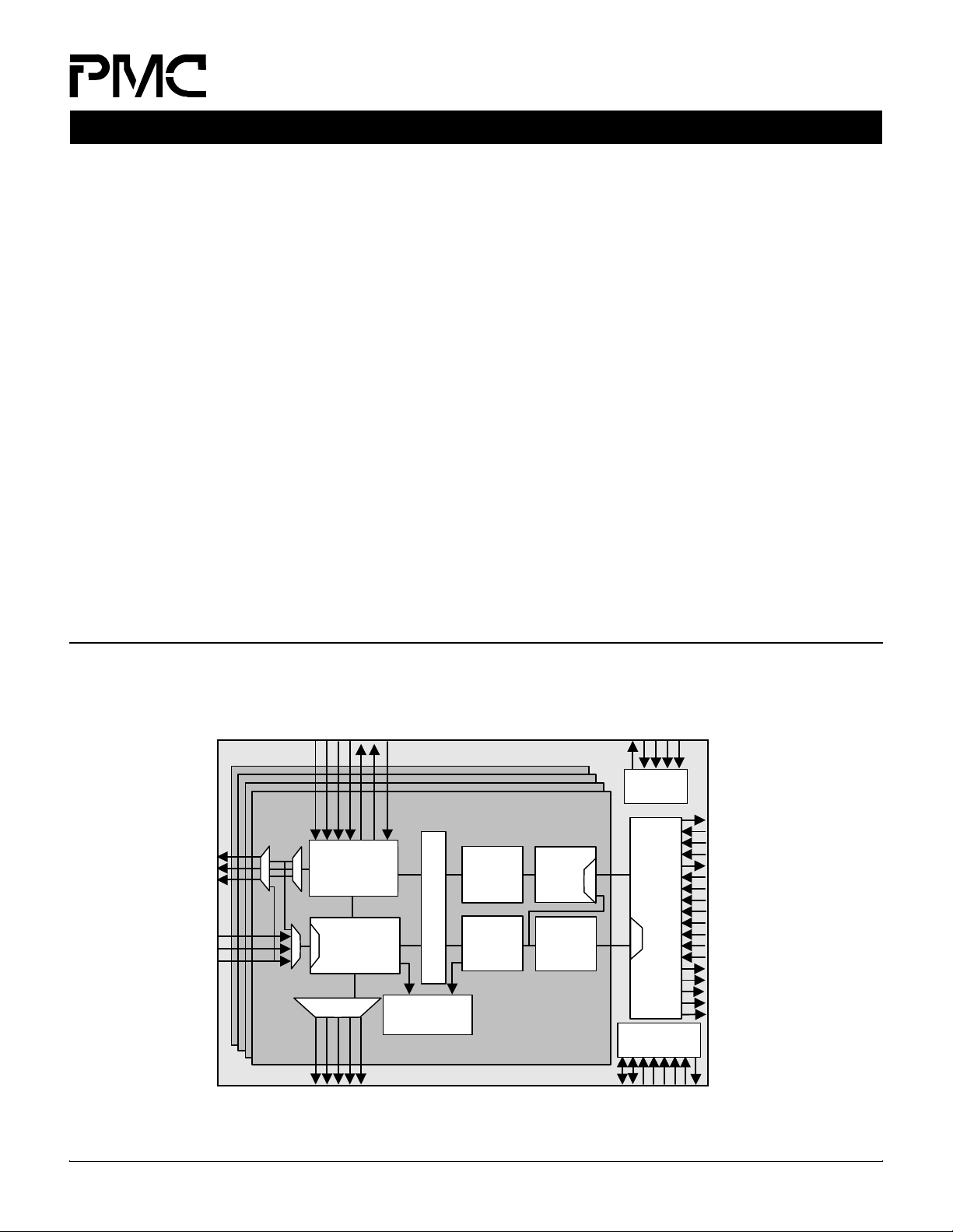

BLOCK DIAGRAM

TPOHINS[4:1]

TPOH[4:1]

TIOHM[4:1]

TICLK[4:1]

TPOHCLK[4:1]

REF8KI

TPOHFP[4:1]

TDATO[4:1]

TOHM[4:1]

TCLK[4:1]

RCLK[4:1]

RDATI[4:1]

ROHM[4:1]

PMC-2000367 (R4) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2001

SPLT

Transmit ATM

and

PLCP Framer

ATM/SPLR

Receive ATM

and PLCP

Framer

LCD [4:1]

RPOH [4:1]

RPOHFP [4:1]

RPOHCLK [4:1]

FRMSTAT [4:1]

PRGD BER Tester

CPPM

PLCP/Cell Perf.

Monitor

TXCP_50

Tx

Cell

Processor

RXCP_50

Rx

Cell

Processor

TXFF

Tx

4 Cell

FIFO

RXFF

Rx

4 Cell

FIFO

TCK

TDI

TMS

TRSTB

TDO

JTAG Test

Access

Port

System

I/F

Microprocessor

Interface

ALE

CSB

RDB

WRB

D [7:0]

A [10:0]

DTCA[4:1]

TDAT[15:0]

TPRTY

TSOC

TCA

TADR[4:0]

TENB

TFCLK

PHY_ADR[2:0]

ATM8

RFCLK

RENB

RADR[4:0]

RCA

RSOC

RPRTY

RDAT[15:0]

R

D

INTB

RSTB

4

:

1

]

A

[

C

Quad Cell Delineation Block Device

PM7339 S/UNI®-CDB

• Provides a four cell FIFO for rate

decoupling between the line and a

higher layer processing entity. FIFO

latency may be reduced by changing

the number of operational cell FIFOs.

• Provides an 8 kHz reference input for

locking the transmit PLCP frame rate

to an externally applied frame

reference.

• Provides programmable pseudorandom test sequence generation (up

32

-1 bit len g th sequences

to 2

conforming to I TU-T O. 151 stan dards).

Diagnostic abilities include single bit

error insertion or error insertion at bit

error rates ranging from 10

-1

to 10-7.

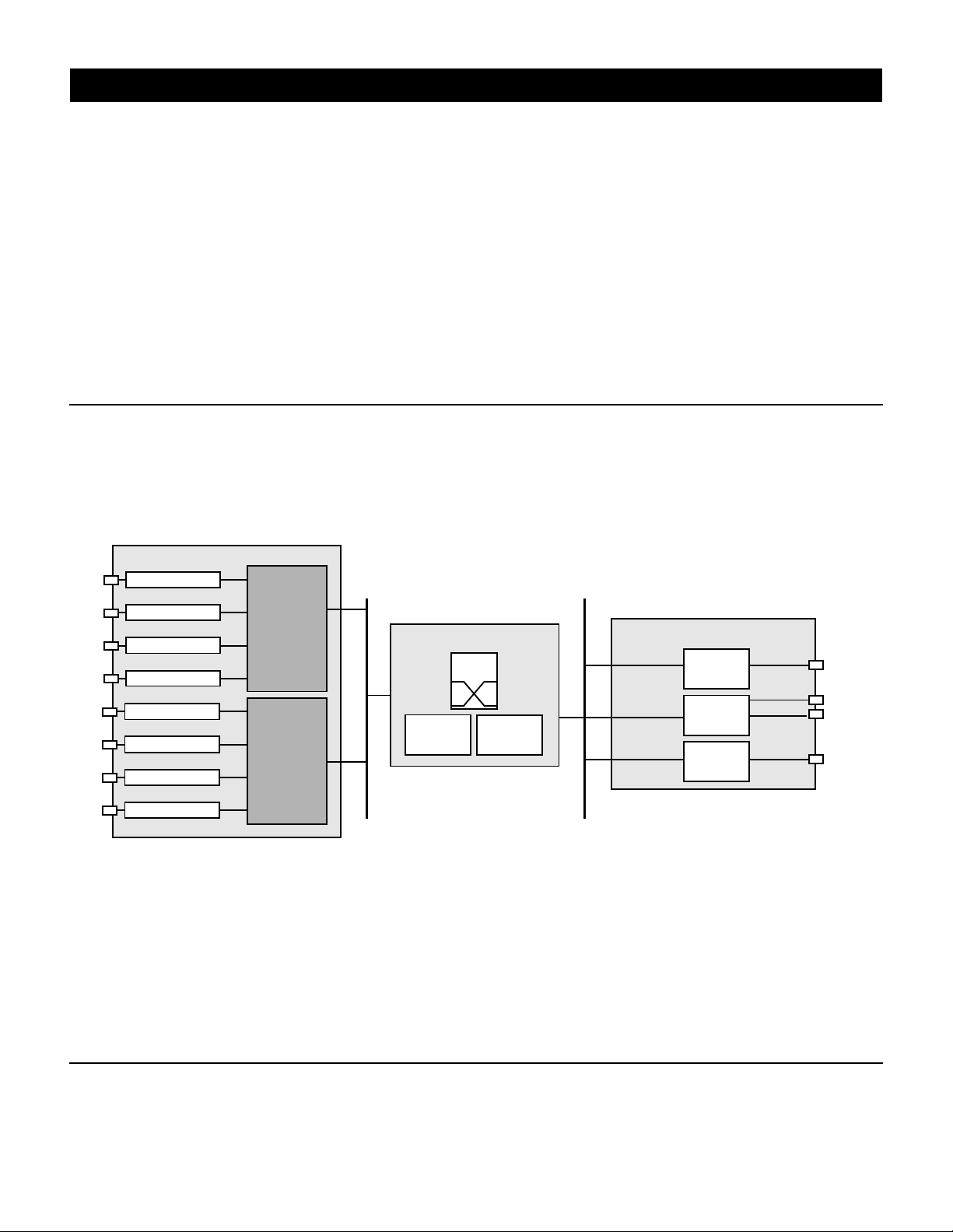

TYPICAL APPLICATION

ATM BASED DSLAM EQUIPMENT

Access Side

8 Port xDSL Card

xDSL Modem

LOOPBACK FEATURES

• Provides for diagnostic loopbac ks and

line loopbacks.

GENERAL

• Provides an 8-bit microprocessor

interface for configuration, control and

status monitoring.

• Provides a standard five signal

P1149.1 JTAG test port for boundary

scan board test purposes.

• Low power 3.3 V CMOS technology

with 5 V tolerant inputs.

• Available in a high density 256-pin

SBGA package (27 mm x 27 mm).

APPLICATIONS

• ATM Switches, Multiplexers, and

Routers.

• SMDS Switches, Multiplexers and

Routers.

• DSLAM.

• Integrated Access Devices (IAD).

xDSL Modem

xDSL Modem

xDSL Modem

xDSL Modem

xDSL Modem

xDSL Modem

xDSL Modem

PM7339

S/UNI-CDB

PM7339

S/UNI-CDB

Uplink Side

UTOPIA Bus

ATM Switch Core

PM7322

RCMP-800

Switch

Fabric

Egress

Device

UTOPIA Bus

OC-3 Line Cards

PM5346

S/UNI-LITE

PM7348

S/UNIDUAL

PM5347

S/UNI-PLUS

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

PMC-2000367 (R4)

© Copyrigh t PMC-Sierra,

Inc. 2001. All rights reserved.

S/UNI is a registered

trademark of PMC-Sierra,

Inc.

Loading...

Loading...