PMC PM7366-BI, PM7366-PI Datasheet

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

PM7366

FREEDM™-8

EIGHT CHANNEL FRAME ENGINE AND

DATALINK MANAGER

PROPRIETARY AND CONFIDENTIAL

ISSUE 4: AUGUST 2001

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

REVISION HISTORY

Issue No. Issue Date Details of Change

Issue 4 August 2001 Added patent information to legal footer, last page. Change

bars pertain to issue 3.

Issue 3 August 1999 Updated to include PBGA package option

· Addition of new pinout, pin description, and mechanical

diagram.

Incorporated Documentation Errata from PMC-980452,

“PM7366 FREEDM-8 Revision D Device Errata Sheet” Issue 4.

Issue 2 May 1998 Updated for Freedm-8 Release to Production

Issue 1 Sept. 1997 Document created for Prototype release

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

CONTENTS

1 FEATURES ....................................................................................................................... 1

2 APPLICATIONS ................................................................................................................ 3

3 REFERENCES.................................................................................................................. 4

4 APPLICATION EXAMPLES .............................................................................................. 5

5 BLOCK DIAGRAM ............................................................................................................ 6

6 DESCRIPTION.................................................................................................................. 7

7 PIN DIAGRAM...................................................................................................................9

8 PIN DESCRIPTION..........................................................................................................11

9 FUNCTIONAL DESCRIPTION........................................................................................ 33

9.1 HIGH-LEVEL DATA LINK CONTROL PROTOCOL ........................................... 33

9.2 RECEIVE CHANNEL ASSIGNER ...................................................................... 34

9.2.1 LINE INTERFACE............................................................................. 34

9.2.2 PRIORITY ENCODER...................................................................... 34

9.2.3 CHANNEL ASSIGNER ..................................................................... 35

9.2.4 LOOPBACK CONTROLLER ............................................................ 35

9.3 RECEIVE HDLC PROCESSOR / PARTIAL PACKET BUFFER ........................ 35

9.3.1 HDLC PROCESSOR ........................................................................ 36

9.3.2 PARTIAL PACKET BUFFER PROCESSOR..................................... 36

9.4 RECEIVE DMA CONTROLLER ......................................................................... 38

9.4.1 DATA STRUCTURES ....................................................................... 38

9.4.2 DMA TRANSACTION CONTROLLER ............................................. 48

9.4.3 WRITE DATA PIPELINE/MUX .......................................................... 48

9.4.4 DESCRIPTOR INFORMATION CACHE........................................... 48

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE i

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

9.4.5 FREE QUEUE CACHE..................................................................... 48

9.5 PCI CONTROLLER............................................................................................ 49

9.5.1 MASTER MACHINE ......................................................................... 49

9.5.2 MASTER LOCAL BUS INTERFACE................................................. 51

9.5.3 TARGET MACHINE .......................................................................... 52

9.5.4 CBI BUS INTERFACE ...................................................................... 54

9.5.5 ERROR / BUS CONTROL................................................................ 54

9.6 TRANSMIT DMA CONTROLLER ...................................................................... 54

9.6.1 DATA STRUCTURES ....................................................................... 55

9.6.2 TASK PRIORITIES ........................................................................... 66

9.6.3 DMA TRANSACTION CONTROLLER ............................................. 66

9.6.4 READ DATA PIPELINE ..................................................................... 66

9.6.5 DESCRIPTOR INFORMATION CACHE........................................... 66

9.6.6 FREE QUEUE CACHE..................................................................... 66

9.7 TRANSMIT HDLC CONTROLLER / PARTIAL PACKET BUFFER .................... 67

9.7.1 TRANSMIT HDLC PROCESSOR..................................................... 67

9.7.2 TRANSMIT PARTIAL PACKET BUFFER PROCESSOR ................. 67

9.8 TRANSMIT CHANNEL ASSIGNER ................................................................... 69

9.8.1 LINE INTERFACE............................................................................. 70

9.8.2 PRIORITY ENCODER...................................................................... 70

9.8.3 CHANNEL ASSIGNER ..................................................................... 71

9.9 PERFORMANCE MONITOR ............................................................................. 71

9.10 JTAG TEST ACCESS PORT INTERFACE ........................................................ 71

9.11 PCI HOST INTERFACE..................................................................................... 71

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ii

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

10 NORMAL MODE REGISTER DESCRIPTION ................................................................ 76

10.1 PCI HOST ACCESSIBLE REGISTERS ............................................................. 76

11 PCI CONFIGURATION REGISTER DESCRIPTION .................................................... 216

11.1 PCI CONFIGURATION REGISTERS .............................................................. 216

12 TEST FEATURES DESCRIPTION ............................................................................... 226

12.1 TEST MODE REGISTERS .............................................................................. 226

12.2 JTAG TEST PORT ........................................................................................... 227

12.2.1 IDENTIFICATION REGISTER ........................................................ 228

12.2.2 BOUNDARY SCAN REGISTER ..................................................... 228

13 OPERATIONS ............................................................................................................... 241

13.1 EQUAD CONNECTIONS................................................................................. 241

13.2 TOCTL CONNECTIONS .................................................................................. 241

13.3 JTAG SUPPORT.............................................................................................. 242

14 FUNCTIONAL TIMING.................................................................................................. 248

14.1 RECEIVE LINK INPUT TIMING ....................................................................... 248

14.2 TRANSMIT LINK OUTPUT TIMING ................................................................ 249

14.3 PCI INTERFACE .............................................................................................. 250

14.4 BERT INTERFACE .......................................................................................... 258

15 ABSOLUTE MAXIMUM RATINGS................................................................................ 260

16 D.C. CHARACTERISTICS ............................................................................................ 261

17 FREEDM-8 TIMING CHARACTERISTICS ................................................................... 263

18 ORDERING AND THERMAL INFORMATION .............................................................. 269

19 MECHANICAL INFORMATION..................................................................................... 270

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iii

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

LIST OF REGISTERS

REGISTER 0X000 : FREEDM-8 MASTER RESET ..................................................................... 77

REGISTER 0X004 : FREEDM-8 MASTER INTERRUPT ENABLE ............................................. 79

REGISTER 0X008 : FREEDM-8 MASTER INTERRUPT STATUS.............................................. 83

REGISTER 0X00C : FREEDM-8 MASTER CLOCK / BERT ACTIVITY MONITOR AND

ACCUMULATION TRIGGER .......................................................................................... 87

REGISTER 0X010 : FREEDM-8 MASTER LINK ACTIVITY MONITOR ...................................... 89

REGISTER 0X014 : FREEDM-8 MASTER LINE LOOPBACK .................................................... 91

REGISTER 0X020 : FREEDM-8 MASTER BERT CONTROL..................................................... 93

REGISTER 0X024 : FREEDM-8 MASTER PERFORMANCE MONITOR CONTROL ................ 95

REGISTER 0X040 : GPIC CONTROL ......................................................................................... 98

REGISTER 0X100 : RCAS INDIRECT LINK AND TIME-SLOT SELECT.................................. 101

REGISTER 0X104 : RCAS INDIRECT CHANNEL DATA .......................................................... 103

REGISTER 0X108 : RCAS FRAMING BIT THRESHOLD ......................................................... 105

REGISTER 0X10C : RCAS CHANNEL DISABLE...................................................................... 107

REGISTER 0X180 : RCAS LINK #0 CONFIGURATION ........................................................... 109

REGISTER 0X184 - 0X188 : RCAS LINK #1 TO #2 CONFIGURATION.................................... 111

REGISTER 0X18C : RCAS LINK #3 CONFIGURATION............................................................113

REGISTER 0X190-0X19C : RCAS LINK #4 TO LINK #7 CONFIGURATION ............................115

REGISTER 0X200 : RHDL INDIRECT CHANNEL SELECT.......................................................117

REGISTER 0X204 : RHDL INDIRECT CHANNEL DATA REGISTER #1 ...................................119

REGISTER 0X208 : RHDL INDIRECT CHANNEL DATA REGISTER #2 .................................. 122

REGISTER 0X210 : RHDL INDIRECT BLOCK SELECT .......................................................... 124

REGISTER 0X214 : RHDL INDIRECT BLOCK DATA ............................................................... 126

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iv

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

REGISTER 0X220 : RHDL CONFIGURATION.......................................................................... 128

REGISTER 0X224 : RHDL MAXIMUM PACKET LENGTH........................................................ 130

REGISTER 0X280 : RMAC CONTROL ..................................................................................... 131

REGISTER 0X284 : RMAC INDIRECT CHANNEL PROVISIONING ........................................ 134

REGISTER 0X288 : RMAC PACKET DESCRIPTOR TABLE BASE LSW ................................ 136

REGISTER 0X28C : RMAC PACKET DESCRIPTOR TABLE BASE MSW............................... 137

REGISTER 0X290 : RMAC QUEUE BASE LSW ...................................................................... 139

REGISTER 0X294 : RMAC QUEUE BASE MSW ..................................................................... 140

REGISTER 0X298 : RMAC PACKET DESCRIPTOR REFERENCE LARGE BUFFER FREE

QUEUE START............................................................................................................. 142

REGISTER 0X29C : RMAC PACKET DESCRIPTOR REFERENCE LARGE BUFFER FREE

QUEUE WRITE............................................................................................................. 143

REGISTER 0X2A0 : RMAC PACKET DESCRIPTOR REFERENCE LARGE BUFFER FREE

QUEUE READ............................................................................................................... 144

REGISTER 0X2A4 : RMAC PACKET DESCRIPTOR REFERENCE LARGE BUFFER FREE

QUEUE END ................................................................................................................. 145

REGISTER 0X2A8 : RMAC PACKET DESCRIPTOR REFERENCE SMALL BUFFER FREE

QUEUE START............................................................................................................. 146

REGISTER 0X2AC : RMAC PACKET DESCRIPTOR REFERENCE SMALL BUFFER FREE

QUEUE WRITE............................................................................................................. 147

REGISTER 0X2B0 : RMAC PACKET DESCRIPTOR REFERENCE SMALL BUFFER FREE

QUEUE READ............................................................................................................... 148

REGISTER 0X2B4 : RMAC PACKET DESCRIPTOR REFERENCE SMALL BUFFER FREE

QUEUE END ................................................................................................................. 149

REGISTER 0X2B8 : RMAC PACKET DESCRIPTOR REFERENCE READY QUEUE START. 150

REGISTER 0X2BC : RMAC PACKET DESCRIPTOR REFERENCE READY QUEUE WRITE 151

REGISTER 0X2C0 : RMAC PACKET DESCRIPTOR REFERENCE READY QUEUE READ .. 152

REGISTER 0X2C4 : RMAC PACKET DESCRIPTOR REFERENCE READY QUEUE END..... 153

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE v

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

REGISTER 0X300 : TMAC CONTROL...................................................................................... 154

REGISTER 0X304 : TMAC INDIRECT CHANNEL PROVISIONING......................................... 156

REGISTER 0X308 : TMAC DESCRIPTOR TABLE BASE LSW ................................................ 158

REGISTER 0X30C : TMAC DESCRIPTOR TABLE BASE MSW .............................................. 159

REGISTER 0X310 : TMAC QUEUE BASE LSW ....................................................................... 161

REGISTER 0X314 : TMAC QUEUE BASE MSW ...................................................................... 162

REGISTER 0X318 : TMAC DESCRIPTOR REFERENCE FREE QUEUE START ................... 164

REGISTER 0X31C TMAC DESCRIPTOR REFERENCE FREE QUEUE WRITE .................... 165

REGISTER 0X320 : TMAC DESCRIPTOR REFERENCE FREE QUEUE READ ..................... 166

REGISTER 0X324 : TMAC DESCRIPTOR REFERENCE FREE QUEUE END ....................... 167

REGISTER 0X328 :TMAC DESCRIPTOR REFERENCE READY QUEUE START.................. 168

REGISTER 0X32C : TMAC DESCRIPTOR REFERENCE READY QUEUE WRITE................ 169

REGISTER 0X330 : TMAC DESCRIPTOR REFERENCE READY QUEUE READ .................. 170

REGISTER 0X334 : TMAC DESCRIPTOR REFERENCE READY QUEUE END..................... 171

REGISTER 0X380 : THDL INDIRECT CHANNEL SELECT...................................................... 172

REGISTER 0X384 : THDL INDIRECT CHANNEL DATA #1 ...................................................... 174

REGISTER 0X388 : THDL INDIRECT CHANNEL DATA #2 ...................................................... 177

REGISTER 0X38C : THDL INDIRECT CHANNEL DATA #3...................................................... 179

REGISTER 0X3A0 : THDL INDIRECT BLOCK SELECT .......................................................... 183

REGISTER 0X3A4 : THDL INDIRECT BLOCK DATA ............................................................... 185

REGISTER 0X3B0 : THDL CONFIGURATION.......................................................................... 187

REGISTER 0X400 : TCAS INDIRECT LINK AND TIME-SLOT SELECT .................................. 189

REGISTER 0X404 : TCAS INDIRECT CHANNEL DATA........................................................... 191

REGISTER 0X408 : TCAS FRAMING BIT THRESHOLD ......................................................... 193

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vi

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

REGISTER 0X40C : TCAS IDLE TIME-SLOT FILL DATA ......................................................... 195

REGISTER 0X410 : TCAS CHANNEL DISABLE....................................................................... 196

REGISTER 0X480 : TCAS LINK #0 CONFIGURATION............................................................ 198

REGISTER 0X484-0X488 : TCAS LINK #1 TO LINK #2 CONFIGURATION ............................ 200

REGISTER 0X48C : TCAS LINK #3 CONFIGURATION ........................................................... 202

REGISTER 0X490-0X49C : TCAS LINK #4 TO LINK #7 CONFIGURATION ........................... 204

REGISTER 0X500 : PMON STATUS......................................................................................... 206

REGISTER 0X504 : PMON RECEIVE FIFO OVERFLOW COUNT .......................................... 208

REGISTER 0X508 : PMON RECEIVE FIFO UNDERFLOW COUNT ....................................... 210

REGISTER 0X50C : PMON CONFIGURABLE COUNT #1....................................................... 212

REGISTER 0X510 : PMON CONFIGURABLE COUNT #2 ....................................................... 214

REGISTER 0X00 : VENDOR IDENTIFICATION/DEVICE IDENTIFICATION............................ 217

REGISTER 0X04 : COMMAND/STATUS................................................................................... 218

REGISTER 0X08 : REVISION IDENTIFIER/CLASS CODE ...................................................... 221

REGISTER 0X0C : CACHE LINE SIZE/LATENCY TIMER/HEADER TYPE ............................. 222

REGISTER 0X10 : CBI MEMORY BASE ADDRESS REGISTER ............................................. 223

REGISTER 0X3C : INTERRUPT LINE / INTERRUPT PIN / MIN_GNT / MAX_LAT ................. 225

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vii

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

LIST OF FIGURES

FIGURE 1 – HDLC FRAME ......................................................................................................... 33

FIGURE 2 – CRC GENERATOR ................................................................................................. 33

FIGURE 3 – PARTIAL PACKET BUFFER STRUCTURE ............................................................ 37

FIGURE 4 – RECEIVE PACKET DESCRIPTOR ......................................................................... 39

FIGURE 5 – RECEIVE PACKET DESCRIPTOR TABLE............................................................. 42

FIGURE 6 – RPDRF AND RPDRR QUEUES.............................................................................. 44

FIGURE 7 – RPDRR QUEUE OPERATION................................................................................ 46

FIGURE 8 – RECEIVE CHANNEL DESCRIPTOR REFERENCE TABLE................................... 47

FIGURE 9 – GPIC ADDRESS MAP............................................................................................. 53

FIGURE 10 – TRANSMIT DESCRIPTOR.................................................................................... 55

FIGURE 11 – TRANSMIT DESCRIPTOR TABLE........................................................................ 58

FIGURE 12 – TDRR AND TDRF QUEUES ................................................................................. 60

FIGURE 13 – TRANSMIT CHANNEL DESCRIPTOR REFERENCE TABLE .............................. 62

FIGURE 14 – TD LINKING .......................................................................................................... 65

FIGURE 15 – PARTIAL PACKET BUFFER STRUCTURE .......................................................... 68

FIGURE 16 – INPUT OBSERVATION CELL (IN_CELL) ........................................................... 238

FIGURE 17 – OUTPUT CELL (OUT_CELL).............................................................................. 239

FIGURE 18 – BI-DIRECTIONAL CELL (IO_CELL).................................................................... 239

FIGURE 19 – LAYOUT OF OUTPUT ENABLE AND BI-DIRECTIONAL CELLS....................... 240

FIGURE 20 – BOUNDARY SCAN ARCHITECTURE ................................................................ 242

FIGURE 21 – TAP CONTROLLER FINITE STATE MACHINE .................................................. 244

FIGURE 22 – UNCHANNELISED RECEIVE LINK TIMING ...................................................... 248

FIGURE 23 – CHANNELISED T1 RECEIVE LINK TIMING ...................................................... 248

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE viii

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

FIGURE 24 – CHANNELISED E1 RECEIVE LINK TIMING ...................................................... 249

FIGURE 25 – UNCHANNELISED TRANSMIT LINK TIMING.................................................... 249

FIGURE 26 – CHANNELISED T1 TRANSMIT LINK TIMING.................................................... 250

FIGURE 27 – CHANNELISED E1 TRANSMIT LINK TIMING.................................................... 250

FIGURE 28 – PCI READ CYCLE............................................................................................... 252

FIGURE 29 – PCI WRITE CYCLE............................................................................................. 253

FIGURE 30 – PCI TARGET DISCONNECT .............................................................................. 254

FIGURE 31 – PCI TARGET ABORT .......................................................................................... 254

FIGURE 32 – PCI BUS REQUEST CYCLE............................................................................... 255

FIGURE 33 – PCI INITIATOR ABORT TERMINATION ............................................................. 255

FIGURE 34 – PCI EXCLUSIVE LOCK CYCLE.......................................................................... 256

FIGURE 35 – PCI FAST BACK TO BACK ................................................................................. 258

FIGURE 36 – RECEIVE BERT PORT TIMING.......................................................................... 258

FIGURE 37 – TRANSMIT BERT PORT TIMING ....................................................................... 259

FIGURE 38 – RECEIVE LINK INPUT TIMING .......................................................................... 264

FIGURE 39 – BERT INPUT TIMING.......................................................................................... 264

FIGURE 40 – TRANSMIT LINK OUTPUT TIMING.................................................................... 265

FIGURE 41 – BERT OUTPUT TIMING...................................................................................... 266

FIGURE 42 – PCI INTERFACE TIMING.................................................................................... 267

FIGURE 43 – JTAG PORT INTERFACE TIMING...................................................................... 268

FIGURE 44 – 256 PIN ENHANCED BALL GRID ARRAY (SBGA)............................................. 270

FIGURE 45 – 272 PIN PLASTIC BALL GRID ARRAY (PBGA).................................................. 271

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ix

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

LIST OF TABLES

TABLE 1 – LINE SIDE INTERFACE SIGNALS (36)......................................................................11

TABLE 2 – PCI HOST INTERFACE SIGNALS (51)..................................................................... 15

TABLE 3 – MISCELLANEOUS INTERFACE SIGNALS (12) ....................................................... 24

TABLE 4 – PRODUCTION TEST INTERFACE SIGNALS (30) ................................................... 25

TABLE 5 – DON’T CARE SIGNALS (58) ..................................................................................... 27

TABLE 6 – NO-CONNECT SIGNALS (9)..................................................................................... 29

TABLE 7 – POWER AND GROUND SIGNALS (60).................................................................... 30

TABLE 8 – RECEIVE PACKET DESCRIPTOR FIELDS .............................................................. 39

TABLE 9 – RPDRR QUEUE ELEMENT....................................................................................... 45

TABLE 10 – RECEIVE CHANNEL DESCRIPTOR REFERENCE TABLE FIELDS...................... 47

TABLE 11 – TRANSMIT DESCRIPTOR FIELDS......................................................................... 55

TABLE 12 – TRANSMIT DESCRIPTOR REFERENCE ............................................................... 61

TABLE 13 – TRANSMIT CHANNEL DESCRIPTOR REFERENCE TABLE FIELDS ................... 62

TABLE 14 – NORMAL MODE PCI HOST ACCESSIBLE REGISTER MEMORY MAP ............... 72

TABLE 15 – PCI CONFIGURATION REGISTER MEMORY MAP............................................... 75

TABLE 16 – BIG ENDIAN FORMAT ............................................................................................ 99

TABLE 17 – LITTLE ENDIAN FORMAT....................................................................................... 99

TABLE 18 – CRC[1:0] SETTINGS ............................................................................................. 120

TABLE 19 – RPQ_RDYN[2:0] SETTINGS ................................................................................. 132

TABLE 20 – RPQ_LFN[1:0] SETTINGS .................................................................................... 133

TABLE 21 – RPQ_SFN[1:0] SETTINGS .................................................................................... 133

TABLE 22 – TDQ_RDYN[2:0] SETTINGS ................................................................................. 155

TABLE 23 – TDQ_FRN[1:0] SETTINGS .................................................................................... 155

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE x

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

TABLE 24 – CRC[1:0] SETTINGS ............................................................................................. 175

TABLE 25 – FLAG[2:0] SETTINGS............................................................................................ 180

TABLE 26 – LEVEL[3:0]/TRANS SETTINGS............................................................................. 181

TABLE 27 – TEST MODE REGISTER MEMORY MAP............................................................. 227

TABLE 28 – INSTRUCTION REGISTER ................................................................................... 228

TABLE 29 – BOUNDARY SCAN CHAIN.................................................................................... 228

TABLE 30 – FREEDM–EQUAD CONNECTIONS ..................................................................... 241

TABLE 31 – FREEDM–TOCTL CONNECTIONS ...................................................................... 241

TABLE 32 – FREEDM-8 ABSOLUTE MAXIMUM RATINGS ..................................................... 260

TABLE 33 – FREEDM-8 D.C. CHARACTERISTICS ................................................................. 261

TABLE 34 – FREEDM-8 LINK INPUT (FIGURE 38, FIGURE 39) ............................................. 263

TABLE 35 – FREEDM-8 LINK OUTPUT (FIGURE 40, FIGURE 41) ......................................... 264

TABLE 36 – PCI INTERFACE (FIGURE 42).............................................................................. 266

TABLE 37 – JTAG PORT INTERFACE (FIGURE 43)................................................................ 267

TABLE 38 – FREEDM-8 ORDERING INFORMATION .............................................................. 269

TABLE 39 – FREEDM-8 THERMAL INFORMATION................................................................. 269

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xi

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

1 FEATURES

· Single-chip Peripheral Component Interconnect (PCI) Bus multi-channel HDLC controller.

· Supports up to 128 bi-directional HDLC channels assigned to a maximum of 8 channelised T1

or E1 links. The number of time-slots assigned to an HDLC channel is programmable from 1

to 24 (for T1) and from 1 to 31 (for E1).

· Supports up to 8 bi-directional HDLC channels each assigned to an unchannelised arbitrary

rate link; subject to a maximum aggregate link clock rate of 64 MHz in each direction.

Channels assigned to links 0 to 2 can have a clock rate of up 52 MHz when SYSCLK is at 33

MHz. Channels assigned to links 3 to 7 can have a clock rate of up to 10 MHz.

· Supports up to two bi-directional HDLC Channels each assigned to an unchannelised arbitrary

rate link of up to 52 MHz when SYSCLK is at 33 MHz.

· Supports a mix of up to 8 channelised and unchannelised links; subject to the constraint of a

maximum of 128 channels and a maximum aggregate link clock rate of 64 MHz in each

direction.

· For each channel, the HDLC receiver performs flag sequence detection, bit de-stuffing, and

frame check sequence validation. The receiver supports the validation of both CRC-CCITT

and CRC-32 frame check sequences. The receiver also checks for packet abort sequences,

octet aligned packet length and for minimum and maximum packet length.

· Alternatively, for each channel, the receiver supports a transparent mode where each octet is

transferred transparently to host memory. For channelised links, the octets are aligned with

the receive time-slots.

· For each channel, time-slots are selectable to be in 56 kbits/s format or 64 kbits/s clear

channel format.

· For each channel, the HDLC transmitter performs flag sequence generation, bit stuffing, and,

optionally, frame check sequence generation. The transmitter supports the generation of

both CRC-CCITT and CRC-32 frame check sequences. The transmitter also aborts packets

under the direction of the host or automatically when the channel underflows.

· Supports two levels of non-preemptive packet priority on each transmit channel. Low priority

packets will not begin transmission until all high priority packets are transmitted.

· Alternatively, for each channel, the transmitter supports a transparent mode where each octet

is inserted transparently from host memory. For channelised links, the octets are aligned with

the transmit time-slots.

· Directly supports a 32-bit, 33 MHz PCI 2.1 interface for configuration, monitoring and transfer

of packet data, with an on-chip DMA controller with scatter/gather capabilities.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 1

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

· Provides 8 kbytes of on-chip memory for partial packet buffering in each direction. This

memory can be configured to support a variety of different channel configurations from a

single channel with 8 kbytes of buffering to 128 channels, each with a minimum of 48 bytes of

buffering.

· Supports PCI burst sizes of up to 128 bytes for transfers of packet data.

· Pin compatible with PM7364 (FREEDM-32) device.

· Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

· Supports 3.3 and 5 Volt PCI signaling environments.

· Low power CMOS technology.

· 256 pin enhanced ball grid array (SBGA) or 272 pin plastic ball grid array (PBGA) packages

(27 mm X 27 mm).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 2

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

2 APPLICATIONS

· IETF PPP interfaces for routers

· Frame Relay interfaces for ATM or Frame Relay switches and multiplexors

· FUNI or Frame Relay service inter-working interfaces for ATM switches and multiplexors.

· D-channel processing in ISDN terminals and switches.

· Internet/Intranet access equipment.

· Packet-based DSLAM equipment.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 3

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

3 REFERENCES

1. International Organization for Standardization, ISO Standard 3309-1993, "Information

Technology - Telecommunications and information exchange between systems - High-level

data link control (HDLC) procedures - Frame structure", December 1993.

2. RFC-1662 - "PPP in HDLC-like Framing" Internet Engineering Task Force, July 1994.

3. PCI Special Interest Group, PCI Local Bus Specification, June 1, 1995, Version 2.1.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 4

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

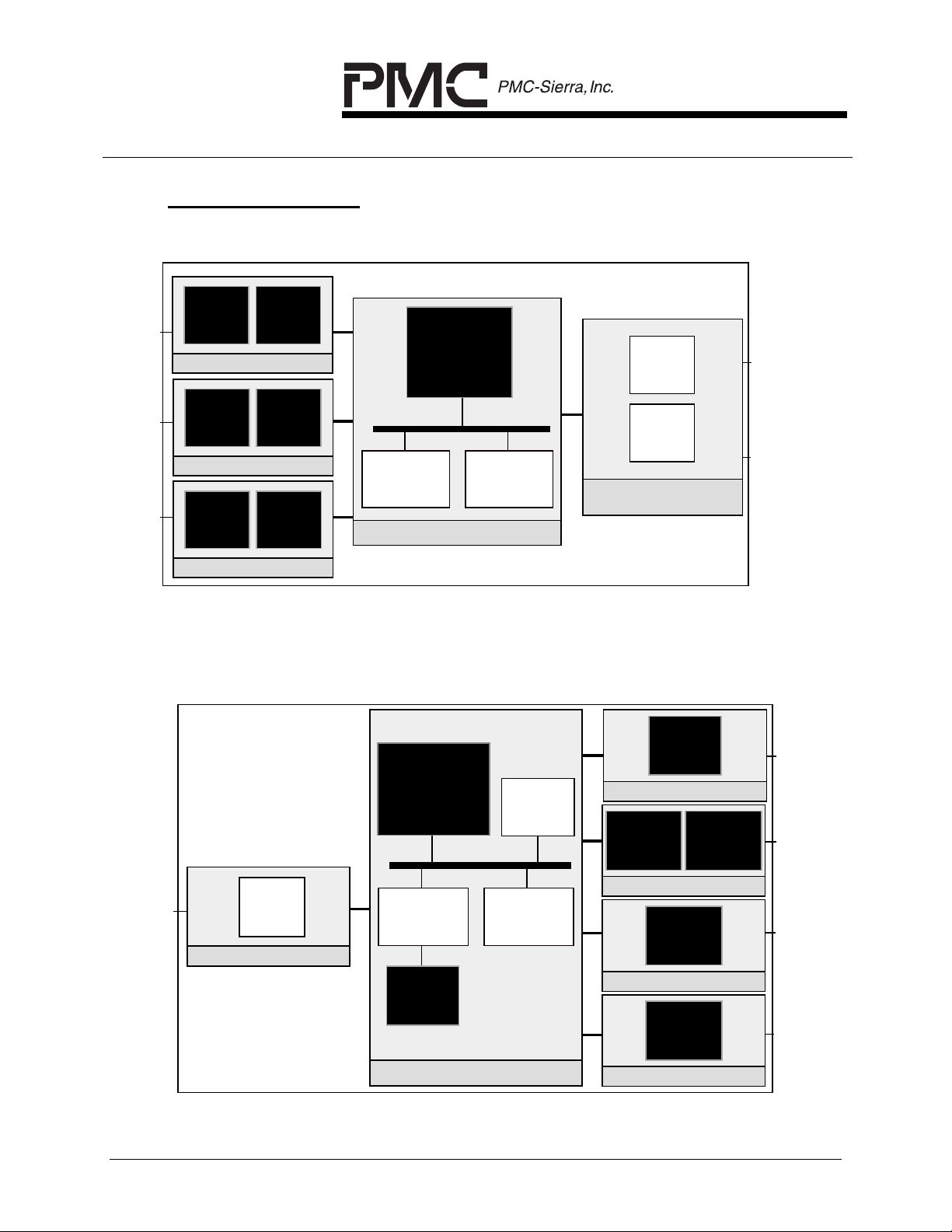

4 APPLICATION EXAMPLES

ACCESS SIDE

PM8313

DS3

D3MX

M13 Access Module

PM4314

T1

QDSX

T1 Access Modu le

E1

PM4314

QDSX

PM4388

TOCTL

PM4388

TOCTL

PM6344

EQUAD

PM7366

FREEDM

FREEDM-8

PCI Bus

Packet

Memory

Processor Module

Micro-

processor

HDLC BASED UPLINK SIDE

HSSI

Module

DS3/E3

Framer

LIU

HDLC Based

Uplink Module

HSSI

DS3/E3/J2

xDSL

E1 Access Module

ACCESS SIDE

XDSL

PHY

xDSL Access Module

PM7366

FREEDM-8

Packet

Memory

PM7322

RCMP

PCI Bus

SAR

Micro-

processor

ATM CELL BASED UPLINK SIDE

PM7345

S/UNI-PDH

DS-3/E3 ATM

PM5346

S/UNI-LITE

PM5348

S/UNI-DUAL

STS-3c ATM UNI

PM5347

S/UNI-PLUS

STS-3c ATM NNI

PM5355

S/UNI-622

T3/E3

OC-3

OC-3

OC-12

Processor Module

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 5

STS-12c ATM UNI/NNI

A

A

A

A

/

/

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

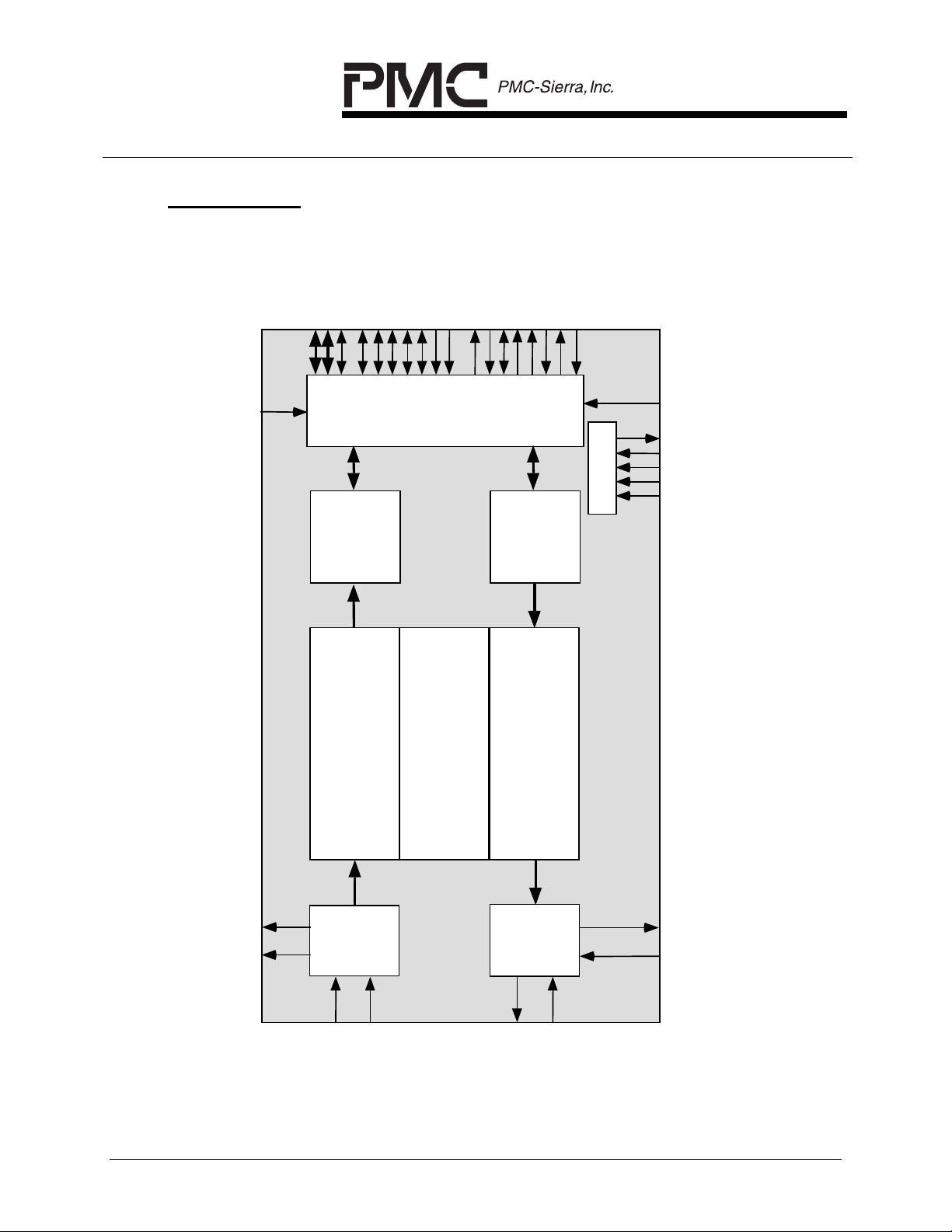

5 BLOCK DIAGRAM

.

AD[31:0]

C/BEB[3:0]

PAR

TRDYB

IRDYB

STOPB

DEVSELB

IDSEL

LOCKB

GNTB

PERRB

SERRB

PCIINTB

PCICLK

PCICLKO

SYSCLK

PMCTEST

TDO

RSTB

FRAMEB

PCI

Controller

REQB

(GPIC)

TDI

TCK

TMS

JTAG Port

TRSTB

RBCLK

RBD

DM

Receive

Controller

(RHDL)

Partial Packet Buffer

(RMAC)

(PMON)

Performance Monitor

Receive HDLC Processor

Transmit

Transmit HDLC Processor

DM

Partial Packet Buffer

(TMAC)

Controller

(THDL)

TBCLK

ssigner

Channel

(RCAS)

Receive

Transmit

Channel

ssigner

(TCAS)

TBD

RD[7:0]

RCLK[7:0]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 6

TD[7:0]

TCLK[7:0]

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

6 DESCRIPTION

The PM7366 FREEDM-8 Frame Engine and Datalink Manager device is a monolithic integrated

circuit that implements HDLC processing, and PCI Bus memory management functions for a

maximum of 128 bi-directional channels.

For channelised links, the FREEDM-8 allows up to 128 bi-directional HDLC channels to be

assigned to individual time-slots within a maximum of 8 independently timed T1 or E1 links. The

channel assignment supports the concatenation of time-slots (N x DS0) up to a maximum of 24

concatenated time-slots for a T1 link and 31 concatenated time-slots for an E1 link. Time-slots

assigned to any particular channel need not be contiguous within the T1 or E1 link.

For unchannelised links, the FREEDM-8 processes up to 8 bi-directional HDLC channels within 8

independently timed links. The links can be of arbitrary frame format. When limited to two

unchannelised links, each link can be rated at up to 52 MHz when SYSCLK is at 33 MHz. For

lower rate unchannelised links, the FREEDM-8 processes up to 8 links, where the aggregate

clock rate of all the links is limited to 64 MHz, links 0 to 2 can have a clock rate of up to 52 MHz

when SYSCLK is at 33 MHz and links 3 to 7 can have a clock rate of up to 10 MHz. The

FREEDM-8 also supports mixing of up to 8 channelised and unchannelised links. The total

number of channels in each direction is limited to 128. The aggregate clock rate over all 8

possible links is limited to 64 MHz.

In the receive direction, the FREEDM-8 performs channel assignment and packet extraction and

validation. For each provisioned HDLC channel, the FREEDM-8 delineates the packet boundaries

using flag sequence detection, and performs bit de-stuffing. Sharing of opening and closing flags,

as well as, sharing of zeros between flags are supported. The resulting packet data is placed into

the internal 8 kbyte partial packet buffer RAM. The partial packet buffer acts as a logical FIFO for

each of the assigned channels. Partial packets are DMA'd out of the RAM, across the PCI bus

and into host packet memory. The FREEDM-8 validates the frame check sequence for each

packet, and verifies that the packet is an integral number of octets in length and is within a

programmable minimum and maximum length. The receive packet status is updated before

linking the packet into a receive ready queue. The FREEDM-8 alerts the PCI Host that there are

packets in a receive ready queue by, optionally, asserting an interrupt on the PCI bus.

Alternatively, in the receive direction, the FREEDM-8 supports a transparent operating mode. For

each provisioned transparent channel, the FREEDM-8 directly transfers the received octets into

host memory verbatim. If the transparent channel is assigned to a channelised link, then the

octets are aligned to the received time-slots.

In the transmit direction, the PCI Host provides packets to transmit using a transmit ready queue.

For each provisioned HDLC channel, the FREEDM-8 DMA's partial packets across the PCI bus

and into the transmit partial packet buffer. The partial packets are read out of the packet buffer by

the FREEDM-8 and frame check sequence is optionally calculated and inserted at the end of each

packet. Bit stuffing is performed before being assigned to a particular link. The flag sequence is

automatically inserted when there is no packet data for a particular channel. Sequential packets

are optionally separated by two flags (an opening flag and a closing flag) or a single flag

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 7

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

(combined opening and closing flag). Zeros between flags are not shared. PCI bus latency may

cause one or more channels to underflow, in which case, the packets are aborted, and the host is

notified. For normal traffic, an abort sequence is generated, followed by inter-frame time fill

characters (flags or all-ones bytes) until a new packet is sourced from the PCI host. No attempt is

made to automatically re-transmit an aborted packet.

Alternatively, in the transmit direction, the FREEDM-8 supports a transparent operating mode. For

each provisioned transparent channel, the FREEDM-8 directly inserts the transmitted octets from

host memory. If the transparent channel is assigned to a channelised link, then the octets are

aligned to the transmitted time-slots. If a channel underflows due to excessive PCI bus latency,

an abort sequence is generated, followed by inter-frame time fill characters (flags or all-ones

bytes) to indicate idle channel. Data resumes immediately when the FREEDM-8 receives new

data from the host.

The FREEDM-8 is configured, controlled and monitored using the PCI bus interface. The

FREEDM-8 is implemented in low power CMOS technology, with TTL compatible inputs and

outputs. The FREEDM-8 is available in two package options; a 256 pin enhanced ball grid array

(SBGA) package, or a 272 pin plastic ball grid array (PBGA) package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 8

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

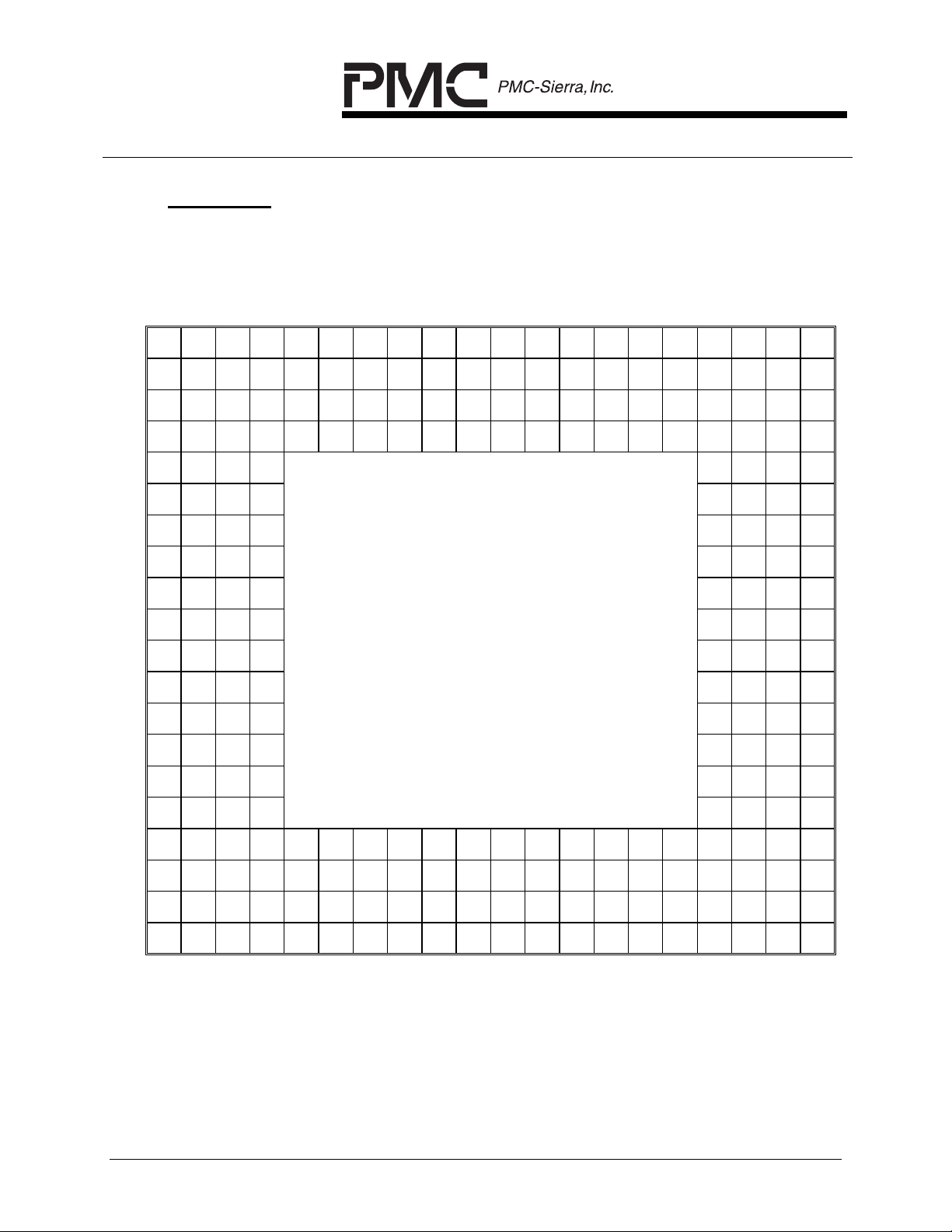

7 PIN DIAGRAM

The PM7366-BI FREEDM-8 is manufactured in a 256 pin enhanced ball grid array (SBGA)

package.

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

A VSS VSS VSS X X TA[2] TA[4] VSS TA[7] TA[9] VSS VSS X X X X X VSS VSS VSS A

B VSS VDD VDD X TA[0] X X X X X TA[ 10] X X X X X X VDD VDD VSS B

C VSS VDD VDD RD[7] X TA[1] X X TA[6] TA[8] X

D RD[5] RCLK[5] RCLK[6] EN5V RCLK[7] X VDD TA[3] TA[5] X VDD TRDB X VDD X PCICLKO VBIAS[2] GNTB AD[31] AD[30] D

E RD[3] RCLK[3] RCLK[4] RD[6] REQB AD[29] AD[27] AD[26] E

F RCLK[1] RD[2] RCLK [2] RD[4] AD[28] AD[25] AD[24] CBEB[3] F

G RBCLK RD[0] RD[1] VDD VDD IDSEL AD[22] AD[21] G

TA[11]/

TWRB X X X PCICLK VDD VDD VSS C

TRS

H VBIAS[1] SYSCLK RBD RCLK[0] AD[23] AD[20] AD[18] VSS H

J VSS TCK TMS TRSTB AD[19] AD[17] AD[16] CBEB[2] J

K VSS TDI TDO VDD FRAMEB IRDYB TRDYB DEVSELB K

BOTTOM VIEW

L TD[0] TCLK[0] TD[1] TCLK[1] VDD STOPB LOCKB VSS L

M TD[2] TCLK[2] TD[3] TD[4] CBEB[1] SERRB PERRB VSS M

N VSS TCLK[3] TCLK[4] TD[6] AD[11] AD[14] AD[15] PAR N

P TD[5] TCLK[5] TCLK[6] VDD VDD AD[10] AD[12] AD[13] P

R TD[7] TCLK[7] NC X AD[5] CBEB[0] AD[8] AD[9] R

T X NC NC X AD[1] AD[4] AD[6] AD[7] T

U X NC NC NC NC NC VDD X TDAT[5] VDD X TDAT[12] TDAT [14] VDD PMCTEST X VBIAS[3] AD[0] AD[2] AD[3] U

V VSS VDD VDD X X X TDAT[2] TDAT[4] TDAT[6] X TDAT[9] TDAT[11] X X TB D PCIINTB X VDD VDD VSS V

W VSS VDD VDD X X TDAT[1] TDAT[3] X X TDAT[7] X X X X X RSTB X VDD VDD VSS W

Y VSS VSS VSS NC TDAT[0] X X X VS S VSS TDAT[8] TDAT[10] VSS TDAT[13] TDAT[15] TBCLK X VSS VSS VSS Y

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 9

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

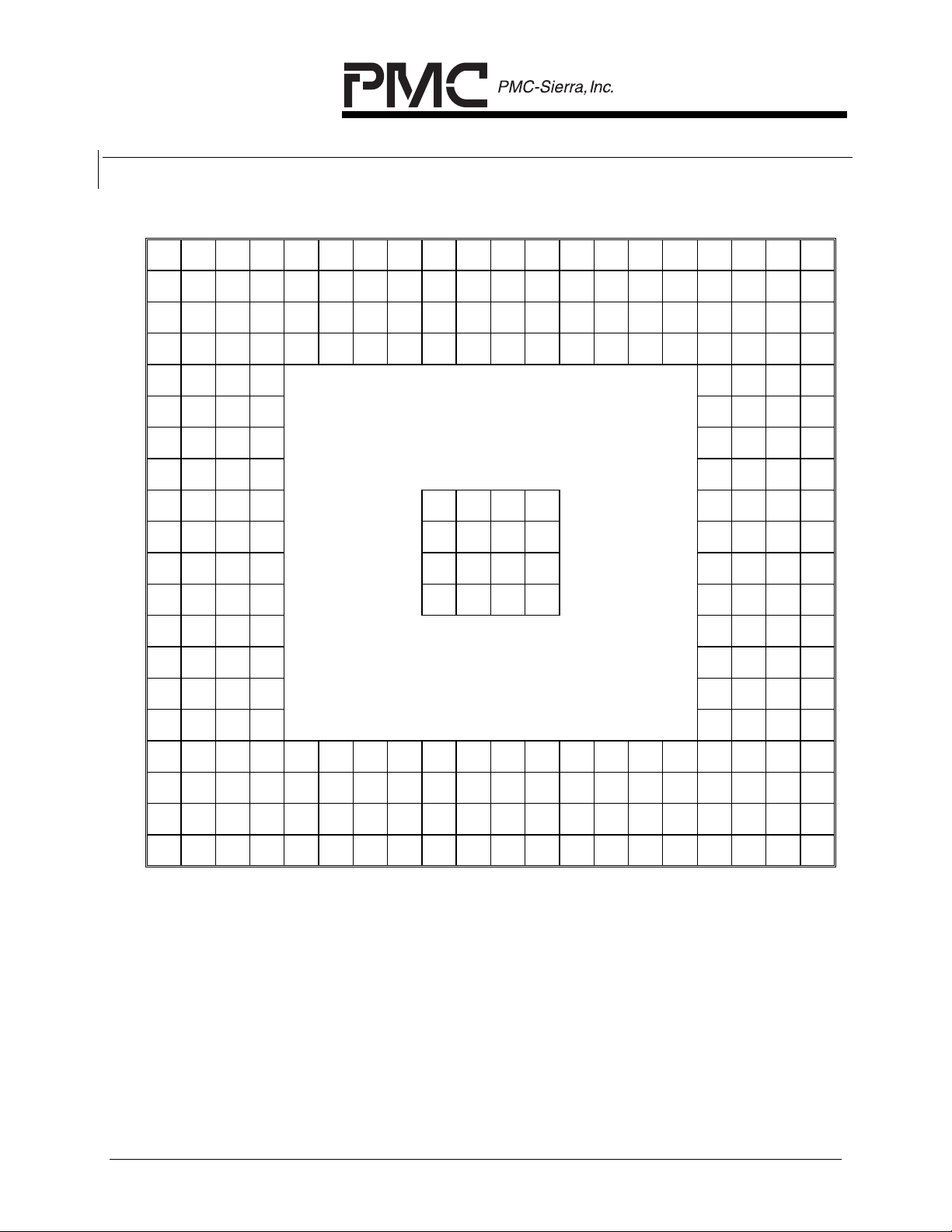

The PM7366-PI FREEDM-8 is manufactured in a 272 pin plastic ball grid array (PBGA) package.

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

A VSS NC NC X X X X X X TA[9] X X X TA[3] TA[2] X X NC NC VSS A

B NC VBIAS [2] NC PCICLK X X X TWRB

CNCNCVDDPCICLKOXXXXXXXXXXXXENV5VDDNCNCC

D AD[29] AD[31] GNTB VSS X VDD X VSS TRDB VDD TA[7] TA[5] VSS TA[0] VDD RD[7] VSS NC RCLK[6] RCLK[5] D

E AD[25] AD[28] AD[30] REQB RD[6] RD[5] RCLK[4] RD[4] E

F IDSEL AD[24] AD[27] VDD VDD RCLK[3] RCLK[2] RD[2] F

TA[11]/

TA[10] TA[8] TA[6] TA[4] X TA[1] X RCLK [7] NC NC NC B

TRS

BOTTOM VIEW

G AD[22] AD[23] CBEB[3] AD[26] RD[3] RCL K[1] RD[1] RCLK[0] G

H AD[19] AD[20] AD[21] VSS VSS RD[0] RBCLK R BD H

J CBEB[2] AD[1 6] AD[17] AD[18] VSS VSS VSS VSS SYSCLK TRSTB VBIA S[1] TMS J

K DEVSELB TRDYB IRDYB FRAMEB VSS VSS VS S VSS VDD TDI TCK T DO K

L STOPB PERRB LOCKB VDD VS S VSS VS S VSS TCLK[1] TD[1] TCLK[0] TD [0] L

M SERRB PAR CBEB[1] AD[15] VSS VSS VSS VSS TCLK[3] TD[3] TCLK[2] TD [2] M

N AD[14] AD[13] AD[12] VSS VSS TD[5] TCLK[4] TD[4] N

P AD[11] AD[10] AD[9] NC X TD[7] TD[6] TCLK[5] P

R AD[8] CBEB[0] AD[7] VDD VDD NC TCLK[7] TCLK[6] R

T AD[6] AD[5] AD[4] A D[2] XXXNCT

U AD[3] AD[0] AD[1] VSS X VDD RSTB VSS TDAT[12 ] TDAT[10] VDD TDAT[5] VSS X VDD X VSS NC NC NC U

V NC NC VDD NC X PMCTEST X X X X X X X TDAT[2] TDAT[0] X NC VDD NC NC V

W NC VBIAS[3] NC X PCINTB TBD X TDAT[13] TDAT[11] TDAT[9] TDAT[7] TDAT[6] TDAT[4] X TDAT[1] NC X NC NC NC W

Y VSS NC NC X TBCLK TD AT[15] TDAT[14] X X X TDAT[8] X X TDAT[3] X X NC NC NC VSS Y

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 10

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

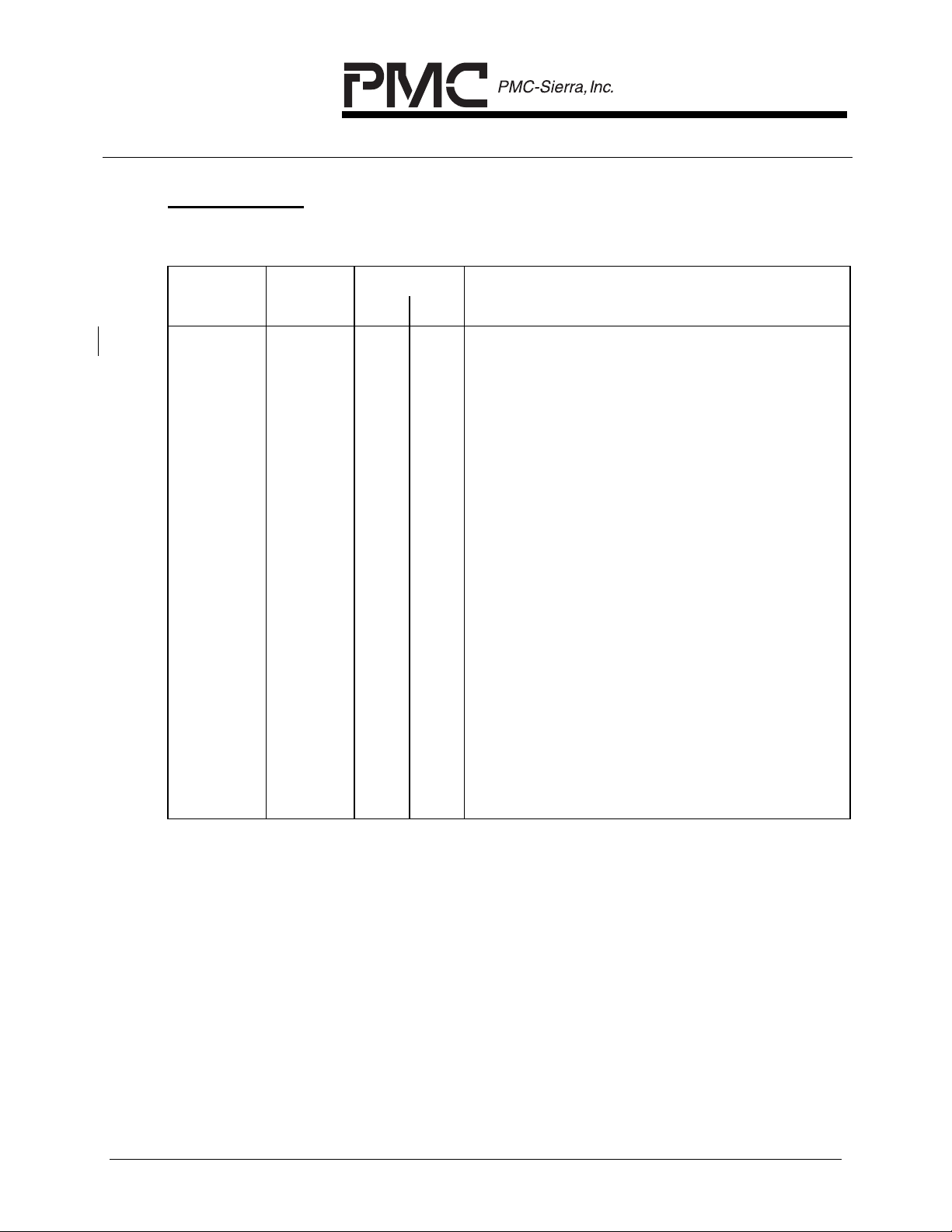

8 PIN DESCRIPTION

Table 1 – Line Side Interface Signals (36)

Pin Name Type

Pin No.

Function

-PI -BI

RCLK[0]

RCLK[1]

RCLK[2]

RCLK[3]

RCLK[4]

RCLK[5]

RCLK[6]

RCLK[7]

Input G1

G3

F2

F3

E2

D1

D2

B4

H17

F20

F18

E19

E18

D19

D18

D16

The receive line clock signals (RCLK[7:0]) contain the

recovered line clock for the 8 independently timed

links. Processing of the receive links is on a priority

basis, in descending order from RCLK[0] to RCLK[7].

Therefore, the highest rate link should be connected

to RCLK[0] and the lowest to RCLK[7]. RD[7:0] is

sampled on the rising edge of the corresponding

RCLK[7:0] clock.

For channelised T1 or E1 links, RCLK[n] must be

gapped during the framing bit (for T1 interfaces) or

during time-slot 0 (for E1 interfaces) of the RD[n]

stream. The FREEDM-8 uses the gapping

information to determine the time-slot alignment in

the receive stream. RCLK[7:0] is nominally a 50%

duty cycle clock of 1.544 MHz for T1 links and 2.048

MHz for E1 links.

For unchannelised links, RCLK[n] must be externally

gapped during the bits or time-slots that are not part

of the transmission format payload (i.e. not part of the

HDLC packet). RCLK[2:0] is nominally a 50% duty

cycle clock between 0 and 52 MHz. RCLK[7:3] is

nominally a 50% duty cycle clock between 0 and 10

MHz.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 11

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

Pin No. Pin Name Type

Function

PM7366 FREEDM-8

-PI -BI

RD[0]

RD[1]

RD[2]

RD[3]

RD[4]

RD[5]

RD[6]

RD[7]

Input H3

G2

F1

G4

E1

E3

E4

D5

G19

G18

F19

E20

F17

D20

E17

C17

The receive data signals (RD[7:0]) contain the

recovered line data for the 8 independently timed

links. Processing of the receive links is on a priority

basis, in descending order form RD[0] to RD[7].

Therefore, the highest rate link should be connected

to RD[0] and the lowest to RD[7].

For channelised links, RD[n] contains the 24 (T1) or

31 (E1) time-slots that comprise the channelised link.

RCLK[n] must be gapped during the T1 framing bit

position or the E1 frame alignment signal (time-slot

0). The FREEDM-8 uses the location of the gap to

determine the channel alignment on RD[n].

For unchannelised links, RD[n] contains the HDLC

packet data. For certain transmission formats, RD[n]

may contain place holder bits or time-slots. RCLK[n]

must be externally gapped during the place holder

positions in the RD[n] stream. The FREEDM-8

supports a maximum data rate of 10 Mbit/s on an

individual RD[7:3] link and a maximum data rate of 52

Mbit/s on RD[2:0].

RBD Tristate

H1 H18 The receive BERT data signal (RBD) contains the

Output

RBCLK Tristate

H2 G20 The receive BERT clock signal (RBCLK) contains the

Output

RD[7:0] is sampled on the rising edge of the

corresponding RCLK[7:0] clock.

receive bit error rate test data. RBD reports the data

on the selected one of the receive data signals

(RD[7:0]) and is updated on the falling edge of

RBCLK. RBD may be tri-stated by setting the RBEN

bit in the FREEDM-8 Master BERT Control register

low.

receive bit error rate test clock. RBCLK is a buffered

version of the selected one of the receive clock

signals (RCLK[7:0]). RBCLK may be tri-stated by

setting the RBEN bit in the FREEDM-8 Master BERT

Control register low.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 12

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

Pin No. Pin Name Type

Function

PM7366 FREEDM-8

-PI -BI

TCLK[0]

TCLK[1]

TCLK[2]

TCLK[3]

TCLK[4]

TCLK[5]

TCLK[6]

TCLK[7]

Input L2

L4

M2

M4

N2

P1

R1

R2

L19

L17

M19

N19

N18

P19

P18

R19

The transmit line clock signals (TCLK[7:0]) contain

the transmit clocks for the 8 independently timed

links. Processing of the transmit links is on a priority

basis, in descending order from TCLK[0] to TCLK[7].

Therefore, the highest rate link should be connected

to TCLK[0] and the lowest to TCLK[7]. TD[7:0] is

updated on the falling edge of the corresponding

TCLK[7:0] clock.

For channelised T1 or E1 links, TCLK[n] must be

gapped during the framing bit (for T1 interfaces) or

during time-slot 0 (for E1 interfaces) of the TD[n]

stream. The FREEDM-8 uses the gapping

information to determine the time-slot alignment in

the transmit stream.

For unchannelised links, TCLK[n] must be externally

gapped during the bits or time-slots that are not part

of the transmission format payload (i.e. not part of the

HDLC packet).

TCLK[7:3] is nominally a 50% duty cycle clock

between 0 and 10 MHz. TCLK[2:0] is nominally a

50% duty cycle clock between 0 and 52 MHz. Typical

values for TCLK[7:0] include 1.544 MHz (for T1 links)

and 2.048 MHz (for E1 links).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 13

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

Pin No. Pin Name Type

Function

PM7366 FREEDM-8

-PI -BI

TD[0]

TD[1]

TD[2]

TD[3]

TD[4]

TD[5]

TD[6]

TD[7]

Output L1

L3

M1

M3

N1

N3

P2

P3

L20

L18

M20

M18

M17

P20

N17

R20

The transmit data signals (TD[7:0]) contains the

transmit data for the 8 independently timed links.

Processing of the transmit links is on a priority basis,

in descending order from TD[0] to TD[7]. Therefore,

the highest rate link should be connected to TD[0]

and the lowest to TD[7].

For channelised links, TD[n] contains the 24 (T1) or

31 (E1) time-slots that comprise the channelised link.

TCLK[n] must be gapped during the T1 framing bit

position or the E1 frame alignment signal (time-slot

0). The FREEDM-8 uses the location of the gap to

determine the channel alignment on TD[n].

For unchannelised links, TD[n] contains the HDLC

packet data. For certain transmission formats, TD[n]

may contain place holder bits or time-slots. TCLK[n]

must be externally gapped during the place holder

positions in the TD[n] stream. The FREEDM-8

supports a maximum data rate of 10 Mbit/s on an

individual TD[7:3] link and a maximum data rate of

52 Mbit/s on TD[2:0]

TD[7:0] is updated on the falling edge of the

corresponding TCLK[7:0] clock.

TBD Input W15 V6 The transmit BERT data signal (TBD) contains the

transmit bit error rate test data. When the TBERTEN

bit in the BERT Control register is set high, the data

on TBD is transmitted on the selected one of the

transmit data signals (TD[7:0]). TBD is sampled on

the rising edge of TBCLK.

TBCLK Tristate

Output

Y16 Y5 The transmit BERT clock signal (TBCLK) contains the

transmit bit error rate test clock. TBCLK is a buffered

version of the selected one of the transmit clock

signals (TCLK[7:0]). TBCLK may be tri-stated by

setting the TBEN bit in the FREEDM-8 Master BERT

Control register low.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 14

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

PM7366 FREEDM-8

Table 2 – PCI Host Interface Signals (51)

Pin Name Type

Pin No.

Function

-PI -BI

PCICLK Input B17 C4 The PCI clock signal (PCICLK) provides timing for

PCI bus accesses. PCICLK is a nominally 50% duty

cycle, 0 to 33 MHz clock.

PCICLKO Output C17 D5 The PCI clock output signal (PCICLKO) is a buffered

version of the PCICLK. PCICLKO may be used to

drive the SYSCLK input.

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

AD[7]

AD[8]

AD[9]

AD[10]

AD[11]

AD[12]

AD[13]

AD[14]

AD[15]

AD[16]

AD[17]

AD[18]

AD[19]

AD[20]

AD[21]

AD[22]

AD[23]

AD[24]

AD[25]

AD[26]

AD[27]

AD[28]

AD[29]

AD[30]

I/O

U19

U18

T17

U20

T18

T19

T20

R18

R20

P18

P19

P20

N18

N19

N20

M17

J19

J18

J17

H20

H19

H18

G20

G19

F19

E20

G17

F18

E19

D20

E18

U3

T4

U2

U1

T3

R4

T2

T1

R2

R1

P3

N4

P2

P1

N3

N2

J2

J3

H2

J4

H3

G1

G2

H4

F2

F3

E1

E2

F4

E3

D1

The PCI address and data bus (AD[31:0]) carries the

PCI bus multiplexed address and data. During the

first clock cycle of a transaction, AD[31:0] contains a

physical byte address. During subsequent clock

cycles of a transaction, AD[31:0] contains data.

A transaction is defined as an address phase followed

by one or more data phases. When Little-Endian

byte formatting is selected, AD[31:24] contain the

most significant byte of a DWORD while AD[7:0]

contain the least significant byte. When Big-Endian

byte formatting is selected. AD[7:0] contain the most

significant byte of a DWORD while AD[31:24] contain

the least significant byte. When the FREEDM-8 is the

initiator, AD[31:0] is an output bus during the first

(address) phase of a transaction. For write

transactions, AD[31:0] remains an output bus for the

data phases of the transaction. For read

transactions, AD[31:0] is an input bus during the data

phases.

When the FREEDM-8 is the target, AD[31:0] is an

input bus during the first (address) phase of a

transaction. For write transactions, AD[31:0] remains

an input bus during the data phases of the

transaction. For read transactions, AD[31:0] is an

output bus during the data phases.

When the FREEDM-8 is not involved in the current

transaction, AD[31:0] is tri-stated.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 15

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

Pin No. Pin Name Type

Function

PM7366 FREEDM-8

-PI -BI

AD[31] I/O D19 D2 As an output bus, AD[31:0] is updated on the rising

edge of PCICLK. As an input bus, AD[31:0] is

sampled on the rising edge of PCICLK.

C/BEB[0]

C/BEB[1]

C/BEB[2]

C/BEB[3]

I/O R19

M18

J20

G18

R3

M4

J1

F1

The PCI bus command and byte enable bus

(C/BEB[3:0]) contains the bus command or the byte

valid indications. During the first clock cycle of a

transaction, C/BEB[3:0] contains the bus command

code. For subsequent clock cycles, C/BEB[3:0]

identifies which bytes on the AD[31:0] bus carry valid

data. C/BEB[3] is associated with byte 3 (AD[31:24])

while C/BEB[0] is associated with byte 0 (AD[7:0]).

When C/BEB[n] is set high, the associated byte is

invalid. When C/BEB[n] is set low, the associated

byte is valid.

When the FREEDM-8 is the initiator, C/BEB[3:0] is an

output bus.

When the FREEDM-8 is the target, C/BEB[3:0] is an

input bus.

When the FREEDM-8 is not involved in the current

transaction, C/BEB[3:0] is tri-stated.

As an output bus, C/BEB[3:0] is updated on the rising

edge of PCICLK. As an input bus, C/BEB[3:0] is

sampled on the rising edge of PCICLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 16

RELEASED

DATA SHEET

PMC-1970930 ISSUE 4 FRAME ENGINE AND DATA LINK MANAGER

Pin No. Pin Name Type

Function

PM7366 FREEDM-8

-PI -BI

PAR I/O M19 N1 The parity signal (PAR) indicates the parity of the

AD[31:0] and C/BEB[3:0] buses. Even parity is

calculated over all 36 signals in the buses regardless

of whether any or all the bytes on the AD[31:0] are

valid. PAR always reports the parity of the previous

PCICLK cycle. Parity errors detected by the

FREEDM-8 are indicated on output PERRB and in

the FREEDM-8 Interrupt Status register.

When the FREEDM-8 is the initiator, PAR is an output

for writes and an input for reads.

When the FREEDM-8 is the target, PAR is an input

for writes and an output for reads.

When the FREEDM-8 is not involved in the current

transaction, PAR is tri-stated.

As an output signal, PAR is updated on the rising

edge of PCICLK. As an input signal, PAR is sampled

on the rising edge of PCICLK.

FRAMEB I/O K17 K4 The active low cycle frame signal (FRAMEB)

identifies a transaction cycle. When FRAMEB

transitions low, the start of a bus transaction is

indicated. FRAMEB remains low to define the

duration of the cycle. When FRAMEB transitions

high, the last data phase of the current transaction is

indicated.

When the FREEDM-8 is the initiator, FRAMEB is an

output.

When the FREEDM-8 is the target, FRAMEB is an

input.

When the FREEDM-8 is not involved in the current

transaction, FRAMEB is tri-stated.

As an output signal, FRAMEB is updated on the rising

edge of PCICLK. As an input signal, FRAMEB is

sampled on the rising edge of PCICLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA,INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 17

Loading...

Loading...