PMC PM7364 Datasheet

PMC-Sierra,Inc.

Frame Engine and Datalink Manager

PM7364

FREEDM-32

FEATURES

• High density HDLC controller ideal for

Internet access, Frame Relay, and

DSLAM equipment supporting rates

ranging from 56 Kbit/s to 52 Mbit/s.

• Supports 32 full-duplex and

independently-timed links.

• Supports 128 full-duplex HDLC or

transparent channels .

• Supports a TimePipe architecture

that enabl es any physical link to be

flexibly mapped to one or more HDLC

channels.

• Provides 8 KB partial packet FIFO in

each transmit and receive direction to

compensate for PCI bus laten cy during

data transfers. The 8 KB partial packet

FIFO is arranged as 512 blocks of 16byte buffers.

• The TimePipe architecture supports

programmable assignm ent of partial

packet buffers to HDLC channels.

• Two physical links can support up to

52 Mbit/s; the remaining six physical

links can individually support up to

10 Mbit/s.

• Supports a mix of channelize d and

unchannelized links.

• The maximum aggregate clock rate is

64 MHz. When the device is interfa ced

to two T3 or HSSI links, the maximum

aggregate clock rate is 104 MHz.

• For channelized operation, the c hannel

assignment support s up to 24 times lots

for a T1 link and 31 ti me slots for an E1

link. Timeslots assigned to a common

HDLC channel can be noncontiguous.

• Performs flag delineation, bit destuffing, CRC verification using either

CRC-32 or CRC-CCITT algorithm, and

length checking on receive HDLC

channels.

• Performs flag inse rtion, bit stuff ing, and

FCS calculation using either CRC-32

or CRC-CCITT algorithm and length

checking on transmit HDLC channels.

• On the system side, provides a

33 MHz, 32-bit PCI 2.1-compliant bus

interface.

• Implements efficient transmit and

receive DMA controllers to support

burst data transfers between partial

packet FIFO and packet memory.

• Supports scatter-gather ca pab ilities

whereby a packet can span multiple

buffers.

• Supports line-side loopback on a perlink basis and sys tem-side loopb ack on

a per-HDLC channel basis.

• Pin-com patible and softwarecompatible with the PM7366

FREEDM-8.

• Provides a standard 5-signal P1149.1

JTAG test port for boundar y scan test

board purposes.

• Implemented in low power 3.3 V

CMOS technology with 5 V-tolerant

inputs.

• Packaged in a 256-pin Ball Grid Array

(BGA) package.

APPLICATIONS

• Ideal for applications requiring HDLC,

PPP, and transparent protocol

processing for physical links, such as

T1, E1, T3, E3, xDSL, and HSSI

• Frame-based Interfaces for Internet

Access and DSLAM equipment

• FUNI or Frame Relay service

interworking interfaces for ATM

switches and multiplexers

BLOCK DIAGRAM

RD[31:0]

RCLK[31:0]

TD[31:0]

TCLK[31:0]

Channel Assigner

Channel Assigner

RBD

RCAS

Receive

TCAS

Transmit

TBD

RBCLK

AD[31:0]

C/BEB[3:0]

PAR

RHDL

Receive HDLC

Processor/

Partial Packet Buffer

PMON

Performance Monitor

THDL

Transmit HDLC

Processor/

Partial Packet Buffer

™

TimePipe

TBCLK

Architecture

RMAC

Receive

DMA

Controller

TMAC

Transmit

DMA

Controller

JTAG Port

TMB

TRSTB

GPIC

PCI

Controller

TDI

TCK

TDO

PMCTEST

FRAMEB

TRDYB

IRDYB

STOPB

DEVSELB

IDSEL

LOCKB

REQB

GNTB

PERRB

SERRB

PCIINTB

PCICLK

PCICLKO

SYSCLK

PMC-960952 (R4)

1998 PMC-Sierra, Inc. October, 1998

Frame Engine and Datalink Manager

TYPICAL APPLICATIONS

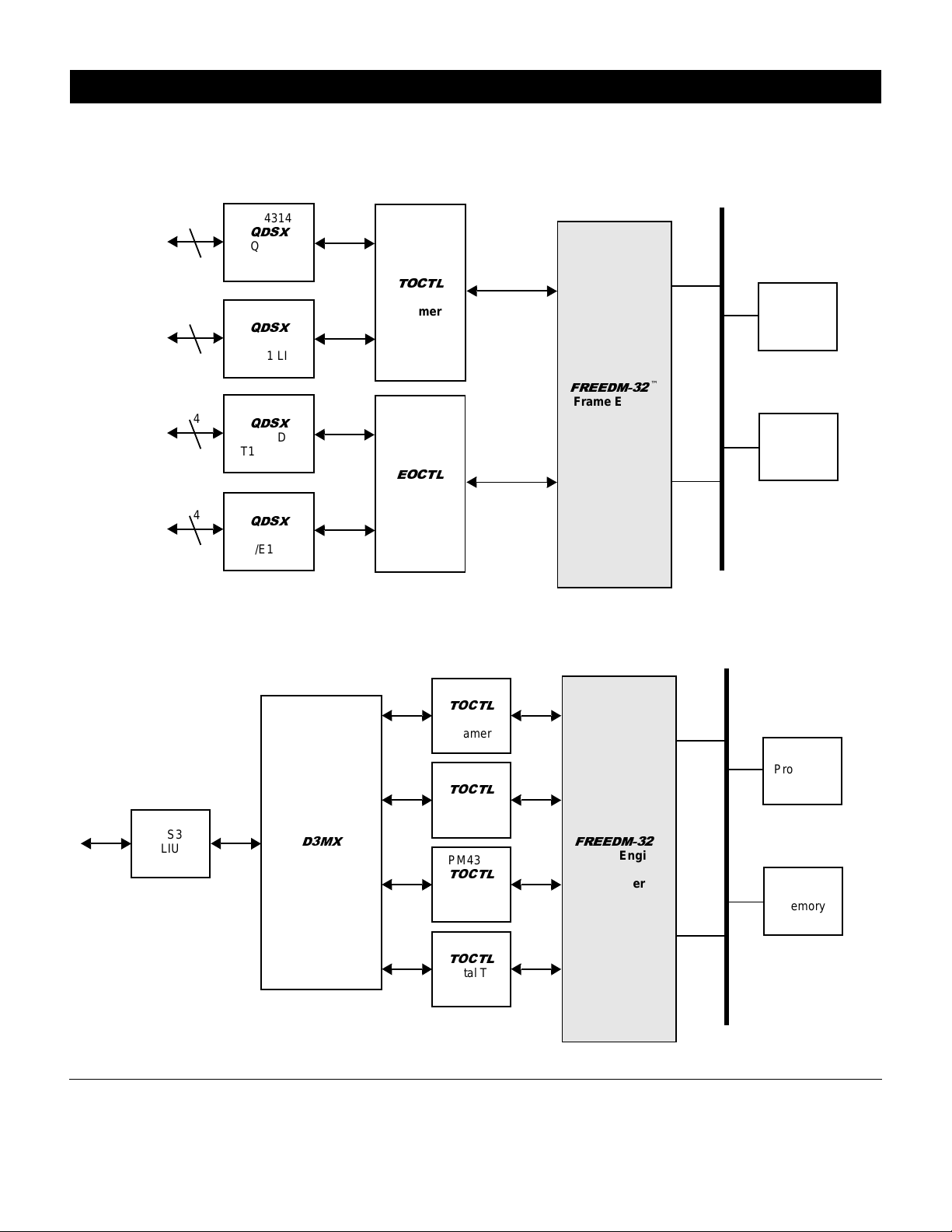

HIGH DENSITY CHANNELIZED AND UNCHANNELIZED T1/E1 INTERFACES

PM7364 FREEDM-32

4

PM4314

4'6;

QUAD

T1/E1 LIU

4

PM4314

4'6;

QUAD

T1/E1 LIU

4

PM4314

4'6;

QUAD

T1/E1 LIU

4

PM4314

4'6;

QUAD

T1/E1 LIU

CHANNELIZED DS3 INTERFACE

PM4388

72&7/

Octal T1

Framer

PM6388

(2&7/

Octal E1

Framer

Processor

PM7364

)5(('0

™

Frame Engine

and Datalink

Manager

Packet

Memory

PCI Bus

DS3

LIU

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

PM8313

'0;

M13 Mux/Demux

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PM4388

72&7/

Octal T1

Framer

PM4388

72&7/

Octal T1

Framer

PM4388

72&7/

Octal T1

Framer

PM4388

72&7/

Octal T1

Framer

PM7364

)5(('0

™

Frame Engine

and Datalink

Manager

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

Processor

Packet

Memory

PCI Bus

PMC-960952 (R4)

1998 PMC-Sierra, Inc.

October, 1998

FREEDM-8, FREEDM-32, and

TimePipe are trademarks

of PMC-Sierra, Inc.

Loading...

Loading...