PMC-Sierra,Inc.

y

g

y g

y

y

g

g

y

g

y

g

g

g

y

gy

g

ge (

y

g

y

g

y

g

g

q

y

g

g

y

(

g

q

g

)

y

Quad J2, E3 and DS-3 Framer

PM7349

S/UNI®-4xD3F

FEATURES

• Quad DS-3, E3 (G.751 and G.832),

and J2 framers.

• Each channel can be independentl

confi

ured to be a DS-3, E3, or J2

Framer.

• Gapped transmit and receive clocks

can be optionall

interface to devices which onl

access to pa

• Provides pro

random test pattern

detection, and anal

• Provides inte

HDLC controllers with 128-b

depths.

• Provides performance monitorin

counters suitable for accumulation

periods of up to 1 second.

• Provides an 8-bit microprocessor

interface for configuration, control and

status monitorin

• Provides a standard five si

P1149.1 JTAG test port for boundar

enerated for

need

load data bits.

rammable pseudo-

eneration,

sis features.

ral transmit and receive

te FIFO

.

nal

scan board test purposes.

• Low power 3.3 V CMOS technolo

with 5 V tolerant inputs.

• Available in a hi

SBGA packa

h density 256-pin

27 mm x 27 mm).

RECEIVER SECTION

• Provides frame synchronization for the

M23 or C-bit parit

alarm detection, and accumulates line

code violations, framin

errors, path parit

events. In addition, far end alarm

channel codes are detected, and an

inte

terminate the path maintenance data

link.

• Provides frame s

G.751 or G.832 E3 applications, alarm

detection, and accumulates line code

violations, framin

and FEBE events. In addition, in

G.832, the Trail Trace is detected, and

an inte

to terminate either the Network

ral HDLC receiver is provided to

ral HDLC receiver is provided

DS3 applications,

errors, parity

errors and FEBE

nchronization for the

errors, parity errors,

Re

uirement or the General Purpose

data link.

• Provides frame s

nchronization for

G.704 and NTT 6.312 Mbit/s J2

applications, alarm detection, and

accumulates line code violations,

framin

errors, and CRC parity errors.

An inte

ral HDLC receiver is provided

to terminate the data link.

• Provides a receive HDLC controller

with a 128-b

te FIFO to accumulate

data link information.

• Provides detection of yellow alarm and

loss of frame

BIP-8 errors, framin

LOF), and accumulates

errors and FEBE

events.

• Provides programmable pseudo-

random test-se

232-1 bit len

ITU-T O.151 standards

uence detection (up to

th patterns conforming to

and analysis

features.

TRANSMITTER SECTION

• Provides frame insertion for the M23 or

C-bit parit

DS3 applications, alarm

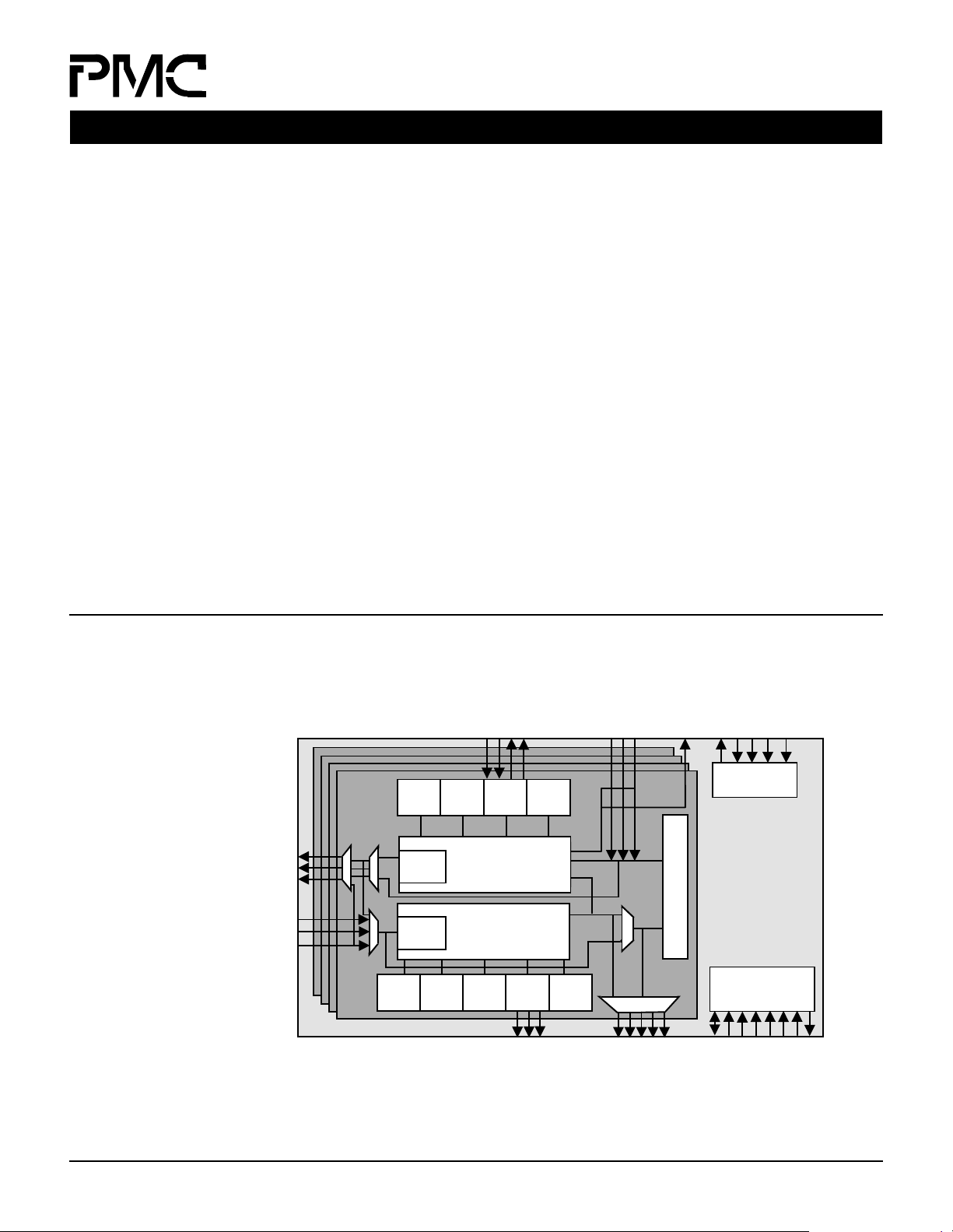

BLOCK DIAGRAM

TPOS/TDATO[4:1]

TNEG/TOHM[4:1]

RPOS/RDATI[4:1]

TCLK[4:1]

RCLK[4:1]

RNEG/RLCV[4:1]

RBOC

Rx

FEAC

XBOC

Tx

FEAC

Line

Encode

Line

Decode

RDLC

HDLC

TDPR

Tx

HDLC

J2, E3, or DS3

Transmit Framer

J2, E3, or DS3

Receive Framer

PMON

Rx

Perf.

Monitor

TOH[4:1]

TOHCLK[4:1]

TOHINS[4:1]

Tx

O/H

Access

TRAN

FRMR

O/H

Access

ROH [4:1]

TOHFP[4:1]

1/2 TTB

Tx Trail

Buffer

Rx

1/2 TTB

Rx Trail

Buffer

ROHPF [4:1]

ROHCLK [4:1]

TDAT[4:1]

TFPI/TMFP[4:1]

TICLK[4:1]

RDATO [4:1]

ROVRHD [4:1]

FRMSTAT[4:1]

TFPO/TMFPO/

TGAPCLK[4:1]

TDO

TCK

IEEE P1149.1

JTAG Test

Access Port

PRGD BER Tester

Microprocessor

ALE

D[7:0]

A[10:0]

RMFOP[4:1]

REF8KD/RFPO/

TDI

I/F

CSB

TMS

WRB

TRSTB

RDB

INTB

RSTB

PMC-2000369 (R2)

RSCLK/RGAPCLK[4:1]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

© Copyright PMC-Sierra, Inc. 2000

Quad J2, E3 and DS-3 Framer

g

q

g

g

q

g

g

g

ging

y

g

y

T

p

p

µ

y

PM7349 S/UNI®-4xD3F

insertion, and diagnostic features. In

addition, far end alarm channel codes

may be inserted, and an integral HDLC

transmitter is provided to insert the

path maintenance data link.

• Provides frame insertion for the G.751

or G.832 E3 applications, alarm

insertion, and dia

nostic features. In

addition, for G.832, the Trail Trace is

inserted, and an integral HDLC

transmitter is provided to insert either

the Network Re

uirement or the

General Purpose data link.

• Provides frame insertion for G.704

6.312 Mbit/s J2 applications, alarm

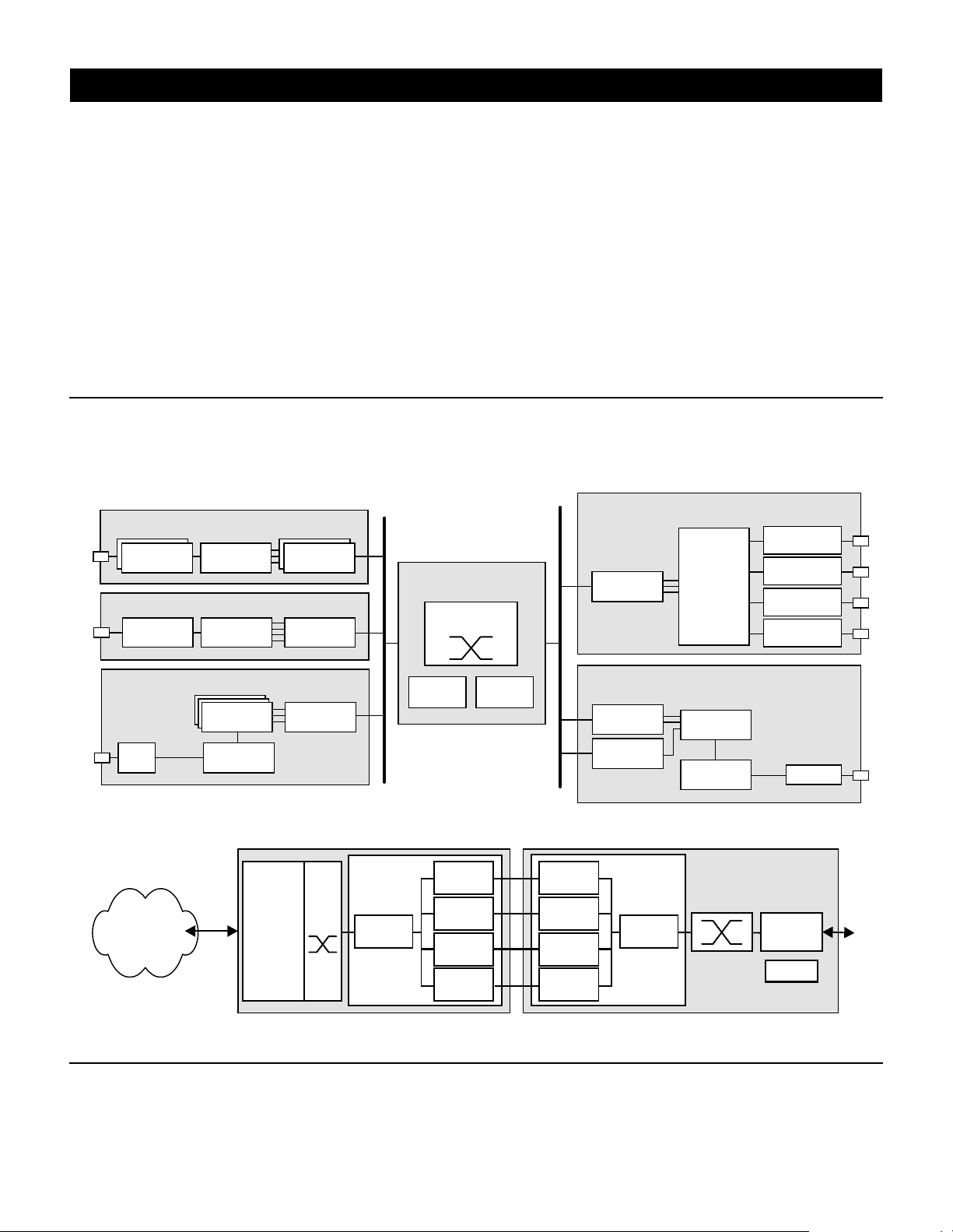

YPICAL APPLICATIONS

FRAME RELAY SWITCH/ROUTER

ACCESS SIDE

8 Port Channelized T1 Card

PM4314

QDSX

4 Port Channelized E1 Card

PM4314

QDSX

PM4388

TOCTL

PM6344

EQUAD

PM7366

FREEDM-8

PM7366

FREEDM-8

insertion, and diagnostic features. An

ral HDLC transmitter is provided

inte

to insert the path maintenance data

link.

• Provides a transmit HDLC controller

with a 128-byte FIFO.

• Provides pro

random test se

to 232-1 bit len

conformin

Dia

nostic abilities include single bit

rammable pseudo-

uence generation (up

th sequences

to ITU-T O.151 standards).

error insertion or error insertion at bit

error rates ran

PCI Bus

IP Switch/Router Core

from 10-1 to 10-7.

PCI Bus

Switch Fabric

LOOPBACK FEATURES

• Provides for diagnostic loopbacks, line

loopbacks, and pa

load loopbacks.

APPLICATIONS

• SONET/SDH Mux E3/DS-3 Tributary

Interfaces.

• PDH Mux J2/E3/DS-3 Line Interfaces.

• DS-3/E3/J2 Di

Interfaces.

• DS-3/E3/J2 PPP Internet Access

Interfaces.

• DS-3/E3/J2 Frame Rela

Unchannelized DS-3/E3/J2 Card

PM7366

FREEDM-8

S/UNI-4xD3F

ital Cross Connect

PM7349

Interfaces.

UPLINK SIDE

DS-3/E3/J2

LIU

DS-3/E3/J2

LIU

DS-3/E3/J2

LIU

DS-3/E3/J2

LIU

28 Port Unchannelized T1 Card (M13)

PM7364

FREEDM-32

DS-3

LIU

PM4388

TOCTL

PM8313

D3MX

WIRELESS BASE STATION APPLICATION

Public Switched

hone Network

Tele

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

DS-3

or Fibre

O

PM7349

S/UNI-4xD3F

tics

PM5342

SPECTRA-155

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

Switch

Fabric

or

PM7349

S/UNI-4xD3F

Base Station Controller

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

Egress

Device

DS-3/E3/J2

DS-3/E3/J2

DS-3/E3/J2

DS-3/E3/J2

LIU

LIU

LIU

LIU

PM7322

RCMP-800

PM7366

FREEDM-8

PM7366

FREEDM-8

DS-3/E3/J2

LIU

DS-3/E3/J2

LIU

DS-3/E3/J2

LIU

DS-3/E3/J2

LIU

Base Transceiver Station

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

Packet-Over-SONET Card

(3 DS-3s Over OC-3)

PM7349

S/UNI-4xD3F

PM5342

SPECTRA-155

PM7349

S/UNI-4xD3F

CDMA/TDMA/GSM

PMC-2000369 (R2)

© Copyright PMC-Sierra,

Inc. 2000. All rights reserved.

July 2000

S/UNI is a registered

trademark of PMC-Sierra,

Inc.

Optics

Tx/Rx RF

Subs

stem

P

Loading...

Loading...