PMC-Sierra,In

c.

5 Gbit/s ATM Switch Fabric Element

Released

PM73488

QSE

FEATURES

SWITCHING ALGORITHM

• Supports blocking resoluti on in the

switch fabric.

• Guarantees a lower bound on switch

performance using a patented

randomization algorithm called Evil

Twin Switching™.

• Determines routes using spec ifie d bits

in the header (self-routing switch

fabric) for unicast traffic.

• Determines output groupings using a

lookup table for multicast traffic.

• Allows output ports to be combined in

groups of 1, 2, 4, 8, 16, or 32 for

unicast traffic.

• Allows output ports to be combined in

groups of 1, 2, or 4 for multicast traffic.

MULTICAST SUPPORT

• Supports optimal tree-b as ed mu lti cast

replication in the switch fabric.

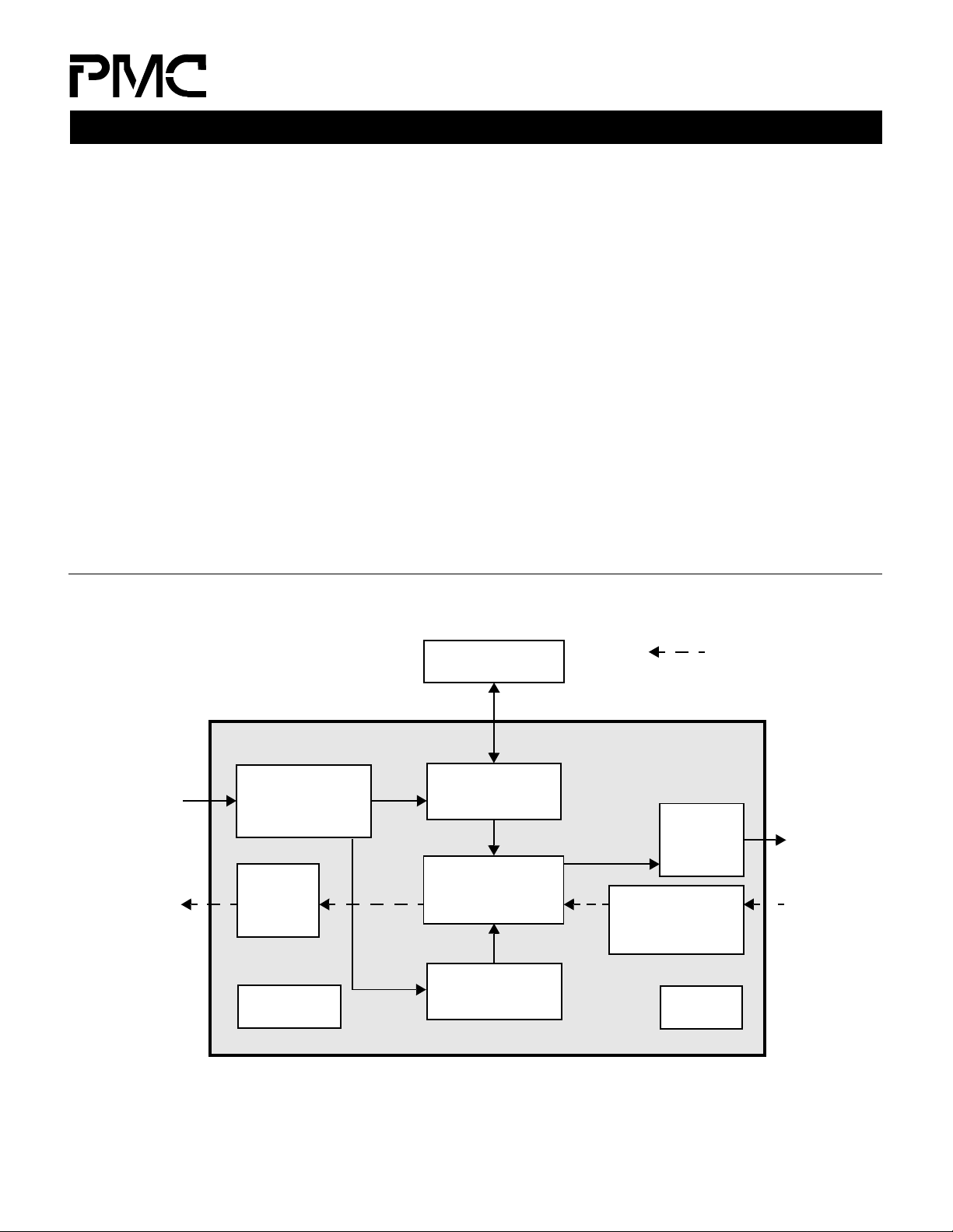

BLOCK DIAGRAM

• Supports 128 internal multicast

groups, expandable to 256 K with

external SRAM.

• Provides 64 internal cell buffers for

multicast cells.

DIAGNOSTIC/ROBUSTNESS

FEATURES

• Checks the header parity.

• Counts tagged cells.

• Checks for connectivity and stuck-at

faults on all swit ch fabr ic inte rconne cts.

I/O FEATURES

• Provides 32 switch fabric interfaces

with integrated phase aligner clock

recovery circuitry.

• Provides a Start-Of-Cell (SOC) output

per four switch element interfaces.

• Provides an external 16-bit

Synchronous SRAM (SSRAM)

interface for multicast group

expansion.

• Provides a demu ltiplexed add ress/data

CPU interface.

• Provides an IEEE 1149.1 (JTAG)

boundary scan test bus.

PHYSICAL CHARACTERISTICS

• 3.3 V supply voltage.

• 5 V tolerant inputs.

• 596-pin Enhanced Plastic Ball Grid

Array (EPBGA) package.

• Operates from a single 66 MHz clock.

APPLICATIONS

• A 5 Gbit/s Switch

• A 10 Gbit/s Switch

• A 5 Gbit/s-to-20 Gbit/s Scalabl e Switch

Architecture

• A 2.4 Gbit/s-to-80 Gbit/s Scalable

Switch Architecture

• A 5 Gbit/s-to-320 Gbit/s Scalable

Switch Architecture

To QRT/QSE

BP/ACK to

QRT/QSE

Phase Aligners

and

Receive SE_D_IN

and SE_SOC_IN

BP_ACK

Drivers

Microprocessor

Interface

External SSRAM

Multicast

Path

Arbiter

Unicast Routing and

Distribution Path

Backpressure/Ack Flow

Data

Drivers

Phase Aligners and

Receive

BP_ACK_IN

JTAG

To QRT/QSE

BP/ACK from

QRT/QSE

PMC-1980617 (R3) © 2001PMC-Sierra, Inc.

5 Gbit/s ATM Switch Fabric Element

TYPICAL APPLICATIONS

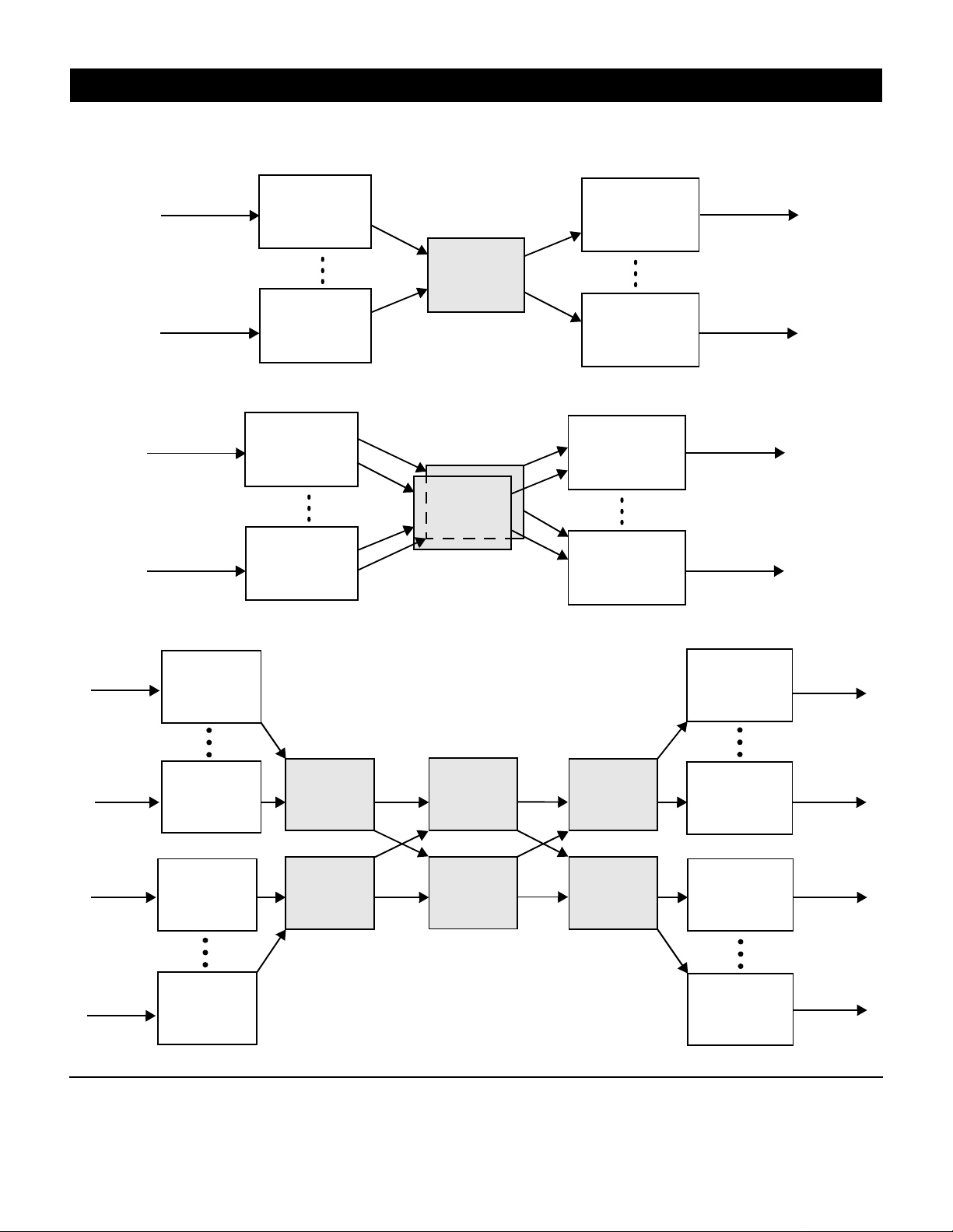

5 Gbit/s ATM SWITCH USING 8 QRTs AND 1 QSE

PM73488 QSE

622 Mbit/s

Aggregate

Receive UTOPIA

Level 2

622 Mbit/s

Aggregate

PM73487 #1

QRT™

Receive Input

PM73487 #8

QRT™

Receive Input

×

4

PM73488

4

×

QSE™

10 Gbit/s ATM SWITCH USING 16 QRTs AND 2 QSEs

622 Mbit/s

Aggregate

Receive UTOPIA

Level 2

622 Mbit/s

Aggregate

PM73487 #1

QRT™

Receive Input

PM73487 #16

QRT™

Receive Input

×

2

×

2

PM73488

2

×

2

×

QSE™

64 x 64 SWITCH APPLICATION (10 Gbit/s)

PM73487 #1

QRT™

4

×

×

2

×

2

×

×

×

2

Transmit Output

4

Transmit Output

PM73487 #1

Transmit Output

2

PM73487 #16

Transmit Output

PM73487 #8

QRT™

QRT™

QRT™

622 Mbit/s

Aggregate

Transmit UTOPIA

Level 2

622 Mbit/s

Aggregate

622 Mbit/s

Aggregate

Transmit UTOPIA

Level 2

622 Mbit/s

Aggregate

622 Mbit/s

Aggregate

Receive

UTOPIA

Level 2

622 Mbit/s

Aggregate

622 Mbit/s

Aggregate

Receive

UTOPIA

Level 2

622 Mbit/s

Aggregate

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

Receive Input

PM73487 #16

Receive Input

PM73487 #1

QRT™

Receive Input

PM73487 #8

QRT™

Receive Input

PM73487 #9

QRT™

QRT™

×

4

PM73488

QSE™

PM73488

QSE™

4

×

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

× 16

× 16

PM73488

QSE™

PM73488

QSE™

4

×

× 16

× 16

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

PM73488

QSE™

PM73488

QSE™

×

4

PM73487 #1

QRT™

Transmit Output

PM73487 #8

QRT™

Transmit Output

PM73487 #9

QRT™

Transmit Output

PM73487 #16

QRT™

Transmit Output

PMC-1980617 (R3)

© 2001 PMC-Sierra, Inc.

Evil Twin Switching, QRT, and

QSE are trademarks

of PMC-Sierra, Inc.

U.S. Patents pending

622 Mbit/s

Aggregate

Transmit

UTOPIA

Level 2

622 Mbit/s

Aggregate

622 Mbit/s

Aggregate

Transmit

UTOPIA

Level 2

622 Mbit/s

Aggregate

Loading...

Loading...