PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

PM7346

TM

S/UNI

-

QJET

S/UNI-QJET

SATURN QUAD USER NETWORK

INTERFACE FOR J2/E3/T3

DATASHEET

PROPRIETARY AND CONFIDENTIAL

ISSUE 6: MAY 1999

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

REVISION HISTORY

Issue No. Issue Date Details of Change

6 May 14, 1999

• The S/UNI-QJET requires a software

initialization sequence in order to

guarantee proper device operation and

long term reliability. Please refer to

Section 12.1 of this document for the

details on how to program this

sequence.

• Updated the RFCLK and TFCLK pin

descriptions to reflect that these pins are

not 5V tolerant. Both pins are 3.3V only

input pins.

• Documentation clarifications.

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS........................................................................................6

3 REFERENCES.........................................................................................7

4 APPLICATION EXAMPLES....................................................................10

5 BLOCK DIAGRAM..................................................................................13

6 DESCRIPTION.......................................................................................17

7 PIN DIAGRAM........................................................................................21

8 PIN DESCRIPTION................................................................................22

9 FUNCTIONAL DESCRIPTION...............................................................59

9.1 DS3 FRAMER..............................................................................59

9.2 E3 FRAMER ................................................................................61

9.3 J2 FRAMER.................................................................................63

9.3.1 J2 FRAME FIND ALGORITHMS.......................................65

9.4 PMON PERFORMANCE MONITOR ACCUMULATOR................68

9.5 RBOC BIT-ORIENTED CODE DETECTOR.................................68

9.6 RDLC FACILITY DATA LINK RECEIVER.....................................69

9.7 SPLR PLCP LAYER RECEIVER .................................................70

9.8 ATMF ATM CELL DELINEATOR ..................................................70

9.9 RXCP-50 RECEIVE CELL PROCESSOR...................................72

9.10 RXFF RECEIVE FIFO..................................................................74

9.11 CPPM CELL AND PLCP PERFORMANCE MONITOR...............75

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

i

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

9.12 PRGD PSEUDO-RANDOM SEQUENCE

GENERATOR/DETECTOR ..........................................................75

9.13 DS3 TRANSMITTER....................................................................76

9.14 E3 TRANSMITTER......................................................................77

9.15 J2 TRANSMITTER.......................................................................78

9.16 XBOC BIT ORIENTED CODE GENERATOR ..............................79

9.17 TDPR FACILITY DATA LINK TRANSMITTER..............................79

9.18 SPLT SMDS PLCP LAYER TRANSMITTER................................81

9.19 TXCP-50 TRANSMIT CELL PROCESSOR.................................82

9.20 TXFF TRANSMIT FIFO................................................................83

9.21 TTB TRAIL TRACE BUFFER.......................................................83

9.22 JTAG TEST ACCESS PORT........................................................84

9.23 MICROPROCESSOR INTERFACE.............................................84

10 NORMAL MODE REGISTER DESCRIPTION........................................91

11 TEST FEATURES DESCRIPTION .......................................................294

11.1 TEST MODE 0 DETAILS...........................................................300

11.2 JTAG TEST PORT......................................................................305

12 OPERATION.........................................................................................308

12.1 SOFTWARE INITIALIZATION SEQUENCE...............................308

12.2 REGISTER SETTINGS FOR BASIC CONFIGURATIONS ........310

12.3 PLCP FRAME FORMATS..........................................................311

12.3.1PLCP PATH OVERHEAD OCTET PROCESSING..........314

12.4 DS3 FRAME FORMAT..............................................................319

12.5 G.751 E3 FRAME FORMAT.......................................................321

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

ii

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

12.6 G.832 E3 FRAME FORMAT.......................................................323

12.7 J2 FRAME FORMAT..................................................................325

12.8 S/UNI-QJET CELL DATA STRUCTURE.....................................327

12.9 RESETTING THE RXFF AND TXFF FIFOS ..............................331

12.10 SERVICING INTERRUPTS........................................................331

12.11 USING THE PERFORMANCE MONITORING FEATURES.......332

12.12 USING THE INTERNAL FDL TRANSMITTER...........................333

12.13 USING THE INTERNAL DATA LINK RECEIVER.......................336

12.14 PRGD PATTERN GENERATION................................................341

12.14.1 GENERATING AND DETECTING REPETITIVE

PATTERNS......................................................................341

12.14.2 COMMON TEST PATTERNS...........................................

........................................................................................342

12.15 JTAG SUPPORT........................................................................344

13 FUNCTIONAL TIMING .........................................................................353

14 ABSOLUTE MAXIMUM RATINGS........................................................380

15 D.C. CHARACTERISTICS ....................................................................381

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS......384

17 A.C. TIMING CHARACTERISTICS.......................................................388

18 ORDERING AND THERMAL INFORMATION ......................................405

19 MECHANICAL INFORMATION.............................................................406

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

iii

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

LIST OF REGISTERS

REGISTER 000H, 100H, 200H, 300H: S/UNI-QJET CONFIGURATION 1.......92

REGISTER 001H, 101H, 201H, 301H: S/UNI-QJET CONFIGURATION 2.......95

REGISTER 002H, 102H, 202H, 302H: S/UNI-QJET TRANSMIT

CONFIGURATION..................................................................................97

REGISTER 003H, 103H, 203H, 303H: S/UNI-QJET RECEIVE

CONFIGURATION................................................................................100

REGISTER 004H, 104H, 204H, 304H: S/UNI-QJET DATA LINK AND FERF/RAI

CONTROL............................................................................................103

REGISTER 005H, 105H, 205H, 305H: S/UNI-QJET INTERRUPT STATUS...107

REGISTER 006H: S/UNI-QJET IDENTIFICATION, MASTER RESET, AND

GLOBAL MONITOR UPDATE ...............................................................108

REGISTER 007H, 107H, 207H, 307H: S/UNI-QJET CLOCK ACTIVITY

MONITOR AND INTERRUPT IDENTIFICATION..................................110

REGISTER 008H, 108H, 208H, 308H: SPLR CONFIGURATION..................112

REGISTER 009H, 109H, 209H, 309H: SPLR INTERRUPT ENABLE............114

REGISTER 00AH, 10AH, 20AH, 30AH: SPLR INTERRUPT STATUS............116

REGISTER 00BH, 10BH, 20BH, 30BH: SPLR STATUS.................................118

REGISTER 00CH, 10CH, 20CH, 30CH: SPLT CONFIGURATION.................120

REGISTER 00DH, 10DH, 20DH, 30DH: SPLT CONTROL.............................123

REGISTER 00EH, 10EH, 20EH, 30EH: SPLT DIAGNOSTICS AND G1 OCTET

..............................................................................................................125

REGISTER 00FH, 10FH, 20FH, 30FH: SPLT F1 OCTET ..............................127

REGISTER 010H, 110H, 210H, 310H: CHANGE OF PMON PERFORMANCE

METERS...............................................................................................128

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

iv

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

REGISTER 011H, 111H, 211H, 311H: PMON INTERRUPT ENABLE/STATUS

..............................................................................................................130

REGISTER 014H, 114H, 214H, 314H: PMON LINE CODE VIOLATION EVENT

COUNT LSB.........................................................................................131

REGISTER 015H, 115H, 215H, 315H: PMON LINE CODE VIOLATION EVENT

COUNT MSB........................................................................................132

REGISTER 016H, 116H, 216H, 316H: PMON FRAMING BIT ERROR EVENT

COUNT LSB.........................................................................................133

REGISTER 017H, 117H, 217H, 317H: PMON FRAMING BIT ERROR EVENT

COUNT MSB........................................................................................134

REGISTER 018H, 118H, 218H, 318H: PMON EXCESSIVE ZERO COUNT LSB

..............................................................................................................135

REGISTER 019H, 119H, 219H, 319H: PMON EXCESSIVE ZERO COUNT MSB

..............................................................................................................136

REGISTER 01AH, 11AH, 21AH, 31AH: PMON PARITY ERROR EVENT COUNT

LSB.......................................................................................................137

REGISTER 01BH, 11BH, 21BH, 31BH: PMON PARITY ERROR EVENT COUNT

MSB......................................................................................................138

REGISTER 01CH, 11CH, 21CH, 31CH: PMON PATH PARITY ERROR EVENT

COUNT LSB.........................................................................................139

REGISTER 01DH, 11DH, 21DH, 31DH: PMON PATH PARITY ERROR EVENT

COUNT MSB........................................................................................140

REGISTER 01EH, 11EH, 21EH, 31EH: PMON FEBE/J2-EXZS EVENT COUNT

LSB.......................................................................................................141

REGISTER 01FH, 11FH, 21FH, 31FH: PMON FEBE/J2-EXZS EVENT COUNT

MSB......................................................................................................142

REGISTER 021H, 121H, 221H, 321H: CPPM CHANGE OF CPPM

PERFORMANCE METERS..................................................................144

REGISTER 022H, 122H, 222H, 322H: CPPM B1 ERROR COUNT LSB.......145

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

v

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

REGISTER 023H, 123H, 223H, 323H: CPPM B1 ERROR COUNT MSB......146

REGISTER 024H, 124H, 224H, 324H: CPPM FRAMING ERROR EVENT

COUNT LSB.........................................................................................147

REGISTER 025H, 125H, 225H, 325H: CPPM FRAMING ERROR EVENT

COUNT MSB........................................................................................148

REGISTER 026H, 126H, 226H, 326H: CPPM FEBE COUNT LSB................149

REGISTER 027H, 127H, 227H, 327H: CPPM FEBE COUNT MSB ...............150

REGISTER 030H, 130H, 230H, 330H: DS3 FRMR CONFIGURATION.........151

REGISTER 031H, 131H, 231H, 331H: DS3 FRMR INTERRUPT ENABLE

(ACE=0)................................................................................................153

REGISTER 031H, 131H, 231H, 331H: DS3 FRMR ADDITIONAL

CONFIGURATION REGISTER (ACE=1)..............................................155

REGISTER 032H, 132H, 232H, 332H: DS3 FRMR INTERRUPT STATUS....158

REGISTER 033H, 133H, 233H, 333H: DS3 FRMR STATUS..........................160

REGISTER 034H, 134H, 234H, 334H: DS3 TRAN CONFIGURATION..........162

REGISTER 035H, 135H, 235H, 335H: DS3 TRAN DIAGNOSTIC.................164

REGISTER 038H, 138H, 238H, 338H: E3 FRMR FRAMING OPTIONS........166

REGISTER 039H, 139H, 239H, 339H: E3 FRMR MAINTENANCE OPTIONS

..............................................................................................................168

REGISTER 03AH, 13AH, 23AH, 33AH: E3 FRMR FRAMING INTERRUPT

ENABLE ...............................................................................................170

REGISTER 03BH, 13BH, 23BH, 33BH: E3 FRMR FRAMING INTERRUPT

INDICATION AND STATUS...................................................................172

REGISTER 03CH, 13CH, 23CH, 33CH: E3 FRMR MAINTENANCE EVENT

INTERRUPT ENABLE..........................................................................175

REGISTER 03DH, 13DH, 23DH, 33DH: E3 FRMR MAINTENANCE EVENT

INTERRUPT INDICATION....................................................................177

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

vi

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

REGISTER 03EH, 13EH, 23EH, 33EH: E3 FRMR MAINTENANCE EVENT

STATUS ................................................................................................179

REGISTER 040H, 140H, 240H, 340H: E3 TRAN FRAMING OPTIONS ........181

REGISTER 041H, 141H, 241H, 341H: E3 TRAN STATUS AND DIAGNOSTIC

OPTIONS .............................................................................................184

REGISTER 042H, 142H, 242H, 342H: E3 TRAN BIP-8 ERROR MASK........186

REGISTER 043H, 143H, 243H, 343H: E3 TRAN MAINTENANCE AND

ADAPTATION OPTIONS.......................................................................187

REGISTER 044H, 144H, 244H, 344H: J2-FRMR CONFIGURATION............189

REGISTER 045H, 145H, 245H, 345H: J2-FRMR STATUS.............................191

REGISTER 046H, 146H, 246H, 346H: J2-FRMR ALARM INTERRUPT ENABLE

..............................................................................................................192

REGISTER 047H, 147H, 247H, 347H: J2-FRMR ALARM INTERRUPT STATUS

..............................................................................................................194

REGISTER 048H, 148H, 248H, 348H: J2-FRMR ERROR/XBIT INTERRUPT

ENABLE ...............................................................................................196

REGISTER 049H, 149H, 249H, 349H: J2-FRMR ERROR/XBIT INTERRUPT

STATUS ................................................................................................198

REGISTER 04CH, 14CH, 24CH, 34CH: J2-TRAN CONFIGURATION ..........200

REGISTER 04DH, 14DH, 24DH, 34DH: J2-TRAN DIAGNOSTIC..................202

REGISTER 04EH, 14EH, 24EH, 34EH: J2-TRAN TS97 SIGNALING............204

REGISTER 04FH, 14FH, 24FH, 34FH: J2-TRAN TS98 SIGNALING.............205

REGISTER 050H, 150H, 250H,350H: RDLC CONFIGURATION...................206

REGISTER 051H, 151H, 251H, 351H: RDLC INTERRUPT CONTROL.........208

REGISTER 052H, 152H, 252H, 352H: RDLC STATUS..................................209

REGISTER 053H, 153H, 253H, 353H: RDLC DATA.......................................212

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

vii

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

REGISTER 054H, 154H, 254H, 354H: RDLC PRIMARY ADDRESS MATCH......

..............................................................................................................213

REGISTER 055H, 155H, 255H, 355H: RDLC SECONDARY ADDRESS MATCH

..............................................................................................................214

REGISTER 058H, 158H, 258H, 358H: TDPR CONFIGURATION..................215

REGISTER 059H, 159H, 259H, 359H: TDPR UPPER TRANSMIT THRESHOLD

..............................................................................................................217

REGISTER 05AH, 15AH, 25AH, 35AH: TDPR LOWER INTERRUPT

THRESHOLD .......................................................................................218

REGISTER 05BH, 15BH, 25BH, 35BH: TDPR INTERRUPT ENABLE ..........219

REGISTER 05CH, 15CH, 25CH, 35CH: TDPR INTERRUPT STATUS/UDR

CLEAR..................................................................................................221

REGISTER 05DH, 15DH, 25DH, 35DH: TDPR TRANSMIT DATA..................223

REGISTER 060H, 160H, 260H, 360H: RXCP-50 CONFIGURATION 1.........224

REGISTER 061H, 161H, 261H, 361H: RXCP-50 CONFIGURATION 2.........226

REGISTER 062H, 162H, 262H, 362H: RXCP-50 FIFO/UTOPIA CONTROL &

CONFIG................................................................................................229

REGISTER 063H, 163H, 263H, 363H: RXCP-50 INTERRUPT ENABLES AND

COUNTER STATUS..............................................................................231

REGISTER 064H, 164H, 264H, 364H: RXCP-50 STATUS/INTERRUPT STATUS

..............................................................................................................233

REGISTER 065H, 165H, 265H, 365H: RXCP-50 LCD COUNT THRESHOLD

(MSB) ...................................................................................................235

REGISTER 066H, 166H, 266H, 366H: RXCP-50 LCD COUNT THRESHOLD

(LSB) ....................................................................................................236

REGISTER 067H, 167H, 267H, 367H: RXCP-50 IDLE CELL HEADER

PATTERN..............................................................................................238

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

viii

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

REGISTER 068H, 168H, 268H, 368H: RXCP-50 IDLE CELL HEADER MASK

..............................................................................................................239

REGISTER 069H, 169H, 269H, 369H: RXCP-50 CORRECTED HCS ERROR

COUNT.................................................................................................240

REGISTER 06AH, 16AH, 26AH, 36AH: RXCP-50 UNCORRECTED HCS

ERROR COUNT...................................................................................241

REGISTER 06BH, 16BH, 26BH, 36BH: RXCP-50 RECEIVE CELL COUNTER

(LSB) ....................................................................................................242

REGISTER 06CH, 16CH, 26CH, 36CH: RXCP-50 RECEIVE CELL COUNTER

..............................................................................................................243

REGISTER 06DH, 16DH, 26DH, 36DH: RXCP-50 RECEIVE CELL COUNTER

(MSB) ...................................................................................................244

REGISTER 06EH, 16EH, 26EH, 36EH: RXCP-50 IDLE CELL COUNTER (LSB)

..............................................................................................................245

REGISTER 06FH, 16FH, 26FH, 36FH: RXCP-50 IDLE CELL COUNTER ....246

REGISTER 070H, 170H, 270H, 370H: RXCP-50 IDLE CELL COUNTER (MSB)

..............................................................................................................247

REGISTER 080H, 180H, 280H, 380H: TXCP-50 CONFIGURATION 1..........248

REGISTER 081H, 181H, 281H, 381H: TXCP-50 CONFIGURATION 2..........251

REGISTER 082H, 182H, 282H, 382H: TXCP-50 CELL COUNT STATUS......253

REGISTER 083H, 183H, 283H, 383H: TXCP-50 INTERRUPT ENABLE/STATUS

..............................................................................................................254

REGISTER 084H, 184H, 284H, 384H: TXCP-50 IDLE CELL HEADER

CONTROL............................................................................................256

REGISTER 085H, 185H, 285H, 385H: TXCP-50 IDLE CELL PAYLOAD

CONTROL............................................................................................257

REGISTER 086H, 186H, 286H, 386H: TXCP-50 TRANSMIT CELL COUNT

(LSB) ....................................................................................................258

REGISTER 087H, 187H, 287H, 387H: TXCP-50 TRANSMIT CELL COUNT.259

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

ix

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

REGISTER 088H, 188H, 288H, 388H: TXCP-50 TRANSMIT CELL COUNT

(MSB) ...................................................................................................260

REGISTER 090H, 190H, 290H, 390H: TTB CONTROL.................................261

REGISTER 091H, 191H, 291H, 391H: TTB TRAIL TRACE IDENTIFIER STATUS

..............................................................................................................263

REGISTER 092H, 192H, 292H, 392H: TTB INDIRECT ADDRESS...............265

REGISTER 093H, 193H, 293H, 393H: TTB INDIRECT DATA........................266

REGISTER 094H, 194H, 294H, 394H: TTB EXPECTED PAYLOAD TYPE LABEL267

REGISTER 095H, 195H, 295H, 395H: TTB PAYLOAD TYPE LABEL

CONTROL/STATUS..............................................................................269

REGISTER 098H, 198H, 298H, 398H: RBOC CONFIGURATION/INTERRUPT

ENABLE ...............................................................................................271

REGISTER 099H, 199H, 299H, 399H: RBOC INTERRUPT STATUS............272

REGISTER 09AH, 19AH, 29AH, 39AH: XBOC CODE...................................273

REGISTER 09BH, 19BH, 29BH, 39BH: S/UNI-QJET MISC...........................274

REGISTER 09CH, 19CH, 29CH, 39CH: S/UNI-QJET FRMR LOF STATUS. ..277

REGISTER 0A0H, 1A0H, 2A0H, 3A0H: PRGD CONTROL............................279

REGISTER 0A1H, 1A1H, 2A1H, 3A1H: PRGD INTERRUPT ENABLE/STATUS

..............................................................................................................281

REGISTER 0A2H, 1A2H, 2A2H, 3A2H: PRGD LENGTH ..............................283

REGISTER 0A3H, 1A3H, 2A3H, 3A3H: PRGD TAP.......................................284

REGISTER 0A4H, 1A4H, 2A4H, 3A4H: PRGD ERROR INSERTION REGISTER

..............................................................................................................285

REGISTER 0A8H, 1A8H, 2A8H, 3A8H: PATTERN INSERTION #1...............286

REGISTER 0A9H, 1A9H, 2A9H, 3A9H: PATTERN INSERTION #2...............287

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

x

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

REGISTER 0AAH, 1AAH, 2AAH, 3AAH: PATTERN INSERTION #3..............288

REGISTER 0ABH, 1ABH, 2ABH, 3ABH: PATTERN INSERTION #4..............289

REGISTER 0ACH, 1ACH, 2ACH, 3ACH: PRGD PATTERN DETECTOR #1..290

REGISTER 0ADH, 1ADH, 2ADH, 3ADH: PRGD PATTERN DETECTOR #2..291

REGISTER 0AEH, 1AEH, 2AEH, 3AEH: PRGD PATTERN DETECTOR #3..292

REGISTER 0AFH, 1AFH, 2AFH, 3AFH: PRGD PATTERN DETECTOR #4...293

REGISTER 400H: S/UNI-QJET MASTER TEST............................................299

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xi

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

LIST OF FIGURES

FIGURE 1 - S/UNI-QJET, AS AN ATM PHY, IN AN ATM SWITCH...................10

FIGURE 3 - S/UNI-QJET, AS A QUAD FRAMER DEVICE, IN FRAME RELAY

EQUIPMENT.....................................................................................................11

FIGURE 5 - S/UNI-QJET, AS A CELL PROCESSOR, IN DSLAM EQUIPMENT

12

FIGURE 7 - NORMAL OPERATING MODE.....................................................13

FIGURE 8 - DS3/E3/J2 FRAMERS BYPASSED..............................................14

FIGURE 9 - DS3/E3/J2 TRANSCEIVER MODE..............................................15

FIGURE 10- LOOPBACK MODES....................................................................16

FIGURE 11- FRAMING ALGORITHM (CRC_REFR = 0)..................................66

FIGURE 13- FRAMING ALGORITHM (CRC_REFR = 1)..................................67

FIGURE 15- CELL DELINEATION STATE DIAGRAM.......................................71

FIGURE 17- HCS VERIFICATION STATE DIAGRAM.......................................74

FIGURE 19- DS3 PLCP FRAME FORMAT.....................................................312

FIGURE 13- DS1 PLCP FRAME FORMAT.....................................................313

FIGURE 14- G.751 E3 PLCP FRAME FORMAT.............................................313

FIGURE 23- E1 PLCP FRAME FORMAT .......................................................314

FIGURE 16- DS3 FRAME STRUCTURE........................................................319

FIGURE 18- G.751 E3 FRAME STRUCTURE................................................321

FIGURE 20- G.832 E3 FRAME STRUCTURE................................................323

FIGURE 22- J2 FRAME STRUCTURE...........................................................325

FIGURE 24- 16-BIT WIDE, 26 WORD STRUCTURE......................................327

FIGURE 26- 16-BIT WIDE, 27 WORD STRUCTURE......................................328

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xii

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

FIGURE 28- 8-BIT WIDE, 52 WORD STRUCTURE........................................329

FIGURE 30- 8-BIT WIDE, 53 WORD STRUCTURE........................................330

FIGURE 32- TYPICAL DATA FRAME..............................................................339

FIGURE 33- EXAMPLE MULTI-PACKET OPERATIONAL SEQUENCE.........340

FIGURE 34- PRGD PATTERN GENERATOR .................................................341

FIGURE 36- BOUNDARY SCAN ARCHITECTURE........................................345

FIGURE 37- TAP CONTROLLER FINITE STATE MACHINE ..........................347

FIGURE 38- INPUT OBSERVATION CELL (IN_CELL)...................................350

FIGURE 39- OUTPUT CELL (OUT_CELL).....................................................351

FIGURE 40- BI-DIRECTIONAL CELL (IO_CELL)...........................................351

FIGURE 41- LAYOUT OF OUTPUT ENABLE AND BI-DIRECTIONAL CELLS

.....................................................................................................352

FIGURE 42- RECEIVE DS1 STREAM............................................................353

FIGURE 43- RECEIVE E1 STREAM ..............................................................353

FIGURE 44- RECEIVE BIPOLAR DS3 STREAM...........................................354

FIGURE 45- RECEIVE UNIPOLAR DS3 STREAM ........................................354

FIGURE 46- RECEIVE BIPOLAR E3 STREAM..............................................355

FIGURE 47- RECEIVE UNIPOLAR E3 STREAM...........................................355

FIGURE 48- RECEIVE BIPOLAR J2 STREAM ..............................................356

FIGURE 49- RECEIVE UNIPOLAR J2 STREAM............................................356

FIGURE 50- GENERIC RECEIVE STREAM ..................................................357

FIGURE 51- RECEIVE DS3 OVERHEAD.......................................................357

FIGURE 52- RECEIVE G.832 E3 OVERHEAD...............................................358

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xiii

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

FIGURE 53- RECEIVE G.751 E3 OVERHEAD...............................................359

FIGURE 54- RECEIVE J2 OVERHEAD..........................................................359

FIGURE 55- RECEIVE PLCP OVERHEAD....................................................360

FIGURE 56- TRANSMIT DS1 STREAM.........................................................361

FIGURE 57- TRANSMIT E1 STREAM............................................................361

FIGURE 58- TRANSMIT BIPOLAR DS3 STREAM.........................................362

FIGURE 59- TRANSMIT UNIPOLAR DS3 STREAM......................................362

FIGURE 60- TRANSMIT BIPOLAR E3 STREAM...........................................363

FIGURE 61- TRANSMIT UNIPOLAR E3 STREAM.........................................363

FIGURE 62- TRANSMIT BIPOLAR J2 STREAM............................................364

FIGURE 63- TRANSMIT UNIPOLAR J2 STREAM.........................................364

FIGURE 64- GENERIC TRANSMIT STREAM................................................365

FIGURE 65- TRANSMIT DS3 OVERHEAD ....................................................366

FIGURE 66- TRANSMIT G.832 E3 OVERHEAD............................................367

FIGURE 67- TRANSMIT G.751 E3 OVERHEAD............................................368

FIGURE 68- TRANSMIT J2 OVERHEAD........................................................368

FIGURE 69- TRANSMIT PLCP OVERHEAD..................................................369

FIGURE 70- FRAMER MODE DS3 TRANSMIT INPUT STREAM..................370

FIGURE 71- FRAMER MODE DS3 TRANSMIT INPUT STREAM WITH

TGAPCLK .....................................................................................................370

FIGURE 72- FRAMER MODE DS3 RECEIVE OUTPUT STREAM ................371

FIGURE 73- FRAMER MODE DS3 RECEIVE OUTPUT STREAM WITH

RGAPCLK .....................................................................................................371

FIGURE 74- FRAMER MODE G.751 E3 TRANSMIT INPUT STREAM..........371

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xiv

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

FIGURE 75- FRAMER MODE G.751 E3 TRANSMIT INPUT STREAM WITH

TGAPCLK .....................................................................................................372

FIGURE 76- FRAMER MODE G.751 E3 RECEIVE OUTPUT STREAM........372

FIGURE 77- FRAMER MODE G.751 E3 RECEIVE OUTPUT STREAM WITH

RGAPCLK .....................................................................................................372

FIGURE 78- FRAMER MODE G.832 E3 TRANSMIT INPUT STREAM..........373

FIGURE 79- FRAMER MODE G.832 E3 TRANSMIT INPUT STREAM WITH

TGAPCLK .....................................................................................................373

FIGURE 80- FRAMER MODE G.832 E3 RECEIVE OUTPUT STREAM........374

FIGURE 81- FRAMER MODE G.832 E3 RECEIVE OUTPUT STREAM WITH

RGAPCLK .....................................................................................................374

FIGURE 82- FRAMER MODE J2 TRANSMIT INPUT STREAM.....................374

FIGURE 83- FRAMER MODE J2 TRANSMIT INPUT STREAM WITH TGAPCLK

.....................................................................................................375

FIGURE 84- FRAMER MODE J2 RECEIVE OUTPUT STREAM ...................375

FIGURE 85- FRAMER MODE J2 RECEIVE OUTPUT STREAM WITH

RGAPCLK .....................................................................................................375

FIGURE 86- MULTI-PHY POLLING AND ADDRESSING TRANSMIT CELL

INTERFACE ....................................................................................................376

FIGURE 87- MULTI-PHY POLLING AND ADDRESSING RECEIVE CELL

INTERFACE ....................................................................................................377

FIGURE 88- MICROPROCESSOR INTERFACE READ TIMING....................385

FIGURE 90- MICROPROCESSOR INTERFACE WRITE TIMING..................387

FIGURE 92- RSTB TIMING ............................................................................388

FIGURE 94- TRANSMIT ATM CELL INTERFACE TIMING.............................389

FIGURE 96- RECEIVE ATM CELL INTERFACE TIMING ...............................391

FIGURE 98- TRANSMIT INTERFACE TIMING ...............................................394

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xv

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

FIGURE 100......................................................- RECEIVE INTERFACE TIMING

.....................................................................................................399

FIGURE 102..................................................- JTAG PORT INTERFACE TIMING

.....................................................................................................403

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xvi

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

LIST OF TABLES

TABLE 1 - SUPPORTED OPERATING FORMATS..........................................1

TABLE 2 - REGISTER MEMORY MAP .........................................................84

TABLE 3 - STATSEL[2:0] OPTIONS ..............................................................96

TABLE 4 - TFRM[1:0] TRANSMIT FRAME STRUCTURE CONFIGURATIONS

.......................................................................................................98

TABLE 5 - LOF[1:0] INTEGRATION PERIOD CONFIGURATION...............101

TABLE 6 - RFRM[1:0] RECEIVE FRAME STRUCTURE CONFIGURATIONS

.....................................................................................................101

TABLE 7 - SPLR FORM[1:0] CONFIGURATIONS.......................................113

TABLE 8 - PLCP LOF DECLARATION/REMOVAL TIMES..........................118

TABLE 9 - SPLT FORM[1:0] CONFIGURATIONS .......................................122

TABLE 10 - DS3 FRMR EXZS/LCV COUNT CONFIGURATIONS ................156

TABLE 11 - DS3 FRMR AIS CONFIGURATIONS .........................................157

TABLE 12 - E3 FRMR FORMAT[1:0] CONFIGURATIONS ............................167

TABLE 13 - E3 TRAN FORMAT[1:0] CONFIGURATIONS.............................181

TABLE 14 - J2 FRMR LOS THRESHOLD CONFIGURATIONS ....................190

TABLE 15 - RDLC PBS[2:0] DATA STATUS...................................................210

TABLE 16 - RXCP-50 HCS FILTERING CONFIGURATIONS........................226

TABLE 17 - RXCP-50 CELL DELINATION ALGORITHM BASE ...................227

TABLE 18 - RXCP-50 LCD INTEGRATION PERIODS..................................237

TABLE 19 - TXCP-50 FIFO DEPTH CONFIGURATIONS..............................252

TABLE 20 - TTB PAYLOAD TYPE MATCH CONFIGURATIONS....................267

TABLE 21 - PRGD PATTERN DETECTOR REGISTER CONFIGURATION..279

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xvii

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

TABLE 22 - PRGD GENERATED BIT ERROR RATE CONFIGURATIONS...285

TABLE 23 - TEST MODE REGISTER MEMORY MAP..................................294

TABLE 24 - TEST MODE 0 INPUT READ ADDRESS LOCATIONS..............300

TABLE 25 - TEST MODE 0 OUTPUT WRITE ADDRESS LOCATIONS ........302

TABLE 26 - INSTRUCTION REGISTER........................................................305

TABLE 27 - BOUNDARY SCAN REGISTER .................................................306

TABLE 28 - REGISTER SETTINGS FOR BASIC CONFIGURATIONS.........310

TABLE 29 - PLCP OVERHEAD PROCESSING............................................314

TABLE 30 - PLCP PATH OVERHEAD IDENTIFIER CODES.........................317

TABLE 32 - DS3 PLCP TRAILER LENGTH ..................................................318

TABLE 34 - E3 PLCP TRAILER LENGTH.....................................................318

TABLE 36 - DS3 FRAME OVERHEAD OPERATION ....................................320

TABLE 37 - G.751 E3 FRAME OVERHEAD OPERATION ............................322

TABLE 38 - G.832 E3 FRAME OVERHEAD OPERATION ............................323

TABLE 39 - J2 FRAME OVERHEAD OPERATION........................................326

TABLE 40 - PSEUDO RANDOM PATTERN GENERATION (PS BIT = 0)......342

TABLE 41 - REPETITIVE PATTERN GENERATION (PS BIT = 1).................343

TABLE 42 - DS3 RECEIVE OVERHEAD BITS..............................................358

TABLE 43 - DS3 TRANSMIT OVERHEAD BITS ...........................................366

TABLE 44 - ABSOLUTE MAXIMUM RATINGS..............................................380

TABLE 45 - DC CHARACTERISTICS............................................................381

TABLE 46 - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 88)

.....................................................................................................384

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xviii

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

TABLE 47 - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 90)

.....................................................................................................386

TABLE 48 - RSTB TIMING (FIGURE 92).......................................................388

TABLE 49 - TRANSMIT ATM CELL INTERFACE TIMING (FIGURE 94).......388

TABLE 50 - RECEIVE ATM CELL INTERFACE TIMING (FIGURE 96).........390

TABLE 51 - TRANSMIT INTERFACE TIMING (FIGURE 98).........................392

TABLE 52 - RECEIVE INTERFACE TIMING (FIGURE 100)..........................398

TABLE 53 - JTAG PORT INTERFACE (FIGURE 102)...................................402

TABLE 54 - PACKAGING INFORMATION .....................................................405

TABLE 55 - THERMAL INFORMATION.........................................................405

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

xix

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

1

FEATURES

Single chip quad ATM User Network Interface operating at 44.736 Mbit/s,

•

34.368 Mbit/s, and 6.312 Mbit/s conforming to ATMF-95-1207R1, ATMF-940406R5, and AF-PHY-0029.000. Each line can be individually configured for

the desired rate.

Implements ATM Direct Cell Mapping into DS1, DS3, E1, E3, and J2

•

transmission systems according to ITU-T Recommendation G.804.

Provides a UTOPIA Level 2 compatible ATM-PHY Interface.

•

Implements the Physical Layer Convergence Protocol (PLCP) for DS1 and

•

DS3 transmission systems according to the ATM Forum User Network

Interface Specification and ANSI TA-TSY-000773, TA-TSY-000772, and E1

and E3 transmission systems according to the ETSI 300-269 and ETSI 300-

270.

Support is provided for SMDS and ATM mappings into various rate

•

transmission systems as follows:

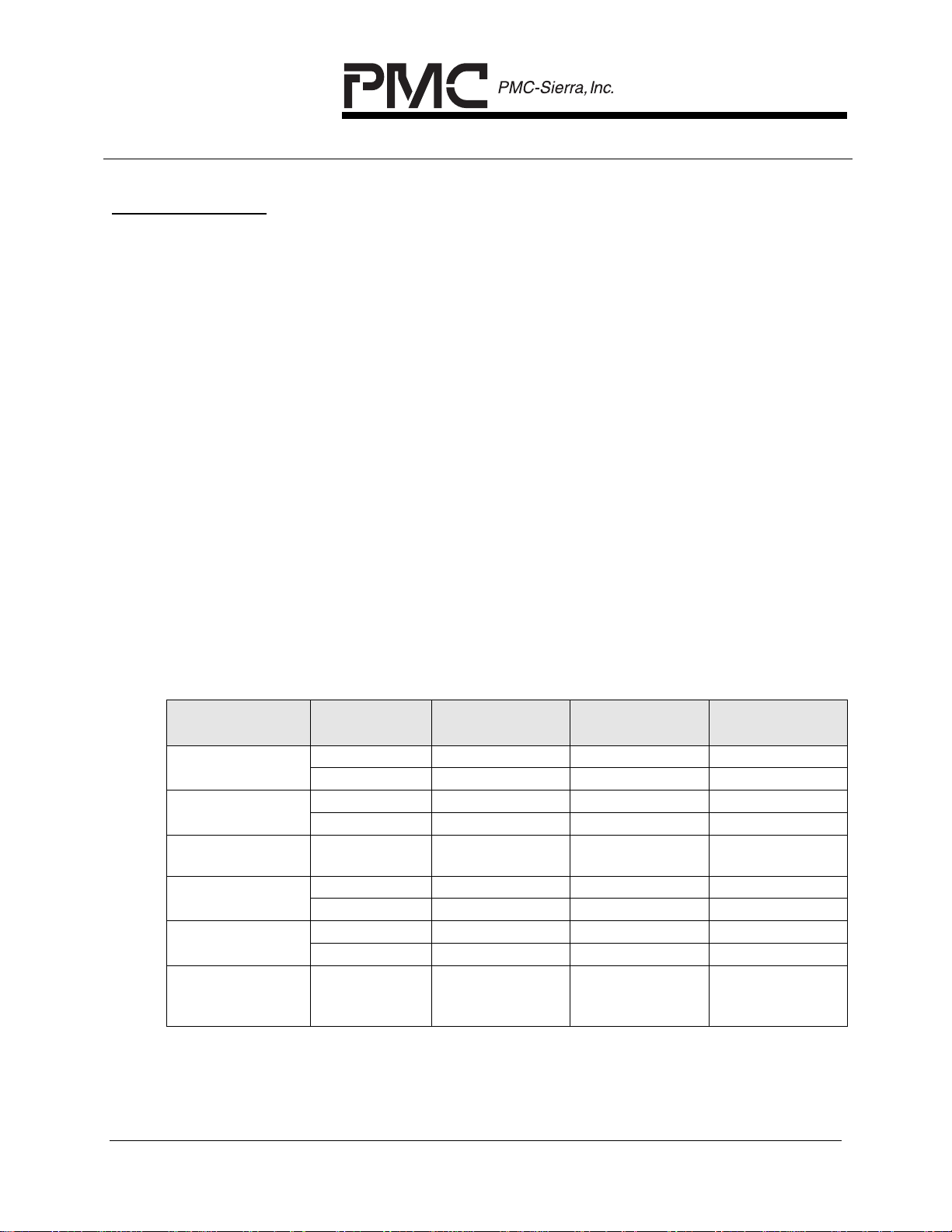

Table 1 - Supported Operating Formats

Rate Format

T3

(44.736 Mbit/s)

E3

(34.368 Mbit/s)

J2

(6.312 Mbit/s)

E1

(2.048 Mbit/s)

T1

(1.544 Mbit/s)

Arbitrary Cell

Rate

(up to 52 Mbit/s)

C-bit Parity

M23

G.751

G.832

G.704 & NTT

CRC-4

PCM30

ESF

SF

Framer

Only

YES YES YES

YES YES YES

YES YES YES

YES n/a YES

YES n/a YES

external YES YES

external YES YES

external YES YES

external YES YES

bypass n/a YES

SMDS PLCP

Mapping

ATM Direct

Mapping

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

1

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

Implements the ATM physical layer for Broadband ISDN according to ITU-T

•

Recommendation I.432.

Provides on-chip DS3, E3 (G.751 and G.832), and J2 framers.

•

Can be configured to be used solely as a DS3, E3, or J2 Framer.

•

When configured to operate as a DS3, E3, or J2 Framer, gapped transmit and

•

receive clocks can be optionally generated for interface to devices which only

need access to payload data bits.

Provides support for an arbitrary rate external transmission system interface

•

up to a maximum rate of 52 Mbit/s which enables the S/UNI-QJET to be used

as a quad ATM cell delineator.

Uses the PMC-Sierra PM4341 T1XC, PM4344 TQUAD, PM6341 E1XC, and

•

PM6344 EQUAD T1 and E1 framer/line interface chips for DS1 and E1

applications.

Provides programmable pseudo-random test pattern generation, detection,

•

and analysis features.

Provides integral transmit and receive HDLC controllers with 128-byte FIFO

•

depths.

Provides performance monitoring counters suitable for accumulation periods

•

of up to 1 second.

Provides an 8-bit microprocessor interface for configuration, control and

•

status monitoring.

Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

•

test purposes.

Low power 3.3V CMOS technology with 5V tolerant inputs.

•

Available in a high density 256-pin SBGA package (27mm x 27mm).

•

The receiver section:

Provides frame synchronization for the M23 or C-bit parity DS3 applications,

•

alarm detection, and accumulates line code violations, framing errors, parity

errors, path parity errors and FEBE events. In addition, far end alarm channel

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

2

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

codes are detected, and an integral HDLC receiver is provided to terminate

the path maintenance data link.

• Provides frame synchronization for the G.751 or G.832 E3 applications, alarm

detection, and accumulates line code violations, framing errors, parity errors,

and FEBE events. In addition, in G.832, the Trail Trace is detected, and an

integral HDLC receiver is provided to terminate either the Network

Requirement or the General Purpose data link.

• Provides frame synchronization for G.704 and NTT 6.312 Mbit/s J2

applications, alarm detection, and accumulates line code violations, framing

errors, and CRC parity errors. An integral HDLC receiver is provided to

terminate the data link.

• Provides frame synchronization, cell delineation and extraction for DS3,

G.751 E3, G.832 E3, and G.704 and NTT J2 ATM direct-mapped formats.

• Provides PLCP frame synchronization, path overhead extraction, and cell

extraction for DS1 PLCP, DS3 PLCP, E1 PLCP, and G.751 E3 PLCP

formatted streams.

• Provides a 50 MHz 8-bit wide or 16-bit wide Utopia FIFO buffer in the receive

path with parity support, and multi-PHY (Level 2) control signals.

• Provides ATM framing using cell delineation. ATM cell delineation may

optionally be disabled to allow passing of all cell bytes regardless of cell

delineation status.

• Provides cell descrambling, header check sequence (HCS) error detection,

idle cell filtering, header descrambling (for use with PPP packets), and

accumulates the number of received idle cells, the number of received cells

written to the FIFO, and the number of HCS errors.

• Provides a four cell FIFO for rate decoupling between the line, and a higher

layer processing entity. FIFO latency may be reduced by changing the

number of operational cell FIFOs.

• Provides a receive HDLC controller with a 128-byte FIFO to accumulate data

link information.

• Provides detection of yellow alarm and loss of frame (LOF), and accumulates

BIP-8 errors, framing errors and FEBE events.

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

3

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

Provides programmable pseudo-random test-sequence detection (up to 232-

•

1 bit length patterns conforming to ITU-T O.151 standards) and analysis

features.

The transmitter section:

Provides frame insertion for the M23 or C-bit parity DS3 applications, alarm

•

insertion, and diagnostic features. In addition, far end alarm channel codes

may be inserted, and an integral HDLC transmitter is provided to insert the

path maintenance data link.

Provides frame insertion for the G.751 or G.832 E3 applications, alarm

•

insertion, and diagnostic features. In addition, for G.832, the Trail Trace is

inserted, and an integral HDLC transmitter is provided to insert either the

Network Requirement or the General Purpose data link.

Provides frame insertion for G.704 6.312 Mbit/s J2 applications, alarm

•

insertion, and diagnostic features. An integral HDLC transmitter is provided

to insert the path maintenance data link.

Provides frame insertion and path overhead insertion for DS1, DS3, E1 or E3

•

based PLCP formats. In addition, alarm insertion and diagnostic features are

provided.

Provides a 50 MHz 8-bit wide or 16-bit wide Utopia FIFO buffer in the transmit

•

path with parity support and multi-PHY (Level 2) control signals.

Provides optional ATM cell scrambling, header scrambling (for use with PPP

•

packets), HCS generation/insertion, programmable idle cell insertion,

diagnostics features and accumulates transmitted cells read from the FIFO.

Provides a four cell FIFO for rate decoupling between the line and a higher

•

layer processing entity. FIFO latency may be reduced by changing the

number of operational cell FIFOs.

Provides a transmit HDLC controller with a 128-byte FIFO.

•

Provides an 8 kHz reference input for locking the transmit PLCP frame rate to

•

an externally applied frame reference.

Provides programmable pseudo-random test sequence generation (up to

•

232-1 bit length sequences conforming to ITU-T O.151 standards).

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

4

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

Diagnostic abilities include single bit error insertion or error insertion at bit

error rates ranging from 10-1 to 10-7.

Bypass and Loopback features:

• Allows bypassing of the DS3, E3, and J2 framers to enable transmission

system sublayer processing by an external device (for example, the PM4344

Quad DS1 Framer may be used for DS1-based services, and the PM6344

Quad E1 Framer may be used for E1-based services).

• Allows bypassing of the PLCP and ATM functions to enable use of the

S/UNI-QJET as a quad DS3, E3, or J2 framer.

• Provides for diagnostic loopbacks, line loopbacks, and payload loopbacks.

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

5

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

2

APPLICATIONS

ATM or SMDS Switches, Multiplexers, and Routers

•

SONET/SDH Mux E3/DS3 Tributary Interfaces

•

PDH Mux J2/E3/DS3 Line Interfaces

•

DS3/E3/J2 Digital Cross Connect Interfaces

•

DS3/E3/J2 PPP Internet Access Interfaces

•

DS3/E3/J2 Frame Relay Interfaces

•

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

6

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

3

REFERENCES

1. ANSI T1.627 - 1993, "Broadband ISDN - ATM Layer Functionality and Specification".

2. ANSI T1.107a - 1990, "Digital Hierarchy - Supplement to Formats Specifications

(DS3 Format Applications)".

3. ANSI T1.107 - 1995, "Digital Hierarchy - Formats Specifications".

4. ANSI T1.646 - 1995, "Broadband ISDN - Physical Layer Specification for UserNetwork Interfaces Including DS1/ATM".

5. ATM Forum - ATM User-Network Interface Specification, V3.1, October, 1995.

6. ATM Forum - “UTOPIA, An ATM PHY Interface Specification, Level 2, Version 1”,

June, 1995.

7. ATM Forum, 94-0406R5, "E3 (34,368 kbps) Physical Layer Interface", Dec. 21, 1994.

8. ATM Forum, 95-1207R1, "DS3 Physical Layer Interface Specification", December

1995.

9. ATM Forum, af-phy-0029.000, "6,312 Kbps UNI Specification, Version 1.0", June

1995.

10. Bell Communications Research, TA-TSY-000773 - “Local Access System Generic

Requirements, Objectives, and Interface in Support of Switched Multi-megabit Data

Service” Issue 2, March 1990 and Supplement 1, December 1990.

11. ETS 300 269 Draft Standard T/NA(91)17 - “Metropolitan Area Network Physical

Layer Convergence Procedure for 2.048 Mbit/s”, April 1994.

12. ETS 300 270 Draft Standard T/NA(91)18 - “Metropolitan Area Network Physical

Layer Convergence Procedure for 34.368 Mbit/s”, April 1994.

13. ITU-T Recommendation O.151 - "Error Performance Measuring Equipment

Operating at the Primary Rate and Above", October, 1992.

14. ITU-T Recommendation I.432 - "B-ISDN User-Network Interface - Physical Layer

Specification", 1993

15. ITU-T Recommendation G.703 - "Physical/Electrical Characteristics of Hierarchical

Digital Interfaces", 1991.

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

7

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

16. ITU-T Recommendation G.704 - "General Aspects of Digital Transmission Systems;

Terminal Equipments - Synchronous Frame Structures Used At 1544, 6312, 2048,

8488 and 44 736 kbit/s Hierarchical Levels", July, 1995.

17. ITU-T Recommendation G.751 - CCITT Blue Book Fa sc. III.4, "Digital Multiplex

Equipments Operating at the Third Order Bit Rate of 34,368 kbit/s and the Fourth

Order Bit Rate of 139,264 kbit/s and Using Positive Justification", 1988.

18. ITU-T Draft Recommendation G.775 - "Loss of Signal (LOS) and Alarm Indication

Signal (AIS) Defect Detection and Clearance Criteria", October 1993.

19. ITU-T Recommendation G.804 - "ATM Cell Mapping into Plesiochronous Digital

Hierarchy (PDH)", 1993.

20. ITU-T Recommendation G.832 - "Transpor t of SDH Elements on PDH Networks:

Frame and Multiplexing Structures", 1993.

21. ITU-T Recommendation Q.921 - "ISDN User-Network Interface - Data Link Layer

Specification", March, 1993.

22. NTT Technical Reference, "NTT Technical Reference for High-Speed Digital Leased

Circuit Services", 1991.

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

8

PM7346 S/UNI-QJET

DATASHEET

PMC-960835 ISSUE 6 SATURN QUAD USER NETWORK INTERFACE FOR J2, E3, T3

4

APPLICATION EXAMPLES

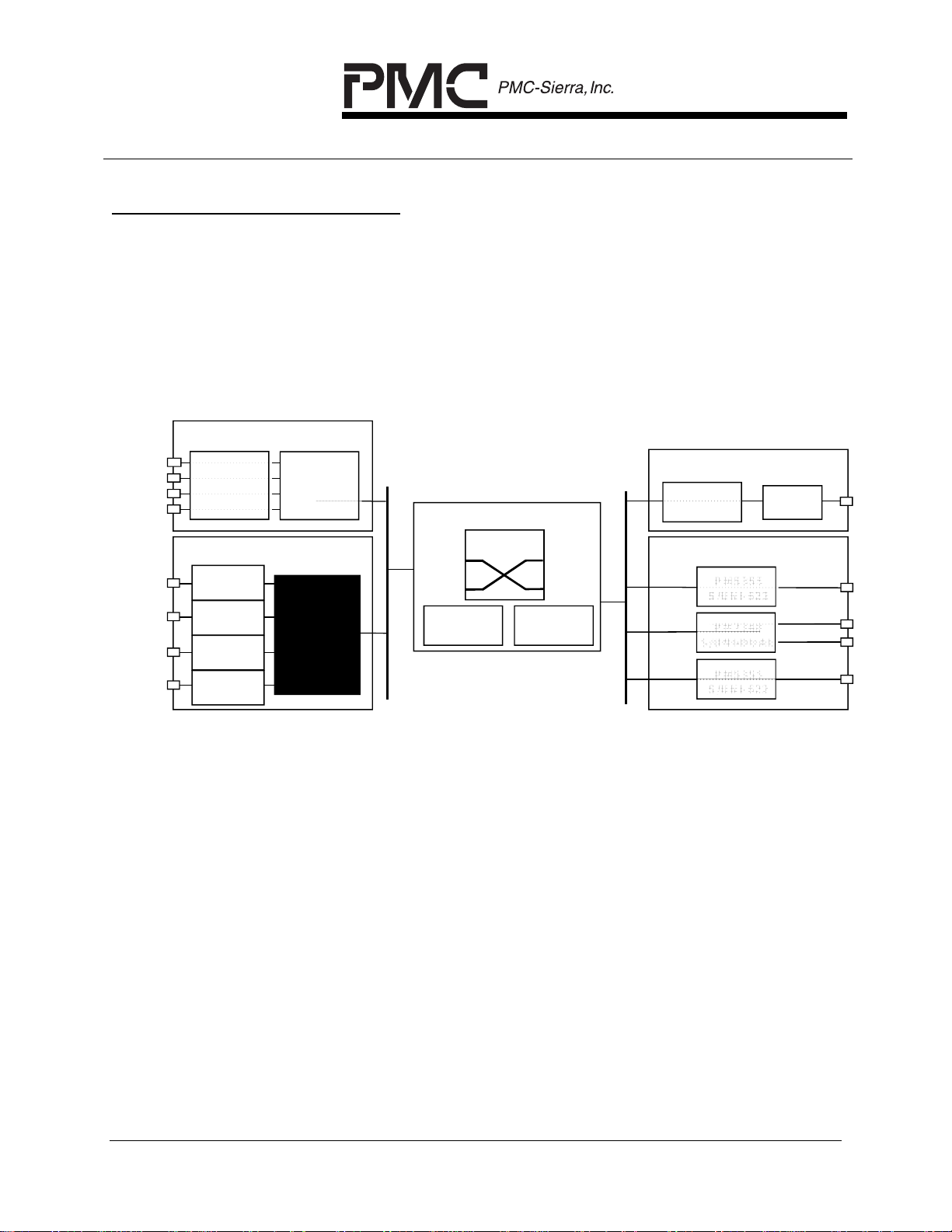

The S/UNI-QJET can be configured as an ATM physical layer device. On the line

side, it connects to one or more J2/E3/T3 line interface units and on the system

side, the S/UNI-QJET interfaces to the ATM layer device, such as PM7322

RCMP-800, over an 8 or 16 bit wide UTOPIA Level 2 interface (as shown in

Figure 1).

Figure 1 - S/UNI-QJET, as an ATM PHY, in an ATM Switch

T1/E1 Line Card

PM4314

QDSX

PM7344

S/UNI-MPH

J2/E3/T3 Line Card

J2/E3/T3

LIU

J2/E3/T3

LIU

J2/E3/T3

LIU

J2/E3/T3

LIU

PM7346

PM5355

PM7346

S/UNI-QJET

S/UNI-622

S/UNI-QJET

UT O P IA Bus

ATM Switch Core

Switch

Fabric

PM7322

RCMP-800

Egress

Device

UT O P IA Bus

OC-12 Line Card

PM5355

S/UNI-622

OC-3 Line Cards

PM5346

PM5355

S/UNI-LITE

S/UNI-622

PM7348

PM7348

S/UNI-DUAL

S/UNI-DUAL

PM5347

PM5355

S/UNI-PLUS

S/UNI-622

PMD

PMC-SIERRA, INC. PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC., AND ITS CUSTOMERS’ INTERNAL USE

9

Loading...

Loading...