PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM7345

TM

P

DH

S/

UNI-

S/UNI-PDH

SATURN USER-NETWORK INTERFACE FOR ATM PLESIOCHRONOUS

DIGITAL HIERARCHY DATACOM

DATA SHEET

ISSUE 6: JUNE 1998

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PUBLIC REVISION HISTORY

Issue

No.

Issue

Date

Details of Change

6 June

1998

Data Sheet Reformatted — No

Change in Technical Content.

Generated R6 data sheet from

PMC-930818, R9

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS........................................................................................4

3 REFERENCES.........................................................................................4

4 APPLICATION EXAMPLES......................................................................6

5 BLOCK DIAGRAM....................................................................................9

6 DESCRIPTION.......................................................................................12

7 PIN DIAGRAM........................................................................................15

8 PIN DESCRIPTION................................................................................17

9 FUNCTIONAL DESCRIPTION...............................................................41

9.1 DS3 FRAMER..............................................................................41

9.2 E3 FRAMER ................................................................................43

9.3 PMON PERFORMANCE MONITOR ACCUMULATOR................45

9.4 RBOC BIT-ORIENTED CODE DETECTOR.................................45

9.5 RFDL FACILITY DATA LINK RECEIVER.....................................46

9.6 SPLR PLCP LAYER RECEIVER .................................................47

9.7 ATMF ATM CELL DELINEATOR ..................................................47

9.8 RXCP RECEIVE CELL PROCESSOR ........................................49

9.9 RXFF RECEIVE FIFO..................................................................51

9.10 CPPM CELL AND PLCP PERFORMANCE MONITOR...............52

9.11 DS3 TRANSMITTER....................................................................52

9.12 E3 TRANSMITTER......................................................................53

9.13 XBOC BIT ORIENTED CODE GENERATOR ..............................55

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

9.14 XFDL FACILITY DATA LINK TRANSMITTER...............................55

9.15 SPLT SMDS PLCP LAYER TRANSMITTER................................56

9.16 TXCP TRANSMIT CELL PROCESSOR ......................................57

9.17 TXFF TRANSMIT FIFO................................................................57

9.18 TTB TRAIL TRACE BUFFER.......................................................59

9.19 MICROPROCESSOR INTERFACE .............................................59

9.20 NORMAL MODE REGISTER MEMORY MAP.............................60

10 NORMAL MODE REGISTER DESCRIPTION........................................63

10.1 BASIC OPERATING MODES ....................................................215

11 TEST FEATURES DESCRIPTION .......................................................217

11.1 TEST MODE 0...........................................................................221

12 OPERATION.........................................................................................225

12.1 PLCP FRAME FORMATS..........................................................225

12.2 PLCP PATH OVERHEAD OCTET PROCESSING.....................227

12.3 G.832 E3 FRAME FORMAT.......................................................231

12.4 G.832 E3 PATH OVERHEAD OCTET PROCESSING...............231

12.5 S/UNI-PDH CELL DATA STRUCTURE ......................................233

12.6 USING THE PERFORMANCE MONITORING FEATURES.......234

12.7 USING THE INTERNAL DATA LINK TRANSMITTER ................235

12.8 USING THE INTERNAL DATA LINK RECEIVER .......................236

12.9 SILICON SYSTEMS 78P7200 IMPLEMENTATION...................238

13 FUNCTIONAL TIMING .........................................................................241

14 ABSOLUTE MAXIMUM RATINGS........................................................262

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

15 D.C. CHARACTERISTICS ....................................................................263

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS......266

17 S/UNI-PDH TIMING CHARA CTERISTICS...........................................271

18 ORDERING AND THERMAL INFORMATION ......................................288

19 MECHANICAL INFORMATION .............................................................289

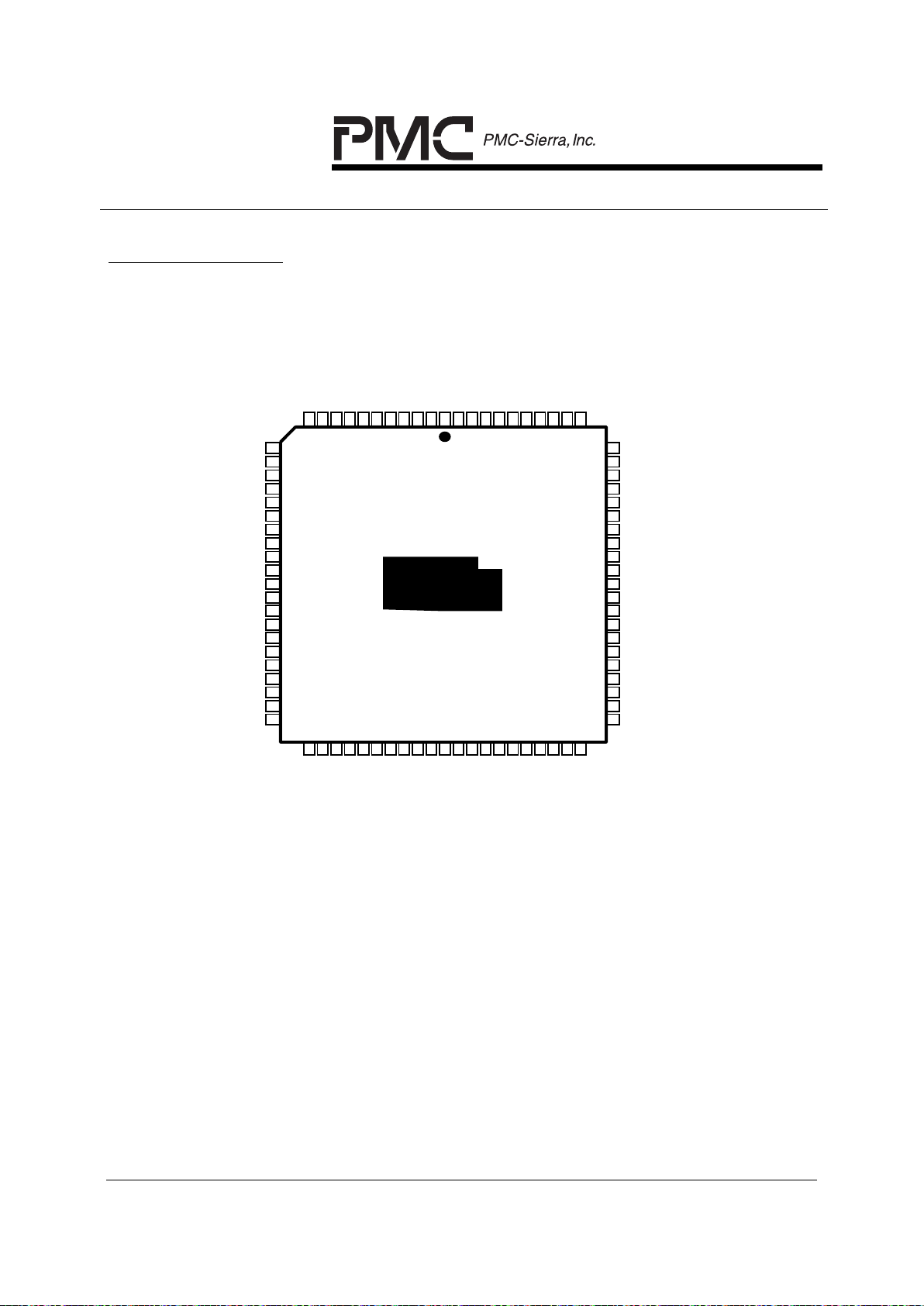

19.1 84 PIN PLASTIC LEADED CHIP CARRIER (Q SUFFIX):.........289

19.2 100 PIN PLASTIC QUAD FLAT PACK (R SUFFIX):...................290

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

LIST OF REGISTERS

REGISTER 00H: S/UNI-PDH CONFIGURATION..............................................64

REGISTER 01H: S/UNI-PDH INTERRUPT ENABLE.......................................67

REGISTER 02H: S/UNI-PDH INTERRUPT STATUS........................................68

REGISTER 03H: S/UNI-PDH CONTROL.........................................................69

REGISTER 04H: S/UNI-PDH IDENTIFICATION AND MASTER RESET.........71

REGISTER 05H: S/UNI-PDH DATA LINK AND FERF CONTROL.....................72

REGISTER 06H: RBOC CONFIGURATION/INTERRUPT ENABLE .................75

REGISTER 07H: RBOC INTERRUPT STATUS.................................................76

REGISTER 08H: DS3 FRMR CONFIGURATION.............................................77

REGISTER 09H: DS3 FRMR INTERRUPT ENABLE (ACE=0) ........................79

REGISTER 09H: DS3 FRMR ADDITIONAL CONFIGURATION REGISTER

(ACE=1)..................................................................................................81

REGISTER 0AH: DS3 FRMR INTERRUPT STATUS........................................84

REGISTER 0BH: DS3 FRMR STATUS.............................................................86

REGISTER 0CH: RFDL CONFIGURATION ......................................................88

REGISTER 0DH: RFDL ENABLE/STATUS .......................................................89

REGISTER 0EH: RFDL STATUS.......................................................................90

REGISTER 0FH: RFDL RECEIVE DATA...........................................................92

REGISTER 10H: S/UNI-PDH CHANGE OF PMON PERFORMANCE METERS

................................................................................................................93

REGISTER 11H: PMON INTERRUPT ENABLE/STATUS ................................94

REGISTER 14H: PMON LINE CODE VIOLATION EVENT COUNT LSB.........95

REGISTER 15H: PMON LINE CODE VIOLATION EVENT COUNT MSB........96

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

REGISTER 16H: PMON FRAMING BIT ERROR EVENT COUNT LSB...........97

REGISTER 17H: PMON FRAMING BIT ERROR EVENT COUNT MSB..........98

REGISTER 18H: PMON SUMMED EXCESSIVE ZERO DETECT AND

INCOMING ERROR COUNT LSB..........................................................99

REGISTER 19H: PMON SUMMED EXCESSIVE ZERO DETECT AND

INCOMING ERROR COUNT MSB.......................................................100

REGISTER 1AH: PMON PARITY ERROR EVENT COUNT LSB...................101

REGISTER 1BH: PMON PARITY ERROR EVENT COUNT MSB..................102

REGISTER 1CH: PMON PATH PARITY ERROR EVENT COUNT LSB.........103

REGISTER 1DH: PMON PATH PARITY ERROR EVENT COUNT MSB........104

REGISTER 1EH: PMON FEBE EVENT COUNT LSB ....................................105

REGISTER 1FH: PMON FEBE EVENT COUNT MSB...................................106

REGISTER 20H: DS3 TRAN CONFIGURATION............................................107

REGISTER 21H: DS3 TRAN DIAGNOSTIC...................................................109

REGISTER 24H: XFDL CONFIGURATION.....................................................111

REGISTER 25H: XFDL INTERRUPT STATUS................................................113

REGISTER 26H: XFDL TRANSMIT DATA.......................................................114

REGISTER 27H: XBOC CODE.......................................................................115

REGISTER 28H: SPLR CONFIGURATION....................................................116

REGISTER 29H: SPLR INTERRUPT ENABLE..............................................118

REGISTER 2AH: SPLR INTERRUPT STATUS ..............................................119

REGISTER 2BH: SPLR STATUS....................................................................121

REGISTER 2CH: SPLT CONFIGURATION....................................................123

REGISTER 2DH: SPLT CONTROL................................................................126

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

REGISTER 2EH: SPLT DIAGNOSTICS AND G1 OCTET..............................128

REGISTER 2FH: SPLT F1 OCTET.................................................................130

REGISTER 30H: CPPM LOSS OF CLOCK METERS....................................131

REGISTER 31H: CPPM CHANGE OF CPPM PERFORMANCE METERS...132

REGISTER 32H: CPPM B1 ERROR COUNT LSB.........................................133

REGISTER 33H: CPPM B1 ERROR COUNT MSB........................................134

REGISTER 34H: CPPM FRAMING ERROR EVENT COUNT LSB................135

REGISTER 35H: CPPM FRAMING ERROR EVENT COUNT MSB................136

REGISTER 36H: CPPM FEBE COUNT LSB .................................................137

REGISTER 37H: CPPM FEBE COUNT MSB ................................................138

REGISTER 38H: CPPM HCS ERROR COUNT LSB .....................................139

REGISTER 39H: CPPM HCS ERROR COUNT MSB ....................................140

REGISTER 3AH: CPPM IDLE/UNASSIGNED CELL COUNT LSB................142

REGISTER 3BH: CPPM IDLE/UNASSIGNED CELL COUNT MSB...............143

REGISTER 3CH: CPPM RECEIVE CELL COUNT LSB.................................144

REGISTER 3DH: CPPM RECEIVE CELL COUNT MSB................................145

REGISTER 3EH: CPPM TRANSMIT CELL COUNT LSB..............................146

REGISTER 3FH: CPPM TRANSMIT CELL COUNT MSB..............................147

REGISTER 40H: RXCP CONTROL................................................................148

REGISTER 41H: RXCP FRAMING CONTROL...............................................150

REGISTER 42H: RXCP INTERRUPT ENABLE/STATUS ................................152

REGISTER 43H: RXCP IDLE/UNASSIGNED CELL PATTERN: H1 OCTET...154

REGISTER 44H: RXCP IDLE/UNASSIGNED CELL PATTERN: H2 OCTET...155

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

REGISTER 45H: RXCP IDLE/UNASSIGNED CELL PATTERN: H3 OCTET...156

REGISTER 46H: RXCP IDLE/UNASSIGNED CELL PATTERN: H4 OCTET...157

REGISTER 47H: RXCP IDLE/UNASSIGNED CELL MASK: H1 OCTET ........158

REGISTER 48H: RXCP IDLE/UNASSIGNED CELL MASK: H2 OCTET ........159

REGISTER 49H: RXCP IDLE/UNASSIGNED CELL MASK: H3 OCTET ........160

REGISTER 4AH: RXCP IDLE/UNASSIGNED CELL MASK: H4 OCTET........161

REGISTER 4BH: RXCP USER-PROGRAMMABLE MATCH PATTERN: H1

OCTET .................................................................................................162

REGISTER 4CH: RXCP USER-PROGRAMMABLE MATCH PATTERN: H2

OCTET .................................................................................................163

REGISTER 4DH: RXCP USER-PROGRAMMABLE MATCH PATTERN: H3

OCTET .................................................................................................164

REGISTER 4EH: RXCP USER-PROGRAMMABLE MATCH PATTERN: H4

OCTET .................................................................................................165

REGISTER 4FH: RXCP USER-PROGRAMMABLE MATCH MASK: H1 OCTET

..............................................................................................................166

REGISTER 50H: RXCP USER-PROGRAMMABLE MATCH MASK: H2 OCTET

..............................................................................................................167

REGISTER 51H: RXCP USER-PROGRAMMABLE MATCH MASK 2: H3 OCTET

..............................................................................................................168

REGISTER 52H: RXCP USER-PROGRAMMABLE MATCH MASK 2: H4 OCTET

..............................................................................................................169

REGISTER 53H: RXCP HCS CONTROL/STATUS..........................................170

REGISTER 54H: RXCP LCD COUNT THRESHOLD......................................171

REGISTER 58H: TXCP CONTROL................................................................172

REGISTER 59H: TXCP INTERRUPT ENABLE/STATUS AND CONTROL.....174

REGISTER 5AH: TXCP IDLE/UNASSIGNED CELL PATTERN: H1 OCTET..176

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

REGISTER 5BH: TXCP IDLE/UNASSIGNED CELL PATTERN: H2 OCTET..177

REGISTER 5CH: TXCP IDLE/UNASSIGNED CELL PATTERN: H3 OCTET..178

REGISTER 5DH: TXCP IDLE/UNASSIGNED CELL PATTERN: H4 OCTET..179

REGISTER 5EH: TXCP IDLE/UNASSIGNED CELL PATTERN: H5 OCTET..180

REGISTER 5FH: TXCP IDLE/UNASSIGNED CELL PAYLOAD......................181

REGISTER 60H: E3 FRMR FRAMING OPTIONS .........................................182

REGISTER 61H: E3 FRMR MAINTENANCE OPTIONS................................184

REGISTER 62H: E3 FRMR FRAMING INTERRUPT ENABLE......................186

REGISTER 63H: E3 FRMR FRAMING INTERRUPT INDICATION AND STATUS

..............................................................................................................188

REGISTER 64H: E3 FRMR MAINTENANCE EVENT INTERRUPT ENABLE190

REGISTER 65H: E3 FRMR MAINTENANCE EVENT INTERRUPT INDICATION

..............................................................................................................192

REGISTER 66H: E3 FRMR MAINTENANCE EVENT STATUS......................194

REGISTER 68H: E3 TRAN FRAMING OPTIONS...........................................196

REGISTER 69H: E3 TRAN STATUS AND DIAGNOSTIC OPTIONS...............198

REGISTER 6AH: E3 TRAN BIP-8 ERROR MASK ..........................................200

REGISTER 6BH: E3 TRAN MAINTENANCE AND ADAPTATION OPTIONS.201

REGISTER 6CH: TTB CONTROL...................................................................203

REGISTER 6DH: TTB TRAIL TRA CE IDENTIFIER STA TUS...........................205

REGISTER 6EH: TTB INDIRECT ADDRESS..................................................207

REGISTER 6FH: TTB INDIRECT DATA...........................................................208

REGISTER 70H: TTB EXPECTED PAYLOAD TYPE LABEL...........................209

REGISTER 71H: TTB PAYLOAD TYPE LABEL CONTROL/STATUS: .............211

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

REGISTER 74H: SYNC FIFO PA RITY CONTROL/STATUS:...........................213

ADDRESS 80H MASTER TEST......................................................................220

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

LIST OF FIGURES

FIGURE 1 - DS3 AND E3 USER NETWORK INTERFACE ...............................7

FIGURE 2 - DS1 AND E1 USER NETWORK INTERFACE ...............................8

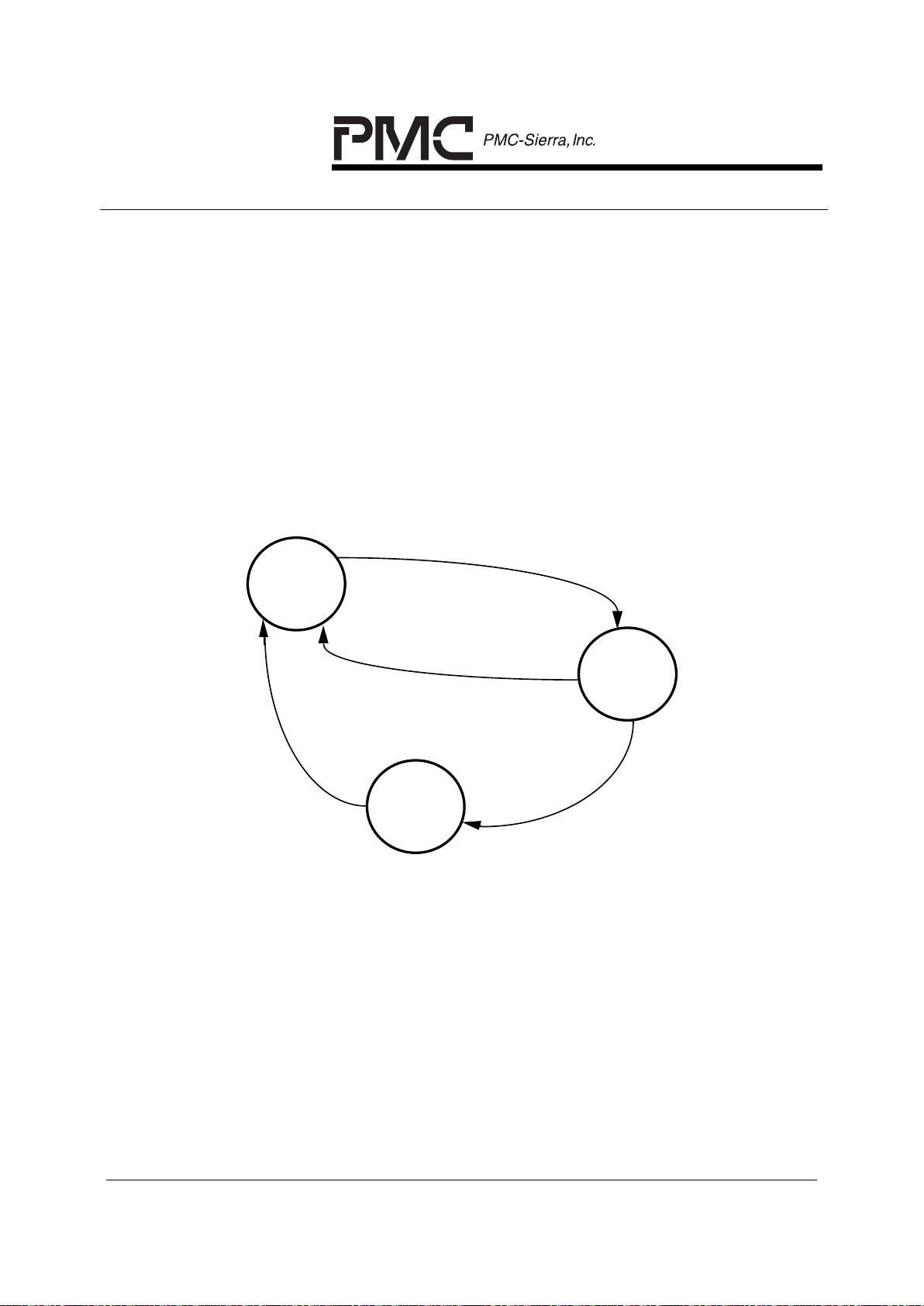

FIGURE 3 - CELL DELINEATION STATE DIAGRAM.......................................48

FIGURE 4 - HCS VERIFICATION STATE DIAGRAM .......................................51

FIGURE 5 - DS3 PLCP FRAME FORMAT.....................................................225

FIGURE 6 - DS1 PLCP FRAME FORMAT.....................................................226

FIGURE 7 - G.751 E3 PLCP FRAME FORMAT.............................................226

FIGURE 8 - E1 PLCP FRAME FORMAT .......................................................227

FIGURE 9 - G.832 E3 FRAME STRUCTURE................................................231

FIGURE 10- CELL DATA STRUCTURE..........................................................233

FIGURE 11- TYPICAL DATA FRAME..............................................................238

FIGURE 12- SSI 78P7200 CONFIGURATION................................................239

FIGURE 13- RECEIVE DS1 STREAM............................................................241

FIGURE 14- RECEIVE E1 PLCP STREAM....................................................241

FIGURE 15- RECEIVE E1 ATM DIRECT-MAPPED STREAM ........................242

FIGURE 16- RECEIVE BIPOLAR DS3 STREAM...........................................242

FIGURE 17- RECEIVE UNIPOLAR DS3 STREAM ........................................243

FIGURE 18- RECEIVE BIPOLAR E3 STREAM..............................................243

FIGURE 19- RECEIVE UNIPOLAR E3 STREAM...........................................244

FIGURE 20- RECEIVE DS3 OVERHEAD.......................................................244

FIGURE 21- RECEIVE G.832 E3 OVERHEAD...............................................245

FIGURE 22- RECEIVE G.751 E3 OVERHEAD...............................................246

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xi

FIGURE 23- RECEIVE PLCP OVERHEAD ....................................................247

FIGURE 24- TRANSMIT DS1 STREAM .........................................................248

FIGURE 25- TRANSMIT E1 STREAM............................................................248

FIGURE 26- TRANSMIT BIPOLAR DS3 STREAM.........................................249

FIGURE 27- TRANSMIT UNIPOLAR DS3 STREAM......................................249

FIGURE 28- TRANSMIT BIPOLAR E3 STREAM ...........................................250

FIGURE 29- TRANSMIT UNIPOLAR E3 STREAM.........................................250

FIGURE 30- TRANSMIT DS3 OVERHEAD ....................................................251

FIGURE 31- TRANSMIT G.832 E3 OVERHEAD............................................252

FIGURE 32- TRANSMIT G.751 E3 OVERHEAD............................................253

FIGURE 33- TRANSMIT PLCP OVERHEAD..................................................254

FIGURE 34- GENERIC TRANSMIT STREAM................................................255

FIGURE 35- RECEIVE FIFO INTERFACE (84-PIN PLCC AND 100-PIN PQFP

WITH SYFIFOB=1)..........................................................................................256

FIGURE 36- TRANSMIT FIFO INTERFACE (84-PIN PLCC AND 100-PIN PQFP

WITH SYFIFOB=1)..........................................................................................257

FIGURE 37- RECEIVE SYNCHRONOUS FIFO (100-PIN PQFP WITH

SYFIFOB=0, TSEN=0)....................................................................................258

FIGURE 38- RECEIVE SYNCHRONOUS FIFO (100-PIN PQFP WITH

SYFIFOB=0, TSEN=1)....................................................................................259

FIGURE 39- TRANSMIT SYNCHRONOUS FIFO (100-PIN PQFP WITH

SYFIFOB=0)....................................................................................................260

FIGURE 40- RECEIVE FIFO BYPASS INTERFACE.......................................260

FIGURE 41- TRANSMIT FIFO BYPASS INTERFACE ....................................261

FIGURE 42- MICROPROCESSOR READ ACCESS TIMING.........................267

FIGURE 43- MICROPROCESSOR WRITE ACCESS TIMING .......................269

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xii

FIGURE 44- TRANSMIT FIFO TIMING...........................................................272

FIGURE 45- RECEIVE FIFO TIMING .............................................................274

FIGURE 46- TRANSMIT FIFO TIMING...........................................................276

FIGURE 47- RECEIVE FIFO TIMING .............................................................278

FIGURE 48- TRANSMIT SYSTEM SIDE - FIFO BYPASS..............................279

FIGURE 49- RECEIVE SYSTEM SIDE - FIFO BYPASS ................................280

FIGURE 50- INPUT TIMING ...........................................................................282

FIGURE 51- INPUT TIMING – CONT’D..........................................................283

FIGURE 52- OUTPUT TIMING .......................................................................284

FIGURE 53- OUTPUT TIMING - CONT’D.......................................................285

FIGURE 54- OVERHEAD OUTPUT TIMING ..................................................286

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

1

FEATURES

• Implements the ATM Direct Cell Mapping into DS1, DS3, E1, E3 transmission

systems according to ITU-T Draft Recommendation G.804.

• Implements the Physical Layer Convergence Protocol (PLCP) for DS1 and DS3

transmission systems according to the ATM Forum User Network Interface

Specification and ANSI TA-TSY-000773, TA-TSY-000772, and E1 and E3

transmission systems according to the ETSI Draft Standards T/NA(91)17, and

T/NA(91)18.

• Implements the ATM physical layer for Broadband ISDN according to ITU-T

Recommendation I.432.

• Provides on-chip DS3 and E3 (G.751 and G.832) framers.

• Directly interfaces to available E3/DS3 line interface units.

• Uses the PMC-Sierra PM4341 T1XC, PM6341 E1XC, and PM4351 COMET

framer/line interface chips for DS1 and E1 applications.

• Provides support for an arbitrary rate external transmission system interface up to

a maximum rate of 52 Mbit/s.

• Support is provided for SMDS and ATM mappings into various rate transmission

systems as defined below, as well as supporting the evolving mappings defined in

G.804:

Rate Format

SMDS PLCP

mapping

ATM Direct

mapping

SMDS PLCP

mapping

ATM Direct

mapping

45 MHz C-bit

M23

√

√

√

√

√√

34 MHz G.751

G.832

√√

√

√

2 MHz CRC-4

PCM30

√

√

√

√

Evolving

through G.804

√

1.5 MHz ESF

SF

√

√

√

√

√

• Provides an 8-bit microprocessor interface for configuration, control and status

monitoring.

• Low power CMOS technology.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

• Available in a high density 100-pin PQFP package, or in an 84-pin PLCC package

which is pin-compatible with the PMC-Sierra PM7321 PLPP standard product.

The receiver section:

• Provides frame synchronization for the M23 or C-bit parity DS3 applications,

alarm detection, and accumulates line code violations, framing errors, parity

errors, path parity errors and FEBE events. In addition, far end alarm channel

codes are detected, and an integral HDLC receiver is provided to terminate the

path maintenance data link.

• Provides frame synchronization for the G.751 or G.832 E3 applications, alarm

detection, and accumulates line code violations, framing errors, parity errors, and

FEBE events. In addition, in G.832, the Trail Trace is detected, and an integral

HDLC receiver is provided to terminate either the Network Requirement or the

General Purpose data link.

• Provides frame synchronization, path overhead extraction, and cell extraction for

DS1 PLCP, DS3 PLCP, E1 PLCP, G.751 E3 PLCP formats, or G.832 formatted

streams.

• Provides detection of yellow alarm and loss of frame (LOF), and accumulates

BIP-8 errors, framing errors and FEBE events.

• Provides ATM framing using cell delineation.

• Provides cell descrambling, header check sequence (HCS) error detection,

idle/unassigned cell filtering, and accumulates the number of received

idle/unassigned cells, the number of received cells written to the FIFO, and the

number of HCS errors.

• Provides a four cell FIFO for rate decoupling between the line, and a higher layer

processing entity. This FIFO may be bypassed to minimize the delay through the

device when processing PLCP frames.

• Provides an asynchronous 8-bit wide FIFO interface for accessing received cell

data bytes (available in either 84-pin PLCC or 100-pin PQFP packages).

• Provides a synchronous 8-bit wide FIFO with receive byte parity generation and

compatible timing with current “UTOPIA” specifications for single PHY and multiPHY interfaces (available only in the 100-pin PQFP package).

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

The transmitter section:

• Provides frame insertion for the M23 or C-bit parity DS3 applications, alarm

insertion, and diagnostic features. In addition, far end alarm channel codes may

be inserted, and an integral HDLC transmitter is provided to insert the path

maintenance data link.

• Provides frame insertion for the G.751 or G.832 E3 applications, alarm insertion,

and diagnostic features. In addition, for G.832, the Trail Trace is inserted, and an

integral HDLC transmitter is provided to insert either the Network Requirement or

the General Purpose data link.

• Provides frame insertion and path overhead insertion for DS1, DS3, E1 or E3

based PLCP formats. In addition, alarm insertion, and diagnostic features are

provided.

• Provides an optional 8 kHz reference input for locking the transmit PLCP frame

rate to an externally applied frame reference.

• Provides optional ATM cell scrambling, HCS generation/insertion, programmable

idle/unassigned cell insertion, diagnostics features and accumulates transmitted

cells read from the FIFO.

• Provides a four cell FIFO for rate decoupling between the line, and a higher layer

processing entity. This FIFO may be bypassed to minimize the delay through the

device when processing PCLP frames.

• Provides an asynchronous 8-bit wide FIFO interface for accessing transmit cell

data bytes (available in either 84-pin PLCC or 100-pin PQFP packages).

• Provides a synchronous 8-bit wide FIFO with transmit byte parity checking and

compatible timing with current “UTOPIA” specifications for single PHY and multiPHY interfaces (available only in the 100-pin PQFP package).

Bypass and Loopback features:

• Allows bypassing of the DS3 or E3 framer to enable transmission system sublayer

processing by an external device (for example, the PM4341 DS1 Framer/LIU may

be used for DS1-based services, and the PM6341 E1 Framer/LIU may be used

for E1-based services).

• Provides for DS3 or E3 diagnostic loopback, DS3 or E3 line loopback, DS3 or E3

payload loopback, and ATM cell loopback.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

2

APPLICATIONS

• ATM or SMDS Routers, Bridges, Switches, and Adapter Cards

• DQDB Access Units

• ATM and SMDS test equipment

3

REFERENCES

• American National Standard for Telecommunications, ANSI T1.107-1995 - “Digital

Hierarchy - Formats Specification s ”.

• Bell Communications Research, TA-TSY-000773 - “Local Access System Generic

Requirements, Objectives, and Interface in Support of Switched Multi-megabit

Data Service” Issue 2, March 1990 and Supplement 1, December 1990.

• ITU-T, Recommendation I.432 - “B-ISDN User-Network Interface - Physical Layer

Specification”, 1993.

• ITU-T Recommendation G.704 – “General Aspects of Digital Transmission

Systems; Terminal Equipments – Synchronous Frame Structures Used At 1544,

6312, 2048, 8488 and 44 736 kbit/s Hierarchical Levels”, July, 1995.

• ITU-T Blue Book, Recommendation G.751, - “Digital Multiplex Equipments

Operating at the Third Order Bit Rate of 34368 kbit/s and the Fourth Order Bit

Rate of 139264 kbit/s and using Positive Justification”, Vol. III, Fascicle III.4, 1988.

• ITU-T Recommendation G.804 - “ATM Cell Mapping into Plesiochronous Digital

Hierarchy (PDH)”, 1993.

• ITU-T Recommendation G.832 - “Transport of SDH Elements on PDH Networks:

Frame and Multiplexing Structures”, 1993.

• ETSI 300 269 “Metropolitan Area Network Physical Layer Convergence

Procedure for 2.048 Mbit/s”, April 1994.

• ETSI 300 270 “Metropolitan Area Network Physical Layer Convergence

Procedure for 34.368 Mbit/s”, April 1994.

• IEEE, Std 802.6-1990 - “Distributed Queue Dual Bus Subnetwork of a

Metropolitan Area Network”.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

• ATM Forum, V3.1, October, 1995 - “ATM User-Network Interface Specification”.

• ATM Forum, 94-0406R5, E3 (34,368 kpbs) Physical Layer Interface”, Dec. 21,

1994.

• ATM Forum, 95-1207R1, “DS3 Physical Layer Interface Specification”, December,

1995.

• ATM Forum, Level 1, V2.00 - February 1994 - “An ATM PHY Data path Interface”.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

4

APPLICATION EXAMPLES

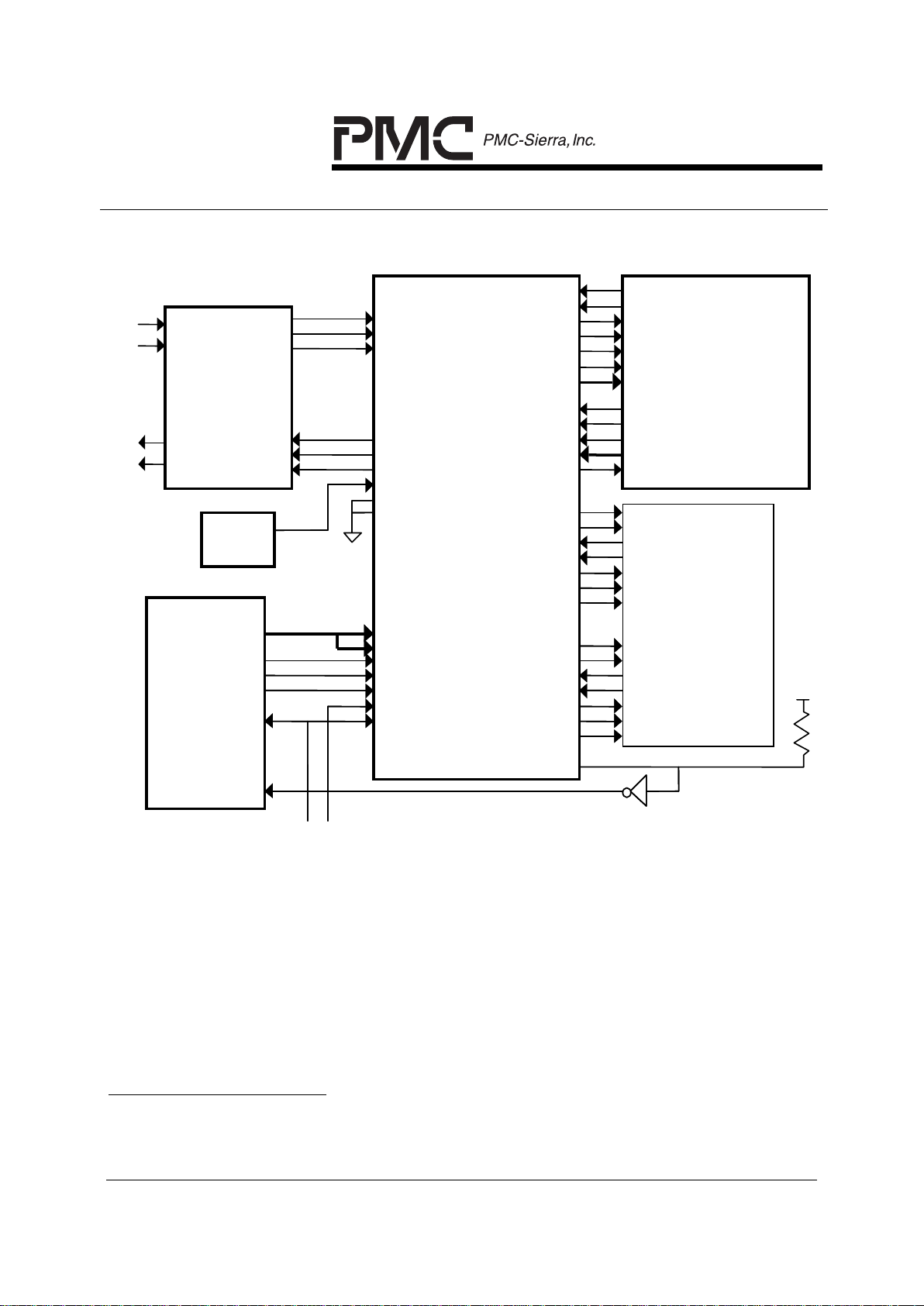

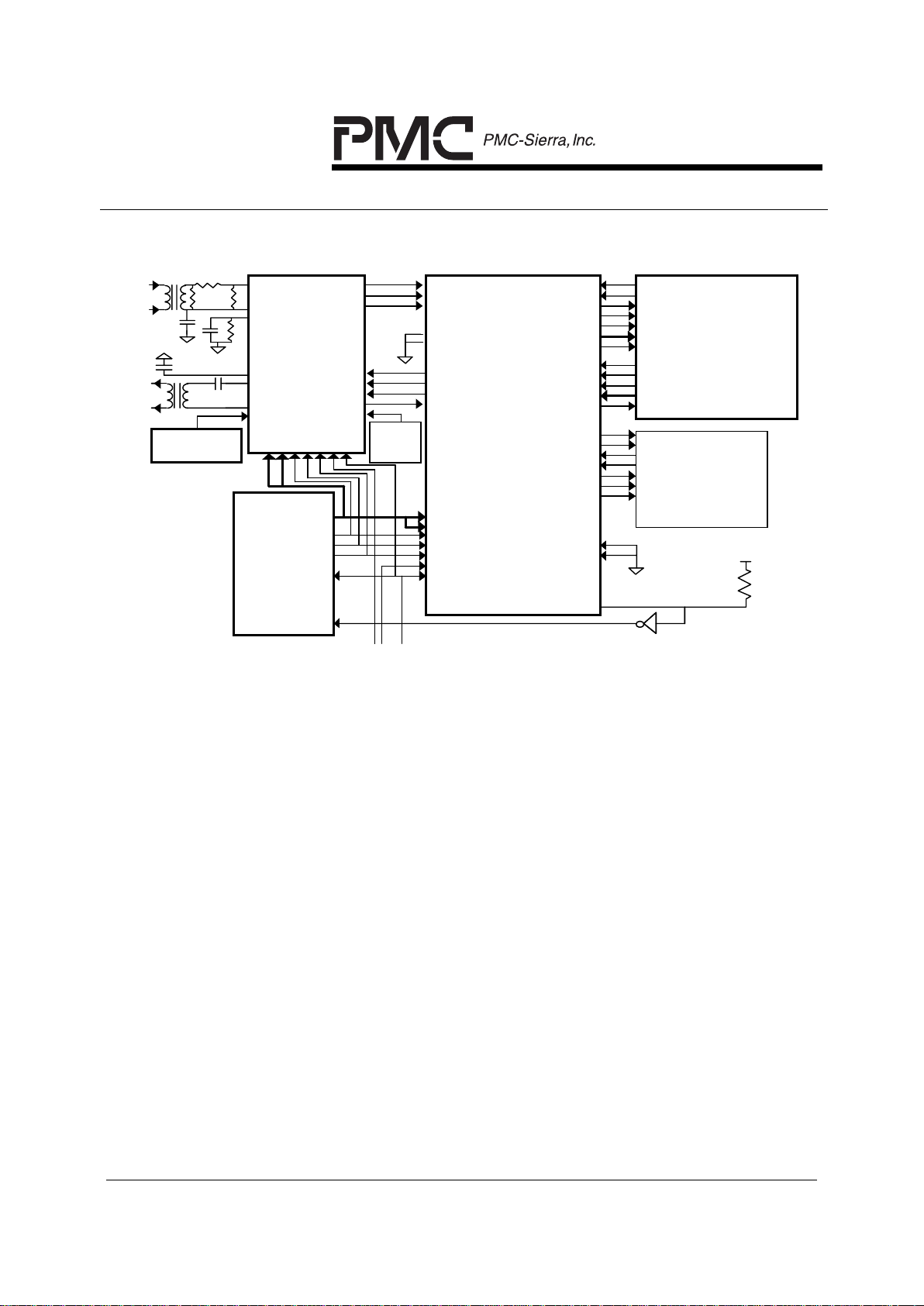

The PM7345 S/UNI-PDH is used to implement ATM user network interfaces (UNI)

and network node interfaces (NNI). An example of a DS3/E3 User Network Interface

(figure 1) and a DS1/E1 User Network Interface (figure 2) illustrate the interconnect

between the S/UNI-PDH and system elements required to implement a complete

ATM physical layer interface.

In figure 1, the DS3/E3 line interface function is provided by a commercially

available DS3/E3 Line Interface Unit (LIU) product available from Silicon Systems.

The DS3/E3 framing function, along with all PLCP processing, and ATM

transmission convergence sublayer processing are performed by the S/UNI-PDH.

In figure 2, the DS1 LIU and framing functions are provided by the PM4341 T1

Transceiver (T1XC) product available from PMC-Sierra. The E1 LIU and framing

functions are provided by the PM6341 E1 Transceiver (E1XC) product, also

available from PMC-Sierra. The combination of these transceiver devices with the

S/UNI-PDH allows both PLCP-formatted DS1/E1 signals, and ITU-T G.804

compliant DS1/E1 signals to be processed. The G.804 specification defines ATM

direct cell mappings for a variety of transmission formats, including the 1.544 Mbit/s

DS1, and the 2.048 Mbit/s E1 formats.

The optional PLCP and DS3/E3 Overhead Processors illustrated are expected to be

implemented using programmable logic devices. For further S/UNI-PDH application

information, please refer to document number PMC-930410, "The ATM Physical

Layer".

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

Figure 1 - DS3 and E3 User Network Interface

Optional

DS3/E3/PLCP

Overhead

Processor

( eg. tester

application)

PM7345

S/UNI-PDH

SATURN

User-Network

Interface for

PDH

ATM/SMDS

Adaptation

Layer

Processor

(eg. SAR or

policing

functions)

SSI

78P7200

E3/DS3

LIU

RPOS

RNEG

RCLK

TPOS

TNEG

TCLK

RPOS/RDAT

RNEG/ROHM

RCLK

TPOS/TDAT

TNEG/TOHM

TCLK

TICLK

TIOHM

C13/CADD

TCELL

RCELL

A[7:0]

D[7:0]

ALE

RDB

WRB

CSB

RSTB

RRDENB

FRDB/RFCLK

RSOC

REOH

REOC

FRDATA[7:0]

RFIFOE/RCA

TWRENB

FWRB/TFCLK

TSOC

FWDATA[7:0]

TFIFOFB/TCA

TPOHCLK

TPOHFP

TPOHINS

TPOH

RPOHCLK

RPOHFP

RPOH

TOHCLK

TOHFP

TOHINS

TOH

ROHCLK

ROHFP

ROH

INTB

AD[15:0]

ALE

RDB

WRB

RESB

INT

From Master

reset circuitry

From chip select

decode circuitry

+5V

OSC

44.736 MHz

LINE

IN

INTERFACE

LINE

OUT

INTERFACE

AD[15:0]

ALE

RDB

WRB

RESB

INT

From Master

reset circuitry

From chip select

decode circuitry

OSC

44.736 MHz

or

34.368 MHz

RX

CELL

INTERFACE

TX

CELL

INTERFACE

Intel/

Motorola

Single Chip

µP

Layout information for the SSI 78P7200 E3/DS3 LIU is found in the OPERATION

section of this document. Please refer to it as an example of the E3 and DS3

configuration used by PMC-Sierra.

1

1

Please contact Silicon Systems at (714) 573-6200 for detailed application information concerning the

78P7200 E3/DS3 LIU.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

Figure 2 - DS1 and E1 User Network Interface

RAS

REF

RRC

TC

TAP

TAN

XCLK

BRPCM

BRFPO

RCLKO

BTPCM

BTFP

BTCLK

TCLKO

TCLKI

PM4341A/PM6341

T1XC/E1XC

DS1 or E1

Transceiver

PM7345

S/UNI-PDH

SATURN

User-Network

Interface for

PDH

RPOS/RDAT

RNEG/ROHM

RCLK

TIOHM

C13/CADD

TPOS/TDAT

TNEG/TOHM

TCLK

TICLK

TCELL

RCELL

A[7:0]

D[7:0]

ALE

RDB

WRB

CSB

RSTB

AD[15:0]

ALE

RDB

WRB

RESB

INT

From Master

reset circuitry

From chip select

decode circuitry

+5V

A[7:0]

D[7:0]

ALE

RDB

WRB

CSB

RSTB

AD[15:0]

ALE

RDB

WRB

RESB

INT

OSC

37.056 MHz (DS1)

49.152 MHz (E1)

RX

CELL

INTERFACE

TX

CELL

INTERFACE

Optional

PLCP

Overhead

Processor

( eg. tester

application )

Intel/

Motorola

Single Chip

µP

ATM/SMDS

Adaptation

Layer

Processor

(eg. SAR or

policing

functions)

RRDENB

FRDB/RFCLK

RSOC

REOH

REOC

FRDATA[7:0]

RFIFOE/RCA

TWRENB

FWRB/TFCLK

TSOC

FWDATA[7:0]

TFIFOFB/TCA

TPOHCLK

TPOHFP

TPOHINS

TPOH

RPOHCLK

RPOHFP

RPOH

TOHCLK

TOHFP

TOHINS

TOH

ROHCLK

ROHFP

ROH

INTB

DS1

1.544 MHz

E1

2.048 MHz

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

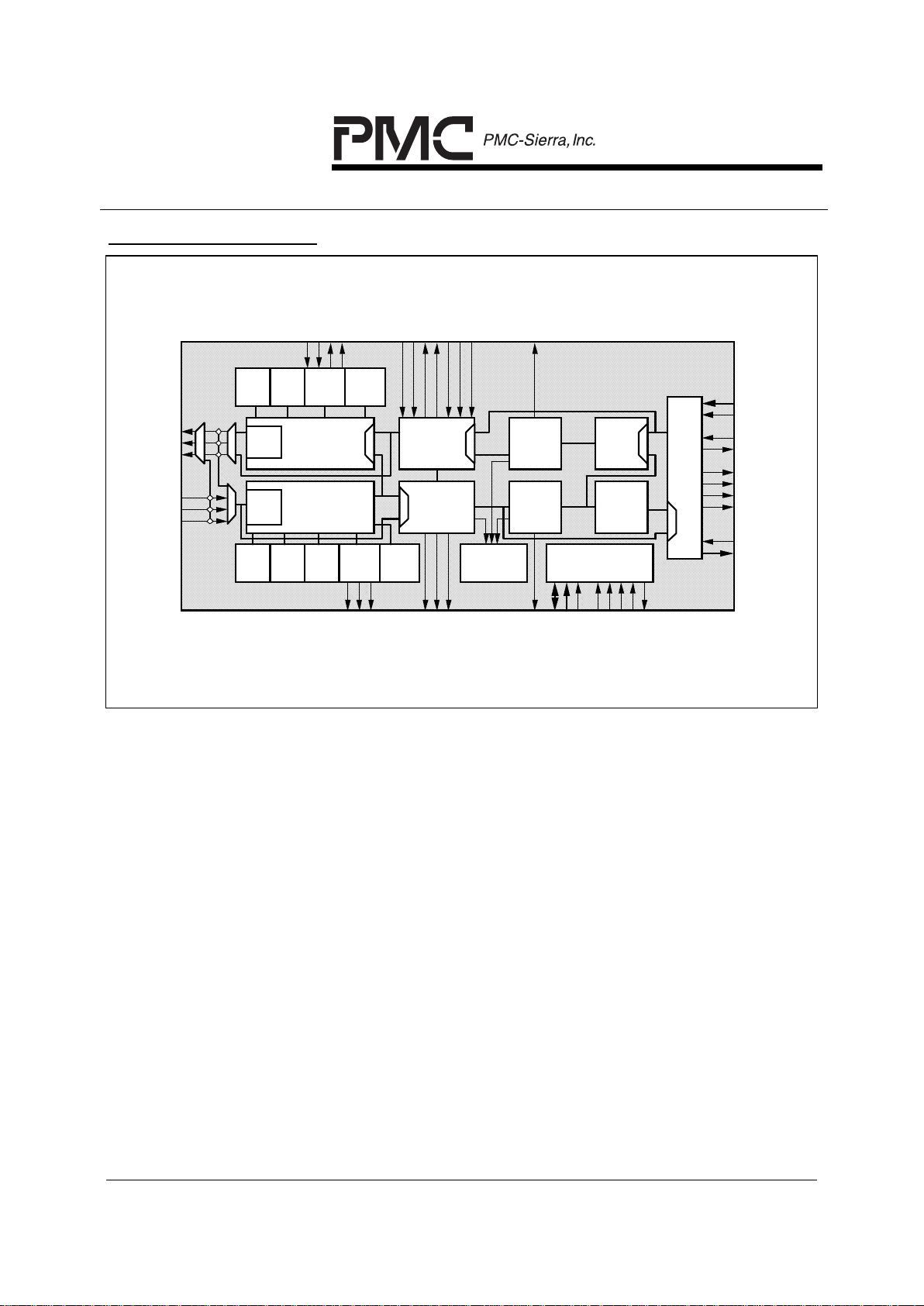

5

BLOCK DIAGRAM

TPOS/TDAT

RNEG/ROHM

RPOS/RDAT

TCLK

TNEG/TOHM

RCLK

TXFF

Tx

4 Cell

FIFO

RXFF

Rx

4 Cell

FIFO

System

I/F

SPLT

Transmit ATM

and PLCP

Framer

FWDATA[7:0]

TSOC

FWRB

FRDATA[7:0]

RSOC

D[7:0]

A[7:0]

ALE

CSB

RDB

WRB

RSTB

INTB

Microprocessor

I/F

Rx

O/H

Access

Tx

O/H

Access

TOHINS

ROH

TOHCLK

ROHFP

RPOH

TPOH

TPOHINS

RPOHCLK

ROHCLK

TOH

TRAN

DS3 or E3

Transmit

Framer

FRMR

DS3 or E3

Receive

Framer

TOHFP

C13/CADD/8KREFRPOHFP

TFIFOFB/FWCLK

TICLK

TIOHM

TXCP

Tx

Cell

Processor

RXCP

Rx

Cell

Processor

REOH/LOF

REOC/OOF

Line

Encode

Line

Decode

TCELL

RCELL

CPPM

PLCP/cell

Perf. Monitor

ATMF/SPLR

Receive

ATM and

PCLP Framer

XFDL

Tx

HDLC

XBOC

Tx

FEAC

RFDL

Rx

HDLC

RBOC

Rx

FEAC

TPOHCLK

TPOHFP

PMON

Perf.

Monitor

1/2 TTB

Rx Trail

Buffer

1/2 TTB

Tx Trail

Buffer

RFIFOE/FRCLK

FRDB

Normal Operating Mode (84-pin PLCC Async FIFO interface shown)

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

TXFF

Tx

4 Cell

FIFO

RXFF

Rx

4 Cell

FIFO

System

I/F

SPLT

Transmit ATM

and PLCP

Framer

FWDATA[7:0]

TSOC

TFCLK

FRDATA[7:0]

RSOC

D[7:0]

A[7:0]

ALE

CSB

RDB

WRB

RSTB

INTB

Microprocessor

I/F

Rx

O/H

Access

Tx

O/H

Access

TOHINS

ROH

TOHCLK

ROHFP

RPOH

TPOH

TPOHINS

RPOHCLK

ROHCLK

TOH

TRAN

DS3 or E3

Transmit

Framer

FRMR

DS3 or E3

Receive

Framer

TOHFP

C13/CADD/8KREFRPOHFP

TCA

TICLK

TIOHM

TXCP

Tx

Cell

Processor

RXCP

Rx

Cell

Processor

REOH

REOC

TPOS/TDAT

Line

Encode

RNEG/ROHM

Line

Decode

RPOS/RDAT

TCLK

TNEG/TOHM

RCLK

TCELL

RCELL

CPPM

PLCP/cell

Perf. Monitor

ATMF/SPLR

Receive

ATM and

PCLP Framer

XFDL

Tx

HDLC

XBOC

Tx

FEAC

RFDL

Rx

HDLC

RBOC

Rx

FEAC

TPOHCLK

TPOHFP

PMON

Perf.

Monitor

1/2 TTB

Rx Trail

Buffer

1/2 TTB

Tx Trail

Buffer

TDLSIG

TDLCLK

TSEN

TWRENB

TXPRTY

RCA

RXPRTY

RRDENB

RFCLK

RDLSIG

RDLCLK

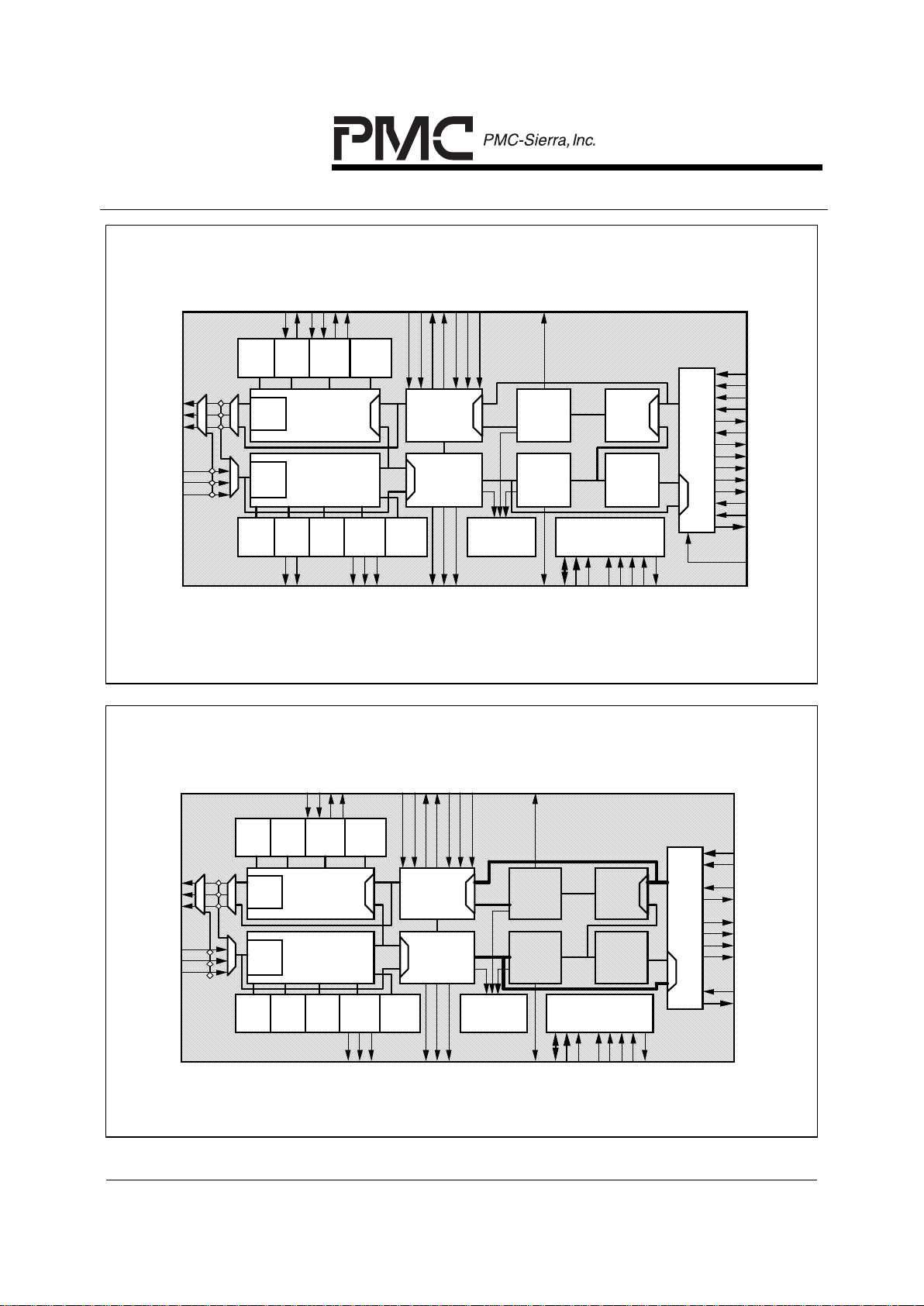

Normal Operating Mode (100-pin PQFP Sync FIFO interface shown)

TPOS/TDAT

RNEG/ROHM

RPOS/RDAT

TCLK

TNEG/TOHM

RCLK

TXFF

Tx

4 Cell

FIFO

RXFF

Rx

4 Cell

FIFO

System

I/F

SPLT

Transmit ATM

and PLCP

Framer

FWDATA[7:0]

TSOC

FWRB

FRDATA[7:0]

RSOC

D[7:0]

A[7:0]

ALE

CSB

RDB

WRB

RSTB

INTB

Microprocessor

I/F

Rx

O/H

Access

Tx

O/H

Access

TOHINS

ROH

TOHCLK

ROHFP

RPOH

TPOH

TPOHINS

RPOHCLK

ROHCLK

TOH

TRAN

DS3 or E3

Transmit

Framer

FRMR

DS3 or E3

Receive

Framer

TOHFP

C13/CADD/8KREFRPOHFP

TFIFOFB/FWCLK

TICLK

TIOHM

TXCP

Tx

Cell

Processor

RXCP

Rx

Cell

Processor

REOH/LOF

REOC/OOF

Line

Encode

Line

Decode

TCELL

RCELL

CPPM

PLCP/cell

Perf. Monitor

ATMF/SPLR

Receive

ATM and

PCLP Framer

XFDL

Tx

HDLC

XBOC

Tx

FEAC

RFDL

Rx

HDLC

RBOC

Rx

FEAC

TPOHCLK

TPOHFP

PMON

Perf.

Monitor

1/2 TTB

Rx Trail

Buffer

1/2 TTB

Tx Trail

Buffer

RFIFOE/FRCLK

FRDB

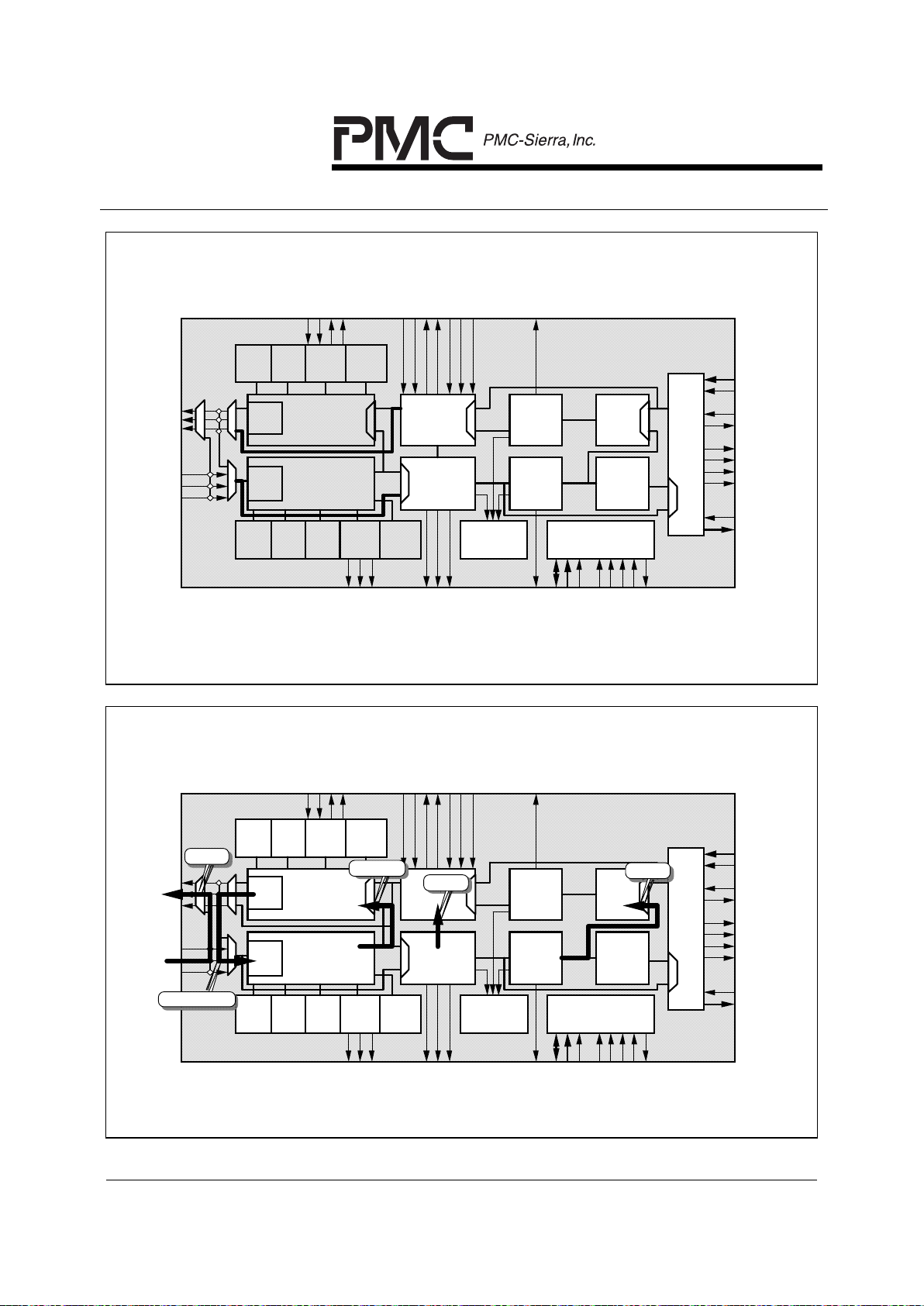

With FIFO Bypass Enabled

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

TPOS/TDAT

RNEG/ROHM

RPOS/RDAT

TCLK

TNEG/TOHM

RCLK

TXFF

Tx

4 Cell

FIFO

RXFF

Rx

4 Cell

FIFO

System

I/F

SPLT

Transmit ATM

and PLCP

Framer

FWDATA[7:0]

TSOC

FWRB

FRDATA[7:0]

RSOC

D[7:0]

A[7:0]

ALE

CSB

RDB

WRB

RSTB

INTB

Microprocessor

I/F

Rx

O/H

Access

Tx

O/H

Access

TOHINS

ROH

TOHCLK

ROHFP

RPOH

TPOH

TPOHINS

RPOHCLK

ROHCLK

TOH

TRAN

DS3 or E3

Transmit

Framer

FRMR

DS3 or E3

Receive

Framer

TOHFP

C13/CADD/8KREFRPOHFP

TFIFOFB/FWCLK

TICLK

TIOHM

TXCP

Tx

Cell

Processor

RXCP

Rx

Cell

Processor

REOH/LOF

REOC/OOF

Line

Encode

Line

Decode

TCELL

RCELL

CPPM

PLCP/cell

Perf. Monitor

ATMF/SPLR

Receive

ATM and

PCLP Framer

XFDL

Tx

HDLC

XBOC

Tx

FEAC

RFDL

Rx

HDLC

RBOC

Rx

FEAC

TPOHCLK

TPOHFP

PMON

Perf.

Monitor

1/2 TTB

Rx Trail

Buffer

1/2 TTB

Tx Trail

Buffer

RFIFOE/FRCLK

FRDB

With DS3/E3 Framer Bypassed

TPOS/TDAT

RNEG/ROHM

RPOS/RDAT

TCLK

TNEG/TOHM

RCLK

TXFF

Tx

4 Cell

FIFO

RXFF

Rx

4 Cell

FIFO

System

I/F

SPLT

Transmit ATM

and PLCP

Framer

FWDATA[7:0]

TSOC

FWRB

FRDATA[7:0]

RSOC

D[7:0]

A[7:0]

ALE

CSB

RDB

WRB

RSTB

INTB

Microprocessor

I/F

Rx

O/H

Access

Tx

O/H

Access

TOHINS

ROH

TOHCLK

ROHFP

RPOH

TPOH

TPOHINS

RPOHCLK

ROHCLK

TOH

TRAN

DS3 or E3

Transmit

Framer

FRMR

DS3 or E3

Receive

Framer

TOHFP

C13/CADD/8KREFRPOHFP

TFIFOFB/FWCLK

TICLK

TIOHM

TXCP

Tx

Cell

Processor

RXCP

Rx

Cell

Processor

REOH/LOF

REOC/OOF

Line

Encode

Line

Decode

TCELL

RCELL

CPPM

PLCP/cell

Perf. Monitor

ATMF/SPLR

Receive

ATM and

PCLP Framer

XFDL

Tx

HDLC

XBOC

Tx

FEAC

RFDL

Rx

HDLC

RBOC

Rx

FEAC

TPOHCLK

TPOHFP

PMON

Perf.

Monitor

1/2 TTB

Rx Trail

Buffer

1/2 TTB

Tx Trail

Buffer

RFIFOE/FRCLK

FRDB

LINE

PAYLOAD

TIMING

CELL

DIAGNOSTIC

Loopback Modes

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

6

DESCRIPTION

The PM7345 S/UNI-PDH is an ATM physical layer processor with integrated DS3

and E3 framing. PLCP sublayer DS1, DS3, E1, and E3 processing is supported as

is ATM cell delineation.

The S/UNI-PDH contains an integral DS3 framer, which provides DS3 framing and

error accumulation in accordance with ANSI specifications, and an integral E3

framer, which provides E3 framing in accordance with ITU-T Recommendations

G.832 and G.751. When configured for DS3 transmission system sublayer

processing, the S/UNI-PDH accepts and outputs either a B3ZS-encoded bipolar or a

unipolar signal compatible with M23 and C-bit parity applications. When configured

for E3 transmission system sublayer processing, the S/UNI-PDH accepts and

outputs either a HDB3-encoded bipolar or a unipolar signal compatible with G.751

and G.832 applications. When configured for DS1, or E1 transmission system

sublayer processing, the S/UNI-PDH accepts and outputs a unipolar signal with

appropriate clock and frame pulse signals for physical sublayer processing. When

configured for other transmission systems, the S/UNI-PDH provides a generic

interface for physical sublayer processing.

In the DS3 receive direction, the S/UNI-PDH frames to a DS3 signal with a

maximum average reframe time of 1.5 ms and detects line code violations, loss of

signal, framing bit errors, parity errors, path parity errors, AIS, far end receive failure

and idle code. The DS3 overhead bits are extracted and presented on a serial

output. When in C-bit parity mode, the Path Maintenance Data Link and the Far End

Alarm and Control (FEAC) channel are extracted. An HDLC receiver is provided for

Path Maintenance Data Link support. In addition, valid bit-oriented codes in the

FEAC channel are detected and are available through the microprocessor port.

In the E3 receive direction, the S/UNI-PDH frames to either a G.751 or G.832 E3

signal with a maximum average reframe time of 0.5 ms and detects line code

violations, loss of signal, framing bit errors, AIS, and remote alarm indication.

Further, when processing G.832 formatted data, parity errors, far end receive failure,

and far end block errors are also detected; and the Trail Trace message is extracted

and made available through the microprocessor port. An HDLC receiver is provided

for either the G.832 Network Requirement or the G.832 General Purpose Data Link

support.

Error event accumulation is also provided by the S/UNI-PDH. Framing bit errors,

line code violations, parity errors, path parity errors and far end block errors are

accumulated in saturating counters.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

In the DS3 transmit direction, the S/UNI-PDH inserts DS3 framing, X and P bits.

When enabled for C-bit parity operation, a bit-oriented code transmitter and an

HDLC transmitter are provided for insertion of the FEAC channel and the Path

Maintenance Data Link into the appropriate overhead bits. The Alarm Indication

Signal can be inserted when enabled by an external input or using an internal

register bit; other status signals such as the idle signal can be inserted when

enabled by an internal register bit. When M23 operation is selected, the C-bit Parity

ID bit (the first C-bit of the first M sub-frame) is forced to toggle so that downstream

equipment will not confuse an M23-formatted stream with stuck-at 1 C-bits for C-bit

Parity application.

In the E3 transmit direction, the S/UNI-PDH inserts E3 framing in either G.832 or

G.751 format. When enabled for G.832 operation, an HDLC transmitter is provided

for insertion of either the Network Requirement or General Purpose Data Link into

the appropriate overhead bits. The Alarm Indication Signal and other status signals

can be inserted by internal register bits.

The S/UNI-PDH also supports diagnostic modes in which it inserts parity or path

parity errors, F-bit framing errors, M-bit framing errors, invalid X or P-bits, line code

violations, or all-zeros.

The S/UNI-PDH provides cell delineation for ATM cells using the PLCP framing

format, or by using the header check sequence octet in the ATM cell header as

specified by ITU-T Recommendation I.432. DS1, DS3, E1 and E3 based PLCP

frame formats can be processed. An interface consistent with the generic physical

interface defined by ITU-T Recommendation I.432 is provided for arbitrary rates up

to 52 Mbit/s. This interface is used to provide physical layer support for

transmission systems that do not have an associated PLCP sublayer, or to provide

an efficient means of directly mapping ATM cells to existing transmission system

formats (such as DS3 and DS1).

In the PLCP receive direction, framing, path overhead extraction and cell extraction

is provided. BIP-8 error events, frame octet error events and far end block error

events are accumulated.

In the PLCP transmit direction, the S/UNI-PDH provides overhead insertion using

inputs or internal registers, DS3 nibble and E3 byte stuffing, automatic BIP-8 octet

generation and insertion and automatic far end block error insertion. Diagnostic

features for BIP-8 error, framing error and far end block error insertion are also

supported.

In the cell receive path, idle/unassigned cells may be dropped according to a

programmable filter. By default, incoming cells with single bit HCS errors are

corrected and written to the FIFO buffer. Optionally, cells can be dropped upon

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

detection of a HCS error. The ATM cell payloads are optionally descrambled.

Assigned cells containing no detectable HCS errors are written to a FIFO buffer.

Cells are read from the FIFO using an asynchronous 8-bit wide datapath interface or

a synchronous 9-bit wide datapath, depending upon the packaging option selected.

Counts of error-free assigned cells, and cells containing HCS errors are

accumulated independently for performance monitoring purposes.

In the cell transmit path, cells are written to a FIFO buffer using an asynchronous 8bit wide datapath interface or a synchronous 9-bit wide datapath interface,

depending upon the packaging option selected. Idle/unassigned cells are

automatically inserted when the FIFO contains less than one full cell. HCS

generation, and cell payload scrambling are optionally provided.

Both receive and transmit cell FIFOs provide buffering for four cells. The FIFOs

provide the rate matching interface between the higher layer ATM entity and the

S/UNI-PDH.

The S/UNI-PDH is configured, controlled and monitored via a generic 8-bit

microprocessor bus through which all internal registers are accessed. All sources of

interrupts can be identified, acknowledged, or masked via this interface.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

15

7

PIN DIAGRAM

The S/UNI-PDH is available in an 84-pin PLCC.

S/

UNI-

PM7345

FWDATA[4]

FWDATA[5]

ROHFP

ROHCLK

ROH

RNEG/ROHM

RPOS/RDAT

RCLK

INTB

RSTB

CSB

VDDO

VSSO

RPOHCLK

FWRB

FWDATA[7]

RPOH

RPOHFP

FWDATA[6]

RDB

WRB

55

54

57

56

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

33 34 52434241403938373635 5150494847464544 53

FWDATA[0]

RSOC

FWDATA[3]

FWDATA[2]

FWDATA[1]

FRDB

FRDATA[7]

FRDATA[6]

FRDATA[5]

FRDATA[4]

VDDO

VSSI

VDDI

FRDATA[3]

FRDATA[2]

FRDATA[1]

FRDATA[0]

REOC/OOF

REOH/LOF

RFIFOE/FRCLK

ALE

A[0]

A[1]

A[2]

A[3]

D[0]

D[1]

D[2]

D[3]

VDDO

VSSI

VDDI

VSSO

D[4]

D[5]

D[6]

D[7]

A[4]

A[5]

A[6]

A[7]

31

29

30

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

32

12

757612345678977787980818283841011

NC

TIOHM

TICLK

C13/CADD/8KREF

TCLK

TPOS/TDAT

TNEG/TOHM

TOHCLK

TOHFP

VDDO

VSSO

TOHINS

TOH

TPOHCLK

TPOHFP

TPOHINS

TPOH

TCELL

TFIFOFB/FWCLK

TSOC

RCELL

VSSO

PDH

TM

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

16

The S/UNI-PDH is also available in a 100-pin PQFP having a body size of 14x14mm

and a pin pitch of 0.5mm.

NC

VDDI

ALE

A[0]

A[1]

A[2]

A[3]

D[0]

D[1]

D[2]

D[3]

VDDO

VSSI

PIN 1

PIN 100

PIN 25

PIN 26

PIN 50

PIN 51

PIN 75

PIN 76

VSSO

NC

TDLSIG

PM7345

VDDI

VSSO

D[4]

D[5]

D[6]

D[7]

A[4]

A[5]

A[6]

A[7]

NC

TIOHM

TICLK

C13/CADD/8KREF

TCLK

TPOS/TDAT

TNEG/TOHM

TOHCLK

TOHFP

VDDO

TDLCLK

VSSO

TOHINS

TOH

TPOHCLK

TPOHFP

TPOHINS

TPOH

TCELL

TFIFOFB/TCA/FWCLK

TSOC

RCELL

SYFIFOB

LCD

FWRDATA[3]

FWRDATA[2]

FWRDATA[1]

FWRDATA[0]

RRDENB

FRDB/RFCLK

FRDATA[7]

FRDATA[6]

FRDATA[5]

FRDATA[4]

VDDO

VSSO

RXPRTY

VSSI

VDDI

FRDATA[3]

FRDATA[2]

FRDATA[1]

FRDATA[0]

RSOC

REOC/OOF

REOH/LOF

RFIFOE/RCA/FRCLK

TSEN

VDDO

RDB

WRB

CSB

RSTB

INTB

RCLK

RPOS/RDAT

RNEG/ROHM

ROH

ROHCLK

ROHFP

RDLSIG

TXPRTY

VSSO

RPOH

RPOHCLK

RPOHFP

TWRENB

FWRB/TFCLK

FWRDATA[7]

FWRDATA[6]

FWRDATA[5]

FWRDATA[4]

VSSI

RDLCLK

Index

TM

PDH

S/

UNI-

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

17

8

PIN DESCRIPTION

Pin Pin No.

Name Type QFP PLCC Function

RCLK Input 95 6

Receive Clock (RCLK). RCLK provides the

receive direction timing. RCLK is the externally

recovered transmission system baud rate clock that

samples the RPOS/RDAT and RNEG/ROHM inputs

on its rising or falling edge. The RCLK maximum

frequency is 52 MHz.

RPOS/

RDAT

Input 94 5

Receive Positive Pulse (RPOS). RPOS contains

the positive pulses received on the B3ZS-encoded

DS3, or the HDB3-encoded E3, transmission

system when the dual-rail NRZ input format is

selected. RPOS contains the entire stream when

the single-rail (unipolar) NRZ input format is

enabled. The dual-rail/single-rail selection is

controlled by the UNI bit in the DS3 FRMR or the E3

FRMR Configuration Registers.

Receive Data (RDAT). RDAT contains the received

transmission system stream when a non-DS3/E3

based transmission system is being processed (for

example RDAT may contain a DS1 or E1 stream).

The RPOS/RDAT pin function selection is controlled

by the FRMRBP bit in the S/UNI-PDH Configuration

Register. Both RPOS and RDAT are sampled on

the rising edge of RCLK by default, and may be

enabled to be sampled on the falling edge of RCLK.

This sampling is controlled by the RCLKINV bit in

the S/UNI-PDH Control Register. In addition, signal

polarity control is provided by the RPNINV bit in the

S/UNI-PDH Control Register.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

18

RNEG/

ROHM

Input 93 4

Receive Negative Pulse (RNEG). RNEG contains

the negative pulses received on the B3ZS encoded

DS3, or the HDB3-encoded E3, transmission

system when the dual-rail NRZ input format is

selected. RNEG contains line code violation

indications when the single-rail (unipolar) NRZ input

format is enabled. Each line code violation is

represented by an RCLK period-wide pulse. The

dual-rail/single-rail selection is controlled by the UNI

bit in the DS3 FRMR or E3 FRMR Configuration

Registers.

Receive Overhead Mask (ROHM). ROHM

indicates the position of overhead bits in the nonDS3/E3 based transmission system stream, RDAT.

When a PLCP formatted signal is received, ROHM

is pulsed once per transmission frame, and

indicates the DS1 or E1 frame alignment. When a

non-PLCP based signal is received, ROHM

indicates the position of each overhead bit in the

transmission frame.

The RNEG/ROHM pin function selection is

controlled by the FRMRBP bit in the S/UNI-PDH

Configuration Register. Both RNEG and ROHM are

sampled on the rising edge of RCLK by default, and

may be enabled to be sampled on the falling edge

of RCLK. This sampling is controlled by the

RCLKINV bit in the S/UNI-PDH Control Register. In

addition, signal polarity control is provided by the

RPNINV bit in the S/UNI-PDH Control Register.

ROHCLK Output 91 2

Receive DS3/E3 Overhead Clock (ROHCLK).

ROHCLK is active when a DS3 or E3 stream is

being processed. ROHCLK is nominally a 526 kHz

clock when processing DS3, is nominally a 1.072

MHz clock when processing G.832 E3, and is

nominally a 1.074 MHz clock when processing

G.751 E3. ROH, and ROHFP are updated on the

falling edge of ROHCLK.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

19

ROH Output 92 3

Receive DS3/E3 Overhead Data (ROH). ROH

contains the overhead bits (C, F, X, P, and M)

extracted from the received DS3 stream; ROH

contains the overhead bytes (FA1, FA2, EM, TR,

MA, NR, and GC) extracted from the received

G.832 E3 stream; ROH contains the overhead bits

(RAI, National Use, Stuff Indication, and Stuff

Opportunity) extracted from the received G.751 E3

stream. ROH is updated on the falling edge of

ROHCLK.

ROHFP Output 90 1

Receive DS3/E3 Overhead Frame Position

(ROHFP). ROHFP locates the individual overhead

bits in the received overhead data stream, ROH.

ROHFP is high during the X1 overhead bit position

in the ROH stream when processing a DS3 stream.

ROHFP is high during the first bit of the FA1 byte

when processing a G.832 E3 stream. ROHFP is

high during the RAI overhead bit position when

processing a G.751 E3 stream. ROHFP is updated

on the falling edge of ROHCLK.

RPOHCLK Output 83 81

Receive PLCP Overhead Clock (RPOHCLK).

RPOHCLK is active when PLCP processing is

enabled. The frequency of this signal depends on

the selected PLCP format. RPOHCLK is nominally

a 26.7 kHz clock for a DS1 PLCP frame, a 768 kHz

clock for a DS3 PLCP frame, a 33.7 kHz clock for an

E1 based PLCP frame, or a 576 kHz clock for a

G.751 E3 based PLCP frame. RPOHFP and RPOH

are updated on the falling edge of RPOHCLK.

RPOH Output 84 82

Receive PLCP Overhead Data (RPOH). RPOH

contains the PLCP path overhead octets (Zn, F1,

B1, G1, M1, M2, and C1) extracted from the

received PLCP frame when the PLCP layer is inframe. When the PLCP layer is in the loss of frame

state, RPOH is forced to all ones. The octet data on

RPOH is shifted out in order from the most

significant bit (bit 1) to the least significant bit (bit 8).

RPOH is updated on the falling edge of RPOHCLK.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

20

RPOHFP Output 82 80

Receive PLCP Overhead Frame Position

(RPOHFP). RPOHFP locates the individual PLCP

path overhead bits in the receive overhead data

stream, RPOH. RPOHFP is logic 1 while bit 1 (the

most significant bit) of the path user channel octet

(F1)is present in the RPOH stream. RPOHFP is

updated on the falling edge of RPOHCLK.

RDLSIG Output 89 n/a

Receive Data Link Signal (RDLSIG). In DS3

mode, RDLSIG contains the Path Maintenance

Data Link signal from the received C-bit Parity DS3

stream. RDLSIG is not affected by the RNETOP bit

in the S/UNI-PDH Data Link and FERF Control

register while in DS3 mode. In E3 G.832 mode,

RDLSIG contains the NR or GC data link signal, as

selected by the RNETOP bit, from the received E3

G.832 stream. In E3 G.751 mode, RDLSIG

contains the National Use bit from the received

G.751 E3 stream if the RNETOP bit is logic one.

RDLSIG is updated on the falling edge of RDLCLK.

RDLCLK Output 88 n/a

Receive Data Link Clock (RDLCLK). RDLCLK is

active when a DS3 or E3 G.832 stream is being

processed. With an E3 G.751 stream, the RNETOP

bit in the S/UNI-PDH Data Link and FERF Control

register must be set to logic one for RDLCLK to be

active.

RCELL Output 49 53

Receive Cell Indication (RCELL). RCELL pulses

once for every cell received. RCELL is updated

using timing derived from the receive input clock

(RCLK) and is active for a minimum of 8 RCLK

periods. RCELL is forced to logic 0 when in the

FIFO bypass mode.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

21

LCD Output 50 n/a

Loss of Cell Delineation (LCD). The LCD signal

indicates when cell delineation cannot be found.

LCD transitions to logic 1 when an out of cell

delineation (OCD) defect has persisted past a

selected threshold. Once asserted, OCD remains

logic 1 until no OCD defect has been detected past

the selected threshold. The OCD defect state is

entered when the cell delineation state machine is

not in the SYNC state (please refer to the

Functional Description section for an explanation of

the cell delineation state machine). The LCD

indication is available for register access and can be

enabled to generate a microprocessor interrupt.

FRDB/

RFCLK

Input 69 70

FIFO Read (FRDB). FRDB reads cell octets from

the receive FIFO. The data is enabled on the

FRDATA[7:0] outputs on the falling edge of FRDB.

RSOC, REOH, and REOC are updated on the rising

edge of FRDB. Note that when the receive FIFO is

bypassed, FRDB should be logic 1 to minimize the

S/UNI-PDH power consumption.

Read FIFO Clock (RFCLK). RFCLK is used to

read bytes from the synchronous FIFO interface.

This interface is only available in the 100-pin PQFP

package when the synchronous FIFO interface is

enabled (SYFIFOB tied to logic 0). RFCLK must

cycle at a 25 MHz or lower instantaneous rate, but

at a high enough rate to avoid FIFO overflow.

RRDENB is sampled using the rising edge of

RFCLK. RSOC, RCA, RXPRTY, and FRDATA[7:0]

are all updated on the rising edge of RFCLK.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

22

RRDENB Input 70 n/a

Receive FIFO Read Enable (RRDENB). This

active low enable signal is used to initiate reads

from the synchronous receive FIFO interface (when

SYFIFOB is tied to logic 0). RRDENB sampled (on

the rising edge of RFCLK) at logic 0 indicates that

RSOC and FRDATA[7:0] will be sampled by the ATM

layer at the end of the current RFCLK cycle (on the

next rising edge of RFCLK). When RRDENB is

sampled at logic 1, no read is performed. RRDENB

must be used in conjunction with RFCLK to access

the FIFO at a high enough instantaneous rate as to

avoid FIFO overflow. The RRDENB signal is only

available in the 100-pin PQFP package. RRDENB

contains an integral pull-down resistor.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

23

RFIFOE/

RCA/

FRCLK

Output 52 54

Receive FIFO Empty (RFIFOE). RFIFOE indicates

the receive FIFO status. RFIFOE is logic 1 when

the cell-based FIFO is empty and logic 0 when the

FIFO contains at least 1 cell. RFIFOE timing is

applicable when using the asynchronous FIFO

interface in the S/UNI-PDH (either in the 84-pin

PLCC or when SYFIFOB is tied to logic 1 in the

100-pin package). Note that with the asynchronous

FIFO interface RFIFOE transitions from empty to full

(logic 1 to logic 0) on write cell boundaries with

timing derived from the RCLK input. RFIFOE

transitions from full to empty (logic 0 to logic 1) on

read cell boundaries on the rising edge of FRDB.

RFIFOE should be treated by the ATM layer as a

purely asynchronous signal.

Receive Cell Available (RCA). RCA is available in

the 100-pin PQFP package when SYFIFOB is tied

to logic 0. When the synchronous FIFO interface is

used, RCA is an active high signal and is logic 1

when the cell-based FIFO contains at least 1 cell

and is logic 0 when the cell-based FIFO is empty.

RCA can be enabled to transition low when the

FIFO is empty (default) or when the FIFO is 4 bytes

away from being empty (almost empty), as

controlled by the REMPTY4 register bit. RCA

transitions on rising edges of the RFCLK.

Receive Cell Clock (FRCLK). FRCLK is derived

from RCLK when the receive FIFO is bypassed (the

FIFOBP bit in the S/UNI-PDH Configuration

Register is logic 1). FRDATA[7:0], LOF, OOF, and

RSOC are updated on the falling edge of FRCLK.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

24

RSOC Tristate 55 57

Receive Start of Cell (RSOC). RSOC indicates

the start of a 53 octet cell. It is asserted when the

first octet is read from the receive FIFO. RSOC is

tristateable in the 100-pin PQFP package when

TSEN is logic 1. It is forced tristate while FRDB is

high and the receive FIFO is not bypassed (when

SYFIFOB is logic 1), or while RRDENB is sampled

high by the rising edge of RFCLK (when SYFIFOB

is logic 0). The RSOC logic va lue is driven on the

pin while FRDB is low (asynchronous FIFO

interface) or while RRDENB is sampled logic 0

(synchronous interface). RSOC is updated on the

rising edge of FRDB or RFCLK. When the receive

FIFO is bypassed, RSOC is updated on the falling

edge of FRCLK.

REOH/

LOF

Tristate 53 55

Receive End of Header (REOH). REOH is

asserted when the fifth octet of the 53 octet cell is

read from the receive FIFO. REOH is tristatable in

the 100-pin PQFP package when TSEN is logic 1. It

is forced tristate while FRDB is high and the receive

FIFO is not bypassed (when SYFIFOB is logic 1), or

while RRDENB is sampled high by the rising edge

of RFCLK (when SYFIFOB is logic 0). The REOH

logic value is driven on the pin while FRDB is low

(asynchronous FIFO interface) or while RRDENB is

sampled logic 0 (synchronous interface). REOH is

updated on the rising edge of FRDB or RFCLK.

PLCP Loss of Frame (LOF). LOF is asserted

while the PLCP receiver is in a loss of frame state.

LOF may be used to indicate the valid/invalid status

of the FRDATA[7:0] octets to a higher layer

processing entity while the receive FIFO is

bypassed. LOF is updated on the falling edge of

FRCLK.

The REOH/LOF pin function selection is controlled

by the FIFOBP bit in the S/UNI-PDH Configuration

Register.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

25

REOC/

OOF

Tristate 54 56

Receive End of Cell (REOC). REOC is asserted

when the 53rd octet of the 53 octet cell is being

read from the receive FIFO. RSOC is tristatable in

the 100-pin PQFP package when TSEN is logic 1. It

is forced tristate while FRDB is high and the receive

FIFO is not bypassed (when SYFIFOB is logic 1), or

while RRDENB is sampled high by the rising edge

of RFCLK (when SYFIFOB is logic 0). The RSOC

logic value is driven on the pin while FRDB is low

(asynchronous FIFO interface) or while RRDENB is

sampled logic 0 (synchronous interface). REOC is

updated on the rising edge of FRDB or RFCLK.

PLCP Out of Frame (OOF). OOF is asserted while

the PLCP receiver is in an out of frame state. OOF

may be used to indicate the valid/invalid status of

the FRDATA[7:0] octets to a higher layer processing

entity while the receive FIFO is bypassed. OOF is

updated on the falling edge of FRCLK.

The REOC/OOF pin function selection is controlled

by the FIFOBP bit in the S/UNI-PDH Configuration

Register.

FRDATA[7]

FRDATA[6]

FRDATA[5]

FRDATA[4]

FRDATA[3]

FRDATA[2]

FRDATA[1]

FRDATA[0]

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

Tristate

68

67

66

65

59

58

57

56

69

68

67

66

61

60

59

58

Receive FIFO Data (FRDATA[7:0]). FRDATA[7:0]

contains the cell octet that is read from the receive

FIFO. The FRDATA[7:0] bus is tristatable in the 100pin PQFP package when TSEN is logic 1.

FRDATA[7:0] is forced tristate while FRDB is high

and the receive FIFO is not bypassed (when

SYFIFOB is logic 1), or while RRDENB is sampled

high by the rising edge of RFCLK (when SYFIFOB

is logic 0). The octet read from the receive FIFO is

driven on the FRDATA[7:0] bus while FRDB is low

(asynchronous FIFO interface) or while RRDENB is

sampled logic 0 (synchronous interface).

FRDATA[7:0] is updated on the falling edge of

FRCLK when the receive FIFO is bypassed.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

26

RXPRTY Tristate 62 n/a

Receive FIFO Read Data Parity (RXPRTY).

RXPRTY is only available in the 100-pin PQFP

package. RXPRTY indicates the parity of the byte

on FRDATA[7:0]. Even or Odd parity is computed

over the FRDATA[7:0] bus, depending upon the

REVEN register bit setting. If REVEN is logic 1,

even parity is calculated; if REVEN is logic 0, odd

parity is calculated. By default, RXPRTY indicates

odd parity. RXPRTY is tristatable when TSEN is

logic 1. RXPRTY is forced tristate while FRDB is

high (when SYFIFOB is logic 1), or while RRDENB

is sampled high by the rising edge of RFCLK (when

SYFIFOB is logic 0). The parity value is driven on

RXPRTY while FRDB is low (asynchronous FIFO

interface) or while RRDENB is sampled logic 0

(synchronous interface).

TSEN Input 51 n/a

Tristate Bus E nable (TSEN). TSEN controls the

tristatability of the FRDATA[7:0], RXPRTY, REOH,

REOC and RSOC pins in the 100-pin PQFP

package. When TSEN is logic 1, the FRDATA[7:0]

bus, RXPRTY, REOH, REOC and RSOC can be

tristated by either the FRDB signal or the sampled

RRDENB signal (depending upon the interface

selected by SYFIFOB). When TSEN is logic 0, the

FRDATA[7:0] bus, RXPRTY, REOH, REOC and

RSOC are always active and forced to digital logic

values. TSEN contains an integral pull-up resistor.

PM7345 S/UNI-PDH

DATA SHEET

PMC-931011 ISSUE 6 SATURN USER-NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

27

FWRB/

TFCLK

Input 80 79

FIFO Write (FWRB). FWRB writes cell octets to the

transmit FIFO. The data present on the

FWDATA[7:0] bus is written into the transmit FIFO

on the rising edge of FWRB. TSOC is sampled on

the falling edge of FWRB.

Transmit FIFO Write Clock (TFCLK). TFCLK is

used to write bytes into the synchronous transmit

FIFO interface. This interface is only available in the

100-pin PQFP package when the synchronous

FIFO interface is enabled (SYFIFOB tied to logic 0).

TFCLK must cycle at a 25 MHz or lower

instantaneous r ate. TWRENB, TSOC, TXPR TY, and

FWDATA[7:0] are all sampled on the rising edge of

TFCLK. TCA is updated on the rising edge of

TFCLK.

TWRENB Input 81 n/a

Transmit FIFO Write Enable (TWRENB). This

active low enable signal is used to initiate writes into

the transmit FIFO. TWRENB is sampled on the

rising edge of TFCLK. When TWRENB is sampled

as a logic 0, the byte sampled on the FWDATA[7:0]

bus is written to the transmit FIFO. When TWRENB

is sampled as a logic 1, no write is performed. A

complete 53 byte cell must be written to the FIFO