PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

PM7341

S/UNI-IMA-84

S/UNI INVERSE MULTIPLEXING FOR

ATM, 84 LINKS

DATASHEET

PROPRIETARY AND CONFIDENTIAL

PRELIMINARY

ISSUE 4: JULY 2001

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iii

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

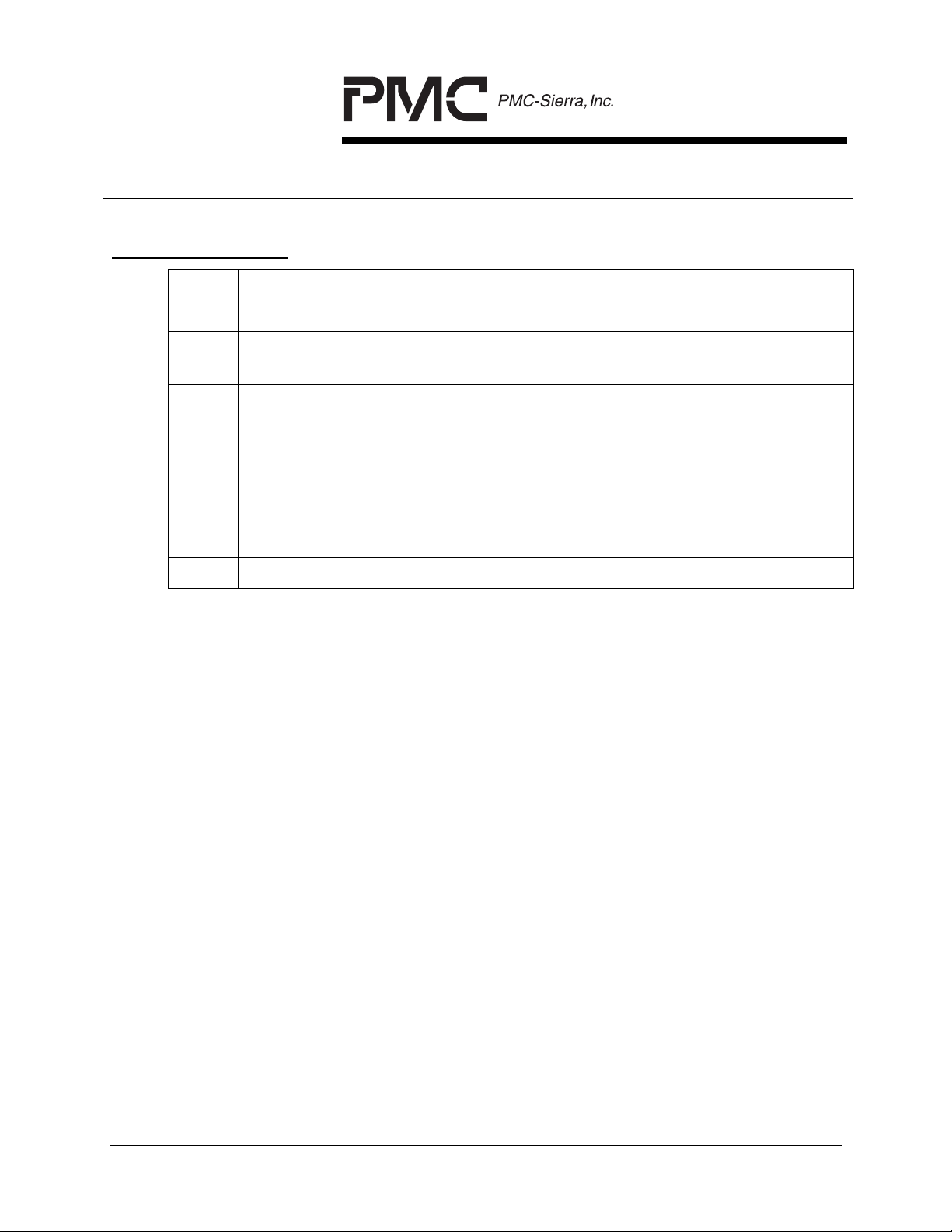

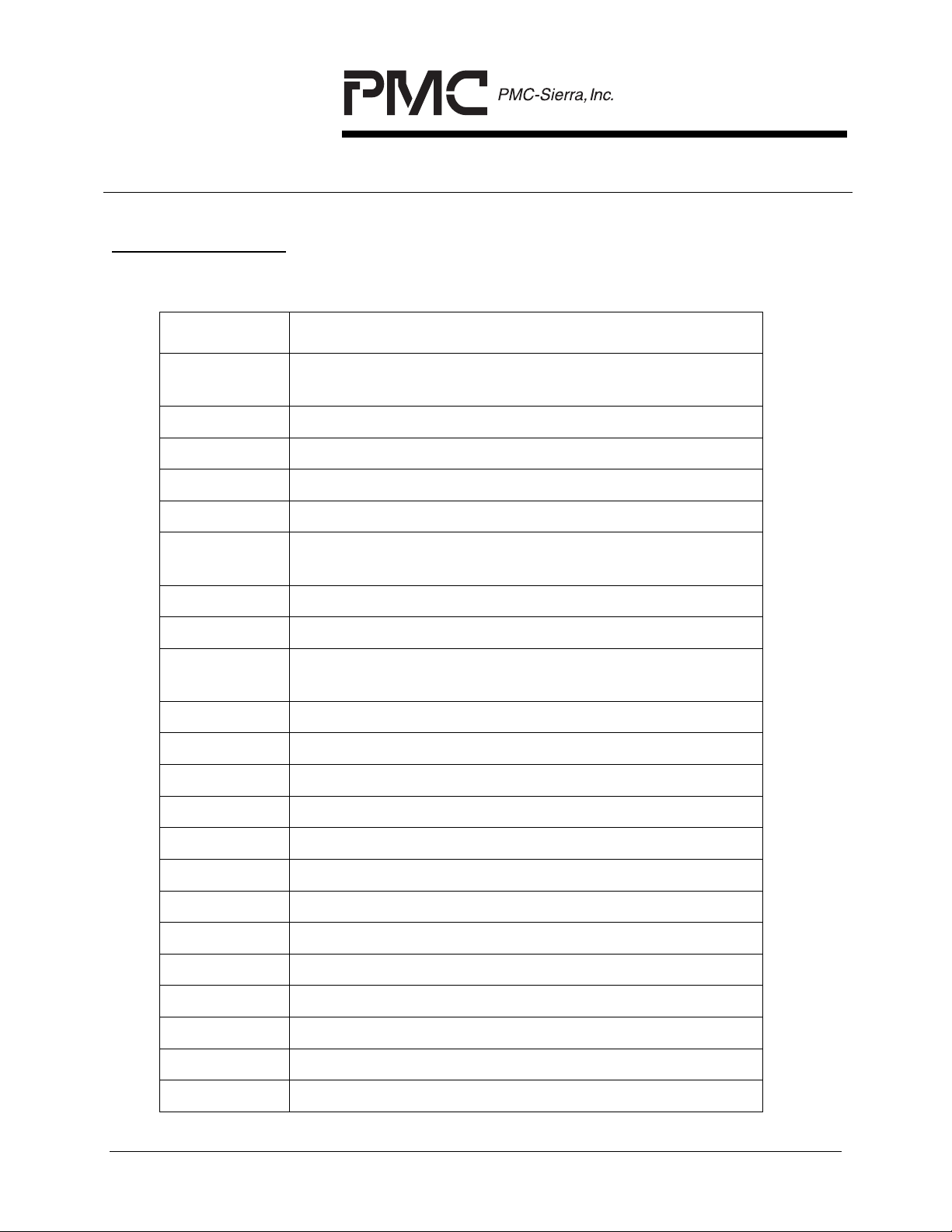

REVISION HISTORY

Issue

Issue Date Details of Change

No.

1 February,

2000

2 March, 2000

3 February,

2001

4 July, 2001

Creation of Document.

Added details in Register Section, Functional

Description, Operations and D.C. characteristics.

Added details in interrupt reporting structure, SBI

async/sync support clarified. Increased number of

TADR pins to 11 for glueless interconnect to the S/UNIAPEX. Rearranged IMA context and configuration

tables. Added capability to add/delete delay from active

groups.

Additional detailed added.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iv

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

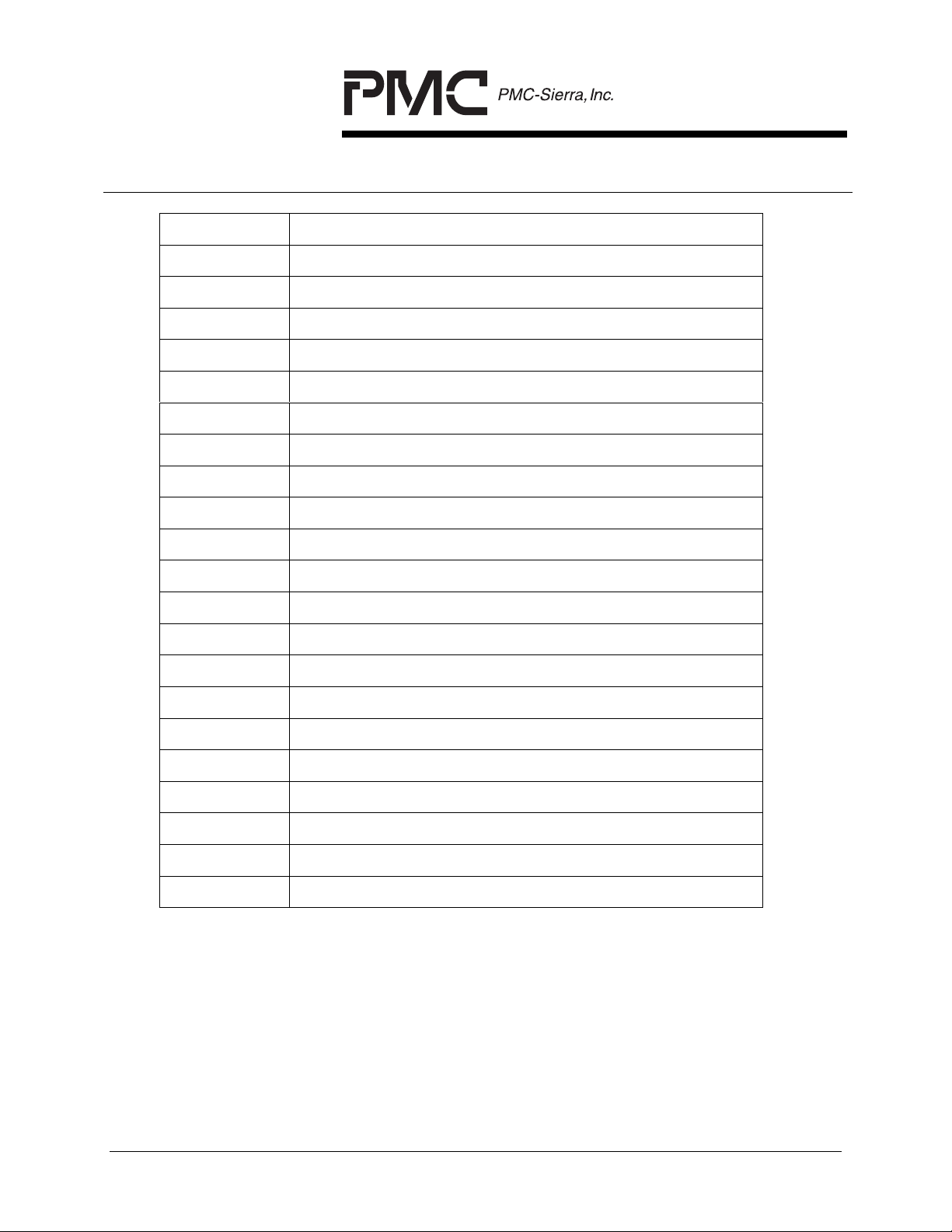

CONTENTS

1 DEFINITIONS ........................................................................................ 23

2 FEATURES ............................................................................................ 25

3 APPLICATIONS ..................................................................................... 31

4 REFERENCES....................................................................................... 32

5 APPLICATION EXAMPLES ................................................................... 33

5.1 ATM MULTISERVICE SWITCH IMA / UNI PORT CARD............. 33

5.2 ATM MULTISERVICE SWITCH, ANY SERVICE ANY PORT CARD

.................................................................................................... 33

6 BLOCK DIAGRAM ................................................................................. 35

7 DESCRIPTION....................................................................................... 36

8 PIN DIAGRAM ....................................................................................... 39

9 PIN DESCRIPTION................................................................................ 41

9.1 RECEIVE SLAVE ATM INTERFACE (ANY-PHY MODE) (28

SIGNALS).................................................................................... 41

9.2 RECEIVE SLAVE ATM INTERFACE (UTOPIA L2 MODE) (26

SIGNALS).................................................................................... 44

9.3 TRANSMIT SLAVE INTERFACE (ANY-PHY MODE) (34 SIGNALS)46

9.4 TRANSMIT SLAVE INTERFACE (UTOPIA L2 MODE) (26

SIGNALS).................................................................................... 49

9.5 MICROPROCESSOR INTERFACE (31 SIGNALS)..................... 51

9.6 SDRAM I/F (35 SIGNALS) .......................................................... 53

9.7 CLK/DATA (129 SIGNALS).......................................................... 56

9.8 SBI INTERFACE SIGNALS (27).................................................. 60

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE v

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

9.9 GENERAL (5 SIGNALS) ............................................................. 65

9.10 JTAG & SCAN INTERFACE (7 SIGNALS) .................................. 67

9.11 POWER (120 SIGNALS)............................................................. 68

10 FUNCTIONAL DESCRIPTION............................................................... 71

10.1 ANY-PHY/UTOPIA INTERFACES ............................................... 71

10.1.1 TRANSMIT ANY-PHY/UTOPIA SLAVE (TXAPS).............. 72

10.1.2 RECEIVE ANY-PHY/UTOPIA SLAVE (RXAPS)................ 75

10.1.3 SUMMARY OF ANY-PHY/UTOPIA MODES..................... 79

10.1.4 ANY-PHY/UTOPIA LOOPBACK ....................................... 81

10.2 IMA SUB-LAYER ......................................................................... 81

10.2.1 OVERVIEW ...................................................................... 81

10.2.2 IDCC SCHEDULER.......................................................... 82

10.2.3 TRANSMIT IMA PROCESSOR (TIMA) ............................ 83

10.2.4 RECEIVE IMA DATA PROCESSOR (RDAT) .................... 87

10.2.5 RECEIVE IMA PROTOCOL PROCESSOR (RIPP) ........ 100

10.2.6 SUPPORT OF IMA TEST PATTERN PROCEDURE ....... 111

10.2.7 SUPPORT OF SYMMETRIC/ASYMMETRIC OPERATION

MODES ...........................................................................111

10.2.8 SUPPORT OF DIFFERENT IMA VERSIONS ..................111

10.2.9 SDRAM INTERFACE.......................................................112

10.3 LINK FIFOS................................................................................115

10.4 TC LAYER ..................................................................................115

10.4.1 TX TC LAYER (TTTC) .....................................................115

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vi

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

10.4.2 RX TC LAYER (RTTC).....................................................116

10.5 LINE SIDE PHYSICAL LAYER ...................................................118

10.5.1 TX CLOCK/DATA (TCAS)................................................118

10.5.2 TX NULL FRAMER (SDFR84).........................................119

10.5.3 INSERT SCALEABLE BANDWIDTH INTERCONNECT

(INSBI).............................................................................119

10.5.4 EXTRACT SCALEABLE BANDWIDTH INTERCONNECT

(EXSBI)............................................................................119

10.5.5 RX DEFRAMER (SDDF84) ............................................ 120

10.5.6 RX CLOCK/DATA (RCAS) .............................................. 120

10.6 MICROPROCESSOR INTERFACE .......................................... 121

10.6.1 MAPPING AND LINK IDENTIFICATION......................... 121

10.6.2 INTERRUPT DRIVEN ERROR/STATUS REPORTING .. 123

10.6.3 REGISTERS................................................................... 124

11 NORMAL MODE REGISTER DESCRIPTION ..................................... 131

11.1 GLOBAL REGISTERS .............................................................. 132

11.2 MASTER INTERRUPT REGISTERS ........................................ 137

11.3 UTOPIA INTERFACE REGISTERS .......................................... 147

11.4 SDRAM REGISTERS................................................................ 156

11.5 TC LAYER REGISTERS ........................................................... 166

11.6 SBI REGISTERS....................................................................... 177

11.7 LINE CLOCK/DATA INTERFACE .............................................. 203

11.8 RIPP REGISTERS .................................................................... 217

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vii

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

11.9 RDAT REGISTERS ................................................................... 292

11.10 TIMA REGISTERS .................................................................... 325

11.11 TX IDCC REGISTERS .............................................................. 341

11.12 RX IDCC REGISTERS.............................................................. 347

12 OPERATION ........................................................................................ 351

12.1 HARDWARE CONFIGURATION............................................... 351

12.2 START-UP................................................................................. 351

12.3 CONFIGURING THE S/UNI-IMA-84.......................................... 352

12.3.1 CONFIGURING SBI INTERFACE .................................. 352

12.3.2 CONFIGURING CLOCK/DATA INTERFACE.................. 354

12.3.3 CONFIGURING TC LAYER OPTIONS........................... 356

12.3.4 UTOPIA INTERFACE CONFIGURATION....................... 357

12.4 IMA_LAYER CONFIGURATION................................................ 358

12.4.1 INDIRECT ACCESS TO INTERNAL MEMORY TABLES 358

12.4.2 CONFIGURING LINKS FOR TRANSMISSION

CONVERGENCE OPERATIONS ................................... 359

12.4.3 CONFIGURING FOR IMA OPERATIONS ...................... 361

12.5 IMA OPERATIONS.................................................................... 365

12.5.1 ISSUING A RIPP COMMAND......................................... 365

12.5.2 SUMMARY OF RIPP COMMANDS ................................ 366

12.5.3 ADDING A GROUP......................................................... 371

12.5.4 DELETING A GROUP..................................................... 372

12.5.5 RESTART GROUP ......................................................... 372

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE viii

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

12.5.6 INHIBIT GROUP/NOT INHIBIT GROUP......................... 373

12.5.7 ADDING A LINK OR LINKS TO AN EXISTING GROUP

(START LASR) ............................................................... 373

12.5.8 REPORTING LINK DEFECTS IN THE ICP CELL .......... 374

12.5.9 FAULTING/INHIBITING LINKS ...................................... 374

12.5.10 CHANGE TRL............................................................ 374

12.5.11 DELETING A LINK FROM A GROUP......................... 375

12.5.12 TEST PATTERN PROCEDURES .............................. 375

12.5.13 IMA EVENTS ............................................................. 375

12.5.14 END-TO-END CHANNEL COMMUNICATION........... 376

12.6 DIAGNOSTIC FEATURES ........................................................ 376

12.6.1 ICP CELL TRACE........................................................... 376

12.6.2 SDRAM DIAGNOSTIC ACCESS.................................... 377

12.7 IMA PERFORMANCE PARAMETERS AND FAILURE ALARMS

SUPPORT................................................................................. 378

13 FUNCTIONAL TIMING......................................................................... 382

13.1 SBI DROP BUS INTERFACE TIMING ...................................... 382

13.2 SBI ADD BUS INTERFACE TIMING ......................................... 383

13.3 RECEIVE LINK INPUT TIMING................................................. 384

13.4 TRANSMIT LINK OUTPUT TIMING .......................................... 385

13.5 ANY-PHY/UTOPIA L2 INTERFACES ........................................ 388

13.5.1 UTOPIA L2 TRANSMIT SLAVE INTERFACE................. 388

13.5.2 ANY-PHY TRANSMIT SLAVE INTERFACE.................... 389

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ix

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

13.5.3 UTOPIA L2 MULTI-PHY RECEIVE SLAVE INTERFACE 390

13.5.4 UTOPIA L2 SINGLE-PHY RECEIVE SLAVE INTERFACE

391

13.5.5 ANY-PHY RECEIVE SLAVE INTERFACE ...................... 392

13.6 SDRAM INTERFACE ................................................................ 392

14 ABSOLUTE MAXIMUM RATINGS ....................................................... 397

15 D. C. CHARACTERISTICS .................................................................. 398

16 A.C. TIMING CHARACTERISTICS...................................................... 401

16.1 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS

.................................................................................................. 401

16.2 SYNCHRONOUS I/O TIMING................................................... 405

16.3 SBI TIMING ............................................................................... 409

16.4 JTAG TIMING............................................................................ 412

17 ORDERING AND THERMAL INFORMATION...................................... 414

18 MECHANICAL INFORMATION ............................................................ 415

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE x

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

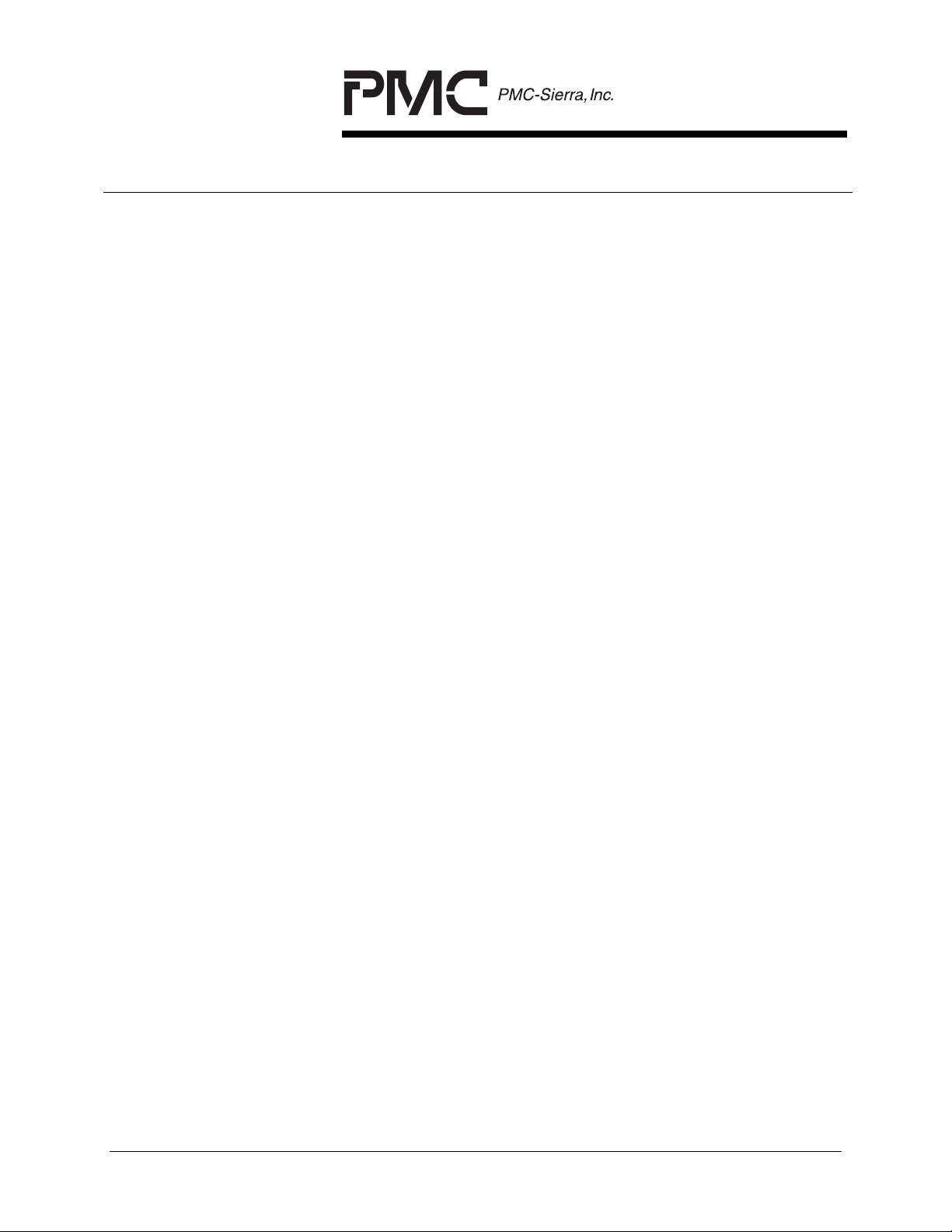

LIST OF FIGURES

FIGURE 1 - ATM EDGE SWITCH IMA AND UNI PORT CARD EXAMPLE ..... 33

FIGURE 2 - ATM MULTISERVICE SWITCH, ANY SERVICE ANY PORT CARD

EXAMPLE 34

FIGURE 3 - S/UNI-IMA-84 BLOCK DIAGRAM................................................ 35

FIGURE 4 - S/UNI-IMA PINOUT (BOTTOM VIEW)......................................... 40

FIGURE 5 - 16-BIT TRANSMIT CELL TRANSFER FORMAT ......................... 74

FIGURE 6 - 8-BIT TRANSMIT CELL TRANSFER FORMAT ........................... 74

FIGURE 7 - 16-BIT RECEIVE CELL TRANSFER FORMAT............................ 78

FIGURE 8 - 8-BIT RECEIVE CELL TRANSFER FORMAT.............................. 78

FIGURE 9 - INVERSE MULTIPLEXING .......................................................... 82

FIGURE 10- MAX DIFFERENTIAL DELAY TOLERANCE VS. SDRAM SIZE .. 88

FIGURE 11 - IFSM STATE MACHINE............................................................... 89

FIGURE 12- STUFF EVENT WITH ERRORED ICP (ADVANCED INDICATION)

91

FIGURE 13- INVALID STUFF SEQUENCE (ADVANCED INDICATION) ......... 91

FIGURE 14- ERRORED/INVALID ICP CELLS IN PROXIMITY TO A STUFF

EVENT 92

FIGURE 15- SNAPSHOT OF DCB BUFFERS................................................. 93

FIGURE 16- SNAPSHOT OF DCB BUFFERS AFTER ADDITION OF LINK WITH

SMALLER TRANSPORT DELAY...................................................................... 94

FIGURE 17- SNAPSHOT OF DCB BUFFERS WHEN TRYING TO ADD LINK

WITH LARGER TRANSPORT DELAY.............................................................. 95

FIGURE 18- SNAPSHOT OF DCB BUFFERS AFTER DELAY ADJUSTMENT 96

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xi

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

FIGURE 19- SNAPSHOT OF DCB BUFFERS AFTER DELETION OF LINKS

FROM GROUP 97

FIGURE 20- IMA ERROR/MAINTENANCE STATE DIAGRAM ........................ 98

FIGURE 21- CELL STORAGE MAP................................................................112

FIGURE 22- 2 MBYTE ....................................................................................113

FIGURE 23- 8 MBYTE ....................................................................................114

FIGURE 24- CELL DELINEATION STATE DIAGRAM.....................................117

FIGURE 25-BURST RAM FORMAT............................................................... 161

FIGURE 26- SBI DROP BUS T1/E1 FUNCTIONAL TIMING.......................... 382

FIGURE 27- SBI DROP BUS DS3 FUNCTIONAL TIMING ............................ 382

FIGURE 28- SBI ADD BUS ADJUSTMENT REQUEST FUNCTIONAL TIMING

383

FIGURE 29- UNCHANNELIZED RECEIVE LINK TIMING ............................. 384

FIGURE 30- CHANNELIZED T1 RECEIVE LINK TIMING ............................. 385

FIGURE 31- CHANNELIZED E1 RECEIVE LINK TIMING ............................. 385

FIGURE 32- UNCHANNELIZED TRANSMIT LINK TIMING........................... 386

FIGURE 33- CHANNELIZED T1 TRANSMIT LINK TIMING W/ CLOCK GAPPED

LOW 386

FIGURE 34- CHANNELIZED T1 TRANSMIT LINK TIMING W/ CLOCK GAPPED

HIGH 387

FIGURE 35- CHANNELIZED E1 TRANSMIT LINK TIMING W/ CLOCK GAPPED

LOW 387

FIGURE 36- CHANNELIZED E1 TRANSMIT LINK TIMING W/ CLOCK GAPPED

HIGH 387

FIGURE 37- UTOPIA L2 TRANSMIT SLAVE ................................................. 389

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xii

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

FIGURE 38- ANY-PHY TRANSMIT SLAVE .................................................... 390

FIGURE 39- UTOPIA L2 MULTI-PHY RECEIVE SLAVE................................ 391

FIGURE 40- UTOPIA L2 SINGLE-PHY RECEIVE SLAVE ............................. 391

FIGURE 41- ANY-PHY RECEIVE SLAVE ...................................................... 392

FIGURE 42- SDRAM READ TIMING ............................................................. 393

FIGURE 43- SDRAM WRITE TIMING............................................................ 394

FIGURE 44- SDRAM REFRESH.................................................................... 395

FIGURE 45- POWER UP AND INITIALIZATION SEQUENCE ....................... 396

FIGURE 46- MICROPROCESSOR INTERFACE READ TIMING................... 402

FIGURE 47- MICROPROCESSOR INTERFACE WRITE TIMING ................. 404

FIGURE 48- RSTB TIMING............................................................................ 405

FIGURE 49- SYNCHRONOUS I/O TIMING ................................................... 405

FIGURE 50- SBI FRAME PULSE TIMING ..................................................... 409

FIGURE 51- SBI DROP BUS TIMING............................................................ 410

FIGURE 52- SBI ADD BUS TIMING................................................................411

FIGURE 53- SBI ADD BUS COLLISION AVOIDANCE TIMING ......................411

FIGURE 54- JTAG PORT INTERFACE TIMING............................................. 413

FIGURE 55- 416 PIN PBGA –27X27 MM BODY – (P SUFFIX) ..................... 415

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xiii

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

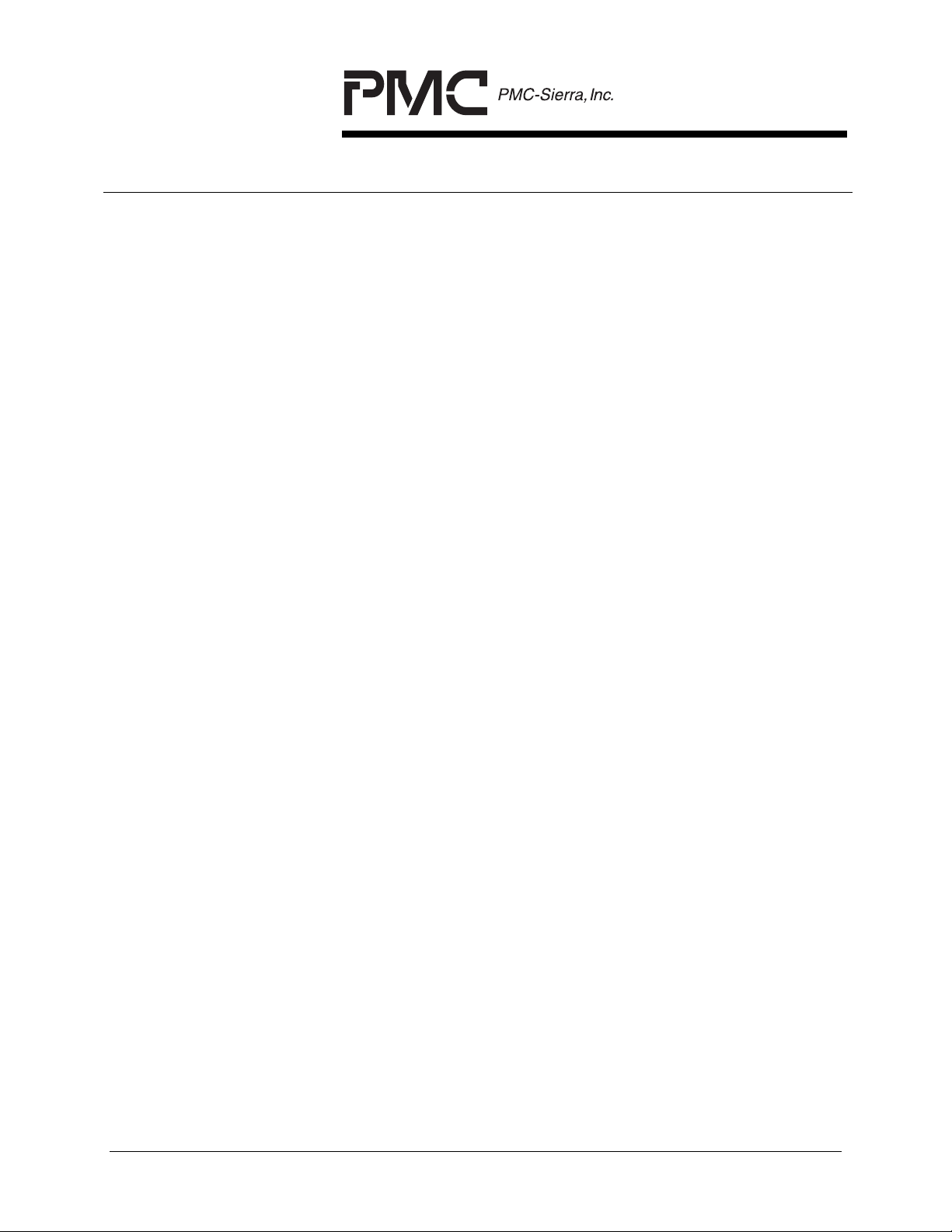

LIST OF TABLES

TABLE 1 TERMINOLOGY............................................................................. 23

TABLE 2 UTOPIA L2 AND ANY-PHY COMPARISON ................................... 76

TABLE 3 PM COMMAND DESCRIPTION .................................................. 101

TABLE 4 REGISTER MEMORY MAP......................................................... 125

TABLE 5 CONFIGURATION MEMORY ADDRESS SPACE ....................... 218

TABLE 6 CONTEXT MEMORY ADDRESS SPACE .................................... 219

TABLE 7 RIPP GROUP CONFIGURATION RECORD STRUCTURE ........ 221

TABLE 8 RX PHYSICAL LINK TABLE ........................................................ 229

TABLE 9 RIPP TX LINK CONFIGURATION RECORD STRUCTURE ........ 230

TABLE 10 RIPP RX LINK CONFIGURATION RECORD STRUCTURE........ 232

TABLE 11 RIPP GROUP CONTEXT RECORD STRUCTURE ..................... 234

TABLE 12 RIPP TX LINK CONTEXT RECORD STRUCTURE..................... 249

TABLE 13 RIPP RX LINK CONTEXT RECORD STRUCTURE .................... 253

TABLE 14 COMMAND REGISTER ENCODING........................................... 271

TABLE 15 COMMAND DATA REGISTER ARRAY FORMAT ........................ 282

TABLE 16 GROUP ERROR/STATUS BIT MAPPING ................................... 284

TABLE 17 LINK EVENT INTERRUPT BIT MAPPING................................... 286

TABLE 18 LINK STATUS BIT MAPPING ...................................................... 288

TABLE 19 RECEIVE ICP CELL BUFFER STRUCTURE .............................. 290

TABLE 20 RDAT LINK STATISTICS RECORD (IMA) ................................... 297

TABLE 21 RDAT LINK STATISTICS RECORD (TC)..................................... 298

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xiv

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

TABLE 22 RDAT IMA GROUP STATISTICS RECORD................................. 299

TABLE 23 RDAT TC LINK STATISTICS RECORD ....................................... 300

TABLE 24 RDAT VALIDATION RECORD ..................................................... 301

TABLE 25 RDAT LINK CONTEXT RECORD................................................ 304

TABLE 26 RDAT LINK MESSAGE STATUS RECORD................................. 309

TABLE 27 RECEIVE ICP CELL BUFFER STRUCTURE .............................. 310

TABLE 28 RDAT IMA GROUP CONTEXT RECORD.................................... 312

TABLE 29 RDAT TC LINK CONTEXT RECORD .......................................... 314

TABLE 30 RECEIVE ATM CONGESTION COUNT REGISTER ................... 315

TABLE 31 TRANSMIT IMA GROUP CONTEXT RECORD ........................... 330

TABLE 32 TRANSMIT IMA GROUP CONFIGURATION TABLE RECORD .... 333

TABLE 33 TRANSMIT LID TO PHYSICAL LINK MAPPING TABLE ............. 335

TABLE 34 TIMA PHYSICAL LINK CONTEXT RECORD............................... 336

TABLE 35 REFCLK/SYSCLK FREQUENCY REQUIREMENT..................... 356

TABLE 36 IMA PERFORMANCE PARAMETER SUPPORT......................... 378

TABLE 37 IMA FAILURE ALARM SUPPORT................................................ 379

TABLE 38 ABSOLUTE MAXIMUM RATINGS ............................................... 397

TABLE 39 D.C. CHARACTERISTICS ........................................................... 398

TABLE 40 MICROPROCESSOR INTERFACE READ ACCESS................... 401

TABLE 41 MICROPROCESSOR INTERFACE WRITE ACCESS ................. 403

TABLE 42 RTSB TIMING.............................................................................. 404

TABLE 43 SYSCLK AND REFCLK TIMING.................................................. 405

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xv

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

TABLE 44 CELL BUFFER SDRAM INTERFACE .......................................... 406

TABLE 45 ANY-PHY/UTOPIA TRANSMIT INTERFACE ............................... 406

TABLE 46 ANY-PHY/UTOPIA RECEIVE INTERFACE.................................. 407

TABLE 47 SERIAL LINK INPUT.................................................................... 407

TABLE 48 SERIAL LINK OUTPUT................................................................ 408

TABLE 49 SBI FRAME PULSE TIMING ....................................................... 409

TABLE 50 SBI DROP BUS TIMING .............................................................. 409

TABLE 51 SBI ADD BUS .............................................................................. 410

TABLE 52 JTAG PORT INTERFACE ............................................................ 412

TABLE 53 ORDERING AND THERMAL INFORMATION.............................. 414

TABLE 54 THERMAL INFORMATION - THETA JA VS. AIRFLOW ............... 414

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xvi

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

LIST OF REGISTERS

REGISTER 0X000: GLOBAL RESET ............................................................. 132

REGISTER 0X002: GLOBAL CONFIGURATION ........................................... 133

REGISTER 0X004: JTAG ID (MSB)................................................................ 135

REGISTER 0X006: JTAG ID (LSB)................................................................. 136

REGISTER 0X008: MASTER INTERRUPT REGISTER................................. 137

REGISTER 0X00A: MISCELLANEOUS INTERRUPT REGISTER................. 140

REGISTER 0X00C: RECEIVE TC INTERRUPT FIFO.................................... 142

REGISTER 0X010: MASTER INTERRUPT ENABLE REGISTER ................. 144

REGISTER 0X012: MISCELLANEOUS INTERRUPT ENABLE REGISTER .. 145

REGISTER 0X014: TC INTERRUPT ENABLE REGISTER............................ 146

REGISTER 0X020: TRANSMIT ANY-PHY/UTOPIA CELL AVAILABLE ENABLE

147

REGISTER 0X022: RECEIVE UTOPIA CELL AVAILABLE ENABLE.............. 148

REGISTER 0X024: RECEIVE ANY-PHY/UTOPIA CONFIG REG (RXAPS_CFG)

149

REGISTER 0X026: TRANSMIT ANY-PHY/UTOPIA CONFIG REG (TXAPS_CFG)151

REGISTER 0X028: TRANSMIT ANY-PHY ADDRESS CONFIG REGISTER

(TXAPS_ADD_CFG) ...................................................................................... 153

REGISTER 0X040: SDRAM CONFIGURATION ............................................ 156

REGISTER 0X042 SDRAM DIAGNOSTICS................................................... 157

REGISTER 0X044: SDRAM DIAG BURST RAM INDIRECT ACCESS .......... 158

REGISTER 0X046: SDRAM DIAG INDIRECT BURST RAM DATA LSB ........ 159

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xvii

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

REGISTER 0X048: SDRAM DIAG INDIRECT BURST RAM DATA MSB ....... 160

REGISTER 0X04A: SDRAM DIAG WRITE CMD 1 ........................................ 162

REGISTER 0X04C: SDRAM DIAG WRITE CMD 2 ........................................ 163

REGISTER 0X04E: SDRAM DIAG READ CMD 1.......................................... 164

REGISTER 0X050: SDRAM DIAG READ CMD 2 .......................................... 165

REGISTER 0X060: TTTC INDIRECT LINK CONTROL REGISTER............... 166

REGISTER 0X062: TTTC INDIRECT LINK CONFIGURATION REGISTER .. 168

REGISTER 0X070: RTTC INDIRECT LINK CONTROL REGISTER .............. 169

REGISTER 0X072: RTTC INDIRECT LINK CONFIGURATION REGISTER .. 171

REGISTER 0X074: RTTC INDIRECT LINK INTERRUPT AND STATUS

REGISTER 173

REGISTER 0X076: RTTC INDIRECT LINK HCS ERROR COUNT REGISTER

175

REGISTER 0X078: LCD COUNT THRESHOLD ............................................ 176

REGISTER 0X080: SBI BUS CONFIGURATION REGISTER

(SBI_BUS_CFG_REG)................................................................................... 177

REGISTER 0X084-0X08E: SBI EXTRACT ALARM INTERRUPT REGISTER 179

REGISTER 0X090-0X09A: SBI EXTRACT ALARM STATUS REGISTER...... 180

REGISTER 0X0A0: SBI EXTRACT CONTROL REGISTER........................... 181

REGISTER 0X0A2: SBI EXTRACT FIFO UNDERRUN INTERRUPT REGISTER

183

REGISTER 0X0A4: SBI EXTRACT FIFO OVERRUN INTERRUPT REGISTER

184

REGISTER 0X0A6: SBI EXTRACT TRIBUTARY CONTROL RAM INDIRECT

ACCESS ADDRESS REGISTER.................................................................... 185

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xviii

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

REGISTER 0X0A8: SBI EXTRACT TRIBUTARY CONTROL RAM INDIRECT

ACCESS CONTROL REGISTER ................................................................... 186

REGISTER 0X0AC: SBI EXTRACT TRIBUTARY CONTROL RAM INDIRECT

ACCESS DATA REGISTER............................................................................ 187

REGISTER 0X0AE: SBI EXTRACT PARITY ERROR INTERRUPT REGISTER

188

REGISTER 0X0BC: SBI EXTRACT DEPTH CHECK INTERRUPT REGISTER

189

REGISTER 0X0BE: SBI EXTRACT MASTER INTERRUPT REGISTER ....... 190

REGISTER 0X0C0: SBI INSERT CONTROL REGISTER .............................. 192

REGISTER 0X0C2: SBI INSERT FIFO UNDERRUN INTERRUPT REGISTER

194

REGISTER 0X0C4: SBI INSERT FIFO OVERRUN INTERRUPT REGISTER 195

REGISTER 0X0C6: SBI INSERT TRIBUTARY CONTROL RAM INDIRECT

ACCESS ADDRESS REGISTER.................................................................... 196

REGISTER 0X0C8: SBI INSERT TRIBUTARY CONTROL RAM INDIRECT

ACCESS CONTROL REGISTER ................................................................... 197

REGISTER 0X0CC: SBI INSERT TRIBUTARY CONTROL RAM INDIRECT

ACCESS DATA REGISTER............................................................................ 198

REGISTER 0X0E2: SBI INSERT DEPTH CHECK INTERRUPT REGISTER. 200

REGISTER 0X0E4: SBI INSERT MASTER INTERRUPT REGISTER ........... 201

REGISTER 0X100: RCAS INDIRECT LINK AND TIME-SLOT CONTROL

REGISTER 203

REGISTER 0X102: RCAS INDIRECT LINK DATA REGISTER ...................... 205

REGISTER 0X104: RCAS FRAMING BIT THRESHOLD ............................... 207

REGISTER 0X106: RCAS LINK DISABLE ..................................................... 208

REGISTER 0X140- 0X17E: RCAS LINK #0 TO LINK #31 CONFIGURATION 209

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xix

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

REGISTER 0X180: TCAS INDIRECT LINK AND TIME-SLOT CONTROL

REGISTER 210

REGISTER 0X182: TCAS INDIRECT LINK DATA REGISTER....................... 212

REGISTER 0X184: TCAS FRAMING BIT THRESHOLD................................ 213

REGISTER 0X186: TCAS IDLE TIME-SLOT FILL DATA................................ 214

REGISTER 0X188: TCAS LINK DISABLE REGISTER .................................. 215

REGISTER 0X1C0 – 0X1FE: TCAS LINK #0 TO LINK #31 CONFIGURATION

216

REGISTER 0X200:RIPP CONTROL .............................................................. 217

REGISTER 0X202:RIPP INDIRECT MEMORY ACCESS CONTROL ............ 218

REGISTER 0X204 – 0X206:RIPP INDIRECT MEMORY DATA REGISTER

ARRAY 220

REGISTER 0X20C: RIPP TIMER TICK CONFIGURATION REGISTER ........ 261

REGISTER 0X20E: GROUP TIMEOUT REGISTER #1 ................................. 262

REGISTER 0X210: GROUP TIMEOUT REGISTER #2.................................. 263

REGISTER 0X212: TX LINK TIMEOUT REGISTER ...................................... 264

REGISTER 0X214: RX LINK TIMEOUT REGISTER...................................... 265

REGISTER 0X216: RIPP INTERRUPT FIFO ................................................. 266

REGISTER 0X218:RIPP GROUP INTERRUPT ENABLE REGISTER........... 267

REGISTER 0X21A:RIPP TX LINK INTERRUPT ENABLE REGISTER .......... 268

REGISTER 0X21C:RIPP RX LINK INTERRUPT ENABLE REGISTER.......... 269

REGISTER 0X220-22C: RIPP COMMAND REGISTER ................................. 270

REGISTER 0X22E: COMMAND READ DATA CONTROL REGISTER........... 276

REGISTER 0X230: ICP CELL FORWARDING STATUS REGISTER............. 277

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xx

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

REGISTER 0X232: ICP CELL FORWARDING CONTROL REGISTER ......... 278

REGISTER 0X240- 0X2BE:RIPP COMMAND DATA REGISTER ARRAY...... 279

REGISTER 0X2C0- 0X2FE: FORWARDING ICP CELL BUFFER.................. 289

REGISTER 0X300: RDAT INDIRECT MEMORY COMMAND ........................ 292

REGISTER 0X302: RDAT INDIRECT MEMORY ADDRESS .......................... 294

REGISTER 0X304: RDAT INDIRECT MEMORY DATA LSB .......................... 295

REGISTER 0X306: RDAT INDIRECT MEMORY DATA MSB ......................... 296

REGISTER 0X308: RDAT CONFIGURATION ................................................ 316

REGISTER 0X30A: RECEIVE ATM CONGESTION INTERRUPT LSB.......... 318

REGISTER 0X30C: RECEIVE ATM CONGESTION INTERRUPT MSB......... 319

REGISTER 0X30E: RECEIVE TC LINK FIFO OVERRUN INTERRUPT

REGISTER 320

REGISTER 0X310: RDAT MASTER INTERRUPT REGISTER ...................... 321

REGISTER 0X312: RECEIVE ATM CONGESTION INTERRUPT ENABLE LSB

322

REGISTER 0X314: RECEIVE ATM CONGESTION INTERRUPT ENABLE MSB

323

REGISTER 0X316: RDAT MASTER INTERRUPT ENABLE .......................... 324

REGISTER 0X320: TIMA INDIRECT MEMORY COMMAND ......................... 325

REGISTER 0X322: TIMA INDIRECT MEMORY ADDRESS ........................... 327

REGISTER 0X324: TIMA INDIRECT MEMORY DATA LSB............................ 328

REGISTER 0X326: TIMA INDIRECT MEMORY DATA MSB........................... 329

REGISTER 0X328-0X332 TRANSMIT LINK FIFO OVERRUN INTERRUPT

REGISTER 339

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xxi

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

REGISTER 0X336 INTERRUPT ENABLE...................................................... 340

REGISTER 0X340: TXIDCC INDIRECT LINK CONTROL REGISTER........... 341

REGISTER 0X342: TXIDCC INDIRECT LINK DATA REGISTER ................... 343

REGISTER 0X350: RXIDCC INDIRECT LINK CONTROL REGISTER .......... 347

REGISTER 0X352: RXIDCC INDIRECT LINK DATA REGISTER................... 349

REGISTER 0X366: DLL STATUS REGISTER................................................ 350

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xxii

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

1 DEFINITIONS

Table 1 Terminology

Term Definition

Any-PHY Interoperable version of UTOPIA and UTOPIA L2, with

inband addressing.

ATM Asynchronous Transfer Mode

CDV Cell Delay Variation

CTC Common Transmit Clock

DLL Delay Locked Loop

ECBI Enhanced Common Bus Interface (asynchronous

register bus and interface)

EXSBI Extract Scalable Bandwidth Interconnect

FIFO First-In-First-Out

Framed Framing information available – may be channelized or

unchannelized.

HEC Header Error Check

HCS Header Check Sequence

ICP IMA Control Protocol Cell

IDCC IMA Data Cell Clock

IDCR IMA Data Cell Rate

IFSN IMA Frame Sequence Number

IMA Inverse Multiplexing for ATM

INSBI Insert Scalable Bandwidth Interconnect

ITC Independent Transmit Clock

LCD Loss of Cell Delineation

LID Link ID

LSI Link Stuff Indication

MIB Management Information Base

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 23

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

MCFD Multi-Channel Cell Based FIFO

OAM Operation, Administration and Maintenance

OCD Out of Cell Delineation

PISO Parallel in Serial Out

PM Plane Management (Microprocessor)

RCAS Receive Channel Assigner

RDAT RX IMA Data Processor

RIPP RX IMA Protocol Processor

RMTS RX Master TX Slave

SBI Scalable Bandwidth Interconnect

SIPO Serial in Parallel Out

SPE Synchronous Payload Envelope

TC Transmission Convergence

TCAS Transmit Channel Assigner

TDM Time Division Multiplexing

TRL Timing Reference Link

TRLCR TRL Cell Rate

TSB Telecom Systems Block

TC Transmission Convergence

TIMA TX IMA Processor

Unframed No framing information available

UTOPIA Universal Test & Operations PHY Interface for ATM

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 24

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

2 FEATURES

The PM7341 S/UNI-IMA-84 is a monolithic integrated circuit that implements the

ATM Forum Inverse Multiplexing for ATM (IMA 1.1) protocol with backward

compatibility to IMA 1.0 and the Transmission Convergence (TC) layer function.

The S/UNI-IMA-84 has two line side interface modes that determine the total

number of physical links supported: the Scalable Bandwidth Interconnect (SBI)

bus interface mode and the Clock and Data interface mode.

In SBI mode, the S/UNI-IMA-84 supports up to 84 T1, 63 E1 or 3 DS3 (TC only)

physical links where each link is dynamically configurable to support either IMA

1.1, backward compatible IMA 1.0, ATM over T1/E1 or up to three ATM over DS3

streams (using HEC delineation).

In Clock and Data mode, the S/UNI-IMA-84 supports 32 independent T1, E1 or

unchannelized physical links. Each link is dynamically configurable to support

either IMA 1.1, backward compatible IMA 1.0, or ATM HEC cell delineation. ATM

over fractional T1/E1 is also supported. Unchannelized links may be used to

support applications such as G.SHDSL.

Standards Supported

• ATM Forum Inverse Multiplexing for ATM Specification Version 1.1, March

1999

• ATM Forum Inverse Multiplexing for ATM Specification Version 1.0 – supports

the method of reporting Rx cell information as in Appendix C.8 of the ATM

Forum Inverse Multiplexing for ATM Specification Version 1.1 for symmetrical

configurations with M=128.

• I.432-1 B-ISDN user network interface – Physical Layer specification: General

characteristics

• I.432-3 B-ISDN user network interface – Physical Layer specification: 1544

kbps and 2048 kbps operation

• DS3 Physical Layer Interface Specification, af-phy-0054.000 January, 1996

• ATM on Fractional E1/T1, af-phy-0130.00 October, 1999.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 25

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

IMA Features

• IMA 1.1 protocol including group and link state machines implemented by on-

chip hardware.

• All ICP cell processing is performed internally by the S/UNI-IMA device with

no requirement for microprocessor intervention; however, ICP cells are made

available for diagnostic purposes.

• Supports up to 42 simultaneous IMA groups.

• Each IMA group can support 1 to 32 links chosen from any of the supported

links.

• Each link can be programmed for either IMA processing or cell delineation.

• Supports all IMA Group Symmetry modes:

• Symmetrical configuration with symmetrical operation

• Symmetrical configuration with asymmetrical operation.

• Asymmetrical configuration with asymmetrical operation.

• Performs IMA differential delay calculation and synchronization.

• Provides programmable limit on allowable differential delay and minimum

number of links per group.

• Supports up to 279 ms (for T1 links) and 226 ms (for E1 links) link-differential

delay among links in an IMA group.

• Performs ICP and stuff-cell insertion and removal.

• Supports both Common Transmit Clock (CTC) and Independent Transmit

Clock (ITC) transmit ICP stuffing modes.

• Supports IMA frame lengths (M) equal to 32, 64, 128, or 256.

• Optionally supports the IMA 1.0 method of reporting Rx cell information as

defined in appendix C.8 of the ATM Forum Inverse Multiplexing for ATM

Specification Version 1.1 for symmetrical configurations with M=128.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 26

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

• Provides IMA layer statistic counts and alarms for support of IMA

Performance and Failure Alarm Monitoring and MIB support.

• Provides per link counters for statistics and performance monitoring:

• ICP Violations

• OIF anomalies

• Rx Link stuff events

• Tx Link stuff events

• User cells

• Filler cells

• Provides per group counters for statistics and performance monitoring:

• User cells received

• Filler cells received

• User cells transmitted

• Filler cells transmitted

TC Features

• Performs cell delineation on all links.

• Performs receive cell Header Error Check (HEC) checking and transmit cell

HEC generation.

• Optionally supports receive cell payload unscrambling and transmit cell

payload scrambling.

• Provides TC layer statistics counts and alarms for MIB support.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 27

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

Interface Support

• Two line side interface modes: Scalable Bandwidth Interconnect (SBI) bus

and Clock and Data.

SBI Interface:

• Supports a byte serial 19.44 MHz Scalable Bandwidth Interconnect (SBI)

bus interface for high-density line-side device interconnection of up to 84

T1, 63 E1, or three DS3 streams.

• The SBI interface bus uses three Synchronous Payload Envelopes (SPE)

where each SPE can carry up to 28 framed T1, 21 framed E1, or one

framed DS3 stream.

• For SPEs configured to support DS3, TC layer processing is supported

only. IMA is not supported over DS3.

• Always acts as a clock slave receiving clock rate information from the SBI

based framer.

• Supports Common Transmit Clock (CTC) and Independent Transmit Clock

(ITC) modes across the SBI bus.

• Seamlessly interconnects to PMC-Sierra’s PM8315 TEMUX and PM8316

TEMUX-84 highly integrated T1/ E1 framers, M13 MUXs and SONET/SDH

VT/TU mapper devices

Clock/Data Interface:

• Supports 32 individual serial (T1 or E1 or unchannelized rates up to 2.304

Mbps) links or 8 individual serial 8Mbps unchannelized links via a 2-pin

clock and data interface.

• Supports ATM over fractional T1/E1 by providing the capability to select

any DS0 timeslots that are active in a link.

• Serial link interface supports both independent transmit clock (ITC) and

common transmit clock (CTC) options.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 28

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

• Interfaces to a 1M x 16 ( for at least 69 msec of T1, 56 msec of E1 differential

delay tolerance)or 4M x 16 SDRAM ( for 279 msec of T1, 226 msec of E1

differential delay tolerance) through a 16-bit SDRAM interface.

• Provides a 16-bit microprocessor bus interface for configuration and Link and

Unit Management.

• ATM receive interface supports 8- and 16-bit UTOPIA L2 or Any-PHY cell

interfaces at clock rates up to 52 MHz.

• Any-PHY receive slave appears as single device. The PHY-ID of each cell

is identified in the in-band address.

• UTOPIA L2 receive slave appears as a 31 port multi-PHY.

• UTOPIA L2 receive slave can also appear as a single port with the logical

port provided as a prepend or in the HEC/UDF field.

• ATM transmit interface supports 8- and 16-bit UTOPIA L2 and Any-PHY cell

interfaces at clock rates up to 52 MHz.

• Each link configured for cell delineation or each IMA group appears as a

PHY port on the Any-PHY and UTOPIA L2 bus.

• Any-PHY transmit slave appears as an 84-port multi-PHY. The PHY-ID of

each cell is identified in the in-band address.

• UTOPIA L2 transmit slave appears as a 31-port multi-PHY.

• Seamlessly interconnects to PMC-Sierra’s PM7326 S/UNI-APEX ATM/Packet

Traffic Manager and Switch and PM7324 S/UNI-ATLAS ATM layer devices.

Loopback and Diagnostic Features

• Supports UTOPIA L2 / Any-PHY Loopback (global loopback– where all cells

received on the UTOPIA L2 / Any-PHY interface are looped back out)

• Supports Line Side Loopback (global loopback– where all data received on

the line side is looped back out)

• Supports the capability to trace ICP cells for any group

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 29

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

Software

• The S/UNI-IMA device driver, written in ANSI C, provides a well-defined

Application Programming Interface (API) for use by application software. Low

level utility functions are also provided for diagnostics and debugging

purposes. Software wrappers are used for RTOS-related functions making the

S/UNI-IMA device driver portable to any Real Time Operating System (RTOS)

and hardware environment. The S/UNI-IMA device driver is compatible across

the S/UNI-IMA family of devices.

Packaging

• Implemented in low power, 0.18 micron, 1.8V CMOS technology with TTL

compatible inputs and outputs.

• Provides a standard 5-pin P1149 JTAG port.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 30

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

3 APPLICATIONS

The S/UNI-IMA-84 is ideal for the following applications:

• ATM Multiservice Switches - IMA/UNI and Any Service Any Port linecards

• Wireless Base Station Controllers

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 31

PRELIMINARY

INVERSE MULTIPLEXING OVER ATM

DATASHEET

PMC-2000223 ISSUE 4 INVERSE MULTIPLEXING OVER ATM

PM7341 S/UNI-IMA-84

4 REFERENCES

• AF-PHY-0086.001 “Inverse Multiplexing for ATM (IMA) Specification Version

1.1”, March 1999

• I.432-1 B-ISDN User Network Interface – Physical Layer specification:

General characteristics

• I.432-3 B-ISDN User Network Interface – Physical Layer specification: 1544

kbps and 2048 kbps operation

• G.804 “ATM Cell Mapping into Plesiochronous Digital Hierarchy (PDH)”

• AF-PHY-0016.000 “ATM Forum DS1 Physical Layer Specification”

• AF-PHY-0064.000 “ATM Forum E1 Physical Interface”

• ATM Forum, UTOPIA, an ATM-PHY Layer Specification, Level 2, V. 1.0,

Foster City, CA USA, June 1995.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 32

Loading...

Loading...