Released

Packet/ATM Traffic Manager and Switch

PM7329

S/UNI-APEX-1K800

FEATURES

• ATM (fixed length cell) and packet/

frame traffic manager and switch.

• 128 line ports, 4 WAN ports, and a

high speed microprocessor port. Any

port to any port switching for 1024

independent connections.

• Manages up to 256 Kbyte cell (16

Mbyte) data buffer and 4 Mbyte

context memory shared over all ports.

• Configurable progressive throttling of

buffer consumption, with me mo ry

reservation under high consumption.

Performs EFCI marking for ABR

support.

• Buffer congestion contr olled v ia Parti al

Packet Discard, Early Packet Discard

(PPD/EPD). Cell at a time discard also

supported.

• For frame/packet flows:

• Supports external wire speed HDLC

processor, SAR, and flow classifier

via packet-contiguous queuing and

scheduling.

• Error indication in AAL5 EOM t rail er

(set by SAR or classifier) can invoke

errored packet discard, thereby

eliminating need for packet buffers

in external devices .

• Traffic queuing algorithm is hig hly

configurable on a per connection, per

class, and per port basis.

• Configurable scheduling of 4 classes

of service on every port, with rate

shaping available for the 4 WAN ports.

Configurable traffic parameters

enabling a mix of CBR, VBR, GFR,

and UBR classes.

• Configurable OAM cell queuing and

special handling on all ports.

• VPI/VCI header mapping.

• Supports 700 Mb/s ingress traffic and

700 Mb/s egress traffic aggregated

across all ports.

• Low power 3.3/ 2.5 V CMOS.

• Standard 5-pin P1149 JTAG port.

• 352-ball SBGA, 35 mm x 35 mm.

BUS INTERFACES

• 8/16 bit, 52 MHz UTOPIA L2 bus.

• Line side:

• Enhanced UTOPIA Tx master

supports 128 ports. Rx master

supports 32 ports.

• Or single port slave.

• WAN side:

• Master (with optional cell length

expansion) supports 4 Tx or Rx

ports.

• Or single port slave.

MICROPROCESSOR INTERFACE

• 66 MHz, 32 bit address/data bus

capable of single or burst access to

internal registers and cell buffers.

• Supports cell/packet transfer to/from

any port, with CRC32 and CRC10

calculation supported in hardware.

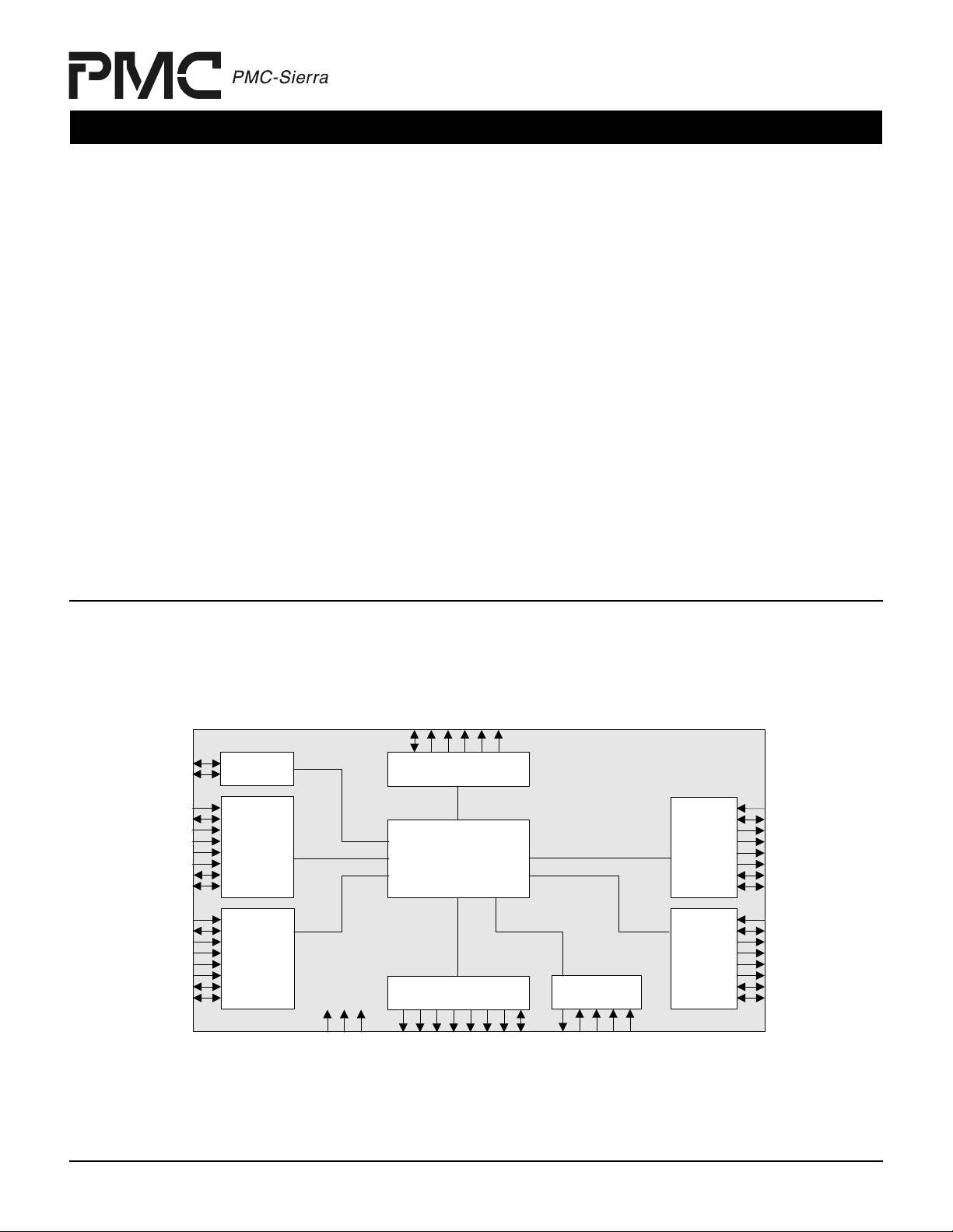

BLOCK DIAGRAM

Ctrl Lines

AD[31:0]

LRCLK

LRPA

LRSX

LRSOP

LRDAT[15:0]

LRPRTY

LRENB

LRADR[5:0]

WRCLK

WRPA

WRSX

WRSOP

WRDAT[15:0]

WRPRTY

WRENB

WRADR[2:0]

Processor

Interface

Loop Rx

Any-PHY

WAN Rx

Any-PHY

OE

CMD[33:0]

CMA[18:0]

CMP[1:0]

SSRAM Interface

Que Management &

Scheduling

SDRAM Interface

RSTB

CBCSB

SYSCLK

CBCASB

CBRASB

CMAB[18:17]

CMCEB

CMRWB

LTCLK

LTPA

LTSX

Loop Tx

Any-PHY

WAN Tx

Any-PHY

JTAG Test

Access Port

TDI

TCK

TMS

TDO

CBRWEB

CBA[11:0]

CBBS[1:0]

CBDQ[31:0]

CBDQM[1:0]

TRSTB

LTSOP

LTDAT[15:0]

LTPRTY

LTENB

LTADR[7:0]

WTCLK

WTPA

WTSX

WTSOP

WTDAT[15:0]

WTPRTY

WTENB

WTADR[2:0]

PMC-2010038 (r3) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2001

Released PM7329 S/UNI-APEX-1K800

Packet/ATM Traffic Manager and Switch

CONGESTION CONTROL

• Traffic discard thresholds configurable

per connection (independent CLP0

and CLP1 thresholds), per class, per

port, and per direction.

• Guaranteed Frame Rate (GFR)

implemented via CLP0 minim um buffer

size reservation per connection.

QUEUING & SCHEDULING

• 1024 traffic staging queues (one per

connection) individually assignable to

any CoS on any port.

• 512 + 20 scheduling queues: 4 CoS

queues per port, 128 line ports, 4 WAN

ports, and 1 processor port.

• Each port’s queuing and scheduling is

configurable as ce ll at a time or packe t

at a time.

• Connections are scheduled into each

class queue using configurable

weighted fair queuing (cell mode), or

FIFO (frame mode).

• Classes are schedul ed into port s using

strict priority with configurable

minimum bandwidth rese rvation.

• Ports are scheduled onto their

corresponding bus using a

configurable weighted interleaved

round robin algorithm.

• On the WAN ports: rate shaping,

individually configured per connection,

within four classes.

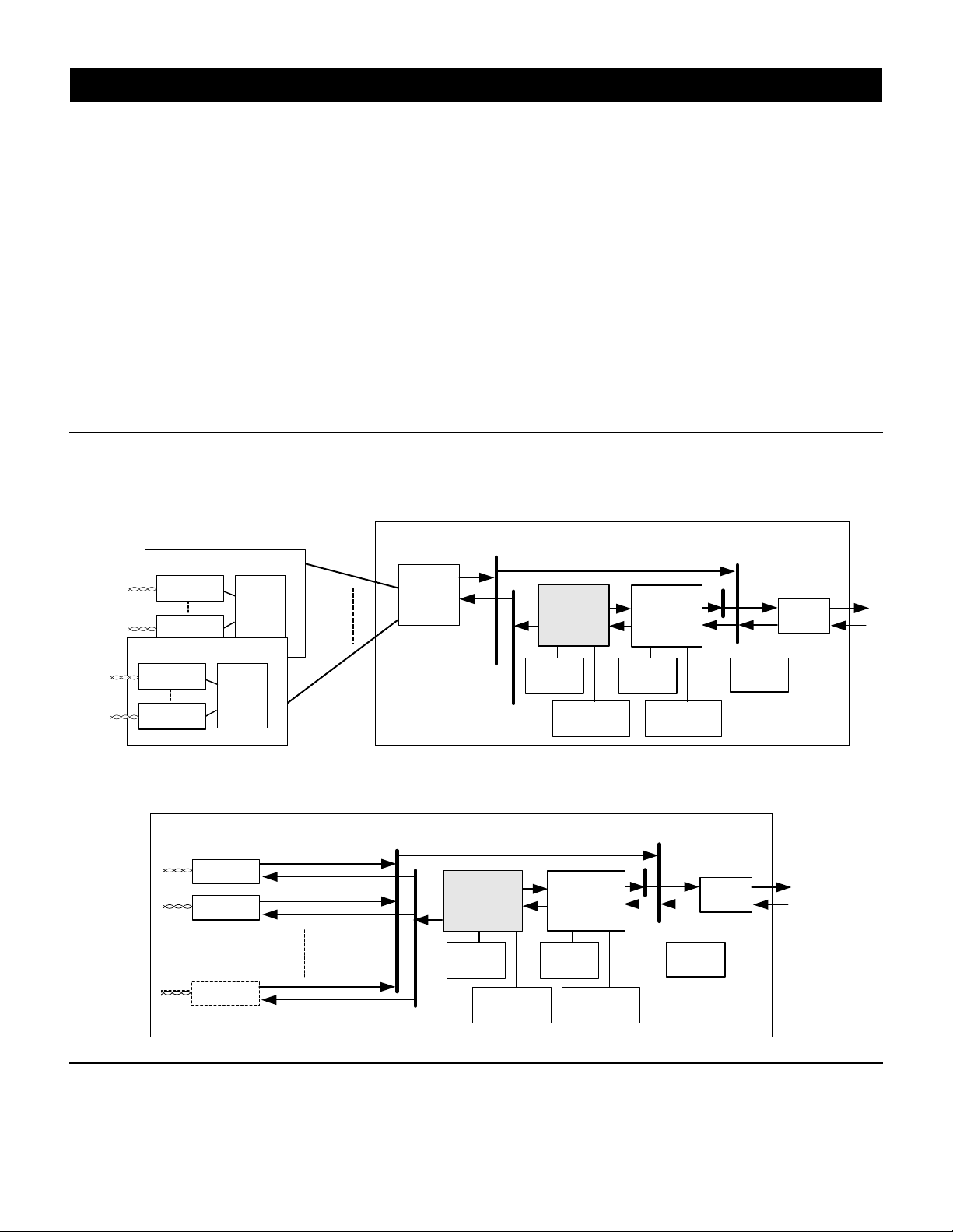

TYPICAL APPLICATION

S/UNI-APEX-1K800 IN OC3 MINI-DSLAM APPLICATION

line cards

up to 31

Utopia

L2 ports

up to 31

Utopia

L2 ports

DSL PHY

DSL PHY

DSL PHY

DSL PHY

PM7350

S/UNI-

DUPLEX

line cards

PM7350

S/UNI-

DUPLEX

200

Mbit/s

LVDS

s

k

n

i

l

r

S

e

D

p

V

s

L

e

8

c

i

v

o

t

e

d

p

U

X

E

L

P

U

D

PM7351

S/UNI-

VORTEX

X

-

I

E

N

T

U

R

/

O

S

V

o

-

I

t

N

U

/

S

Any-PHY/

SCI-PHY

PM7329

S/UNI-APEX-

1K800

Context

SSRAM

Packet/Cell

SDRAM

ACCOUNTING

• Per connection CLP0/CLP1 upstream/

downstream Tx counts.

• Error statistics accumulation.

• CLP0/CLP1 cell discard counts with

indication of connecti on ID of last cel l

discarded.

APPLICATIONS

• Mini Digital Subscriber Loop Access

Multiplexer (mini-DSLAM).

• Subscriber Access equipment.

• Digital Loop Card traffic aggregation.

PM7328

ATLAS-

Ingress

SSRAM

S/UNI1K800

SSRAM

Host CPU

Egress

PHY

Core Card

S/UNI-APEX-1K800 IN OC3 DIGITAL LOOP CARD APPLICATION

line interface

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

DSL PHY

DSL PHY

expansion

DSL PHY

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

Any-PHY/

SCI-PHY Bus

PM7329

S/UNI-APEX-

1K800

Context

SSRAM

Packet/Cell

SDRAM

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate informatio n,

send email to:

info@pmc-sierra.com

PM7328

S/UNI-ATLAS-

1K800

Ingress

SSRAM

Egress SSRAM

PHY

Host CPU

Digital Loop Card

PMC-2010038 (r3)

© Copyright PMC-Sierra, Inc. 2001. All

rights reserved. June 2001

S/UNI is a registered trademark of

PMC-Sierra, Inc.

Any-PHY and SCI-PHY are trademarks of

PMC-Sierra, Inc.

Loading...

Loading...