ATM Layer Solution

]

Release

PM7328

S/UNI-ATLAS-1K800

FEATURES

• Monolithic single chip device which

handles bi-directional ATM Layer

functions including VPI/VCI address

translation, cell appending, policing

(ingress only), cell counting and OAM

requirements for 1024 VCs (virtual

connections).

• Instantaneous bi-directional transfer

rate of 800 Mbit/s supports a bidirectional cell transfer rate of

1.42x10

6

cell/s.

• Ingress input in terface supports an 8 or

16 bit PHY interface using direct

addressing for up to 4 PHY devices

(Utopia Level 1) and Multi-PHY

addressing for up to 32 PHY devices

(Utopia Level 2).

• Ingress output interface supports an 8

or 16 bit SCI-PHY (52 - 64 byte cell)

interface (Utopia Level 1) to a switch

fabric.

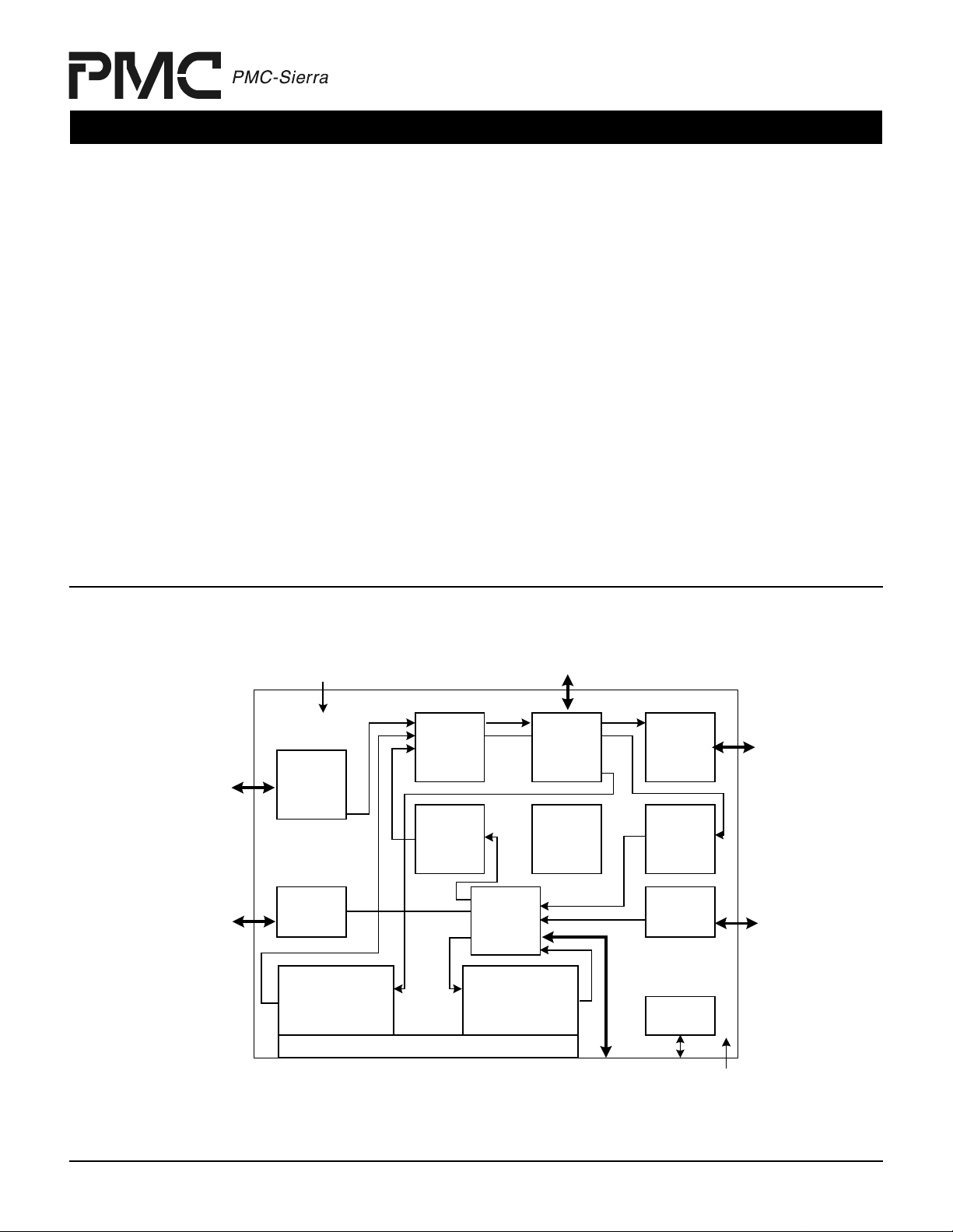

BLOCK DIAGRAM

• Egress input and output interfaces

support an 8 or 16 bit SCI-PHY (52 64 byte cell) interface using direct

addressing for up to 4 PHY devices

(Utopia Level 1) and Multi-PHY

addressing for up to 32 PHY devices

(Utopia Level 2).

• Compatible with the PM7329 S/UNIAPEX-1K800 Traffic Manager, and

PMC-Sierra’s VORTEX Architecture.

• Ingress functionality includes a highly

flexible search engine that covers the

entire PHYID/VPI/VCI address range,

dual leaky bucket policing, per-VC cel l

counts, OAM-FM and OAM-PM

processing.

• Egress functionality includes direct

address lookup, per-VC cell counts,

OAM-FM and OAM-PM processing.

Per-PHY output buffering scheme

resolves the head-of-line blocking

issue.

To External Synchronou s SRAM

• Includes a FIFO buffered 16-bit

microprocessor bus inte rface for ce ll

insertion and extraction, deterministic

VC Table access, status monitoring

and configuration of the device.

• Supports DMA access for cell

extraction.

• The UTOPIA and external SRAM

interfaces are 52 MHz max.

POLICING

• ITU-I.371, ATM Forum TM4.0

compliant, per-VC programmable dual

leaky bucket policing with a

programmable action (tag, discard, or

count only) for each bucket, each with

3 programmable 16 bit non-compliant

cell counts.

• Per-PHY single leaky bucket policing

with a programmable action (tag,

discard, or count only).

SCI-PHY Level 1/ Level 2

Interface (Mast er )

RDAT[15:0]

RPRTY

RDRENB[1]

RCA[1]

RADDR[4:3]/RCA[3:2]

RAVALID/RCA[4]

RADDR[2:0]/RRDENB[4:2]

RSOC

RFCLK

RPOLL

TDAT[15:0]

TPRTY

TWRENB[1]

TCA[1]

TADDR[4:3]/TCA[3:2]

TAVALID/TCA[4]

TADDR[2:0]/TDWRENB[4:2]

TSOC

TFCLK

TPOLL

SCI-PHY Level 1/ Level

2 Interface (Master)

ISYSCLK

Ingress

Input Cell

Interface

Egress

Output Cell

Ingress

Microprocessor Cell

Interface

Microprocessor Interface

Ingress

Search

Engine

Ingress

Backward

Cell

Interface

Micro processor Cell

ISD[63:0]

ISP[7:0]

ISA[19:16]

ISA[9:0]

ISWRB

Ingress

Cell

Processor

PHY

Statistics

Collection

Egress

Cell

Processor

Egress

Interface

ESP[3:0]

ESD[31:0]

To External Synchronous SRAM

ISOEB

ISADSB

ESA[9:0]

ESA[19:16]

ESADSB

ESRWB

Ingress

Output Cell

Interface

Egress

Backward

Cell

Interface

Egress

Input Cell

Interface

JTAG

Interface

ESOEB

SCI-PHY Level 1

Interface (Slave)

ODAT[15:0]

OPRTY

OSOC

OFCLK

OCA

ORDENB

OTSEN

IDAT[15:0]

IPRTY

IFCLK

ISOC

ICA[1]

IWRENB[1]

IAVALID/ICA[4]

IADDR[4:3]/ICA[3:2]

IADDR[2:0]/IWRENB[4:2

IPOLL

SCI-PHY Level 1/ Level

2 Interface (Slave)

ESYSCLK

PMC-2010037 (r2) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2001

ATM Layer Solution

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

Release PM7328 S/UNI-ATLAS-1K800

• Guaranteed Frame Rate (GFR)

Policing with Minimum Cell Rate

Frame Tagging.

OAM

• ITU-I.610 compliant OAM on both

Ingress and Egress directions.

• Complete Fault Management (AIS,

RDI, CC) processing, for VP/VC,

Segment/End-to-end flows on all VCs.

• Complete Performance Monitoring

processing, for VP/VC, Segment/Endto-end, Forward/Backward flows, on

256 Bi-directional VCs.

CELL COUNTING

• Per-VC counts include CLP0 cells,

CLP1 cells, policing violations.

• Per-PHY counts include CLP0 cells,

CLP1 cells, OAM cells, errored OAM

cells, unassigned/invalid cells and

policing violations.

• Per-device counts include total cells

received/transmitted, and physical

layer cells.

PACKAGING

• Provides a standard 5 signal P1149.1

JTAG test port for boundary scan

board test purposes.

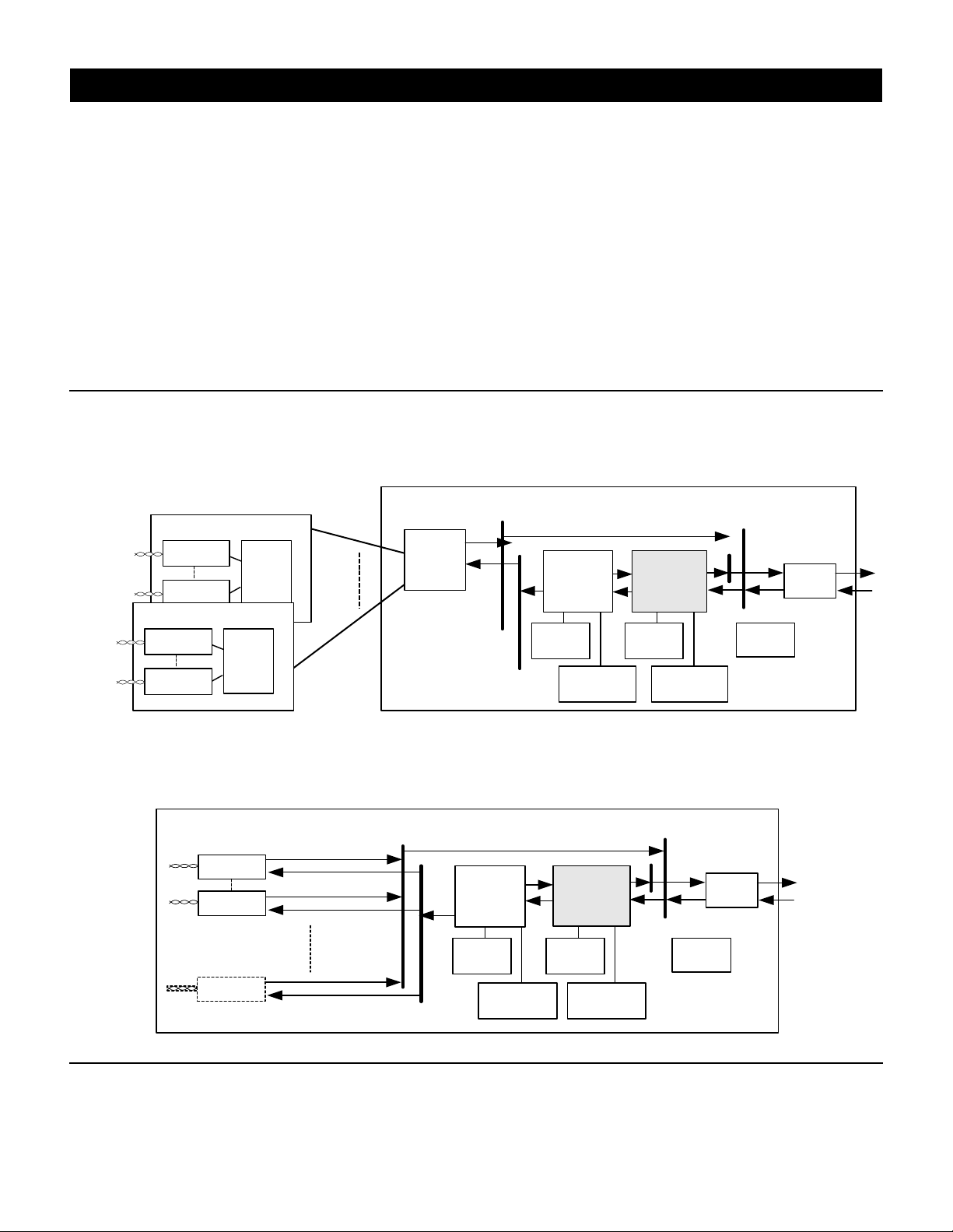

TYPICAL APPLICATION

S/UNI-ATLAS-1K800 IN OC3 MINI-DSLAM APPLICATION

line cards

up to 31

Utopia

L2 ports

up to 31

Utopia

L2 ports

DSL PHY

DSL PHY

DSL PHY

DSL PHY

PM7350

S/UNI-

DUPLEX

line cards

PM7350

S/UNI-

DUPLEX

200

Mbit/s

LVDS

s

k

n

i

l

r

S

e

D

p

V

s

L

e

8

c

i

v

o

t

e

d

p

U

X

E

L

P

U

D

PM7351

S/UNI-

VORTEX

X

-

I

E

N

T

U

R

/

O

S

V

o

-

I

t

N

U

/

S

Any-PHY/

SCI-PHY

PM7329

S/UNI-APEX-

1K800

Context

SSRAM

Packet/Cell

SDRAM

• Low power 0.35 micron, 3.3V CMOS

technology with a 3.3V UTOPIA (SCIPHY), 3.3/5V Microprocessor I/O

interfaces and 3.3V external

synchronous SRAM interfaces.

• Packaged in 432-pin ball grid array

(BGA) package.

APPLICATIONS

• Mini Digital Subscriber Loop Access

Multiplexer (Mini-DSLAM).

• Subscriber Access Equipment.

• Digital Loop Card Traffic Aggregation.

PM7328

S/UNI-ATLAS-

1K800

Ingress

SSRAM

Egress

SSRAM

Host CPU

PHY

Core Card

S/UNI-ATLAS-1K800 IN OC3 DIGITAL LOOP CARD APPLICATION

line interface

DSL PHY

DSL PHY

expansion

DSL PHY

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

Fax: 604.415.6200

Any-PHY/

SCI-PHY Bus

PM7329

S/UNI-APEX-

1K800

Context

SSRAM

Packet/Cell

SDRAM

PM7328

S/UNI-ATLAS-

1K800

Ingress

SSRAM

Egress SSRAM

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate informatio n,

send email to:

info@pmc-sierra.com

PHY

Host CPU

Digital Loop Card

PMC-2010037 (r2)

© Copyright PMC-Sierra, Inc. 2001. All

rights reserved. August 2001

S/UNI is a registered trademark of

PMC-Sierra, Inc.

Any-PHY and SCI-PHY are trademarks of

PMC-Sierra, Inc.

Loading...

Loading...