PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

PM7326

TM

S/UNI

-

APEX

S/UNI APEX

ATM/PACKET TRAFFIC MANAGER AND SWITCH

DATA SHEET

ISSUE 6: APRIL 2000

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

REVISION HISTORY

Issue No. Issue Date Details of Change

Issue 6 April, 2000 Final update for production release.

Changes from Issue 5 marked with

change bars

Issue 5 December, 1999 Removed Applications Examples and

Operations sections, replaced with

dedicated documents. IDDOP

(operating current) value inserted.

Issue 4 August, 1999 Datasheet re-written to incorporate

extensive updates and clarifications.

Issue 3 June, 1999 No material change from Issue 2,

formatted for web site.

Issue 2 February, 1999 Updates and clarifications throughout

Issue 1 November, 1998 Document created.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

CONTENTS

1 DEFINITIONS .......................................................................................... 1

2 FEATURES .............................................................................................. 3

3 APPLICATIONS ....................................................................................... 7

4 REFERENCES......................................................................................... 8

5 APPLICATION EXAMPLES ..................................................................... 9

6 BLOCK DIAGRAM ................................................................................. 10

7 DESCRIPTION ...................................................................................... 12

8 PIN DIAGRAM ....................................................................................... 16

9 PIN DESCRIPTION................................................................................ 17

9.1 LOOP ANY-PHY RECEIVE MASTER/TRANSMIT SLAVE

INTERFACE (28 SIGNALS) ........................................................ 17

9.2 LOOP ANY-PHY TRANSMIT MASTER/RECEIVE SLAVE

INTERFACE (34 SIGNALS) ........................................................ 22

9.3 WAN ANY-PHY RECEIVE MASTER/TRANSMIT SLAVE

INTERFACE (25 SIGNALS) ........................................................ 26

9.4 WAN ANY-PHY TRANSMIT MASTER/RECEIVE SLAVE

INTERFACE (25 SIGNALS) ........................................................ 31

9.5 CONTEXT MEMORY SYNCHRONOUS SSRAM INTERFACE (60

SIGNALS).................................................................................... 36

9.6 CELL BUFFER SDRAM INTERFACE (52 SIGNALS) ................. 38

9.7 MICROPROCESSOR INTERFACE (44 SIGNALS)..................... 40

9.8 GENERAL (9 SIGNALS) ............................................................. 44

9.9 JTAG & SCAN INTERFACE (7 SIGNALS) .................................. 45

9.10 POWER....................................................................................... 46

10 FUNCTIONAL DESCRIPTION............................................................... 48

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE i

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

10.1 ANY-PHY INTERFACES ............................................................. 48

10.1.1 RECEIVE INTERFACE..................................................... 48

10.1.2 TRANSMIT INTERFACE .................................................. 50

10.2 LOOP PORT SCHEDULER ........................................................ 53

10.3 WAN PORT SCHEDULER.......................................................... 54

10.4 WAN PORT ALIASING................................................................ 56

10.5 WAN AND LOOP ICI SELECTION.............................................. 57

10.6 MICROPROCESSOR INTERFACE ............................................ 57

10.7 MEMORY PORT ......................................................................... 61

10.8 SAR ASSIST ............................................................................... 62

10.8.1 TRANSMIT ....................................................................... 62

10.8.2 RECEIVE.......................................................................... 63

10.9 QUEUE ENGINE......................................................................... 64

10.9.1 SERVICE ARBITRATION ................................................. 65

10.9.2 CELL QUEUING............................................................... 66

10.9.3 CLASS SCHEDULING ..................................................... 73

10.9.4 CONGESTION CONTROL ............................................... 75

10.9.5 STATISTICS ..................................................................... 82

10.9.6 MICROPROCESSOR QUEUE BUFFER RE-

ALLOCATION/TEAR DOWN ............................................ 84

10.10 CONTEXT MEMORY SSRAM INTERFACE ............................... 84

10.11 CELL BUFFER SDRAM INTERFACE ......................................... 89

10.12 JTAG TEST ACCESS PORT....................................................... 93

11 PERFORMANCE ................................................................................... 94

11.1 THROUGHPUT ........................................................................... 94

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ii

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

11.2 LATENCY.................................................................................... 96

11.3 CDV............................................................................................. 96

12 REGISTER............................................................................................. 97

12.1 GENERAL CONFIGURATION AND STATUS.............................. 98

12.2 LOOP CELL INTERFACE ......................................................... 107

12.3 WAN CELL INTERFACE............................................................113

12.4 MEMORY PORT ........................................................................119

12.5 SAR........................................................................................... 125

12.5.1 RECEIVE........................................................................ 125

12.5.2 TRANSMIT ..................................................................... 127

12.5.3 CELL BUFFER DIAGNOSTIC ACCESS......................... 128

12.6 QUEUE ENGINE....................................................................... 129

12.7 MEMORY INTERFACE ............................................................. 144

12.8 TEST INTERFACE .................................................................... 145

12.9 CBI INTERFACE ....................................................................... 149

13 CBI REGISTER PORT MAPPING ....................................................... 151

14 MEMORY PORT MAPPING................................................................. 157

14.1 CONTEXT SIZE AND LOCATION............................................. 157

14.2 QUEUE CONTEXT DEFINITION .............................................. 160

14.2.1 VC CONTEXT RECORDS.............................................. 161

14.2.2 PORT CONTEXT RECORDS......................................... 169

14.2.3 CLASS CONTEXT RECORDS....................................... 173

14.2.4 SHAPING CONTEXT RECORDS................................... 178

14.2.5 CELL CONTEXT RECORD ............................................ 180

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iii

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

14.2.6 MISC CONTEXT ............................................................ 180

14.3 WAN PORT SCHEDULER CONTEXT...................................... 184

14.3.1 WAN TRANSMIT PORT POLLING WEIGHT RECORD. 184

14.3.2 WAN TRANSMIT CLASS STATUS RECORD ................ 185

14.4 LOOP PORT SCHEDULER CONTEXT .................................... 186

14.4.1 LOOP TRANSMIT PORT POLLING SEQUENCE RECORD

........................................................................................ 186

14.4.2 LOOP TRANSMIT PORT POLLING WEIGHT RECORD 187

14.4.3 LOOP TRANSMIT CLASS STATUS RECORD .............. 188

15 TEST FEATURES DESCRIPTION ...................................................... 190

15.1 JTAG TEST PORT .................................................................... 190

16 OPERATION ........................................................................................ 194

17 FUNCTIONAL TIMING......................................................................... 195

17.1 MICROPROCESSOR INTERFACE .......................................... 195

17.2 SDRAM INTERFACE ................................................................ 197

17.3 ZBT SSRAM INTERFACE......................................................... 199

17.4 LATE WRITE SSRAM INTERFACE.......................................... 200

17.5 ANY-PHY/UTOPIA INTERFACES ............................................. 201

17.5.1 RECEIVE MASTER/TRANSMIT SLAVE INTERFACES . 201

17.5.2 TRANSMIT MASTER/RECEIVE SLAVE INTERFACES . 204

18 ABSOLUTE MAXIMUM RATINGS ....................................................... 209

19 D.C. CHARACTERISTICS ................................................................... 210

20 A.C. TIMING CHARACTERISTICS...................................................... 212

20.1 JTAG INTERFACE .................................................................... 217

21 ORDERING AND THERMAL INFORMATION...................................... 219

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iv

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

22 MECHANICAL INFORMATION............................................................ 220

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE v

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

LIST OF REGISTERS

REGISTER 0X00: RESET AND IDENTITY ...................................................... 98

REGISTER 0X10: HI PRIORITY INTERRUPT STATUS REGISTER ............... 99

REGISTER 0X14: HIGH PRIORITY INTERRUPT MASK............................... 101

REGISTER 0X18: LOW PRIORITY INTERRUPT ERROR REGISTER ......... 102

REGISTER 0X1C: LOW PRIORITY INTERRUPT ERROR MASK................. 104

REGISTER 0X20: LOW PRIORITY INTERRUPT STATUS REGISTER ........ 105

REGISTER 0X24: LOW PRIORITY INTERRUPT STATUS MASK................. 106

REGISTER 0X100: LOOP CELL RX INTERFACE CONFIGURATION........... 107

REGISTER 0X104: LOOP CELL TX INTERFACE CONFIGURATION ............110

REGISTER 0X200: WAN CELL RX INTERFACE CONFIGURATION .............113

REGISTER 0X204: WAN CELL TX INTERFACE CONFIGURATION .............116

REGISTER 0X300: MEMORY PORT CONTROL............................................119

REGISTER 0X340-0X34C: MEMORY WRITE DATA (BURSTABLE)............. 121

REGISTER 0X350: MEMORY WRITE DATA OVERFLOW (BURSTABLE) ... 122

REGISTER 0X380-0X38C: MEMORY READ DATA (BURSTABLE)............... 123

REGISTER 0X390: MEMORY READ DATA OVERFLOW (BURSTABLE) ..... 124

REGISTER 0X400-0X43C: SAR RECEIVE DATA (BURSTABLE).................. 125

REGISTER 0X500-0X53C: SAR TRANSMIT DATA, CLASS 0 (BURSTABLE)127

REGISTER 0X540-0X57C: SAR TRANSMIT DATA, CLASS 1 (BURSTABLE)127

REGISTER 0X580-0X5BC: SAR TRANSMIT DATA, CLASS 2 (BURSTABLE)127

REGISTER 0X5C0-0X5FC: SAR TRANSMIT DATA, CLASS 3 (BURSTABLE)127

REGISTER 0X600: CELL BUFFER DIAGNOSTIC CONTROL ...................... 128

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vi

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

REGISTER 0X700: QUEUE CONTEXT CONFIGURATION .......................... 129

REGISTER 0X704: RECEIVE AND TRANSMIT CONTROL .......................... 132

REGISTER 0X710: MAX DIRECTION CONGESTION THRESHOLDS ......... 134

REGISTER 0X714: CLP0 DIRECTION CONGESTION THRESHOLDS........ 135

REGISTER 0X718: CLP1 DIRECTION CONGESTION THRESHOLDS........ 136

REGISTER 0X71C: RE-ASSEMBLY MAXIMUM LENGTH............................. 137

REGISTER 0X720: WATCH DOG ICI PATROL RANGE................................ 138

REGISTER 0X724: TEAR DOWN QUEUE ID................................................ 139

REGISTER 0X728: WATCH DOG / TEAR DOWN STATUS .......................... 140

REGISTER 0X730: SHAPER 0 CONFIGURATION (N = 0)............................ 141

REGISTER 0X734: SHAPER 1 CONFIGURATION (N = 1)............................ 141

REGISTER 0X738: SHAPER 2 CONFIGURATION (N = 2)............................ 141

REGISTER 0X73C: SHAPER 3 CONFIGURATION (N = 3)........................... 141

REGISTER 0X800: SDRAM/SSRAM CONFIGURATION............................... 144

REGISTER 0X900: BIST_OK......................................................................... 145

REGISTER 0X904: BIST_MODE ................................................................... 146

REGISTER 0X908: BIST_RESULTS A........................................................... 147

REGISTER 0X90C: BIST_RESULTS B.......................................................... 148

REGISTER 0XA00: CBI REGISTER PORT ................................................... 149

CBI REGISTER 0X00: CONFIGURATION ..................................................... 151

CBI REGISTER 0X01: VERNIER CONTROL................................................. 153

CBI REGISTER 0X02: DELAY TAP STATUS ................................................. 154

CBI REGISTER 0X03: CONTROL STATUS................................................... 155

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vii

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

LIST OF FIGURES

FIGURE 1 - S/UNI APEX BLOCK WITH DATAPATH .......................................11

FIGURE 2 - S/UNI APEX BOTTOM VIEW PIN OUT....................................... 16

FIGURE 3 - 16BIT RECEIVE CELL TRANSFER FORMAT............................. 48

FIGURE 4 - 8-BIT RECEIVE CELL TRANSFER FORMAT ............................. 49

FIGURE 5 - 16-BIT TRANSMIT CELL TRANSFER FORMAT......................... 51

FIGURE 6 - 8-BIT TRANSMIT CELL TRANSFER FORMAT........................... 52

FIGURE 7 - I960 (80960CF) INTERFACE....................................................... 60

FIGURE 8 - POWERPC (MPC860) INTERFACE............................................ 60

FIGURE 9 - SAR ASSIST TRANSMIT CELL TRANSFER FORMAT............... 63

FIGURE 10- SAR ASSIST RECEIVE CELL TRANSFER FORMAT ................. 64

FIGURE 11 - SERVICE ARBITRATION HIERARCHY ...................................... 66

FIGURE 12- QUEUE LINKED LIST STRUCTURE .......................................... 67

FIGURE 13- TRAFFIC SHAPING ON THE WAN PORT.................................. 71

FIGURE 14- NON-INTEGER SHPINCR........................................................... 72

FIGURE 15- THRESHOLDS AND COUNT DEFINITIONS............................... 76

FIGURE 16- EPD/PPD CONGESTION DISCARD RULES .............................. 79

FIGURE 17 CELL CONGESTION DISCARD RULES ...................................... 80

FIGURE 18 FCQ DISCARD RULES ................................................................ 81

FIGURE 19- 1 BANK CONFIGURATION FOR 1MB OF ZBT SSRAM............. 85

FIGURE 20- 1 BANK CONFIGURATION FOR 1MB OF LATE WRITE SSRAM86

FIGURE 21- 2 BANK CONFIGURATION FOR 2MB OF ZBT SSRAM............. 87

FIGURE 22- 2 BANK CONFIGURATION FOR 2MB OF LATE WRITE SSRAM88

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE viii

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

FIGURE 23- 4 BANK CONFIGURATION FOR 4MB OF ZBT SSRAM............. 89

FIGURE 24- CELL STORAGE MAP................................................................. 90

FIGURE 25- 4 MB – 64K CELLS...................................................................... 91

FIGURE 26- 8 MB – 128K CELLS.................................................................... 91

FIGURE 27- 16 MB – 256K CELLS.................................................................. 92

FIGURE 28- CONTEXT LOCATION............................................................... 157

FIGURE 29- INPUT OBSERVATION CELL (IN_CELL) .................................. 191

FIGURE 30- OUTPUT CELL (OUT_CELL) .................................................... 192

FIGURE 31- BI-DIRECTIONAL CELL (IO_CELL) .......................................... 192

FIGURE 32- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS193

FIGURE 33- SINGLE WORD READ AND WRITE ......................................... 195

FIGURE 34- BURST READ AND WRITE....................................................... 196

FIGURE 35- CONSECUTIVE WRITE ACCESSES USING WRDONEB........ 197

FIGURE 36- READ TIMING ........................................................................... 198

FIGURE 37- WRITE TIMING.......................................................................... 198

FIGURE 38- REFRESH.................................................................................. 199

FIGURE 39- POWER UP AND INITIALIZATION SEQUENCE....................... 199

FIGURE 40- READ FOLLOWED BY WRITE TIMING.................................... 200

FIGURE 41- READ FOLLOWED BY WRITE TIMING.................................... 201

FIGURE 42- UTOPIA L2 TRANSMIT SLAVE (LOOP & WAN) ....................... 202

FIGURE 43- UTOPIA L1 RECEIVE MASTER (LOOP & WAN) ...................... 202

FIGURE 44- UTOPIA L2 RECEIVE MASTER (LOOP & WAN) ...................... 203

FIGURE 45- ANY-PHY RECEIVE MASTER (LOOP & WAN)......................... 204

FIGURE 46- UTOPIA L2 RECEIVE SLAVE (LOOP & WAN).......................... 205

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ix

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

FIGURE 47- WAN UTOPIA L1 TRANSMIT MASTER .................................... 205

FIGURE 48- LOOP UTOPIA L1 TRANSMIT MASTER................................... 206

FIGURE 49- WAN UTOPIA L2 TRANSMIT MASTER .................................... 206

FIGURE 50- LOOP UTOPIA L2 TRANSMIT MASTER................................... 207

FIGURE 51- WAN ANY-PHY TRANSMIT MASTER....................................... 207

FIGURE 52- LOOP ANY-PHY TRANSMIT MASTER ..................................... 208

FIGURE 53- RSTB TIMING............................................................................ 212

FIGURE 54- SYNCHRONOUS I/O TIMING ................................................... 213

FIGURE 55- JTAG PORT INTERFACE TIMING ............................................ 217

FIGURE 56- MECHANICAL DRAWING 352 PIN BALL GRID ARRAY (SBGA)220

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE x

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

LIST OF TABLES

TABLE 1 - TERMINOLOGY ............................................................................ 1

TABLE 2 - SAMPLE FEATURE SET AS A FUNCTION OF MEMORY

CAPACITY ..................................................................................... 15

TABLE 3 - PIN TYPE DEFINITION ............................................................... 17

TABLE 4 - NUMBER OF PORTS SUPPORTED, RECEIVE INTERFACE.... 50

TABLE 5 - NUMBER OF PORTS SUPPORTED, TRANSMIT INTERFACE.. 53

TABLE 6 - EXAMPLE WIRR TRANSMISSION SEQUENCE........................ 56

TABLE 7 - AVAILABLE QUEUING PROCEDURES ...................................... 68

TABLE 8 - OAM & RRM CELL IDENTIFICATION ......................................... 73

TABLE 9 - CONGESTION ERROR FLAGS .................................................. 77

TABLE 10 - CONGESTION DISCARD RULES SELECTION ......................... 78

TABLE 11 - STATISTICAL COUNTS .............................................................. 82

TABLE 12 - IN/OUT BOUND CLP STATE FOR STATISTICAL COUNTS ....... 83

TABLE 13 - CONGESTION RULE & COUNT SUMMARY.............................. 83

TABLE 14 - RECEIVE INTERFACE THROUGHPUT, MCELLS/SEC ............. 94

TABLE 15 - QUEUE ENGINE THROUGHPUT, MCELLS/SEC....................... 95

TABLE 16 - TRANSMIT INTERFACE THROUGHPUT, MCELLS/SEC ........... 95

TABLE 17 - EXTERNAL QUEUE CONTEXT MEMORY MAP....................... 158

TABLE 18 - INTERNAL QUEUE CONTEXT MEMORY MAP........................ 158

TABLE 19 - INTERNAL WAN PORT SCHEDULER CONTEXT MEMORY MAP

..................................................................................................... 159

TABLE 20 - INTERNAL LOOP PORT SCHEDULER CONTEXT MEMORY MAP

..................................................................................................... 159

TABLE 21 - 2 BIT LOGARITHMIC, 2 BIT FRACTIONAL .............................. 160

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xi

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

TABLE 22 - 4 BIT LOGARITHMIC, 2 BIT FRACTIONAL .............................. 160

TABLE 23 - 4 BIT LOGARITHMIC, 4 BIT FRACTIONAL .............................. 160

TABLE 24 - VC CONTEXT RECORD STRUCTURE .................................... 161

TABLE 25 - VC STATISTICS RECORD STRUCTURE ................................. 168

TABLE 26 - VC ADDRESS MAP RECORD STRUCTURE ........................... 168

TABLE 27 - PORT THRESHOLD CONTEXT RECORD STRUCTURE ........ 170

TABLE 28 - PORT COUNT CONTEXT RECORD STRUCTURE.................. 171

TABLE 29 - CLASS SCHEDULER RECORD STRUCTURE ........................ 173

TABLE 30 - CLASS CONTEXT RECORD STRUCTURE ............................. 176

TABLE 31 - SHAPE TXSLOT CONTEXT RECORD STRUCTURE .............. 178

TABLE 32 - SHAPE RATE CONTEXT RECORD STRUCTURE................... 179

TABLE 33 - CELL CONTEXT RECORD STRUCTURE ................................ 180

TABLE 34 - FREE COUNT CONTEXT STRUCTURE .................................. 181

TABLE 35 - OVERALL COUNT CONTEXT STRUCTURE............................ 181

TABLE 36 - CONGESTION DISCARD CONTEXT STRUCTURE ................ 182

TABLE 37 - MAXIMUM CONGESTION ID CONTEXT STRUCTURE........... 183

TABLE 38 - MISC ERROR CONTEXT STRUCTURE................................... 183

TABLE 39 - WAN TRANSMIT PORT POLLING WEIGHT ............................ 184

TABLE 40 - WAN POLL WEIGHT FORMAT ................................................. 185

TABLE 41 - WAN CLASS STATUS............................................................... 185

TABLE 42 - LOOP TRANSMIT PORT POLLING SEQUENCE ..................... 186

TABLE 43 - LOOP TRANSMIT PORT POLLING WEIGHT........................... 187

TABLE 44 - LOOP CLASS STATUS ............................................................. 188

TABLE 45 - INSTRUCTION REGISTER ....................................................... 190

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xii

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

TABLE 46 - IDENTIFICATION REGISTER ................................................... 190

TABLE 47 - BOUNDARY SCAN REGISTER ................................................ 190

TABLE 48 - ABSOLUTE MAXIMUM RATINGS ............................................. 209

TABLE 49 - D.C. CHARACTERISTICS......................................................... 210

TABLE 50 - RTSB TIMING............................................................................ 212

TABLE 51 - SYSCLK TIMING ....................................................................... 213

TABLE 52 - CELL BUFFER SDRAM INTERFACE........................................ 213

TABLE 53 - CONTEXT MEMORY ZBT & LATE WRITE SSRAM INTERFACE

..................................................................................................... 213

TABLE 54 - MICROPROCESSOR INTERFACE ........................................... 214

TABLE 55 - LOOP ANY-PHY TRANSMIT INTERFACE ................................ 214

TABLE 56 - WAN ANY-PHY TRANSMIT INTERFACE.................................. 215

TABLE 57 - LOOP ANY-PHY RECEIVE INTERFACE................................... 215

TABLE 58 - WAN ANY-PHY RECEIVE INTERFACE .................................... 216

TABLE 59 - JTAG PORT INTERFACE.......................................................... 217

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xiii

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

This page left blank intentionally.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xiv

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

1 DEFINITIONS

Table 1 - Terminology

Term Definition

AAL5 ATM Adaptation Layer

ABR Available Bit Rate

Any-PHY Interoperable version of UTOPIA and SCI-PHY, with

inband addressing.

ATLAS PMC’s OAM and Address Resolution device

ATM Asynchronous Transfer Mode

BOM Beginning of Message

CBI Common Bus Interface

CBR Constant Bit Rate

CDV Cell Delay Variation

CDVT Cell Delay Variation Tolerance

CES Circuit Emulation Service

CLP Cell Loss Priority

COM Continuation of Message

COS Class of Service

CTD Cell Transfer Delay

DLL Delay Locked Loop

DSL Digital Subscriber Loop

DSLAM DSL access Multiplexer

DUPLEX PMC UTOPIA deserializer

ECI Egress Connection Identifier

EFCI Early forward congestion indicator

EOM End of Message

EPD Early Packet Discard

FIFO First-In-First-Out

GCRA Generic Cell Rate Algorithm

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 1

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

GFR Guaranteed Frame Rate

IBT Intrinsic Burst Tolerance

ICI Ingress Connection Identifier

MBS Maximum Burst Size

MCR Minimum Cell Rate

OAM Operation, Administration and Maintenance

PCR Peak Cell Rate

PDU Packet Data Unit

PHY Physical Layer Device

PPD Partial Packet Discard

PTI Payload Type Indicator

QOS Quality of Service

QRT PMC’s traffic management device

QSE PMC’s switch fabric device

RRM Reserved or Resource Management

SAR Segmentation and Re-assembly

SCI-PHY PMC-Sierra enhanced UTOPIA bus

SCR Sustained Cell Rate

UBR Unspecified Bit Rate

UTOPIA Universal Test & Operations PHY Interface for ATM

VBR Variable Bit Rate

VCC Virtual Channel Connection

VORTEX PMC UTOPIA/Any-PHY slave serializer

VPC Virtual Path Connection

WAN Wide Area Network

WIRR Weighted Interleaved Round Robin

WRR Weighted Round Robin

ZBT Zero Bus Turnaround

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 2

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

2 FEATURES

• Monolithic single chip ATM traffic manager providing VC queuing/shaping and

VC, Class Of Service(COS), and Port scheduling, congestion management,

and switching across 2048 ports.

• Targeted at systems where many low speed ATM data ports are multiplexed

onto few high speed ports.

• 869 Kcells/s non shaped throughput in full duplex.

• 1.73 Mcells/s non shaped throughput in half duplex.

• 1.42 Mcells/s shaped throughput (aggregate of the four shapers)

• Supports four WAN uplink ports, with port aliasing

• Supports 2048 loop ports. Loop port can support an uncongested rate up to

230Kcells/sec.

• Provides 4 Classes of Service per port with configurable traffic parameters

enabling support for a mix of CBR, VBR, GFR, and UBR classes.

• Provides 64k per-VC queues individually assignable to any COS in any port.

• Provides support of up to 256k cells of shared buffer

• Provides 2 independent cell emission schedulers, 1 for the WAN ports, and 1

for the Loop ports. The schedulers have the following features: Three level

hierarchical cell emission scheduling at the port, class, and VC levels.

• WAN Port Scheduling

• Weighted Interleaved Round Robin WAN port scheduling.

• Per port Priority Fair Queued class scheduling with port

independence.

• Per Class

• Weighted Fair Queued VC scheduling with class independence

or

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 3

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

• Shaped Fair Queued VC scheduling applying rate based per VC

shaping or

• Frame Continuous Queued VC scheduling for VC Merge and

packet re-assembly.

• Loop Port Scheduling

• Weighted Interleaved Round Robin Loop port scheduling.

• Per port Priority Fair Queued class scheduling with port

independence.

• Per Class

• Weighted Fair Queued VC scheduling with class independence

or

• Frame Continuous Queued scheduling for VC Merge and

packet re-assembly

• Congestion Control applied per-VC, per-class, per-port and per-direction.

• Flexible, progressive hierarchical throttling of buffer consumption.

Provides sharing of resources during low congestion, memory reservation

during high congestion.

• Applies EPD and PPD on a per-VC, per-class, per-port, and per-direction

basis with CLP differentiation, following emerging GFR standards.

• Provides EFCI marking on a per VC basis.

• Provides interrupts and indication of most recent VC/Class/Port that

exceeded maximum thresholds.

• Provides flexible VPC or VCC switching selectable on a per VC basis as

follows

• Any WAN port to any WAN port

• Any WAN port to any Loop port

• Any Loop port to any WAN port.

• Any Loop port to any Loop port.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 4

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

• Microprocessor port to any loop or WAN port.

• Any loop or WAN port to microprocessor port

• VP Termination (in conjunction with ATLAS)

• VPI or VPI/VCI header mapping

• VC merge

• Provides flexible signaling and control capabilities

• Provides 4 independent uP transmit queues

• Provides simultaneous AAL5 SAR assistance for traffic to/from the uP on

up to 64k VCs.

• Supports uP cell injection into any queue.

• Provides per VC selectable OAM cell pass through or switching to

microprocessor port.

• Supports CRC10 calculation for OAM cells destined for/originating from

the microprocessor.

• Diagnostic access provided to context memory and cell buffer memory via

the microprocessor.

• Provides per VC CLP0/1 transmit counts.

• Provide global per CLP0/1 discard counts

• Provides various error statistics accumulation.

• Determines the ingress connection identifier from one of several locations:

the cell prepend, the VPI/VCI field, or the HEC/UDF field.

• Interface support

• Provides a 8/16-bit Any-PHY compliant master/slave Loop side interface

supporting up to 2048 ports (logical PHYs).

• Provides an 8/16-bit Any-PHY compliant master/slave WAN side interface

supporting up to 4 ports (PHYs).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 5

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

• Provides a 32-bit multiplexed microprocessor bus interface for signaling,

control, and cell message extraction and insertion, context memory

access, control and status monitoring, and configuration of the IC.

• Provides a 32-bit SDRAM interface for cell buffering.

• Provides a 36-bit pipelined ZBT or register to register late write SSRAM

interface for context storage.

• Packaging

• Provides a standard 5 signal P1149.1 JTAG test port for boundary scan

board test purposes.

• Implemented in low power, 0.25 micron, +2.5/3.3V CMOS technology with

CMOS compatible inputs and outputs.

• 352-pin high-performance ball grid array (SBGA) package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 6

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

3 APPLICATIONS

• DSL Access Multiplexers

• ATM Switches

• Multiservice Access Multiplexers

• 3rd generation wireless base stations and base station controllers

• OC-12 ingress congestion and traffic management

• OC-12 egress traffic manager and shaper

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 7

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

4 REFERENCES

1. PMC-Sierra; “Saturn Compatible Interface For ATM PHY Layer And ATM Layer

Devices, Level 2”; PMC-940212; Dec. 8, 1995

2. PMC-Sierra; VORTEX engineering document

3. PMC-Sierra; DSLAM engineering document

4. “Traffic Management And Switching With The Vortex Chip Set: S/UNI-APEX

Technical Overview”, PMC-981024

5. PMC-Sierra, “S/UNI APEX Test Bench Engineering Document”, PMC-981029

6. ATM Forum, “Universal Test & Operations PHY Interface for ATM (UTOPIA), Level

2”, Version 1.0, af-phy-0039.000, June 1995

7. ITU-T Recommendation I.432.1, “B-ISDN user-network interface – Physical layer

specification: General characteristics”, 08/96

8. ITU-T Recommendation I.363, “B-ISDN ATM Adaptation Layer (AAL) Specification”,

March 1993

9. AF Traffic Management Specification Version 4.1 AF-TM-0121.000, March 1999.

10. AF Traffic Management Baseline Text Document BTD-TM-01.01, April 1998

11. I.610 OAM

12. PMC Sierra, “Saturn Interface Specification and Interoperability Framework for

Packet and Cell Transfer Between Physical Layer and Link Layer Devices”,

PMC980902

13. PMC Sierra, “S/UNI APEX H/W Programmer’s Guide”, PMC-991454

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 8

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

5 APPLICATION EXAMPLES

Please refer to the document “Traffic Management And Switching With The

Vortex Chip Set: S/UNI-APEX Technical Overview”, PMC-981024

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 9

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

6 BLOCK DIAGRAM

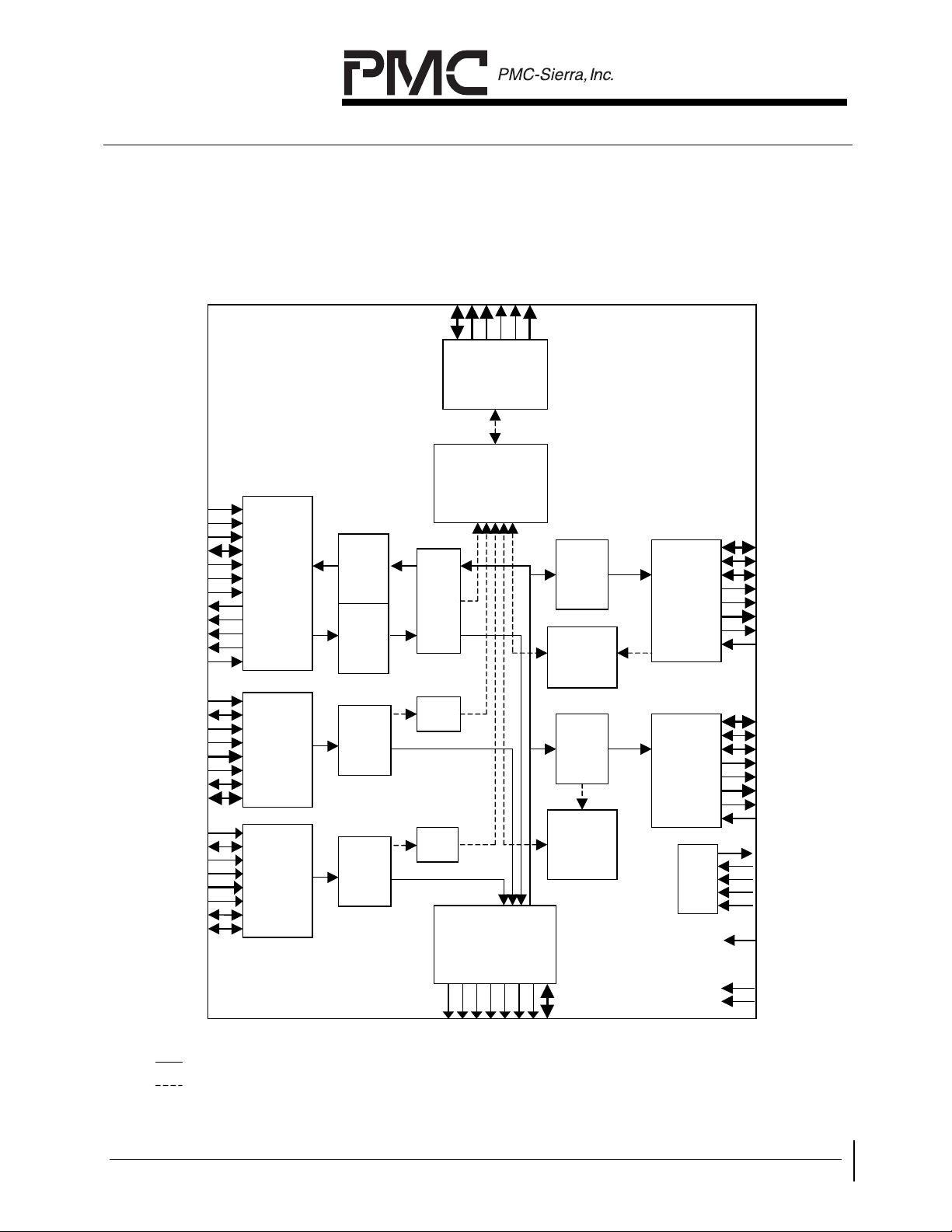

Figure 1 shows the function block diagram of the S/UNI APEX ATM traffic

manager. The functional diagram is arranged such that cell traffic flows through

the S/UNI APEX from left to right.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 10

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

Figure 1 - S/UNI APEX Block with Datapath

CMD[33:0]

CMP[1:0]

CMA[19:0]

CMRWB

CMCEB

CMAB[18:17]

SSRAM I/F

Queue Engine

BCLK

CSB

WR

AD[31:0]

ADSB

BURSTB

BLAST

READYB

WRDONEB

INTHIB

INTLOB

BUSPOL

uProc I/F

FIFO

4 chan

2 cell

FIFO

2 cell

SAR

Assist

FIFO

4 cell

Loop Port

Scheduler

Loop Tx

Any-PHY

LTADR[11:0]

LTPA

LTENB

LTSX

LTSOP

LTDAT[15:0]

LTPRTY

LTCLK

LRCLK

LRPA

LRSX

LRSOP

LRDAT[15:0]

LRPRTY

LRENB

LRADR[5:0]

WRCLK

WRPA

WRSX

WRSOP

WRDAT[15:0]

WRPRTY

WRENB

WRADDR[2:0]

Loop Rx

Any-PHY

WAN Rx

Any-PHY

Cell Data Path

Context Data Path

FIFO

4 cell

FIFO

4 cell

ICI

Select

ICI

Select

SDRAM I/F

B

B

B

S

S

S

A

A

C

R

B

C

B

B

C

C

C

WTADR[2:0]

FIFO

4 chan

4 cell

Wan

Port

Scheduler

]

]

]

B

E

W

R

B

C

]

0

0

0

0

:

:

:

:

1

1

1

1

[

[

1

3

[

[

S

M

A

B

Q

Q

B

B

D

D

C

C

B

B

C

C

WAN Tx

Any-PHY

JTAG

WTPA

WTENB

WTSX

WTSOP

WTDAT[15:0]

WTPRTY

WTCLK

TDO

TDI

TCK

TMS

TRSTB

SYSCLK

RSTB

OE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 11

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

7 DESCRIPTION

The PM7326 S/UNI APEX is a full duplex ATM traffic management device,

providing cell switching, per VC queuing, traffic shaping, congestion

management, and hierarchical scheduling to up to 2048 loop ports and up to 4

WAN ports.

The S/UNI APEX provides per-VC queuing for 64K VCs. A per-VC queue may be

allocated to any Class of Service (COS), within any port, in either direction

(ingress or egress path). Per-VC queuing enables PCR or SCR per-VC shaping

on WAN ports and greater fairness of bandwidth allocation between VCs within a

COS.

The S/UNI APEX provides three level hierarchical scheduling for port, COS, and

VC level scheduling. There are two, three level schedulers; one for the loop ports

and one for the WAN ports. The three level scheduler for the WAN ports

provides

• Weighted Interleaved Round Robin (WIRR) scheduling across the 4 WAN

ports enabling selectability of bandwidth allocation between the ports.

• Priority Fair scheduling across the 4 COS’s within each port. This class

scheduler is a modified priority scheduler allowing minimum bandwidth

allocations to lower priority classes within the port. Class scheduling within

a port is independent of activity on all other ports.

• There are three types of VC schedulers. VC scheduling within a class is

independent of activity on all other classes

• Shaped fair queuing is available for 4 classes. If the COS is shaped,

each VC within the class is scheduled for emission based on its VCs

shaping rate. During class congestion, the VC scheduler may lower a

VCs rate in proportion to a normalization factor calculated as a function

of the VCs rate and the aggregate rate of all active VCs within the

class.

• Weighted Interleaved Round Robin scheduling in which weights are

used to provide fairness between the VCs within a class.

• Frame continuous scheduling where an entire packet is accumulated

prior to transferring to a class queue.

The three level scheduler for the loop ports provides

• Weighted Interleaved Round Robin (WIRR) scheduling across the 2048

loop ports enabling selectability of bandwidth allocation between the ports

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 12

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

and ensuring minimal PHY layer FIFOing is required to support a wide

range of port bandwidths.

• Priority scheduling across the 4 COS’s within each port. Class scheduling

within a port is independent of activity on all other ports.

• VCs within a class are scheduled with a Round Robin scheduler or Frame

Continuous scheduling. VC scheduling within a class is independent of

activity on all other classes. Shaping is not supported on loop ports.

The S/UNI APEX forwards cells via tail of queue enqueuing and head of queue

dequeuing (emission) where tail of queue enqueuing is controlled by the VC

context record and subject to congestion control, and head of queue dequeuing

is controlled by the three level hierarchical schedulers. The VC context record

allows for enqueuing to any queue associated with any port, thus full switching is

supported, any port to any port.

The S/UNI APEX supports up to 256k cells of shared buffering in a 32-bit wide

SDRAM. Memory protection is provided via an inband CRC on a cell by cell

basis. Buffering is shared across direction, port, class, and VC levels. The

congestion control mechanism provides guaranteed resources to all active VCs,

allows sharing of available resources to VCs with excess bandwidth, and restricts

buffer allocation on a per-VC, per-class, per-port, and per-direction basis. The

congestion control mechanism supports PPD and EPD on a CLP0 and CLP1

basis across per-VC, per-class, per-port, and per-direction structures. EFCI

marking is supported on a per-VC basis. Congestion thresholds and packet

awareness is selectable on a per connection basis.

The S/UNI APEX provides flexible capabilities for signaling, management, and

control traffic. There are 4 independent uP receive queues to which both cell and

AAL5 frame traffic may be en-queued for termination by the uP. A staging buffer

is also provided enabling the uP to en-queue both cell and AAL5 frame traffic to

any outgoing queue. AAL5 SAR assistance is provided for AAL5 frame traffic to

and from the uP. AAL5 SAR assistance includes the generation and checking of

the 32-bit CRC field and the ability to reassemble all the cells from a frame in the

VC queue prior to placement on the uP queues. Any or all of the 64k VCs may

be configured to be routed to/from the uP port. Any or all of the VCs configured

to be routed to/from the uP port may also be configured for AAL5 SAR

assistance simultaneously. OAM cells may optionally (per-VC selectable) be

routed to a uP receive queue or switched with the user traffic. CRC10 generation

and checking is optionally provided on OAM cells to/from the uP.

The S/UNI APEX maintains cell counts of CLP0 and CLP1 cell transmits on a

per-VC basis. Global CLP0 and CLP1 congestion discards are also maintained.

Various error monitoring conditions and statistics are accumulated or flagged.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 13

PM7326 S/UNI APEX

DATA SHEET

PMC-1981224 ISSUE 6 ATM/PACKET TRAFFIC MANAGER AND SWITCH

The uP has access to both internal S/UNI APEX registers and the context

memory as well as diagnostic access to the cell buffer memory.

The S/UNI APEX provides a 8/16-bit Any-PHY compliant loop side master/slave

interface supporting up to 2048 ports. Egress cell transfers across the interface

are identified via an inband port identifier prepended to the cell. The slave

devices must match the inband port identifier with their own port ID or port ID

range in order to accept the cell. Per port egress flow control is effected via an

12-bit address polling bus to which the appropriate slave device responds with

out of band per port flow control status. Ingress cell transfers across the interface

are effected via a combination of UTOPIA L2 flow control polling and device

selection for up to 32 slave devices. The Any-PHY loop side interface may be

reconfigured as a standard single port UTOPIA L2 compliant slave interface. 16bit prepends are optionally supported on both ingress and egress for cell flow

identification enabling use with external address resolution devices, switch fabric

interfaces, or other layer devices.

The S/UNI APEX provides an 8/16-bit Any-PHY or UTOPIA L2 compliant WAN

side master/slave interface supporting up to 4 ports. 16-bit prepends are

optionally supported on both ingress and egress for cell flow identification

enabling use with external address resolution devices, switch fabric interfaces, or

other layer devices. The WAN port has port aliasing on the egress, providing in

service re-direction without requiring re-programming the context of active VCs.

The S/UNI APEX provides a 32-bit microprocessor bus interface for signaling,

control, cell and frame message extraction and insertion, VC. Class and port

context access, control and status monitoring, and configuration of the IC.

Microprocessor burst access for registers, cell and frame traffic is supported.

The S/UNI APEX provides a 36-bit ZBT or late write SSRAM interface for context

storage supporting up to 4MB of context for up to 64kVCs and up to 256k cell

buffer pointer storage. Context Memory protection is provided via 2 bits of parity

over each 34-bit word.

The total number of cells, the total number of VCs, support for address mapping

and shaped fair queuing is limited to the amount of context and cell buffer

memory available. Below is a table illustrating the most common combinations

of memory/features.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 14

Loading...

Loading...