PMC-Sierra,Inc.

2.4 Gbit/s ATM Layer Solution

Preliminary

PM7325

S/UNI®-ATLAS-3200

FEATURES

• Monolithic single chip device which

handles ATM Layer functions for one

direction including VPI/VCI address

translation, cell appending, cell rate

policing, cell counting and OAM

requirements for 64 k VCs (virtual

connections). Two or more PM7325

®

-ATLAS-3200 devices can be

S/UNI

cascaded to suppor t addit ion al VC 's .

• Instantaneous transfer rate of 3200

Mbit/s supports a cell transfer rate of

5.68x106 cells/s.

• Can be configured as an Ingress mode

device or an Egress mode device.

• POS-PHY/UTOPIA Level 3 PHY and

Switch interface supports a 32-bit

104 MHz interface. Extended cell

format is supported (52 - 64 byte cell).

Packets are not processed and are

buffered and passed through

transparently. Handles up t o 48 logical

PHY ports.

• Supports a full duplex 16 bit 5 2MHz

SCI-PHY™ Backwards Cell Interface

Port which allows an Ing r es s mod e

device and an Egress mode device to

communicate and behave as a single

bi-directional de vice.

• Supports a 64-bit (with or without

parity) 125 MHz External Pipelined

ZBT SRAM interface.

• Includes a FIFO buffered 32-bit

microprocessor bus interface for cell

insertion and extracti on, determ ini stic

VC Table access, status monitoring

and configuration of the de vi ce.

• Per-PHY output buffering scheme

resolves the head-of-li ne blocking

issue.

• Ingress and Egress functio ns include

flexible search engines that cover the

entire PHYID/VPI/VCI address range,

dual leaky-bucket policing, per-VC cell

counts, OAM-FM and OAM-PM

processing.

POLICING

• ITU-I.371, ATM Forum TM4.1

compliant, per-VC programmable dual

leaky-bucket polici ng with a

programmable action (tag, discard, or

count only) for each bucket, each with

three programmable 16 bit noncompliant cell counts.

• Per-PHY single leaky-bucket policing

with a programmable action (tag,

discard, or count only).

• Guaranteed Frame Rate (GF R)

Policing with Minimum Cell Rate

Frame Tagging.

OAM

• ITU-I.610 (1999) compliant OAM on

both Ingress and Egress directions .

• Complete Fault Management (AIS,

RDI, CC) processing, for VP/VC,

Segment/End-to-end flows on all VCs.

• Complete Performanc e Mon itoring

processing, for VP/VC, Segment/Endto-end, Forward/Backward flows, on

512 Uni-directional VCs.

• Per-PHY AIS/RDI generation.

CELL COUNTING

• Per-VC counts include CLP0 cells,

CLP1 cells, OAM cells, RM cells, and

invalid cells, cell s vio lating the c ontrac t

and total AAL5 frames.

• Per-PHY counts include CLP0 cells,

CLP1 cells, OAM cells, errored OAM

cells, unassigned/invalid cells and

policing violations.

• Per-device counts include total cells

received/ transmitted, and physical

layer cells.

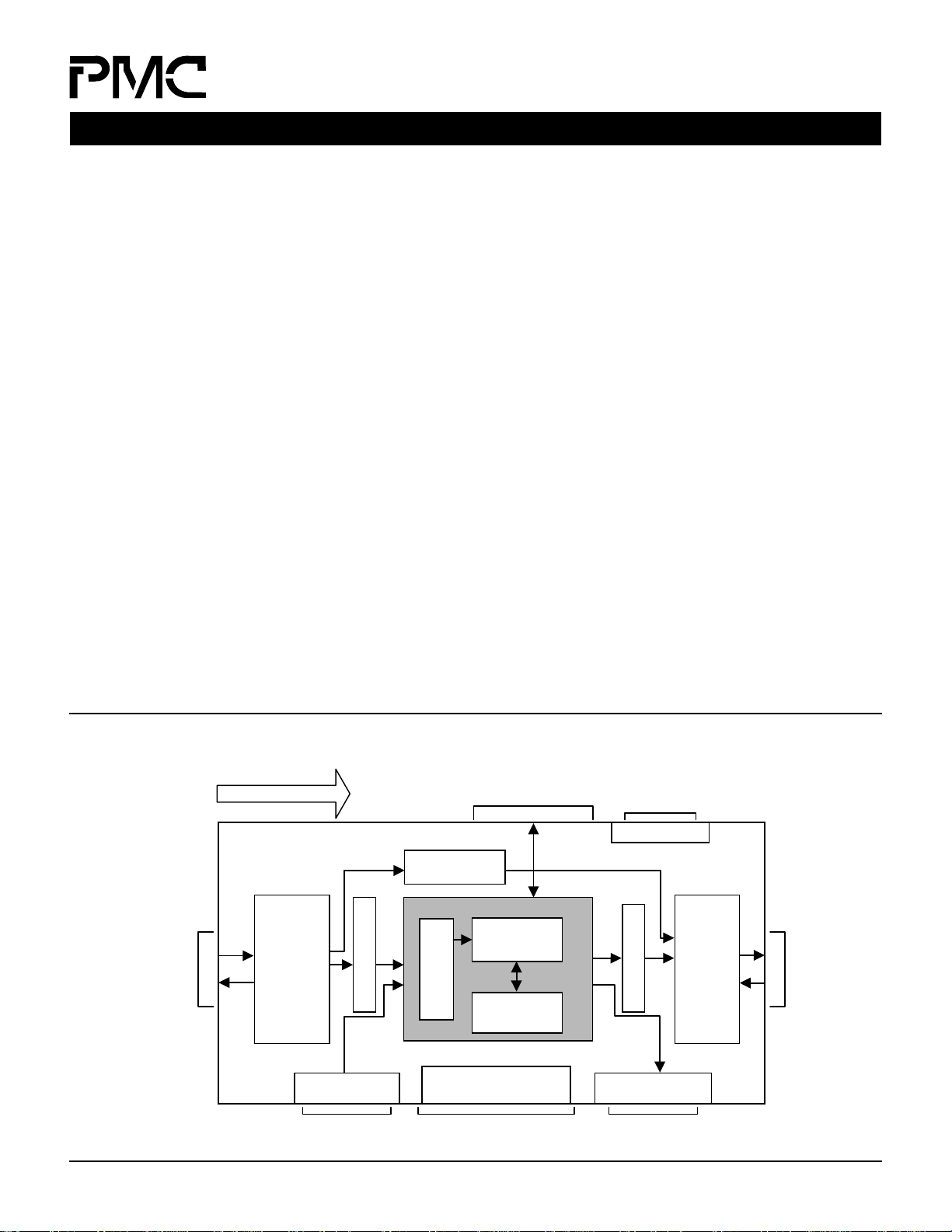

BLOCK DIAGRAM

Cell Flow

Packet Bypass

Interface

MHz Cell/Packet

UL3/PL3 32-bit 104

PMC-1990444 (p2) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2000

ICIF

SCI-PHY Rx Master

Input SDQ

IBCIF

Interface

125 MHz Pipelined ZBT

SRAM Interface

SDQ

Cell Processor

Policing, OAM,

Statistics,

Translation

Address Resolution

Microprocessor Interface

VC Table

(EDRAM)

MPIF

JTAG

JTAG Interface

Output SDQ

OBCIF

SCI-PHY Rx Slave

Interface

OCIF

104 MHz Cell/

UL3/PL3 32-bit

Packet Interface

2.4 Gbit/s ATM Layer Solution

Preliminary

PM7325 S/UNI®-ATLAS-3200

PACKAGING

• Provides a standard five signal

P1149.1 JTAG test port for boundary

scan board test purposes.

• Implemented in low power, 0.18

SRAM interface, and 3.3 V external

interfaces (excluding the SRAM

interface).

• Packaged in a 768 pin Tape Ball Grid

Array (TBGA) package.

micron, 1.5 V CMOS technology with

2.5 V embedded DRAM, 2 .5 V external

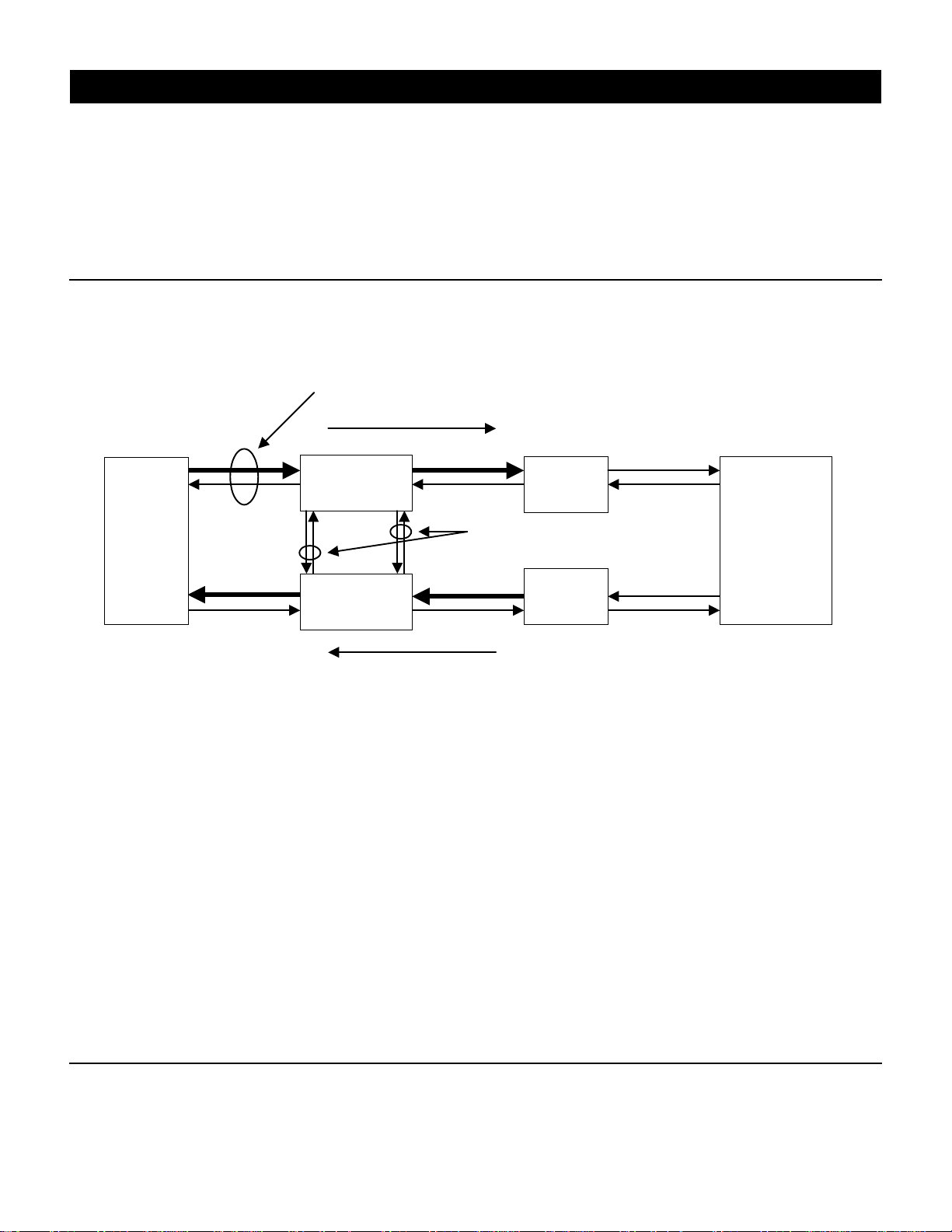

TYPICAL APPLICATION

S/UNI-ATLAS-3200 OC-48 PORT CARD APPLICATION

UTOPIA or POS-PHY (Level 3)

Ingress Direction

Ingress Mode

S/UNI-ATLAS3200 (+SRAM)

PHY

APPLICATIONS

• Core ATM switches.

• Wide Area Network ATM Core and

Edge Switches.

• ATM Enterprise and Workgroup

Switches.

• Broadband Access Mu lti ple xers.

Traffic

Manager

16 bit SCI PHY (Backward

Cell Interface)

Switch

Fabric

Egress Mode

S/UNI-ATLAS3200 (+SRAM)

Egress Direction

Traffic

Manager

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office ,

Attn: Document Coordina tor

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate inform ation,

send email to:

info@pmc-sierra.com

PMC-1990444 (p2)

© Copyright PMC-Sierra,

Inc. 2000. All rights reserved.

March 2000

S/UNI is a registered

trademark of PMC-Sierra,

Inc. SCI-PHY is a trademark

of PMC-Sierra, Inc.

Loading...

Loading...