S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

PM7324

S/UNI-ATLAS

SATURN USER NETWORK INTERFACE

ATM LAYER SOLUTION

DATASHEET

ISSUE 7: JANUARY, 2000

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

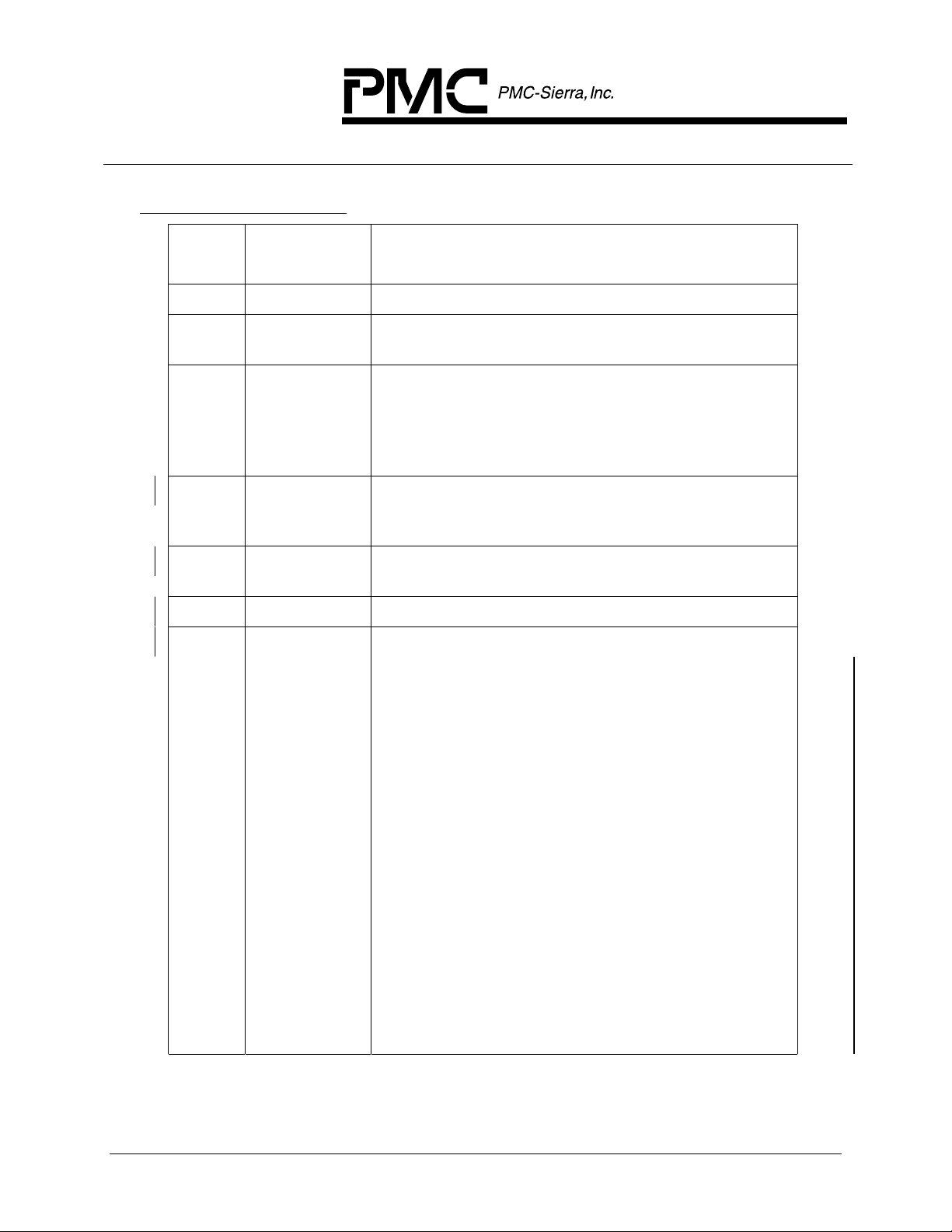

PUBLIC REVISION HISTORY

Issue

No.

1

2

3

4

5

6

7

Issue Date Details of Change

Sep., 1997

Nov., 1997

Initial release

Revised F4toF5 AIS processing and numerous other

clarifications and expanded descriptions.

Feb., 1998

Updated the Ingress and Egress VC Tables to include room

for Segment Defect Location and Defect Type fields. Also

included GFR policing. Modified PM internal RAM to 80bits wide to include support for I.356 measurement

requirements.

Oct., 1998

Updated VC Table and Register Addresses. Included

432SBGA package drawing. Enhanced description of OAM

processing, GFR policing, per-PHY policing, etc.

Jan., 1999

Removed “Proprietary and Confidential”. No content

change.

Sep., 1999

Jan., 2000

Aligns with Revision C

Corrected Reliability Calculations.

Corrected Block Diagram to reflect correct ingress/egress

backward cell interface block positions.

Modified RPOLL, IPOLL and TPOLL pin descriptions.

Table 37 – Added VOH specification.

Table 38 – Changed the timing specification to become

“Typical” for tSALR, tHALR, tSLR, tHLR.

Table 40 – Changed IAVALID setup and hold times (t

t

) to become “Typical”.

hold

setup

and

Table 40-45 – Changed Min CLK Frequency for RFCLK,

TFCLK, IFCLK, OFCLK, ISYSCLK, ESYSCLK.

Table 40-43 – Changed Utopia input hold times for

IWRENB[4:1], IAVALID, IADDR[4:0], IDAT[15:0], IPRTY,

ISOC, ORDENB, RPRTY, RDAT[15:0], RCA[4:1], RSOC

and TCA[4:1].

Table 40, 44, 45 – Changed prop delay times for ICA[4:1],

ISD[63:0], ISP[7:0], ESD[31:0] and ESP[3:0].

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

CONTENTS

1 FEATURES..................................................................................................................................... 1

1.1 POLICING ........................................................................................................................ 5

1.2 CELL COUNTING............................................................................................................. 5

2 APPLICATIONS.............................................................................................................................. 6

3 REFERENCES...............................................................................................................................7

4 APPLICATION EXAMPLES............................................................................................................ 8

5 DESCRIPTION............................................................................................................................... 9

6 PIN DIAGRAM.............................................................................................................................. 10

7 PIN DESCRIPTION...................................................................................................................... 11

8 FUNCTIONAL DESCRIPTION...................................................................................................... 42

8.1 INGRESS VC TABLE..................................................................................................... 45

8.2 CONNECTION IDENTIFICATION.................................................................................. 47

8.2.1 INGRESS CONNECTION IDENTIFICATION................................................... 47

8.3 SEARCH TABLE DATA STRUCTURE........................................................................... 52

8.3.1 PRIMARY SEARCH TABLE............................................................................. 52

8.3.2 SECONDARY SEARCH KEY TABLE.............................................................. 53

8.4 INGRESS CELL PROCESSING..................................................................................... 54

8.5 EGRESS VC TABLE...................................................................................................... 63

8.5.1 EGRESS CONNECTION IDENTIFICATION.................................................... 64

8.6 EGRESS CELL PROCESSING...................................................................................... 67

8.7 PERFORMANCE MONITORING.................................................................................... 76

8.7.1 PERFORMANCE MONITORING FLOWS........................................................ 86

8.8 CHANGE OF CONNECTION STATE............................................................................. 88

8.9 HEADER TRANSLATION............................................................................................... 90

8.10 CELL ROUTING............................................................................................................. 91

8.11 CELL RATE POLICING.................................................................................................. 91

8.11.1 PER-PHY POLICING....................................................................................... 99

8.11.2 GUARANTEED FRAME RATE ...................................................................... 104

8.11.3 CONTINUOUSLY VIOLATING MODE........................................................... 107

8.11.4 ATLAS POLICING CONFIGURATION........................................................... 107

8.12 CELL COUNTING......................................................................................................... 108

8.13 OPERATIONS, ADMINISTRATION AND MAINTENANCE (OAM) CELL SERVICING 111

8.14 FAULT MANAGEMENT CELLS................................................................................... 113

8.15 LOOPBACK CELLS...................................................................................................... 115

8.16 ACTIVATION/DEACTIVATION CELLS ........................................................................ 115

8.17 SYSTEM MANAGEMENT CELLS................................................................................ 115

PROPRIETARY AND CONFIDENTIAL i

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

8.18 F4 TO F5 OAM PROCESSING.................................................................................... 115

8.19 F5 TO F4 OAM PROCESSING.................................................................................... 124

8.20 RESOURCE MANAGEMENT CELLS .......................................................................... 129

8.21 S/UNI-ATLAS BACKGROUND PROCESSES.............................................................. 129

8.22 INGRESS BACKWARD OAM CELL INTERFACE........................................................ 131

8.23 EGRESS BACKWARD OAM CELL INTERFACE......................................................... 131

8.24 JTAG TEST ACCESS PORT........................................................................................ 132

8.25 MICROPROCESSOR INTERFACE.............................................................................. 132

8.26 EXTERNAL SRAM ACCESS........................................................................................ 132

8.27 WRITING CELLS.......................................................................................................... 133

8.28 READING CELLS......................................................................................................... 134

8.29 ATLAS DLL CLOCK OPERATION............................................................................... 138

9 NORMAL MODE REGISTER MEMORY MAP............................................................................ 139

9.1 NORMAL MODE REGISTER DESCRIPTION.............................................................. 147

10 TEST FEATURES DESCRIPTION............................................................................................. 407

10.1 TEST MODE 0 DETAILS.............................................................................................. 410

10.2 JTAG TEST PORT....................................................................................................... 410

11 OPERATION............................................................................................................................... 415

11.1 SCI-PHY EXTENDED CELL FORMAT......................................................................... 415

11.2 SYNCHRONOUS STATIC RAMS ................................................................................ 417

11.2.1 INGRESS VC-TABLE SRAM ......................................................................... 417

11.2.2 EGRESS VC-TABLE SRAM........................................................................... 418

11.3 ATM CELL PROCESSING........................................................................................... 419

11.3.1 OAM CELL FORMAT..................................................................................... 419

11.4 INGRESS VC IDENTIFICATION SEARCH ALGORITHM............................................ 421

11.4.1 OVERVIEW.................................................................................................... 422

11.4.2 INGRESS PERFORMANCE MONITORING ACTIVATION / DEACTIVATION428

11.5 EGRESS VC TABLE OPERATION.............................................................................. 428

11.5.1 INITIALIZATION PROCEDURE..................................................................... 428

11.5.2 CONNECTION SETUP.................................................................................. 429

11.5.3 EGRESS PERFORMANCE MONITORING ACTIVATION / DEACTIVATION 430

11.6 JTAG SUPPORT.......................................................................................................... 431

11.6.1 TAP CONTROLLER....................................................................................... 432

12 FUNCTIONAL TIMING ............................................................................................................... 436

12.1 INGRESS INPUT CELL INTERFACE........................................................................... 436

12.2 INGRESS OUTPUT CELL INTERFACE....................................................................... 439

12.3 EGRESS INPUT CELL INTERFACE............................................................................ 441

12.4 EGRESS OUTPUT CELL INTERFACE........................................................................ 444

PROPRIETARY AND CONFIDENTIAL ii

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

13 ABSOLUTE MAXIMUM RATINGS.............................................................................................. 447

14 D.C. CHARACTERISTICS.......................................................................................................... 448

15 A.C. TIMING CHARACTERISTICS............................................................................................. 450

16 MECHANICAL INFORMATION .................................................................................................. 464

PROPRIETARY AND CONFIDENTIAL iii

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

LIST OF FIGURES

FIGURE 1 S/UNI-ATLAS BLOCK DIAGRAM................................................................................................ 8

FIGURE 2 VC SEARCH KEY COMPOSITION........................................................................................... 47

FIGURE 3 PARAMETERS OF THE PRIMARY KEY AND SECONDARY KEY.......................................... 49

FIGURE 4 SEARCH KEY LOCATIONS WITHIN THE ROUTING WORD ................................................. 50

FIGURE 5 ATLAS SEARCH TABLE STRUCTURE.................................................................................... 52

FIGURE 6 EGRESS ROUTING WORD AND EGRESS LOOKUP ADDRESS............................................ 65

FIGURE 7 ATLAS PM FLOWS ........................................................................................................ 86

FIGURE 8 F4 TO F5 OAM FLOWS ...................................................................................................... 116

FIGURE 9 INGRESS TERMINATION OF F4 SEGMENT AND END-TO-END-POINT

CONNECTIONS............................................................................................. 117

FIGURE 10 INGRESS TERMINATION OF F4 SEGMENT AND END-TO-END POINT CONNECTION .. 118

FIGURE 11 INGRESS TERMINATION OF F4 SEGMENT END-POINT CONNECTION.......................... 119

FIGURE 12 INGRESS TERMINATION OF F4 END-TO-END POINT CONNECTION.............................. 120

FIGURE 13 F5 TO F4 OAM FLOWS ...................................................................................................... 124

FIGURE 14 EGRESS TERMINATION OF A VPC SEGMENT END-POINT............................................. 125

FIGURE 15 VPC INTERMEDIATE POINT............................................................................................... 126

FIGURE 16 VCC INTERMEDIATE POINT................................................................................................ 126

FIGURE 17 VPC SEGMENT END-POINT................................................................................................ 127

FIGURE 18 VCC SEGMENT END POINT................................................................................................ 127

FIGURE 19 VPC SEGMENT END-POINT AND END-TO-END POINT.................................................... 128

FIGURE 20 INGRESS VPC END-TO-END POINT AND SEGMENT END-POINT, VC SEGMENT

END-POINT AND SEGMENT SOURCE POINT. EGRESS VPC END-TO-

END AND SEGMENT SOURCE POINT WITH VCC SEGMENT END-

POINT AND VCC SEGMENT SOURCE POINT ............................................ 128

FIGURE 21 INGRESS VPC END-TO-END AND SEGMENT END POINT WITH VC INTERMEDIATE

POINT. EGRESS VPC END-TO-END AND SEGMENT SOURCE POINT

WITH VC INTERMEDIATE POINT AND VC SEGMENT SOURCE POINT. .. 129

FIGURE 22 INPUT OBSERVATION CELL (IN_CELL)............................................................................ 413

FIGURE 23 OUTPUT CELL (OUT_CELL)................................................................................................ 413

FIGURE 24 BI-DIRECTIONAL CELL (IO_CELL)...................................................................................... 414

FIGURE 25 LAYOUT OF OUTPUT ENABLE AND BI-DIRECTIONAL CELLS......................................... 414

FIGURE 26 EIGHT BIT WIDE CELL FORMAT......................................................................................... 416

FIGURE 27 SIXTEEN BIT WIDE CELL FORMAT .................................................................................... 417

FIGURE 28 COMMON OAM CELL FORMAT........................................................................................... 419

FIGURE 29 SPECIFIC FIELDS FOR AIS/RDI FAULT MANAGEMENT CELL......................................... 420

FIGURE 30 SPECIFIC FIELDS FOR THE FPM CELL ............................................................................. 420

FIGURE 31 SPECIFIC FIELDS FOR THE BR CELL................................................................................ 421

FIGURE 32 CONNECTION INSERTION WHEN BINARY TREE IS EMPTY............................................ 424

FIGURE 33 CONNECTION INSERTION WHEN BINARY TREE CONTAINS ONLY SINGLE VC

RECORD. ...................................................................................................... 424

FIGURE 34 CONNECTION INSERTION AT THE ROOT OF THE TREE................................................. 425

FIGURE 35 CONNECTION INSERTION IN THE MIDDLE OF THE BINARY TREE................................ 426

FIGURE 36 NEW SECONDARY SEARCH TABLE ENTRY INSERTED AT A LEAF. .............................. 427

FIGURE 37 BOUNDARY SCAN ARCHITECTURE................................................................................... 431

FIGURE 38 TAP CONTROLLER FINITE STATE MACHINE.................................................................... 433

FIGURE 39 INGRESS INPUT CELL INTERFACE (RPOLL=0) ................................................................ 436

FIGURE 40 INGRESS INPUT CELL INTERFACE (RPOLL=1) EXAMPLE 1........................................... 437

FIGURE 41 INGRESS INPUT CELL INTERFACE (RPOLL=1) EXAMPLE 2............................................ 438

FIGURE 42 INGRESS OUTPUT CELL INTERFACE (OTSEN=0)............................................................ 439

FIGURE 43 INGRESS OUTPUT CELL INTERFACE (OTSEN=1)............................................................ 440

FIGURE 44 EGRESS INPUT CELL INTERFACE (IPOLL=0)................................................................... 441

FIGURE 45 EGRESS INPUT CELL INTERFACE POLLED MODE (IPOLL=1) ........................................ 443

FIGURE 46 EGRESS OUTPUT CELL INTERFACE DIRECT MODE (TPOLL=0).................................... 444

FIGURE 47 EGRESS OUTPUT CELL INTERFACE POLLED MODE (TPOLL=1)................................... 445

FIGURE 48 MICROPROCESSOR INTERFACE READ TIMING.............................................................. 451

PROPRIETARY AND CONFIDENTIAL iv

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

FIGURE 49 MICROPROCESSOR INTERFACE WRITE TIMING............................................................. 453

FIGURE 50 EGRESS INPUT CELL INTERFACE TIMING....................................................................... 454

FIGURE 51 INGRESS OUTPUT CELL INTERFACE TIMING.................................................................. 455

FIGURE 52 INGRESS INPUT CELL INTERFACE TIMING..................................................................... 456

FIGURE 53 EGRESS OUTPUT CELL INTERFACE TIMING................................................................... 457

FIGURE 54 INGRESS SRAM INTERFACE TIMING................................................................................. 459

FIGURE 55 EGRESS SRAM INTERFACE TIMING.................................................................................. 460

FIGURE 56 JTAG PORT INTERFACE TIMING........................................................................................ 461

FIGURE 57 ATLAS THETA JA VS. AIR FLOW GRAPH........................................................................... 463

FIGURE 58 432 PIN SBGA – 40 X 40 MM BODY -(B SUFFIX)................................................................ 464

PROPRIETARY AND CONFIDENTIAL v

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

LIST OF TABLES

TABLE 1 INGRESS VC TABLE ........................................................................................................46

TABLE 2 INGRESS VC TABLE CELL FIELDS........................................................................................... 48

TABLE 3 INGRESS VC TABLE STATUS FIELD........................................................................................ 55

TABLE 4 INGRESS VC TABLE CONFIGURATION FIELD....................................................................... 56

TABLE 5 INGRESS VC TABLE OAM CONFIGURATION FIELD.............................................................. 58

TABLE 6 INGRESS INTERNAL STATUS FIELD....................................................................................... 59

TABLE 7 INGRESS VC TABLE MISCELLANEOUS FIELDS..................................................................... 61

TABLE 8 INGRESS VC TABLE ACTIVATION FIELDS ............................................................................. 62

TABLE 9 EGRESS VC TABLE ........................................................................................................63

TABLE 10 EGRESS VC TABLE CONNECTION IDENTIFIER FIELDS..................................................... 64

TABLE 11 EGRESS VC TABLE ACTIVATION FIELD............................................................................... 68

TABLE 12 EGRESS VC TABLE STATUS FIELD. ..................................................................................... 68

TABLE 13 EGRESS VC TABLE CONFIGURATION FIELD....................................................................... 69

TABLE 14 EGRESS OAM CONFIGURATION FIELD................................................................................ 71

TABLE 15 EGRESS INTERNAL STATUS FIELD...................................................................................... 73

TABLE 16 EGRESS VC TABLE MISCELLANEOUS FIELDS.................................................................... 74

TABLE 17 INTERNAL PM TABLE ........................................................................................................ 76

TABLE 18 PM TABLE CONFIGURATION FIELD...................................................................................... 77

TABLE 19 QOS PARAMETERS FOR PERFORMANCE MONITORING................................................... 79

TABLE 20 INGRESS AND EGRESS CHANGE OF STATE FIFO .............................................................. 89

TABLE 21 ATLAS ACTIONS ON POLICING WITH COCUP=0................................................................. 97

TABLE 22 ATLAS ACTIONS ON POLICING WITH COCUP=1................................................................. 97

TABLE 23 ATLAS ACTIONS WITH PER-PHY POLICING ...................................................................... 100

TABLE 24 INTERNAL PER-PHY POLICING RAM................................................................................... 101

TABLE 25 PER-PHY AND PER-VC NON-COMPLIANT CELL COUNTING PHYVCCOUNT=0.............. 103

TABLE 26 PER-PHY AND PER-VC NON-COMPLIANT CELL COUNTING PHYVCCOUNT=1.............. 104

TABLE 27 INGRESS/EGRESS OAM CONFIGURATION FIELD............................................................. 111

TABLE 28 F4 TO F5 FAULT MANAGEMENT PROCESSING.................................................................. 122

TABLE 29 REGISTER MEMORY MAP..................................................................................................... 139

TABLE 30 INSTRUCTION REGISTER..................................................................................................... 410

TABLE 31 IDENTIFICATION REGISTER................................................................................................. 410

TABLE 32 BOUNDARY SCAN REGISTER .............................................................................................. 411

TABLE 33 ATLAS VC-TABLE AVAILABLE SRAM TYPES....................................................................... 418

TABLE 34 OAM TYPE AND FUNCTION TYPE IDENTIFIERS................................................................. 419

TABLE 35 VC TABLE CONNECTION SETUP.......................................................................................... 429

TABLE 36 ABSOLUTE MAXIMUM RATINGS........................................................................................... 447

TABLE 37 D.C. CHARACTERISTICS ......................................................................................................448

TABLE 38 MICROPROCESSOR INTERFACE READ ACCESS.............................................................. 450

TABLE 39 MICROPROCESSOR INTERFACE WRITE ACCESS............................................................. 452

TABLE 40 EGRESS INPUT CELL INTERFACE....................................................................................... 454

TABLE 41 INGRESS OUTPUT CELL INTERFACE.................................................................................. 455

TABLE 42 INGRESS INPUT CELL INTERFACE...................................................................................... 456

TABLE 43 EGRESS OUTPUT CELL INTERFACE................................................................................... 457

TABLE 44 INGRESS SRAM INTERFACE................................................................................................ 458

TABLE 45 EGRESS SRAM INTERFACE................................................................................................. 459

TABLE 46 JTAG PORT INTERFACE ...................................................................................................... 460

TABLE 47 ORDERING INFORMATION.................................................................................................... 463

TABLE 48 THERMAL INFORMATION...................................................................................................... 463

PROPRIETARY AND CONFIDENTIAL vi

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

1

FEATURES

Point form summary of features.

•

Monolithic single chip device which handles bi-directional ATM Layer functions including

VPI/VCI address translation, cell appending (ingress only), cell rate policing (ingress only),

per-connection counting and I.610 compliant OAM requirements for 65536 VCs (virtual

connections).

•

Instantaneous bi-directional transfer rate of 800 Mbit/s supports a bi-directional cell transfer

rate of 1.42x10

•

The Ingress input interface supports an 8 or 16 bit SCI-PHY interface using direct addressing

6

cells/s (one STS-12c or four STS-3c).

for up to 4 PHY devices (compatible with Utopia Level 1 cell-level handshaking) and Multi-PHY

addressing for up to 32 PHY devices (Utopia Level 2 compatible).

•

The Ingress output interface supports an 8 or 16 bit SCI-PHY (52 – 64 byte extended ATM cell

with prepend/postpend) interface (compatible with Utopia Level 1 cell-level handshaking) to a

switch fabric.

•

The Egress input interface supports an 8 or 16 bit extended cell format SCI-PHY interface

using direct addressing for up to 4 PHY devices (compatible with Utopia Level 1 cell-level

handshaking) and Multi-PHY addressing for up to 32 PHY devices (Utopia Level 2

compatible).

•

The Egress output interface supports an 8 or 16 bit extended cell format SCI-PHY interface

using direct addressing for up to 4 PHY devices (compatible with Utopia Level 1 cell-level

handshaking) and Multi-PHY addressing for up to 32 PHY devices (Utopia Level 2

compatible).

•

Compatible with a wide range of switching fabrics and traffic management architectures

including per-VC or per-PHY queuing.

•

Highly flexible OAM-type cell and connection identification which can use arbitrary

PHYID/VPI/VCI values and/or cell appended bytes for connection identification (N.B. this is an

ingress function only). A direct lookup function is provided in the egress direction. The direct

lookup can use an arbitrary header or prepend/postpend location.

•

Ingress functionality includes a highly flexible search engine that covers the entire

PHYID/VPI/VCI address range, programmable dual leaky bucket UPC/NPC, per-connection

CLP0 and CLP1 cell counts (programmable), OAM-PM termination, generation and

monitoring, and OAM-FM termination, generation and alarm generation (monitoring).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 1

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

•

Egress functionality includes programmable direct lookup function, OAM-PM termination,

PM7324 S/UNI-ATLAS

generation and monitoring, per-connection CLP0 and CLP1 cell counts (programmable) and

OAM-FM termination, generation and alarm generation (monitoring). An egress per-PHY

output buffering scheme resolves the head-of-line blocking issue.

•

UPC/NPC function is a programmable dual leaky bucket policing device with a programmable

action (tag, discard, or count only) for each bucket. A total of 3 programmable 16 bit noncompliant cell counts are provided. The non-compliant cell counts may be programmed to

count, for example, dropped CLP0 cells, dropped CLP1 cells, and tagged CLP0 cells. The

UPC/NPC function also has a continuously violating mode, where a programmable action is

taken on all cells regardless of their compliance. AAL5 partial packet discard is also provided

so that the remainder of an AAL5 packet can be tagged or discarded if a single cell in the

packet is tagged or discarded as a result of violating policing.

•

In addition to the per-connection dual leaky bucket, a single leaky bucket UPC/NPC function is

provided on a per-PHY basis. A programmable action (tag, discard or count only) may be

configured for each PHY policing device. Three programmable non-compliant cell counts are

provided for each PHY. The non-compliant cell counts may be programmed to count, for

example, dropped CLP0 cells, dropped CLP1 cells and tagged CLP0 cells. The per-PHY

policing parameters and non-compliant cell counts are maintained in an on-chip RAM that can

be programmed and read via the 16-bit general purpose microprocessor interface.

•

Guaranteed Frame Rate frame-based policing selectable on a per-connection basis.

•

OAM-Performance monitoring is provided in the ingress and egress direction for bi-directional

PM sessions. A maximum of 512 (256 bi-directional sessions) PM sessions may be

simultaneously active. PM is supported on the F4 and F5 levels. The S/UNI-ATLAS provides

for the generation of Forw ard Monitoring and Backward Reporting PM cells (both segment

and end-to-end), the termination of Forward Monitoring and Backward Reporting cells, and for

non-intrusive monitoring of Forward Monitoring and Backward Reporting cells. The following

statistics are collected when terminating or monitoring PM flows:

1. Forward Impaired Block.

2. Forward Lost/Misinserted Impaired Block

3. Forward Severely Errored Cell Block (Lost).

4. Forward Severely Errored Cell Block (Misinserted).

5. Forward Severely Errored Cell Block (BIP-16 violations).

6. Forward Severely Errored Cell Block Combined (non-saturating)

7. Forward Lost CLP0+1 cell count.

8. Forward Lost CLP0 cell count.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 2

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

9. Forward Tagged CLP0 cell count

10. Forward Misinserted CLP0+1 cell count.

11. Forward Errored cell count.

12. Forward Total Lost CLP0+1 cell count.

13. Forward Total Lost CLP0 cell count.

14. Forward Lost Forward Monitoring cell count.

15. Backward Impaired Block.

16. Backward Lost/Misinserted Impaired Block.

17. Backward Severely Errored Cell Block (Lost).

18. Backward Severely Errored Cell Block (Misinserted).

19. Backward Severely Errored Cell Block (BIP-16 violations).

20. Backward Severely Errored Cell Block Combined (non-saturating)

21. Backward Severely Errored Cell Block Combined (saturating)

22. Backward Lost CLP0+1 cell count.

23. Backward Lost CLP0 cell count.

24. Backward Tagged CLP0 cell count.

25. Backward Misinserted CLP0+1 cell count.

26. Backward Errored cell count.

27. Backward Total Lost CLP0+1 cell count.

28. Backward Total Lost CLP0 cell count.

29. Backward Lost Fwd Monitoring PM cell count.

30. Backward Lost Backward Reporting PM cell count.

31. Total Transmitted CLP0+1 cell count.

32. Total Transmitted CLP0 cell count.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 3

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Statistics for PM sessions are held in on-chip RAM that can be read at any time through the

16-bit general-purpose microprocessor port.

Paced insertion of PM cells is provided.

PM block size generation and termination is per-session programmable ranging from 128 –

32768 cells.

Each of the 512 PM sessions can be configured to be a source, sink or non-intrusive

monitoring point of PM cells.

•

OAM-F ault Management is provided on a per-connection basis in the ingress and egress

directions. Simultaneous segment and end-to-end F4 and F5 AIS, RDI and CC cell

generation, termination and monitoring is supported. Alarm bits and interrupt masks are

provided on a per-connection basis. F4 to F5 AIS alarm splitting is provided in the Ingress

direction. Paced insertion of FM cells is provided.

•

OAM-Loopback extraction (to a Microprocessor Cell Interface) is per-connection configurable

in both the ingress and egress directions.

•

Includes a FIFO buffered microprocessor bus interface for cell insertion and extraction (in both

the ingress and egress directions), Ingress and Egress VC Table access, control and status

monitoring and configuration of the device.

•

Supports DMA access for cell extraction.

•

Uses common external Synchronous Flow-Through SRAM (with or without parity) for

maintaining per-connection information. Separate SRAM’s are used for the Ingress and

Egress context tables.

•

Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

•

Provides a generic 16 bit microprocessor bus interface for configuration, control and status

monitoring.

•

Low power 0.35 micron, 3.3V CMOS technology with a 3.3V UTOPIA (SCI-PHY), 3.3/5V

Microprocessor I/O interfaces and 3.3V external synchronous SRAM interfaces.

•

The UTOPIA (SCI-PHY) and external Synchronous SRAM interfaces are 52 MHz max.

•

432 Super BGA package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 4

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

1.1

1.2

Policing

•

•

•

•

Cell Counting

•

Policing is performed in the ingress direction for adherence to peak cell rate (PCR), cell delay

variation tolerance (CD VT), sustained cell rate (SCR) and burst tolerance (BT). Violating cells

can be noted, dropped or tagged.

Policing is performed using the virtual scheduling Generic Cell Rate Algorithm (GCRA)

described in ITU-T I.371.

Two policing instantiations available per VC. The policed cell streams can be any combination

of user cells, OAM cells, Resource Management, high priority cells or low priority cells.

Per-PHY policing may also be enabled. Each of 32 PHY devices may have a single leaky

bucket enabled, in addition to the dual leaky bucket of the connection. Violating cells can be

noted (counted only), dropped or tagged.

Counts maintained on a per-VC basis include total low priority cells, total high priority cells

and cells violating the traffic contract. Per-VC counts are maintained for both the ingress and

egress directions.

•

Counts maintained on a per-PHY basis (in both the Ingress and Egress directions) include:

number of CLP0 cells received, number of CLP1 cells received, number of OAM cells

received, number of RM cells received, number of errored OAM cells, number of errored RM

cells, number of cells with unassigned/invalid VPI/VCI/PTI and the number of cells received

with a non-zero GFC (ingress UNI only).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 5

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

2

APPLICATIONS

•

Wide Area Network ATM Core and Edge switches.

•

ATM Enterprise and Workgroup switches.

•

Broadband Access multiplexers.

•

XDSL Access Multiplexers (DSLAMs).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 6

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

3

REFERENCES

•

ATM Forum – ATM User-Network Interface Specification, V3.1 September, 1994

•

ITU-T Recommendation I.361 – “B-ISDN ATM Layer Specification”, November 1995

•

ITU-T Recommendation I.371 – “Traffic Control and Congestion Control in B-ISDN”, May, 1996

•

ITU-T Recommendation I.610 – “B-ISDN Operation and Maintenance Principles and

Functions”, June, 1997 (Rapporteur’s edition)

•

Bell Communications Research – Broadband Switching System (BSS) Generic Requirements,

GR-1110-CORE, Issue 1, September 1994

•

Bell Communications Research – Asynchronous Transfer Mode (ATM) and ATM Adaptation

Layer (AAL) Protocols, GR-1113-CORE, Issue 1, July 1994

•

Bell Communications Research – Generic Requirements for Operations of Broadband

Switching Systems, GR-1248-CORE, Issue 3, August, 1996.

•

IEEE 1149.1 – Standard Test Access Port and Boundary Scan Architecture, May 21, 1990

•

PMC-940212, ATM SCI-PHY, “SATURN Compliant Interface for ATM Devices”, July 1994,

Issue 2.

•

ATMF TM4.0 – ATM Forum Traffic Management Specification Version 4.0, af-tm-0056.000,

April, 1996.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 7

S/UNI-ATLAS

PM7324 S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

4

APPLICATION EXAMPLES

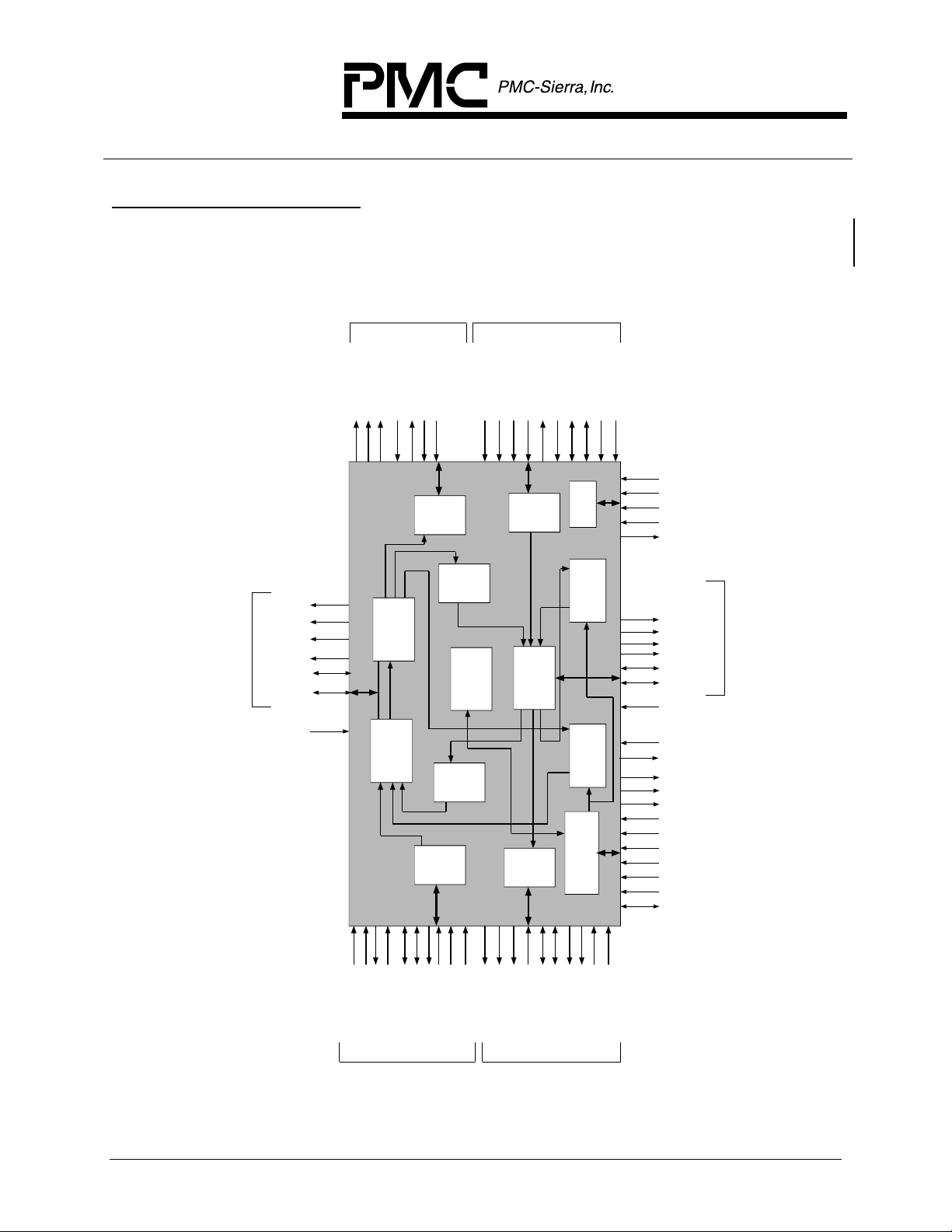

Figure 1 S/UNI-ATLAS Block Diagram

M

A

R

S

s

u

no

o

hr

nc

y

S

l

na

r

te

x

E

To

isadsb

isoeb

isrwb

isa[19:0]

isp[7:0]

isd[63:0]

isysclk

(Slave)

SCI-PHY Level1 Interface

0]

5:

[1

y

at

rt

od

op

b

n

c

lk

a

o

de

c

os

ofc

o

or

t

s

es

utpu

gr

O

In

r

s

so

l

s

es

el

ce

gr

C

o

In

r

P

s

e

h

c

in

es

r

r

g

a

g

e

n

S

E

In

s

t

es

gr

Inpu

In

]

:0

15

n

t[

se

ida

ot

e

l

ac

el

erf

C

Int

d

e

ar

l

ac

w

el

erf

gress

C

ck

t

E

a

In

B

n

s

Y

o

H

ti

tic

P

-

tis

r

lec

l

e

ta

o

P

S

C

d

e

ar

l

ac

w

el

ress

erf

C

ck

t

a

Ing

In

B

e

l

ac

el

erf

C

Int

1]

c

k

ty

o

ipr

is

ifcl

ica[

e

s

t

l

s

ac

e

el

pu

r

erf

C

In

Eg

Int

r

s

so

l

s

s

e

el

r

ce

C

g

o

E

r

P

e

t

s

l

s

ac

e

el

tpu

r

erf

u

C

g

O

E

Int

b[1]

ren

iw

]

:2

[3

ca

[4]

/i

ca

:3

/i

d

[4

dr

ail

iav

iad

e

G

ac

A

erf

JT

Int

or

ss

s

s

ce

e

r

g

pro

E

ro

ic

M

or

ss

s

ce

es

gr

pro

In

ro

ic

M

or

ss

e

ce

ac

erf

pro

ro

Int

ic

M

(Slave)

SCI-PHY Level1/Level2 Interface

]

:2

b[4

ren

iw

0]/

2:

dr[

iad

ipoll

e

l

ac

el

erf

C

Int

e

l

ac

el

erf

C

Int

tdi

trstb

tms

tck

tdo

busyb

edreq

idreq

intb

wrb

rdb

csb

ale

M

A

R

S

esoeb

esrwb

esadsb

esp[3:0]

esysclk

rstb

a[11:0]

d[15:0]

s

u

no

o

hr

nc

y

esa[19:0]

S

l

na

r

te

x

esd[31:0]

E

To

halfsecclk

]

]

]

ty

:0

r

15

rp

t[

rda

]

:2

[1]

[4

[1]

b

a[3

rca

en

rca

/

rc

d

]/

rrd

:3

ali

[4

rav

dr

rad

:2

c

o

b[4

rs

en

rd

/r

:0]

[2

dr

rad

l

k

0]

rfcl

rpol

15:

t[

tda

(Master)

SCI-PHY Level1/Level2 Interface

[1]

renb

tw

1]

tca[

]

2]

2]

oc

3:

a[4

ts

tfclk

[4:

b

en

r

w

]/t

2:0

dr[

tad

tpoll

(Master)

SCI-PHY Level1/Level2 Interface

a[

/tc

/tc

lid

3]

[4:

tava

r

d

tad

ty

tpr

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 8

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

5

DESCRIPTION

The S/UNI-ATLAS is a bi-directional ATM Layer device that implements the ATM layer functions

including header translation, policing, fault management, performance monitoring, per-connection

and per-PHY counting. The S/UNI-ATLAS is intended to be situated between a switch core and a

physical layer device. The S/UNI-ATLAS supports a sustained throughput of 1.42x10

6

cells/s in

both the ingress (from the PHY into the switch core) and the egress (from the switch core to the

PHY device) directions. The S/UNI-ATLAS uses external synchronous flow-through SRAM to

store the per-connection data structures. The device is capable of supporting up to 65536

connections.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 9

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

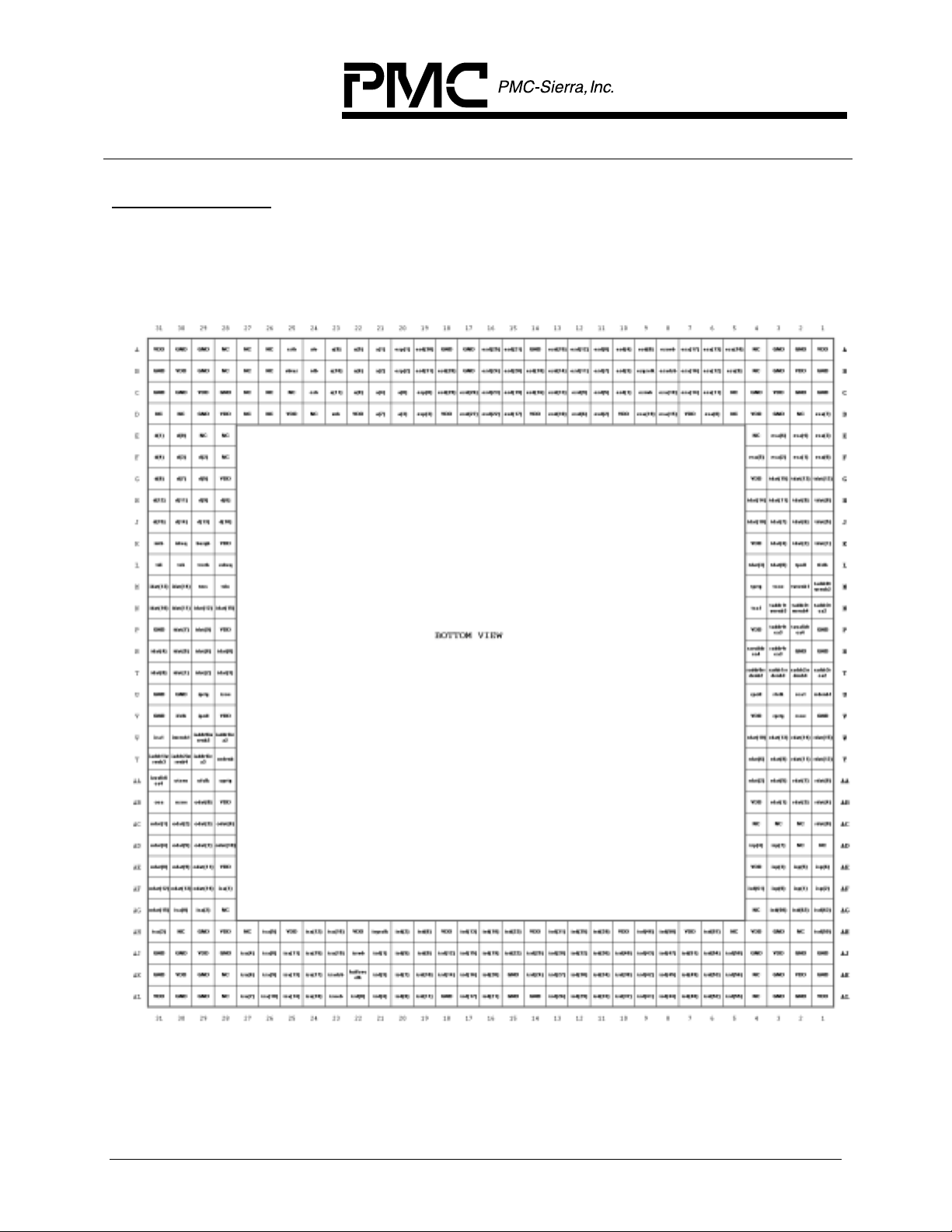

6

PIN DIAGRAM

The S/UNI-ATLAS is packaged in a 432 thermally enhanced BGA -SBGA package having a body

size of 40 mm x 40 mm x 1.54 mm and a ball pitch of 1.27 mm. This pin diagram can be

downloaded from the PMC-Sierra website (http://www.pmc-sierra.com).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 10

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

7

PIN DESCRIPTION

Pin Name Type Pin

Function

No.

Ingress Input Cell Interface: 28 pins

RFCLK Input U3 The Ingress Input Cell Interface clock (RFCLK) is used to read

words from the PHY receive side into the S/UNI-ATLAS Ingress

Input Cell Interface. RFCLK must cycle at a 52 MHz or lower

instantaneous rate. RSOC, RCA[4:1], RPRTY and RDAT[15:0]

are sampled on the rising edge of RFCLK. RRDENB[4:1],

RADDR[4:0] and RAVALID are updated on the rising edge of

RFCLK.

RPOLL Input U4 The Ingress Input Cell Interface Poll pin (RPOLL) is used to

control whether the Ingress Input Cell Interface operates in SCIPHY Level 1 mode or SCI-PHY Level 2 mode. If RPOLL is low,

the Ingress Input Cell Interface operates in SCI-PHY Level 1

mode (compatible with UTOPIA Level 1 cell-level handshaking).

This is a direct addressing mode using the RCA[4:1] inputs and

the RRDENB[4:1] outputs. If RPOLL is high, the Ingress Input

Cell Interface operates in a SCI-PHY Level 2 mode (compatible

with UTOPIA Level 2). This is a polled addressing mode using

the RADDR[4:0], RAVALID and RRDENB[1] outputs, and the

RCA[1] input. If fewer than 32 PHY devices are used, the

RAVALID pin need not be connected.

Note: In direct addressing mode, the 4-PHY configuration is not

recommended. Instead the 4-PHY address-polling mode should

be used. This does not apply to the Single or Dual-PHY

configurations.

RPOLL is assumed to be a static input.

RSOC Input V2 The Ingress Input Cell Interface Start of Cell (RSOC) marks the

start of the cell on the RDAT[15:0] bus. When RSOC is high, the

first word of the cell structure is present on the RDAT[15:0]

stream. It is not necessary for RSOC to be asserted for each

cell. An interrupt may be generated if RSOC is high during any

word other than the first word of the cell structure.

RSOC is sampled on the rising edge of RFCLK and considered

valid only when one of the RRDENB[4:1] signals so indicates.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 11

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

RCA[1]

RCA[2]

RCA[3]

RCA[4]

I/O U2

T1

R3

R4

RCA[4:1]

(continued)

Function

The active polarity of these signals is programmable and defaults

to active high.

If the RPOLL pin is low, the ATLAS asserts the appropriate

RRDENB[4:1] signal in response to a round robin polling of the

RCA[4:1] signals. Once committed, the ATLAS will transfer an

entire cell from a single PHY before servicing the next. The

ATLAS will complete the read of an entire cell even if the

associated RCA[4:1] input is deasserted during the cell transfer.

Sampling of the RCA[4:1] inputs resumes the cycle after the last

octet of a cell has been transferred.

Note, RCA[1] is an input only.

If the RPOLL pin is high, the RCA[3:2] pins are redefined as

RADDR[4:3] and the RCA[4] pin is redefined as RAVALID.

If the RPOLL pin is high, the ATLAS polls up to 32 PHYs using

the PHY address signals RADDR[4:0]. A PHY device being

addressed by RADDR[4:0] is expected to indicate whether or not

it has a complete cell available for transfer by driving RCA[1]

during the clock cycle foll owing that in which it is addressed.

When a cell transfer is in progress, the ATLAS will not poll the

PHY device which is sending the cell and so PHY devices need

not support the cell availability indication during cell transfer. The

selection of a particular PHY device from which to transfer a cell

is indicated by the state of RADDR[4:0] and when RRDENB[1] is

asserted.

Note, RCA[1] is an input only. The RCA[4:1] signals are sampled

on the rising edge of RFCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 12

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

RRDENB[1]

RRDENB[2]

RRDENB[3]

RRDENB[4]

RADDR[4]

RADDR[3]

RADDR[2]

RADDR[1]

RADDR[0]

Output U1

T4

T3

T2

Output R3

T1

T2

T3

T4

Function

The active low read enable (RRDENB[4:1]) outputs are used to

initiate the reading of cells from a PHY device into the Ingress

Input Cell Interface.

If the RPOLL pin is low, the ATLAS asserts one of the

RRDENB[4:1] outputs to transfer a cell from one of up to 4 PHY

devices. A valid word is expected on the RDAT[15:0] bus at the

second rising edge of RFCLK after one of the enables is

asserted. When all of the enables are deasserted, no valid data

is expected.

The RRDENB[4:1] outputs are updated on the rising edge of

RFCLK.

If the RPOLL pin is high, the RRDENB[4:2] pins are redefined as

RADDR[2:0]. The RRDENB[1] pin is used to transfer all cells.

The source PHY is selected by the RADDR[4:0] signals.

If the RPOLL pin is high, the RADDR[4:0] pins are used for PHY

addressing. If the RPOLL pin is low, the RADDR[4:0] pins are

redefined as RCA[3:2] and RRDENB[4:2].

If the RPOLL pin is high, the RADDR[4:0] signals are used to

address up to 32 PHY devices for the purposes of polling and

selection for cell transfer. When conducting polling, in order to

avoid bus contention, the ATLAS inserts gap cycles during which

RADDR[4:0] is set to 0x1F and RAVALID is logic 0. When this

occurs, no PHY device should drive RCA[1] during the following

clock cycle. Polling is performed in incrementing sequential

order. The PHY device selected for transfer is based on the

RADDR[4:0] value present when RRDENB[1] is falls. The

RADDR[4:0] bus is updated on the rising edge of RFCLK.

RAVALID I/O R4 If the RPOLL pin is high, the PHY Address Valid (RAVALID) pin is

active. If the RPOLL pin is low, the RAVALID pin is redefined as

RCA[4].

If the RPOLL pin is high, the RAVALID pin indicates that the

RADDR[4:0] bus is asserting a valid PHY address for polling

purposes. When this signal is deasserted, the RADDR[4:0] bus

is set to 0x1F.

RAVALID is not necessary when less than 32 PHY devices are

being polled. RAVALID is updated on the rising edge of RFCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 13

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

RDAT[15]

RDAT[14]

RDAT[13]

RDAT[12]

RDAT[11]

RDAT[10]

RDAT[9]

RDAT[8]

RDAT[7]

RDAT[6]

RDAT[5]

RDAT[4]

RDAT[3]

RDAT[2]

Input W1

W2

W3

Y1

Y2

W4

Y3

AA1

AA2

Y4

AA3

AB1

AB2

AA4

Function

The Ingress Input Cell Interface cell data bus (RDAT[15:0])

carries the ATM cell octets that are written to the Ingress Input

Cell Interface. The RDAT[15:0] bus is sampled on the rising edge

of RFCLK and considered valid only when one of the

RRDENB[4:1] signals so indicates. RDAT[15:8] is only valid if the

RBUS8 register bit is low.

RDAT[1]

RDAT[0]

AB3

AC1

RPRTY Input V3 The Ingress Input Cell Interface parity (RPRTY) signal indicates

the parity (programmable for odd or even parity) of the

RDAT[15:0] bus. If the RBUS8 register bit is low, the RPRTY

signal indicates parity over the RDAT[15:0] data bus. If RBUS8 is

high, the RPRTY signal indicates parity over the RDAT[7:0] data

bus. A maskable interrupt status is generated upon a parity

error; no other actions are taken. The RPRTY signal is sampled

on the rising edge of RFCLK and is considered valid only when

one of the RRDENB[4:1] signals so indicates.

Ingress SRAM Interface: 96 pins

ISYSCLK Input AH21 The Ingress System clock (ISYSCLK) is used for the Ingress

portion of the ATLAS. ISYSCLK must cycle at a 52 MHz or lower

instantaneous rate, but a high enough rate to maintain an

800Mbit/s throughput. ISADSB, ISOEB, ISRWB are updated on

the rising edge of ISYSCLK. When ISD[63:0] and ISP[7:0] are

outputs, they are updated on the rising edge of ISYSCLK. When

ISD[63:0] and ISP[7:0] are inputs, they are sampled on the rising

edge of ISYSCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 14

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

ISD[63]

ISD[62]

ISD[61]

ISD[60]

ISD[59]

ISD[58]

ISD[57]

ISD[56]

ISD[55]

ISD[54]

ISD[53]

ISD[52]

ISD[51]

ISD[50]

I/O AG1

AG2

AF4

AG3

AH1

AJ5

AH6

AK5

AL5

AJ6

AK6

AL6

AJ7

AH8

Function

The bi-directional Ingress VC Table SRAM data bus (ISD[63:0])

pins interface directly with the synchronous SRAM data ports.

A SRAM read is performed when the ATLAS drives the address

strobe (ISADSB) low and the ISRWB output high. The ATLAS

tristates the ISD[63:0] pins and samples the value driven by the

SRAM on the second rising edge of the ISYSCLK input after

ISADSB is asserted.

A SRAM write is performed when the ATLAS drives the address

strobe low (ISADSB) and the ISRWB output low. The ATLAS

presents valid data on the ISD[63:0] pins upon the rising edge of

ISYSCLK which is written into the SRAM on the next ISYSCLK

rising edge. ISD[63:0] is tristated on the rising edge of ISYSCLK.

Contention is avoided by not performing a write during the cycle

after a read burst.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 15

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

ISD[49]

ISD[48]

ISD[47]

ISD[46]

ISD[45]

ISD[44]

ISD[43]

ISD[42]

ISD[41]

ISD[40]

ISD[39]

ISD[38]

ISD[37]

ISD[36]

I/O AK7

AL7

AJ8

AH9

AK8

AL8

AJ9

AK9

AL9

AJ10

AH11

AK10

AL10

AJ11

Function

Continued

ISD[35]

ISD[34]

ISD[33]

ISD[32]

AH12

AK11

AL11

AJ12

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 16

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

ISD[31]

ISD[30]

ISD[29]

ISD[28]

ISD[27]

ISD[26]

ISD[25]

ISD[24]

ISD[23]

ISD[22]

ISD[21]

ISD[20]

ISD[19]

ISD[18]

I/O AH13

AK12

AL12

AJ13

AK13

AL13

AJ14

AK14

AH15

AJ15

AL16

AK16

AJ16

AH16

Function

Continued

ISD[17]

ISD[16]

AL17

AK17

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 17

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

ISD[15]

ISD[14]

ISD[13]

ISD[12]

ISD[11]

ISD[10]

ISD[9]

ISD[8]

ISD[7]

ISD[6]

ISD[5]

ISD[4]

ISD[3]

ISD[2]

I/O AJ17

AK18

AH17

AJ18

AL19

AK19

AJ19

AL20

AK20

AH19

AJ20

AL21

AK21

AH20

Function

Continued

ISD[1]

ISD[0]

AJ21

AL22

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 18

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

ISP[7]

ISP[6]

ISP[5]

ISP[4]

ISP[3]

ISP[2]

ISP[1]

ISP[0]

I/O AD3

AE1

AE2

AD4

AE3

AF1

AF2

AF3

Function

The Ingress VC Table SRAM parity (ISP[7:0]) pins provide parity

protection over the ISD[63:0] data bus.

ISP[0] completes odd parity for ISD[7:0]

ISP[1] completes odd parity for ISD[15:8]

ISP[2] completes odd parity for ISD[23:16]

ISP[3] completes odd parity for ISD[31:24]

ISP[4] completes odd parity for ISD[39:32]

ISP[5] completes odd parity for ISD[47:40]

ISP[6] completes odd parity for ISD[55:48]

ISP[7] completes odd parity for ISD[63:56]

ISP[7:0] has the same timing as ISD[63:0]. When data are being

written into the SRAM, the ATLAS generates correct parity.

When data are being read from the SRAM, the ATLAS asserts a

maskable interrupt indication upon parity error detection. No

other action is taken, therefore, the ISP[7:0] may be unconnected

if parity protection is not required.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 19

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

ISA[19]

ISA[18]

ISA[17]

ISA[16]

ISA[15]

ISA[14]

ISA[13]

ISA[12]

ISA[11]

ISA[10]

ISA[9]

ISA[8]

ISA[7]

ISA[6]

Output AJ23

AL24

AK24

AH23

AJ24

AL25

AK25

AH24

AJ25

AL26

AK26

AJ26

AL27

AK27

Function

The Ingress VC Table SRAM (ISA[19:0]) outputs identify the

SRAM locat ions accessed.

The 16 least significant bits (ISA[15:0]) locate 1 of 65536

possible Ingress VC Table entries. If 65536 connections are not

required, the most significant bits of ISA[15:0] may be

unconnected with no physical memory associated with the

unused memory space.

The four most significant bits (ISA[19:16]) identify the fields

within an Ingress VC Table record. In most applications, the

ISA[19:16] pins are decoded to SRAM chip selects. Physical

memory need not be allocated for unused fields.

The ISA[15:0] outputs are also used to access the Ingress VC

Table Search Table.

The ISA[19:0] bus is updated on the rising edge of ISYSCLK.

ISA[5]

ISA[4]

ISA[3]

ISA[2]

ISA[1]

ISA[0]

AH26

AJ27

AH31

AG29

AF28

AG30

ISRWB Output AJ22 The Ingress VC Table SRAM Read Write Bar (ISRWB) qualifies

the data and parity busses. If the ISRWB output is asserted

high, a read operation is performed and the ATLAS tristates the

data and parity busses so they may be driven by the SRAM. If

the ISRWB output is asserted low, a write operation is performed

and the ATLAS drives the data and parity busses.

ISRWB is updated on the rising edge of ISYSCLK.

ISADSB Output AK23 The Ingress VC Table SRAM Address Strobe (ISADSB) qualifies

the address bus. If the ISADSB output is asserted low, an SRAM

access is initiated.

ISADSB is updated on the rising edge of ISYSCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 20

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

Function

No.

ISOEB Output AL23 The Ingress VC Table asynchronous SRAM Output Enable

(ISOEB) controls the SRAM tristate outputs. When ISOEB is low

during a read cycle, the selected SRAM (as determined by

ISA[19:0] decoding) is expected to drive the ISD[63:0] and

ISP[7:0] data busses.

ISOEB is updated on the rising edge of ISYSCLK.

Ingress Output Cell Interface: 22 pins

OFCLK Input AA29 The Ingress Output Cell Interface clock (OFCLK) is used to read

words from the Ingress Output Cell Interface. OFCLK must cycle

at a 52 MHz or lower instantaneous rate, but a high enough rate

to avoid a FIFO overflow. OSOC, OCA, OPRTY and ODAT[15:0]

are updated on the rising edge of OFCLK. ORDENB is sampled

on the rising edge of OFCLK.

ORDENB Input Y28 The active low read enable (ORDENB) signal is used to indicate

transfers from the Ingress Output Cell Interface. When ORDENB

is sampled low, using the rising edge of OFCLK, a word is read

from the internal synchronous Ingress Output Cell Interface

FIFO, and output on bus ODAT[15:0]. When ORDENB is

sampled high, no read is performed and outputs ODAT[15:0],

OPRTY and OSOC are tristated if the OTSEN input is high.

ORDENB must operate in conjunction with OFCLK to access the

FIFO at a high enough rate to avoid a FIFO overflow.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 21

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

ODAT[15]

ODAT[14]

ODAT[13]

ODAT[12]

ODAT[11]

ODAT[10]

ODAT[9]

ODAT[8]

ODAT[7]

ODAT[6]

ODAT[5]

ODAT[4]

ODAT[3]

ODAT[2]

Tristate

AG31

AF29

AF30

AF31

AE29

AD28

AE30

AE31

AD29

AC28

AD30

AD31

AC29

AC30

Function

The Ingress Output Cell Interface data bus (ODAT[15:0]) carries

the ATM cell octets that are read from the Ingress Output Cell

Interface FIFO. If the OBUS8 register bit is high, only ODAT[7:0]

carries cell octets, The ODAT[15:0] bus is updated on the rising

edge of OFCLK.

When the Ingress Output Cell Interface is configured for tristate

operation using the OTSEN input, tristating of the ODAT[15:0]

output bus is controlled by the ORDENB input.

When OTSEN is low, the ODAT[15:0] bus is low when no cells

are being transferred.

ODAT[1]

ODAT[0]

OPRTY

OSOC

Tristate

Tristate

AC31

AB29

AA28 The Ingress Output Cell Interface parity (OPRTY) signal

indicates the parity of the ODAT[15:0] data bus. OPRTY is the

parity (programmable odd or even parity) calculation over the

ODAT[15:0] data bus if the OBUS8 register bit is low. If OBUS8

is high, OPRTY indicates the parity of the ODAT[7:0] data bus.

OPRTY is updated on the rising edge of OFCLK.

When the Ingress Output Cell Interface is configured for tristate

operation using the OTSEN input, tristating of the OPRTY output

signal is controlled by the ORDENB input.

AB30 The Ingress Output Cell Interface start of cell (OSOC) signal

marks the start of cell on the ODAT[15:0] data bus. When OSOC

is high, the first word of the cell structure is present on the

ODAT[15:0] bus. OSOC is updated on the rising edge OFCLK.

When the Ingress Output Cell Interface is configured for tristate

operation using the OTSEN input, tristating of the OSOC output

is controlled by the ORDENB input.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 22

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

Function

No.

OCA Output AB31 The active polarity of this signal is programmable and defaults to

active high.

The OCA signal indicates when the Ingress Output Cell Interface

has a cell available. When asserted, OCA indicates that at least

one cell is available to be read from the Ingress Output Cell

Interface FIFO. The OCA signal is deasserted when the Ingress

Output Cell Interface has 0 to 4 words available for the current

cell. OCA is updated on the rising edge of OFCLK.

OTSEN Input AA30 The tristate enable, OTSEN, signal allows control over the

Ingress Output Cell Interface ODAT[15:0], OPRTY, and OSOC

outputs. When OTSEN is high, the active low read enab le input,

ORDENB controls when the ODAT[15:0], OPRTY, and OSOC

outputs are driven. When OTSEN is low, the ODAT[15:0],

OPRTY and OSOC outputs are always driven.

Egress Input Cell Interface: 28 pins

IFCLK Input V30 The Egress Input Cell Interface clock (IFCLK) is used to write

words from the Traffic Shaper (or Switch Port) transmit port into

the S/UNI-ATLAS Egress Input Cell Interface. IFCLK must cycle

at a 52 MHz or lower instantaneous rate. ISOC, IPRTY,

IDAT[15:0] and IWRENB[4:1] are sampled on the rising edge of

IFCLK. IADDR[4:0], IAVALID and ICA[4:1] are updated on the

rising edge of IFCLK.

IPOLL Input V29 The Egress Input Cell Interface POLL pin (IPOLL) is used to

control whether the Egress Input Cell Interface operates in SCI-

PHY Level 1 mode or SCI-PHY Level 2 mode. If IPOLL is low,

the Egress Input Cell Interface operates in SCI-PHY Level 1

mode (compatible with UTOPIA Level 1 cell-level handshaking).

This is a direct addressing mode using the ICA[4:1] outputs and

the IWRENB[4:1] inputs. If IPOLL is high, the Egress Input Cell

Interface operates in SCI-PHY Level 2 mode (compatible with

UTOPIA Level 2). This is a polled addressing mode using the

IADDR[4:0], IAVALID and IWRENB[1] inputs, and the ICA[1]

output. If fewer than 32 PHY devices are used, the IAVALID pin

can be tied high.

Note: In direct addressing mode, the 4-PHY configuration is not

recommended. Instead the 4-PHY address-polling mode should

be used. This does not apply to the Single or Dual-PHY

configurations.

IPOLL is assumed to be a static input.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 23

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

Function

No.

ISOC Input U28 The Egress Input Cell Interface Start of Cell (ISOC) marks the

start of the cell on the IDAT[15:0] bus. When ISOC is high, the

first word of the cell structure is present on the IDAT[15:0]

stream. It is not necessary for ISOC to be asserted for each cell.

An interrupt may be generated if ISOC is high during any word

other than the first word of the cell structure. ISOC is sampled

on the rising edge of IFCLK and considered valid only when one

of the IWRENB[4:1] signals so indicates.

ICA[1]

ICA[2]

ICA[3]

ICA[4]

O

I/O

I/O

I/O

W31

W28

Y29

AA31

The active polarity of these signals is programmable and defaults

to active high.

If the IPOLL pin is low, the ATLAS asserts the appropriate

ICA[4:1] signal indicating the availability of space in the Egress

Input Cell Interface per-PHY 4 cell FIFO of the ATLAS. The

Egress Input Cell Interface of the ATLAS must be programmed to

emulate the number of PHY devices to which the ATLAS is

connected.

Note, ICA[1] is an output only.

ICA[4:1]

(continued)

If the IPOLL pin is high, the ICA[3:2] pins are redefined as

IADDR[4:3] and the ICA[4] pin is redefined as IAVALID.

If the IPOLL pin is high, the ATLAS asserts the availability of

space in the FIFO of a particular PHY device when polled using

the IADDR[4:0] and IAVALID signals. The ATLAS will drive the

ICA[1] signal to the appropriate value during the clock cycle

following that in which a particular PHY device is addressed.

When a cell transfer is in progress, the ATLAS will assert the

availability of the PHY device to which the current cell is being

transmitted, and the true availability of the PHY device will be

asserted 4 words before the end of the cell transfer. The

selection of a particular PHY device to which a cell is to be

transferred is indicated by the state of the IADDR[4:0] bus when

IWRENB[4:1] is asserted.

Note, ICA[1] is an output only.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 24

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

IWRENB[1]

IWRENB[2]

IWRENB[3]

IWRENB[4]

IADDR[4]

IADDR[3]

IADDR[2]

IADDR[1]

IADDR[0]

I

I

I

I

I/O

I/O

I

I

I

W30

W29

Y31

Y30

Y29

W28

Y30

Y31

W29

Function

The active low write enable (IWRENB[4:1]) inputs are used to

initiate the transfer of cells from the Traffic Shaper into the ATLAS

Egress Input Cell Interface.

If the IPOLL pin is low, the ATLAS samples the IWRENB[4:1]

inputs to determine to which one of up to 4 PHY devices a cell is

to be written. A valid word is expected on the IDAT[15:0] bus

when one of the enables is sampled low on the rising edge of

IFCLK. If a cell is written into the ATLAS while that particular

PHY ICA[x] is deasserted, that cell transfer is ignored, and a

maskable interrupt is asserted. If more than one enable is

asserted simultaneously, a maskable interrupt is asserted, and

the cell transfer is ignored.

If the IPOLL pin is high, the IWRENB[4:2] pins are redefined as

IADDR[2:0]. The IWRENB[1] pin is used to transfer all cells. The

destination PHY is selected by the IADDR[4:0] signals.

If the IPOLL pin is high, the IADDR[4:0] pins are used for PHY

addressing. If the IPOLL register bit is logic pin is low, the

IADDR[4:0] pins are redefined as ICA[3:2] and IWRENB[4:2].

If the IPOLL pin is high, the IADDR[4:0] signals are used to

address up to 32 PHY devices for polling and selection for cell

transfer. The PHY devices selected for transfer is based on the

IADDR[4:0] value present when the IWRENB[1] signal falls.

The IADDR[4:0] bus is sampled on the rising edge of IFCLK.

IAVALID I/O AA31 If the IPOLL pin is high, the PHY address valid pin (IAVALID) is

active. If the IPOLL pin is low, the IAVALID pin is redefined as

ICA[4].

If the IPOLL pin is high, the IAVALID pin indicates that the

IADDR[4:0] bus is asserting a valid PHY address for polling

purposes. When this signal is deasserted, the IADDR[4:0] bus

must be set to 0x1F.

If fewer than 32 PHY devices are being polled and the IAVALID

pin is not functionally used, then IAVALID must be tied high.

IAVALID is sampled on the rising edge of IFCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 25

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

IDAT[15]

IDAT[14]

IDAT[13]

IDAT[12]

IDAT[11]

IDAT[10]

IDAT[9]

IDAT[8]

IDAT[7]

IDAT[6]

IDAT[5]

IDAT[4]

IDAT[3]

IDAT[2]

Input

N28

M30

M31

N29

N30

N31

P29

R28

P30

R29

R30

R31

T28

T29

Function

The Egress Input Cell Interface cell data bus (IDAT[15:0]) carries

the ATM cell octets that are written to the Egress Input Cell

Interface. The IDAT[15:0] bus is sampled on the rising edge of

IFCLK and considered valid only when one of the IWRENB[4:1]

signals so indicates. IDAT[15:8] is only valid if the IBUS8 register

bit is low.

IDAT[1]

IDAT[0]

IPRTY Input

T30

T31

U29

Egress Output Cell Interface: 28 pins

TFCLK Input

L1

The Egress Input Cell Interface parity (IPRTY) signal indicates

the parity (programmable for odd or e ven parity) of the IDAT[15:0]

bus. If the IBUS8 register bit is low, the IPRTY signal indicates

parity over the IDAT[15:0] data bus. If IBUS8 is high, the IPRTY

signal indicates parity over the IDAT[7:0] data bus. A maskable

interrupt status is generated upon a parity error; no other actions

are taken. The IPRTY signal is sampled on the rising edge of

IFCLK and is considered valid only when one of the

IWRENB[4:1] signals so indicates.

The Egress Output Cell Interface clock (TFCLK) is used to write

words from the Egress Output Cell Interface. TFCL K must cycle

at a 52 MHz or lower instantaneous rate, but a high enough rate

to avoid a FIFO overflow. TSOC, TWRENB[4:1], TADDR[4:0],

TAVALID, TPRTY and TDAT[15:0] are updated on the rising edge

of TFCLK. TCA[4:1] is sampled on the rising edge of TFCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 26

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

TPOLL Input

TSOC Output

L2

M3

Function

The Egress Output Cell Interface POLL pin (TPOLL) is used to

control whether the Egress Output Cell Interface operates in

SCI-PHY Level 1 mode or SCI-PHY Le vel 2 mode. If TPOLL is

low, the Egress Output Cell Interface operates in SCI-PHY Level

1 mode (compatible with UTOPIA Level 1 cell-level

handshaking). This is a direct addressing mode using the

TCA[4:1] inputs and the TWRENB[4:1] outputs. If TPOLL is high,

the Egress Output Cell Interface operates in SCI-PHY Level 2

mode (compatible with UTOPIA Level 2). This is a polled

addressing mode using the TADDR[4:0], TAVALID and

TWRENB[1] outputs, and the TCA[1] input. If fewer than 32 PHY

devices are used, the TAVALID pin can be left unconnected.

Note: In direct addressing mode, the 4-PHY configuration is not

recommended. Instead the 4-PHY address-polling mode should

be used. This does not apply to the Single or Dual-PHY

configurations.

TPOLL is assumed to be a static input.

The Egress Output Cell Interface start of cell (TSOC) indication

signal marks the start of cell on the TDAT[15:0] data bus. When

TSOC is high, the first word of the cell structure is present on the

TDAT[15:0] bus. TSOC is updated on the rising edge of TFCLK.

TCA[4]

TCA[3]

TCA[2]

TCA[1]

I/O

P2

P3

N1

N4

The active polarity of these signals is programmable and defaults

to active high.

If the TPOLL pin is low, the ATLAS samples the state of the cell

availabl e signals of the PHY devices to examine whether or not

cells can be transferred to the PHY devices. The ATLAS will

complete the writing of an entire cell into the PHY device even if

the associated TCA[4:1] input is deasserted during the cell

transfer. Sampling of the TCA[4:1] signals resumes the cycle

after the last octet of a cell has been transferred.

If the TPOLL pin is high, the TCA[3:2] pins are redefined as

TADDR[4:3] and the TCA[4] pin is redefined as TAVALID.

Note, TCA[1] is an input only.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC AND FOR ITS CUSTOMERS’ INTERNAL USE 27

S/UNI-ATLAS

DATASHEET

PMC-1971154 ISSUE 7 S/UNI-ATM LAYER SOLUTION

PM7324 S/UNI-ATLAS

Pin Name Type Pin

No.

TCA[4:1]

(continued)

TWRENB[4]

TWRENB[3]

TWRENB[2]

TWRENB[1]

Output

N2

N3

M1

M2

Function

If the TPOLL pin is high, the ATLAS polls up to 32 PHYs using

the PHY address signals TADDR[4:0]. A PHY device being

addressed by TADDR[4:0] is expected to indicate whether or not

it has a complete cell available for transfer by driving the TCA[1]

during the clock cycle foll owing that in which it is addressed.

When a cell transfer is in progress, the ATLAS will not poll the

PHY device which is sending the cell and so PHY devices need

not support the cell availability indication during cell transfer. The

selection of a particular PHY device to which a cell will be written

is indicated by the state of TADDR[4:0] and when TWRENB[1] is

asserted.

Note, TCA[1] is an input only.