STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

PM7323

RCMP-200

ATM LAYER ROUTING CONTROL,

MONITORING AND POLICING 200 MBPS

ISSUE 2: NOVEMBER 1997

Proprietary and Confidential to PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

Proprietary and Confidential to PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

CONTENTS

1 FEATURES.............................................................................................. 1

2 APPLICATIONS....................................................................................... 4

3 REFERENCES......................................................................................... 5

4 APPLICATION EXAMPLES ..................................................................... 6

5 BLOCK DIAGRAM................................................................................... 9

6 DESCRIPTION....................................................................................... 10

7 PIN DIAGRAM ....................................................................................... 12

8 PIN DESCRIPTION (TOTAL 240) .......................................................... 13

9 FUNCTIONAL DESCRIPTION............................................................... 32

9.1 INPUT BUFFERING.................................................................... 32

9.2 VC IDENTIFICATION.................................................................. 33

9.2.1 SEARCH TABLE DATA STRUCTURE............................... 37

9.3 CELL PROCESSING .................................................................. 41

9.3.1 CONFIGURATION AND STATUS ..................................... 42

9.3.2 HEADER TRANSLATION................................................. 44

9.3.3 CELL ROUTING............................................................... 45

9.3.4 CELL RATE POLICING.................................................... 46

9.3.5 CELL COUNTING............................................................. 50

9.3.6 OPERATIONS, ADMINISTRATION AND MAINTENANCE

(OAM) CELL SERVICING ................................................. 52

9.3.7 FAULT MANAGEMENT CELLS ........................................ 55

Proprietary and Confidential to PMC-Sierra, Inc. i

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

9.3.8 PERFORMANCE MANAGEMENT CELLS....................... 56

9.3.9 ACTIVATION/DEACTIVATION CELLS.............................. 58

9.3.10RESOURCE MANAGEMENT CELLS .............................. 59

9.3.11BACKWARD OAM AND RM CELL IDENTIFICATION...... 59

9.4 MULTICASTING.......................................................................... 60

9.5 OUTPUT BUFFERING................................................................ 61

9.6 CONGESTION CONTROL.......................................................... 61

9.7 JTAG TEST ACCESS PORT INTERFACE................................... 62

9.8 MICROPROCESSOR INTERFACE............................................. 62

9.8.1 SRAM ACCESSES........................................................... 62

9.8.2 WRITING CELLS.............................................................. 63

9.8.3 READING CELLS............................................................. 64

9.8.4 NORMAL MODE REGISTER MEMORY MAP.................. 68

10 NORMAL MODE REGISTER DESCRIPTIONS..................................... 70

10.1 MASTER REGISTERS................................................................ 71

11 TEST FEATURES DESCRIPTION....................................................... 152

11.1 TEST MODE 0 DETAILS .......................................................... 154

11.2 JTA G TEST PORT..................................................................... 155

12 OPERATION........................................................................................ 158

12.1 SCI-PHY EXTENDED CELL FORMAT...................................... 158

12.2 SYNCHRONOUS STATIC RAMS.............................................. 160

12.3 OAM CELL FORMAT................................................................. 160

Proprietary and Confidential to PMC-Sierra, Inc. ii

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

12.3.1RECEIVED OAM CELLS................................................ 161

12.3.2GENERATED OAM CELLS ............................................ 163

12.4 VC IDENTIFICATION SEARCH ALGORITHM.......................... 164

12.4.1OVERVIEW..................................................................... 165

12.4.2INITIALIZATION.............................................................. 166

12.4.3ADDING A CONNECTION............................................. 166

12.4.4REMOVING A CONNECTION........................................ 171

12.4.5MULTICAST CONNECTIONS........................................ 172

12.5 JTAG SUPPORT........................................................................ 175

13 FUNCTIONAL TIMING......................................................................... 182

13.1 INPUT CELL INTERFACE......................................................... 182

13.2 OUTPUT CELL INTERFACE..................................................... 186

14 ABSOLUTE MAXIMUM RATINGS ....................................................... 188

15 D.C. CHARACTERISTICS................................................................... 189

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS...... 191

17 RCMP-200 TIMING CHARACTERISTICS ........................................... 197

18 MECHANICAL INFORMATION............................................................ 207

Proprietary and Confidential to PMC-Sierra, Inc. iii

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

LIST OF REGISTERS

REGISTER 0X00: MASTER RESET AND IDENTITY / LOAD METERS.......... 71

REGISTER 0X01: MASTER CONFIGURATION............................................... 73

REGISTER 0X02: MASTER INTERRUPT STATUS #1..................................... 76

REGISTER 0X03: MASTER INTERRUPT STATUS #2..................................... 81

REGISTER 0X04: MASTER INTERRUPT ENABLE #1.................................... 83

REGISTER 0X05: MASTER INTERRUPT ENABLE #2.................................... 85

REGISTER 0X06: MASTER CLOCK MONITOR.............................................. 86

REGISTER 0X07: LATEST ALARMED VIRTUAL CONNECTIONS ................. 88

REGISTER 0X08: INPUT CELL FIFO CONFIGURATION................................ 90

REGISTER 0X09: PHYSICAL LAYER CELL COUNT...................................... 93

REGISTER 0X0A: INPUT CELL COUNTER (LSB) ......................................... 95

REGISTER 0X0B: INPUT CELL COUNTER (MSB) ........................................ 96

REGISTER 0XC: INPUT POLLING CONFIGURATION.................................... 98

REGISTER 0X10: MICROPROCESSOR EXTRACT BUFFER CONTROL AND

STATUS................................................................................................ 100

REGISTER 0X11: MICROPROCESSOR INSERT BUFFER CONTROL AND

STATUS................................................................................................ 103

REGISTER 0X12: MICROPROCESSOR CELL DATA................................... 106

REGISTER 0X18: CELL PROCESSOR CONFIGURATION.......................... 108

REGISTER 0X19: PERFORMANCE MONITORING CONFIGURATION 1..... 112

REGISTER 0X1A: PERFORMANCE MONITORING CONFIGURATION 2..... 114

Proprietary and Confidential to PMC-Sierra, Inc. iv

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

REGISTER 0X1B: ABR CELL RATE POLICING CONFIGURATION.............. 116

REGISTER 0X1C: VBR/CBR CELL RATE POLICING CONFIGURATION ..... 118

REGISTER 0X1D: ROUTING CONFIGURATION........................................... 121

REGISTER 0X20: CRAM CONFIGURATION................................................ 125

REGISTER 0X21: EXTERNAL RAM ADDRESS (LSB)................................. 128

REGISTER 0X22: EXTERNAL RAM ADDRESS (MSB) AND ACCESS

CONTROL............................................................................................ 129

REGISTER 0X23: EXTERNAL RAM DATA (LSB).......................................... 131

REGISTER 0X24: EXTERNAL RAM DATA.................................................... 132

REGISTER 0X25: EXTERNAL RAM DATA (MSB)......................................... 133

REGISTER 0X26: MAXIMUM VC TABLE INDEX........................................... 134

REGISTER 0X27: SEARCH KEY CONSTRUCTION..................................... 135

REGISTER 0X28: FIELD A LOCATION AND LENGTH................................. 137

REGISTER 0X29: FIELD B LOCATION AND LENGTH................................. 139

REGISTER 0X30: COUNTER STATUS ......................................................... 141

REGISTER 0X31: VALID OAM CELL COUNT................................................ 143

REGISTER 0X32: ERRORED OAM CELL COUNT........................................ 145

REGISTER 0X33: INVALID CELL COUNT..................................................... 146

REGISTER 0X34: COUNT OF CELLS DROPPED DUE TO CONGESTION 147

REGISTER 0X38: OUTPUT CELL FIFO CONFIGURATION......................... 148

REGISTER 0X3A: OUTPUT CELL COUNTER (LSB) ................................... 150

REGISTER 0X3B: OUTPUT CELL COUNTER (MSB) .................................. 151

REGISTER 0X40: MASTER TEST ................................................................. 153

Proprietary and Confidential to PMC-Sierra, Inc. v

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

LIST OF FIGURES

FIGURE 1 - OC-3 SWITCH PORT APPLICATION............................................ 6

FIGURE 2 - DS-1 PHY ADDRESSING APPLICATION..................................... 6

FIGURE 3 - VC SEARCH KEY COMPOSITION ............................................. 34

FIGURE 4 - PARAMETERS OF PRIMARY KEY AND SECONDARY KEY ..... 35

FIGURE 5 - CONSTRUCTION OF SEARCH KEYS........................................ 36

FIGURE 6 - DATA STRUCTURES................................................................... 38

FIGURE 7 - EIGHT BIT WIDE CELL FORMAT.............................................. 159

FIGURE 8 -.................................................................................................... 168

FIGURE 9 -.................................................................................................... 168

FIGURE 10-.................................................................................................... 169

FIGURE 11-.................................................................................................... 170

FIGURE 12-.................................................................................................... 171

FIGURE 13-.................................................................................................... 173

FIGURE 14-.................................................................................................... 174

FIGURE 15- BOUNDARY SCAN ARCHITECTURE....................................... 176

FIGURE 16- TAP CONTROLLER FINITE STATE MACHINE.......................... 178

FIGURE 17- INPUT CELL MASTER INTERFACE (IPOLL=0)........................ 182

FIGURE 18- INPUT CELL INTERFACE ADDRESS LINE POLLING MASTER

CONFIGURATION (IPOLL=1) – EXAMPLE 1................................................. 183

FIGURE 19- INPUT CELL INTERFACE ADDRESS LINE POLLING MASTER

CONFIGURATION (IPOLL=1) – EXAMPLE 2................................................. 184

Proprietary and Confidential to PMC-Sierra, Inc. vi

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

FIGURE 20- OUTPUT CELL INTERFACE SINGLE-PHY SLAVE ( OTSEN=0)186

FIGURE 21- OUTPUT CELL INTERFACE SINGLE-PHY SLAVE ( OTSEN=1)187

FIGURE 22- MICROPROCESSOR INTERFACE READ TIMING................... 192

FIGURE 23- MICROPROCESSOR INTERFACE WRITE TIMING.................. 195

FIGURE 24- INPUT CELL INTERFACE MASTER (IPOLL=0) TIMING .......... 198

FIGURE 25- INPUT CELL INTERFACE MASTER (IPOLL=1) TIMING .......... 199

FIGURE 26- OUTPUT CELL INTERFACE SLAVE TIMING............................ 201

FIGURE 27- SYNCHRONOUS SRAM INTERFACE TIMING......................... 203

FIGURE 28- JTAG PORT INTERFACE TIMING ............................................. 205

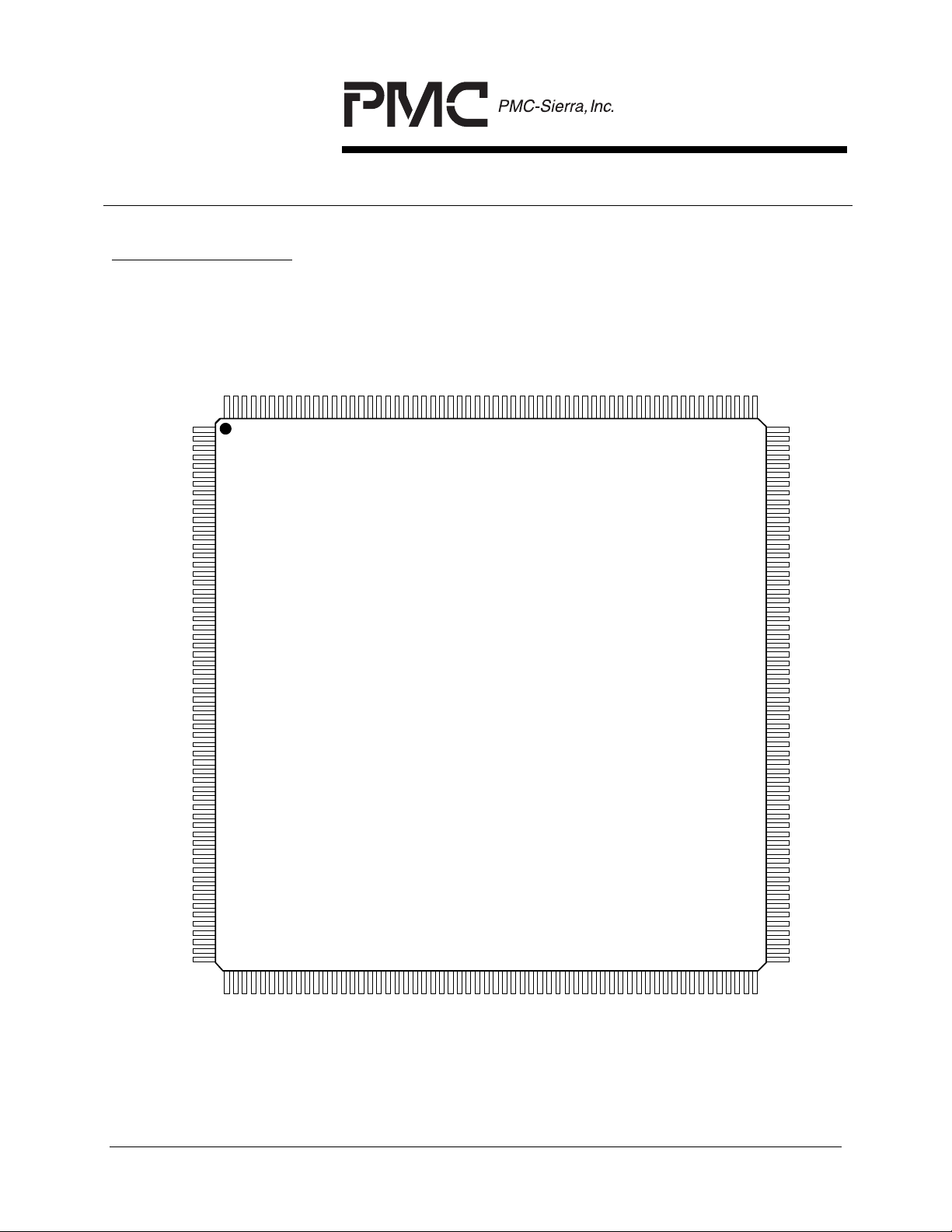

FIGURE 29- 240 PIN SLUGGED PLASTIC QUAD FLAT PACK (S SUFFIX): 207

Proprietary and Confidential to PMC-Sierra, Inc. vii

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

LIST OF TABLES

TABLE 1 - OUTPUT CELL INTERFACE SIGNALS (24)............................... 13

TABLE 2 - INPUT CELL INTERFACE SIGNALS (30)................................... 15

TABLE 3 - SYNCHRONOUS SRAM INTERFACE SIGNALS (70)................. 20

TABLE 4 - MICROPROCESSOR INTERFACE SIGNALS (30) ..................... 23

TABLE 5 - MISC. INTERFACE SIGNALS (66) .............................................. 26

TABLE 6 - VC TABLE RECORD.................................................................... 42

TABLE 7 -...................................................................................................... 43

TABLE 8 -...................................................................................................... 44

TABLE 9 -...................................................................................................... 48

TABLE 10 -...................................................................................................... 52

TABLE 11 -...................................................................................................... 54

TABLE 12 -...................................................................................................... 59

TABLE 13 -...................................................................................................... 60

TABLE 14 -...................................................................................................... 63

TABLE 15 -...................................................................................................... 65

TABLE 16 -...................................................................................................... 65

TABLE 17 -...................................................................................................... 67

TABLE 18 70

TABLE 19 -.................................................................................................... 154

TABLE 20 - INSTRUCTION REGISTER....................................................... 156

TABLE 21 - BOUNDARY SCAN REGISTER................................................. 157

Proprietary and Confidential to PMC-Sierra, Inc. viii

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

TABLE 22 -.................................................................................................... 160

TABLE 23 - RCMP-200 ABSOLUTE MAXIMUM RATINGS .......................... 188

TABLE 24 - RCMP-200 D.C. CHARACTERISTICS....................................... 189

TABLE 25 - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 22)

..................................................................................................... 191

TABLE 26 - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 23)

..................................................................................................... 194

TABLE 27 - INPUT CELL INTERFACE (FIGURE 24 AND FIGURE 25) ....... 197

TABLE 28 - OUTPUT CELL INTERFACE (FIGURE 26) ............................... 200

TABLE 29 - SYNCHRONOUS SRAM INTERFACE (FIGURE 27)................ 202

TABLE 30 - JTAG PORT INTERFACE (FIGURE 28)..................................... 204

Proprietary and Confidential to PMC-Sierra, Inc. ix

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

1

FEATURES

Monolithic single chip device which handles ATM switch Ingress VPI/VCI

•

address translation, cell appending, cell rate policing, counting, and OAM

requirements for 65,536 VCs (virtual circuits)

Instantaneous transfer rate of 200 Mbit/s supports a cell transfer rate of

•

0.355x106 cells/s (one STS-3c).

Concentrates the traffic from several PHY interfaces into one switch port.

•

8 bit PHY interface using direct addressing for up to 4 PHYs (compatible with

•

Utopia Level 1 cell-level handshake) and Multi-PHY addressing for up to 32

PHYs (Utopia Level 2 compatible).

8 bit extended cell format SCI-PHY (52 - 64 byte extended ATM cell with

•

prepend/postpend) interface at output to switch fabric.

Compatible with wide range of switching fabrics and traffic management

•

architectures including per VC or per PHY queuing.

Provides identification/tagging of RM cells to support adjunct processing

•

applications such as Virtual Source/Virtual Destination ABR service.

Supports logical multicast.

•

Flexible CAM-type cell identification which can use

•

arbitrary

VPI/VCI values

and/or cell appended bytes for identification.

Discards on command all low priority (high CLP bit) cells to relieve switch

•

congestion.

Can discard or tag the remainder of an AAL5 packet if a single cell in that

•

packet is discarded or tagged due to policing.

Includes a 16-bit FIFO buffered microprocessor bus interface for cell

•

extraction and insertion (including OAM), VC table access, control and status

monitoring, and configuration of the device.

Supports DMA access for cell extraction and insertion.

•

Proprietary and Confidential to PMC-Sierra, Inc. 1

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

Uses common synchronous SRAMs for maintaining per-VC information.

•

Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

•

PM7323 RCMP-200

200 MBPS

test purposes.

Provides a generic 16-bit microprocessor bus interface for configuration,

•

control and status monitoring.

Low power, 0.6 micron, +5 Volt CMOS technology.

•

240 copper slugged plastic quad flat pack (PQFP) package.

•

Policing

Policing is performed for adherence to peak cell rate (PCR), cell delay

•

variation (CDV), sustained cell rate (SCR) and burst tolerance (BT). Violating

cells can be noted, dropped or have CLP bits set to 1.

Policing performed by an approximation to the Generic Cell Rate Algorithm

•

(GCRA).

Two policing instantiations available per VC. The policed cell streams can be

•

any combination of user cells, OAM cells, Resource Management, high

priority cells or low priority cells.

Cell Counting

Counts maintained on a per VC basis include total low priority cells, total high

•

priority cells and cells violating the traffic contract.

Performance management counts are maintained for forward and reverse

•

flows on a per VC basis: lost cells, misinserted cells, BIP-16 errors and the

number of Severely Errored Cell Blocks (SECB).

Counts maintained for entire device include total cells input, total cells output,

•

OAM cells, cells discarded due to congestion, corrupted OAM cells, and cells

with unassigned/invalid VPI/VCIs.

Proprietary and Confidential to PMC-Sierra, Inc. 2

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

OAM Handling and Performance Monitoring

OAM performance monitoring for all VCs as described in ITU-T

•

Recommendation I.610, Bellcore TR-NWT-001248 and Bellcore GR-1113CORE.

Automatic OAM handling includes reception and generation of AIS, RDI,

•

Forward Monitoring and Backward Reporting cells.

Backward generated OAM cell identification/tagging provided to enable direct

•

extraction by Egress device.

Incoming OAM cells can be terminated or passed to the Output Cell Interface

•

and/or microprocessor.

Outgoing OAM cells sourced from automatic OAM generating circuitry, Input

•

Cell Interface or microprocessor.

Proprietary and Confidential to PMC-Sierra, Inc. 3

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

2

APPLICATIONS

ATM Hubs and Workgroup Switches

•

ATM Enterprise, Edge and Access Switches

•

Proprietary and Confidential to PMC-Sierra, Inc. 4

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

3

REFERENCES

•

•

ATM Forum - ATM User-Network Interface Specification, V3.0, October, 1993

ITU-T Recommendation I.361 - "B-ISDN ATM Layer Specification", March

1993

ITU-T Recommendation I.371 - "Traffic Control and Congestion Control in B-

•

ISDN", March 1993

ITU-T Recommendation I.610 - "B-ISDN Operation and Maintenance

•

Principles and Functions", Helsinki, March 1993.

Bell Communications Research - Broadband Switching System (BSS)

•

Generic Requirements, GR-1110-CORE, Issue 1, September 1994.

Bell Communications Research -Asynchronous Transfer Mode (ATM) and

•

ATM Adaptation Layer (AAL) Protocols, GR-1113-CORE, Issue 1, July 1994.

Bell Communications Research - Generic Requirements for Operations of

•

Broadband Switching Systems, TA-NWT-001248, Issue 2, October 1993.

IEEE 1149.1 - Standard Test Access Port and Boundary Scan Architecture,

•

May 21, 1990.

PMC-940212, ATM_SCI_PHY, "SATURN Compliant Interface For ATM

•

Devices", July 1994, Issue 2.

PMC-960338, “Asynchronous SRAM for RCMP-200”, April 1996, Issue 1.

•

ATM Forum/95-0013R9, Draft Version 3.0 of ATM Forum Traffic Management

•

Specification Version 4.0, October, 1995

Proprietary and Confidential to PMC-Sierra, Inc. 5

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

4

APPLICATION EXAMPLES

The RCMP-200 device is combined with up to 32 PHY devices to implement the

ingress direction an ATM switch port. Two ATM switch port applications are

shown in Figure 1 and Figure 2.

The RCMP-200 device accepts standard 53 byte cells through a SCI-PHY

interface and outputs cells with variable length pre-pends or post-pends through

an extended cell format SCI-PHY interface. The appendages added by the

RCMP-200 are used by the switch for routing. The HEC can optionally be

omitted. The combined pre-pend and post-pend length can vary from 0 to 10

bytes, with the cells correspondingly being 52 to 63 octets or 26 to 32 words.

Backward generated OAM cells and Resource Management cells are specially

labelled by overwriting an appended byte to allow these cells to be processed

and routed in the reverse direction.

The RCMP-200 utilizes external synchronous RAMs to store VPI/VCI translation

tables and per VPI/VCI switch-specific routing appendages, as well as per

VPI/VCI policing and performance monitoring information. All of this information

is stored in a single structure called the

VC table

.

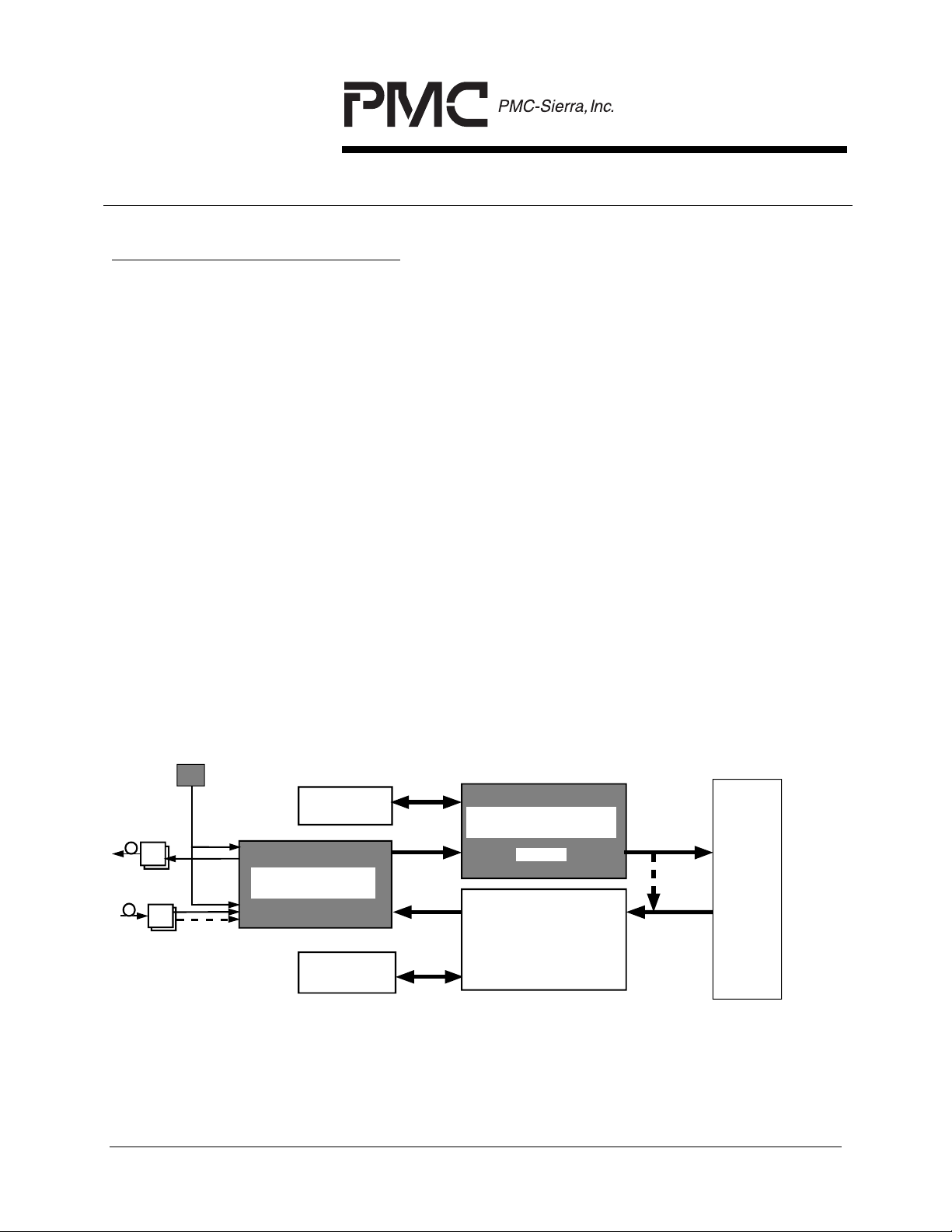

Figure 1 - OC-3 Switch Port Application

Ref.

Clock

E/O

O/E

19.44 MHz

TRCLK+/-

RRCLK+/-

RXD+/-

ALOS+/-

TXD+/-

PM5347 S/ UNI-PLUS

USER NETWORK INTERFACE

SONET/SD H

PER VC

PARAMETER

SRAM

OUTPUT

BUFFER

RAM

UTOPIA

Level 1/2

Interfa ce

ROUTING C ONTROL MONIT O RING AND

PER VC OR PER PHY TRAFFIC

SHAPING AND ABR RM CELL

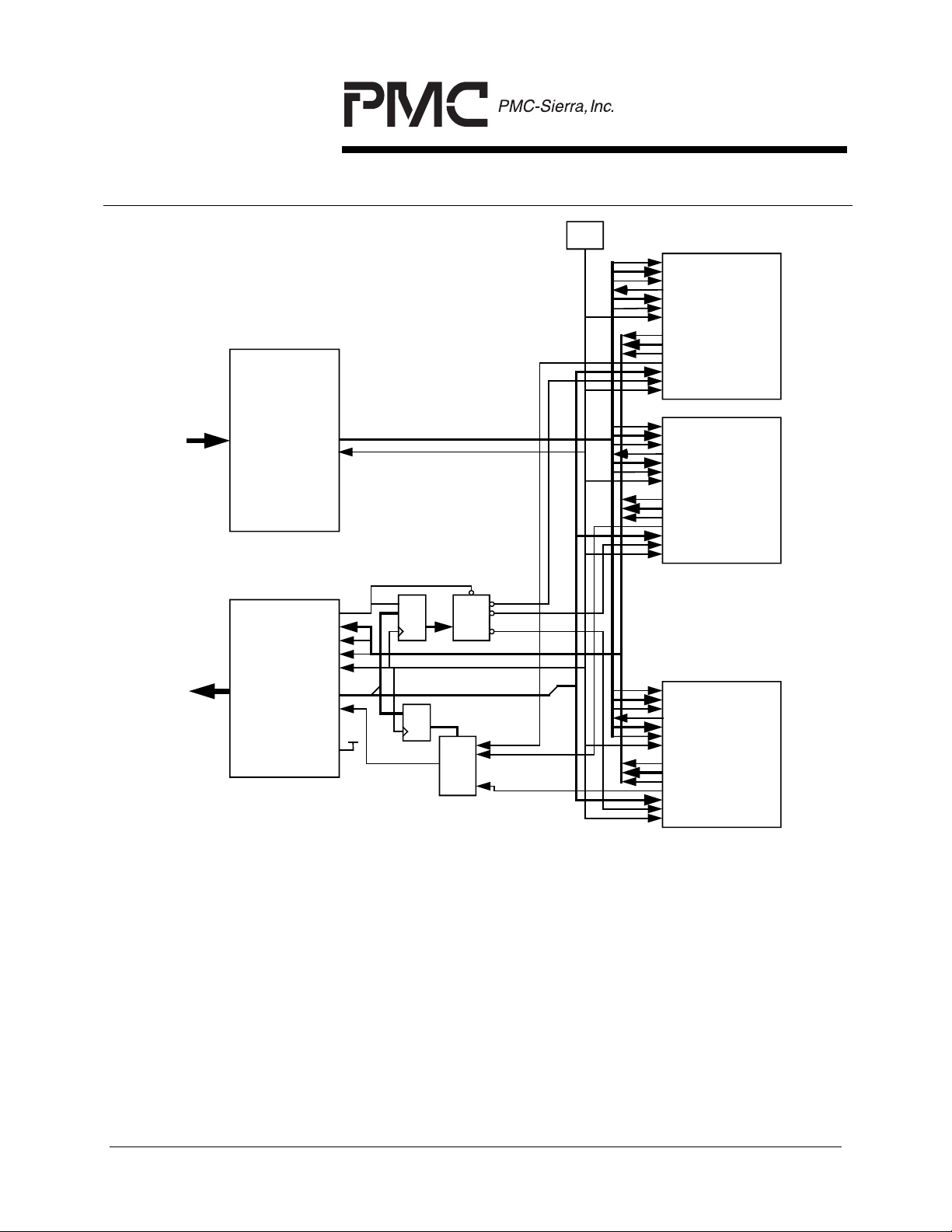

Figure 2 - DS-1 PHY Addressing Application

Proprietary and Confidential to PMC-Sierra, Inc. 6

and for its Customer’s Internal Use.

PM7323 RCMP-200

POLICING 200 Mbps

ING RESS

PROCESSING

EGRESS

Extended

SCI-PHY

Interface

OAM / RM

Cells

ATM

SWITCHING

FABRIC

STANDARD PRODUCT

PM7323 RCMP-200

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

200 MBPS

OSC

TSOC

TDAT [7 :0 ]

TXPRTY

TCAMPH

TWA[1:0]

TWRMPHB

TFCLK

S/UNI-MPH

Single-PHY

or M ulti-P H Y

interfa ce to

switch

EGRESS

DEVICE

RSOC

RDAT[7:0]

RXPRTY

RCAMPH

RRA[1 :0 ]

RRDMPHB

RFCLK

TSOC

TDAT[7:0]

TXPRTY

TCAMPH

TWA[1:0]

TWRMPHB

TFCLK

RSOC

RDAT[7:0]

RXPRTY

RCAMPH

RRA[1:0]

RRDMPHB

RFCLK

#1

S/UNI-MPH

#2

Single-PHY

interface to

switch

RCMP-200

IWRENB[1]

IDAT[7:0]

IPRTY[0]

ISOC

IFC LK

IAVALID

IADDR[4:0]

ICA[ 1]

IPOLL

4:2

load

D

E

3-to-N

decoder

Q

D

Q

N-to-1

mux

. . .

1:0

. . .

TSOC

TDAT[7:0]

TXPRTY

TCAMPH

TWA[1:0]

TWRMPHB

TFCLK

RSOC

RDAT[7:0]

RXPRTY

RCAMPH

RRA[1:0]

RRDMPHB

RFCLK

. . .

S/UNI-MPH

Figure 2 illustrates how up to 32 PHY Utopia Level 1 entities may be interfaced to

an RCMP-200. With a minimum amount of support circuitry (eg. a single PAL),

the PHY addressing mode of operation polls the PHY devices to determine the

next cell for transfer. In this example, a quad DS-1 ATM device, the S/UNI-MPH

(PM7344), provides the PHY transmission convergence function. Eight S/UNIMPH devices would be required to provide 32 DS-1 ports.

#N

The S/UNI-MPH supports PHY address polling by sampling the two least

significant address bits (RRA[1:0] and TWA[1:0]) and generating the cell

available status for the selected PHY entity. It also holds the last state of

Proprietary and Confidential to PMC-Sierra, Inc. 7

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

RRA[1:0] and TWA[1:0] before the assertion of RRDMPHB and TWRMPHB,

respectively, thus latching the PHY address resolved by the polling process. The

only support logic is that required to select between the S/UNI-MPH devices.

The IAVALID output is not required for this application.

In this application, the aggregate throughput is less than 6.144 Mbyte/s with 32

DS-1 ports; therefore, the clock oscillator frequency can be as low as 6.5 MHz.

To lower system cost further, asynchronous SRAM’s may also be used in this

application with the addition of external circuitry. Refer to the application note

PMC-960308 “Asynchronous SRAM for RCMP-200” for a detailed description.

Proprietary and Confidential to PMC-Sierra, Inc. 8

and for its Customer’s Internal Use.

STANDARD PRODUCT

PM7323 RCMP-200

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

200 MBPS

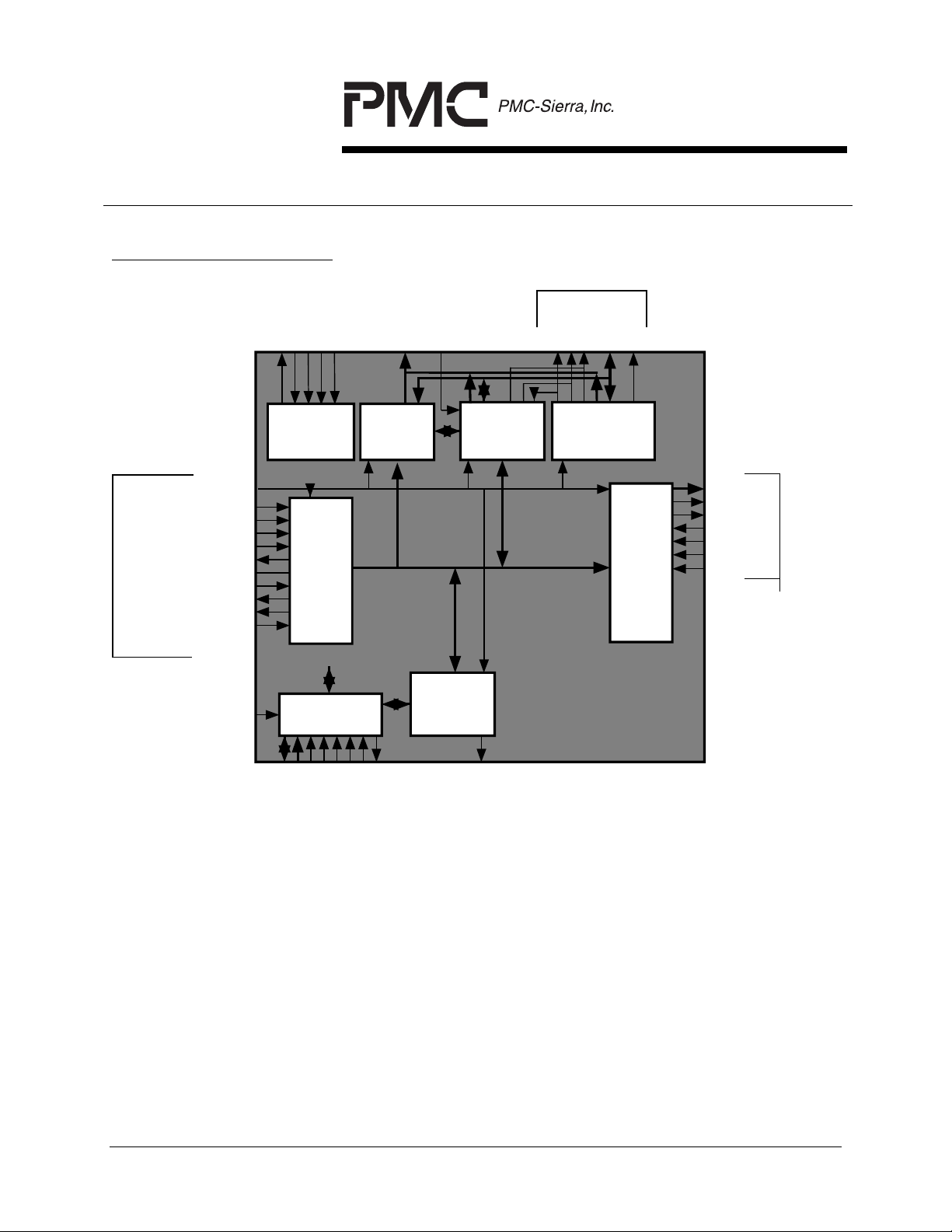

5

BLOCK DIAGRAM

IAV ALID/ICA[4]

IADDR[4:3]/ICA[3:2]

IADDR[2:0]/IW RENB[4:2]

1 or 2

SYSCLK

IDAT[7:0]

IPR TY

ISO C

IFCLK

ICA[1]

IWRENB[1]

IPO LL

ONESEC

S

I

O

K

M

D

T

TC

T

TD

JTAG Test

Access

Port

Input

FIFO

All Blocks

Microprocessor

Interface

B

T

S

TR

0]

SA[19:

External

RAM

Address

Lookup

G

N

O

C

Micro

Cell

Buffer

Cell

Processor

To External RAM

,

0]

RAM

SD[39:0]

SP[4:

Output

YB

BUS

FIFO

B

WB

OE

SADS

SR

S

Microprocessor

Arbitration

ODAT[7:0]

OPRTY

OSOC

OFCLK

OCA

ORDENB

OTSEN

face

ATM Cells)

Interface

Ut opia L e v e l

]

A[6:0

D[15:0]

ALE

CSB

B

T

TB

RDB

IN

WRB

RS

Q

E

R

D

Proprietary and Confidential to PMC-Sierra, Inc. 9

and for its Customer’s Internal Use.

(appended

SCI-PHY + Inter

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

6

DESCRIPTION

The PM7322 Routing Control, Monitoring and Policing 200 Mbps (RCMP-200)

device is a monolithic integrated circuit that implements ATM layer functions that

include fault and performance monitoring, header translation and cell rate

policing. The RCMP-200 is intended to be situated between a switch core and

the physical layer devices in the ingress direction. The RCMP-200 supports a

sustained aggregate throughput of 0.355x106 cells/s. The RCMP-200 uses

external SRAM to store per-VPI/VCI data structures. The device is capable of

supporting up to 65536 connections.

The Input Cell Interface can be connected to up to 32 physical layer devices

through a SCI-PHY compatible bus. The 53 byte ATM cell is encapsulated in a

data structure which can contain pre-pended or post-pended routing information.

Received cells are buffered in a four cell deep FIFO. All Physical Layer and

unassigned cells are discarded. For the remaining cells, a subset of ATM header

and appended bits is used as a search key to find the VC Table Record for the

virtual connection. If a connection is not provisioned and the search terminates

unsuccessfully as a result, the cell is discarded and a count of invalid cells is

incremented. If the search is successful, subsequent processing of the cell is

dependent on contents of the cell and configuration fields in the VC Table

Record.

The RCMP-200 performs header translation if so configured. The ATM header is

replaced by contents of fields in the VC Table Record for the connection. The VCI

contents are passed through transparently for VPCs. Appended bytes can be

replaced, added or removed.

If the RCMP-200 is the end point for a F4 or F5 OAM stream, the OAM cells are

dropped and processed. If the RCMP-200 is not the end point, the OAM cells

are passed to the Output Cell Interface with an optional copy passed to the

Microprocessor Cell Buffer. The reception of an AIS or RDI cell results in the

appropriate alarm. Upon the arrival of a Forward Monitoring or

Monitoring/Reporting cell, error counts are updated and a Backward Reporting

cell is optionally generated. Activate/Deactivate cells are passed to the

Microprocessor Cell Buffer for external processing. Continuity Check cells can

be generated if no user cells have been received in the latest 1.5 +/- 0.5 or 2.5

+/- 0.5 (default) seconds.

Proprietary and Confidential to PMC-Sierra, Inc. 10

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

Cell rate policing is supported through two instances of the Generic Cell Rate

Algorithm (GCRA) for each connection. Each cell that violates the traffic contract

can be tagged (CLP bit set high) or discarded. To allow full flexibility, each GCRA

instance can be programmed to police any combination of user cells, OAM cells,

Resource Management, high priority cells or low priority cells.

The RCMP-200 supports multicasting. A single received cell can result in an

arbitrary number of cells presented on the Output Cell Interface, each with its

own unique VPI/VCI value and appended bytes. The ATM cell payload is

duplicated without modification.

The Output Cell Interface can be connected to the switch core through an

extended cell format SCI-PHY compatible bus. Cells are stored in a four cell

deep FIFO until the downstream devices are ready to accept them. The details

of how cells are handled in this FIFO depends on the particular application of the

RCMP-200 and are presented in "Operational Modes" section.

The Microprocessor Interface is provided for device configuration, control and

monitoring by an external microprocessor. This interface provides access to the

external SRAM to allow creation of the data structure, configuration of individual

connections and monitoring of the connections. The Microprocessor Cell Buffer

gives access to the cell stream, either directly or through intervention by a DMA

controller. Programmed cell types can be routed to a microprocessor readable

sixteen cell FIFO. The microprocessor can send cells over the Output Cell

Interface.

The RCMP-200 is implemented in low power, 0.6 micron, +5 Volt CMOS

technology. It has TTL compatible inputs and outputs and is packaged in a 240

pin copper slugged plastic QFP package.

Proprietary and Confidential to PMC-Sierra, Inc. 11

and for its Customer’s Internal Use.

STANDARD PRODUCT

PM7323 RCMP-200

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

200 MBPS

7

PIN 1

VSS_DC

VSS_DC

VSS_DC

VSS_DC

VSS_DC

VSS_DC

VSS_DC

VSS_DC

VDD_DC

VSS_DC

VSS_DC

IAVALID/ICA[4]

IADDR[4]/ICA[3]

VDD_AC

VSS_AC

IADDR[3]/ICA[2]

IADDR[2]/IWRENB[4]

IADDR[1]/IWRENB[3]

VDD_DC

VSS_DC

IADDR[0]/IWRENB[2]

IWRENB[1]

VDD_DC

VDD_AC

VSS_AC

VDD_DC

VSS_DC

VDD_DC

VSS_DC

VDD_DC

VSS_DC

VDD_AC

VSS_AC

PIN 60

PIN DIAGRAM

The RCMP-200 is packaged in a 240 pin slugged plastic QFP package having a

body size of 32 mm by 32 mm and a pin pitch of 0.5 mm.

SA[10]

VSS_DC

VDD_DC

SOEB

SADSB

SRWB

PIN 181

PIN 180

NC

VSS_AC

VDD_AC

SA[9]

SA[8]

SA[7]

SA[6]

SA[5]

SA[4]

VSS_AC

VDD_AC

VSS_DC

VDD_DC

SA[3]

SA[2]

SA[1]

SA[0]

SD[15]

SD[14]

SD[13]

VDD_AC

VSS_AC

VSS_DC

VDD_DC

SD[12]

SD[11]

SD[10]

SD[9]

SD[8]

VSS_AC

VDD_AC

VSS_DC

VDD_DC

SYSCLK

NC

NC

NC

VSS_DC

VDD_DC

SP[1]

SD[7]

SD[6]

SD[5]

SD[4]

SD[3]

VSS_AC

VDD_AC

SD[2]

SD[1]

SD[0]

SP[0]

NC

VSS_DC

VDD_DC

OFCLK

VSS_DC

VDD_DC

CONG

OTSEN

NC

PIN 121

IDAT[7]

IDAT[6]

IDAT[5]

IDAT[4]

IDAT[3]

IDAT[2]

IDAT[1]

IDAT[0]

IPRTY

ISOC

ICA[1]

IPOLL

IFCLK

TCK

TMS

TDO

TRSTB

D[0]

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

SD[37]

VDD_AC

SD[34]

VDD_DC

SD[33]

SD[32]

SP[4]

SD[31]

SD[30]

VDD_AC

VSS_AC

SD[29]

SD[28]

SD[27]

SD[26]

VSS_DC

SD[25]

SD[24]

SP[3]

VDD_DC

VDD_AC

VSS_AC

SD[23]

SD[22]

SD[21]

SD[20]

SD[19]

SD[18]

SD[17]

VSS_AC

VSS_DC

VDD_AC

VDD_DC

SD[16]

SP[2]

SA[18]

SA[19]

SA[17]

SA[16]

SA[15]

VSS_AC

SA[14]

SA[13]

VDD_AC

SA[11]

SA[12]

VSS_AC

SD[36]

SD[35]

VSS_DC

VSS_DC

SD[39]

PIN 240

SD[38]

VDD_DC

NC

Pin 1 Index

PM7323

RCMP-200

TOP VIEW

TDI

A[0]

A[5]

A[4]

A[3]

A[2]

A[1]

VDD_DC

VSS_DC

ALE

RSTB

ONESEC

A[6]

D[8]

PIN 61

D[9]

D[10]

D[11]

VDD_AC

VSS_AC

VDD_DC

D[12]

VSS_DC

D[13]

D[14]

D[15]

INTB

DREQ

BUSYB

RDB

WRB

CSB

Proprietary and Confidential to PMC-Sierra, Inc. 12

and for its Customer’s Internal Use.

DNC

DNC

DNC

DNC

VDD_DC

VSS_DC

DNC

DNC

VSS_AC

VDD_AC

DNC

DNC

ODAT[6]

ODAT[7]

ODAT[5]

ODAT[4]

ODAT[3]

VDD_DC

VSS_AC

VDD_AC

VSS_DC

ODAT[1]

ODAT[2]

DNC

ODAT[0]

OSOC

OPRTY

OCA

ORDENB

VDD_DC

PIN 120

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

8

PIN DESCRIPTION (TOTAL 240)

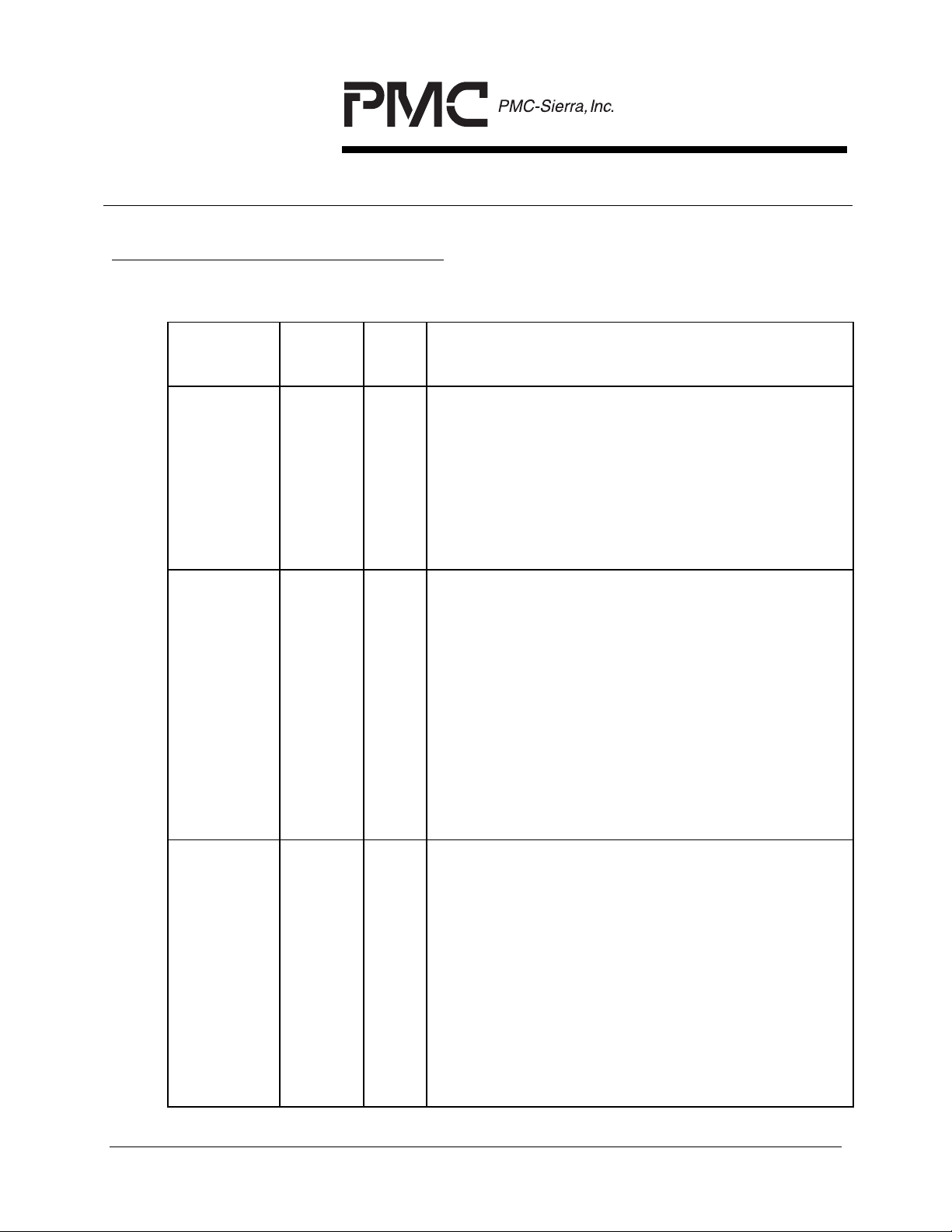

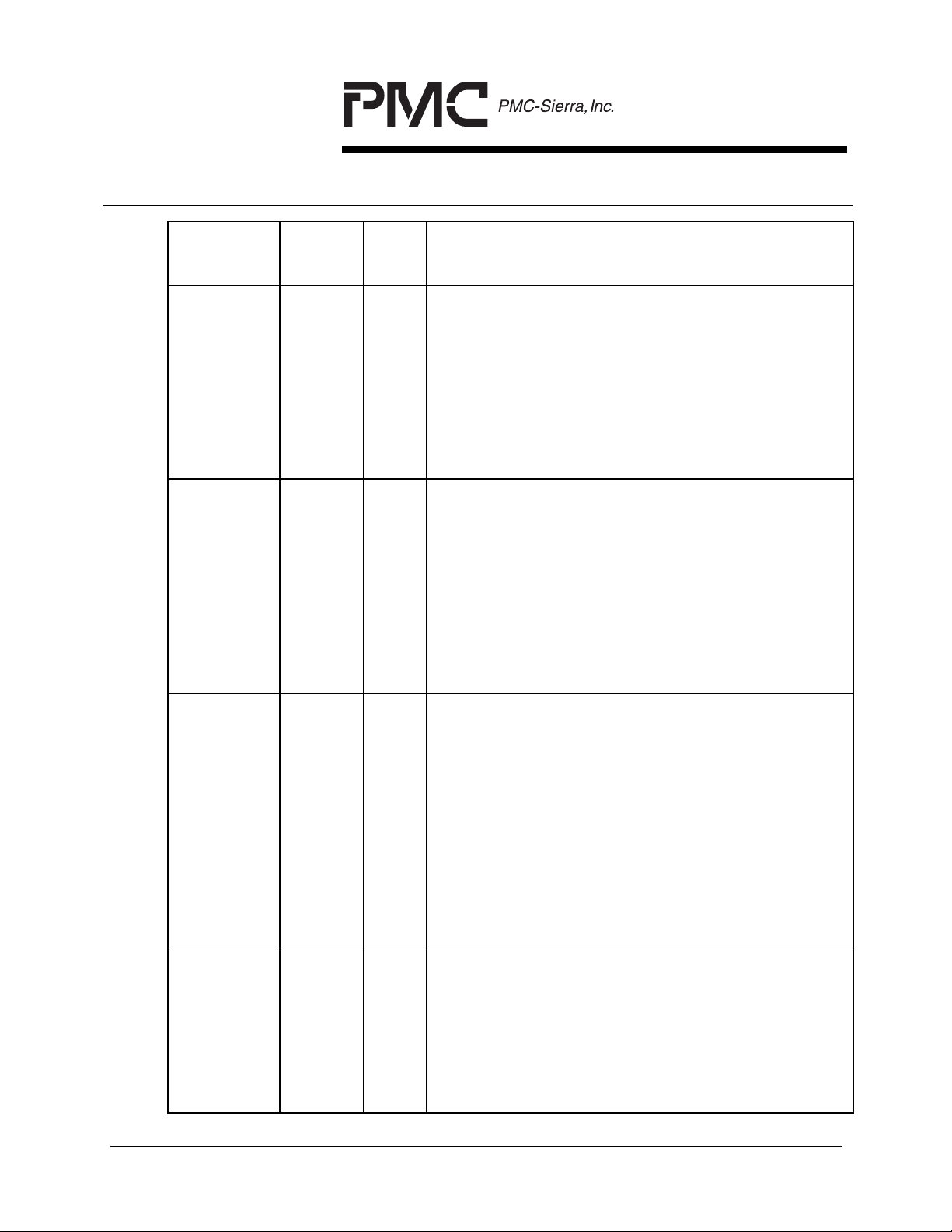

Table 1 - Output Cell Interface Signals (24)

Pin Name Type Pin

Feature

No.

OFCLK Input 126 The output FIFO clock (OFCLK) is used to read

words from the Output Cell Interface. OFCLK

must cycle at a 25 MHz or lower instantaneous

rate, but at a high enough rate to avoid FIFO

overflow. OSOC, OCA, OPRTY and ODAT[7:0]

are updated on the rising edge of OFCLK.

ORDENB is sampled using the rising edge of

OFCLK.

ORDENB Input 119 The active low read enable (ORDENB) signal is

used to indicate transfers from the Output Cell

Interface. When ORDENB is sampled low using

the rising edge of OFCLK, a word is read from

the internal synchronous FIFO and output on bus

ODAT[7:0]. When ORDENB is sampled high

using the rising edge of OFCLK, no read is

performed and outputs ODAT[7:0], OPRTY and

OSOC are tristated if the OTSEN input is high.

ORDENB must operate in conjunction with

OFCLK to access the FIFO at a high enough

instantaneous rate as to avoid FIFO overflows.

ODAT[0]

ODAT[1]

ODAT[2]

ODAT[3]

ODAT[4]

ODAT[5]

ODAT[6]

ODAT[7]

Tristate 114

113

112

107

106

105

104

103

The output cell data (ODAT[7:0]) bus carries the

ATM cell octets that are read from the output

FIFO. If the IBUS8 input is high, only ODAT[7:0]

carries cell octets. The ODAT[7:0] bus is updated

on the rising edge of OFCLK.

When the Output Cell Interface is configured for

tristate operation using the OTSEN input,

tristating of the ODAT[7:0] output bus is

controlled by the ORDENB input.

When OTSEN is low, the ODAT[7:0] bus is low

when no cell is being transferred.

Proprietary and Confidential to PMC-Sierra, Inc. 13

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

Pin Name Type Pin

Feature

No.

OPRTY Tristate 116 The output parity (OPRTY) signals indicate the

parity of the ODAT[7:0] bus. Odd or even parity

selection can be made using a register bit.

OPRTY is updated on the rising edge of OFCLK.

When the Output Cell Interface is configured for

tristate operation using the OTSEN input,

tristating of the OPRTY output bus is controlled

by the ORDENB input.

OSOC Tristate 117 The output start of cell (OSOC) signal marks the

start of cell on the ODAT[7:0] bus. When OSOC

is high, the first word of the cell structure is

present on the ODAT[7:0] stream. OSOC is

updated on the rising edge of OFCLK.

When the Output Cell Interface is configured for

tristate operation using the OTSEN input,

tristating of the OSOC output is controlled by the

ORDENB input.

OCA Output 118 The active polarity of this signal is programmable

and defaults to active high.

OCA indicates when a cell is available in the

output FIFO. When asserted, the OCA signal

indicates that the output FIFO has at least one

cell available to be read. The OCA signal is

deasserted when the output FIFO contains four

or zero words available for the current cell.

Selection is made using the OCALEVEL0 bit in

the Output FIFO Configuration register. OCA is

updated on the rising edge of OFCLK.

OTSEN Input 122 The tristate enable (OTSEN) signal allows tristate

control over the ODAT[7:0], OPRTY and OSOC

outputs. When OTSEN is high, the active low

read enable input, ORDENB, controls when the

ODAT[7:0], OPRTY and OSOC outputs are

driven. When OTSEN is low, the ODAT[7:0],

OPRTY and OSOC outputs are always driven.

Proprietary and Confidential to PMC-Sierra, Inc. 14

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

Pin Name Type Pin

Feature

No.

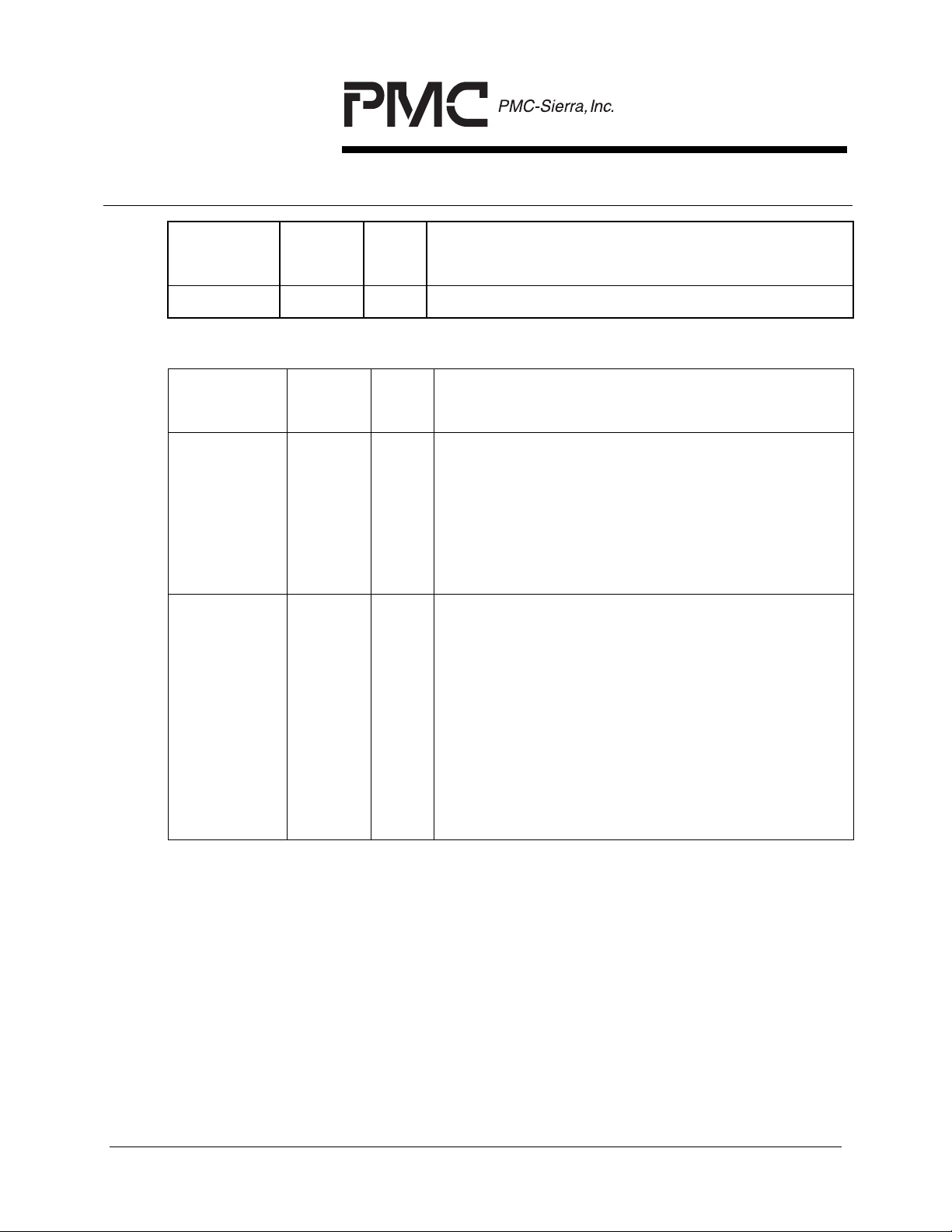

Table 2 - Input Cell Interface Signals (30)

Pin Name Type Pin

Feature

No.

IFCLK Input 41 The input FIFO clock (IFCLK) is used to write

words to the synchronous FIFO interface.

IFCLK must cycle at a 25 MHz or lower

instantaneous rate. ISOC, ICA[4:1], IPRTY and

IDAT[7:0] are sampled on the rising edge of

IFCLK. IWRENB[4:1], IADDR[4:0] and IAVALID

are updated on the rising edge of IFCLK.

IPOLL Input 35 The input polling select (IPOLL) pin determines

the method used to poll PHY devices.

If IPOLL is low, the IWRENB[4:1] and ICA[4:1]

signals are connected directly to up to four

single-PHY entities.

If IPOLL is high, polling using address lines is

used. The RCMP-200 uses the IADDR[4:0] and

IAVALID outputs to perform sequential polling of

the PHY devices to determine the next cell to

transfer.

Proprietary and Confidential to PMC-Sierra, Inc. 15

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

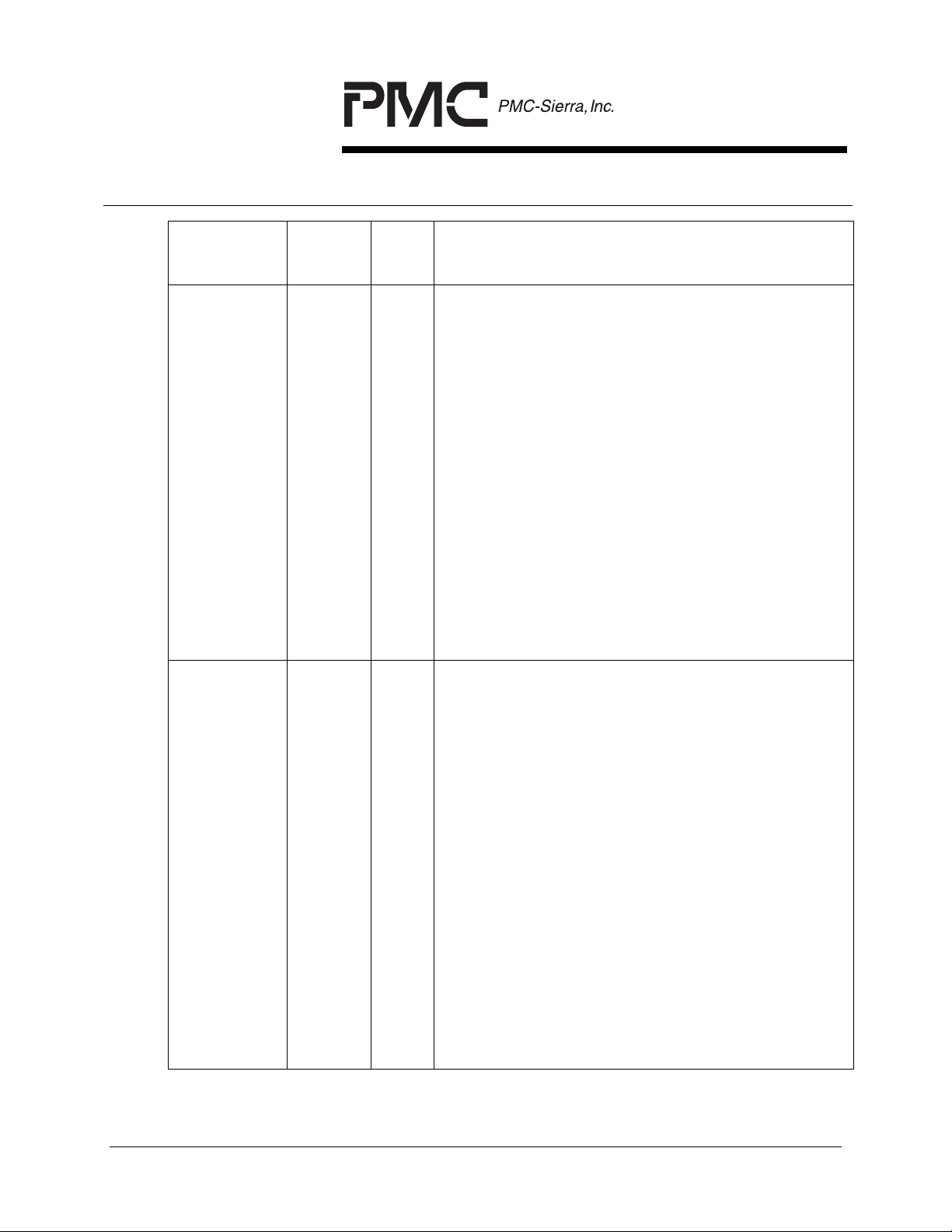

Pin Name Type Pin

No.

IWRENB[1]

IWRENB[2]

IWRENB[3]

IWRENB[4]

IADDR[4]

IADDR[3]

IADDR[2]

IADDR[1]

IADDR[0]

Output 34

33

30

29

I/O 24

27

29

30

33

Feature

The active low write enable (IWRENB[4:1])

inputs are used to initiate writes to the input

FIFO.

If the IPOLL input is low, the RCMP-200 asserts

one of the IWRENB[4:1] outputs to transfer a

cell from one of up to four PHY devices. A valid

word is expected on the IDAT[7:0] bus at the

second rising edge of IFCLK after one of the

enables is asserted low. When all of the enables

are high, no valid data is expected. The

IWRENB[4:1] outputs are updated on the rising

edge of IFCLK. See Figure 7.

If the IPOLL input is high, the IWRENB[4:2] pins

are redefined as IADDR[2:0]. The IWRENB[1]

pin is used to transfer all cells. The source PHY

is selected by the IADDR[4:0] signals.

If the IPOLL input is high, the IADDR[4:0] pins

are used for PHY addressing. If the IPOLL input

is low, the IADDR[4:0] pins are redefined as

ICA[3:2] and IWRENB[4:2].

If the IPOLL input is high, the IADDR[4:0]

signals are outputs and are used to address up

to 32 PHY devices for the purposes of polling

and selection for cell transfer. When conducting

polling, in order to avoid bus contention, the

RCMP-200 inserts gap cycles during which

IADDR[4:0] is set to 1F hex and IAVALID to logic

0. When this occurs, no PHY device should

drive ICA[1] during the following clock cycle.

Polling is performed in a incrementing sequential

order. The PHY device selected for transfer is

based on the IADDR[4:0] value present when

IWRENB[1] falls. The IADDR[4:0] bus is

updated on the rising edge of IFCLK.

Proprietary and Confidential to PMC-Sierra, Inc. 16

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

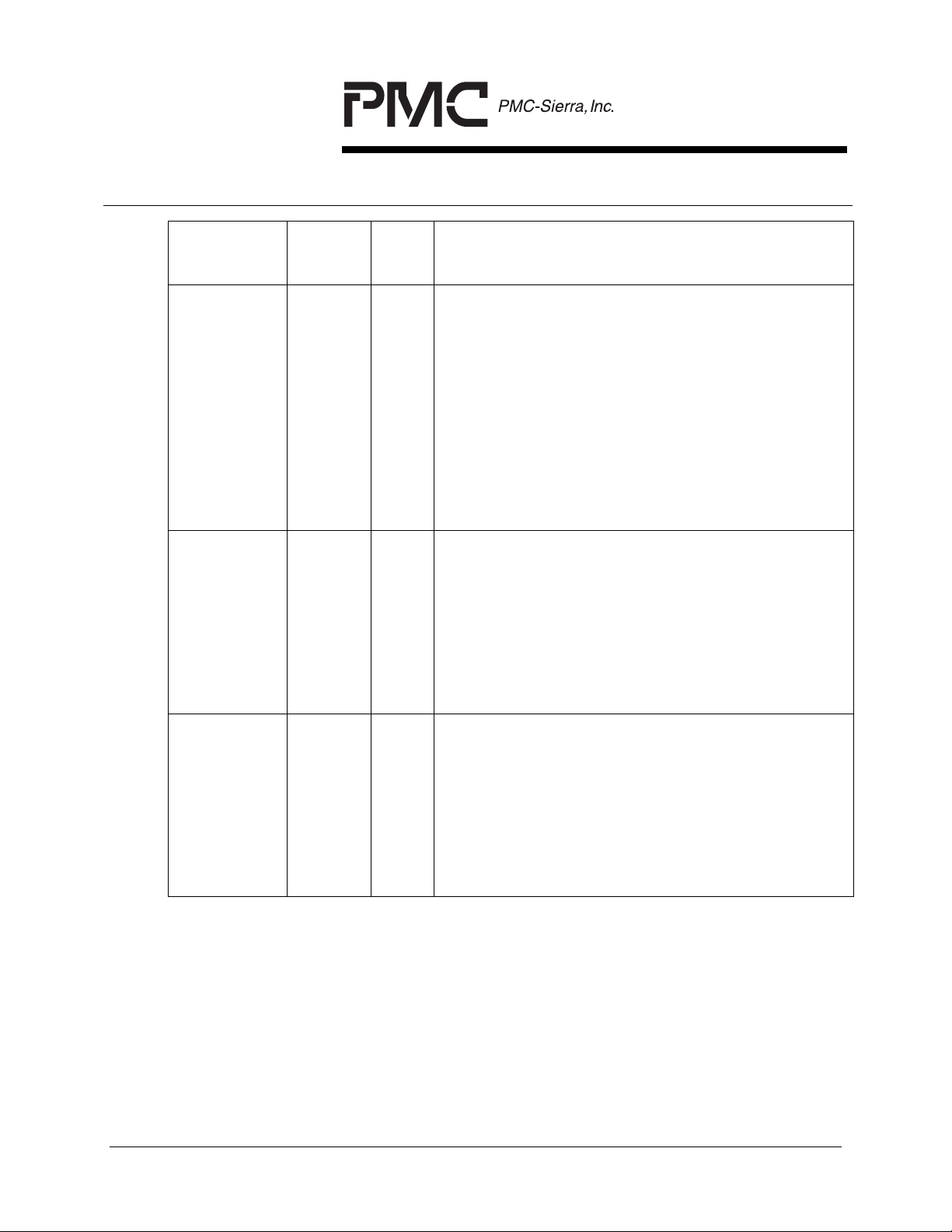

Pin Name Type Pin

Feature

No.

IAVALID I/O 23 If the IPOLL input is high, the PHY Address

Valid (IAVALID) pin is active. If the IPOLL input

is low, the IAVALID pin is redefined as ICA[4].

If the IPOLL input is high, the IAVALID pin

indicates that the IADDR[4:0] bus is outputting a

valid PHY address for polling purposes. When

this signal is deasserted, the IADDR[4:0] bus is

set to 1F hex.

IAVALID is not necessary when less than 32

PHY links are being polled.

IDAT[0]

IDAT[1]

IDAT[2]

IDAT[3]

IDAT[4]

IDAT[5]

IDAT[6]

IDAT[7]

Input 19

18

17

16

15

14

13

10

The input cell data (IDAT[7:0]) bus carries the

ATM cell octets that are written to the input

FIFO. The IDAT[7:0] bus is sampled on the

rising edge of IFCLK and is considered valid

only when one of the IWRENB[4:1] signals so

indicates.

IPRTY Input 21 The input parity (IPRTY) signals indicate the

parity of the IDAT[7:0] bus. Odd or even parity

selection can be made using a register. A

maskable interrupt status is generated upon a

parity error; no other actions are taken. IPRTY

is sampled on the rising edge of IFCLK and is

considered valid only when one of the

IWRENB[4:1] signals so indicates.

Proprietary and Confidential to PMC-Sierra, Inc. 17

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

Pin Name Type Pin

Feature

No.

ISOC Input 22 The input start of cell (ISOC) signal marks the

start of cell on the IDAT[7:0] bus. When ISOC is

high, the first word of the cell structure is present

on the IDAT[7:0] stream. It is not necessary for

ISOC asserted for each cell. An interrupt may

be generated if ISOC is high during any word

other than the first word of the cell structure.

ISOC is sampled on the rising edge of IFCLK

and is considered valid only when one of the

IWRENB[4:1] signals so indicates.

Proprietary and Confidential to PMC-Sierra, Inc. 18

and for its Customer’s Internal Use.

STANDARD PRODUCT

DATASHEET

PMC-960543 ISSUE 2 ROUTING CONTROL, MONITORING, & POLICING

PM7323 RCMP-200

200 MBPS

Pin Name Type Pin

No.

ICA[1]

ICA[2]

ICA[3]

ICA[4]

I/O 28

27

24

23

Feature

The active polarity of these signals is

programmable and defaults to active high.

If the IPOLL input is low, the RCMP-200 asserts

the appropriate IWRENB[4:1] signal in response

to a round-robin polling of the ICA[4:1] signals.

Once committed, the RCMP-200 will transfer an

entire cell from a single physical link before

servicing the next. The RCMP-200 will complete

the read of an entire cell even if the associated

ICA[4:1] input is deasserted during the cell.

Sampling of ICA[4:1] resumes the cycle after the

last octet of a cell has been transferred.

Note that ICA[1] is an input only.

If the IPOLL input is high, the ICA[3:2] pins are

redefined as IADDR[4:3] and the ICA[4] pin is

redefined as IAVALID.

If the IPOLL input is high, the RCMP-200 polls

up to 32 PHY devices using the PHY address

signals IADDR[4:0]. A PHY device being

addressed by IADDR[4:0] is expected to indicate

whether or not it has a complete cell available

for transfer by driving ICA[1] during the clock

cycle following that in which it is addressed.

(When a cell transfer is in progress, the RCMP200 will not poll the PHY device which is

sending the cell and so PHY devices need not

support cell availability indication during cell

transfer.) The selection of a particular PHY

device from which to transfer a cell is indicated

by the state of IADDR[4:0] when IWRENB[1]

falls.

Note that ICA[1] is an input only.

Proprietary and Confidential to PMC-Sierra, Inc. 19

and for its Customer’s Internal Use.

Loading...

Loading...