4 Link CES/DBCES AAL1 SAR

Preliminary

PM73124

AAL1gator™-4

FEATURES

• Supports four structured/unstructured

T1 or E1 links, or one unstructured

DS3, E3 or STS-1/STM-0 link over an

AAL1 CBR ATM network.

• Compliant with ATM Forum's CES (AFVTOA-0078), and ITU-T I.363.1.

• Supports up to 128 VCs.

• Supports n x 64 (consecutive

channels) and m x 64 (nonconsecutive channels) structured data

format with channel associated

signaling (CAS) support.

• Internal E1/T1 clock synthesizers

provided for each line which can be

controlled via internal synchronous

residual time stamp (SRTS) or an

internal programmable weighted

moving average adaptive cl ock in g

algorithm in unstructured mode. Clock

synthesizers can also be controlled

externally to provide customization of

SRTS or adaptive clocking methods.

• Provides transparent transmission of

CCS and CAS and terminatio n of CAS

signaling.

• Compliant with ATM Forum's Dynamic

Bandwidth Circuit Emulation Service

(DBCES) AF-VTOA-0085. Supports

idle channel detection via processor

intervention, CAS signaling, or data

pattern detection. Provides idle

channel indication on a per chan nel

basis.

• Supports AAL0 mode, selectable on a

per VC basis.

• Provides transmit and receive buffers

which can be used for OAM cells as

well as any other user-generated cells

such as AAL5 cells for ATM signaling.

LINE INTERFACE

• Supports the following flexible line

interfaces:

• Four individual T1 or E1 lines.

• One H-MVIP line at 8 MHz.

• One unstructured DS3, E3 or STS-

1/STM-0 line.

• Provides lineside loopback support on

a per channel basis.

UTOPIA INTERFACE

• Supports 52 MHz, 8/16-bit Level 2,

Multi-Phy Mode (MPHY) with parity, 8/

16-bit Level 1, SPHY and 8-bit L evel 1,

ATM Master modes.

• Provides an optional 8/16-bit AnyPHY™ slave interface.

• Provides a three cell FIFO for UTOPIA

loopback support on a per VC ba si s or

a global basis.

TRANSMIT SECTION

• Provides individually enabled per-VC

data and signaling conditioning in the

transmit cell direction and per DS0

data and signaling conditioning in the

transmit line direction.

• Provides per-VC configuration of time

slots allocated, CAS support, partial

cell size, data and signaling

conditioning, ATM Cell header

definition.

• Generates AAL1 sequence numb ers ,

pointers and SRTS values in

accordance with ITU-T I.363.1.

Multicast connections are supported.

• Provides a patented f rame based

calendar queue service algorithm with

anti-clumping add-queue mechanism

that produces minimal CDV. In

unstructured mode uses non-frame

based scheduling to optimize CDV.

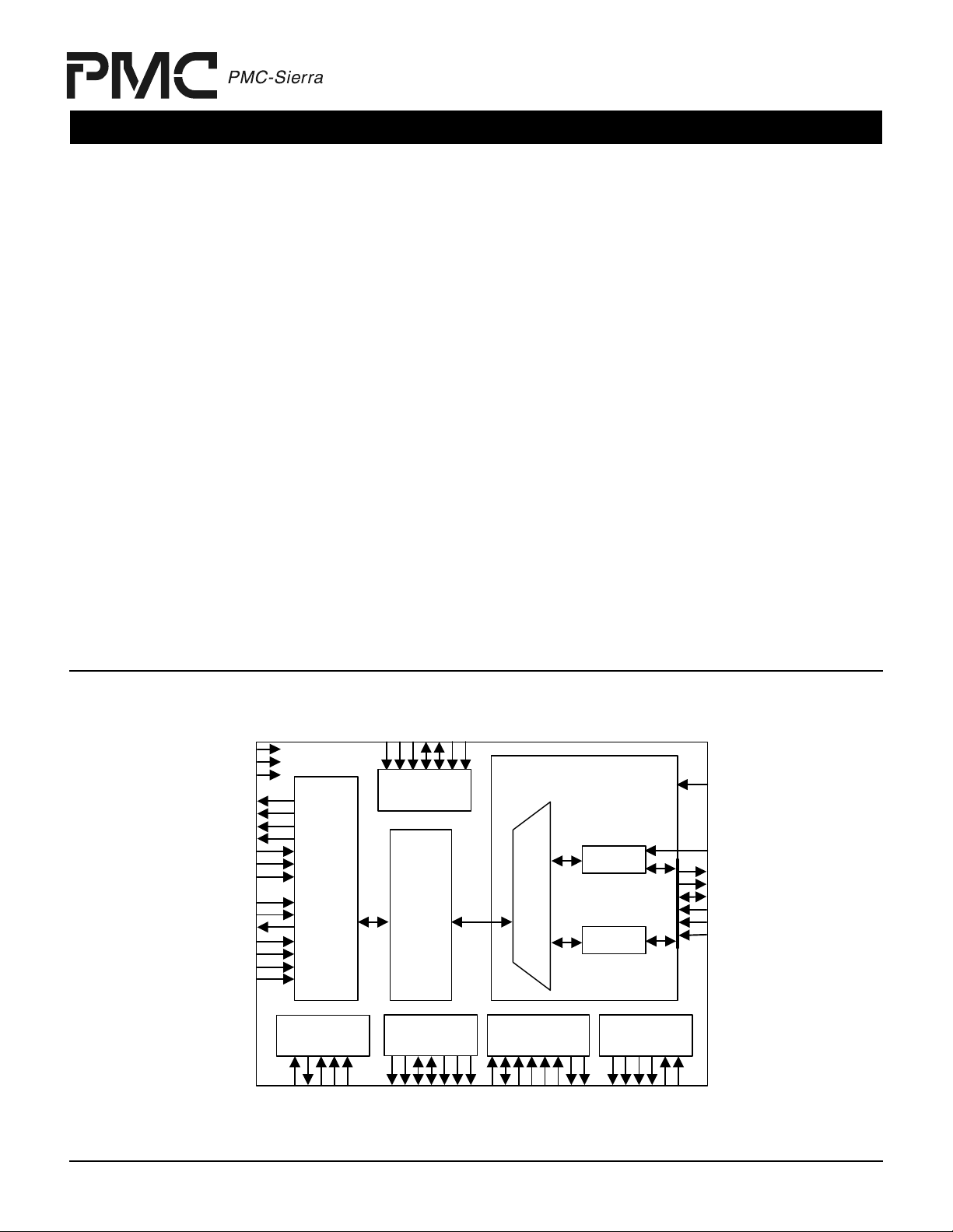

BLOCK DIAGRAM

SCAN_ENB

SCAN_MODEB

TATM_DATA[15:0]

TATM_PAR

TATM_ENB

TATM_SOC

TATM_CLAV

TATM_CLK

RPHY_ADD[4:0]

RATM_DATA[15:0]

RATM_PAR

RATM_ENB

RATM_SOC

RATM_CLAV

RATM_CLK

TPHY_ADD[4:0]

RSTB

UTOPIA

Interface

JTAG

TDO

TRST

SYSCLK

TL_CLK_OE

TL_CLK[3:0]

RL_CLK[3:0]

CRL_CLK

NCLK

Clock

MUX

4

A1SP

RAM

Interface

TDI

TCK

TMS

RAM_D[15:0]

RAM_A[16:0]

RAM_ADSCB

CTL_CLK

Line Interface

4

H-MVIP

4

4

Direct

Mode

Processor Interface

ALE

CSB

RDB

WRB

A[19:0]

RAM_CSB

RAM_PAR[1:0]

RAM_WEB[1:0]

D[15:0]

RAM_OEB

INTB

ACKB

4

4

External Clock

Interface

SRTS_STB

ADAP_STB

GC_DOUT[3:0]

CGC_LINE[3:0]

LINE_MODE

F0B

TL_DATA[3:0]

TL_SYNC[3:0]

TL_SIG[3:0]

RL_DATA[3:0]

RL_SYNC[3:0]

RL_SIG[3:0]

CGC_VALID

CGC_SER_D

PMC-1991273 (P2) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE Copyright PMC-Sierra, Inc. 2001

4 Link CES/DBCES AAL1 SAR

Preliminary PM73124 AAL1gator™-4

• Queues are added by making entries

into an add queue FIFO to minimize

queue activation overhead.

RECEIVE SECTION

• Provides per-VC configuration of time

slots allocated, parti al cell size,

sequence number processing options,

cell delay variation tolerance buffer

depth, maximum buffer depth.

• Supports Fast Sequence Number

processing and Robust Sequence

Number processing.

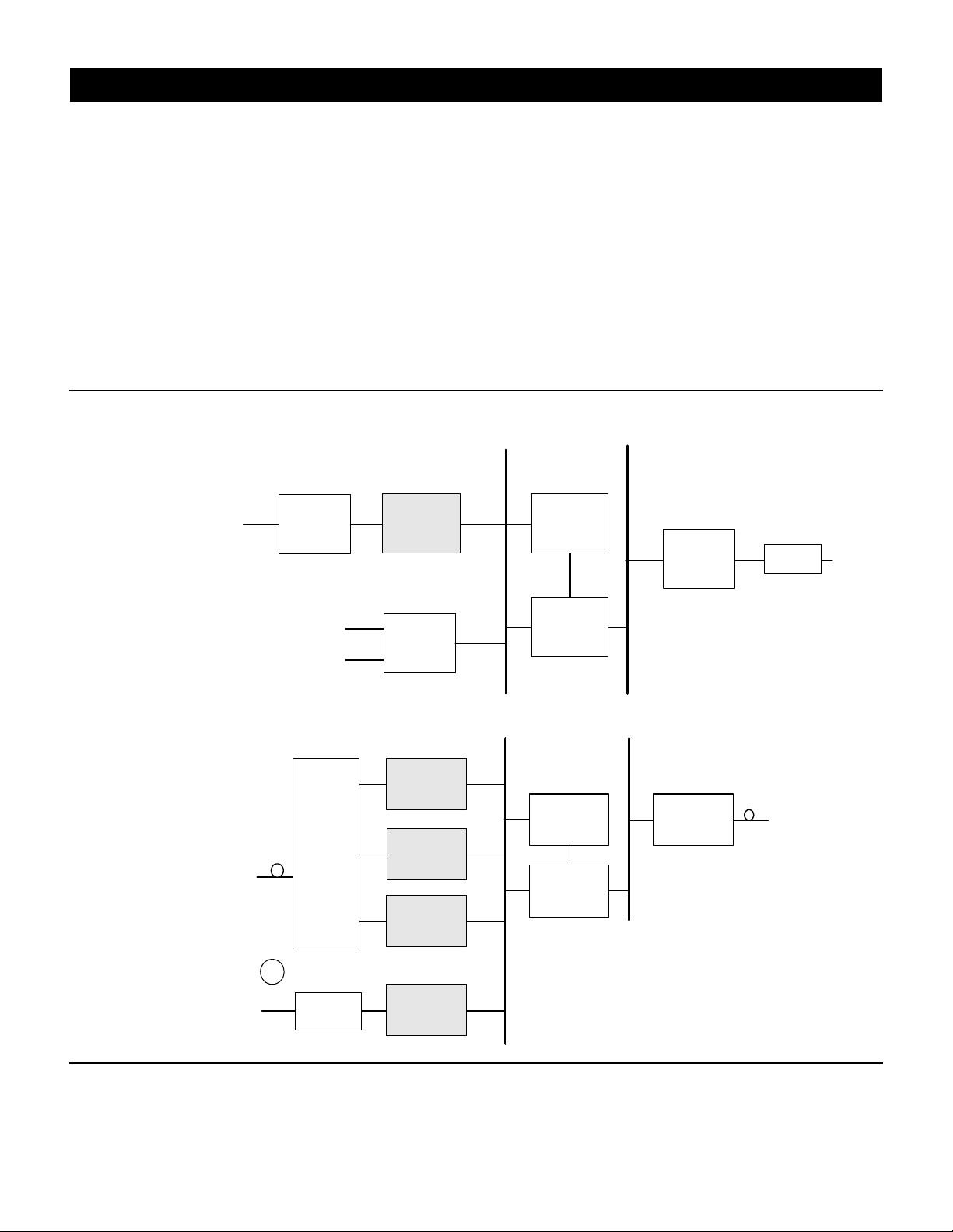

TYPICAL APPLICATIONS

INTEGRATED ACCESS DEVICE

PM4354

T1/E1 x 4

COMET-

QUAD

GENERAL

• Provides a microprocessor interface

for configuration, management, and

statistics gathering.

• Provides single maskable, opencollector interrupt with ma ste r in terrupt

register to facilitate processing for

AAL1, RAM and UTOPIA exceptions.

• Provides multiple counters in the Cell

Transmit and Receive directions as

required by the ATM Forum's CES-IS

2.0 MIB.

• Provides a seamless interface to an

external 128K x 16(18) (10 ns)

Synchronous SRAM or ZBT RAM.

UTOPIA L2/

Any-PHY

PM73124

AAL1gator-4

PM7329

S/UNI-APEX-

1K800

• Low-power 2.5V CMOS with 3.3V, 5V

tolerant I/O.

• 324-pin plastic ball grid array (PBGA)

package.

• Pin compatible with PM73123

AAL1gator-8.

APPLICATIONS

• Integrated Access Device.

• ATM Optical Networking Unit (ONU),

ATM Passive Optical Network (APON).

• Local Multipoint Distribution System

(LMDS).

• Unstructured DS-3 over ATM.

UTOPIA L2

PM7347

S/UNI-JET

DS3 LIU

Ethernet

UNSTRUCTURED DS3 OVER ATM

PM5342

SPECTRA-

OR

Video

155

DS3 LIU

ATM

Interworking

Function,

AAL5 SAR

PM73124

AAL1gator-4

PM73124

AAL1gator-4

PM73124

AAL1gator-4

PM73124

AAL1gator-4

UTOPIA L2/

Any-PHY

PM7328

S/UNI-

ATLAS-

1K800

PM7329

S/UNI-APEX-

1K800

PM7328

S/UNI-ATLAS-

1K800

UTOPIA L2

PM5384

S/UNI-1x155

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

PMC-1991273 (P2)

Copyright PMC-Sierra, Inc. 2001.

All rights reserved.

August 2001.

S/UNI is a registered trademark and

AAL1gator-4, COMET-QUAD, AnyPHY, SPECTRA-155, and

PMC-Sierra are trademarks of PMCSierra, Inc.

Loading...

Loading...