PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

PM6541

E1XC-EVBD

E1XC EVALUATION DAUGHTERBOARD

ISSUE 1: DECEMBER 1997

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

CONTENTS

1 OVERVIEW...............................................................................................1

2 FUNCTIONAL DESCRIPTION.................................................................2

2.1 BLOCK DIAGRAM.........................................................................2

2.2 BUS TRANSCEIVERS...................................................................2

2.3 DECODE LOGIC ...........................................................................3

2.4 DIP SWITCHES.............................................................................3

2.5 CLOCK DPLL.................................................................................3

2.6 OSCILLATORS ..............................................................................3

2.7 E1XC DEVICES.............................................................................4

2.8 "CSU" CONNECTION BLOCKS....................................................4

2.9 TRANSMIT/RECEIVE INTERFACE...............................................5

3 INTERFACE DESCRIPTION....................................................................6

3.1 EDGE CONNECTOR INTERFACE................................................6

3.2 HEADER CONNECTIONS.............................................................7

3.2.1 EXTERNAL SIGNAL HEADER...........................................8

3.2.2 DPLL HEADER...................................................................8

3.2.3 E1XC HEADERS ................................................................9

3.2.4 PROTOTYPE CHIP SELECT HEADER............................10

3.3 DIP SWITCHES...........................................................................11

4 PHYSICAL DESCRIPTION ....................................................................12

4.1 CHARACTERISTICS...................................................................12

4.2 LAYOUT.......................................................................................13

i

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

5 D.C. CHARACTERISTICS......................................................................14

6 IMPLEMENTATION DESCRIPTION.......................................................15

6.1 BUS TRANSCEIVERS.................................................................15

6.2 DECODE LOGIC .........................................................................16

6.3 CLOCK PLL AND DIP SWITCHES..............................................18

6.4 E1XC ...........................................................................................22

6.5 "CSU" DIPS AND JUMPERS.......................................................22

6.6 TRANSMIT/RECEIVE INTERFACES...........................................24

7 E1XC DAUGHTERBOARD FIRMWARE DESCRIPTION.......................25

8 STOCK LIST...........................................................................................35

9 REFERENCES.......................................................................................41

APPENDIX 1: COMPONENT PLACEMENT DIAGRAM....................................42

APPENDIX 2: SCHEMATICS ............................................................................43

ii

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

1 OVERVIEW

The PM6541 E1XC EVBD evaluation daughterboard allows for the test, evaluation

and demonstration of the PMC PM6341 E1XC device. It is also compatible with the

PM4341 T1XC device. This daughterboard can be used standalone with up to two

E1XC devices but has been especially designed to mate with the PMC PM1501

EVMB evaluation motherboard to form a complete evaluation system. All required

decoding logic is provided on the E1XC EVBD daughterboard to give the EVMB

direct access to all registers of both E1XC devices.

All of the principal connections to both devices have been brought out to header

strips for convenient test access. E-1 digital interfaces are provided on a header

strip and BNC or mini-bantam connectors are provided for E-1 analog signals. Both

75 Ω and 120 Ω interfaces are provided. The backplane interfaces of each device

are accessible through header strips and the devices can be interconnected back to

back, effectively creating a jitter-attenuating format converter by dropping in shorting

connectors into specific DIP sockets.

Clocks for the backplane are provided by a T1/CEPT digital trunk DPLL which

provides a synchronized 1.544 MHz, 2.048 MHz, or 4.096 MHz signal. The PLL can

be easily bypassed to allow direct drive of the backplane with an appropriate

oscillator. A prototype area has been provided for breadboarding more complex

applications.

The E1XC EVBD evaluation daughterboard is configured, monitored, and powered

through an edge connector that is designed to mate with the EVMB evaluation

motherboard

1

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

2 FUNCTIONAL DESCRIPTION

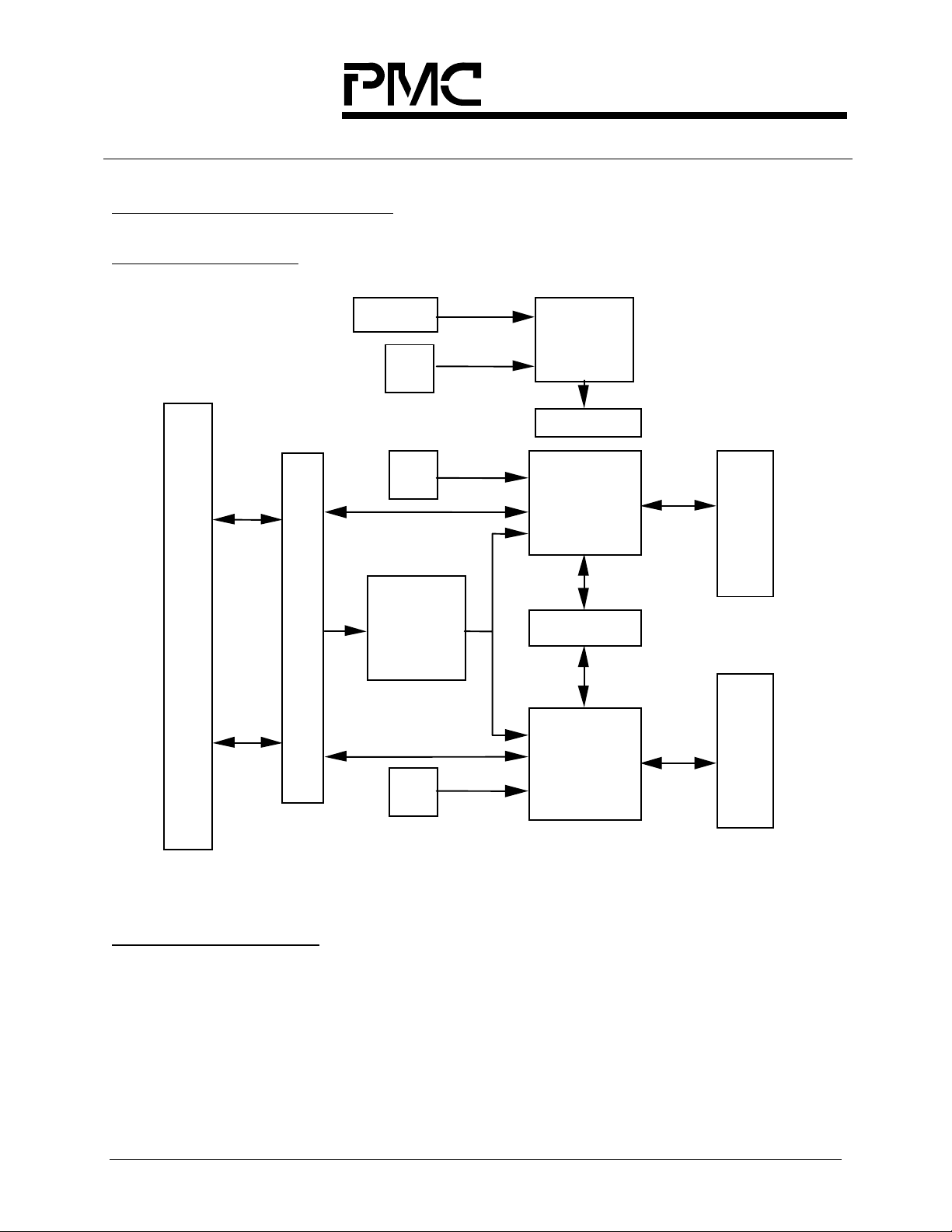

2.1 Block Diagram

DIP Sw.

Clock/PLL

Osc

Clock Hdr

96 Pin Male DIN Connector

Bus Transceivers

Osc

E1XC

Decode

Headers

Logic

E1XC

West

Osc

Figure 1: Block Diagram

East Tx / Rx

Interface

East

West Tx / Rx

Interface

2.2 Bus T ransceivers

Bus transceivers are provided at the connector interface to prevent excessive

loading of the 68HC11 on the EVMB evaluation motherboard. In addition they

provide some measure of isolation for the daughterboard and protection for other

external signals such as the EXTCLK and EXTFP inputs.

2

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

2.3 Decode Logic

Decode logic is provided on the daughterboard to give memory mapped access to

all of the registers within both E1XCs. Registers within the "east" E1XC are

accessible starting at address C000H. Registers within the "west" E1XC are

accessible starting at address C100H. Additional chip selects are provided for

addresses C200H-C2FFH and C300H-C3FFH for use on the prototype area.

2.4 DIP Switches

The DIP switch settings control the operational modes of the MT8940 DPLL device

that is used to generate the backplane clock. Access to the enable inputs for the

various clock outputs is also provided through these switches.

2.5 Clock DPLL

The MT8940 T1/CEPT Digital Trunk DPLL can provide a number of different clocks

with different methods of synchronization, depending upon its mode setting, which

can be used to drive the backplane interface of the E1XCs. The device can output

1.544 MHz, 2.048 MHz, and 4.096 MHz clocks in true or complement format. The

DPLL can be allowed to free-run or it can be synchronized to the receive frame

pulses of either E1XC. PLL control is accomplished with the DIP switches

connected to the inputs.

2.6 Oscillators

Up to four oscillators can be used on the E1XC EVBD daughterboard depending

upon the choice of configuration. The E1XC devices require a 49.152 MHz clock if

all of the device's features are to be utilized. Although two oscillator sockets are

provided, only a single oscillator is necessary if two E1XC devices are used. The

insertion of a jumper (J25) will join the two E1XC XCLK inputs together to allow the

single clock to drive both devices. If a T1XC device is used in place of one of the

E1XC devices then the jumper must be removed to isolate each clock line and a

37.056 MHz oscillator is used to drive the T1XC XCLK input.

The MT8940 DPLL device requires two oscillators to drive internal DPLLs, one at

12.355 MHz, and the other at 16.384 MHz. If the MT8940 is removed from the

daughterboard, then these oscillators can be replaced with ones directly compatible

with the backplane rate. Each oscillator output is directly accessible at header pins,

allowing connections to be made by connecting jumpers to the E1XC devices.

3

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

2.7 E1XC Devices

Up to two E1XC devices can be placed on the daughterboard at a time. Each

device runs independent of the other, except when explicit connections are made

through the header strips (i.e. when configured as a jitter attenuating format

converter). All internal registers are individually accessible and each device has

been set up with individual receiver, transmitter and backplane access through

headers and connectors. A full description of the E1XC device is beyond the scope

of this document. For more information, refer to the PM6341 E1XC datasheet.

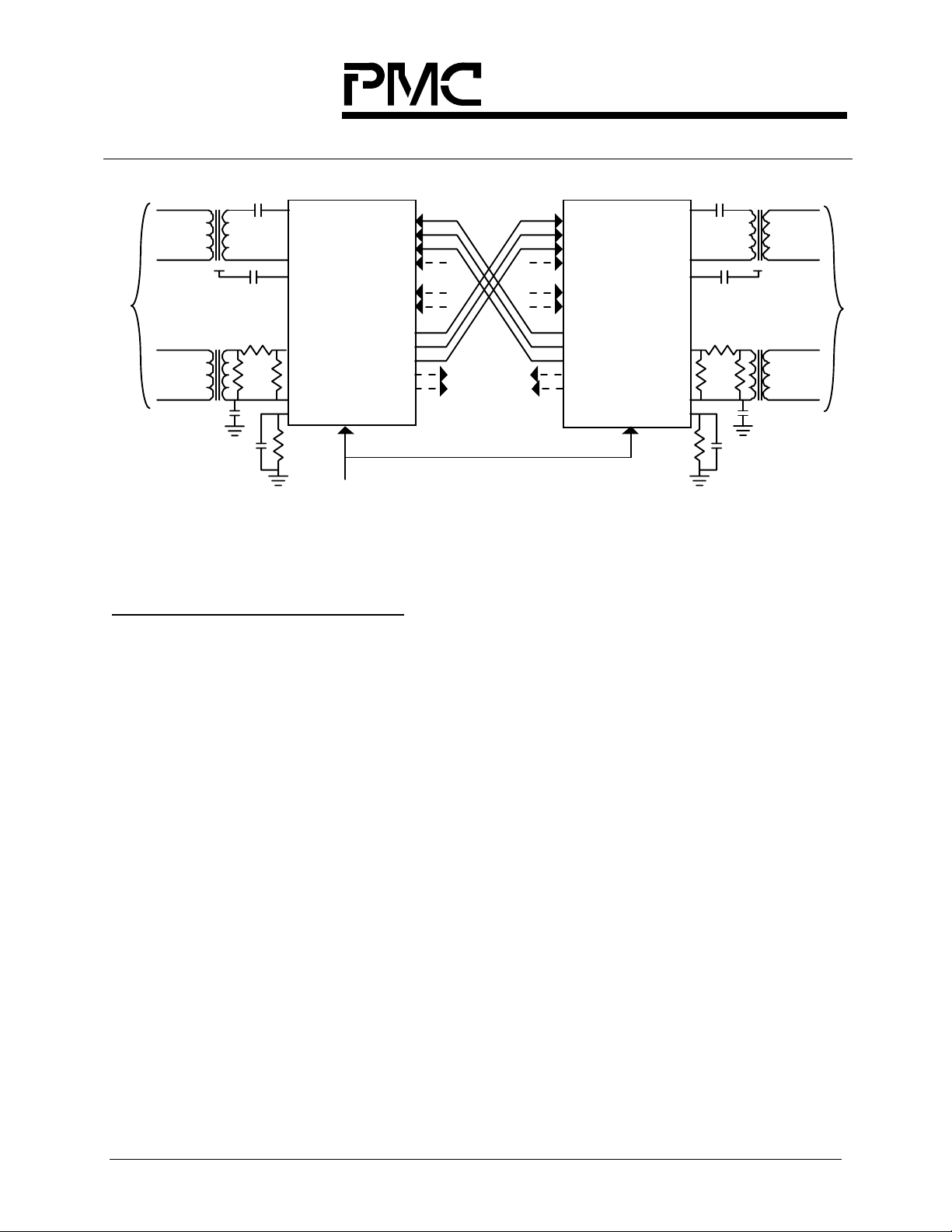

2.8 "CSU" Connection Blocks

While the main purpose of the evaluation daughterboard is to provide unrestricted

access to all of the features of the E1XC device, one application is conveniently

provided which allows easy evaluation of most of the features of the device. By

plugging in shorting jumpers into the two 16 pin CSU DIP sockets (U5 and U6) on

the daughterboard, the two E1XCs are connected back to back to implement a jitterattenuating format converter (a function often implemented within a CSU) as

described in the E1XC datasheet. These CSU DIP socket jumpers make almost all

of the necessary connections except for the signals BRCLK, BRFPI, and BTCLK.

Connections for these signals are made through E-W and W-E jumper blocks J19,

J20, J21, J22, J23, and J24. By installing jumper connections between pin 1 and

pin 2 of jumper blocks J19 and J20, between pin 3 and pin 4 of each of jumper

blocks J21, J22, J23, J24, and between pin 2 and 3 of jumper block J30, a "CSU"

like application can be implemented where the 2.048 MHz clock for the backplane

between the two E1XC devices is provided by the MT8940, which in turn is locked to

the recovered clock provided by E1XC #1. Variations of this application can be

explored by using the other options provided on the jumper blocks. Connections are

provided for 2.048 MHz and externally supplied backplane clock rates.

4

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

N

w

TAP

E-1

Transmit

e

t

AVD

+

TAN

TC

o

r

E-1

k

Receive

AVS

RAS

REF

RRC

AVS

BTPCM

BTSIG

BTFP

BTCLK

BRFPI

BRCLK

BRPCM

BRSIG

BRFPO

RCLKO

RFP

PM6341 E1XC

#1

37.056MHz

BTPCM

BTSIG

BTFP

BTCLK

BRFPI

BRCLK

BRPCM

BRSIG

BRFPO

RCLKO

RFP

#2

XCLKXCLK

TAP

TAN

TC

RAS

PM6341 E1XC

REF

RRC

AVS

+

AVD

AVS

Figure 2: Jitter Attenuating "CSU" Application Hookup

2.9 Transmit/Receive Interface

The daughterboard provides three different types of interfaces for the transmit and

receive signals. The two standard analog interfaces provided are a 120 ohm minibantam interface and a 75 ohm BNC interface. The transmit mini-bantams are

terminated with a 200 ohm resistor on the TN/RN pins to prevent an excessive

voltage kick when mini-bantam plugs are inserted or removed. The BNC connector

barrel can optionally be terminated with a resistor to ground, or grounded directly, by

stuffing a resistor or shorting strap in locations R15, R16, R17, and R18. The

daughterboard is shipped with these 4 locations empty, thereby providing a 75• BNC

interface. The third interface provided is strictly digital and brings out all of the

E1XC's digital E-1 signals to header pins for easy test access. When the digital

interface is used each E1XC's analog receiver can be powered down by moving the

jumper on jumper block J31 or J32.

E-1

Transmit

E-1

Receive

C

u

s

t

o

m

e

r

5

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

3 INTERFACE DESCRIPTION

3.1 Edge Connector Interface

The Edge Connector Interface is made up of a male 96 pin DIN of which 64 pins are

actually used. It consists of signals appropriate to read and write to the registers of

the devices on the daughterboard, and it provides the necessary power and ground.

The connections have been specially designed to mate with PMC's PM1501 EVMB

evaluation motherboard. TTL signal levels are used on this interface.

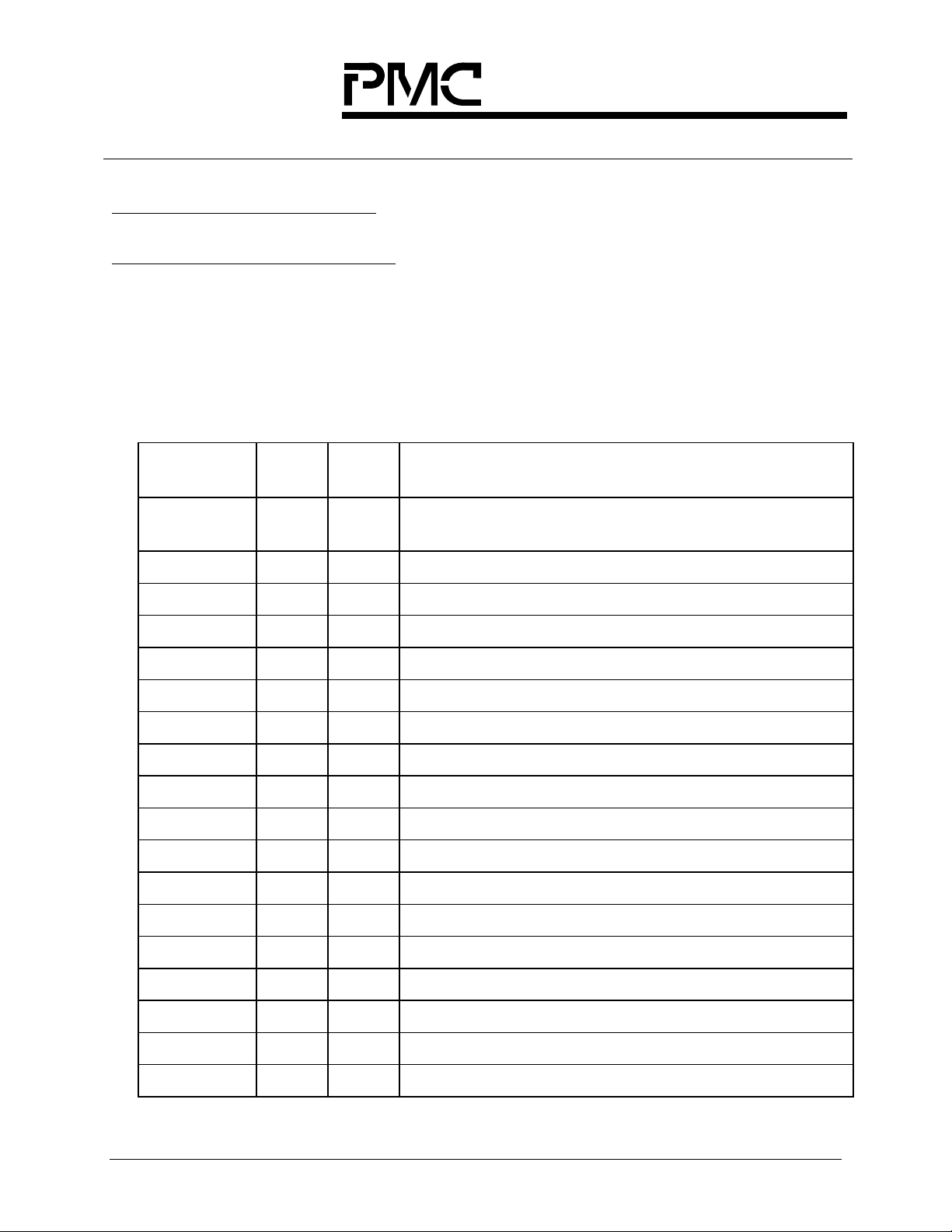

Signal

Name Type

Pin

Function

ALE O C1 Address latch enable. When high, identifies that

address is valid on AD[7:0].

E O C2 Microprocessor Clock

RWB O C3 Active low write, active high read enable

RSTB O C4 Active low H/W reset

A[15] O C5 Address bus bit 15

A[14] O C6 Address bus bit 14

A[13] O C7 Address bus bit 13

A[12] O C8 Address bus bit 12

A[11] O C9 Address bus bit 11

A[10] O C10 Address bus bit 10

A[9] O C11 Address bus bit 9

A[8] O C12 Address bus bit 8

AD[7] I/O C13 Multiplexed address/data bus bit 7

AD[6] I/O C14 Multiplexed address/data bus bit 6

AD[5] I/O C15 Multiplexed address/data bus bit 5

AD[4] I/O C16 Multiplexed address/data bus bit 4

AD[3] I/O C17 Multiplexed address/data bus bit 3

AD[2] I/O C18 Multiplexed address/data bus bit 2

6

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

AD[1] I/O C19 Multiplexed address/data bus bit 1

AD[0] I/O C20 Multiplexed address/data bus bit 0

PA3 O C21 68HC11 Processor Port A bit 3

PA4 O C22 68HC11 Processor Port A bit 4

PA5 O C23 68HC11 Processor Port A bit 5

PA6 O C24 68HC11 Processor Port A bit 6

PD2 I C25 MISO. Master In Slave Out of Port D acting as SPI.

Pulled up on motherboard.

PD3 O C26 MOSI. Master Out Slave In of Por t D acting as SPI.

Pulled up on motherboard.

PD4 O C27 SCK. Serial clock of Port D acting as SPI. Pulled up

on motherboard.

PD5 O C28 SS. Slave Select of Port D acting as SPI active low.

Pulled up on motherboard.

IRQ I C29 Maskable interrupt

XIRQ I C30 Non Maskable Interrupt

DISB I C31 EVMB memory disable. Pulling this signal low will

disable MPU access to the EVMB's on-board RAM

and EPROM.

SP O C32 SPARE

GND O A1-

Ground

A28

+5V O A29-

+5 Volts

A32

3.2 Header Connections

All E1XC functional pins are connected to male header strips to provide as much

access as possible. These headers may be used as probe points or as a means to

build sample applications by making appropriate connections between points. Each

E1XC can run in isolation of the other, thus any application, other than the default

sample "CSU", will require header connections to be made.

7

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

3.2.1 External Signal Header

This header is provided to accept an external clock and framing pulse source. These

inputs are then buffered for use on the board. External clock sources must be

buffered through this header to avoid possible damage to the E1XCs or DPLL.

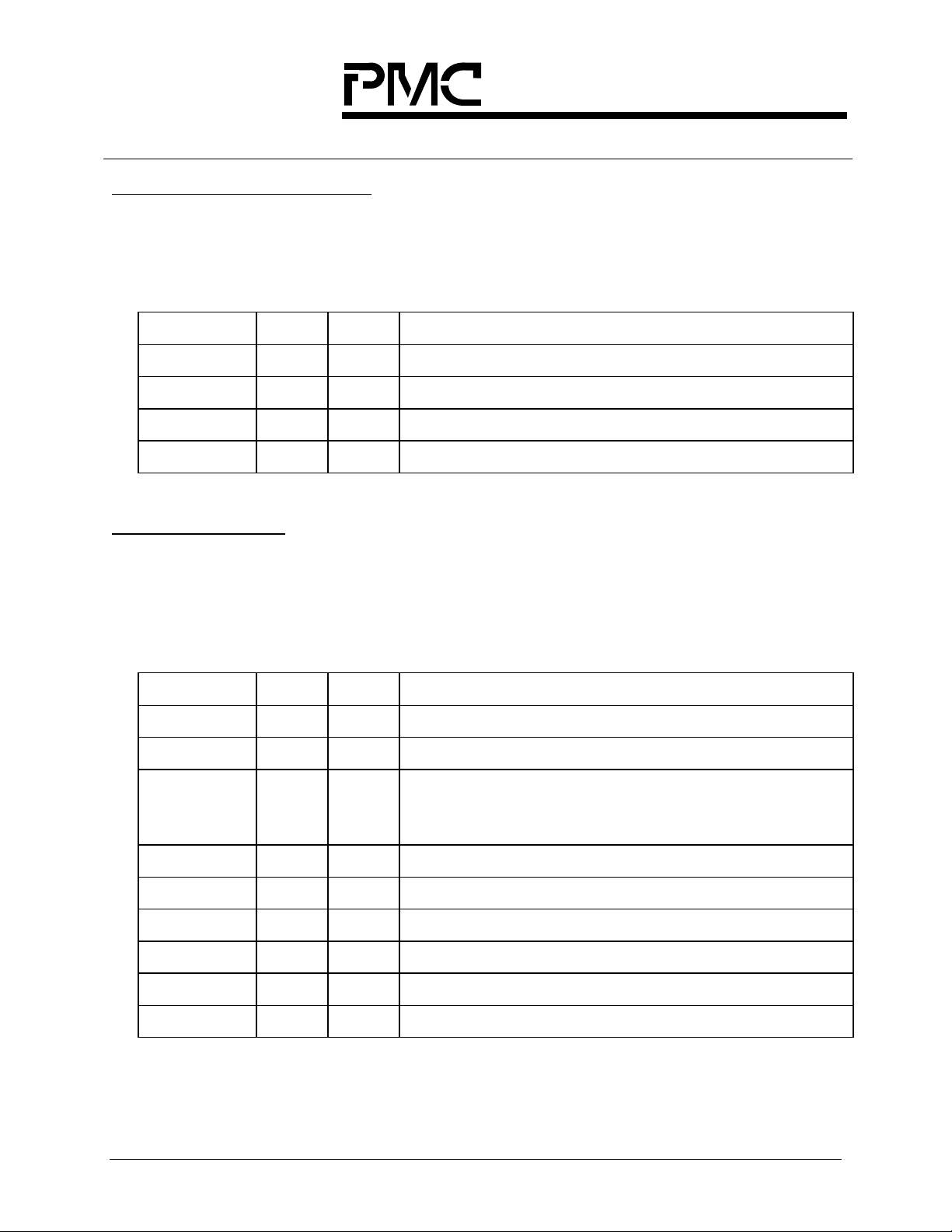

Signal Type Ref. Description

EXTFP I J26-2 External Framing Pulse Input

EXTCLK I J26-4 External Clock Input

BEXTFP O J27-1 Buffered External Framing Pulse

BEXTCLK O J27-2 Buffered External Clock

3.2.2 DPLL Header

This header is provided to give access to the clock generating MT8940 DPLL chip

as well as provide direct oscillator access. All of the major DPLL outputs are brought

out to this header even though they may be of limited use with the E1XC (e.g. the

4.096 MHz clock).

Signal Type Ref. Description

FPIN I J29-2 1.544 MHz Framing pulse input to MT8940.

C8KB I/O J29-1 2.048 MHz Framing pulse in/out (mode dependent).

GFP I/O J29-3 8 kHz Framing pulse output from the MT8940. Note

that this active low output signal is derived from the

16.388 MHz clock and has a 244ns pulse width.

C1M5 O J29-4 1.544 MHz Output clock from MT8940.

C1M5B O J29-5 Inverted C1M5 clock.

C2M O J29-6 2.048 MHz output clock from MT8940.

C2MB O J29-7 Inverted C2M clock.

C4M O J29-8 4.096 MHz Output clock from MT8940.

C4MB O J29-9 Inverted C4M clock.

8

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

C16M O J29-10 Direct access to 16.388 MHz clock driving the

MT8940. This pin is mainly provided for direct

oscillator access. If the MT8940 is not used the

16.388 MHz clock can be replaced by a 2.048 MHz

clock with access to the clock signal provided by

this pin.

C12M O J29-11 Direct access to 12.355 MHz clock driving the

MT8940. This pin is mainly provided for direct

oscillator access. If the MT8940 is not used the

12.355 MHz clock can be replaced by a 1.544 MHz

clock with access to the clock signal provided by

this pin.

GND G J29-12 MT8940 DPLL header ground reference.

3.2.3 E1XC Headers

A number of headers are provided which give direct access to the main functional

pins on the E1XCs. Both devices on the daughterboard have the same pins brought

out to headers and every effort has been made to insure that all headers are

symmetrical with both devices. The E1XCs are uniquely identified by an east/west

designation. The following table gives a brief description of the E1XC signals. For a

more detailed description of the E1XC device, refer to the E1XC datasheet.

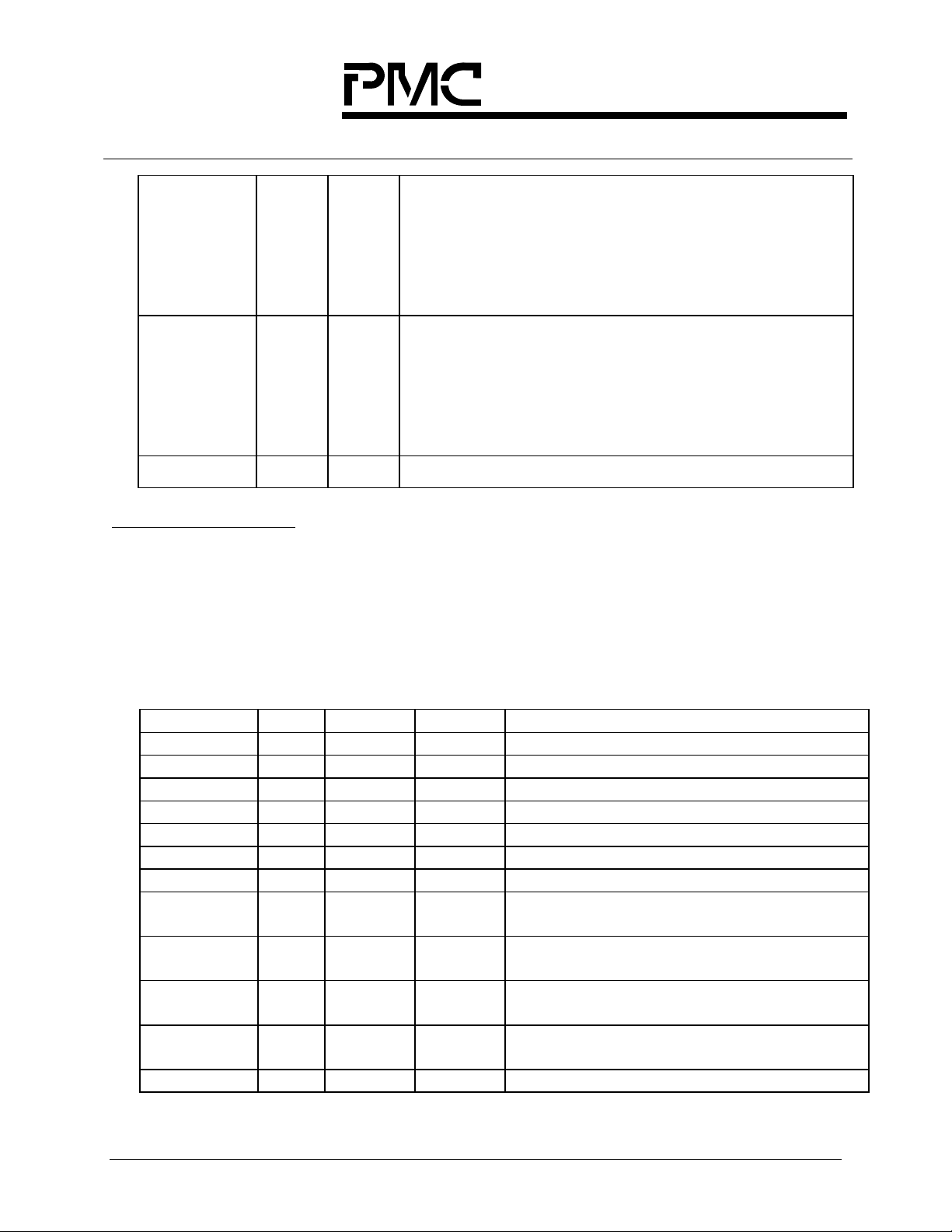

Signal Type Ref (E) Ref (W) Description

TAP O J9-1 J10-1 Transmit Analog Positive Pulse

TAN O J9-2 J10-2 Transmit Analog Negative Pulse

RAS I J9-3 J10-3 Receive Analog Signal

REF I/O J9-4 J10-4 Receive Reference

GND G J9-5 J10-5 E1XC Analog Ground Reference

TCLKI I J15-1 J16-1 Transmit Clock Input

TCLKO O J15-2 J16-2 Transmit Clock Output

TDP/TDD O J15-3 J16-3 Transmit Digital Positive Line Pulse/

Transmit Digital DS-1 Signal

TDN/TFLG O J15-4 J16-4 Transmit Digital Negative Line Pulse/

Transmit FIFO Flag

TDLCLK/

TDLUDR

TDLSIG/

TDLINT

O J15-5 J16-5 Transmit Data Link Clock/ Transmit Data

Link Underrun

I/O J15-6 J16-6 Transmit Data Link Signal/ Transmit Data

Link Interrupt

GND G J15-7 J16-7 E1XC Digital Transmit Ground Reference

9

PMC-Sierra, Inc.

/

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

RDLCLK/

RDLEOM

RDLSIG/

RDLINT

O J13-1 J14-1 Receive Data Link Clock/ Receive Data

Link End of Message

O J13-2 J14-2 Receive Data Link Signal/ Receive Data

Link Interrupt

RCLKI I J13-3 J14-3 Receive Line Clock Input

RDP/ RDD/

SDP

I/O J13-4 J14-4 Receive Digital Positive Line Pulse/

Receive Digital DS-1 Signal/ Sliced

Positive Line Pulse

RDN/ RLCV

SDN

I/O J13-5 J14-5 Receive Digital Negative Line Pulse/

Receive Line Code Violation Indication/

Sliced Negative Line Pulse

GND G J13-6 J14-6

BTPCM/

BTDP

BTSIG/

BTDN

I J11-4 J12-4 Backplane Transmit PCM/ Backplane

Transmit Positive Line Pulse

I J11-3 J12-3 Backplane Transmit Signaling/ Backplane

Transmit Negative Line Pulse

BTFP I J11-2 J12-2 Backplane Transmit Frame Pulse

BTCLK I J11-1 J12-1 Backplane Transmit Cloc k

GND G J11-5 J12-5 Backplane Transmit Header Ground

Reference

BRCLK I J17-1 J18-1 Backplane Receive Clock

BRFPI I J17-2 J18-2 Backplane Frame Pulse Input

BRPCM/

BRDP

BRSIG/

BRDN

O J17-3 J18-3 Backplane Receive PCM/ Backplane

Receive Positive Line Pulse

O J17-4 J18-4 Backplane Receive Signaling/ Backplane

Receive Negative Line Pulse

BRFPO O J17-5 J18-5 Backplane Frame Pulse Output

RDPCM/

RPCM

O J17-6 J18-6 Recovered Decoded PCM/ Recovered

PCM

RCLKO O J17-7 J18-7 Recovered PCM Clock Output

RFP O J17-8 J18-8 Receive Frame Pulse

GND G J17-9 J18-9 Backplane Receive Ground Reference

3.2.4 Prototype Chip Select Header

Two unused chip selects from the decoding logic are provided on a header near the

prototype area.

10

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

Signal Type Ref. Description

Spare1_CSB O J28-1 Spare CSB pin address (C2XX)

Spare2_CSB O J28-2 Spare CSB pin address (C3XX)

3.3 DIP Switches

One 8 bit dip switch is provided on the daughterboard. This switch controls the

operating modes of MT8940 PLL chip and the output enables for the various clock

outputs. When open, each bit line is pulled high. When closed, the bit lines are

individually pulled to ground. For a brief description of the MT8940 operating

modes, consult the tables in the Clock PLL implementation description section.

Switch ID Mapping

Clock 1 MS0

Clock 2 MS1

Clock 3 MS2

Clock 4 MS3

Clock 5 ENC2O

Clock 6 ENCV

Clock 7 ENC4O

Clock 8 Unused

11

PMC-Sierra, Inc.

TELECOM STANDARD PRODUCT

PMC-930917 ISSUE 1 E1XC EVALUATION DAUGHTERBOARD

PM6541 E1XC-EVBD

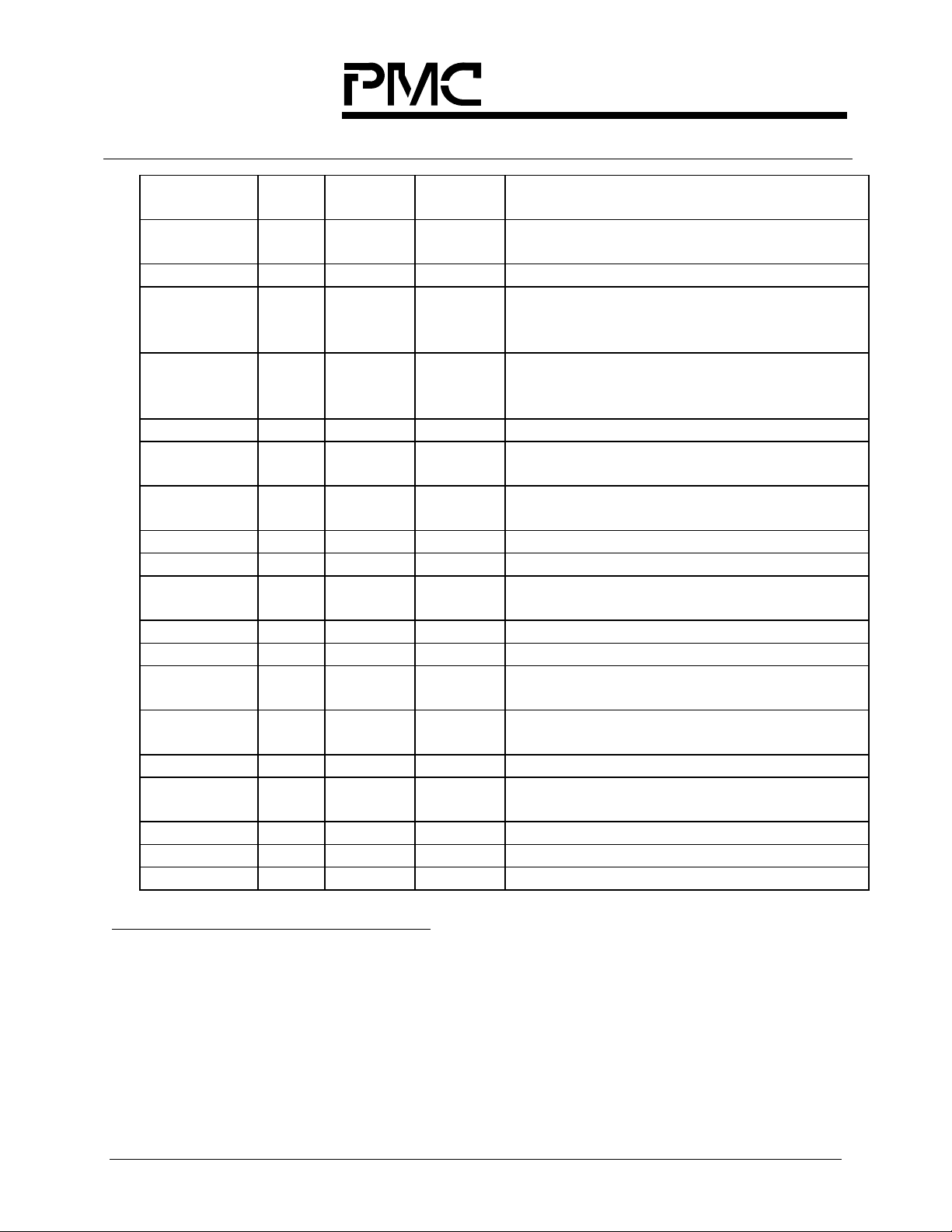

4 PHYSICAL DESCRIPTION

4.1 Characteristics

The E1XC EVBD is an evaluation board that allows the E1XC device to be feature

tested and evaluated for various applications. While the daughterboard can be used

standalone with a limited feature set, it has been especially designed to link with

PMC's EVMB (Evaluation Motherboard). The EVMB controller board provides a

microprocessor to read and write to all of the E1XC's internal registers allowing

configuration, control and set-up of the various modes of E1XC operation.

The E1XC EVBD is laid out for convenient bench top use for test or demonstration

purposes. It is provided with rubber feet that are placed to avoid PCB flexing. Pin

headers provide easy access to all signals necessary during device testing. A

T1/CEPT Digital PLL is installed to provide the necessary 2.048 MHz backplane

rate. External pins allow access when using an externally generated backplane

clock. Ground pins for scope probes are conveniently provided and distributed.

Simple configuration into the example CSU application is provided. The DIP

switches, pin headers, and interface connections are labeled on the silkscreen for

easy identification and ample prototype area is provided. The size of the E1XC

EVBD is constrained to 8.5 x 6.5 inches and, when mated with the EVMB card, will

fit into a standard three ring binder.

12

Loading...

Loading...