PMC PM6388-RI Datasheet

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

PM6388

EOCTL

OCTAL E1 FRAMER

DATA SHEET

ISSUE 6: JANUARY, 2000

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA INC. AND FOR ITS CUSTOMERS’ INTERNAL USE

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

CONTENTS

1 FEATURES.............................................................................................. 1

2 APPLICATIONS....................................................................................... 4

3 REFERENCES......................................................................................... 5

4 APPLICATION EXAMPLES..................................................................... 7

5 BLOCK DIAGRAM................................................................................... 8

6 DESCRIPTION ........................................................................................ 9

7 PIN DIAGRAM ........................................................................................11

8 PIN DESCRIPTION................................................................................ 12

9 FUNCTIONAL DESCRIPTION............................................................... 24

9.1 E1 FRAMER (E1-FRMR)............................................................. 24

9.2 PERFORMANCE MONITOR COUNTERS (PMON) ................... 30

9.3 DATA LINK EXTRACTOR (RXCE).............................................. 31

9.4 HDLC RECEIVER (RDLC).......................................................... 31

9.5 ELASTIC STORE (ELST)............................................................ 32

9.6 SIGNALING EXTRACTOR (SIGX).............................................. 32

9.7 RECEIVE PER-CHANNEL SERIAL CONTROLLER (RPSC)...... 33

9.8 PATTERN DETECTOR/GENERATOR (PRGD).......................... 33

9.9 E1 TRANSMITTER (E1-TRAN)................................................... 34

9.10 TRANSMIT PER-CHANNEL SERIAL CONTROLLER (TPSC).... 34

9.11 TRANSMIT DATA LINK INSERTER (TXCI)................................. 35

9.12 FACILITY DATA LINK TRANSMITTER (TDPR) .......................... 35

9.13 RECEIVE AND TRANSMIT DIGITAL JITTER ATTENUATOR (RJAT,

TJAT)........................................................................................... 36

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use i

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

9.14 TIMING OPTIONS (TOPS) ......................................................... 40

9.15 BACKPLANE RECEIVE INTERFACE (BRIF) ............................. 40

9.15.1 NON-MULTIPLEXED BUS INGRESS MODES............. 40

9.15.2 MULTIPLEXED BUS INGRESS MODE........................ 42

9.16 BACKPLANE TRANSMIT INTERFACE (BTIF)........................... 43

9.16.1 NON-MULTIPLEXED BUS EGRESS MODES.............. 43

9.16.2 MULTIPLEXED EGRESS INTERFACE ........................ 45

9.17 JT AG TEST ACCESS PORT....................................................... 46

9.18 MICROPROCESSOR INTERFACE ............................................ 46

10 NORMAL MODE REGISTER DESCRIPTION....................................... 52

11 OPERATION........................................................................................ 255

11.1 CONFIGURING THE EOCTL FROM RESET ........................... 255

11.2 USING THE MULTIPLEXED BACKPLANE............................... 263

11.2.1 INGRESS MULTIPLEXED BUS CONFIGURATION... 263

11.2.2 EGRESS MULTIPLEXED BUS CONFIGURATION.... 264

11.3 USING THE PER-TIMESLOT TRANSMIT DATA LINK DIRECTOR

.................................................................................................. 266

11.4 USING THE INTERNAL FDL TRANSMITTER.......................... 267

11.5 USING THE PER-TIMESLOT RECEIVE DATA LINK EXTRACTOR

.................................................................................................. 270

11.6 USING THE INTERNAL FDL RECEIVER................................. 271

11.7 USING THE PRGD PATTERN GENERATOR/DETECTOR...... 275

11.8 USING THE LOOPBACK MODES............................................ 280

11.8.1 LINE LOOPBACK.......................................................280

11.8.2 DIAGNOSTIC DIGITAL LOOPBACK.......................... 280

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use ii

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

11.8.3 PER-TS LOOPBACK.................................................. 281

11.9 USING THE PER-TS SERIAL CONTROLLERS....................... 283

11.9.1 INITIALIZATION.......................................................... 283

1 1.9.2 DIRECT ACCESS MODE ........................................... 283

1 1.9.3 INDIRECT ACCESS MODE........................................ 283

1 1.10 USING THE TRANSMIT DIGIT AL JITTER ATTENUATOR....... 284

1 1.10.1 DEF AUL T APPLICA TION............................................ 284

11.10.2 DATA BURST APPLICATION...................................... 285

11.10.3 ELASTIC STORE APPLICATION ............................... 285

1 1.10.4 ALTERNATE TLCLK REFERENCE APPLICATION.... 286

1 1.1 1 ISOLA TING AN INTERRUPT.................................................... 286

11.12 USI NG THE PERFORMA NCE MONITOR COUNTER VALUES286

11.13 JTAG SUPPORT....................................................................... 289

12 FUNCTIONAL TIMING......................................................................... 294

13 ABSOLUTE MAXIMUM RATINGS....................................................... 302

14 D .C. CHARACTERISTICS................................................................. 303

15 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS..... 305

16 EOCTL I/O TIMING CHARACTERISTICS........................................... 310

17 ORDERING AND THERMAL INFORMA TION...................................... 322

18 MECHANICAL INFORMATION............................................................ 323

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use iii

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

LIST OF REGISTERS

REGISTERS 000H, 080H, 100H, 180H, 200H, 280H, 300H, 380H: RECEIVE

LINE OPTIONS................................................................................................. 53

REGISTERS 001H, 081H, 101H, 181H, 201H, 281H, 301H, 381H: INGRESS

INTERFACE OPTIONS .................................................................................... 56

REGISTERS 002H, 082H, 102H, 182H, 202H, 282H, 302H. 382H: TRANSMIT

INTERFACE CONFIGURATION....................................................................... 59

REGISTERS 003H, 083H, 103H, 183H, 203H, 283H, 303H, 383H: EGRESS

INTERFACE OPTIONS .................................................................................... 61

REGISTERS 004H, 084H, 104H, 184H, 204H, 284H, 304H, 384H: TRANSMIT

TIMING OPTIONS............................................................................................ 63

REGISTERS 005H, 085H, 105H, 185H, 205H, 285H, 305H, 385H: INTERRUPT

SOURCE #169

REGISTERS 006H, 086H, 106H, 186H, 206H, 286H, 306H, 386H: INTERRUPT

SOURCE #270

REGISTERS 007H, 087H, 107H, 187H, 207H, 287H, 307H, 387H:

DIAGNOSTICS................................................................................................. 71

REGISTER 008H: EOCTL MASTER TEST...................................................... 73

REGISTER 009H: EOCTL REVISION/CHIP ID/GLOBAL PMON UPDATE...... 75

REGISTERS 00AH, 08AH, 10AH, 18AH, 20AH, 28AH, 30AH, 38AH: DATA LINK

MICRO SELECT/FRAMER RESET.................................................................. 76

REGISTER 00BH: INTERRUPT ID .................................................................. 78

REGISTERS 00CH, 08CH, 10CH, 18CH, 2 0CH, 28CH, 30CH, 38CH: PATTERN

GENERATOR/DETECTOR POSITIONING/CONTROL.................................... 79

REGISTERS 00DH, 08DH, 10DH, 18DH, 2 0DH, 28DH, 30DH, 38DH: CLOCK

MONITOR 81

REGISTERS 00EH, 08EH, 10EH, 18EH, 20EH, 28EH, 30EH, 38EH: INGRESS

FRAME PULSE CONFIGURATION.................................................................. 83

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use iv

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

REGISTERS 010H, 090H, 110H, 190H, 210H, 290H, 310H, 390H: RECEIVE

BACKPLANE CONFIGURATION ..................................................................... 85

REGISTERS 011H, 091H, 111H, 191H, 211H, 291H, 311H, 391H: RECEIVE

BACKPLANE FRAME PULSE CONFIGURATION........................................... 88

REGISTERS 012H, 092H, 112H, 192H, 212H, 292H, 312H, 392H: RECEIVE

BACKPLANE PARITY/F-BIT CONFIGURATION.............................................. 92

REGISTERS 013H, 093H, 113H, 193H, 213H, 293H, 313H, 393H: RECEIVE

BACKPLANE TIME SLOT OFFSET................................................................. 94

REGISTERS 014H, 094H, 114H, 194H, 214H, 294H, 314H, 394H: RECEIVE

BACKPLANE BIT OFFSET .............................................................................. 95

REGISTERS 018H, 098H, 118H, 198H, 218H, 298H, 318H, 398H: TRANSMIT

BACKPLANE CONFIGURATION ..................................................................... 97

REGISTERS 019H, 099H, 119H, 199H, 219H, 299H, 319H, 399H: TRANSMIT

BACKPLANE FRAME PULSE CONFIGURATION......................................... 100

REGISTERS 01AH, 09AH, 11AH, 19AH, 21AH, 29AH, 31AH, 39AH: TRANSMIT

BACKPLANE PARITY CONFIGURATION AND STATUS............................... 101

REGISTERS 01BH, 09BH, 11BH, 19BH, 21BH, 29BH, 31BH, 39BH: TRANSMIT

BACKPLANE TIME SLOT OFFSET............................................................... 103

REGISTERS 01CH, 09CH, 11CH, 19CH, 21CH, 29CH, 31CH, 39CH:

TRANSMIT BACKPLANE BIT OFFSET......................................................... 104

REGISTERS 020H, 0A0H, 120H, 1A0H, 220H, 2A0H, 320H, 3A0H: RJAT

INTERRUPT STATUS..................................................................................... 106

REGISTER 021H, 0A1H, 121H, 1A1H, 221H, 2A1H, 321H, 3A1H: RJAT

REFERENCE CLOCK DIVISOR (N1) CONTROL.......................................... 107

REGISTERS 022H, 0A2H, 122H, 1A2H, 222H, 2A2H, 322H, 3A2H: RJAT

OUTPUT CLOCK DIVISOR (N2) CONTROL.................................................. 108

REGISTERS 023H, 0A3H, 123H, 1A3H, 223H, 2A3H, 323H, 3A3H: RJAT

CONFIGURATION.......................................................................................... 109

REGISTERS 024H, 0A4H, 124H, 1A4H, 224H, 2A4H, 324H, 3A4H: TJAT

INTERRUPT STATUS......................................................................................111

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use v

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

REGISTER 025H, 0A5H, 125H, 1A5H, 225H, 2A5H, 325H, 3A5H: TJAT

REFERENCE CLOCK DIVISOR (N1) CONTROL...........................................112

REGISTERS 026H, 0A6H, 126H, 1A6H, 226H, 2A6H, 326H, 3A6H: TJAT

OUTPUT CLOCK DIVISOR (N2) CONTROL...................................................113

REGISTERS 027H, 0A7H, 127H, 1A7H, 227H, 2A7H, 327H, 3A7H: TJAT

CONFIGURATION...........................................................................................114

REGISTERS 028H, 0A8H, 128H, 1A8H, 228H, 2A8H, 328H, 3A8H (TXCISEL =

0): RXCE RECEIVE DATA LINK 1 CONTROL.................................................116

REGISTERS 029H, 0A9H, 129H, 1A9H, 229H, 2A9H, 329H, 3A9H (TXCISEL =

0): RXCE DATA LINK 1 BIT SELECT REGISTER...........................................118

REGISTERS 02AH, 0AAH, 12AH, 1AAH, 22AH, 2AAH, 32AH, 3AAH (TXCISEL

= 0): RXCE RECEIVE DATA LINK 2 CONTROL .............................................119

REGISTERS 02BH, 0ABH, 12BH, 1ABH, 22BH, 2ABH, 32BH, 3ABH (TXCISEL

= 0): RXCE DATA LINK 2 BIT SELECT REGISTER....................................... 120

REGISTERS 02CH, 0ACH, 12CH, 1ACH, 22CH, 2ACH, 32CH, 3ACH (TXCISEL

= 0): RXCE RECEIVE DATA LINK 3 CONTROL ............................................ 121

REGISTERS 02DH, 0ADH, 12DH, 1ADH, 22DH, 2ADH, 32DH, 3ADH (TXCISEL

= 0): RXCE DATA LINK 3 BIT SELECT REGISTER....................................... 122

REGISTER 028H, 0A8H, 128H, 1A8H, 228H, 2A8H, 328H, 3A8H (TXCISEL =

1): TXCI TRANSMIT DATA LINK 1 CONTROL............................................... 123

REGISTERS 029H, 0A9H, 129H, 1A9H, 229H, 2A9H, 329H, 3A9H (TXCISEL =

1): TXCI DATA LINK 1 BIT SELECT REGISTER............................................ 125

REGISTER 02AH, 0AAH, 12AH, 1AAH, 22AH, 2AAH, 32AH, 3AAH (TXCISEL =

1): TXCI TRANSMIT DATA LINK 2 CONTROL............................................... 126

REGISTERS 02BH, 0ABH, 12BH, 1ABH, 22BH, 2ABH, 32BH, 3ABH (TXCISEL

= 1): TXCI DATA LINK 2 BIT SELECT REGISTER......................................... 128

REGISTER 02CH, 0ACH, 12CH, 1ACH, 2 2CH, 2ACH, 32CH, 3ACH (TXCISEL =

1): TXCI TRANSMIT DATA LINK 3 CONTROL............................................... 131

REGISTERS 02DH, 0ADH, 12DH, 1ADH, 22DH, 2ADH, 32DH, 3ADH (TXCISEL

= 1): TXCI DATA LINK 3 BIT SELECT REGISTER......................................... 133

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use vi

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

REGISTERS 030H, 0B0H, 130H, 1B0H, 230H, 2B0H, 330H, 3B0H: E1 FRMR

FRAME ALIGNMENT OPTIONS .................................................................... 134

REGISTERS 031H, 0B1H, 131H, 1B1H, 231H, 2B1H, 331H, 3B1H: E1 FRMR

MAINTENANCE MODE OPTIONS................................................................. 136

REGISTERS 032H, 0B2H, 132H, 1B2H, 232H, 2B2H, 332H, 3B2H: E1 FRMR

FRAMING STATUS INTERRUPT ENABLE.................................................... 138

REGISTERS 033H, 0B3H, 133H, 1B3H, 233H, 2B3H, 333H, 3B3H: E1 FRMR

MAINTENANCE/ALARM STATUS INTERRUPT ENABLE............................. 139

REGISTERS 034H, 0B4H, 134H, 1B4H, 234H, 2B4H, 334H, 3B1H: E1 FRMR

FRAMING STATUS INTERRUPT INDICATION.............................................. 140

REGISTERS 035H, 0B5H, 135H, 1B5H, 235H, 2B5H, 335H, 3B5H: E1 FRMR

MAINTENANCE/ALARM STATUS INTERRUPT INDICATION....................... 141

REGISTERS 036H, 0B6H, 136H, 1B6H, 236H, 2B6H, 336H, 3B6H: E1 FRMR

FRAMING STATUS......................................................................................... 142

REGISTERS 037H, 0B7H, 137H, 1B7H, 237H, 2B7H, 337H, 3B7H: E1 FRMR

MAINTENANCE/ALARM STATUS.................................................................. 144

REGISTERS 038H, 0B8H, 138H, 1B8H, 238H, 2B8H, 338H, 3B8H: E1 FRMR

TIMESLOT 0 INTERNATIONAL/NATIONAL BITS.......................................... 146

REGISTERS 039H, 0B9H, 139H, 1B9H, 239H, 2B9H, 339H, 3B9H: E1 FRMR

CRC ERROR COUNTER – LSB..................................................................... 148

REGISTERS 03AH, 0BAH, 13AH, 1BAH, 23AH, 2BAH, 33AH, 3BAH: E1 FRMR

CRC ERROR COUNTER – MSB/TIMESLOT 16 EXTRA BITS...................... 149

REGISTERS 03BH, 0BBH, 13BH, 1BBH, 23BH, 2BBH, 33BH, 3BBH: E1 FRMR

NATIONAL BIT CODEWORD INTERRUPT ENABLES.................................. 151

REGISTERS 03CH, 0BCH, 13CH, 1BCH, 2 3CH, 2BCH, 33CH, 3BCH: E1 FRMR

NATIONAL BIT CODEWORD INTERRUPTS................................................. 153

REGISTERS 03DH, 0BDH, 13DH, 1BDH, 2 3DH, 2BDH, 33DH, 3BDH: E1 FRMR

NATIONAL BIT CODEWORD......................................................................... 154

REGISTERS 03EH, 0BEH, 13EH, 1BEH, 23EH, 2BEH, 33EH, 3BEH: E1 FRMR

FRAME PULSE/ALARM/V5.2 LINK ID INTERRUPT ENABLES.................... 155

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use vii

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

REGISTERS 03FH, 0BFH, 13FH, 1BFH, 23FH, 2BFH, 33FH, 3BFH: E1 FRMR

FRAME PULSE/ALARM INTERRUPTS......................................................... 157

REGISTERS 040H, 0C0H, 140H, 1C0H, 240H, 2C0H, 340H, 3C0H: E1 TRAN

CONFIGURATION.......................................................................................... 159

REGISTERS 041H, 0C1H, 141H, 1C1H, 241H, 2C1H, 341H, 3C1H: E1 TRAN

TRANSMIT ALARM/DIAGNOSTIC CONTROL............................................... 163

REGISTERS 042H, 0C2H, 142H, 1C2H, 242H, 2C2H, 342H, 3C2H: E1 TRAN

INTERNATIONAL BITS CONTROL................................................................ 165

REGISTERS 043H, 0C3H, 143H, 1C3H, 243H, 2C3H, 343H, 3C3H: E1 TRAN

EXTRA BITS CONTROL ................................................................................ 166

REGISTERS 044H, 0C4H, 144H, 1C4H, 244H, 2C4H, 344H, 3C4H: E1 TRAN

INTERRUPT ENABLE REGISTER................................................................. 167

REGISTERS 045H, 0C5H, 145H, 1C5H, 245H, 2C5H, 345H, 3C5H: E1 TRAN

INTERRUPT STATUS REGISTER................................................................. 168

REGISTERS 046H, 0C6H, 146H, 1C6H, 246H, 2C6H, 346H, 3C6H: E1 TRAN

NATIONAL BIT CODEWORD SELECT.......................................................... 169

REGISTERS 047H, 0C7H, 147H, 1C7H, 247H, 2C7H, 347H, 3C7H: E1 TRAN

NATIONAL BIT CODEWORD......................................................................... 171

REGISTERS 048H, 0C8H, 148H, 1C8H, 248H, 2C8H, 348H, 3C8H: RDLC #1,

#2, #3 CONFIGURATION............................................................................... 172

REGISTERS 049H, 0C9H, 149H, 1C9H, 249H, 2C9H, 349H, 3C9H: RDLC #1,

#2, #3 INTERRUPT CONTROL...................................................................... 174

REGISTERS 04AH, 0CAH, 14AH, 1CAH, 24AH, 2CAH, 34AH, 3CAH: RDLC#1,

#2, #3 STATUS............................................................................................... 175

REGISTERS 04BH, 0CBH, 14BH, 1CBH, 24BH, 2CBH, 34BH, 3CBH: RDLC #1,

#2, #3 DATA 178

REGISTERS 04CH, 0CCH, 14CH, 1CCH, 24CH, 2CCH, 34CH, 3CCH: RDLC

#1, #2, #3 PRIMARY ADDRESS MATCH....................................................... 179

REGISTERS 04DH, 0CDH, 14DH, 1CDH, 24DH, 2CDH, 34DH, 3CDH: RDLC

#1, #2, #3 SECONDARY ADDRESS MATCH................................................. 180

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use viii

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

REGISTER 050H, 0D0H, 150H, 1D0H, 250H, 2D0H ,350H, 3D0H: TDPR #1,

#2, #3 CONFIGURATION............................................................................... 181

REGISTER 051H, 0D1H, 151H, 1D1H, 251H, 2D1H ,351H, 3D1H: TDPR #1,

#2, #3 UPPER TRANSMIT THRESHOLD...................................................... 183

REGISTER 052H, 0D2H, 152H, 1D2H, 252H, 2D2H ,352H, 3D2H: TDPR #1,

#2, #3LOWER INTERRUPT THRESHOLD.................................................... 184

REGISTER 053H, 0D3H, 153H, 1D3H, 253H, 2D3H ,353H, 3D3H: TDPR #1,

#2, #3 INTERRUPT ENABLE......................................................................... 185

REGISTER 054H, 0D4H, 154H, 1D4H, 254H, 2D4H ,354H, 3D4H: TDPR #1,

#2, #3 INTERRUPT STATUS/UDR CLEAR.................................................... 187

REGISTER 055H, 0D5H, 155H, 1D5H, 255H, 2D5H ,355H, 3D5H: TDPR #1,

#2, #3 TRANSMIT DATA ................................................................................ 189

REGISTERS 058H, 0D8H, 158H, 1D8H, 258H, 2D8H, 358H, 3D8H: ELST

CONFIGURATION.......................................................................................... 190

REGISTERS 059H, 0D9H, 159H, 1D9H, 259H, 2D9H, 359H, 3D9H: ELST

INTERRUPT ENABLE/STATUS ..................................................................... 191

REGISTERS 05AH, 0DAH, 15AH, 1DAH, 25AH, 2DAH, 35AH, 3DAH: ELST

IDLE CODE 192

REGISTER 05CH, 0DCH, 15CH, 1DCH, 25CH, 2 DCH ,35CH, 3DCH: RPSC

CONFIGURATION.......................................................................................... 193

REGISTER 05DH, 0DDH, 15DH, 1DDH, 25DH, 2 DDH ,35DH, 3DDH: RPSC µP

ACCESS STATUS.......................................................................................... 194

REGISTER 05EH, 0DEH, 15EH, 1DEH, 25EH, 2DEH ,35EH, 3DEH: RPSC

CHANNEL INDIRECT ADDRESS/CONTROL ................................................ 195

REGISTER 05FH, 0DFH, 15FH, 1DFH, 25FH, 2DFH ,35FH, 3DAH: RPSC

CHANNEL INDIRECT DATA BUFFER............................................................ 196

REGISTER 060H, 0E0H, 160H, 1E0H, 260H, 2E0H ,360H, 3E0H: TPSC

CONFIGURATION.......................................................................................... 203

REGISTER 061H, 0E1H, 161H, 1E1H, 261H, 2E1H ,361H, 3E1H: TPSC µP

ACCESS STATUS.......................................................................................... 204

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use ix

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

REGISTER 062H, 0E2H, 162H, 1E2H, 262H, 2E2H ,362H, 3E2H: TPSC

CHANNEL INDIRECT ADDRESS/CONTROL ................................................ 205

REGISTER 063H, 0E3H, 163H, 1E3H, 263H, 2E3H ,363H, 3E3H: TPSC

CHANNEL INDIRECT DATA BUFFER............................................................ 206

REGISTER 064H, 0E4H, 164H, 1E4H, 264H, 2E4H ,364H, 3E4H: SIGX

CONFIGURATION REGISTER (COSS = 0)................................................... 213

REGISTER 064H, 0E4H, 164H, 1E4H, 264H, 2E4H ,364H, 3E4H: SIGX

CHANGE OF SIGNALING STATE REGISTER (COSS = 1)........................... 215

REGISTER 065H, 0E5H, 165H, 1E5H, 265H, 2E5H ,365H, 3E5H: SIGX

TIMESLOT INDIRECT STATUS (COSS = 0).................................................. 216

REGISTER 065H, 0E5H, 165H, 1E5H, 265H, 2E5H ,365H, 3E5H: SIGX

CHANGE OF SIGNALING STATE CHANGE (COSS=1)................................ 217

REGISTER 066H, 0E6H, 166H, 1E6H, 266H, 2E6H ,366H, 3E6H: SIGX

TIMESLOT INDIRECT ADDRESS/CONTROL (COSS = 0)............................ 218

REGISTER 066H, 0E6H, 166H, 1E6H, 266H, 2E6H ,366H, 3E6H: SIGX

CHANGE OF SIGNALING STATE REGISTER (COSS = 1)........................... 219

REGISTER 067H, 0E7H, 167H, 1E7H, 267H, 2E7H ,367H, 3E7H: SIGX

TIMESLOT INDIRECT DATA BUFFER (COSS = 0)....................................... 220

REGISTER 067H, 0E7H, 167H, 1E7H, 267H, 2E7H ,367H, 3E7H: SIGX

CHANGE OF SIGNALING STATE (COSS = 1).............................................. 221

SIGX INDIRECT REGISTERS 32 (20H)- 63 (3FH): SIGX TIMESLOT/CHANNEL

SIGNALING DATA REGISTERS..................................................................... 223

SIGX INDIRECT REGISTERS 64 (40H) - 95 (5FH): SIGX PER-TIMESLOT

CONFIGURATION REGISTER....................................................................... 224

REGISTER 068H, 0E8H, 168H, 1E8H, 268H, 2E8H ,368H, 3E8H: PMON

INTERRUPT ENABLE/STATUS ..................................................................... 226

REGISTER 068H, 0E8H, 168H, 1E8H, 268H, 2E8H ,368H, 3E8H: FRAMING BIT

ERROR COUNT............................................................................................. 228

REGISTER 06AH, 0EAH, 16AH, 1EAH, 26AH, 2EAH ,36AH, 3EAH: FAR END

BLOCK ERROR COUNT LSB........................................................................ 229

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use x

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

REGISTER 06BH, 0EBH, 16BH, 1EBH, 26BH, 2EBH ,36BH, 3EBH: FAR END

BLOCK ERROR COUNT MSB....................................................................... 229

REGISTER 06CH, 0ECH, 16CH, 1ECH, 26CH, 2ECH ,36CH, 3ECH: CRC

ERROR COUNT LSB ..................................................................................... 230

REGISTER 06DH, 0EDH, 16DH, 1EDH, 26DH, 2EDH ,36DH, 3EDH: CRC

ERROR COUNT MSB .................................................................................... 230

REGISTER 070H, 0F0H, 170H, 1F0H, 270H, 2F0H ,370H, 3F0H: PRGD

CONTROL 231

REGISTER 071H, 0F1H, 171H, 1F1H, 271H, 2F1H ,371H, 3F1H: PRGD

INTERRUPT ENABLE/STATUS ..................................................................... 233

REGISTER 072H, 0F2H, 172H, 1F2H, 272H, 2F2H ,372H, 3F2H: PRGD SHIFT

REGISTER LENGTH...................................................................................... 235

REGISTER 073H, 0F3H, 173H, 1F3H, 273H, 2F3H ,373H, 3F3H: PRGD TAP

236

REGISTER 074H, 0F4H, 174H, 1F4H, 274H, 2F4H ,374H, 3F4H: PRGD

ERROR INSERTION...................................................................................... 237

REGISTER 078H, 0F8H, 178H, 1F8H, 278H, 2F8H ,378H, 3F8H: PRGD

PATTERN INSERTION #1.............................................................................. 238

REGISTER 079H, 0F9H, 179H, 1F9H, 279H, 2F9H ,379H, 3F0H: PRGD

PATTERN INSERTION #2.............................................................................. 238

REGISTER 07AH, 0FAH, 17AH, 1FAH, 27AH, 2FAH ,37AH, 3FAH: PRGD

PATTERN INSERTION #3.............................................................................. 239

REGISTER 07BH, 0FBH, 17BH, 1FBH, 27BH, 2FBH ,37BH, 3FBH: PRGD

PATTERN INSERTION #4.............................................................................. 239

REGISTER 07CH, 0FCH, 17CH, 1FCH, 27CH, 2FCH ,37CH, 3FCH: PRGD

PATTERN DETECTOR #1.............................................................................. 241

REGISTER 07DH, 0FDH, 17DH, 1FDH, 27DH, 2FDH ,37DH, 3FDH: PRGD

PATTERN DETECTOR #2.............................................................................. 241

REGISTER 07EH, 0FEH, 17EH, 1FEH, 27EH, 2FEH ,37EH, 3FEH: PRGD

PATTERN DETECTOR #3.............................................................................. 242

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use xi

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

REGISTER 07FH, 0FFH, 17FH, 1FFH, 27FH, 2FFH ,37FH, 3F0H: PRGD

PATTERN DETECTOR #4.............................................................................. 242

REGISTER 008H: EOCTL MASTER TEST.................................................... 245

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use xii

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

LIST OF FIGURES

FIGURE 1 - HIGH DENSITY CHANNELIZED PORT CARD APPLICATION... 7

FIGURE 2 - E1-FRMR FRAMING ALGORITHM........................................... 27

FIGURE 3 - DJAT JITTER TOLERANCE...................................................... 38

FIGURE 4 - DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY39

FIGURE 5 - DJAT JITTER TRANSFER......................................................... 39

FIGURE 6 - CLOCK MASTER: FULL E1...................................................... 40

FIGURE 7 - CLOCK MASTER: NXTS........................................................... 41

FIGURE 8 - CLOCK SLAVE: ICLK REFERENCE......................................... 41

FIGURE 9 - CLOCK SLAVE: EXTERNAL SIGNALING................................. 42

FIGURE 10 - INGRESS MULTIPLEXED BUS OPERATION........................... 42

FIGURE 11 - CLOCK MASTER: FULL E1...................................................... 43

FIGURE 12 - CLOCK MASTER: NXTS........................................................... 44

FIGURE 13 - CLOCK SLAVE: EFP ENABLED............................................... 44

FIGURE 14 - CLOCK SLAVE: EXTERNAL SIGNALING................................. 45

FIGURE 15 - EGRESS MULTIPLEXED BUS OPERATION............................ 45

FIGURE 16 - TRANSMIT TIMING OPTIONS.................................................. 68

FIGURE 17 - INPUT OBSERVATION CELL (IN_CELL)................................ 252

FIGURE 18 - OUTPUT CELL (OUT_CELL).................................................. 253

FIGURE 19 - BIDIRECTIONAL CELL (IO_CELL)......................................... 253

FIGURE 20 - LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS

254

FIGURE 21 - TYPICAL DATA FRAME .......................................................... 273

FIGURE 22 - EXAMPLE MULTI-PACKET OPERATIONAL SEQUENCE...... 274

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use xiii

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

FIGURE 23 - PRGD PATTERN GENERATOR.............................................. 277

FIGURE 24 - LINE LOOPBACK.................................................................... 280

FIGURE 25 - DIAGNOSTIC DIGITAL LOOPBACK....................................... 281

FIGURE 26 - PER-TS LOOPBACK............................................................... 282

FIGURE 27 - FER COUNT VS. BER............................................................. 287

FIGURE 28 - CRCE COUNT VS. BER.......................................................... 288

FIGURE 29 - BOUNDARY SCAN ARCHITECTURE..................................... 289

FIGURE 30 - TAP CONTROLLER FINITE STATE MACHINE....................... 291

FIGURE 31 - INGRESS INTERFACE CLOCK MASTER : FULL E1 MODE. 294

FIGURE 32 - EGRESS INTERFACE CLOCK MASTER : FULL E1 MODE... 294

FIGURE 33 - INGRESS INTERFACE CLOCK MASTER : NXTS MODE...... 295

FIGURE 34 - EGRESS INTERFACE CLOCK MASTER : NXTS MODE....... 295

FIGURE 35 - INGRESS INTERFACE CLOCK SLAVE MODES.................... 296

FIGURE 36 - EGRESS INTERFACE CLOCK SLAVE : EFP ENABLED MODE

296

FIGURE 37 - EGRESS INTERFACE CLOCK SLAVE : EXTERNAL SIGNALING

MODE 297

FIGURE 38 - NON-MULTIPLEXED TRANSMIT BACKPLANE AT 2.048/4.096

MHZ 297

FIGURE 39 - MULTIPLEXED TRANSMIT BACKPLANE AT 8.192 AND 16.384

MHZ 298

FIGURE 40 - TRANSMIT CONCENTRATION HIGHWAY INTERFACE........ 298

FIGURE 41 - SERIAL TELECOM BUS (ST-BUS), EXAMPLE 1................... 299

FIGURE 42 - SERIAL TELECOM BUS (ST-BUS), EXAMPLE 2................... 299

FIGURE 43 - NON-MULTIPLEXED RECEIVE BACKPLANE AT 2.048/4.096

MHZ 300

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use xiv

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

FIGURE 44 - MULTIPLEXED RECEIVE BACKPLANE AT 8.192 AND 16.384

MHZ 300

FIGURE 45 - RECEIVE CONCENTRATION HIGHWAY INTERFACE......... 301

FIGURE 46 - MICROPROCESSOR READ ACCESS TIMING..................... 306

FIGURE 47 - MICROPROCESSOR WRITE ACCESS TIMING................... 308

FIGURE 48 - HIGH SPEED CLOCK TIMING............................................... 310

FIGURE 49 - EGRESS INTERFACE TIMING - CLOCK SLAVE: EFP ENABLED

MODE 311

FIGURE 50 - EGRESS INTERFACE TIMING - CLOCK SLAVE: EXTERNAL

SIGNALING MODE ........................................................................................ 312

FIGURE 51 - EGRESS INTERFACE TIMING - CLOCK MASTER: FULL E1

MODE 313

FIGURE 52 - EGRESS INTERFACE INPUT TIMING - CLOCK MASTER :

NXTS MODE .................................................................................................. 313

FIGURE 53 - INGRESS INTERFACE TIMING - CLOCK SLAVE MODES... 314

FIGURE 54 - INGRESS INTERFACE TIMING - CLOCK MASTER MODES315

FIGURE 55 - TRANSMIT LINE INTERFACE TIMING.................................. 316

FIGURE 56 - RECEIVE LINE INTERFACE INPUT TIMING......................... 317

FIGURE 57 - MULTIPLEXED INGRESS INTERFACE TIMING................... 318

FIGURE 58 - MULTIPLEXED EGRESS INTERFACE TIMING .................... 319

FIGURE 59 - JTAG PORT INTERFACE TIMING.......................................... 320

FIGURE 60 - 128 PIN COPPER LEADFRAME PLASTIC QUAD FLAT PACK (R

SUFFIX) 323

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use xv

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

LIST OF TABLES

TABLE 1 - E1-FRMR CRC FRAME FIND S TATE MACHINE OUTPUTS ... 28

TABLE 2 - REGISTER MEMORY MAP....................................................... 46

TABLE 3 - TRANSMIT LINE CLOCK OPTIONS......................................... 64

TABLE 4 - RECEIVE DATALINK CONTROLLER SELECTION.................. 76

TABLE 5 - TRANSMIT DATALINK CONTROLLER SELECTION................ 77

TABLE 6 - TXTS[1:0] BACKPLANE RECEIVE OPERATION ..................... 85

TABLE 7 - RATE[1:0] BACKPLANE RECEIVE OPERATION..................... 86

TABLE 8 - IFP[X] BACKPLANE RECEIVE CONFIGURATION................... 89

TABLE 9 - RECEIVE BACKPLANE BIT OFFSET FOR FP MASTER......... 96

TABLE 10 - RECEIVE BACKPLANE BIT OFFSET FOR FP SLAVE ............ 96

TABLE 11 - TRANSMIT BACKPLANE NXTS MODE SELECTION.............. 97

TABLE 12 - TRANSMIT BACKPLANE RATE................................................ 99

TABLE 13 - TRANSMIT BACKPLANE BIT OFFSET FOR CMS = 0........... 105

TABLE 14 - TRANSMIT BACKPLANE BIT OFFSET FOR CMS = 1........... 105

TABLE 15 - TIMESLOT 0 BIT POSITION ALLOCATION............................ 146

TABLE 16 - TS0 NFAS BITS....................................................................... 147

TABLE 17 - TIMESLOT 16, FRAME 0 BIT POSITION ALLOCATION ........ 150

TABLE 18 - NATIONAL BIT CODEWARD SELECTION............................. 151

TABLE 19 - E1 SIGNALING INSERTION MODE........................................ 159

TABLE 20 - E1 TIMESLOT 0 INSERTION CONTROL SUMMARY (INDIS =

FDIS = 0) 161

TABLE 21 - NATIONAL BIT CODEWARD SELECTION............................. 170

TABLE 22 - RECEIVE PACKET BYTE STATUS......................................... 176

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use xvi

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

TABLE 23 - RPSC INDIRECT REGISTER MAP......................................... 196

TABLE 24 - RECEIVE TEST PATTERN MODES ....................................... 199

TABLE 25 - RPSC INDIRECT REGISTERS 40 -5 FH: DATA TRUNK

CONDITIONING CODE BYTE........................................................................ 201

TABLE 26 - RPSC INDIRECT REGISTERS 61-7FH: SIGNALING TRUNK

CONDITIONING BYTE................................................................................... 202

TABLE 27 - TPSC INDIRECT REGISTER MAP......................................... 207

TABLE 28 - TPSC INDIRECT REGISTERS 20-3FH: TIMESLOT CONTROL

BYTE 208

TABLE 29 - TRANSMIT TEST PATTERN MODES..................................... 209

TABLE 30 - TPSC INDIRECT REGISTERS 40-5FH: IDLE CODE BYTE... 210

TABLE 31 - TPSC INDIRECT REGISTERS 60-7FH: SIGNALING/PCM

CONTROL BYTE.............................................................................................211

TABLE 32 - TRANSMIT PER-TIMESLOT DATA MANIPULATION ..............211

TABLE 33 - A-LAW DIGITAL MILLIWATT PATTERN.................................. 212

TABLE 34 - µ-LAW DIGITAL MILLIWATT PATTERN.................................. 212

TABLE 35 - SIGX INDIRECT REGISTER MAP.......................................... 221

TABLE 36 - RINV[1:0] EFFECT ON TIMESLOT DATA BITS...................... 224

TABLE 37 - PATTERN DETECTOR REGISTER CONFIGURATIONS....... 231

TABLE 38 - ERROR INSERTION RATES................................................... 237

TABLE 39 - TEST MODE 0 INPUT SIGNAL WRITE ADDRESSES............ 247

TABLE 40 - TEST MODE 0 OUTPUT SIGNAL READ ADDRESSES......... 248

TABLE 41 - INSTRUCTION REGISTER..................................................... 250

TABLE 42 - IDENTIFICATION REGISTER................................................. 250

TABLE 43 - BOUNDARY SCAN REGISTER.............................................. 251

TABLE 44 - PSEUDO-RANDOM PATTERN GENERATION (PS BIT = 0).. 277

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use xvii

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

TABLE 45 - REPETITIVE PATTERN GENERATION (PS BIT = 1)............. 278

TABLE 46 - PMON COUNTER SATURATION LIMITS............................... 286

TABLE 47 - EOCTL ABSOLUTE MAXIMUM RATINGS.............................. 302

TABLE 48 - EOCTL D.C. CHARACTERISTICS.......................................... 303

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use xviii

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

1 FEATURES

• Integrates eight E1 framers in a single device for terminating duplex E1

signals.

• Supports transfer of PCM data to/from 2.048 MHz system-side devices. Also

supports a fractional E1 system interface with independent ingress/egress

fractional E1 rates.

• Provides an optional backplane interface which is compatible with Mitel ST®-

bus, A T&T CHI® and MVIP PCM backplanes, supporting data rates of

2.048 Mbit/s and 8.192 Mbit/s. Up to four links may be byte interleaved on

each interface bus with no external circuitry.

• Extracts/inserts up to three HDLC links from/to arbitrary time slots to support

the D-channel for ISDN Primary Rate Interfaces and the C-channels for

V5.1/V5.2 interfaces as per ITU-T G.964, ITU-T G.965, ETS 300-324-1, and

ETS 300-347-1.

• Provides jitter attenuation in the receive and transmit directions.

• Provides per-channel payload loopback and per link diagnostic and line

loopbacks.

• Provides an integral pattern generator/detector that may be programmed to

generate and detect common pseudo-random (as recommended in ITU-T

O.151) or repetitive sequences. The programmed sequence may be

inserted/detected in the entire E1 frame, or on a fractional E1 basis, in both

the ingress and egress directions. Each framer possesses its own

independent pattern generator/detector, and each detector counts pattern

errors using a 32-bit saturating error counter.

• Provides signaling extraction and insertion on a per-channel basis.

• Software compatible with the PM6341 E1XC Single E1 Transceiver, the

PM6344 EQUAD Quad E1 Framer, the PM4388 TOCTL Octal T1 Framer, and

PM4351 COMET Combined E1/T1 Transceiver.

• Seamless interface to the PM4314 QDSX Quad Line Interface.

• Provides a IEEE P1149.1 (JTAG) compliant test access port (TAP) and

controller for boundary scan test.

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 1

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

• Provides an 8-bit microprocessor bus interface for configuration, control, and

status monitoring.

• Low power 3.3V CMOS technology with 5V tolerant inputs.

• Available in a 128 pin PQFP (14 mm by 20 mm) package.

• Provides a -40°C to +85°C Industrial temperature operating range.

Each one of eight receiver sections:

• Frames to ITU-T G.704 basic and CRC-4 multiframe formatted E1 signals.

The framing procedures are consistent with ITU-T G.706 specifications.

• Red, and AIS alarm detection and integration are done according to ITU-T

Q.431 specifications.

• Provides performance monitoring counters sufficiently large as to allow

performance monitor counter polling at a minimum rate of once per second.

Optionally, updates the perfo rmance monitoring counters and interrupts the

microprocessor once per second, timed to the receive line. Accumulators are

provided for counting CRC-4 errors, framing bit errors and loss of frame or

change of frame alignment events.

• Provides an optional elastic store for backplane rate adaptation. It may be

used to time the ingress streams to a common clock and frame alignment, or

to facilitate per-channel loopbacks.

• Provides a digital phase locked loop to reduce jitter on the receive clock.

• Supports polled or interrupt-driven servicing of the HDLC interface.

• Optionally extracts a datalink in the E1 national use bits.

• Extracts up to three HDLC links from arbitrary time slots to support the D-

channel for ISDN Primary Rate Interfaces and the C-channels for V5.1/V5.2

interfaces.

• Frames to the E1 signaling multiframe alignment when enabled and extracts

channel associated signaling. Alternatively, a common channel signaling data

link may be extracted from timeslot 16.

• Can be programmed to generate an interrupt on change of signaling state.

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 2

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

• Provides trunk conditioning which forces programmable idle code substitution

and signaling conditioning on all channels or on selected channels.

• Provides diagnostic, line loopbacks and per-channel line loopback.

• Provides programmable idle code substitution, data inversion, and A-Law or

µ-Law digital milliwatt code insertion on a per-channel basis.

• Each one of eight transmitter sections:

• Transmits G.704 basic and CRC-4 multiframe formatted E1 signals.

• Supports unframed mode and framing bit, CRC, or data link by-pass.

• May be timed to its associated receive clock (loop timing) or may derive its

timing from a common egress clock or a common transmit clock; the transmit

line clock may be synthesized from an N*8kHz reference.

• Provides a 128 byte buffer to allow insertion of the facility data link using the

host interface.

• Optionally inserts a datalink in the E1 national use bits.

• Inserts up to three HDLC links into arbitrary time slots to support the D-

channel for ISDN Primary Rate Interfaces and the C-channels for V5.1/V5.2

interfaces.

• Provides a digital phase locked loop for generation of a low jitter transmit

clock.

• Provides programmable idle code substitution, data inversion, signaling

insertion, and A-Law or µ-Law digital milliwatt code insertion on a per-channel

basis.

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 3

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

2 APPLICATIONS

• High density Internet E1 interfaces for multiplexers, switches, routers and

digital modems.

• Frame Relay switches and access devices (FRADS)

• SONET/SDH Add Drop Multiplexers

• Digital Private Branch Exchanges (PBX)

• E1 Channel Service Units (CSU) and Data Service Units (DSU)

• E1 Channel Banks and Multiplexers

• Digital Access and Cross-Connect Systems (DACS)

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 4

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

3 REFERENCES

1. AT&T - Interface Specification - Concentration Highway Interface November, 1990.

2. ETSI - ETS 300 011 - ISDN Primary Rate User-Network Interface

Specification and Test Principles, 1992.

3. ETSI - ETS 300 233 - Access Digital Section for ISDN Primary Rates

4. ETSI – ETS 324-1 – Signaling Protocols and Switching (SPS); V interfaces at

the digital Local Exchange (LE); V5.1 interface for the support of Access

Network (AN); Part 1: V5.1 interface specification, Nov. 1995.

5. ETSI – ETS 347-1 – Signaling Protocols and Switching (SPS); V interfaces at

the digital Local Exchange (LE) V5.2 interface for the support of Access

Network (AN) Part 1: V5.2 interface specification, Sept. 1994.

6. ETSI - TBR 4 - Integrated Services Digital Network (ISDN); Attachment

requirements for terminal equipment to connect to an ISDN using ISDN

primary rate access, November 1995.

7. ETSI - TBR 12 - Business Telecommunications (BT); Open Network

Provision (ONP) technical requirements; 2 048 kbit/s digital unstructured

leased lines (D2048U) Attachment requirements for teminal equipment

interface, December 1993.

8. ETSI - TBR 13 - Business Telecommunications (BTC); 2 048 kbit/s digital

structured leased lines (D2048S); Attachment requirements for terminal

equipment interface, January 1996.

9. ITU-T - Recommendation G.704 - Synchronous Frame Structures Used at

Primary Hierarchical Levels, July 1995.

10. ITU-T - Recommendation G.706 - Frame Alignment and CRC Procedures

Relating to G.704 Frame Structures.

11. ITU-T Recommendation G.823, - The Control of Jitter and Wander Within

Digital Networks Which are Based on the 2048 kbit/s Hierarchy, 1993.

12. ITU-T Recommendation G.964, - V-Interfaces at the Digital Local Exchange

(LE) - V5.1 Interface (Based on 2048kbit/s) for the Support of Access

Network (AN), June 1994.

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 5

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

13. ITU-T Recommendation G.965, - V-Interfaces at the Digital Local Exchange

(LE) - V5.2 Interface (Based on 2048kbit/s) for the Support of Access

Network (AN), March 1995.

14. ITU-T - Recommendation I.431 - Primary Rate User-Network Interface –

Layer 1 Specification, 1993.

15. ITU-T Recommendation O.151, - Error Performance Measuring Equipment

For Digital Systems at the Primary Bit Rate and Above, 1988.

16. ITU-T Recommendation O.152 - Error Performance Measuring Equipment for

Bit Rates of 64 kbit/s and N X 64 kbit/s, October 1992

17. ITU-T Recommendation O.153 - Basic Parameters for the Measurement of

Error Performance at Bit Rates below the Primary Rate, October 1992

18. GO-MVIP - Multi-Vendor Integration Protocol, MVIP-90 Release 1.1, 1994.

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 6

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

4 APPLICATION EXAMPLES

Figure 1 - High Density Channelized Port Card Application

#1 of 8

E1 C ha nne liz ed

E3 Interface

PM6388-RI

EOCTL

LIU

LIU

E13 Mux

E13 Mux

AND / O R

PM4314-RI

QDSX

PM4314-RI

QDSX

Channelized

And/Or Unchannelized E1

Inte r f a c e s

PM4314-RI

QDSX

PM4314-RI

QDSX

PM6388-RI

EOCTL

PM6388-RI

EOCTL

PM4388-RI

EOCTL

#4 of 8

PM6388-R I

EOCTL

#5 of 8

PM6388-RI

EOCTL

#8 of 8

PM7364

FREEDM (s)

Channelized

/Unchannelized

HDLC

Processor(s)

Packet Router Core

or

Packet Switch Core

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 7

PM6388 EOCTL

A

A

A

A

A

r

A

A

r

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

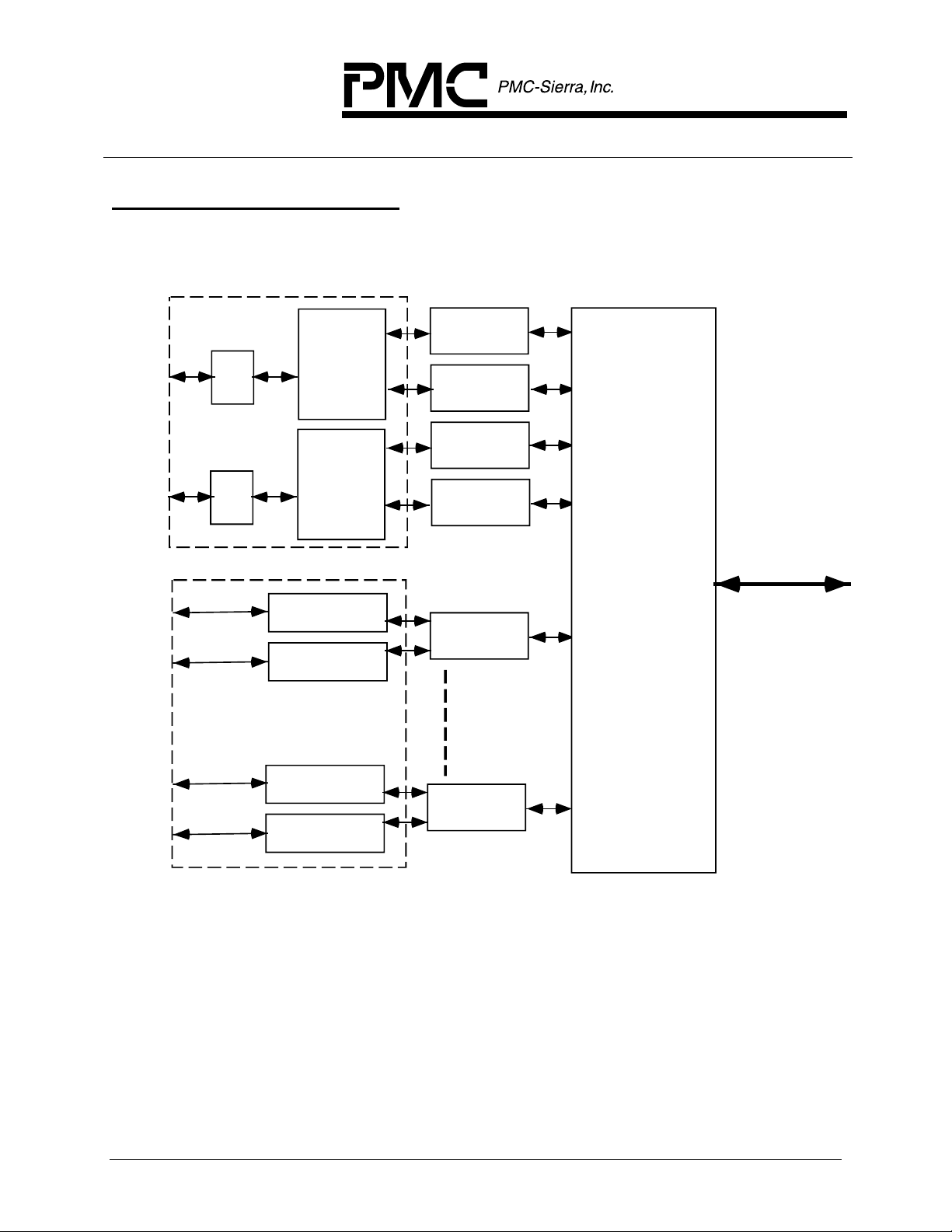

5 BLOCK DIAGRAM

CTCLK*

CECLK/MCECLK*

CEFP/MCEFP*

ESIG[1:2]/ECLK[1:2]/

EFP[1:2]/MESIG[1;2]

ED[1:2]/MED[1:2]

ESIG[3:8]/

ECLK[3:8]/

EFP[3:8]

ED[3:8]

BTIF

Backplane

Egress

Interface

PRGD

Pattern

Generator/

Detector

TPSC

Per-

Channel

Controller

TRANSMITTER

TRAN

BasicTransmitter:

Frame Generation,

larm Insertion,

Signaling Ins ertio n,

Trunk Conditioning

TDPR[2:0]

HDLC

Transmitter

TOPS

Timing Options

TJAT

Digital Jitter

ttenuato

TLCLK[1:8]

TLD[1:8]

XCLK*

CICLK/MCICLK*

CIFP/MCIFP*

ICLK[1:2]/ISIG[1:2]/

MISIG[1:2]

IFP[1:2]/MIFP[1:2]

ID[3:8]

ICLK[3:8]/

ISIG[3:8]

IFP[3:8]

[10:0]*

RDB*

WRB*

CSB*

LE*

INTB*

RSTB*

D[7:0]*

BRIF

Ingress

Backplane

Interface

MPIF

Micro-

Processor

Interface

RECEIVER

ELST

Elastic

SIGX

RPSC

Per-

Channel

Controller

* These signals are shared between all eight framers.

Signaling

Extractor

Store

ELST

Elastic

Store

Framer:

lignment,

Extraction

RDLC[2:0]

Performance

Counters

FRMR

Frame

larm

HDLC

Receiver

PMON

Monitor

RJAT

Digital Jitter

ttenuato

JTAG

Test Access

Port

RLCLK[1:8]

RLD[1:8]

TDO

TDI

TCLK

TMS

TRSTB

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 8

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

6 DESCRIPTION

The PM6388 Octal E1 Framer (EOCTL) is a feature-rich device for use in systems

carrying data (frame relay, Point to Point Protocol, or other protocols) or voice over

E1 facilities. Each of the framers and transmitters is independently software

configurable, allowing feature selection without changes to external wiring.

On the receive side, each of eight independent framers can be configured to frame

to a basic G.704 2048 kbit/s signal as well as finding the signaling multiframe

alignment signal and the CRC multiframe alignment:. Framing can also be

bypassed (unframed mode). The EOCTL detects and indicates the presence

various alarm conditions such as loss of frame-alignment, loss of signaling

multiframe alignment, loss of CRC multiframe alignment, reception of remote alarm

indication signals, remote multiframe alarm signals, alarm indication signal (AIS),

and timeslot 16 alarm indication signal. The EOCTL integrates red and IS alarms as

per industry specifications. Performance monitoring with accumulation of CRC-4

errors, far-end block errors, framing bit errors, and out-of-frame events is provided.

The EOCTL also detects and terminates HDLC messages on TS16, the Sa National

bits, and/or on any arbitrary timeslot. Each HDLC link is terminated in a 128 byte

FIFO.

An elastic store that optionally supports slip buffering and adaptation to backplane

timing is provided, as is a signaling extractor that supports signaling debounce,

signaling freezing and interrupt on signaling state change on a per-channel basis.

The EOCTL also supports idle code substitution and detection, digital milliwatt code

insertion, data extraction, trunk conditioning, data inversion, and pattern generation

or detection on a per-channel basis.

On the transmit side, the EOCTL generates framing for a G.704 2048 kbit/s E1

signal. Framing can be optionally disabled. The signaling multiframe alignment

structure and the CRC multiframe structure may be optionally inserted. The EOCTL

supports signaling insertion, idle code substitution, data insertion, line loopback,

data inversion, and test pattern generation or detection on a per-channel basis.

Up to 3 HDLC links can be supported by the each octant of the EOCTL. Datalink

messages can be transmitted on TS16, the Sa National bits, and on an arbitrary

channel timeslot at the same time. The datalink messages may also be configured

to operate on 3 arbitrary channel timeslots.

The EOCTL can generate a low jitter transmit clock from a variety of clock

references, and also provides jitter attenuation in the receive path.

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 9

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

The EOCTL provides a parallel microprocessor interface for controlling the operation

of the EOCTL device. Serial PCM interfaces allow 2048 kbit/s ingress/egress

system interfaces to be directly supported.

The EOCTL also supports an alternate backplane interface where up to 4 links can

be byte-multiplexed onto one of two 8.192 Mbit/s buses. A link can be placed on

either bus. Slots which are not occupied by a link from the EOCTL device can be

used by other devices attached to the bus. This bus protocol is consistent with that

defined in the Mitel ST®, A T&T CHI® and MVIP PCM standards.

It should be noted that the EOCTL device operates on unipolar data only: HDB3

encoding and line code violation monitoring, if required, must be processed by the

E1 LIU.

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 10

PM6388 EOCTL

DATA SHEET

PMC-1971019 ISSUE 6 OCTAL E1 FRAMER

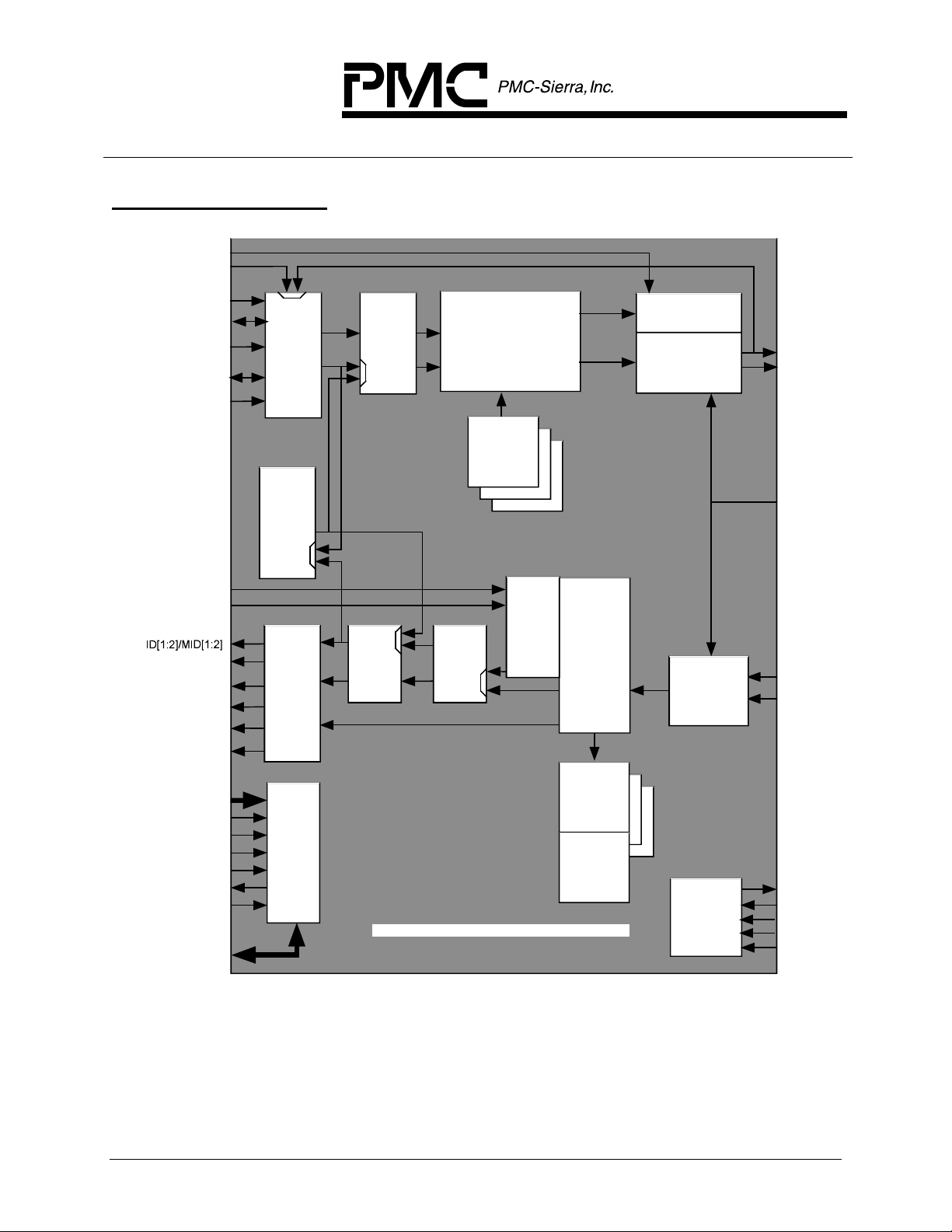

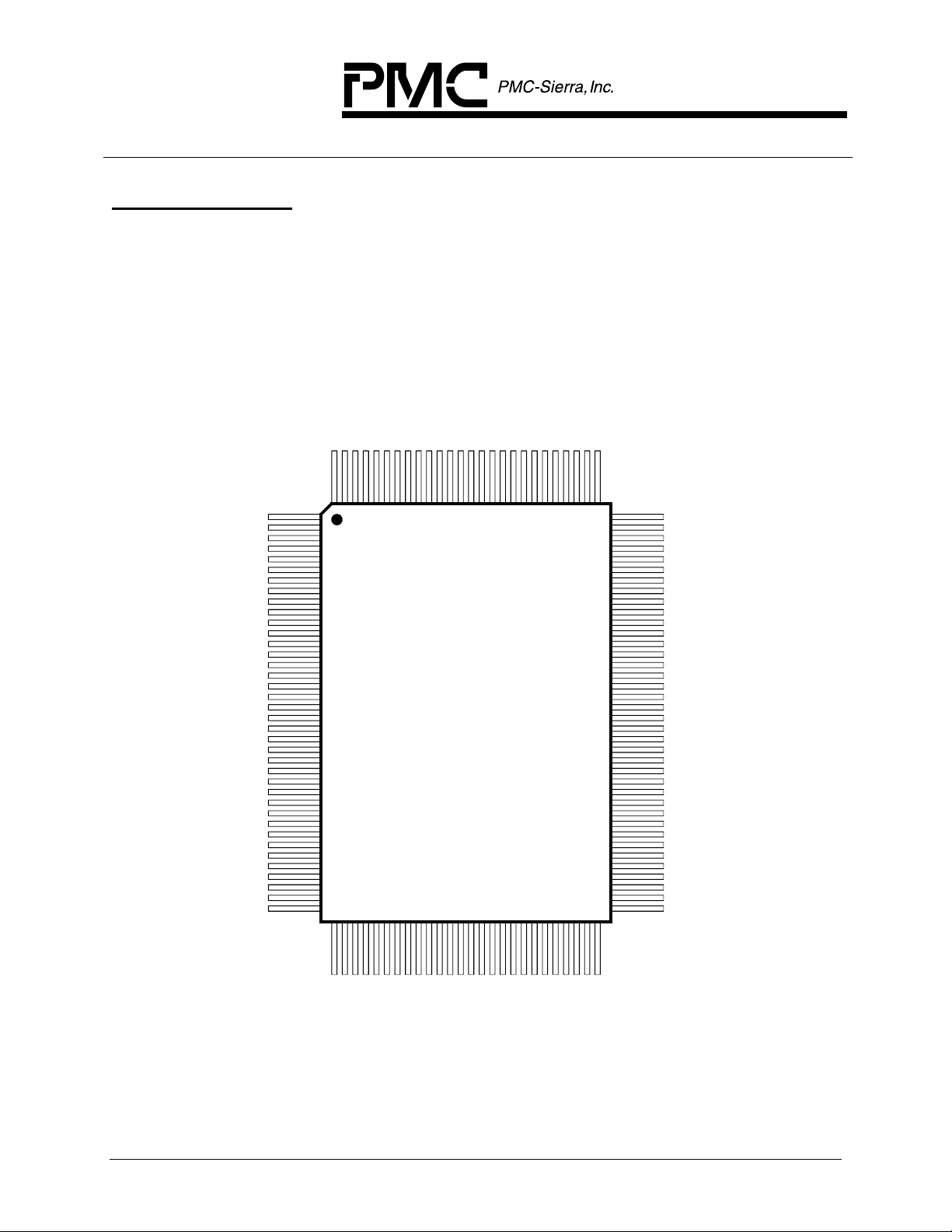

7 PIN DIAGRAM

The EOCTL is packaged in a 128-pin plastic QFP package having a body size of

14mm by 20mm and a pin pitch of 0.5 mm.

]

]

1

2

[

[

G

G

I

I

S

S

E

PIN 128

E

M

M

/

K

L

K

P

L

C

F

E

C

P

I

E

C

F

C

I

C

M

C

/

M

M

/

]

/

B

K

K

M

K

/

3

L

P

T

S

M

T

L

I

S

K

C

O

D

T

R

C

D

T

T

T

C

T

[

K

L

P

F

C

E

C

L

D

C

F

E

I

I

L

C

C

C

P

X

C

/

P

P

F

F

E

E

/

/

]

]

K

K

1

2

L

L

[

[

C

C

D

D

]

E

E

E

E

/

3

/

[

D

H

P

]

M

3

M

G

G

/

[

I

/

I

D

D

S

S

D

E

E

E

E

E

]

]

3

[

P

F

E

/

K

L

C

E

/

]

4

G

[

I

D

S

E

E

]

4

5

[

[

P

P

F

F

E

E

/

/

K

K

L

L

C

C

]

]

E

E

4

/

/

]

]

5

[

[

A

L

P

6

5

G

G

A

[

[

I

I

H

D

D

S

S

P

E

E

E

E

PIN 103

PIN 1

RLD[1]

RLCLK[1]

RLD[2]

RLCLK[2]

RLD[3]

RLCLK[3]

RLD[4]

RLCLK[4]

TLD[1]

TLCLK[1]

TLD[2]

TLCLK[2]

TLD[3]

TLCLK[3]

TLD[4]

TLCLK[4]

BIAS

PHA[0]

PLA[0]

PHD[0]

PLD[0]

TLD[5]

TLCLK[5]

TLD[6]

TLCLK[6]

TLD[7]

TLCLK[7]

TLD[8]

TLCLK[8]

PLA[1]

RLD[5]

RLCLK[5]

RLD[6]

RLCLK[6]

RLD[7]

RLCLK[7]

RLD[8]

RLCLK[8]

PIN 38

Index P in

PM6388

EOCTL

Top

View

PIN 102

ESIG/ECLK/EFP[6]

ED[7]

ESIG/ECLK/EFP[7]

ED[8]

ESIG/ECLK/EFP[8]

ID/M ID [1]

ICLK/ISIG /MISIG[ 1 ]

IFP/MIFP[1]

ID/M ID [2]

PLA[4]

PHA[3]

ICLK/ISIG /MISIG[ 2 ]

IFP/MIFP[2]

ID[3]

ICLK/ISIG [3]

IFP[3]

PLD[2]

PHD[2]

ID[4]

ICLK/ISIG [4]

IFP[4]

ID[5]

ICLK/ISIG [5]

IFP[5]

ID[6]

ICLK/ISIG [6]

IFP[6]

PLA[3]

PHA[2]

ID[7]

ICLK/ISIG [7]

IFP[7]

ID[8]

ICLK/ISIG [8]

IFP[8]

RDB

WRB

CSB

PIN 65

D[3]

D[4]

D[2]

D[1]

D[0]

INTB

RSTB

PHA[1]

D[7]

D[6]

PLA[2]

D[5]

PHD[1]

ALE

PLD[1]

A[4]

A[3]

A[2]

A[0]

A[1]

A[8]

A[7]

A[10]

A[9]

A[5]

A[6]

PIN 39 PIN 64

PROPRIETARY and CONFIDENTIAL to PMC-Sierra Inc. and for its customers’ internal use 11

Loading...

Loading...